ADS8363, ADS7263, ADS7223

SBAS523D - OCTOBER 2010-REVISED SEPTEMBER 2017

# ADSxxx3 Dual, 1-MSPS, 16-, 14-, and 12-Bit, 4x2 or 2x2 Channel, Simultaneous Sampling Analog-to-Digital Converter

#### 1 Features

- Eight Pseudo- or Four Fully-Differential Inputs

- Simultaneous Sampling of Two Channels

- Excellent AC Performance:

- SNR:

- 93 dB (ADS8363)

- 85 dB (ADS7263)

- 73 dB (ADS7223)

- THD:

- -98 dB (ADS8363)

- -92 dB (ADS7263)

- -86 dB (ADS7223)

- Dual Programmable and Buffered 2.5-V Reference Allows:

- Two Different Input Voltage Range Settings

- Two-Level PGA Implementation

- Programmable Auto-Sequencer

- Integrated Data Storage (up to 4 per channel) for Oversampling Applications

- 2-Bit Counter for Safety Applications

- Fully Specified Over the Extended Industrial Temperature Range: -40°C to +125°C

#### 2 Applications

- Motor Control: Current and Position Measurement including Safety Applications

- · Power Quality Measurement

- Three-Phase Power Control

- Programmable Logic Controllers

- Industrial Automation

- Protection Relays

## 3 Description

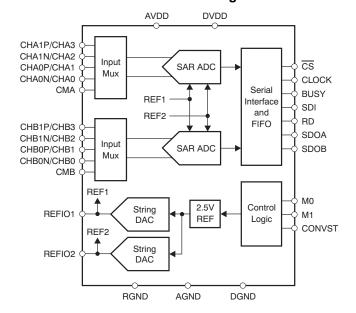

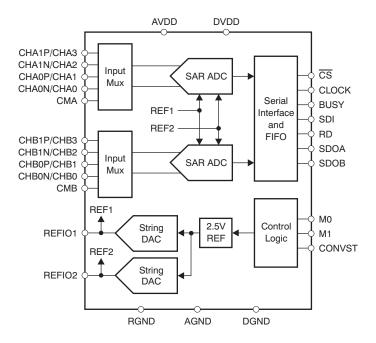

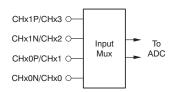

The ADS8363 is a dual, 16-bit, 1-MSPS analog-to-digital converter (ADC) with eight pseudo- or four fully-differential input channels grouped into two pairs for simultaneous signal acquisition. The analog inputs are maintained differentially to the input of the ADC. The input multiplexer can be used in either pseudo-differential mode, supporting up to four channels per ADC (4x2), or in fully-differential mode that allows to convert up to two inputs per ADC (2x2). The ADS7263 is a 14-bit version and the ADS7223 is a 12-bit version of the ADS8363.

The ADS8363, ADS7263, and ADS7223 offer two programmable reference outputs, flexible supply voltage ranges, a programmable auto-sequencer, data storage of up to four conversion results per channel, and several power-down features.

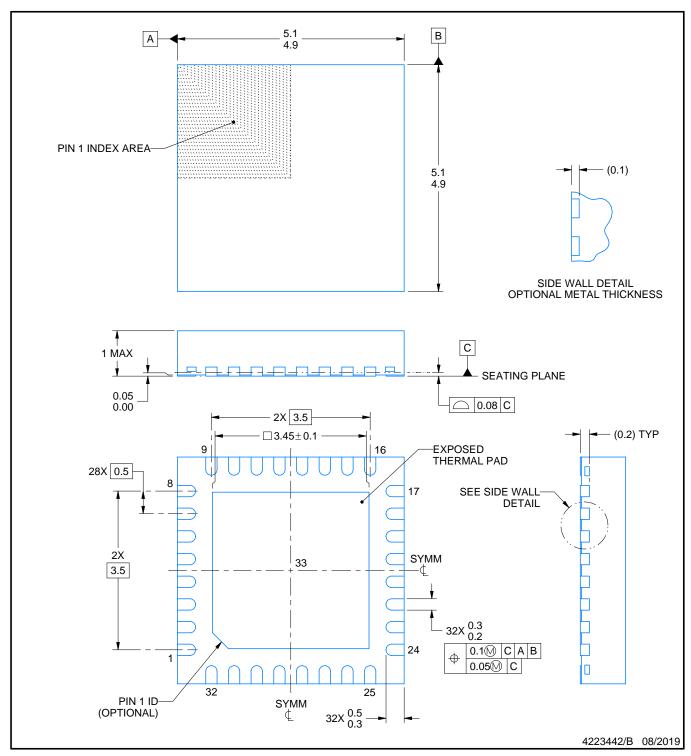

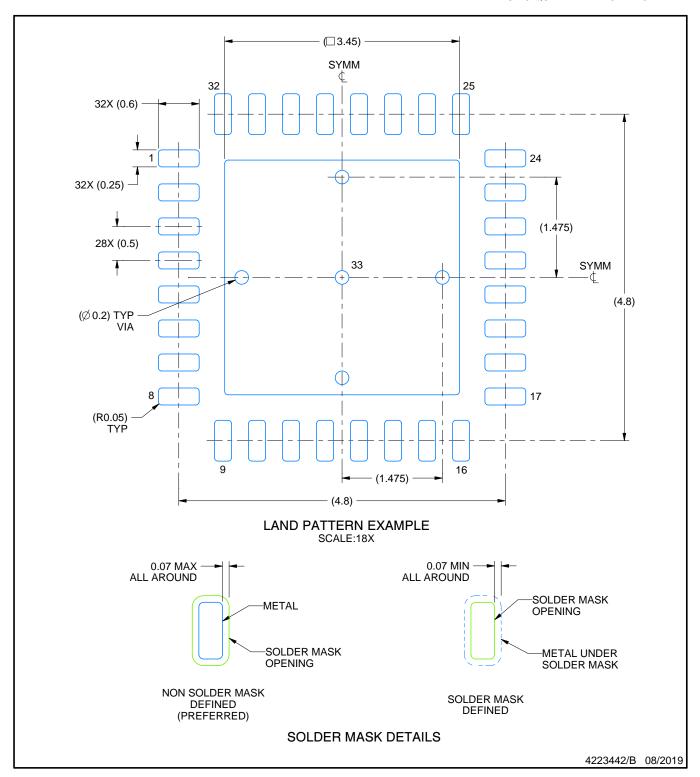

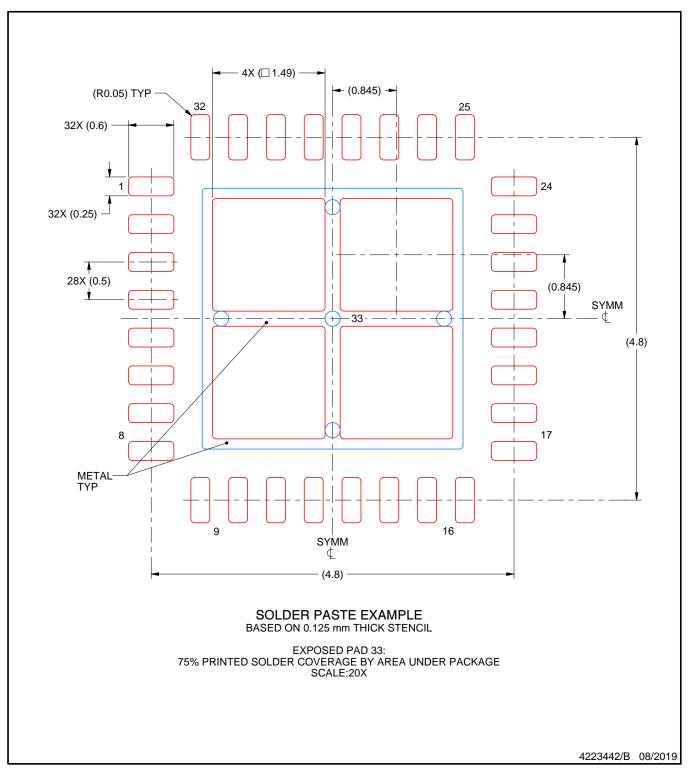

All devices are offered in a 5-mm x 5-mm, 32-pin VQFN package.

## Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)   |

|-------------|-----------|-------------------|

| ADSxxx3     | VQFN (32) | 5.00 mm x 5.00 mm |

(1) For all available packages, see the package option addendum at the end of the data sheet.

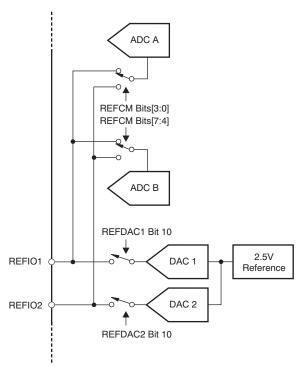

## **Functional Block Diagram**

Page

#### **Table of Contents**

| 1 | Features 1                              |    | 8.3 Feature Description                             | 19    |

|---|-----------------------------------------|----|-----------------------------------------------------|-------|

| 2 | Applications 1                          |    | 8.4 Device Functional Modes                         | 24    |

| 3 | Description 1                           |    | 8.5 Programming                                     | 26    |

| 4 | Revision History                        |    | 8.6 Register Maps                                   | 34    |

| 5 | Device Comparison Table 4               | 9  | Application and Implementation                      | 42    |

| 6 | Pin Configuration and Functions 4       |    | 9.1 Application Information                         | 42    |

| 7 | Specifications                          | 10 | Power Supply Recommendations                        | 45    |

| • | 7.1 Absolute Maximum Ratings            | 11 | Layout                                              | 46    |

|   | 7.2 ESD Ratings                         |    | 11.1 Layout Guidelines                              | 46    |

|   | 7.3 Recommended Operating Conditions    |    | 11.2 Layout Example                                 | 47    |

|   | 7.4 Thermal Information                 | 12 | Device and Documentation Support                    | 48    |

|   | 7.5 Electrical Characteristics: General |    | 12.1 Documentation Support                          |       |

|   | 7.6 Electrical Characteristics: ADS8363 |    | 12.2 Related Links                                  | 48    |

|   | 7.7 Electrical Characteristics: ADS7263 |    | 12.3 Receiving Notification of Documentation Update | es 48 |

|   | 7.8 Electrical Characteristics: ADS7223 |    | 12.4 Community Resources                            | 48    |

|   | 7.9 Switching Characteristics           |    | 12.5 Trademarks                                     | 48    |

|   | 7.10 Typical Characteristics            |    | 12.6 Electrostatic Discharge Caution                | 48    |

| 8 | Detailed Description                    |    | 12.7 Glossary                                       | 48    |

| Ū | 8.1 Overview                            | 13 | Mechanical, Packaging, and Orderable                | 40    |

|   | 8.2 Functional Block Diagram            |    | Information                                         | 48    |

|   |                                         |    |                                                     |       |

|   |                                         |    |                                                     |       |

## 4 Revision History

Changes from Revision C (January 2017) to Revision D

| CI | hanges from Revision B (January 2011) to Revision C                                                                                                                                                                                                                                                                                                           |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| •  | Added Device Information table, ESD Ratings table, Recommended Operating Conditions table, Feature Description section, Device Functional Modes section, Application and Implementation section, Power Supply Recommendations section, Layout section, Device and Documentation Support section, and Mechanical, Packaging, and Orderable Information section |

| •  | Changed ADS8363/7263/7223 to ADS8363, ADS7263, and ADS7223 throughout document                                                                                                                                                                                                                                                                                |

| •  | Changed Description section: changed last sentence of first paragraph and last paragraph                                                                                                                                                                                                                                                                      |

| •  | Changed Device Comparison Table title                                                                                                                                                                                                                                                                                                                         |

| •  | Changed Pin Configuration and Functions section title                                                                                                                                                                                                                                                                                                         |

| •  | Changed footnote of Figure 1 and for clarity                                                                                                                                                                                                                                                                                                                  |

| •  | Changed second and third columns of <i>Midscale – 1 LSB</i> row in <i>Output Data Format</i> table: changed –V <sub>REF</sub> to –2V <sub>REF</sub> in column 2, changed last two voltage values in column 3                                                                                                                                                  |

| •  | Changed footnote of Figure 31                                                                                                                                                                                                                                                                                                                                 |

| •  | Changed footnote of Figure 32                                                                                                                                                                                                                                                                                                                                 |

| •  | Changed footnote of Figure 33                                                                                                                                                                                                                                                                                                                                 |

| Cł | nanges from Revision A (December, 2010) to Revision B                                 | Page |

|----|---------------------------------------------------------------------------------------|------|

| •  | Revised test conditions for gain error parameter                                      | 9    |

| •  | Revised test conditions for gain error parameter                                      |      |

| •  | Revised test conditions for gain error parameter                                      | 10   |

| •  | Updated CONVST high time specification                                                | 1′   |

| •  | Revised CONVST section                                                                |      |

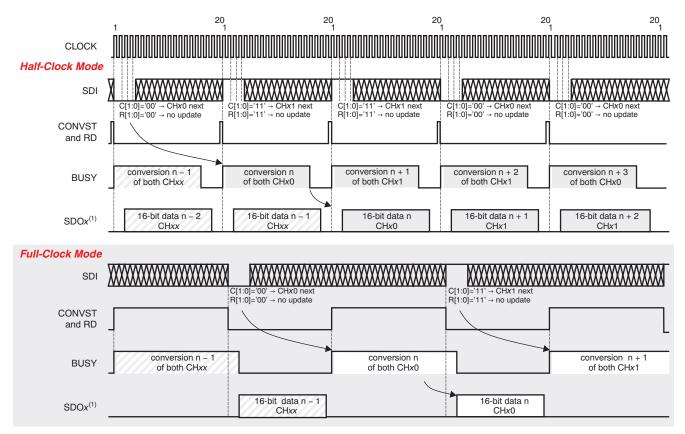

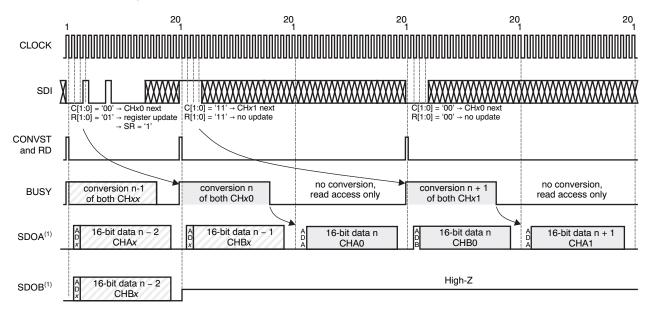

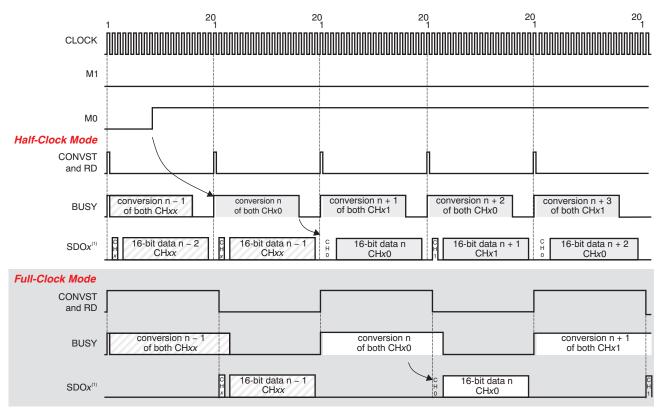

| •  | Revised Mode II section                                                               | 28   |

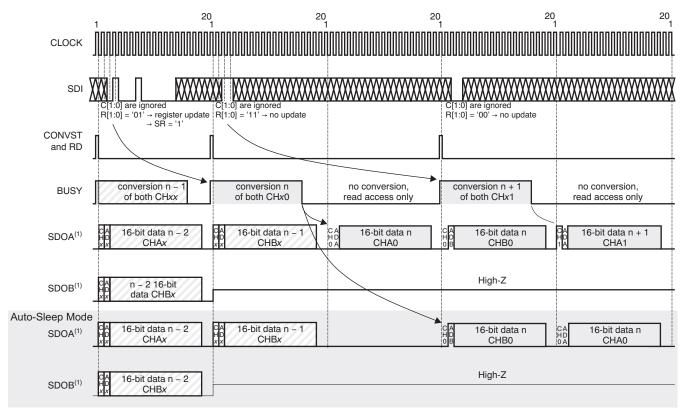

| •  | Revised Special Read Mode II section                                                  | 29   |

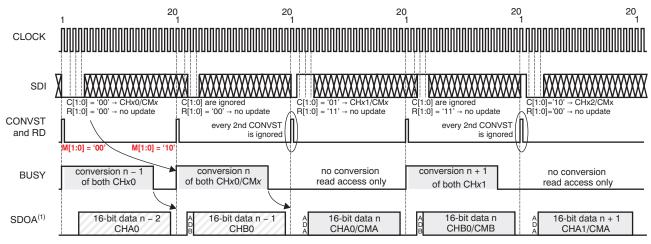

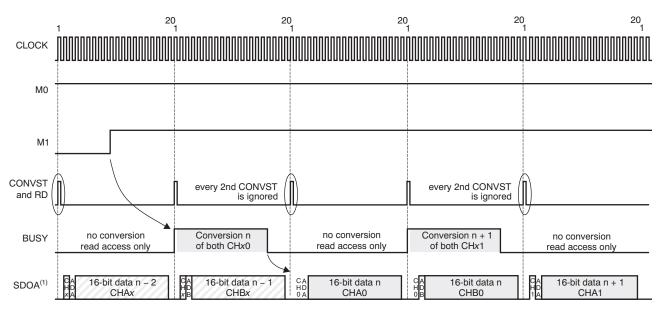

| •  | Revised Fully-Differential Mode IV section                                            | 3′   |

| •  | Revised Special Mode IV section                                                       | 32   |

| •  | Added CONVST section in ADS8361 Compatibility                                         | 43   |

| Cł | nanges from Original (October, 2010) to Revision A                                    | Page |

| •  | Added RD high time (t <sub>3</sub> ) parameter to <i>Timing Characteristics</i> table | 1.   |

|    | Updated Figure 1                                                                      |      |

|    | Revised RD section in ADS8361 Compatibility                                           |      |

|    | Added t <sub>3</sub> timing trace to Figure 48                                        | 4!   |

| •  | Deleted Four-Wire Application Timing Requirements table                               |      |

|    |                                                                                       |      |

## 5 Device Comparison Table

| PRODUCT | RESOLUTION | NMC                          | INL                         | SNR         | THD          |

|---------|------------|------------------------------|-----------------------------|-------------|--------------|

| ADS8363 | 16 bits    | 16 or 15 bits <sup>(1)</sup> | ±3 or ±4 LSB <sup>(1)</sup> | 93 dB (typ) | -98 dB (typ) |

| ADS7263 | 14 bits    | 14 bits                      | ±1 LSB                      | 85 dB (typ) | -92 dB (typ) |

| ADS7223 | 12 bits    | 12 bits                      | ±0.5 LSB                    | 73 dB (typ) | -86 dB (typ) |

<sup>(1)</sup> See the *Electrical Characteristics* table.

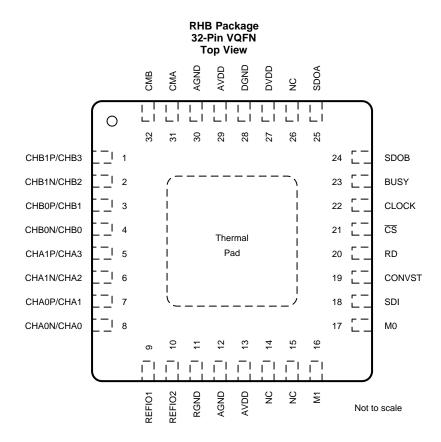

## 6 Pin Configuration and Functions

## **Pin Functions**

| PIN        |        |                     |                                                                                                                                |  |

|------------|--------|---------------------|--------------------------------------------------------------------------------------------------------------------------------|--|

| NAME       | NO.    | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                    |  |

| AGND       | 12, 30 | Р                   | Analog ground. Connect to analog ground plane.                                                                                 |  |

| AVDD       | 13, 29 | Р                   | Analog power supply, 2.7 V to 5.5 V. Decouple to AGND with a 1-μF ceramic capacitor.                                           |  |

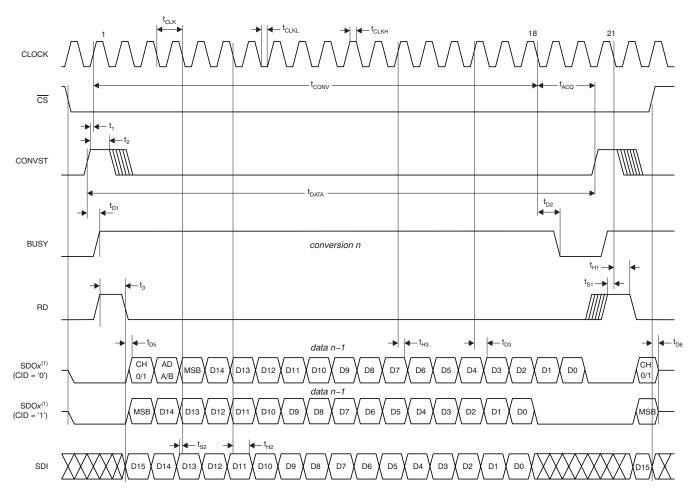

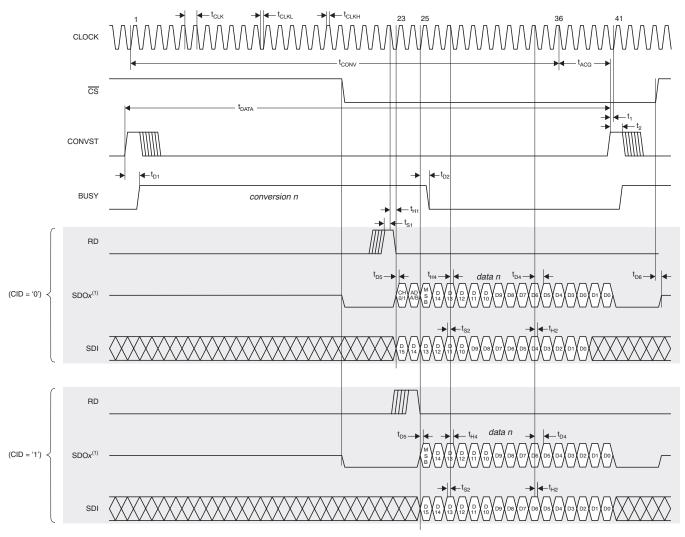

| BUSY       | 23     | DO                  | Converter busy indicator. BUSY goes high when the inputs are in hold mode and returns to low after the conversion is complete. |  |

| CHA0N/CHA0 | 8      | Al                  | Fully-differential inverting analog input channel A1 or pseudo-differential input A0                                           |  |

| CHA0P/CHA1 | 7      | Al                  | differential noninverting analog input channel A1 or pseudo-differential input A1                                              |  |

| CHA1N/CHA2 | 6      | Al                  | differential inverting analog input channel A1 or pseudo-differential input A2                                                 |  |

| CHA1P/CHA3 | 5      | Al                  | Fully-differential noninverting analog input channel A1 or pseudo-differential input A3                                        |  |

| CHB0N/CHB0 | 4      | Al                  | Fully-differential inverting analog input channel B0 or pseudo-differential input B0                                           |  |

| CHB0P/CHB1 | 3      | Al                  | Fully-differential noninverting analog input channel B0 or pseudo-differential input B1                                        |  |

| CHB1N/CHB2 | 2      | Al                  | Fully-differential inverting analog input channel B1 or pseudo-differential input B2                                           |  |

| CHB1P/CHB3 | 1      | Al                  | Fully-differential noninverting analog input channel B1 or pseudo-differential input B3                                        |  |

AI = analog input, AIO = analog input/output, DI = digital input, DO = digital output, DIO = digital input/output, P = power supply, NC = not connected.

## Pin Functions (continued)

| PI     | IN         |                     |                                                                                                                                                                           |

|--------|------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME   | NO.        | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                               |

| CLOCK  | 22         | DI                  | External clock input. The range is 0.5 MHz to 20 MHz in half-clock mode, or 1 MHz to 40 MHz in full-clock mode.                                                           |

| CMA    | 31         | Al                  | Common-mode voltage input for channels Ax (in pseudo-differential mode only).                                                                                             |

| СМВ    | 32         | Al                  | Common-mode voltage input for channels Bx (in pseudo-differential mode only).                                                                                             |

| CONVST | 19         | DI                  | Conversion start. The ADC switches from sample into hold mode on the rising edge of CONVST. Thereafter, the conversion starts with the next rising edge of the CLOCK pin. |

| CS     | 21         | DI                  | Chip select. When this pin is low, the SDOx, SDI, and RD pins are active; when this pin is high, the SDOx outputs are 3-stated, and the SDI and RD inputs are ignored.    |

| DGND   | 28         | Р                   | Digital ground. Connect to digital ground plane.                                                                                                                          |

| DVDD   | 27         | Р                   | Digital supply, 2.3 V to 5.5 V. Decouple to DGND with a 1-μF ceramic capacitor.                                                                                           |

| MO     | 17         | DI                  | Mode pin 0. Selects analog input channel mode (see Table 5).                                                                                                              |

| M1     | 16         | DI                  | Mode pin 1. Selects the digital output mode (see Table 5).                                                                                                                |

| NC     | 14, 15, 26 | NC                  | This pin is not internally connected.                                                                                                                                     |

| RD     | 20         | DI                  | Read data. Synchronization pulse for the SDOx outputs and SDI input. RD only triggers when $\overline{CS}$ is low.                                                        |

| REFIO1 | 9          | AIO                 | Reference voltage input/output 1. A ceramic capacitor of 22 µF connected to RGND is required.                                                                             |

| REFIO2 | 10         | AIO                 | Reference voltage input/output 2. A ceramic capacitor of 22 µF connected to RGND is required.                                                                             |

| RGND   | 11         | Р                   | Reference ground. Connect to analog ground plane with a dedicated via.                                                                                                    |

| SDI    | 18         | DI                  | Serial data input. This pin is used to set up of the internal registers, and can also be used in ADS8361-compatible manner. The data on SDI are ignored when CS is high.  |

| SDOA   | 25         | DO                  | Serial data output for converter A. 3-state when $\overline{\text{CS}}$ is high.                                                                                          |

| SDOB   | 24         | DO                  | Serial data output for converter B. Active only if M1 is low. 3-state when $\overline{\text{CS}}$ is high.                                                                |

## 7 Specifications

#### 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

|                                                         | MIN        | MAX                       | UNIT |

|---------------------------------------------------------|------------|---------------------------|------|

| Supply voltage, AVDD to AGND or DVDD to DGND            | -0.3       | 6                         | V    |

| Supply voltage, DVDD to AVDD                            |            | 1.2 × AVDD <sup>(2)</sup> | V    |

| Analog and reference input voltage with respect to AGND | AGND - 0.3 | AVDD + 0.3                | V    |

| Digital input voltage with respect to DGND              | DGND - 0.3 | DVDD + 0.3                | V    |

| Ground voltage difference  AGND-DGND                    |            | 0.3                       | V    |

| Input current to any pin except supply pins             | -10        | 10                        | mA   |

| Maximum virtual junction temperature, T <sub>J</sub>    |            | 150                       | °C   |

| Storage temperature, T <sub>stg</sub>                   | -65        | 150                       | °C   |

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 7.2 ESD Ratings

|                    |                         |                                                                                | VALUE | UNIT |

|--------------------|-------------------------|--------------------------------------------------------------------------------|-------|------|

| \/                 | Floatroatatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)                         | ±2000 | \/   |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±500  | V    |

JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|      |                        | MIN | NOM | MAX | UNIT |

|------|------------------------|-----|-----|-----|------|

| AVDD | Analog supply voltage  |     | 5   |     | V    |

| DVDD | Digital supply voltage |     | 3.3 |     | V    |

|      | Operating temperature  | -40 |     | 125 | °C   |

## 7.4 Thermal Information

|                      |                                              | ADS8363, ADS7263, ADS7223                                                                                                                                                                                                  |      |

|----------------------|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | RHB (VQFN)         UNIT           32 PINS         33.3         °C/W           nce         39.5         °C/W           7.3         °C/W           meter         0.2         °C/W           rameter         7.4         °C/W |      |

|                      |                                              | 32 PINS                                                                                                                                                                                                                    |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 33.3                                                                                                                                                                                                                       | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 29.5                                                                                                                                                                                                                       | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 7.3                                                                                                                                                                                                                        | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter   | 0.2                                                                                                                                                                                                                        | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 7.4                                                                                                                                                                                                                        | °C/W |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | 0.9                                                                                                                                                                                                                        | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

Exceeding the specified limit causes an increase of the DVDD leakage current and leads to malfunction of the device.

## 7.5 Electrical Characteristics: General

All minimum and maximum specifications at  $T_A = -40$ °C to +125°C, specified supply voltage range, VREF = 2.5 V (int), and  $t_{DATA} = 1$  MSPS (unless otherwise noted). Typical values are at  $T_A = +25$ °C, AVDD = 5 V, and DVDD = 3.3 V.

|                          | PARAMETER                                             | TEST CONDITIONS                | MIN                    | TYP   | MAX               | UNIT             |

|--------------------------|-------------------------------------------------------|--------------------------------|------------------------|-------|-------------------|------------------|

| ANALOG INI               | PUT                                                   |                                |                        |       |                   |                  |

| FSR                      | Full-scale input range                                | (CHxxP – CHxxN) or CHxx to CMx | -V <sub>REF</sub>      |       | +V <sub>REF</sub> | V                |

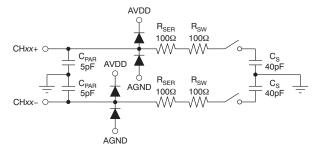

| V <sub>IN</sub>          | Absolute input voltage                                | CHxxx to AGND                  | -0.1                   |       | AVDD + 0.1        | V                |

| C <sub>IN</sub>          | Input capacitance                                     | CHxxx to AGND                  |                        | 45    |                   | pF               |

| C <sub>ID</sub>          | Differential input capacitance                        |                                |                        | 22.5  |                   | pF               |

| I <sub>IL</sub>          | Input leakage current                                 |                                | -16                    |       | 16                | nA               |

| PSRR                     | Power-supply rejection ratio                          | AVDD = 5.5 V                   |                        | 75    |                   | dB               |

| SAMPLING I               | DYNAMICS                                              |                                | 1                      |       | •                 |                  |

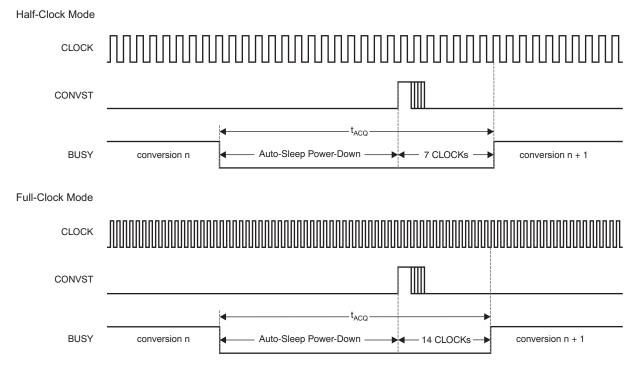

|                          | 0                                                     | Half-clock mode                | 17.5                   |       |                   |                  |

| tCONV                    | Conversion time per ADC                               | Full-clock mode                | 35                     |       |                   | t <sub>CLK</sub> |

|                          |                                                       | Half-clock mode                | 2                      |       |                   |                  |

| t <sub>ACQ</sub>         | Acquisition time                                      | Full-clock Mode                | 4                      |       |                   | t <sub>CLK</sub> |

| f <sub>DATA</sub>        | Data rate                                             |                                | 25                     |       | 1000              | kSPS             |

| t <sub>A</sub>           | Aperture delay                                        |                                |                        |       | 6                 | ns               |

|                          | t <sub>A</sub> match                                  | ADC to ADC                     |                        | 50    |                   | ps               |

| t <sub>AJIT</sub>        | Aperture jitter                                       |                                |                        | 50    |                   | ps               |

| ,                        | Olask formula                                         | Half-clock mode                | 0.5                    |       | 20                | N 41 1           |

| f <sub>CLK</sub>         | Clock frequency                                       | Full-clock mode                | 1                      |       | 40                | MHz              |

|                          | Clashanariad                                          | Half-clock mode                | 50                     |       | 2000              | 20               |

| tCLK                     | Clock period                                          | Full-clock mode                | 25                     |       | 1000              | ns               |

| INTERNAL V               | OLTAGE REFERENCE                                      |                                |                        |       | •                 |                  |

| Resolution               | Reference output DAC resolution                       |                                | 10                     |       |                   | Bits             |

|                          |                                                       | Over 20% to 100% DAC range     | 0.2V <sub>REFOUT</sub> |       | $V_{REFOUT}$      |                  |

| $V_{REFOUT}$             | Reference output voltage                              | REFIO1, DAC = 3FFh             | 2.485                  | 2.500 | 2.515             | V                |

|                          |                                                       | REFIO2, DAC = 3FFh             | 2.480                  | 2.500 | 2.520             |                  |

| dV <sub>REFOUT</sub> /dT | Reference voltage drift                               |                                |                        | ±10   |                   | ppm/°            |

| DNL <sub>DAC</sub>       | DAC differential linearity error                      |                                | -4                     | ±1    | 4                 | LSB              |

| INL <sub>DAC</sub>       | DAC integral linearity error                          |                                | -4                     | ±0.5  | 4                 | LSB              |

| V <sub>OSDAC</sub>       | DAC offset error                                      | V <sub>REFOUT</sub> = 0.5 V    | -4                     | ±1    | 4                 | LSB              |

| PSRR                     | Power-supply rejection ratio                          |                                |                        | 73    |                   | dB               |

| I <sub>REFOUT</sub>      | Reference output dc current                           |                                | -2                     |       | +2                | mA               |

| I <sub>REFSC</sub>       | Reference output short-circuit current <sup>(1)</sup> |                                |                        | 50    |                   | mA               |

| t <sub>REFON</sub>       | Reference output settling time                        | $C_{REF} = 22 \mu F$           |                        | 8     |                   | ms               |

| VOLTAGE R                | EFERENCE INPUT                                        |                                |                        |       | '                 |                  |

| V <sub>REF</sub>         | Reference input voltage range                         |                                | 0.5                    | 2.5   | 2.525             | V                |

| I <sub>REF</sub>         | Reference input current                               |                                |                        | 50    |                   | μΑ               |

| C <sub>REF</sub>         | External ceramic reference capacitance                |                                |                        | 22    |                   | μF               |

<sup>(1)</sup> Reference output current is not internally limited.

## **Electrical Characteristics: General (continued)**

All minimum and maximum specifications at  $T_A = -40$ °C to +125°C, specified supply voltage range, VREF = 2.5 V (int), and  $t_{DATA} = 1$  MSPS (unless otherwise noted). Typical values are at  $T_A = +25$ °C, AVDD = 5 V, and DVDD = 3.3 V.

|                   | PARAMETER                 | TEST CONDITIONS                              | MIN        | TYP            | MAX       | UNIT |  |

|-------------------|---------------------------|----------------------------------------------|------------|----------------|-----------|------|--|

| DIGITAL I         | NPUTS <sup>(2)</sup>      |                                              |            |                | <u>'</u>  |      |  |

| I <sub>IN</sub>   | Input current             | V <sub>IN</sub> = DVDD to DGND               | -50        |                | +50       | nA   |  |

| C <sub>IN</sub>   | Input capacitance         |                                              |            | 5              |           | pF   |  |

|                   | Logic family              |                                              | CMOS wi    | th Schmitt-Tri | gger      |      |  |

| V <sub>IH</sub>   | High-level input voltage  | DVDD = 4.5 V to 5.5 V                        | 0.7DVDD    | D'             | VDD + 0.3 | V    |  |

| V <sub>IL</sub>   | Low-level input voltage   | DVDD = 4.5 V to 5.5 V                        | -0.3       |                | 0.3DVDD   | V    |  |

|                   | Logic family              |                                              | l          | VCMOS          |           |      |  |

| V <sub>IH</sub>   | High-level input voltage  | DVDD = 2.3 V to 3.6 V                        | 2          | D'             | VDD + 0.3 | V    |  |

| V <sub>IL</sub>   | Low-level input voltage   | DVDD = 2.3 V to 3.6 V                        | -0.3       |                | 0.8       | V    |  |

| DIGITAL (         | OUTPUTS <sup>(2)</sup>    | 1                                            |            |                |           |      |  |

| C <sub>OUT</sub>  | Output capacitance        |                                              |            | 5              |           | pF   |  |

| C <sub>LOAD</sub> | Load capacitance          |                                              |            |                | 30        | pF   |  |

|                   | Logic family              |                                              |            | CMOS           |           | ·    |  |

| V <sub>OH</sub>   | High-level output voltage | DVDD = 4.5 V, $I_{OH} = -100 \mu A$          | 4.44       |                |           | V    |  |

| V <sub>OL</sub>   | Low-level output voltage  | DVDD = 4.5 V, I <sub>OH</sub> = +100 μA      |            |                | 0.5       | V    |  |

|                   | Logic family              |                                              | l          | VCMOS          |           |      |  |

| V <sub>OH</sub>   | High-level output voltage | DVDD = 2.3 V, I <sub>OH</sub> = -100 μA      | DVDD - 0.2 |                |           | V    |  |

| V <sub>OL</sub>   | Low-level output voltage  | DVDD = 2.3 V, I <sub>OH</sub> = +100 μA      |            |                | 0.2       | V    |  |

| POWER S           | SUPPLY                    |                                              |            |                |           |      |  |

|                   |                           | AVDD to AGND, half-clock mode                | 2.7        | 5.0            | 5.5       |      |  |

| AVDD              | Analog supply voltage     | AVDD to AGND, full-clock mode                | 4.5        | 5.0            | 5.5       | V    |  |

|                   |                           | 3-V and 3.3-V levels                         | 2.3        | 2.5            | 3.6       |      |  |

| DVDD              | Digital supply voltage    | 5-V levels, half-clock mode only             | 4.5        | 5.0            | 5.5       | V    |  |

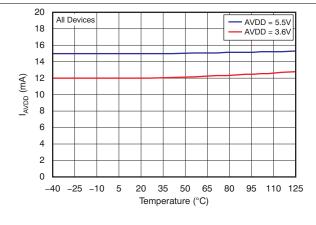

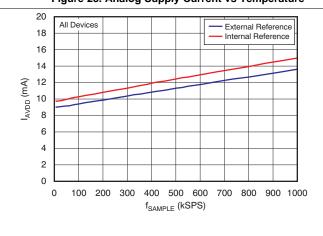

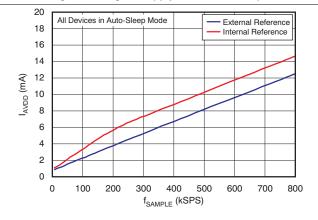

|                   |                           | AVDD = 3.6 V                                 |            | 12.0           | 16.0      |      |  |

|                   |                           | AVDD = 5.5 V                                 |            | 15.0           | 20.0      |      |  |

| AIDD              | Analog supply current     | AVDD = 3.6 V, sleep and auto-<br>sleep modes |            | 0.8            | 1.2       | mA   |  |

|                   |                           | AVDD = 5.5 V, sleep and auto-<br>sleep modes |            | 0.9            | 1.4       |      |  |

|                   |                           | Power-down mode                              |            |                | 0.005     |      |  |

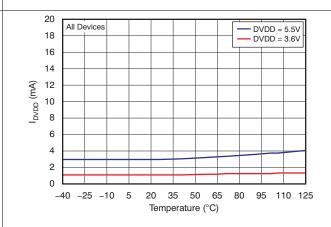

| DIDD              | British I is a            | DVDD = 3.6 V, C <sub>LOAD</sub> = 10 pF      |            | 1.1            | 2.5       |      |  |

| DIDD              | Digital supply current    | DVDD = 5.5 V, C <sub>LOAD</sub> = 10 pF      |            | 3              | 6         | mA   |  |

|                   | Power dissipation (normal | AVDD = DVDD = 3.6 V                          |            | 47.2           | 66.6      |      |  |

| $P_{D}$           | operation)                | AVDD = 5.5 V, DVDD = 3.6 V                   |            | 86.5           | 117.0     | mW   |  |

<sup>(2)</sup> Specified by design; not production tested.

#### 7.6 Electrical Characteristics: ADS8363

All minimum and maximum specifications at  $T_A = -40^{\circ}\text{C}$  to +125°C, specified supply voltage range, VREF = 2.5 V (int), and  $t_{DATA} = 1$  MSPS (unless otherwise noted). Typical values are at  $T_A = +25^{\circ}\text{C}$ , AVDD = 5 V, and DVDD = 3.3 V.

| INL Integral nonlinearity  Full-clock mode  -4 ±  Half-clock mode  -0.99 ±  Full-clock mode  -1.5 ±  Vos Input offset error  Vos match  ADC to ADC  -1 ±  dVos/dT Input offset thermal drift  Gers Gain error  Gers (AT Gain error thermal drift  Referenced to the voltage at                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1.2 +3<br>1.5 +4<br>0.6 +2<br>0.8 +3<br>0.2 +2 | - LSB<br>- LSB |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|----------------|

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1.5 +4<br>0.6 +2<br>0.8 +3                     | LSB<br>LSB     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1.5 +4<br>0.6 +2<br>0.8 +3                     | - LSB<br>- LSB |

| INL Integral nonlinearity  Full-clock mode  -4 ±  Half-clock mode  -0.99 ±  Full-clock mode  -1.5 ±  Vos Input offset error  Vos match  dVos/dT Input offset thermal drift  Gerral Gain error  Gerral Gain error  Gerral Gain error thermal drift  Referenced to the voltage at REFIOx  Referenced to the voltage at                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1.5 +4<br>0.6 +2<br>0.8 +3                     | - LSB<br>- LSB |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0.6 +2<br>0.8 +3                               | LSB            |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0.8 +3                                         | LSB            |

| Full-clock mode  -1.5 ±  V <sub>OS</sub> Input offset error  V <sub>OS</sub> match  ADC to ADC  -1 ±  dV <sub>OS</sub> /dT Input offset thermal drift  G <sub>ERR</sub> Gain error  G <sub>ERR</sub> match  ADC to ADC  -0.1% ±0.00  Referenced to the voltage at  REFIOX  ADC to ADC  -0.1% ±0.00  Referenced to the voltage at                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                |                |

| $V_{OS}$ match ADC to ADC $-1$ $\pm$ $dV_{OS}/dT$ Input offset thermal drift $G_{ERR}$ Gain error Referenced to the voltage at REFIOx $-0.1\%$ $\pm 0.0$ $G_{ERR}$ match ADC to ADC $-0.1\%$ $\pm 0.00$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ).2 +2                                         | mV             |

| dV <sub>OS</sub> /dT Input offset thermal drift  G <sub>ERR</sub> Gain error Referenced to the voltage at REFIOx  G <sub>ERR</sub> match ADC to ADC -0.1% ±0.00  G <sub>ERR</sub> match Referenced to the voltage at Referenced to the voltage at Referenced to the voltage at                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                |                |

| $G_{ERR}$ Gain error     Referenced to the voltage at REFIOx $-0.1\%$ $\pm 0.0$ $G_{ERR}$ match     ADC to ADC $-0.1\%$ $\pm 0.00$ $G_{ERR}$ match     Referenced to the voltage at Referenced to the Referenced to th | 0.1 +1                                         | mV             |

| GERR Gain error thermal drift  REFIOx  ADC to ADC  —0.1% ±0.00  Referenced to the voltage at                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1                                              | μV/°C          |

| Garage of the root thermal drift  Referenced to the voltage at                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1% +0.1%                                       |                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5% +0.1%                                       |                |

| REFIOx                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1                                              | ppm/°C         |

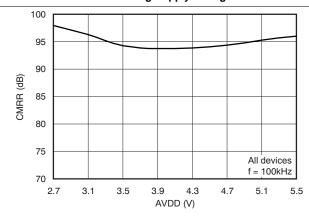

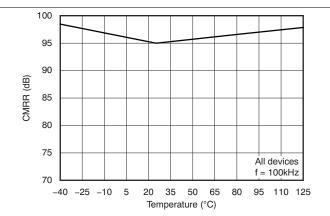

| CMRR Common-mode rejection ratio Both ADCs, dc to 100 kHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 92                                             | dB             |

| AC ACCURACY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                |                |

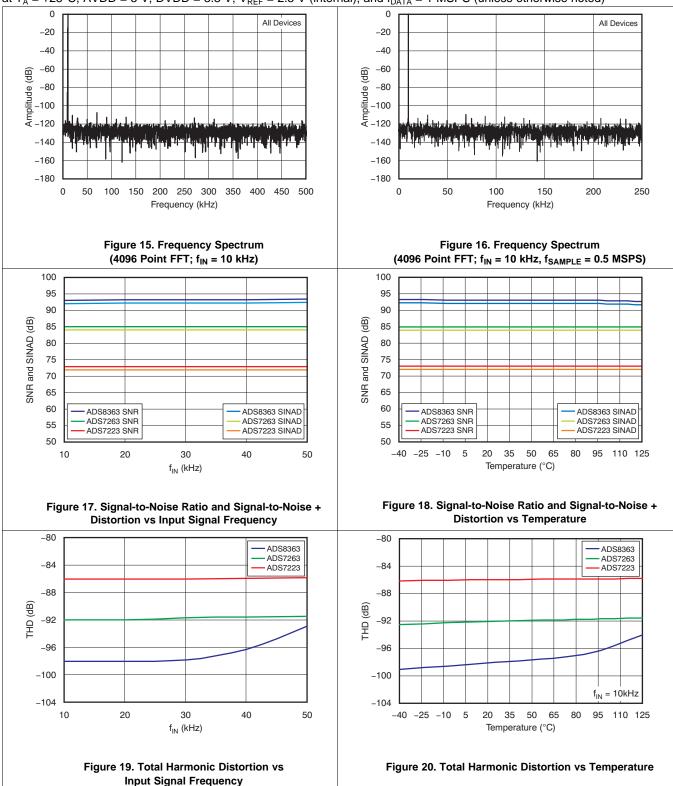

| SINAD Signal-to-noise + distortion $V_{IN} = 5 V_{PP}$ at 10 kHz 89                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 92                                             | dB             |

| SNR Signal-to-noise ratio $V_{IN} = 5 V_{PP}$ at 10 kHz 90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 93                                             | dB             |

| THD Total harmonic distortion $V_{IN} = 5 V_{PP}$ at 10 kHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -98 –90                                        | dB             |

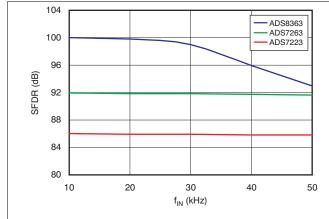

| SFDR Spurious-free dynamic range $V_{IN} = 5 V_{PP}$ at 10 kHz 90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 00                                             | dB             |

## 7.7 Electrical Characteristics: ADS7263

All minimum and maximum specifications at  $T_A = -40$ °C to +125°C, specified supply voltage range, VREF = 2.5 V (int), and  $t_{DATA} = 1$  MSPS (unless otherwise noted). Typical values are at  $T_A = +25$ °C, AVDD = 5 V, and DVDD = 3.3 V.

|                      | PARAMETER                    | TEST CONDITIONS                               | MIN   | TYP     | MAX   | UNIT   |

|----------------------|------------------------------|-----------------------------------------------|-------|---------|-------|--------|

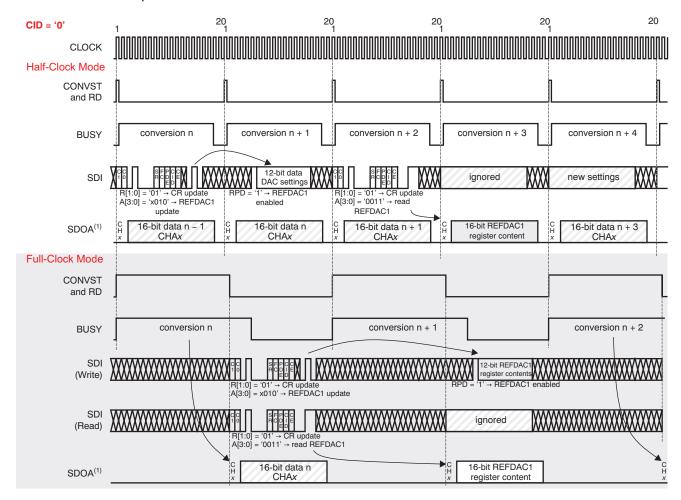

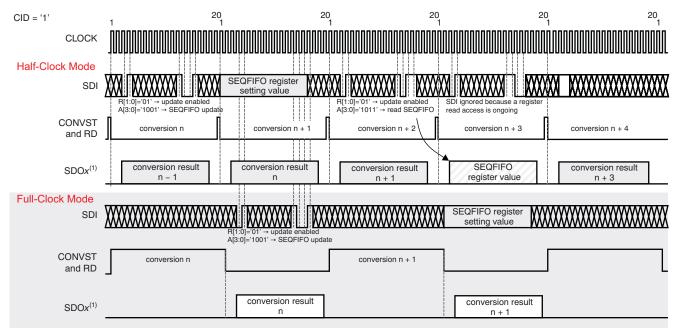

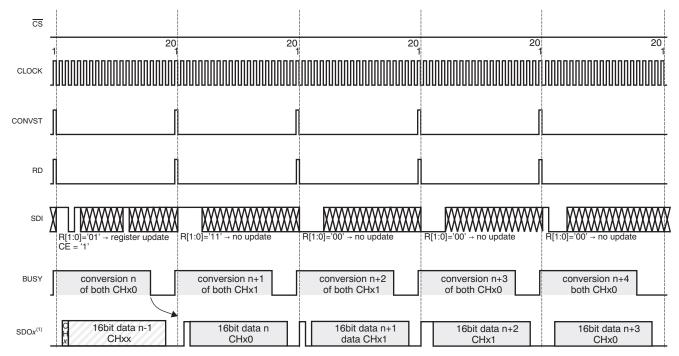

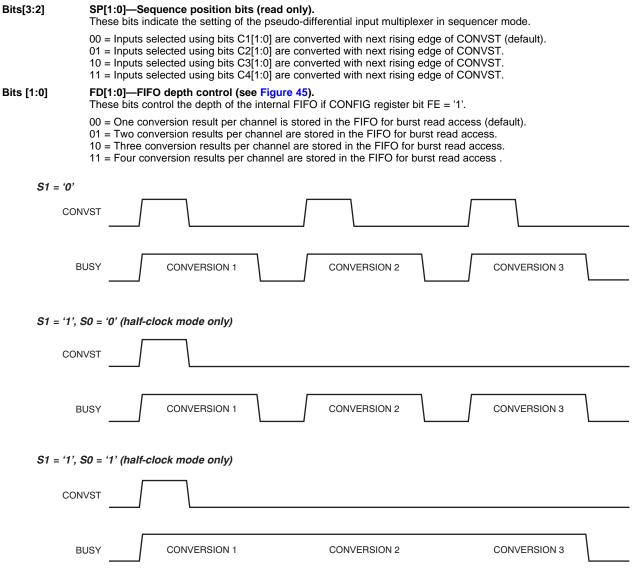

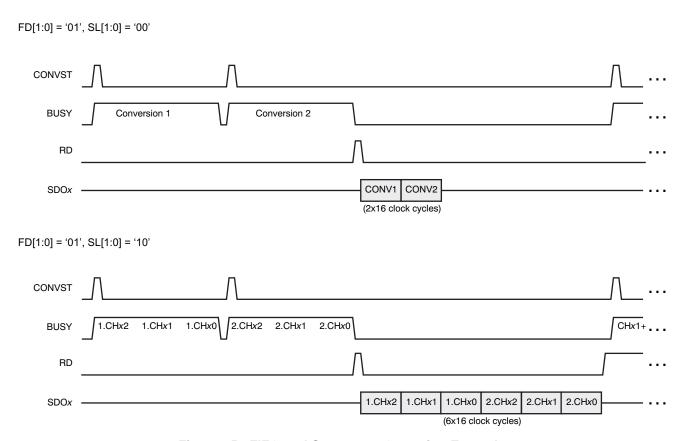

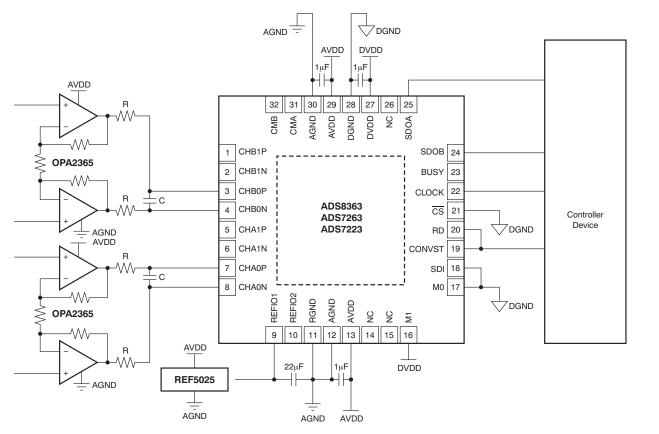

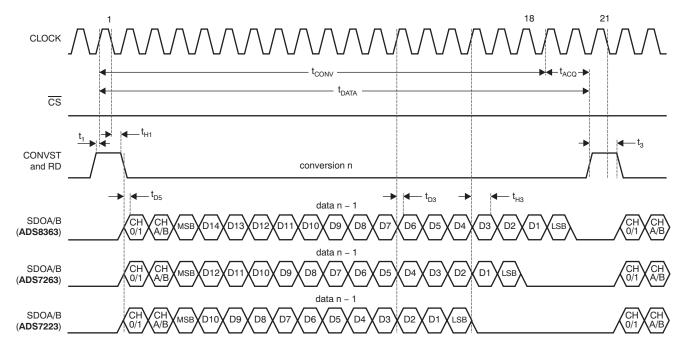

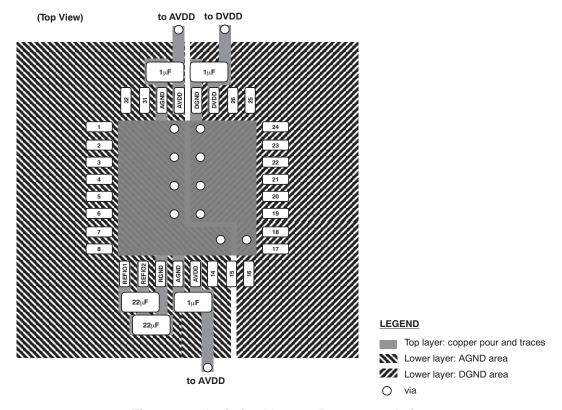

| RESOLUTION           | ON                           |                                               |       |         |       |        |