SLAS918B - DECEMBER 2012 - REVISED APRIL 2022

# ADS54T01 Single 12-Bit 750-Msps Receiver and Feedback IC

#### 1 Features

- Single channel

- 12-bit resolution

- Maximum clock rate: 750 Msps Low swing fullscale input: 1.0 Vpp

- Analog input buffer with high impedance input

- Input bandwidth (3 dB): > 1.2 GHz Data output interface: DDR LVDS

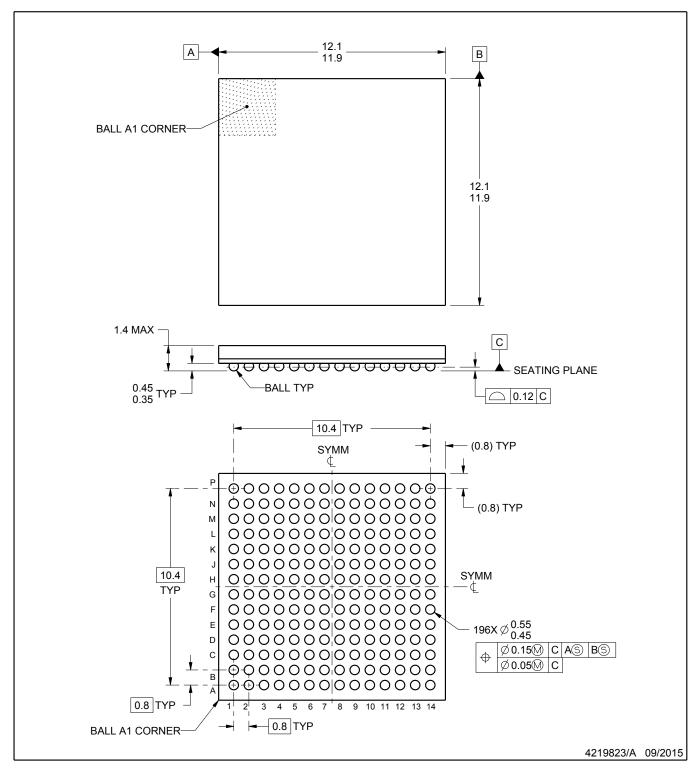

- 196-Pin NFBGA package (12 mm × 12 mm)

- Power dissipation: 1.2 W

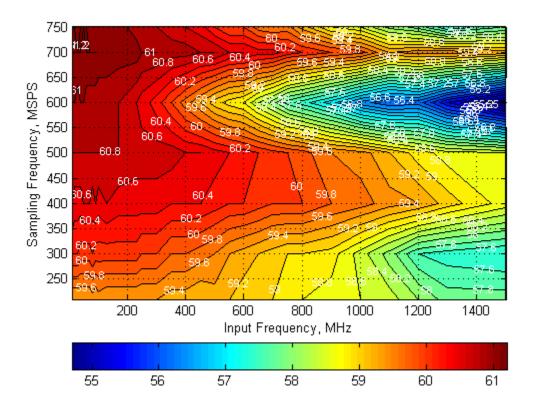

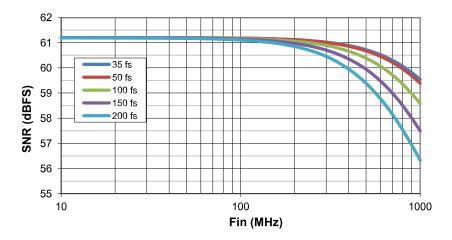

- Performance at f<sub>in</sub> = 230 MHz IF

- SNR: 60.7 dBFS SFDR: 73 dBc

- Performance at f<sub>in</sub> = 700 MHz IF

- SNR: 58.6 dBFS SFDR: 64 dBc

- Receive mode: 2x decimation with low-pass or high-pass filter

- Feedback mode: burst mode output for full bandwidth DPD feedback

## 2 Applications

- **Telecommunications**

- Wireless infrastructure

- Power amplifier linearization

## 3 Description

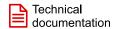

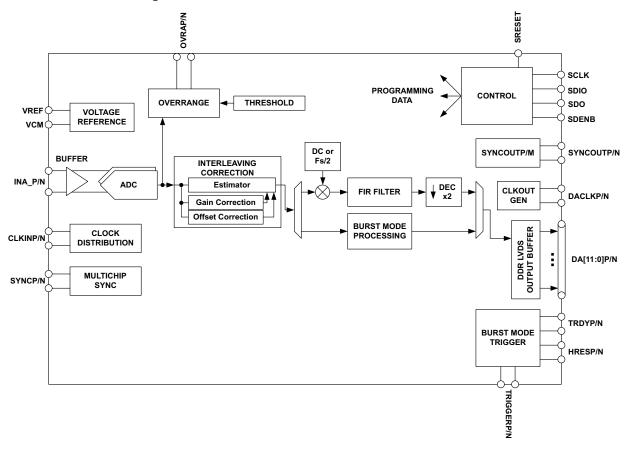

The ADS54T01 is a high linearity, single channel, 12-bit, 750-Msps analog-to-digital converter (ADC) easing front end filter design for wide bandwidth receivers. The analog input buffer isolates the internal switching of the on-chip track-and-hold from disturbing the signal source as well as providing a highimpedance input.

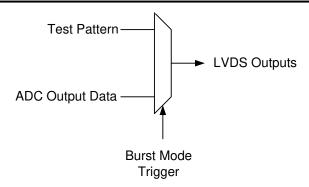

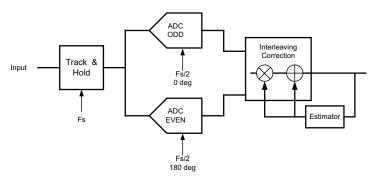

Two output modes are available for the output data —the data can be decimated by two or the data can be output in burst mode. The burst mode output is designed specifically for DPD feedback applications where high-resolution output data is available for a short period of time. Designed for high SFDR, the ADC has low-noise performance and outstanding spurious-free dynamic range over a large input-frequency range. The device is available in a 196-pin NFBGA package and is specified over the full industrial temperature range (-40°C to 85°C).

#### **Device Information**

| PART NUMBER | PACKAGE <sup>(1)</sup> | BODY SIZE (NOM)     |

|-------------|------------------------|---------------------|

| ADS54T01    | NFBGA (196)            | 12.00 mm × 12.00 mm |

For all available packages, see the orderable addendum at the end of the data sheet.

**Functional Block Diagram**

# **Table of Contents**

| 1 Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1                                                                                                                  | 8 Detailed Description                                                                                                                                                                             | 22                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| 2 Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1                                                                                                                  | 8.1 Overview                                                                                                                                                                                       | <mark>22</mark>       |

| 3 Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1                                                                                                                  | 8.2 Functional Block Diagram                                                                                                                                                                       | <mark>22</mark>       |

| 4 Revision History                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                    | 8.3 Feature Description                                                                                                                                                                            | <mark>22</mark>       |

| 5 Device Comparison                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                    | 8.4 Device Functional Modes                                                                                                                                                                        |                       |

| 6 Pin Configuration and Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                    | 8.5 Programming                                                                                                                                                                                    |                       |

| 7 Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                    | 8.6 Register Maps                                                                                                                                                                                  |                       |

| 7.1 Absolute Maximum Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                    | 9 Power Supply Recommendations                                                                                                                                                                     |                       |

| 7.2 ESD Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                    | 10 Device and Documentation Support                                                                                                                                                                |                       |

| 7.3 Recommended Operating Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                    | 10.1 Receiving Notification of Documentation Up                                                                                                                                                    |                       |

| 7.4 Thermal Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                    | 10.2 Support Resources                                                                                                                                                                             |                       |

| 7.5 Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                    | 10.3 Trademarks                                                                                                                                                                                    |                       |

| 7.6 Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                    | 10.4 Electrostatic Discharge Caution                                                                                                                                                               |                       |

| 7.7 Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                    | 10.5 Glossary                                                                                                                                                                                      | 40                    |

| 7.8 Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                    | 11 Mechanical, Packaging, and Orderable                                                                                                                                                            | 40                    |

| 7.9 Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                    | Information                                                                                                                                                                                        | 40                    |

| 4 Povision History                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                    |                                                                                                                                                                                                    |                       |

| 4 Revision History<br>Changes from Revision A (January 2014) to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | o Revisior                                                                                                         | n B (April 2022)                                                                                                                                                                                   | Page                  |

| Implementation section, Power Supply Red                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | commenda                                                                                                           |                                                                                                                                                                                                    |                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                    | ckaging, and Orderable Information section                                                                                                                                                         | 1                     |

| <ul> <li>Updated the numbering format for tables, f</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                    | d cross-references throughout the document                                                                                                                                                         | _                     |

| <ul> <li>Changed Revision A History from "Deleted</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                    |                                                                                                                                                                                                    |                       |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                    | Deleted G4, G3"                                                                                                                                                                                    | <mark>2</mark>        |

| Changed Pin Functions table to match TI S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                    |                                                                                                                                                                                                    | <mark>2</mark>        |

| Changes from Revision * (December 2012)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | to Revision                                                                                                        | on A (January 2014)                                                                                                                                                                                | 3 Page                |

| Changes from Revision * (December 2012)  Deleted G4, G3 from TRDYP/N pin numbe                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | to Revisions                                                                                                       | on A (January 2014)                                                                                                                                                                                | 3                     |

| Changes from Revision * (December 2012)  Deleted G4, G3 from TRDYP/N pin numbe                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | to Revisions                                                                                                       | on A (January 2014)                                                                                                                                                                                | 3                     |

| Changes from Revision * (December 2012)  Deleted G4, G3 from TRDYP/N pin numbe Changed package from QFN to nFBGA in                                                                                                                                                                                                                                                                                                                                                                                                                                | to RevisionsTHERMAL                                                                                                | on A (January 2014)                                                                                                                                                                                | Page3                 |

| Changes from Revision * (December 2012)  Deleted G4, G3 from TRDYP/N pin numbe Changed package from QFN to nFBGA in Added text and figure to TEST PATTERN C                                                                                                                                                                                                                                                                                                                                                                                        | to RevisionsTHERMAL                                                                                                | on A (January 2014)  INFORMATION                                                                                                                                                                   | Page3722              |

| <ul> <li>Changes from Revision * (December 2012)</li> <li>Deleted G4, G3 from TRDYP/N pin numbe</li> <li>Changed package from QFN to nFBGA in</li> <li>Added text and figure to TEST PATTERN 0</li> <li>Deleted text from last paragraph in INTERI</li> </ul>                                                                                                                                                                                                                                                                                      | to Revisions THERMAL DUTPUT s LEAVING (                                                                            | on A (January 2014)  INFORMATION  CORRECTION section.                                                                                                                                              | Page                  |

| Changes from Revision * (December 2012)  Deleted G4, G3 from TRDYP/N pin numbe  Changed package from QFN to nFBGA in  Added text and figure to TEST PATTERN 0  Deleted text from last paragraph in INTERI  Changed second paragraph in MULTI DEV                                                                                                                                                                                                                                                                                                   | to Revisions THERMAL DUTPUT s LEAVING (VICE SYNC                                                                   | on A (January 2014)  INFORMATION  CORRECTION section.  CHRONIZATION section.                                                                                                                       | Page7222628           |

| Changes from Revision * (December 2012)  Deleted G4, G3 from TRDYP/N pin numbe  Changed package from QFN to nFBGA in  Added text and figure to TEST PATTERN (  Deleted text from last paragraph in INTERI  Changed second paragraph in MULTI DEV  Deleted Register Initialization section and a                                                                                                                                                                                                                                                    | to Revisions to Revisions to Revisions rs THERMAL DUTPUT s LEAVING (VICE SYNC) added Dev                           | D' "Deleted G4, G3"                                                                                                                                                                                | Page3  Page3722262832 |

| Changes from Revision * (December 2012)  Deleted G4, G3 from TRDYP/N pin numbe  Changed package from QFN to nFBGA in  Added text and figure to TEST PATTERN (  Deleted text from last paragraph in INTERI  Changed second paragraph in MULTI DEV  Deleted Register Initialization section and a  Changed Register Address 2 Bit D13 from                                                                                                                                                                                                           | to Revisions to Revisions to Revisions rs THERMAL DUTPUT s LEAVING (VICE SYNO) added Dev to 1 in S                 | D "Deleted G4, G3"                                                                                                                                                                                 | Page                  |

| Changes from Revision * (December 2012)  Deleted G4, G3 from TRDYP/N pin numbe  Changed package from QFN to nFBGA in  Added text and figure to TEST PATTERN C  Deleted text from last paragraph in INTERI  Changed second paragraph in MULTI DEV  Deleted Register Initialization section and a  Changed Register Address 2 Bit D13 from  Changed Register Address E Bits D1 and I                                                                                                                                                                 | to Revision rsTHERMAL DUTPUT so LEAVING (VICE SYNC) added Develon 1 in S D0 to 0 in S                              | on A (January 2014)  INFORMATION  CORRECTION section  CHRONIZATION section  rice Initialization section  ERIAL REGISTER MAP  SERIAL REGISTER MAP                                                   | 23  Page372226323434  |

| Changes from Revision * (December 2012)  Deleted G4, G3 from TRDYP/N pin numbe  Changed package from QFN to nFBGA in  Added text and figure to TEST PATTERN C  Deleted text from last paragraph in INTERI  Changed second paragraph in MULTI DEV  Deleted Register Initialization section and a  Changed Register Address 2 Bit D13 from  Changed Register Address E Bits D1 and I  Changed Register Address 38 Bits D3 to D                                                                                                                       | to Revisions THERMAL DUTPUT s LEAVING (VICE SYNC) added Dev 0 to 1 in S D0 to 0 in S 00 from 0 to                  | on A (January 2014)  INFORMATION  CORRECTION section  CHRONIZATION section  CICE Initialization section  SERIAL REGISTER MAP  O 1 in SERIAL REGISTER MAP                                           | 23  Page372226323434  |

| Changes from Revision * (December 2012)  Deleted G4, G3 from TRDYP/N pin numbe  Changed package from QFN to nFBGA in  Added text and figure to TEST PATTERN C  Deleted text from last paragraph in INTERI  Changed second paragraph in MULTI DEV  Deleted Register Initialization section and a  Changed Register Address 2 Bit D13 from  Changed Register Address B Bits D1 and I  Changed Register Address 38 Bits D3 to D  Changed Register Address 2 Bit D13 from                                                                              | to Revisions THERMAL DUTPUT s LEAVING (VICE SYNC) added Dev 0 to 1 in S D0 to 0 in S 00 from 0 to 0 to 1 and       | on A (January 2014)  INFORMATION  CORRECTION section  CHRONIZATION section  Fice Initialization section  SERIAL REGISTER MAP  SERIAL REGISTER MAP  o 1 in SERIAL REGISTER MAP  add D13 Read back 1 | Page                  |

| Changes from Revision * (December 2012)  Deleted G4, G3 from TRDYP/N pin numbe  Changed package from QFN to nFBGA in  Added text and figure to TEST PATTERN C  Deleted text from last paragraph in INTERL  Changed second paragraph in MULTI DEV  Deleted Register Initialization section and a  Changed Register Address 2 Bit D13 from  Changed Register Address Bits D1 and I  Changed Register Address 2 Bit D13 from  Changed Register Address 2 Bit D13 from  Changed Register Address 2 Bit D13 from  Changed Register Address Bit D1 and D | to Revisions THERMAL DUTPUT S LEAVING (VICE SYNCO Ended Develor 1 in S DO to 0 in S DO from 0 to 0 to 1 and 0 to 0 | on A (January 2014)  INFORMATION  CORRECTION section  CHRONIZATION section  CICE Initialization section  SERIAL REGISTER MAP  O 1 in SERIAL REGISTER MAP                                           | Page                  |

# **5 Device Comparison**

## **Table 5-1. Device Comparison**

| PART NUMBER | NUMBER OF CHANNELS | SPEED GRADE |

|-------------|--------------------|-------------|

| ADS54T02    | 2                  | 750 Msps    |

| ADS54T01    | 1                  | 750 Msps    |

| ADS54T04    | 2                  | 500 Msps    |

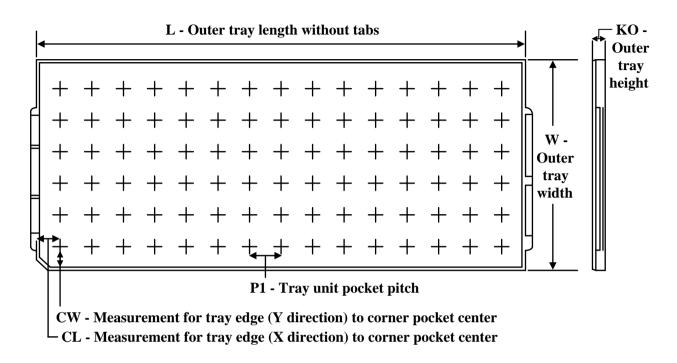

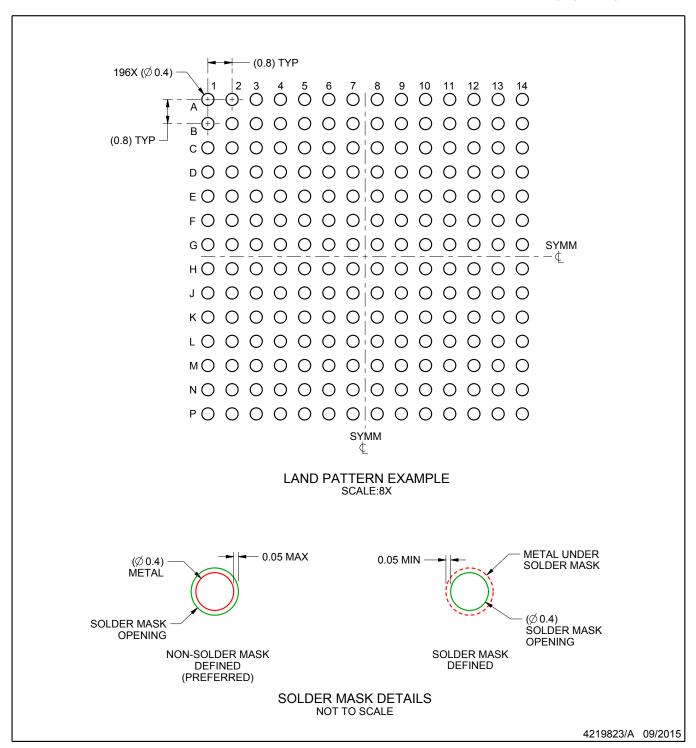

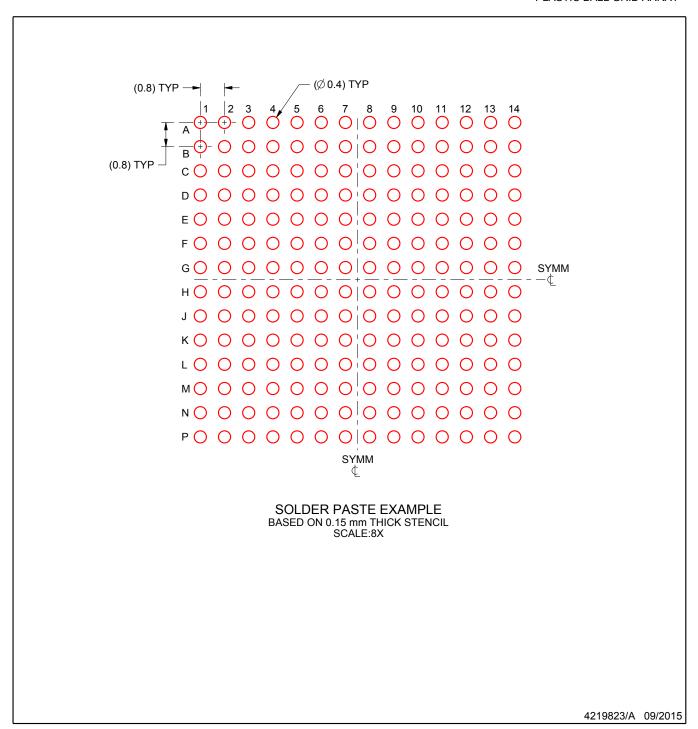

# **6 Pin Configuration and Functions**

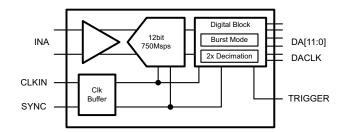

Figure 6-1. ADS54T01 ZAY Package, 196-Pin NFBGA, Top View (DDR Output Mode)

**Table 6-1. Pin Functions**

| PIN NAME NUMBER  |          | I/O TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                            |  |  |

|------------------|----------|-------------------------|------------------------------------------------------------------------------------------------------------------------|--|--|

|                  |          | //OTTPEC                | DESCRIPTION                                                                                                            |  |  |

| INPUT/REFERE     | NCE      |                         |                                                                                                                        |  |  |

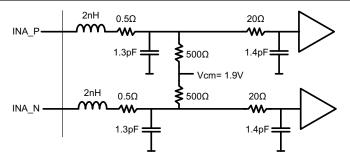

| INA_P/N K14, L14 |          | I                       | Analog ADC differential input signal.                                                                                  |  |  |

| VCM B14          |          | 0                       | Output of the analog input common mode (nominally 1.9 V). A 0.1-µF capacitor to AGND is recommended, but not required. |  |  |

| VREF A14         |          | I                       | Reference voltage input. A 0.1-µF capacitor to AGND is recommended.                                                    |  |  |

| CLOCK/SYNC       |          |                         |                                                                                                                        |  |  |

| CLKINP/N         | P14, P13 | I                       | Differential input clock                                                                                               |  |  |

# **Table 6-1. Pin Functions (continued)**

|              | PIN                                                                                                                                                                                         | 6-1. Pin Functions (continued) |                                                                                                                                                                                                                        |  |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME         | NUMBER                                                                                                                                                                                      | I/O TYPE <sup>(1)</sup>        | DESCRIPTION                                                                                                                                                                                                            |  |

| SYNCP/N      | P9, N9                                                                                                                                                                                      | ı                              | Synchronization input. Inactive if logic low. When clocked in a high state initially, this is used for resetting internal clocks and digital logic and starting the SYNCOUT signal. Internal $100-\Omega$ termination. |  |

| CONTROL/SER  | IAL                                                                                                                                                                                         |                                |                                                                                                                                                                                                                        |  |

| SRESET       | B12                                                                                                                                                                                         | I                              | Serial interface reset input. Active low. Initialized internal registers during high-to-low transition. Asynchronous. Internal 50-kΩ pullup resistor to IOVDD.                                                         |  |

| ENABLE       | B11                                                                                                                                                                                         | I                              | Chip enable – active high. Power-down function can be controlled through SPI register assignment. Internal 50-kΩ pullup resistor to IOVDD.                                                                             |  |

| SCLK         | A12                                                                                                                                                                                         | I                              | Serial interface clock. Internal 50-kΩ pulldown resistor.                                                                                                                                                              |  |

| SDIO         | A11                                                                                                                                                                                         | I/O                            | Bidirectional serial data in 3-pin mode (default). In 4-pin interface mode (register x00, D16), the SDIO pin in an input only. Internal 50-k $\Omega$ pulldown resistor.                                               |  |

| SDENB        | A13                                                                                                                                                                                         | I                              | Serial interface enable. Internal 50-kΩ pulldown resistor.                                                                                                                                                             |  |

| SDO          | A10                                                                                                                                                                                         | 0                              | Uni-directional serial interface data in 4-pin mode (register x00, D16). The SDO pin is tri-stated in 3-pin interface mode (default). Internal 50-k $\Omega$ pulldown resistor.                                        |  |

| DATA INTERFA | CE                                                                                                                                                                                          |                                |                                                                                                                                                                                                                        |  |

| DA[11:0]P/N  | P3, N3, P2, N2,<br>P1, N1, M4, M3,<br>M2, M1, L4, L3,<br>L2, L1, K4, K3,<br>K2, K1, J4, J3,<br>J2, J1, H4, H3                                                                               | 0                              | ADC A Data Bits 11 (MSB) to 0 (LSB) in DDR output mode. Standard LVDS output.                                                                                                                                          |  |

| DACLKP/N     | H2, H1                                                                                                                                                                                      | 0                              | DDR differential output data clock for Bus A. Register programmable to provide eith rising or falling edge to center of stable data nominal timing.                                                                    |  |

| SYNCOUTP/N   | P5, N5                                                                                                                                                                                      | 0                              | Synchronization output signal for synchronizing multiple ADCs. Can be disabled through the SPI.                                                                                                                        |  |

| OVRAP/N      | M5, L5                                                                                                                                                                                      | 0                              | Bus A, Overrange indicator, LVDS output. A logic high signals an analog input in excess of the full-scale range. Optional SYNC output.                                                                                 |  |

| TRIGGERP/N   | P10, N10                                                                                                                                                                                    | ı                              | Trigger used for high-resolution output data in feedback mode. Internal $100-\Omega$ termination.                                                                                                                      |  |

| TRDYP/N      | P7, N7                                                                                                                                                                                      | 0                              | Trigger ready output indicator                                                                                                                                                                                         |  |

| HRESP/N      | P6, N6                                                                                                                                                                                      | 0                              | Indicator for high-resolution output data; logic high signals 12-bit output data.                                                                                                                                      |  |

| NO CONNECT   |                                                                                                                                                                                             |                                |                                                                                                                                                                                                                        |  |

| NC           | A1, A2, A3, A4,<br>A5, A6, A7, B1,<br>B2, B3, B4, B5,<br>B6, B7, C1, C2,<br>C3, C4, C5, D1,<br>D2, D3, D4, D5,<br>D14, E1, E2, E3,<br>E4, E14, F1, F2,<br>F3, F4, G1, G2,<br>G3, G4, N4, P4 | -                              | Do not connect to pin, leave floating.                                                                                                                                                                                 |  |

| TESTMODE     | B13                                                                                                                                                                                         | _                              | Used for factory internal test. Do not connect to pin, leave floating.                                                                                                                                                 |  |

| POWER SUPPL  | Υ                                                                                                                                                                                           |                                |                                                                                                                                                                                                                        |  |

| AVDD33       | D12, E12, F12,<br>G12, H12, J12,<br>K12, L12, N12,<br>P12                                                                                                                                   | Р                              | 3.3-V analog supply                                                                                                                                                                                                    |  |

| AVDDC        | G14, H14                                                                                                                                                                                    | Р                              | 1.8-V supply for clock input                                                                                                                                                                                           |  |

| AVDD18       | D10, D11, E11,<br>F11, G11, H11,<br>J11, K11, L10,<br>L11, N11, P11                                                                                                                         | Р                              | 1.8-V analog supply                                                                                                                                                                                                    |  |

# **Table 6-1. Pin Functions (continued)**

|          | Table 0-1. Fill I dilctions (continued)                                                                                                                                                                                                                                                         |                         |                                |  |  |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--------------------------------|--|--|

|          | PIN                                                                                                                                                                                                                                                                                             | I/O TYPE <sup>(1)</sup> | DESCRIPTION                    |  |  |

| NAME     | NUMBER                                                                                                                                                                                                                                                                                          | WO TTPE                 | DESCRIPTION                    |  |  |

| DVDD     | A8, A9, B8, B9,<br>C8, D8, L8, M8,<br>N8, P8                                                                                                                                                                                                                                                    | Р                       | 1.8-V supply for digital block |  |  |

| DVDDLVDS | C6, C7, D6, D7,<br>L6, L7, M6, M7                                                                                                                                                                                                                                                               | Р                       | 1.8-V supply for LVDS outputs  |  |  |

| IOVDD    | B10                                                                                                                                                                                                                                                                                             | Р                       | 1.8-V for digital I/Os         |  |  |

| GND      | C9, C10, C11,<br>C12, C13, C14,<br>D9, D13, E5, E6,<br>E7, E8, E9, E10,<br>E13, F5, F6, F7,<br>F8, F9, F10, F13,<br>F14, G5, G6, G7,<br>G8, G9, G10,H5,<br>H6, H7, H8, H9,<br>H10, J5, J6, J7,<br>J8, J9, J10, K5,<br>K6, K7, K8, K9,<br>K10, L9, M9,<br>M10, M11, M12,<br>M13, M14,N13,<br>N14 | GND                     | Ground                         |  |  |

- (1) The definitions below define the I/O type for each pin.

- I = Input

- O = Output

- I/O = Input / Output

- P = Power Supply

- G = Ground

# 7 Specifications

# 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)

|                                               |                                        | MIN  | MAX          | UNIT |

|-----------------------------------------------|----------------------------------------|------|--------------|------|

| Supply voltage                                | AVDD33                                 | -0.5 | 4            | V    |

|                                               | AVDDC                                  | -0.5 | 2.3          | V    |

|                                               | AVDD18                                 | -0.5 | 2.3          | V    |

|                                               | DVDD                                   | -0.5 | 2.3          | V    |

|                                               | DVDDLVDS                               | -0.5 | 2.3          | V    |

|                                               | IOVDD                                  | -0.5 | 4            | V    |

|                                               | INA_P, INA_N                           | -0.5 | AVDD33 + 0.5 | V    |

| Valtage applied to input pine                 | CLKINP, CLKINN                         | -0.5 | AVDDC + 0.5  | V    |

| Voltage applied to input pins                 | SYNCP, SYNCN                           | -0.5 | AVDD33 + 0.5 | V    |

|                                               | SRESET, SDENB, SCLK, SDIO, SDO, ENABLE | -0.5 | IOVDD + 0.5  | V    |

| Operating free-air temperature                | e, T <sub>A</sub>                      | -40  | 85           | °C   |

| Derating junction temperature, T <sub>J</sub> |                                        |      | 150          | °C   |

| Storage temperature, T <sub>stg</sub>         |                                        | -65  | 150          | °C   |

<sup>(1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

# 7.2 ESD Ratings

|                    |                         |                                                                             | VALUE | UNIT |

|--------------------|-------------------------|-----------------------------------------------------------------------------|-------|------|

| V <sub>(ESD)</sub> | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup> | ±2000 | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

## 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                |                                                             | MIN | NOM | MAX | UNIT |

|----------------|-------------------------------------------------------------|-----|-----|-----|------|

| _              | Recommended operating junction temperature                  |     |     | 105 | °C   |

| l J            | Maximum rated operating junction temperature <sup>(1)</sup> | 125 |     |     |      |

| T <sub>A</sub> | Recommended free-air temperature                            | -40 | 25  | 85  | °C   |

<sup>(1)</sup> Prolonged use at this junction temperature may increase the device failure-in-time (FIT) rate.

#### 7.4 Thermal Information

|                         | THERMAL METRIC(1)                                           | ADS54T01 ZAY (NFBGA) 196 PINS | UNIT |

|-------------------------|-------------------------------------------------------------|-------------------------------|------|

| $\theta_{JA}$           | Junction-to-ambient thermal resistance <sup>(2)</sup>       | 37.6                          | °C/W |

| $\theta_{\text{JCtop}}$ | Junction-to-case (top) thermal resistance <sup>(3)</sup>    | 6.8                           | °C/W |

| $\theta_{JB}$           | Junction-to-board thermal resistance <sup>(4)</sup>         | 16.8                          | °C/W |

| ΨЈТ                     | Junction-to-top characterization parameter <sup>(5)</sup>   | 0.2                           | °C/W |

| ΨЈВ                     | Junction-to-board characterization parameter <sup>(6)</sup> | 16.4                          | °C/W |

- (1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

- (2) The junction-to-ambient thermal resistance under natural convection is obtained in a simulation on a JEDEC-standard, high-K board, as specified in JESD51-7, in an environment described in JESD51-2a.

- (3) The junction-to-case (top) thermal resistance is obtained by simulating a cold plate test on the package top. No specific JEDEC-standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

- (4) The junction-to-board thermal resistance is obtained by simulating in an environment with a ring cold plate fixture to control the PCB temperature, as described in JESD51-8.

- (5) The junction-to-top characterization parameter,  $\psi_{JT}$ , estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining  $R_{\theta,JA}$ , using a procedure described in JESD51-2a (sections 6 and 7).

- (6) The junction-to-board characterization parameter, ψ<sub>JB</sub>, estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining R<sub>θ,JA</sub>, using a procedure described in JESD51-2a (sections 6 and 7).

### 7.5 Electrical Characteristics

Typical values at  $T_A$  = 25°C, full temperature range is  $T_{MIN}$  = -40°C to  $T_{MAX}$  = 85°C, ADC sampling rate = 750 Msps, 50% clock duty cycle, AVDD33 = 3.3 V, AVDDC/AVDD18/DVDD/DVDDLVDS/IOVDD = 1.8 V, -1-dBFS differential input (unless otherwise noted).

|                       | PARAMETER                        | TEST CONDITIONS                                     | MIN  | TYP | MAX  | UNITS |

|-----------------------|----------------------------------|-----------------------------------------------------|------|-----|------|-------|

| ADC Clock             | Frequency                        |                                                     | 40   |     | 750  | MSPS  |

| Resolution            | 1                                |                                                     | 12   |     |      | Bits  |

| SUPPLY                |                                  |                                                     |      |     |      |       |

| AVDD33                |                                  |                                                     | 3.15 | 3.3 | 3.45 | V     |

| AVDDC, AV             | /DD18, DVDD, DVDDLVDS            |                                                     | 1.7  | 1.8 | 1.9  | V     |

| IOVDD                 |                                  |                                                     | 1.7  | 1.8 | 3.45 | V     |

| POWER S               | UPPLY                            |                                                     |      |     | ,    |       |

| I <sub>AVDD33</sub>   | 3.3-V Analog supply current      |                                                     |      | 154 | 170  | mA    |

| I <sub>AVDD18</sub>   | 1.8-V Analog supply current      |                                                     |      | 66  | 80   | mA    |

| I <sub>AVDDC</sub>    | 1.8-V Clock supply current       |                                                     |      | 42  | 60   | mA    |

| I <sub>DVDD</sub>     | 1.8-V Digital supply current     | Auto Correction Enabled                             |      | 250 | 280  | mA    |

| I <sub>DVDD</sub>     | 1.8-V Digital supply current     | Auto Correction Disabled                            |      | 215 |      | mA    |

| I <sub>DVDD</sub>     | 1.8-V Digital supply current     | Auto Correction Disabled, decimation filter enabled |      | 234 |      | mA    |

| I <sub>DVDDLVDS</sub> | 1.8-V LVDS supply current        |                                                     |      | 66  | 90   | mA    |

| I <sub>IOVDD</sub>    | 1.8-V I/O Voltage supply current |                                                     |      | 1   | 2    | mA    |

Copyright © 2022 Texas Instruments Incorporated

Submit Document Feedback

## 7.5 Electrical Characteristics (continued)

| PARAMETER                                | TEST CONDITIONS                                      | MIN | TYP  | MAX  | UNITS |

|------------------------------------------|------------------------------------------------------|-----|------|------|-------|

| P <sub>dis</sub> Total power dissipation | Auto Correction Enabled, decimation filter disabled  |     | 1.28 | 1.75 | W     |

| P <sub>dis</sub> Total power dissipation | Auto Correction Disabled, decimation filter disabled |     | 1.2  |      | W     |

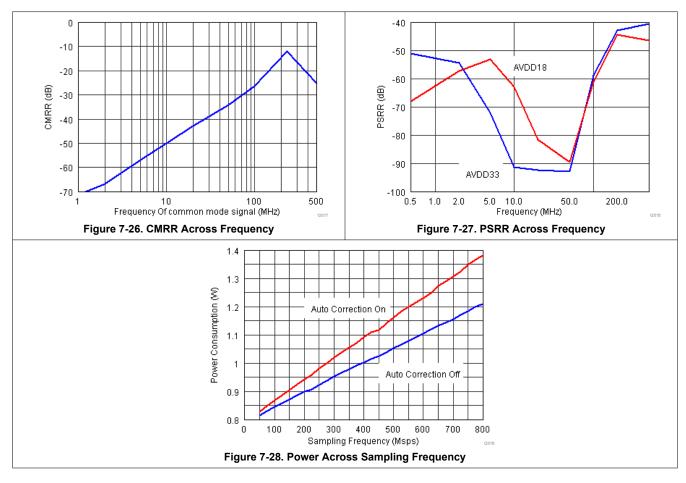

| PSRR                                     | 250 kHz to 500 MHz                                   | 40  |      |      | dB    |

| Shutdown power dissipation               |                                                      |     | 7    |      | mW    |

| Shutdown wake-up time                    |                                                      |     | 2.5  |      | ms    |

| Standby power dissipation                |                                                      |     | 7    |      | mW    |

| Standby wake-up time                     |                                                      |     | 100  |      | μs    |

| Doon aloon made namer discinction        | Auto correction disabled                             |     | 350  |      | mW    |

| Deep-sleep mode power dissipation        | Auto correction enabled                              |     | 475  |      | mW    |

| Deep-sleep mode wake-up time             |                                                      |     | 20   |      | μs    |

| Light alon made navor discination        | Auto correction disabled                             |     | 655  |      | mW    |

| Light-sleep mode power dissipation       | Auto correction enabled                              |     | 780  |      | mW    |

| Light-sleep mode wake-up time            |                                                      |     | 2    |      | μs    |

### 7.6 Electrical Characteristics

| PARAMETER                      | TEST CONDITIONS           | MIN      | TYP   | MAX  | UNITS  |

|--------------------------------|---------------------------|----------|-------|------|--------|

| ANALOG INPUTS                  |                           |          |       |      |        |

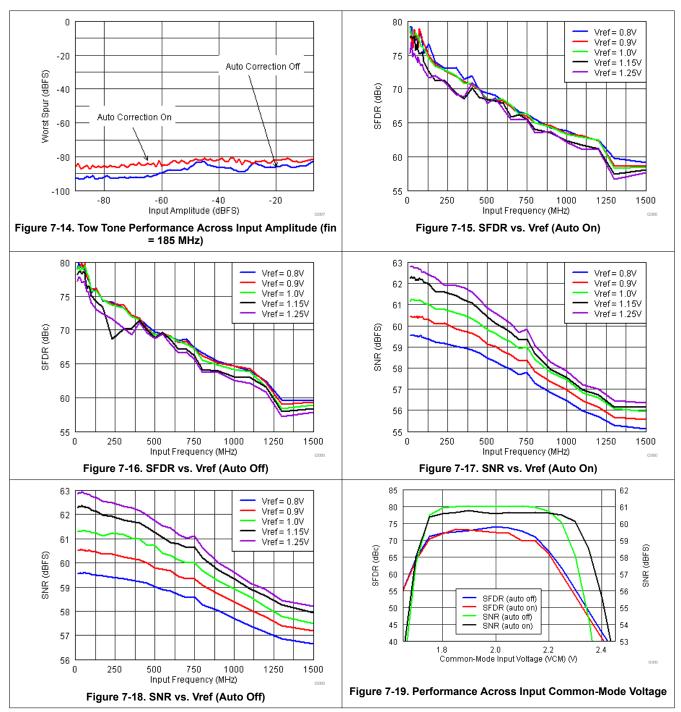

| Differential input full-scale  |                           |          | 1.0   | 1.25 | Vpp    |

| Input common-mode voltage      |                           |          | 1.9   | ±0.1 | V      |

| Input resistance               | Differential at DC        |          | 1     |      | kΩ     |

| Input capacitance              | Each input to GND         |          | 2     |      | pF     |

| VCM common-mode voltage output |                           |          | 1.9   |      | V      |

| Analog input bandwidth (3 dB)  |                           |          | 1200  |      | MHz    |

| DYNAMIC ACCURACY               |                           | ·        |       |      |        |

| Offset Error                   | Auto Correction Disabled  | -20      | -7.5  | 20   | mV     |

|                                | Auto Correction Enabled   | -1       | 0     | 1    | mV     |

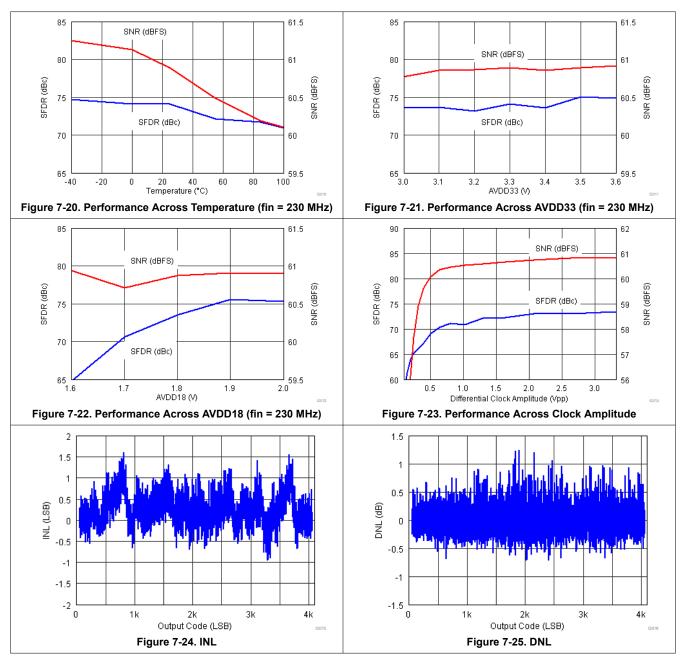

| Offset temperature coefficient |                           |          | -6.5  |      | μV/°C  |

| Gain error                     |                           | -5       |       | 5    | %FS    |

| Gain temperature coefficient   |                           |          | 0.005 |      | %FS/°C |

| Differential nonlinearity      | f <sub>IN</sub> = 230 MHz | -1       | ±0.9  | 2    | LSB    |

| Integral nonlinearity          | f <sub>IN</sub> = 230 MHz | -5       | ±1.5  | 5    | LSB    |

| CLOCK INPUT                    |                           | <u> </u> |       |      |        |

| Input clock frequency          |                           | 40       |       | 750  | MHz    |

| Input clock amplitude          |                           |          | 2     |      | Vpp    |

| Input clock duty cycle         |                           | 40%      | 50%   | 60%  |        |

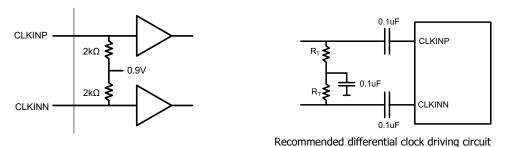

| Internal clock biasing         |                           |          | 0.9   |      | V      |

#### 7.7 Electrical Characteristics

|              | PARAMETER                                        | TEST CONDITIONS                                | MIN       | TYP MAX        | MIN | TYP      | MAX | UNITS |  |

|--------------|--------------------------------------------------|------------------------------------------------|-----------|----------------|-----|----------|-----|-------|--|

| Auto Co      | rrection                                         |                                                |           | Enabled        |     | Disabled |     | Vpp   |  |

| DYNAMI       | C AC CHARACTERISTICS(1) - I                      | Burst Mode Enabled: 12-bit High                | Resolutio | on Output Data |     |          |     |       |  |

|              |                                                  | f <sub>IN</sub> = 10 MHz                       |           | 61.1           |     | 61.2     |     |       |  |

|              |                                                  | f <sub>IN</sub> = 100 MHz                      |           | 61.1           |     | 61.1     |     |       |  |

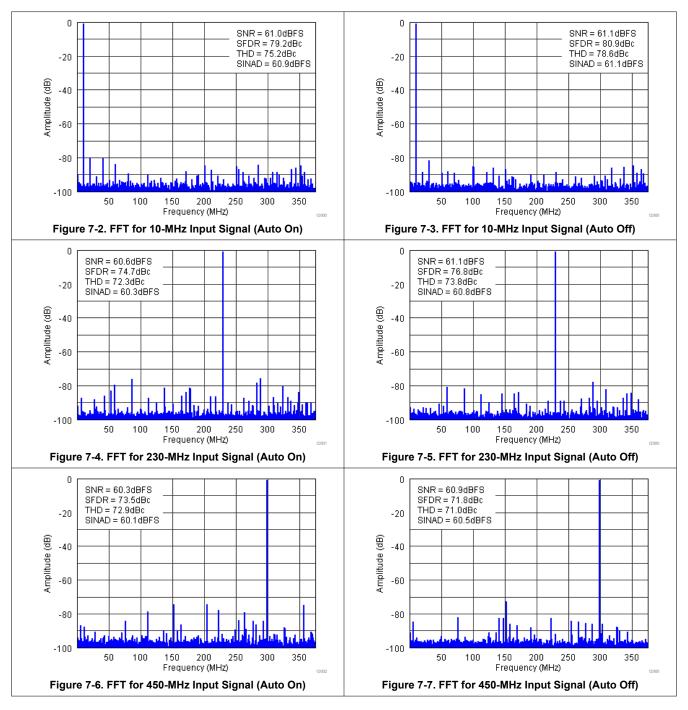

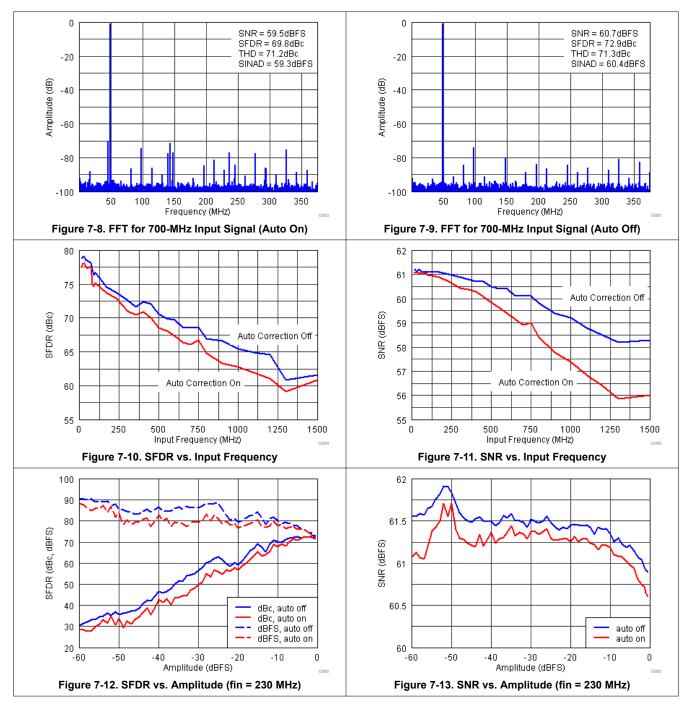

| SNR          | Signal to Noise Ratio                            | f <sub>IN</sub> = 230 MHz                      | 59        | 60.7           |     | 60.9     |     | dBFS  |  |

|              |                                                  | f <sub>IN</sub> = 450 MHz                      |           | 59.9           |     | 60.5     |     |       |  |

|              |                                                  | f <sub>IN</sub> = 700 MHz                      |           | 58.6           |     | 59.6     |     |       |  |

|              |                                                  | f <sub>IN</sub> = 10 MHz                       |           | 81             |     | 83       |     |       |  |

|              |                                                  | f <sub>IN</sub> = 100 MHz                      |           | 76             |     | 81       |     |       |  |

| HD2,3        | Second and third harmonic distortion             | f <sub>IN</sub> = 230 MHz                      |           | 78             |     | 79       |     | dBc   |  |

|              | distortion                                       | f <sub>IN</sub> = 450 MHz                      |           | 75             |     | 76       |     |       |  |

|              |                                                  | f <sub>IN</sub> = 700 MHz                      |           | 74             |     | 76       |     |       |  |

|              |                                                  | f <sub>IN</sub> = 10 MHz                       |           | 78             |     | 79       |     |       |  |

|              | Spur Free Dynamic Range                          | f <sub>IN</sub> = 100 MHz                      | 68        | 75             |     | 77       |     |       |  |

| Non<br>HD2,3 | (excluding second and third harmonic distortion) | f <sub>IN</sub> = 230 MHz                      |           | 73             |     | 73       |     | dBc   |  |

| 1102,5       |                                                  | f <sub>IN</sub> = 450 MHz                      |           | 68             |     | 69       |     |       |  |

|              |                                                  | f <sub>IN</sub> = 700 MHz                      |           | 64             |     | 66       |     |       |  |

|              |                                                  | f <sub>IN</sub> = 10 MHz                       |           | 90             |     | 87       |     |       |  |

|              |                                                  | f <sub>IN</sub> = 100 MHz                      |           | 84             |     | 82       |     |       |  |

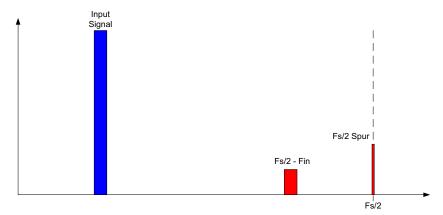

| IL           | Fs/2-Fin interleaving spur                       | f <sub>IN</sub> = 230 MHz                      | 65        | 79             |     | 76       |     | dBc   |  |

|              |                                                  | f <sub>IN</sub> = 450 MHz                      |           | 72             |     | 72       |     |       |  |

|              |                                                  | f <sub>IN</sub> = 700 MHz                      |           | 66             |     | 69       |     |       |  |

|              |                                                  | f <sub>IN</sub> = 10 MHz                       |           | 61.0           |     | 61.1     |     |       |  |

|              |                                                  | f <sub>IN</sub> = 100 MHz                      |           | 60.8           |     | 61.0     |     |       |  |

| SINAD        | Signal to noise and distortion ratio             | f <sub>IN</sub> = 230 MHz                      | 57.5      | 60.5           |     | 60.8     |     | dBc   |  |

|              | Tallo                                            | f <sub>IN</sub> = 450 MHz                      |           | 59.8           |     | 60.3     |     |       |  |

|              |                                                  | f <sub>IN</sub> = 700 MHz                      |           | 58.4           |     | 59.4     |     |       |  |

|              |                                                  | f <sub>IN</sub> = 10 MHz                       |           | 76             |     | 76       |     |       |  |

|              |                                                  | f <sub>IN</sub> = 100 MHz                      |           | 73             |     | 76       |     |       |  |

| THD          | Total Harmonic Distortion                        | f <sub>IN</sub> = 230 MHz                      | 66        | 74             |     | 74       |     | dBc   |  |

|              |                                                  | f <sub>IN</sub> = 450 MHz                      |           | 74             |     | 73       |     |       |  |

|              |                                                  | f <sub>IN</sub> = 700 MHz                      |           | 72             |     | 74       |     |       |  |

| IMPO         | Laborate de de Maria d'Arbantana                 | F <sub>in</sub> = 184.5 and 185.5 MHz, –7 dBFS |           | 82             | 83  |          |     | ID=0  |  |

| IMD3         | Inter modulation distortion                      | F <sub>in</sub> = 549.5 and 550.5 MHz, -7 dBFS |           | 76             |     | 77       |     | dBFS  |  |

|              | Crosstalk                                        |                                                |           | 90             |     | 90       |     | dB    |  |

| ENOB         | Effective number of bits                         | f <sub>IN</sub> = 230 MHz                      |           | 9.8            |     | 9.8      |     | LSB   |  |

<sup>(1)</sup> SFDR and SNR calculations do not include the DC or Fs/2 bins when Auto Correction is disabled.

#### 7.8 Electrical Characteristics

Typical values at  $T_A$  = 25°C, full temperature range is  $T_{MIN}$  = -40°C to  $T_{MAX}$  = 85°C, ADC sampling rate = 500 Msps, 50% clock duty cycle, AVDD33 = 3.3 V, AVDDC/AVDD18/DVDD/DVDDLVDS/IOVDD = 1.8 V, -1-dBFS differential input (unless otherwise noted).

| 01.10. | wise noted).            |                                                                                   |     |     |                             |                 |

|--------|-------------------------|-----------------------------------------------------------------------------------|-----|-----|-----------------------------|-----------------|

|        | PARAMETER               | TEST CONDITIONS                                                                   | MIN | TYP | MAX                         | UNITS           |

| OVEF   | R-DRIVE RECOVERY ERROF  | 2                                                                                 |     |     |                             |                 |

|        | Input overload recovery | Recovery to within 5% (of final value) for 6-dB overload with sine wave input     |     | 2   |                             | ns              |

| SAME   | PLE TIMING CHARACTERIS  | TICS                                                                              |     |     |                             |                 |

| rms    | Aperture Jitter         | Sample uncertainty                                                                |     | 100 |                             | fs rms          |

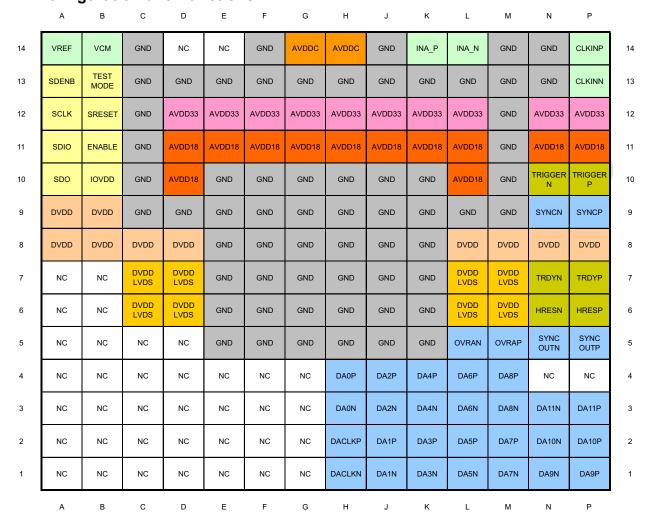

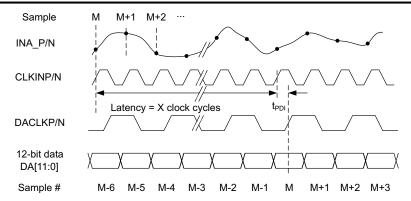

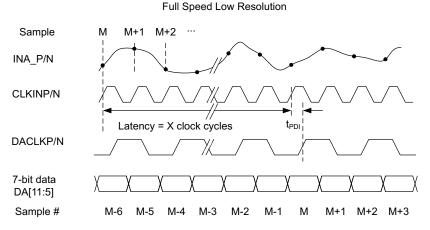

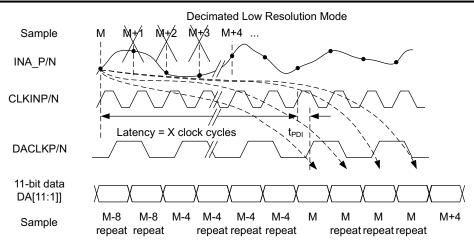

|        | Data Latency            | ADC sample to digital output, Auto correction disabled                            |     | 38  |                             | Clock           |

|        |                         | ADC sample to digital output, Auto correction enabled                             |     | 50  |                             | Cycles          |

|        |                         | ADC sample to digital output, Decimation filter enabled, Auto correction disabled | 74  |     | Sampling<br>clock<br>Cycles |                 |

|        | Over-range Latency      | ADC sample to over-range output                                                   |     | 12  |                             | Clock<br>Cycles |

#### 7.9 Electrical Characteristics

The DC specifications refer to the condition where the digital outputs are not switching, but are permanently at a valid logic level 0 or 1. AVDD33 = 3.3 V, AVDDC/AVDD18/DVDD/DVDDLVDS/IOVDD = 1.8 V

|                 | PARAMETER                     | TEST CONDITIONS                                 | MIN            | TYP  | MAX             | UNITS    |

|-----------------|-------------------------------|-------------------------------------------------|----------------|------|-----------------|----------|

| DIGITA          | AL INPUTS – SRESET, SCLK, SDE | ENB, SDIO, ENABLE                               |                |      | <u> </u>        |          |

|                 | High-level input voltage      | All digital inputs support 1.8-V and 3.3-V      | 0.7 x<br>IOVDD |      |                 | V        |

|                 | Low-level input voltage       | logic levels.                                   |                |      | 0.3 x<br>IOVDD  | V        |

|                 | High-level input current      |                                                 | -50            |      | 200             | μA       |

|                 | Low-level input current       |                                                 | -50            |      | 50              | μA       |

|                 | Input capacitance             |                                                 |                | 5    |                 | pF       |

| DIGITA          | AL OUTPUTS – SDO              |                                                 |                |      |                 |          |

|                 | High lovel output veltage     | lload = -100 μA                                 | IOVDD –<br>0.2 |      |                 | V        |

|                 | High-level output voltage     | Iload = -2 mA                                   | 0.8 x<br>IOVDD |      |                 | <b>v</b> |

|                 |                               | lload = 100 μA                                  |                |      | 0.2             |          |

|                 | Low-level output voltage      | Iload = 2 mA                                    |                |      | 0.22 x<br>IOVDD | V        |

| DIGITA          | AL INPUTS – SYNCP/N, TRIGGER  | P/N                                             |                |      | 1               |          |

| $V_{ID}$        | Differential input voltage    |                                                 | 250            | 350  | 450             | mV       |

| $V_{CM}$        | Input common-mode voltage     |                                                 | 1.125          | 1.2  | 1.375           | V        |

| t <sub>SU</sub> |                               |                                                 | 500            |      |                 | ps       |

| DIGITA          | AL OUTPUTS – DA[11:0]P/N, DAC | LKP/N, OVRAP/N, SYNCOUTP/N, TRDYP/N, F          | IRESP/N        |      |                 |          |

| $V_{OD}$        | Output differential voltage   | lout = 3.5 mA                                   | 250            | 350  | 450             | mV       |

| $V_{OCM}$       | Output common-mode voltage    | lout = 3.5 mA                                   | 1.125          | 1.25 | 1.375           | V        |

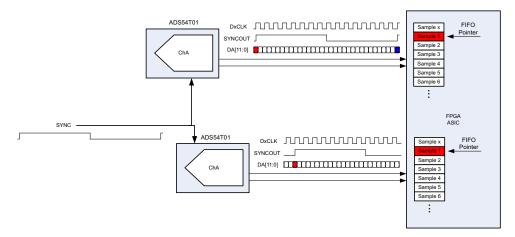

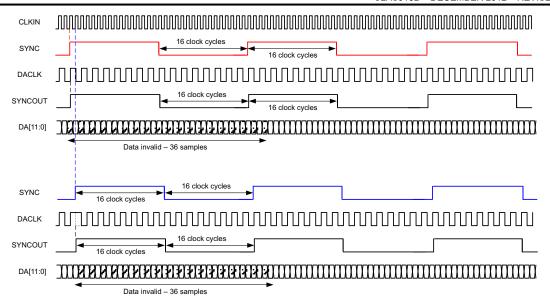

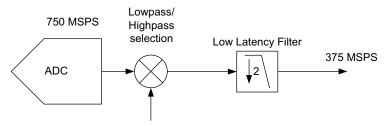

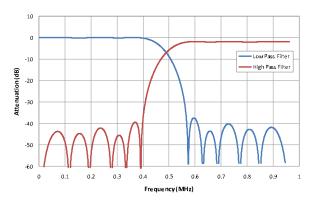

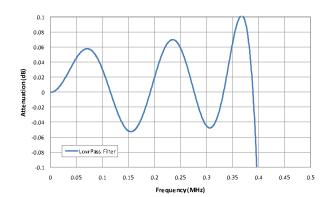

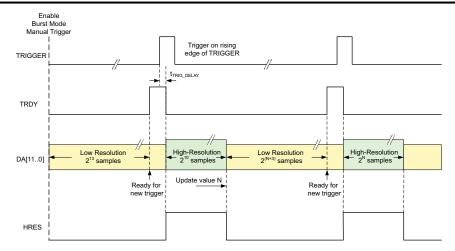

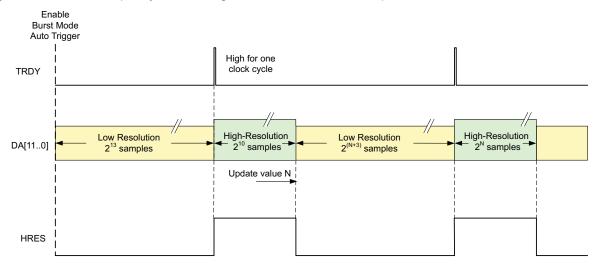

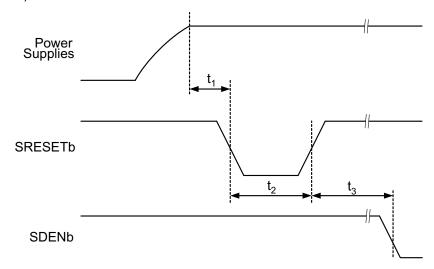

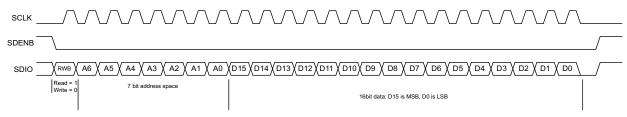

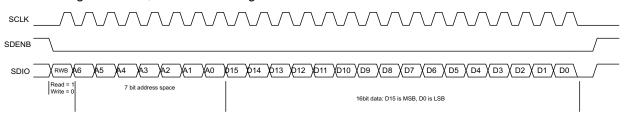

| t <sub>su</sub> | F <sub>s</sub> = 750 Msps     | Data valid to zero-crossing of DACLK            | 320            | 400  |                 | ps       |