# 10-Bit, Octal-Channel ADC Up to 65MSPS

Check for Samples: ADS5287

# **FEATURES**

www.ti.com

- **Speed and Resolution Grades:**

- 10-bit, 65MSPS

- **Power Dissipation:**

- 46mW/Channel at 30MSPS

- 53mW/Channel at 40MSPS

- 62mW/Channel at 50MSPS

- 74mW/Channel at 65MSPS

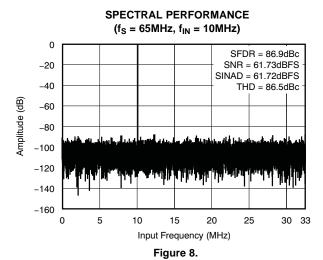

- 61.7dBFS SNR at 10MHz IF

- Analog Input Full-Scale Range: 2V<sub>PP</sub>

- **Low-Frequency Noise Suppression Mode**

- 6dB Overload Recovery in One Clock

- **External and Internal (Trimmed) Reference**

- 3.3V Analog Supply, 1.8V Digital Supply

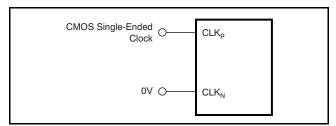

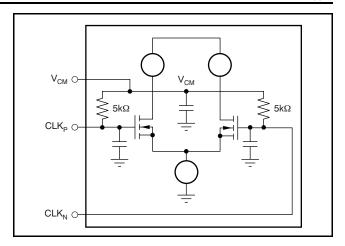

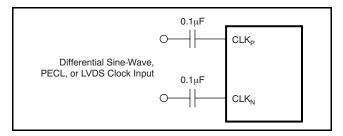

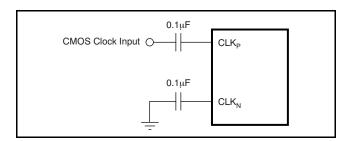

- Single-Ended or Differential Clock:

- Clock Duty Cycle Correction Circuit (DCC)

- Programmable Digital Gain: 0dB to 12dB

- Serialized DDR LVDS Output

- **Programmable LVDS Current Drive, Internal Termination**

- **Test Patterns for Enabling Output Capture**

- **Straight Offset Binary or Two's Complement** Output

- **Package Options:**

- 9mm × 9mm QFN-64

# **APPLICATIONS**

- **Medical Imaging**

- Wireless Base-Station Infrastructure

- **Test and Measurement Instrumentation**

# DESCRIPTION

The ADS5287 is a high-performance, low-power, octal channel analog-to-digital converter (ADC). Available in a 9mm x 9mm QFN package, with serialized low-voltage differential signaling (LVDS) outputs and a wide variety of programmable features, the ADS5287 is highly customizable for a wide range of applications and offers an unprecedented level of system integration. An application note, XAPP774 (available at www.xilinx.com), describes how to interface the serial LVDS outputs of TI's ADCs to Xilinx<sup>®</sup> field-programmable gate arrays (FPGAs). The ADS5287 is specified over the industrial temperature range of -40°C to +85°C.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PowerPAD is a trademark of Texas Instruments, Inc. Xilinx is a registered trademark of Xilinx, Inc.

All other trademarks are the property of their respective owners.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

### **RELATED PRODUCTS**

| MODEL   | RESOLUTION (BITS) | SAMPLE RATE (MSPS) | CHANNELS |

|---------|-------------------|--------------------|----------|

| ADS5281 | 12                | 50                 | 8        |

| ADS5282 | 12                | 65                 | 8        |

| ADS5287 | 10                | 65                 | 8        |

| ADS5270 | 12                | 40                 | 8        |

| ADS5271 | 12                | 50                 | 8        |

| ADS5272 | 12                | 65                 | 8        |

| ADS5273 | 12                | 70                 | 8        |

| ADS5242 | 12                | 65                 | 4        |

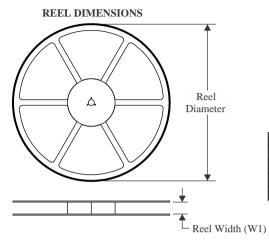

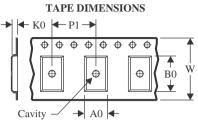

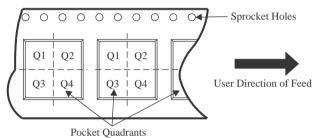

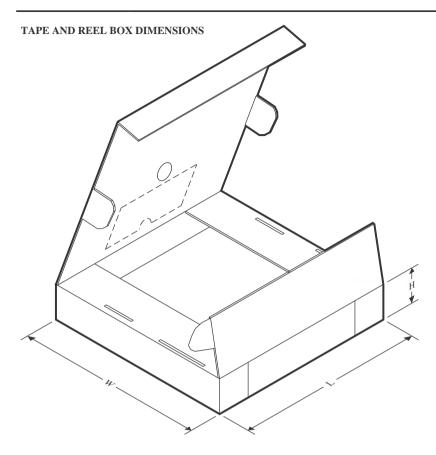

# Table 1. ORDERING INFORMATION<sup>(1)</sup> (2)

| PRODUCT | PACKAGE-LEAD | PACKAGE<br>DESIGNATOR | SPECIFIED<br>TEMPERATURE<br>RANGE | PACKAGE<br>MARKING | ORDERING<br>NUMBER | TRANSPORT<br>MEDIA, QUANTITY <sup>(3)</sup> |

|---------|--------------|-----------------------|-----------------------------------|--------------------|--------------------|---------------------------------------------|

| ADS5287 | QFN-64       | RGC                   | -40°C to +85°C                    | A 7E207            | ADS5287IRGCT       | Tape and Reel                               |

| AD35267 | QFIN-04      | RGC                   | -40 C to +65 C                    | AZ5287             | ADS5287IRGCR       | Tape and Reel                               |

- (1) For the most current package and ordering information see the Package Option Addendum at the end of this document, or see the TI web site at www.ti.com.

- (2) These devices meet the following planned eco-friendly classification: Green (RoHS and No Sb/Br): Texas Instruments defines Green to mean Pb-free (RoHS compatible) and free of bromine (Br)- and antimony (Sb)-based flame retardants. Refer to the Quality and Lead-Free (Pb-Free) Data web site for more information. These devices have a Cu NiPdAu lead/ball finish.

- (3) Refer to the Package Option Addendum at the end of this document for specific transport media and quantity information.

# ABSOLUTE MAXIMUM RATINGS(1)

Over operating free-air temperature range, unless otherwise noted.

|                                                  | AD\$5287                            | UNIT |

|--------------------------------------------------|-------------------------------------|------|

| Supply voltage range, AVDD                       | −0.3 to +3.9                        | V    |

| Supply voltage range, LVDD                       | −0.3 to +2.2                        | V    |

| Voltage between AVSS and LVSS                    | -0.3 to +0.3                        | V    |

| External voltage applied to REF <sub>T</sub> pin | -0.3 to +3                          | V    |

| External voltage applied to REF <sub>B</sub> pin | -0.3 to +2                          | V    |

| Voltage applied to analog input pins             | -0.3 to minimum [3.6, (AVDD + 0.3)] | V    |

| Voltage applied to digital input pins            | -0.3 to minimum [3.9, (AVDD + 0.3)] | V    |

| Peak solder temperature                          | +260                                | °C   |

| Junction temperature                             | +125                                | °C   |

| Storage temperature range                        | -65 to +150                         | °C   |

(1) Stresses above these ratings may cause permanent damage. Exposure to absolute maximum conditions for extended periods may degrade device reliability. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those specified is not supported. www.ti.com

# RECOMMENDED OPERATING CONDITIONS

|                   |                                                                                         |     | ADS5287           |          |          |

|-------------------|-----------------------------------------------------------------------------------------|-----|-------------------|----------|----------|

| PARAM             | ETER                                                                                    | MIN | TYP               | MAX      | UNIT     |

| SUPPLI            | ES, ANALOG INPUTS, AND REFERENCE VOLTAGES                                               |     |                   |          |          |

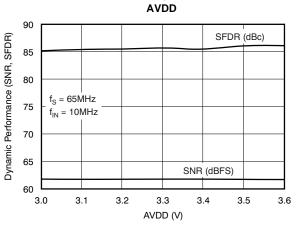

| AVDD              | Analog supply voltage                                                                   | 3.0 | 3.3               | 3.6      | V        |

| LVDD              | Digital supply voltage                                                                  | 1.7 | 1.8               | 1.9      | V        |

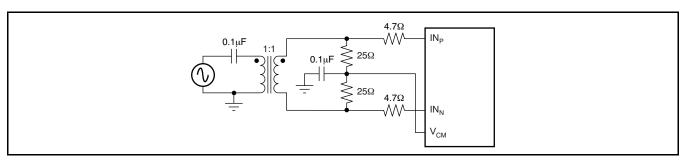

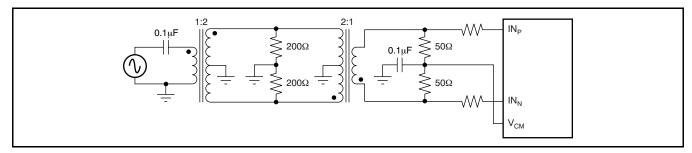

|                   | Differential input voltage range                                                        |     | 2                 |          | $V_{PP}$ |

|                   | Input common-mode voltage                                                               |     | $V_{CM} \pm 0.05$ |          | V        |

| $REF_T$           | External reference mode                                                                 |     | 2.5               |          | V        |

| REFB              | External reference mode                                                                 |     | 0.5               |          | V        |

| CLOCK             | INPUTS                                                                                  |     |                   |          |          |

|                   | ADCLK input sample rate 1/ t <sub>C</sub>                                               | 10  |                   | 50, 65   | MSPS     |

|                   | Input clock amplitude differential (V <sub>CLKP</sub> -V <sub>CLKN</sub> ) peak-to-peak |     |                   |          |          |

|                   | Sine wave, ac-coupled                                                                   |     | 3.0               |          | $V_{PP}$ |

|                   | LVPECL, ac-coupled                                                                      |     | 1.6               |          | $V_{PP}$ |

|                   | LVDS, ac-coupled                                                                        |     | 0.7               |          | $V_{PP}$ |

|                   | Input clock CMOS, single-ended (V <sub>CLKP</sub> )                                     |     |                   |          |          |

|                   | $V_{IL}$                                                                                |     |                   | 0.6      | V        |

|                   | $V_{IH}$                                                                                | 2.2 |                   |          | V        |

|                   | Input clock duty cycle                                                                  |     | 50                |          | %        |

| DIGITAL           | OUTPUTS                                                                                 |     |                   |          |          |

|                   | ADCLK <sub>P</sub> and ADCLK <sub>N</sub> outputs (LVDS)                                | 10  | 1x (sample rate)  | 50, 65   | MHz      |

|                   | LCLK <sub>P</sub> and LCLK <sub>N</sub> outputs (LVDS)                                  | 60  | 6x (sample rate)  | 300, 390 | MHz      |

| $C_{LOAD}$        | Maximum external capacitance from each pin to LVSS                                      |     | 5                 |          | pF       |

| R <sub>LOAD</sub> | Differential load resistance between the LVDS output pairs                              |     | 100               |          | Ω        |

| T <sub>A</sub>    | Operating free-air temperature                                                          | -40 |                   | +85      | °C       |

# **INITIALIZATION REGISTERS**

If the analog input is ac-coupled, the following registers must be written to in the order listed below.

|                           | ADDRESS (hex) | DATA (hex) |

|---------------------------|---------------|------------|

| Initialization Register 1 | 01            | 0010       |

| Initialization Register 5 | E2            | 00C0       |

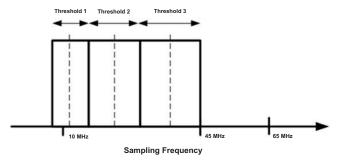

To disable the PLL configuration switching (especially useful in systems where a system-level timing calibration is done once after power-up), the following registers must be written to in the order listed below. Also, see section PLL Operation Across Sampling Frequency.

|                                 | ADDRESS (hex) | DATA (hex) |

|---------------------------------|---------------|------------|

| For 10 ≤ Fs ≤ 25 <sup>(1)</sup> | E3            | 0060       |

| For $15 \le Fs = \le 45^{(1)}$  | E3            | 00A0       |

<sup>(1)</sup> where Fs = sampling clock frequency

# **DIGITAL CHARACTERISTICS**

DC specifications refer to the condition where the digital outputs are not switching, but are permanently at a valid logic level  $^{'0'}$  or  $^{'1'}$ . At  $C_{LOAD} = 5pF^{(1)}$ ,  $I_{OUT} = 3.5mA^{(2)}$ ,  $R_{LOAD} = 100\Omega^{(2)}$ , and no internal termination, unless otherwise noted.

|                                               |                                                                    |     | ADS5287 |     |      |

|-----------------------------------------------|--------------------------------------------------------------------|-----|---------|-----|------|

| PARAMETER                                     | TEST CONDITIONS                                                    | MIN | TYP     | MAX | UNIT |

| DIGITAL INPUTS                                |                                                                    |     |         |     |      |

| High-level input voltage                      |                                                                    | 1.4 |         |     | V    |

| Low-level input voltage                       |                                                                    |     |         | 0.3 | V    |

| High-level input current                      |                                                                    |     | 33      |     | μA   |

| Low-level input current                       |                                                                    |     | -33     |     | μA   |

| Input capacitance                             |                                                                    |     | 3       |     | pF   |

| LVDS OUTPUTS                                  |                                                                    |     |         |     |      |

| High-level output voltage                     |                                                                    |     | 1375    |     | mV   |

| Low-level output voltage                      |                                                                    |     | 1025    |     | mV   |

| Output differential voltage,  V <sub>OD</sub> |                                                                    |     | 350     |     | mV   |

| V <sub>OS</sub> output offset voltage         | Common-mode voltage of OUT <sub>P</sub> and OUT <sub>N</sub>       |     | 1200    |     | mV   |

| Output capacitance                            | Output capacitance inside the device, from either output to ground |     | 2       |     | pF   |

$C_{\text{LOAD}}$  is the effective external single-ended load capacitance between each output pin and ground.  $I_{\text{OUT}}$  refers to the LVDS buffer current setting;  $R_{\text{LOAD}}$  is the differential load resistance between the LVDS output pair.

# **ELECTRICAL CHARACTERISTICS**

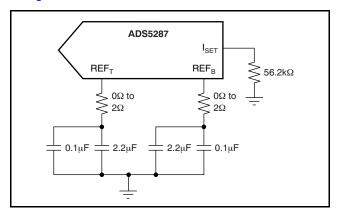

Typical values at +25°C. Minimum and maximum values are measured across the specified temperature range of T<sub>MIN</sub> = -40°C to  $T_{MAX} = +85$ °C, AVDD = 3.3V, LVDD = 1.8V, clock frequency = 10MSPS to 65MSPS, 50% clock duty cycle, -1dBFS differential analog input, internal reference mode,  $I_{SET}$  resistor = 56.2k $\Omega$ , and LVDS buffer current setting = 3.5mA, unless otherwise noted. Typical values at +25°C.

|            |                                                                 |                                                                                                        |       | ADS5287           |       | _                 |

|------------|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-------|-------------------|-------|-------------------|

|            | PARAMETER                                                       | TEST CONDITIONS                                                                                        | MIN   | TYP               | MAX   | UNIT              |

| INTERNAL   | REFERENCE VOLTAGES                                              |                                                                                                        |       |                   |       |                   |

| $V_{REFB}$ | Reference bottom                                                |                                                                                                        |       | 0.5               |       | V                 |

| $V_{REFT}$ | Reference top                                                   |                                                                                                        |       | 2.5               |       | V                 |

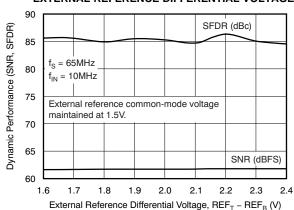

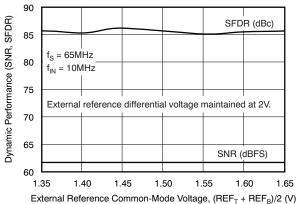

|            | $V_{REFT} - V_{REFB}$                                           |                                                                                                        | 1.95  | 2.0               | 2.05  | V                 |

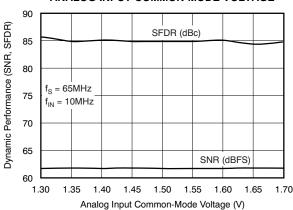

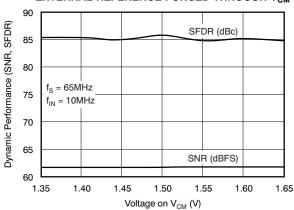

| $V_{CM}$   | Common-mode voltage (internal)                                  |                                                                                                        | 1.425 | 1.5               | 1.575 | V                 |

|            | V <sub>CM</sub> output current                                  |                                                                                                        |       | ±2                |       | mA                |

| EXTERNA    | L REFERENCE VOLTAGES                                            |                                                                                                        |       |                   |       |                   |

| $V_{REFB}$ | Reference bottom                                                |                                                                                                        | 0.4   | 0.5               | 0.6   | V                 |

| $V_{REFT}$ | Reference top                                                   |                                                                                                        | 2.4   | 2.5               | 2.6   | V                 |

|            | $V_{REFT} - V_{REFB}$                                           |                                                                                                        | 1.9   | 2.0               | 2.1   | V                 |

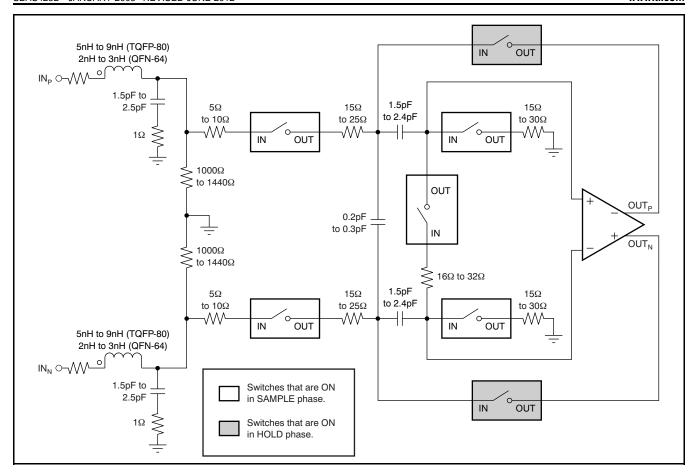

| ANALOG     | INPUT                                                           |                                                                                                        |       |                   |       |                   |

|            | Differential input voltage range                                |                                                                                                        |       | 2.0               |       | $V_{PP}$          |

|            | Differential input capacitance                                  |                                                                                                        |       | 3                 |       | pF                |

|            | Analog input bandwidth                                          |                                                                                                        |       | 520               |       | MHz               |

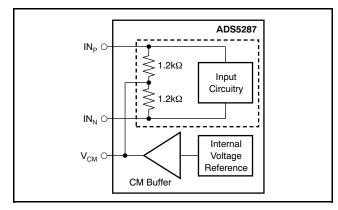

|            | Analog input common-mode range                                  | DC-coupled input                                                                                       |       | $V_{CM} \pm 0.05$ |       | V                 |

|            | Analog input common-mode current                                | Per input pin per MSPS of sampling speed                                                               |       | 2.5               |       | µA/MHz<br>per pin |

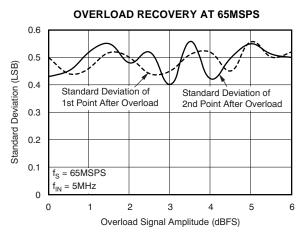

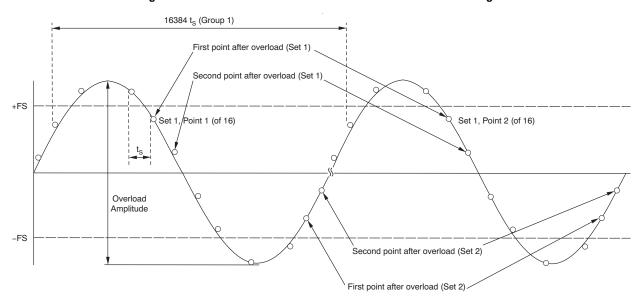

|            | Voltage overload recovery time                                  | Recovery from 6dB overload to within 1% accuracy                                                       |       | 1                 |       | Clock cycle       |

|            | Voltage overload recovery repeatability                         | Standard deviation seen on a periodic first data within full-scale range in a 6dB overloaded sine wave |       | 1                 |       | LSB               |

| DC ACCU    | RACY                                                            |                                                                                                        |       |                   |       |                   |

|            | Offset error                                                    |                                                                                                        | -1.25 | ±0.2              | +1.25 | %FS               |

|            | Offset error temperature coefficient (1)                        |                                                                                                        |       | ±5                |       | ppm/°C            |

|            | Channel gain error                                              | Excludes error in internal reference                                                                   |       | -0.8              |       | %FS               |

|            | Channel gain error temperature coefficient                      | Excludes temperature coefficient of internal reference                                                 |       | ±10               |       | ppm/°C            |

|            | Internal reference error temperature coefficient <sup>(2)</sup> |                                                                                                        |       | ±15               |       | ppm/°C            |

| DC PSRR    | DC power-supply rejection ratio (3)                             |                                                                                                        |       | 1.5               |       | mV/V              |

| POWER-D    | OWN MODES                                                       |                                                                                                        |       |                   |       |                   |

|            | Power in complete power-down mode                               |                                                                                                        |       | 45                |       | mW                |

|            | Power in partial power-down mode                                | Clock at 65MSPS                                                                                        |       | 135               |       | mW                |

|            | Power with no clock                                             |                                                                                                        |       | 88                |       | mW                |

| DYNAMIC    | PERFORMANCE                                                     |                                                                                                        |       |                   |       |                   |

|            | Crosstalk                                                       | 5MHz full-scale signal applied to seven channels, measurement taken on channel with no input signal    |       | -90               |       | dBc               |

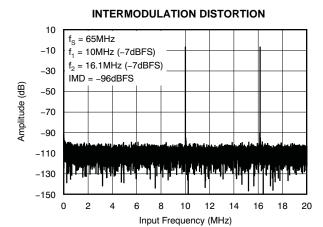

|            | Two-tone, third-order intermodulation distortion                | $f_1 = 9.5$ MHz at $-7$ dBFs $f_2 = 10.2$ MHz at $-7$ dBFs                                             |       | -92               |       | dBFS              |

| DC ACCU    | RACY                                                            |                                                                                                        |       |                   |       |                   |

|            | No missing codes                                                |                                                                                                        |       | Assured           |       |                   |

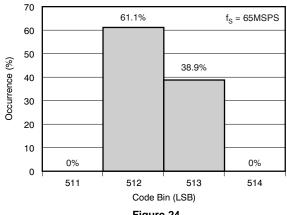

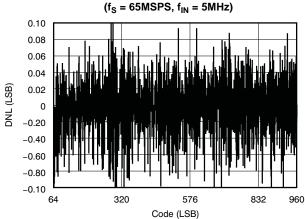

| DNL        | Differential nonlinearity                                       |                                                                                                        | -0.55 | ±0.1              | +0.55 | LSB               |

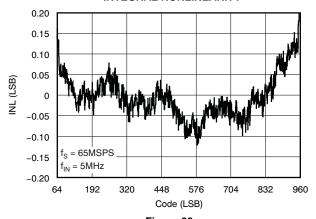

| INL        | Integral nonlinearity                                           |                                                                                                        | -1    | ±0.1              | +1    | LSB               |

|            | UPPLY—INTERNAL REFERENCE MODE                                   |                                                                                                        | *     |                   |       |                   |

<sup>(1)</sup> The offset temperature coefficient in ppm/°C is defined as  $(O_1 - O_2) \times 10^6/(T_1 - T_2)/1024$ , where  $O_1$  and  $O_2$  are the offset codes in LSB

at the two extreme temperatures,  $T_1$  and  $T_2$ . The internal reference temperature coefficient is defined as  $(REF_1 - REF_2) \times 10^6/(T_1 - T_2)/2$ , where  $REF_1$  and  $REF_2$  are the internal reference voltages ( $V_{REFT} - V_{REFB}$ ) at the two extreme temperatures,  $T_1$  and  $T_2$ . DC PSRR is defined as the ratio of the change in the ADC output (expressed in mV) to the change in supply voltage (in volts).

Typical values at +25°C. Minimum and maximum values are measured across the specified temperature range of  $T_{MIN}$  = -40°C to  $T_{MAX}$  = +85°C, AVDD = 3.3V, LVDD = 1.8V, clock frequency = 10MSPS to 65MSPS, 50% clock duty cycle, -1dBFS differential analog input, internal reference mode,  $I_{SET}$  resistor = 56.2k $\Omega$ , and LVDS buffer current setting = 3.5mA, unless otherwise noted. Typical values at +25°C.

|         |                                |                                                                                                       | ADS5287 |      |       |      |

|---------|--------------------------------|-------------------------------------------------------------------------------------------------------|---------|------|-------|------|

|         | PARAMETER                      | TEST CONDITIONS                                                                                       | MIN     | TYP  | MAX   | UNIT |

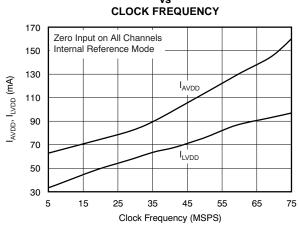

| IAVDD   | Analog supply current          |                                                                                                       |         | 139  | 165   | mA   |

| ILVDD   | Digital current                | Zero input to all channels                                                                            |         | 87   | 97    | mA   |

|         | Total power                    |                                                                                                       |         | 615  | 719.1 | mW   |

|         | Incremental power saving       | Obtained on powering down one channel at a time                                                       |         | 61   |       | mW   |

| POWER S | UPPLY—EXTERNAL REFERENCE MOD   | E                                                                                                     |         |      |       |      |

| IAVDD   | Analog supply current          |                                                                                                       |         | 132  |       | mA   |

| ILVDD   | Digital current                | Zero input to all channels                                                                            |         | 87   |       | mA   |

|         | Total power                    |                                                                                                       |         | 592  |       | mW   |

|         | Incremental power saving       | Obtained on powering down one channel at a time                                                       |         | 59   |       | mW   |

| EXTERNA | L REFERENCE LOADING            |                                                                                                       |         |      |       |      |

|         | Switching current              | Current drawn by the eight ADCs from the external reference voltages; sourcing for REF <sub>B</sub> . |         | 3.5  |       | mA   |

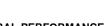

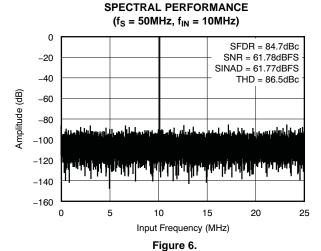

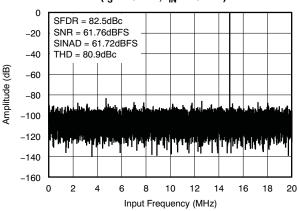

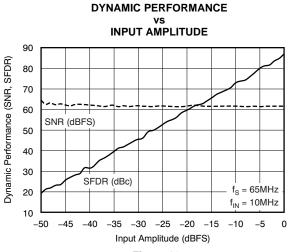

| DYNAMIC | CHARACTERISTICS                |                                                                                                       |         |      |       |      |

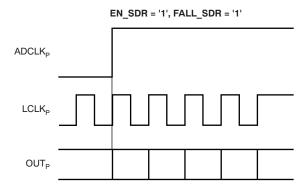

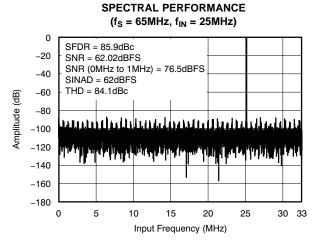

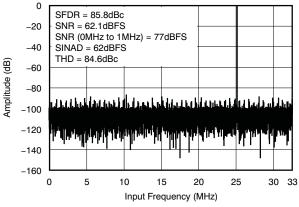

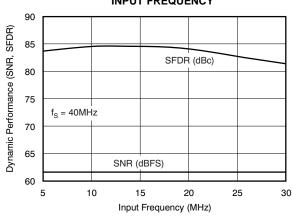

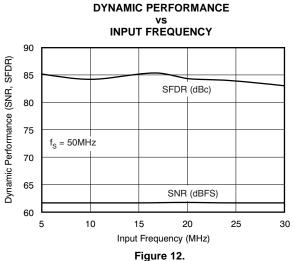

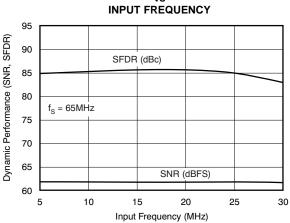

| SFDR    | Spurious-free dynamic range    | f <sub>IN</sub> = 5MHz, single-ended clock                                                            | 72      | 85   |       | dBc  |

| SFUK    | Spurious-free dynamic range    | f <sub>IN</sub> = 30MHz, differential clock                                                           |         | 80   |       | dBc  |

| HD2     | Magnitude of second harmonic   | f <sub>IN</sub> = 5MHz, single-ended clock                                                            | 72      | 85   |       | dBc  |

| ПО2     | Magnitude of Second Harmonic   | f <sub>IN</sub> = 30MHz, differential clock                                                           |         | 82   |       | dBc  |

| HD3     | Magnitude of third harmonic    | f <sub>IN</sub> = 5MHz, single-ended clock                                                            | 72      | 85   |       | dBc  |

| прз     | Magnitude of third narmonic    | f <sub>IN</sub> = 30MHz, differential clock                                                           |         | 80   |       | dBc  |

| THD     | Total harmonic distortion      | f <sub>IN</sub> = 5MHz, single-ended clock                                                            | 70      | 80   |       | dBc  |

| טווו    | Total Harmonic distortion      | f <sub>IN</sub> = 30MHz, differential clock                                                           |         | 78   |       | dBc  |

| SNR     | Signal-to-noise ratio          | f <sub>IN</sub> = 5MHz, single-ended clock                                                            | 60.5    | 61.7 |       | dBc  |

| SINK    | Signal-to-Hoise ratio          | f <sub>IN</sub> = 30MHz, differential clock                                                           |         | 61.7 |       | dBc  |

| SINAD   | Signal-to-noise and distortion | f <sub>IN</sub> = 5MHz, single-ended clock                                                            | 60.4    | 61.6 |       | dBc  |

| SINAD   | Signal-to-noise and distortion | f <sub>IN</sub> = 30MHz, differential clock                                                           |         | 61.6 |       | dBc  |

# **PIN CONFIGURATION**

# QFN-64 PowerPAD™ TOP VIEW

Table 2. PIN DESCRIPTIONS: QFN-64

| PIN NAME           | DESCRIPTION                                                                           | PIN NUMBER              | # OF PINS |

|--------------------|---------------------------------------------------------------------------------------|-------------------------|-----------|

| ADCLK <sub>N</sub> | LVDS frame clock (1X)—negative output                                                 | 24                      | 1         |

| ADCLK <sub>P</sub> | LVDS frame clock (1X)—positive output                                                 | 23                      | 1         |

| AVDD               | Analog power supply, 3.3V                                                             | 49, 50, 57, 60          | 4         |

| AVSS               | Analog ground                                                                         | 3, 6, 9, 37, 40, 43, 46 | 7         |

| CLK <sub>N</sub>   | Negative differential clock input Tie CLK <sub>N</sub> to 0V for a single-ended clock | 59                      | 1         |

| CLK <sub>P</sub>   | Positive differential clock input                                                     | 58                      | 1         |

| <u>cs</u>          | Serial enable chip select—active low digital input                                    | 61                      | 1         |

| IN1 <sub>N</sub>   | Negative differential input signal, channel 1                                         | 2                       | 1         |

| IN1 <sub>P</sub>   | Positive differential input signal, channel 1                                         | 1                       | 1         |

| IN2 <sub>N</sub>   | Negative differential input signal, channel 2                                         | 5                       | 1         |

| IN2 <sub>P</sub>   | Positive differential input signal, channel 2                                         | 4                       | 1         |

| IN3 <sub>N</sub>   | Negative differential input signal, channel 3                                         | 8                       | 1         |

| IN3 <sub>P</sub>   | Positive differential input signal, channel 3                                         | 7                       | 1         |

| IN4 <sub>N</sub>   | Negative differential input signal, channel 4                                         | 11                      | 1         |

| IN4 <sub>P</sub>   | Positive differential input signal, channel 4                                         | 10                      | 1         |

# Table 2. PIN DESCRIPTIONS: QFN-64 (continued)

| PIN NAME          | DESCRIPTION                                   | PIN NUMBER | # OF PINS |

|-------------------|-----------------------------------------------|------------|-----------|

| IN5 <sub>N</sub>  | Negative differential input signal, channel 5 | 39         | 1         |

| IN5 <sub>P</sub>  | Positive differential input signal, channel 5 | 38         | 1         |

| IN6 <sub>N</sub>  | Negative differential input signal, channel 6 | 42         | 1         |

| IN6 <sub>P</sub>  | Positive differential input signal, channel 6 | 41         | 1         |

| IN7 <sub>N</sub>  | Negative differential input signal, channel 7 | 45         | 1         |

| IN7 <sub>P</sub>  | Positive differential input signal, channel 7 | 44         | 1         |

| IN8 <sub>N</sub>  | Negative differential input signal, channel 8 | 48         | 1         |

| IN8 <sub>P</sub>  | Positive differential input signal, channel 8 | 47         | 1         |

| INT/EXT           | Internal/external reference mode select input | 56         | 1         |

| I <sub>SET</sub>  | Bias pin—56.2kΩ to ground                     | 51         | 1         |

| LCLK <sub>N</sub> | LVDS bit clock (6X)—negative output           | 26         | 1         |

| LCLK <sub>P</sub> | LVDS bit clock (6X)—positive output           | 25         | 1         |

| LVDD              | Digital and I/O power supply, 1.8V            | 35         | 1         |

| LVSS              | Digital ground                                | 12, 14, 36 | 3         |

| OUT1 <sub>N</sub> | LVDS channel 1—negative output                | 16         | 1         |

| OUT1 <sub>P</sub> | LVDS channel 1—positive output                | 15         | 1         |

| OUT2 <sub>N</sub> | LVDS channel 2—negative output                | 18         | 1         |

| OUT2 <sub>P</sub> | LVDS channel 2—positive output                | 17         | 1         |

| OUT3 <sub>N</sub> | LVDS channel 3—negative output                | 20         | 1         |

| OUT3 <sub>P</sub> | LVDS channel 3—positive output                | 19         | 1         |

| OUT4 <sub>N</sub> | LVDS channel 4—negative output                | 22         | 1         |

| OUT4 <sub>P</sub> | LVDS channel 4—positive output                | 21         | 1         |

| OUT5 <sub>N</sub> | LVDS channel 5—negative output                | 28         | 1         |

| OUT5 <sub>P</sub> | LVDS channel 5—positive output                | 27         | 1         |

| OUT6 <sub>N</sub> | LVDS channel 6—negative output                | 30         | 1         |

| OUT6 <sub>P</sub> | LVDS channel 6—positive output                | 29         | 1         |

| OUT7 <sub>N</sub> | LVDS channel 7—negative output                | 32         | 1         |

| OUT7 <sub>P</sub> | LVDS channel 7—positive output                | 31         | 1         |

| OUT8 <sub>N</sub> | LVDS channel 8—negative output                | 34         | 1         |

| OUT8 <sub>P</sub> | LVDS channel 8—positive output                | 33         | 1         |

| PD                | Power-down input                              | 13         | 1         |

| REFB              | Negative reference input/output               | 54         | 1         |

| REF <sub>T</sub>  | Positive reference input/output               | 55         | 1         |

| RESET             | Active low RESET input                        | 64         | 1         |

| SCLK              | Serial clock input                            | 63         | 1         |

| SDATA             | Serial data input                             | 62         | 1         |

| TP                | Test pin, do not use                          | 52         | 1         |

| $V_{CM}$          | Common-mode output pin, 1.5V output           | 53         | 1         |

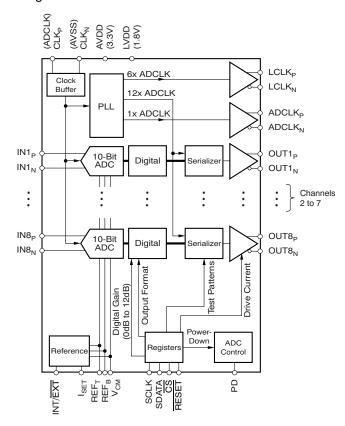

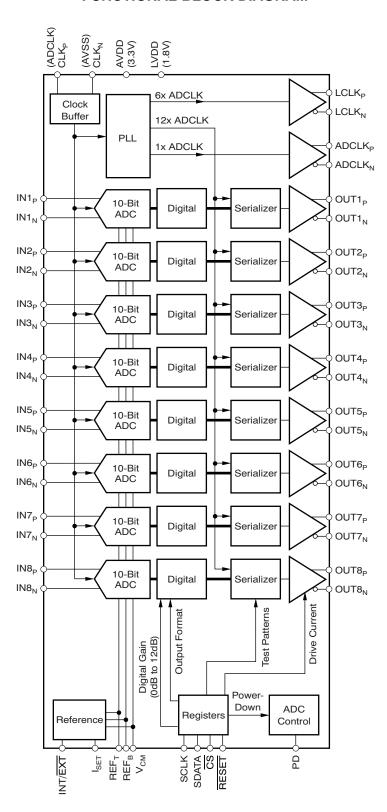

# **FUNCTIONAL BLOCK DIAGRAM**

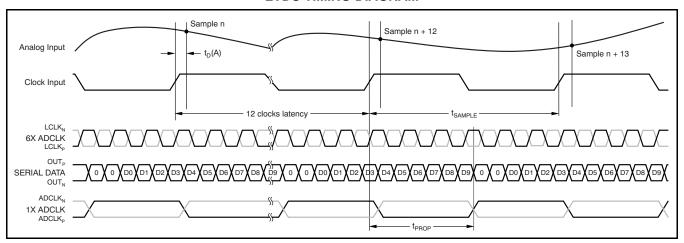

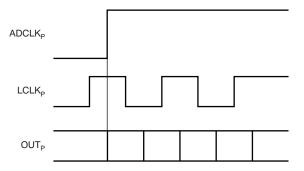

# **LVDS TIMING DIAGRAM**

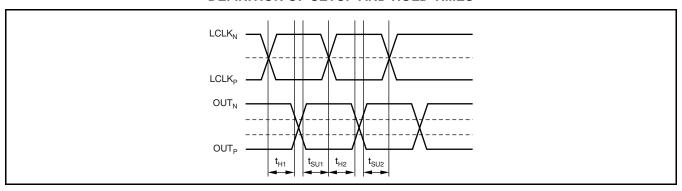

# **DEFINITION OF SETUP AND HOLD TIMES**

$t_{SU} = min(t_{SU1}, t_{SU2})$  $t_{H} = min(t_{H1}, t_{H2})$

# TIMING CHARACTERISTICS(1)

|                   |                          |                                                                                                                 |     | ADS5287 |     |                 |

|-------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------|-----|---------|-----|-----------------|

|                   | PARAMETER                | TEST CONDITIONS                                                                                                 | MIN | TYP     | MAX | UNIT            |

| t <sub>A</sub>    | Aperture delay           |                                                                                                                 | 1.5 |         | 4.5 | ns              |

|                   | Aperture delay variation | Channel-to-channel within the same device (3σ)                                                                  |     | ±20     |     | ps              |

| tJ                | Aperture jitter          |                                                                                                                 |     | 400     |     | fs              |

| t <sub>WAKE</sub> |                          | Time to valid data after coming out of COMPLETE POWER-DOWN mode                                                 |     | 50      |     | μs              |

|                   | Wake-up time             | Time to valid data after coming out of PARTIAL POWER-DOWN mode (with clock continuing to run during power-down) |     | 2       |     | μs              |

|                   |                          | Time to valid data after stopping and restarting the input clock                                                |     | 40      |     | μs              |

|                   | Data latency             |                                                                                                                 |     | 12      |     | Clock<br>cycles |

(1) Timing parameters are ensured by design and characterization; not production tested.

# LVDS OUTPUT TIMING CHARACTERISTICS(1)

Typical values are at +25°C, minimum and maximum values are measured across the specified temperature range of  $T_{MIN} = -40$ °C to  $T_{MAX} = +85$ °C, sampling frequency = as specified,  $C_{LOAD} = 5pF^{(2)}$ ,  $I_{OUT} = 3.5mA$ ,  $R_{LOAD} = 100\Omega^{(3)}$ , and no internal termination, unless otherwise noted.

|                                                |                                                |                                                                                                         |      |        |      |      | ADS5287 |      |      |        |     |        |

|------------------------------------------------|------------------------------------------------|---------------------------------------------------------------------------------------------------------|------|--------|------|------|---------|------|------|--------|-----|--------|

|                                                |                                                |                                                                                                         |      | 40MSPS |      |      | 50MSPS  |      |      | 65MSPS |     |        |

|                                                | PARAMETER                                      | TEST CONDITIONS(4)                                                                                      | MIN  | TYP    | MAX  | MIN  | TYP     | MAX  | MIN  | TYP    | MAX | UNIT   |

| t <sub>SU</sub>                                | Data setup time <sup>(5)</sup>                 | Data valid <sup>(6)</sup> to zero-crossing of LCLK <sub>P</sub>                                         | 0.67 |        |      | 0.47 |         |      | 0.27 |        |     | ns     |

| t <sub>H</sub>                                 | Data hold time <sup>(5)</sup>                  | Zero-crossing of LCLK <sub>P</sub> to data becoming invalid <sup>(6)</sup>                              | 0.85 |        |      | 0.65 |         |      | 0.4  |        |     | ns     |

| t <sub>PROP</sub>                              | Clock propagation delay                        | Input clock (ADCLK) rising edge cross-over to output clock (ADCLK <sub>P</sub> ) rising edge cross-over | 10   | 14     | 16.6 | 10   | 12.5    | 14.1 | 9.7  | 11.5   | 14  | ns     |

|                                                | LVDS bit clock duty cycle                      | Duty cycle of differential clock,<br>(LCLK <sub>P</sub> – LCLK <sub>N</sub> )                           | 45.5 | 50     | 53   | 45   | 50      | 53.5 | 41   | 50     | 57  |        |

|                                                | Bit clock cycle-to-cycle jitter                |                                                                                                         |      | 250    |      |      | 250     |      |      | 250    |     | ps, pp |

|                                                | Frame clock cycle-to-cycle jitter              |                                                                                                         |      | 150    |      |      | 150     |      |      | 150    |     | ps, pp |

| t <sub>RISE</sub> ,<br>t <sub>FALL</sub>       | Data rise time, data fall time                 | Rise time is from -100mV to +100mV Fall time is from +100mV to -100mV                                   | 0.09 | 0.2    | 0.4  | 0.09 | 0.2     | 0.4  | 0.09 | 0.2    | 0.4 | ns     |

| t <sub>CLKRISE</sub> ,<br>t <sub>CLKFALL</sub> | Output clock rise time, output clock fall time | Rise time is from -100mV to +100mV Fall time is from +100mV to -100mV                                   | 0.09 | 0.2    | 0.4  | 0.09 | 0.2     | 0.4  | 0.09 | 0.2    | 0.4 | ns     |

- (1) Timing parameters are ensured by design and characterization; not production tested.

- (2) C<sub>LOAD</sub> is the effective external single-ended load capacitance between each output pin and ground.

- (3) IOUT refers to the LVDS buffer current setting; RLOAD is the differential load resistance between the LVDS output pair.

- (4) Measurements are done with a transmission line of 100Ω characteristic impedance between the device and the load.

- (5) Setup and hold time specifications take into account the effect of jitter on the output data and clock. These specifications also assume that data and clock paths are perfectly matched within the receiver. Any mismatch in these paths within the receiver would appear as reduced timing margin.

- (6) Data valid refers to a logic high of +100mV and a logic low of -100mV.

# LVDS OUTPUT TIMING CHARACTERISTICS(1)

Typical values are at +25°C, minimum and maximum values are measured across the specified temperature range of  $T_{MIN} = -40$ °C to  $T_{MAX} = +85$ °C, sampling frequency = as specified,  $C_{LOAD} = 5pF^{(2)}$ ,  $I_{OUT} = 3.5mA$ ,  $R_{LOAD} = 100\Omega^{(3)}$ , and no internal termination, unless otherwise noted.

|                                                |                                                |                                                                                                         |      |        |      |      | ADS5287 |      |      |        |      |        |

|------------------------------------------------|------------------------------------------------|---------------------------------------------------------------------------------------------------------|------|--------|------|------|---------|------|------|--------|------|--------|

|                                                |                                                |                                                                                                         |      | 30MSPS |      |      | 20MSPS  |      |      | 10MSPS |      |        |

|                                                | PARAMETER                                      | TEST CONDITIONS(4)                                                                                      | MIN  | TYP    | MAX  | MIN  | TYP     | MAX  | MIN  | TYP    | MAX  | UNIT   |

| t <sub>SU</sub>                                | Data setup time <sup>(5)</sup>                 | Data valid <sup>(6)</sup> to zero-crossing of LCLK <sub>P</sub>                                         | 0.8  |        |      | 1.5  |         |      | 3.7  |        |      | ns     |

| t <sub>H</sub>                                 | Data hold time <sup>(5)</sup>                  | Zero-crossing of LCLK <sub>P</sub> to data becoming invalid <sup>(6)</sup>                              | 1.2  |        |      | 1.9  |         |      | 3.9  |        |      | ns     |

| t <sub>PROP</sub>                              | Clock propagation delay                        | Input clock (ADCLK) rising edge cross-over to output clock (ADCLK <sub>P</sub> ) rising edge cross-over | 9.5  | 13.5   | 17.3 | 9.5  | 14.5    | 17.3 | 10   | 14.7   | 17.1 | ns     |

|                                                | LVDS bit clock duty cycle                      | Duty cycle of differential clock,<br>(LCLK <sub>P</sub> – LCLK <sub>N</sub> )                           | 46.5 | 50     | 52   | 48   | 50      | 51   | 49   | 50     | 51   |        |

|                                                | Bit clock cycle-to-cycle jitter                |                                                                                                         |      | 250    |      |      | 250     |      |      | 750    |      | ps, pp |

|                                                | Frame clock cycle-to-cycle jitter              |                                                                                                         |      | 150    |      |      | 150     |      |      | 500    |      | ps, pp |

| t <sub>RISE</sub> ,<br>t <sub>FALL</sub>       | Data rise time, data fall time                 | Rise time is from -100mV to +100mV Fall time is from +100mV to -100mV                                   | 0.09 | 0.2    | 0.4  | 0.09 | 0.2     | 0.4  | 0.09 | 0.2    | 0.4  | ns     |

| t <sub>CLKRISE</sub> ,<br>t <sub>CLKFALL</sub> | Output clock rise time, output clock fall time | Rise time is from -100mV to +100mV Fall time is from +100mV to -100mV                                   | 0.09 | 0.2    | 0.4  | 0.09 | 0.2     | 0.4  | 0.09 | 0.2    | 0.4  | ns     |

- (1) Timing parameters are ensured by design and characterization; not production tested.

- (2) C<sub>LOAD</sub> is the effective external single-ended load capacitance between each output pin and ground.

- (3) I<sub>OUT</sub> refers to the LVDS buffer current setting; R<sub>LOAD</sub> is the differential load resistance between the LVDS output pair.

- (4) Measurements are done with a transmission line of 100Ω characteristic impedance between the device and the load.

- (5) Setup and hold time specifications take into account the effect of jitter on the output data and clock. These specifications also assume that data and clock paths are perfectly matched within the receiver. Any mismatch in these paths within the receiver would appear as reduced timing margin.

- (6) Data valid refers to a logic high of +100mV and a logic low of -100mV.

# LVDS OUTPUT TIMING CHARACTERISTICS

| PARAMETER <sup>(1)</sup> | TEST CONDITIONS                                                                          | TIMINGS WH | EN USING REGISTE<br>At 40 MSPS | ER 0xE3 <sup>(2)</sup> |

|--------------------------|------------------------------------------------------------------------------------------|------------|--------------------------------|------------------------|

|                          |                                                                                          | MIN        | TYP                            | MAX                    |

| Data setup time          | Data valid <sup>(3)</sup> to zero-crossing of LCLKp                                      | 0.60       |                                |                        |

| Data hold time           | Zero-crossing of LCLKP to data becoming invalid <sup>(3)</sup>                           | 0.92       |                                |                        |

| Clock propagation delay  | Input clock (ADCLK) rising edge cross-over to output clock (ADCLK) rising edge crossover | 8          | 12                             | 14.6                   |

- (1) Only the setup time, hold time and clock propagation delay parameters are affected. Rest of the parameters are same as given in previous two tables.

- (2) Only timing specifications for 40MSPS are affected when using register 0xE3 (as specified in the recommended operating table section). The timing specifications for other clock frequencies are same as given in previous two tables.

- (3) Data valid refers to logic high of +100mV and logic low of -100mV.

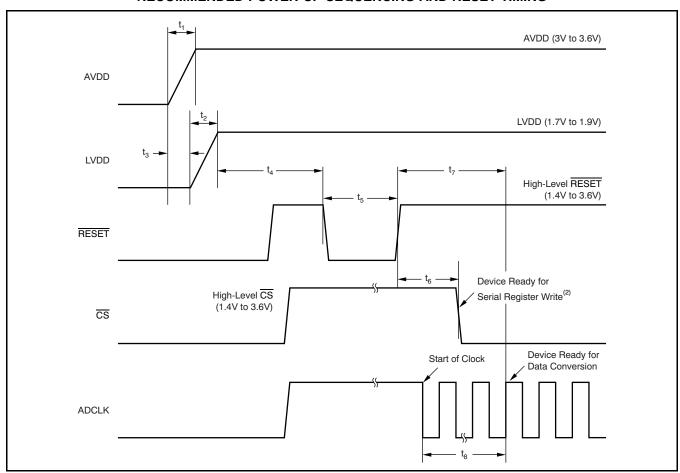

# RECOMMENDED POWER-UP SEQUENCING AND RESET TIMING

$10\mu s < t_1 < 50ms$ ,  $10\mu s < t_2 < 50ms$ , -10ms  $< t_3 < 10ms$ ,  $t_4 > 10ms$ ,  $t_5 > 100ns$ ,  $t_6 > 100ns$ ,  $t_7 > 10ms$ , and  $t_8 > 100\mu s$ .

- (1) The AVDD and LVDD power-on sequence does not matter as long as -10ms <  $t_3$  < 10ms. Similar considerations apply while shutting down the device.

- (2) Write initialization registers listed in the Initialization Registers table.

# **POWER-DOWN TIMING**

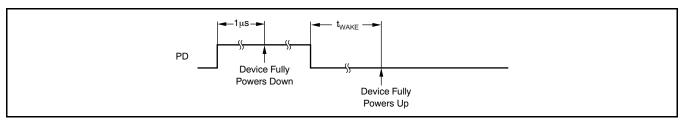

Power-up time shown is based on  $1\mu F$  bypass capacitors on the reference pins.  $t_{WAKE}$  is the time it takes for the device to wake up completely from power-down mode. The ADS5287 has two power-down modes: complete power-down mode and partial power-down mode. The device can be configured in partial power-down mode through a register setting.

$t_{WAKE}$  < 50µs for complete power-down mode.

$t_{\text{WAKE}}$  <  $2\mu s$  for partial power-down mode (provided the clock is not shut off during power-down).

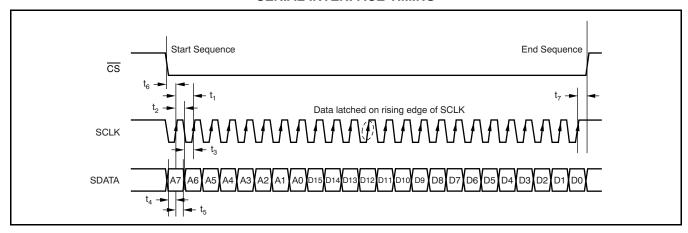

#### SERIAL INTERFACE

The ADS5287 has a set of internal registers that can be accessed through the serial interface formed by pins CS (chip select, active low), SCLK (serial interface clock), and SDATA (serial interface data). When CS is low, the following actions occur:

- · Serial shift of bits into the device is enabled

- SDATA (serial data) is latched at every rising edge of SCLK

- SDATA is loaded into the register at every 24th SCLK rising edge

If the word length exceeds a multiple of 24 bits, the excess bits are ignored. Data can be loaded in multiples of 24-bit words within a single active  $\overline{\text{CS}}$  pulse. The first eight bits form the register address and the remaining 16 bits form the register data. The interface can work with SCLK frequencies from 20MHz down to very low speeds (a few hertz) and also with a non-50% SCLK duty cycle.

# **Register Initialization**

After power-up, the internal registers *must* be initialized to the respective default values. Initialization can be done in one of two ways:

- 1. Through a hardware reset, by applying a low-going pulse on the RESET pin; or

- 2. Through a software reset; using the serial interface, set the RST bit high. Setting this bit initializes the <a href="internal">internal</a> registers to the respective default values and then self-resets the RST bit low. In this case, the RESET pin stays high (inactive).

# **SERIAL INTERFACE TIMING**

|                |                                                      |     | ADS5287 |     |      |

|----------------|------------------------------------------------------|-----|---------|-----|------|

| PARAMETER      | DESCRIPTION                                          | MIN | TYP     | MAX | UNIT |

| t <sub>1</sub> | SCLK period                                          | 50  |         |     | ns   |

| t <sub>2</sub> | SCLK high time                                       | 20  |         |     | ns   |

| t <sub>3</sub> | SCLK low time                                        | 20  |         |     | ns   |

| t <sub>4</sub> | Data setup time                                      | 5   |         |     | ns   |

| t <sub>5</sub> | Data hold time                                       | 5   |         |     | ns   |

| t <sub>6</sub> | CS fall to SCLK rise                                 | 8   |         |     | ns   |

| t <sub>7</sub> | Time between last SCLK rising edge to CS rising edge | 8   |         |     | ns   |

# **SERIAL REGISTER MAP**

# Table 3. SUMMARY OF FUNCTIONS SUPPORTED BY SERIAL INTERFACE<sup>(1)</sup> (2) (3) (4)

| ADDRESS<br>IN HEX | D15 | D14 | D13 | D12 | D11  | D10  | D9 | D8 | D7         | D6 | D5 | D4 | D3 | D2 | D1 | D0 | NAME                  | DESCRIPTION                                                                                                     | DEFAULT                           |

|-------------------|-----|-----|-----|-----|------|------|----|----|------------|----|----|----|----|----|----|----|-----------------------|-----------------------------------------------------------------------------------------------------------------|-----------------------------------|

| 00                | D13 | D14 | D13 | D12 | D.11 | D.10 | D3 | 50 | <i>D</i> , | D0 | 55 | 54 | 55 | D2 | -  | X  | RST                   | Self-clearing software RESET.                                                                                   | Inactive                          |

|                   |     |     |     |     |      |      |    |    |            |    | ., | ., | ., |    |    |    |                       | Channel-specific ADC power-                                                                                     |                                   |

|                   |     |     |     |     |      |      |    |    | Х          | Х  | Х  | Х  | Х  | Х  | Х  | Х  | PDN_CH<8:1>           | down mode.                                                                                                      | Inactive                          |

| 0F                |     |     |     |     |      |      |    | Х  |            |    |    |    |    |    |    |    | PDN_PARTIAL           | Partial power-down mode (fast recovery from power-down).                                                        | Inactive                          |

| 01                |     |     |     |     |      |      | Х  |    |            |    |    |    |    |    |    |    | PDN_COMPLETE          | Register mode for complete power-down (slower recovery).                                                        | Inactive                          |

|                   |     |     |     |     |      | Х    |    |    |            |    |    |    |    |    |    |    | PDN_PIN_CFG           | Configures the PD pin for partial power-down mode.                                                              | Complete power-down               |

|                   |     |     |     |     |      |      |    |    |            |    |    |    |    | Х  | Х  | х  | ILVDS_LCLK<2:0>       | LVDS current drive programmability for LCLK <sub>N</sub> and LCLK <sub>P</sub> pins.                            | 3.5mA drive                       |

| 11                |     |     |     |     |      |      |    |    |            | X  | Х  | X  |    |    |    |    | ILVDS_FRAME<br><2:0>  | LVDS current drive programmability for ADCLK <sub>N</sub> and ADCLK <sub>P</sub> pins.                          | 3.5mA drive                       |

|                   |     |     |     |     |      | Х    | Х  | х  |            |    |    |    |    |    |    |    | ILVDS_DAT<2:0>        | LVDS current drive programmability for OUT <sub>N</sub> and OUT <sub>P</sub> pins.                              | 3.5mA drive                       |

|                   |     | Х   |     |     |      |      |    |    |            |    |    |    |    |    |    |    | EN_LVDS_TERM          | Enables internal termination for LVDS buffers.                                                                  | Termination disabled              |

| 12                |     | 1   |     |     |      |      |    |    |            |    |    |    |    | Х  | Х  | х  | TERM_LCLK<2:0>        | Programmable termination for LCLK <sub>N</sub> and LCLK <sub>P</sub> buffers.                                   | Termination disabled              |

| 12                |     | 1   |     |     |      |      |    |    |            | Х  | Х  | Х  |    |    |    |    | TERM_FRAME<br><2:0>   | Programmable termination for ADCLK $_{\rm N}$ and ADCLK $_{\rm P}$ buffers.                                     | Termination disabled              |

|                   |     | 1   |     |     |      | х    | Х  | х  |            |    |    |    |    |    |    |    | TERM_DAT<2:0>         | Programmable termination for OUT <sub>N</sub> and OUT <sub>P</sub> buffers.                                     | Termination disabled              |

| 14                |     |     |     |     |      |      |    |    | X          | Х  | Х  | X  | Х  | X  | Х  | Х  | LFNS_CH<8:1>          | Channel-specific, low-frequency noise suppression mode enable.                                                  | Inactive                          |

| 24                |     |     |     |     |      |      |    |    | Х          | Х  | х  | Х  | х  | Х  | Х  | х  | INVERT_CH<8:1>        | Swaps the polarity of the analog input pins electrically.                                                       | IN <sub>P</sub> is positive input |

|                   |     |     |     |     |      |      |    |    |            | Х  | 0  | 0  |    |    |    |    | EN_RAMP               | Enables a repeating full-scale ramp pattern on the outputs.                                                     | Inactive                          |

|                   |     |     |     |     |      |      |    |    |            | 0  | Х  | 0  |    |    |    |    | DUALCUSTOM_<br>PAT    | Enables the mode wherein the output toggles between two defined codes.                                          | Inactive                          |

| 25                |     |     |     |     |      |      |    |    |            | 0  | 0  | Х  |    |    |    |    | SINGLE_CUSTOM<br>_PAT | Enables the mode wherein the output is a constant specified code.                                               | Inactive                          |

|                   |     |     |     |     |      |      |    |    |            |    |    |    |    |    | x  | x  | BITS_CUSTOM1<br><9:8> | 2MSBs for a single custom pattern (and for the first code of the dual custom pattern). <9> is the MSB.          | Inactive                          |

|                   |     |     |     |     |      |      |    |    |            |    |    |    | х  | Х  |    |    | BITS_CUSTOM2<br><9:8> | 2MSBs for the second code of the dual custom pattern.                                                           | Inactive                          |

| 26                | Х   | Х   | х   | х   | Х    | х    | x  | х  |            |    |    |    |    |    |    |    | BITS_CUSTOM1<br><7:0> | 8 lower bits for the single custom pattern (and for the first code of the dual custom pattern). <0> is the LSB. | Inactive                          |

| 27                | Х   | Х   | Х   | Х   | Х    | Х    | Х  | х  |            |    |    |    |    |    |    |    | BITS_CUSTOM2<br><7:0> | 8 lower bits for the second code of the dual custom pattern.                                                    | Inactive                          |

|                   |     |     |     |     |      |      |    |    |            |    |    |    | Х  | Х  | Х  | Х  | GAIN_CH1<3:0>         | Programmable gain channel 1.                                                                                    | 0dB gain                          |

| 2A                |     |     |     |     |      |      |    |    | Χ          | Х  | Х  | Х  |    |    |    |    | GAIN_CH2<3:0>         | Programmable gain channel 2.                                                                                    | 0dB gain                          |

| 20                |     |     |     |     | Х    | Х    | Х  | Х  |            |    |    |    |    |    |    |    | GAIN_CH3<3:0>         | Programmable gain channel 3.                                                                                    | 0dB gain                          |

|                   | Χ   | Χ   | Χ   | Х   |      |      |    |    |            |    |    |    |    |    |    |    | GAIN_CH4<3:0>         | Programmable gain channel 4.                                                                                    | 0dB gain                          |

|                   | Х   | Χ   | Χ   | Χ   |      |      |    |    |            |    |    |    |    |    |    |    | GAIN_CH5<3:0>         | Programmable gain channel 5.                                                                                    | 0dB gain                          |

| 2B                |     |     |     |     | Х    | Х    | Χ  | Х  |            |    |    |    |    |    |    |    | GAIN_CH6<3:0>         | Programmable gain channel 6.                                                                                    | 0dB gain                          |

| 20                |     |     |     |     |      |      |    |    | Х          | Х  | Х  | Х  |    |    |    |    | GAIN_CH7<3:0>         | Programmable gain channel 7.                                                                                    | 0dB gain                          |

|                   |     |     |     |     |      |      |    |    |            |    |    |    | Χ  | Χ  | Χ  | Χ  | GAIN_CH8<3:0>         | Programmable gain channel 8.                                                                                    | 0dB gain                          |

The unused bits in each register (identified as blank table cells) must be programmed as '0'.

<sup>(2)</sup>

X = Register bit referenced by the corresponding name and description (default is 0).

Bits marked as '0' should be forced to 0, and bits marked as '1' should be forced to 1 when the particular register is programmed.

Multiple functions in a register should be programmed in a single write operation.

# Table 3. SUMMARY OF FUNCTIONS SUPPORTED BY SERIAL INTERFACE<sup>(1) (2) (3) (4)</sup> (continued)

| ADDRESS<br>IN HEX | D15 | D14 | D13 | D12   | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | NAME           | DESCRIPTION                                                                                                                | DEFAULT                                                                  |

|-------------------|-----|-----|-----|-------|-----|-----|----|----|----|----|----|----|----|----|----|----|----------------|----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

|                   | 1   |     |     | - 1.2 |     | 2.0 |    |    |    |    |    |    |    |    |    | Х  | DIFF_CLK       | Differential clock mode.                                                                                                   | Single-<br>ended clock                                                   |

|                   | 1   |     |     |       |     |     |    |    |    |    |    |    |    | Х  |    |    | EN_DCC         | Enables the duty-cycle correction circuit.                                                                                 | Disabled                                                                 |

| 42                | 1   |     |     |       |     |     |    |    |    |    |    |    | x  |    |    |    | EXT_REF_VCM    | Drives the external reference mode through the V <sub>CM</sub> pin.                                                        | External<br>reference<br>drives REF <sub>T</sub><br>and REF <sub>B</sub> |

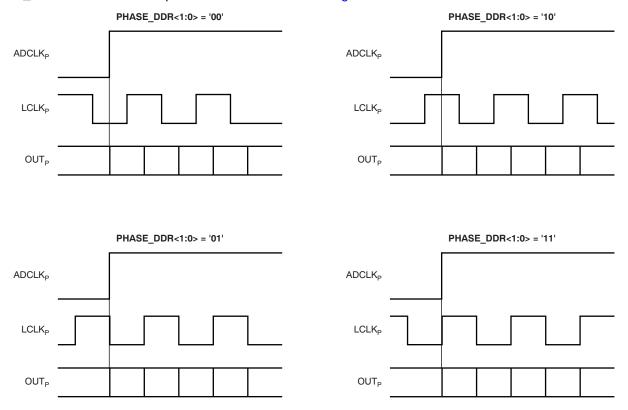

|                   | 1   |     |     |       |     |     |    |    |    | х  | х  |    |    |    |    |    | PHASE_DDR<1:0> | Controls the phase of LCLK output relative to data.                                                                        | 90 degrees                                                               |

| 45                |     |     |     |       |     |     |    |    |    |    |    |    |    |    | 0  | Х  | PAT_DESKEW     | Enables deskew pattern mode.                                                                                               | Inactive                                                                 |

| 45                |     |     |     |       |     |     |    |    |    |    |    |    |    |    | Χ  | 0  | PAT_SYNC       | Enables sync pattern mode.                                                                                                 | Inactive                                                                 |

|                   | 1   |     |     |       |     |     | 1  |    |    |    |    |    |    | Х  |    |    | BTC_MODE       | Binary two's complement format for ADC output.                                                                             | Straight offset binary                                                   |

|                   | 1   |     |     |       |     |     | 1  |    |    |    |    |    | Х  |    |    |    | MSB_FIRST      | Serialized ADC output comes out MSB-first.                                                                                 | LSB-first output                                                         |

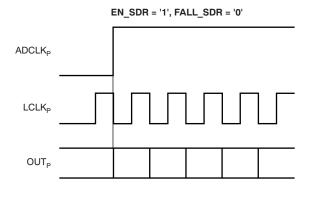

| 46                | 1   |     |     |       |     |     | 1  |    |    |    |    | х  |    |    |    |    | EN_SDR         | Enables SDR output mode (LCLK becomes a 12x input clock).                                                                  | DDR output mode                                                          |

|                   | 1   |     | х   |       |     |     | 1  |    |    |    |    | 1  |    |    |    |    | FALL_SDR       | Controls whether the LCLK rising or falling edge comes in the middle of the data window when operating in SDR output mode. | Rising edge<br>of LCLK in<br>middle of<br>data window                    |

# **SUMMARY OF FEATURES**

| FEATURES                                                                                  | DEFAULT           | SELECTION           | POWER IMPACT (relative to default) AT f <sub>S</sub> = 65MSPS                                                                                                      |

|-------------------------------------------------------------------------------------------|-------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ANALOG FEATURES                                                                           |                   |                     |                                                                                                                                                                    |

| Internal or external reference (driven on the REF <sub>T</sub> and REF <sub>B</sub> pins) | N/A               | Pin                 | Internal reference mode takes approximately 23mW more power on AVDD                                                                                                |

| External reference driven on the V <sub>CM</sub> pin                                      | Off               | Register 42         | Approximately 9mW less power on AVDD                                                                                                                               |

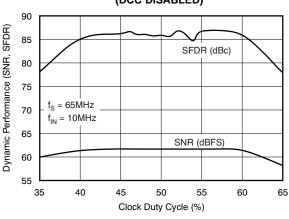

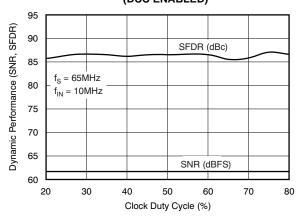

| Duty cycle correction circuit                                                             | Off               | Register 42         | Approximately 7mW more power on AVDD                                                                                                                               |

| Low-frequency noise suppression                                                           | Off               | Register 14         | With zero input to the ADC, low-frequency noise suppression causes digital switching at $f_{\rm S}/2$ , thereby increasing LVDD power by approximately 7mW/channel |

| Single-ended or differential clock                                                        | Single-ended      | Register 42         | Differential clock mode takes approximately 7mW more power on AVDD                                                                                                 |

| Power-down mode                                                                           | Off               | Pin and register 0F | Refer to the <i>Power-Down Modes</i> section in the Electrical Characteristics table                                                                               |

| DIGITAL FEATURES                                                                          |                   |                     |                                                                                                                                                                    |

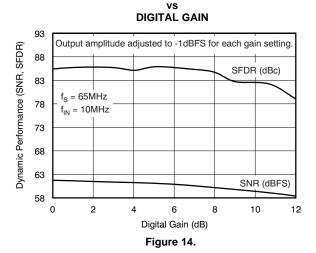

| Programmable digital gain (0dB to 12dB)                                                   | 0dB               | Registers 2A and 2B | No difference                                                                                                                                                      |

| Straight offset or BTC output                                                             | Straight offset   | Register 46         | No difference                                                                                                                                                      |

| Swap polarity of analog input pins                                                        | Off               | Register 24         | No difference                                                                                                                                                      |

| LVDS OUTPUT PHYSICAL LAYER                                                                |                   |                     |                                                                                                                                                                    |

| LVDS internal termination                                                                 | Off               | Register 12         | Approximately 7mW more power on AVDD                                                                                                                               |

| LVDS current programmability                                                              | 3.5mA             | Register 11         | As per LVDS clock and data buffer current setting                                                                                                                  |

| LVDS OUTPUT TIMING                                                                        |                   |                     |                                                                                                                                                                    |

| LSB- or MSB-first output                                                                  | LSB-first         | Register 46         | No difference                                                                                                                                                      |

| DDR or SDR output                                                                         | DDR               | Register 46         | SDR mode takes approximately 2mW more power on LVDD (at f <sub>S</sub> = 30MSPS)                                                                                   |

| LCLK phase relative to data output                                                        | Refer to Figure 1 | Register 42         | No difference                                                                                                                                                      |

### **DESCRIPTION OF SERIAL REGISTERS**

### SOFTWARE RESET

| ADDRESS<br>IN HEX | D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | NAME |

|-------------------|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|------|

| 00                |     |     |     |     |     |     |    |    |    |    |    |    |    |    |    | Х  | RST  |

Software reset is applied when the RST bit is set to '1'; setting this bit resets all internal registers and self-clears to '0'.

# **POWER-DOWN MODES**

| ADDRESS<br>IN HEX | D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | NAME         |

|-------------------|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|--------------|

|                   |     |     |     |     |     |     |    |    | Х  | Х  | Х  | Х  | Х  | Х  | Χ  | Х  | PDN_CH<8:1>  |

| 0F                |     |     |     |     |     |     |    | Х  |    |    |    |    |    |    |    |    | PDN_PARTIAL  |

| UF                |     |     |     |     |     | 0   | Х  |    |    |    |    |    |    |    |    |    | PDN_COMPLETE |

|                   |     |     |     |     |     | X   | 0  |    |    |    |    |    |    |    |    |    | PDN_PIN_CFG  |

Each of the eight channels can be individually powered down. PDN\_CH<N> controls the power-down mode for the ADC channel <N>.

In addition to channel-specific power-down, the ADS5287 also has two global power-down modes—partial power-down mode and complete power-down mode. Partial power-down mode partially powers down the chip; recovery from this mode is much quicker, provided that the clock has been running for at least 50µs before exiting this mode. Complete power-down mode, on the other hand, completely powers down the chip, and involves a much longer recovery time.

In addition to programming the device for either of these two power-down modes (through either the PDN\_PARTIAL or PDN\_COMPLETE bits, respectively), the PD pin itself can be configured as either a partial power-down pin or a complete power-down pin control. For example, if PDN\_PIN\_CFG = 0 (default), when the PD pin is high, the device enters complete power-down mode. However, if PDN\_PIN\_CFG = 1, when the PD pin is high, the device enters partial power-down mode.

# LVDS DRIVE PROGRAMMABILITY

| ADDRESS<br>IN HEX | D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | NAME             |

|-------------------|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|------------------|

|                   |     |     |     |     |     |     |    |    |    |    |    |    |    | Х  | Х  | Х  | ILVDS_LCLK<2:0>  |

| 11                |     |     |     |     |     |     |    |    |    | Х  | Х  | Х  |    |    |    |    | ILVDS_FRAME<2:0> |

|                   |     |     |     |     |     | Х   | Χ  | Χ  |    |    |    |    |    |    |    |    | ILVDS_DAT<2:0>   |

The LVDS drive strength of the bit clock (LCLK<sub>P</sub> or LCLK<sub>N</sub>) and the frame clock (ADCLK<sub>P</sub> or ADCLK<sub>N</sub>) can be individually programmed. The LVDS drive strengths of all the data outputs  $OUT_P$  and  $OUT_N$  can also be programmed to the same value.

All three drive strengths (bit clock, frame clock, and data) are programmed using sets of three bits. Table 4 shows an example of how the drive strength of the bit clock is programmed (the method is similar for the frame clock and data drive strengths).

Table 4. Bit Clock Drive Strength<sup>(1)</sup>

| ILVDS_LCLK<2> | ILVDS_LCLK<1> | ILVDS_LCLK<0> | LVDS DRIVE STRENGTH FOR LCLK <sub>P</sub> AND LCLK <sub>N</sub> |

|---------------|---------------|---------------|-----------------------------------------------------------------|

| 0             | 0             | 0             | 3.5mA (default)                                                 |

| 0             | 0             | 1             | 2.5mA                                                           |