SBAS273 - DECEMBER 2002

# Low-Power, 24-Bit ANALOG-TO-DIGITAL CONVERTER

### FEATURES

- 20-BIT EFFECTIVE RESOLUTION

- CURRENT CONSUMPTION: 90μA

- ANALOG SUPPLY: 2.5V to 5.25V

- DIGITAL SUPPLY: 1.8V to 3.6V

- ±5V DIFFERENTIAL INPUT RANGE

- 0.0002% INL (TYP), 0.0008% INL (MAX)

- SIMPLE 2-WIRE SERIAL INTERFACE

- SIMULTANEOUS 50Hz AND 60Hz REJECTION

- SINGLE CONVERSIONS WITH SLEEP MODE

- SINGLE-CYCLE SETTLING

- SELF-CALIBRATION

- WELL-SUITED FOR MULTICHANNEL SYSTEMS

- EASILY CONNECTS TO THE MSP430

### APPLICATIONS

- HAND-HELD INSTRUMENTATION

- PORTABLE MEDICAL EQUIPMENT

- INDUSTRIAL PROCESS CONTROL

- WEIGH SCALES

## DESCRIPTION

The ADS1244 is a 24-bit, delta-sigma Analog-to-Digital (A/D) converter. It offers excellent performance and very low power in an MSOP-10 package and is well suited for demanding high-resolution measurements, especially in portable and other space- and power-constrained systems.

A 3rd-order delta-sigma modulator and digital filter form the basis of the A/D converter. The analog modulator has a  $\pm$ 5V differential input range. The digital filter rejects both 50Hz and 60Hz signals, completely settles in one cycle, and outputs data at 15 samples per second.

A simple, 2-wire serial interface provides all the necessary control. Data retrieval, self-calibration, and Sleep Mode are handled with a few simple waveforms. When only single conversions are needed, the ADS1244 can be shut down (Sleep Mode) while idle between measurements to dramatically reduce the overall power dissipation. Multiple ADS1244s can be connected together to create a synchronously sampling multichannel measurement system. The ADS1244 is designed to easily connect to microcontrollers, such as the MSP430.

The ADS1244 supports 2.5V to 5.25V analog supplies and 1.8V to 3.6V digital supplies. Power is typically less than 270 $\mu$ W in normal operation and less than 1 $\mu$ W during Sleep Mode.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

#### ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

| AVDD to GND                       | 0.3V to +6V         |

|-----------------------------------|---------------------|

| DVDD to GND                       | 0.3V to +3.6V       |

| Input Current                     | 100mA, Momentary    |

| Input Current                     | 10mA, Continuous    |

| Analog Input Voltage to GND       | 0.5V to AVDD + 0.5V |

| Digital Input Voltage to GND      | 0.3V to DVDD + 0.3V |

| Digital Output Voltage to GND     | 0.3V to DVDD + 0.3V |

| Maximum Junction Temperature      | +150°C              |

| Operating Temperature Range       | 40°C to +85°C       |

| Storage Temperature Range         | 60°C to +150°C      |

| Lead Temperature (soldering, 10s) | +300°C              |

NOTE: (1) Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. Exposure to absolute maximum conditions for extended periods may affect device reliability.

### DEMO BOARD ORDERING INFORMATION

| PRODUCT     | DESCRIPTION               |

|-------------|---------------------------|

| ADS1244-EVM | ADS1244 Evaluation Module |

# ELECTROSTATIC DISCHARGE SENSITIVITY

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

| PRODUCT | PACKAGE-LEAD | PACKAGE<br>DESIGNATOR <sup>(1)</sup> | SPECIFIED<br>TEMPERATURE<br>RANGE | PACKAGE<br>MARKING | ORDERING<br>NUMBER | TRANSPORT<br>MEDIA, QUANTITY |

|---------|--------------|--------------------------------------|-----------------------------------|--------------------|--------------------|------------------------------|

| ADS1244 | MSOP-10      | DGS                                  | –40°C to +85°C                    | BHG                | ADS1244IDGST       | Tape and Reel, 250           |

| "       | "            | "                                    | "                                 | "                  | ADS1244IDGSR       | Tape and Reel, 2500          |

NOTE: (1) For the most current specifications and package information, refer to our web site at www.ti.com.

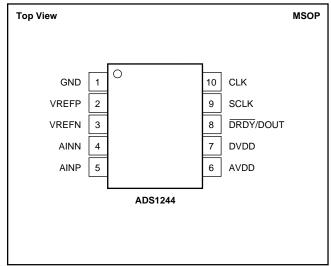

### **PIN CONFIGURATION**

#### **PIN DESCRIPTIONS**

| PIN<br>NUMBER | NAME          | DESCRIPTION                                                                                                                                          |

|---------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1             | GND           | Analog and Digital Ground                                                                                                                            |

| 2             | VREFP         | Positive Reference Input                                                                                                                             |

| 3             | VREFN         | Negative Reference Input                                                                                                                             |

| 4             | AINN          | Negative Analog Input                                                                                                                                |

| 5             | AINP          | Positive Analog Input                                                                                                                                |

| 6             | AVDD          | Analog Power Supply, 2.5V to 5.25V                                                                                                                   |

| 7             | DVDD          | Digital Power Supply, 1.8V to 3.6V                                                                                                                   |

| 8             | DRDY/<br>DOUT | Dual-Purpose Output:<br>Data Ready: Indicates valid data by going LOW.<br>Data Output: Outputs data, MSB first, on the first<br>rising edge of SCLK. |

| 9             | SCLK          | Serial Clock Input: Clocks out data on the rising<br>edge. Used to initiate calibration and Sleep Mode,<br>see text for more details.                |

| 10            | CLK           | System Clock Input: Typically 2.4576MHz                                                                                                              |

# **ELECTRICAL CHARACTERISTICS**

All specifications –40°C to +85°C, AVDD = 5V, DVDD = +3V,  $f_{CLK}$  = 2.4576MHz, and  $V_{REF}$  = 2.5V, unless otherwise specified.

|                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                         | ADS1244                         |                                                   |                                                  |                                                                                                                          |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|---------------------------------------------------|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--|

| PARAMETER                                                                                                                                                                                                                                                                                                                                                                     | CONDITIONS                                                                                                                                                                                                                                              | MIN TYP                         |                                                   | MAX                                              | UNITS                                                                                                                    |  |

| ANALOG INPUT<br>Full-Scale Input Voltage Range<br>Absolute Input Range<br>Differential Input Impedance                                                                                                                                                                                                                                                                        | AINP – AINN<br>AINP, AINN with Respect to GND<br>$f_{CLK} = 2.4576MHz$                                                                                                                                                                                  | GND – 0.1                       | ±2V <sub>REF</sub><br>5                           | AVDD + 0.1                                       | ν<br>ν<br>ΜΩ                                                                                                             |  |

| SYSTEM PERFORMANCE<br>Resolution<br>Data Rate<br>Integral Nonlinearity (INL)<br>Offset Error<br>Offset Error Drift <sup>(3)</sup><br>Gain Error<br>Gain Error Drift <sup>(3)</sup><br>Common-Mode Rejection                                                                                                                                                                   | No Missing Codes<br>$f_{CLK} = 2.4576MHz$<br>Differential Input Signal, End Point Fit<br>at DC<br>$f_{CM}^{(4)} = 50 \pm 1Hz$ , $f_{CLK} = 2.4576MHz$<br>$f_{CM} = 60 \pm 1Hz$ , $f_{CLK} = 2.4576MHz$<br>$f_{CM} = 50 \pm 1Hz$ , $f_{CLK} = 2.4576MHz$ | 24<br>90<br>100<br>100<br>60    | 15<br>±0.0002<br>1<br>0.01<br>0.005<br>0.5<br>130 | ±0.0008<br>10<br>0.02                            | Bits<br>sps <sup>(1)</sup><br>% FSR <sup>(2)</sup><br>ppm of FSR<br>ppm of FSR/°C<br>%<br>ppm/°C<br>dB<br>dB<br>dB<br>dB |  |

| Normal-Mode Rejection<br>Input Referred Noise<br>Analog Power-Supply Rejection<br>Digital Power-Supply Rejection                                                                                                                                                                                                                                                              | $ \begin{split} f_{SIG}^{(5)} &= 50 \pm 1 \text{Hz}, \ f_{CLK} = 2.4576 \text{MHz} \\ f_{SIG} &= 60 \pm 1 \text{Hz}, \ f_{CLK} = 2.4576 \text{MHz} \\ \text{at DC, } \Delta \text{AVDD} = 5\% \\ \text{at DC, } \Delta \text{DVDD} = 5\% \end{split} $  | 60<br>70                        | 1<br>105<br>100                                   |                                                  | dB<br>dB<br>ppm of FSR, rms<br>dB<br>dB                                                                                  |  |

| VOLTAGE REFERENCE INPUT<br>Reference Input Voltage (V <sub>REF</sub> )<br>Negative Reference Input (VREFN)<br>Positive Reference Input (VREFP)<br>Voltage Reference Impedance                                                                                                                                                                                                 | V <sub>REF</sub> ≡ VREFP – VREFN<br>f <sub>CLK</sub> = 2.4576MHz                                                                                                                                                                                        | 0.5<br>GND – 0.1<br>VREFN + 0.5 | 2.5                                               | AVDD <sup>(6)</sup><br>VREFP – 0.5<br>AVDD + 0.1 | ν<br>ν<br>ν<br>ΜΩ                                                                                                        |  |

| $\begin{array}{c} \textbf{DIGITAL INPUT/OUTPUT} \\ \text{Logic Levels} \\ V_{\text{IH}} (\text{CLK, SCLK}) \\ V_{\text{IL}} (\text{CLK, SCLK}) \\ V_{\text{OH}} (\overline{\text{DRDY}}/\text{DOUT}) \\ V_{\text{OL}} (\overline{\text{DRDY}}/\text{DOUT}) \\ \text{Input Leakage (CLK, SCLK)} \\ \text{CLK Frequency (f_{\text{CLK}})} \\ \text{CLK Duty Cycle} \end{array}$ | I <sub>OH</sub> = 1mA<br>I <sub>OL</sub> = 1mA<br>0 < (CLK, SCLK) < DVDD                                                                                                                                                                                | 2.1<br>GND<br>2.6<br>30         |                                                   | 5.25<br>0.9<br>0.4<br>±10<br>6<br>70             | V<br>V<br>V<br>μA<br>MHz<br>%                                                                                            |  |

| POWER SUPPLY<br>AVDD<br>DVDD<br>AVDD Current<br>DVDD Current                                                                                                                                                                                                                                                                                                                  | Sleep Mode<br>AVDD = 3V<br>AVDD = 5V<br>Sleep Mode, CLK Stopped<br>Sleep Mode, 2.4576MHz CLK Running<br>DVDD = 3V                                                                                                                                       | 2.5<br>1.8                      | 0.1<br>85<br>90<br>0.1<br>1.3<br>4.5              | 5.25<br>3.6<br>1<br>150<br>5<br>10               | V<br>V<br>μΑ<br>μΑ<br>μΑ<br>μΑ<br>μΑ                                                                                     |  |

| Total Power Dissipation                                                                                                                                                                                                                                                                                                                                                       | AVDD = DVDD = 3V                                                                                                                                                                                                                                        |                                 | 270                                               | 10                                               | μΑ<br>μW                                                                                                                 |  |

NOTES: (1) sps = Samples Per Second. (2) FSR = Full-Scale Range =  $4V_{REF}$ . (3) Recalibration can reduce these errors to the level of the noise. (4)  $f_{CM}$  is the frequency of the common-mode input. (5)  $f_{SIG}$  is the frequency of the input signal. (6) It will not be possible to reach the digital output full-scale code when  $V_{REF}$  > AVDD/2.

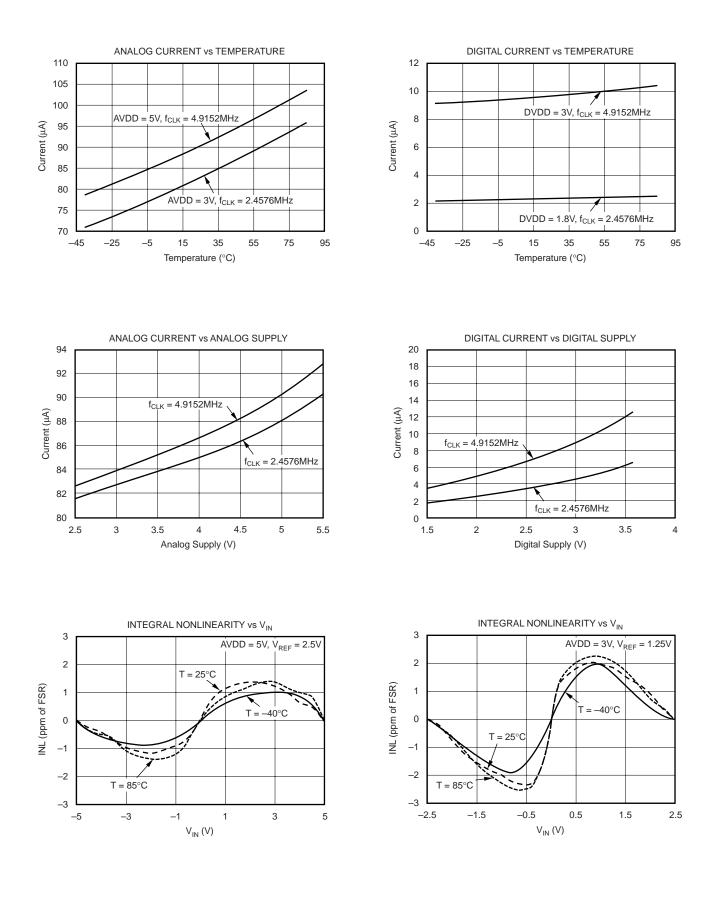

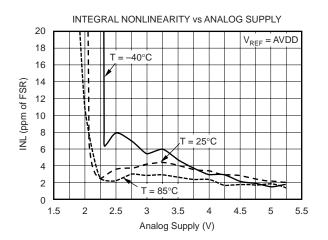

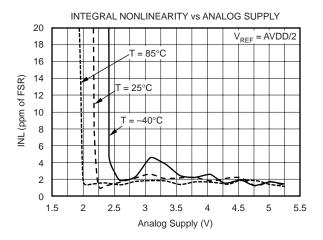

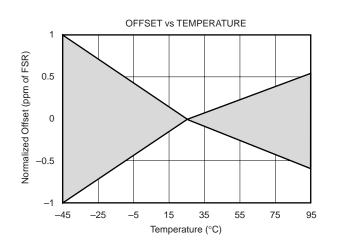

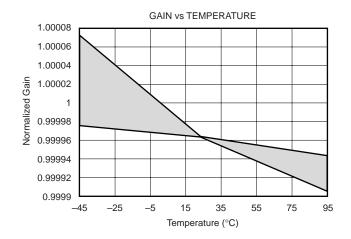

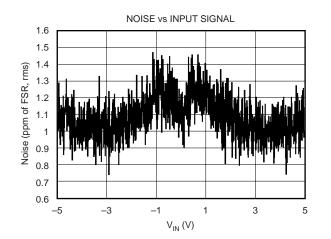

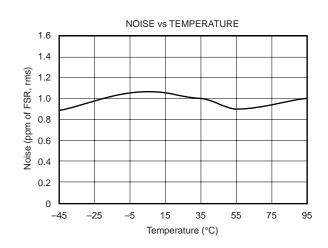

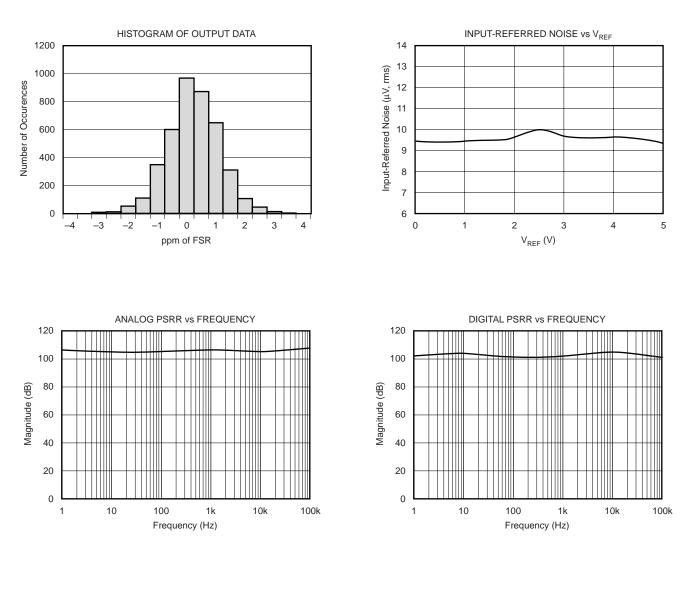

# **TYPICAL CHARACTERISTICS**

At  $T_A$  = +25°C, AVDD = +5V, DVDD = +3V,  $f_{CLK}$  = 2.4576MHz, and  $V_{REF}$  = +2.5V, unless otherwise specified.

# **TYPICAL CHARACTERISTICS (Cont.)**

At T<sub>A</sub> = +25°C, AVDD = +5V, DVDD = +3V, f<sub>CLK</sub> = 2.4576MHz, and V<sub>REF</sub> = +2.5V, unless otherwise specified.

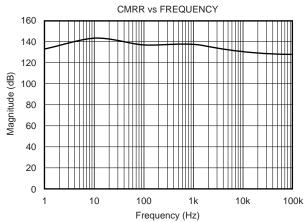

# **TYPICAL CHARACTERISTICS (Cont.)**

At T<sub>A</sub> = +25°C, AVDD = +5V, DVDD = +3V, f<sub>CLK</sub> = 2.4576MHz, and V<sub>REF</sub> = +2.5V, unless otherwise specified.

## **OVERVIEW**

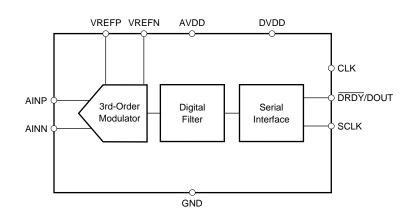

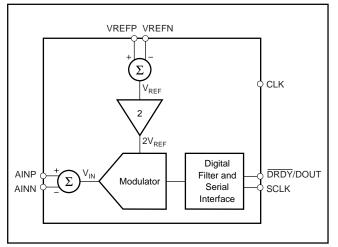

The ADS1244 is an A/D converter comprised of a 3rd-order modulator followed by a digital filter. The modulator measures the differential input signal  $V_{IN} = (AINP - AINN)$  against the differential reference  $V_{REF} = (VREFP - VREFN)$ . Figure 1 shows a conceptual diagram. The differential reference is scaled internally so that the full-scale input range is  $\pm 2V_{REF}$ . The digital filter receives the modulator's signal and provides a low-noise digital output. The filter also sets the frequency response of the converter and provides 50Hz and 60Hz rejection while settling in a single conversion cycle. A 2-wire serial interface indicates conversion completion and provides the user with the output data.

FIGURE 1. Conceptual Diagram of the ADS1244.

#### ANALOG INPUTS (AINP, AINN)

The input signal to be measured is applied to the input pins AINP and AINN. The ADS1244 accepts differential input signals, but can also measure unipolar signals. When measuring unipolar (or "single-ended" signals) with respect to ground, connect the negative input (AINN) to ground and connect the input signal to the positive input (AINP). Note that when the ADS1244 is used this way, only half of the converter's full-scale range is used since only positive digital output codes will be produced.

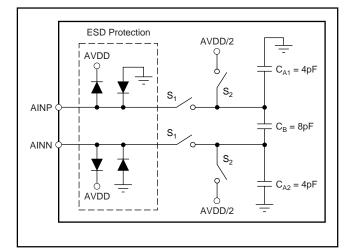

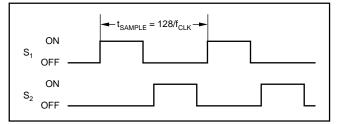

The ADS1244 measures the input signal using internal capacitors that are continuously charged and discharged. Figure 2 shows a simplified schematic of the ADS1244's input circuitry with Figure 3 showing the ON/OFF timings of the switches. S<sub>1</sub> switches close during the input sampling phase. With S<sub>1</sub> closed, C<sub>A1</sub> charges to AINP, C<sub>A2</sub> charges to AINN, and C<sub>B</sub> charges to (AINP – AINN). For the discharge phase, S<sub>1</sub> opens first and then S<sub>2</sub> closes. C<sub>A1</sub> and C<sub>A2</sub> discharge to approximately AVDD/2 and C<sub>B</sub> discharges to 0V. This 2-phase sample/discharge cycle repeats with a frequency of f<sub>CLK</sub>/128 (19.2kHz for f<sub>CLK</sub> = 2.4576MHz).

FIGURE 2. Simplified Input Structure.

FIGURE 3.  $S_1$  and  $S_2$  Switch Timing for Figure 1.

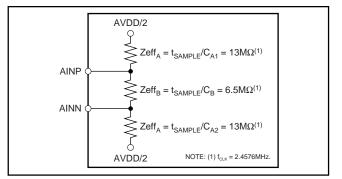

The constant charging of the input capacitors presents a load on the inputs that can be represented by effective impedances. Figure 4 shows the input circuitry with the capacitors and switches of Figure 2 replaced by their effective impedances. These impedances scale inversely with f<sub>CLK</sub> frequency. For example, if f<sub>CLK</sub>'s frequency is reduced by a factor of 2, the impedances will double.

FIGURE 4. Effective Analog Input Impedances.

ESD diodes protect the inputs. To keep these diodes from turning on, make sure the voltages on the input pins do not go below GND by more than 100mV, and likewise do not exceed AVDD by 100mV: GND - 100mV < (AINP, AINN) < AVDD + 100mV.

#### **VOLTAGE REFERENCE INPUTS (VREFP, VREFN)**

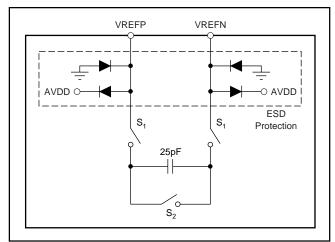

The voltage reference used by the modulator is generated from the voltage difference between VREFP and VREFN:  $V_{REF} = VREFP - VREFN$ . The reference inputs use a structure similar to that of the analog inputs. A simplified diagram of the circuitry on the reference inputs is shown in Figure 5. The switches and capacitors can be modeled with an effective

| impedance = | $\left(\frac{t_{SAMPLE}}{2}\right)$ | $)/25pF = 1M\Omega$ for $f_{CLK} = 2.4576MHz$ . |

|-------------|-------------------------------------|-------------------------------------------------|

|-------------|-------------------------------------|-------------------------------------------------|

FIGURE 5. Simplified Reference Input Circuitry.

ESD diodes protect the reference inputs. To prevent these diodes from turning on, make sure the voltages on the reference pins do not go below GND by more than 100mV, and likewise do not exceed AVDD by 100mV: GND - 100mV < (VREFP, VREFN) < AVDD + 100mV.

$V_{\text{REF}}$  is typically AVDD/2, but it can be raised as high as AVDD. When  $V_{\text{REF}}$  exceeds AVDD/2, it will not be possible to reach the full-scale digital output value corresponding to  $\pm 2V_{\text{REF}}$  since this would require the analog inputs to exceed the power supplies. For example, if  $V_{\text{REF}} = \text{AVDD} = 5\text{V}$ , the positive full-scale signal is 10V. The maximum positive input signal that can be supplied before the ESD diodes begin to turn on is when AINP = 5.1V and AINN =  $-0.1V \rightarrow V_{\text{IN}} = 5.2V$ . Therefore, it will not be possible to reach the positive (or negative) full-scale readings in this configuration. The digital output codes will be limited to approximately one half of the entire range.

For best performance, bypass the voltage reference inputs with a  $0.1\mu F$  capacitor between VREFP and VREFN. Place the capacitor as close as possible to the pins.

#### **CLOCK INPUT (CLK)**

This digital input supplies the system clock to the ADS1244. The recommended CLK frequency is 2.4576MHz. This places the notches of the digital filter at 50Hz and 60Hz and sets the data rate at 15SPS. The CLK frequency can be increased to speed up the data rate, but the frequency notches will move in frequency proportionally. CLK must be left running during normal operation. It may be turned off during Sleep Mode to save power, but this is not required. The CLK input may be driven with 5V logic, regardless of the DVDD or AVDD voltage.

Minimize the overshoot and undershoot on CLK for the best analog performance. A small resistor in series with CLK ( $10\Omega$ to  $100\Omega$ ) can often help. CLK can be generated from a number of sources including stand-alone crystal oscillators and microcontrollers. The MSP430, an ultra low power microcontroller, is especially well suited for this task. Using the MSP430's FLL clock generator available on the 4xx family, it's easy to produce a 2.4576MHz clock from a 32.768kHz crystal.

#### DATA READY/DATA OUTPUT (DRDY/DOUT)

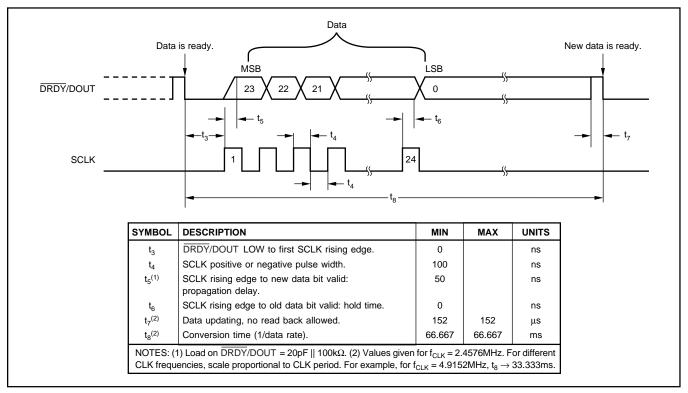

This digital output pin serves two purposes. It indicates when new data is ready by going LOW. Afterwards, on the first rising edge of SCLK, the DRDY/DOUT pin changes function and begins outputting the conversion data, MSB first. Data is shifted out on each subsequent SCLK rising edge. After all 24 bits have been retrieved, the pin can be forced HIGH with an additional SCLK. It will then stay HIGH until new data is ready. This is useful when polling on the status of DRDY/DOUT to determine when to begin data retrieval.

#### SERIAL CLOCK INPUT (SCLK)

This digital input shifts serial data out with each rising edge. As with CLK, this input may be driven with 5V logic regardless of the DVDD or AVDD voltage. There is hysteresis built into this input, but care should still be taken to ensure a clean signal. Glitches or slow rising signals can cause unwanted additional shifting. For this reason, it is best to make sure the rise-and-fall times of SCLK are less than 50ns.

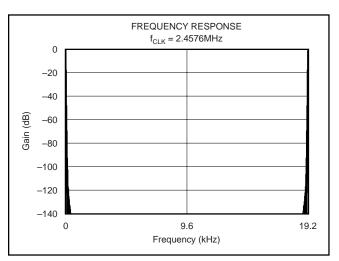

#### FREQUENCY RESPONSE

The ADS1244's frequency response for  $f_{CLK} = 2.4576$ MHz is shown in Figure 6. The frequency response repeats at multiples of 19.2kHz. The overall response is that of a low-pass filter with a –3dB cutoff frequency of 13.7Hz. As can be seen, the ADS1244 does a good job attenuating out to 19kHz. For the best resolution, limit the input bandwidth to below this value to keep higher frequency noise from affecting performance. Often a simple RC filter on the ADS1244's analog inputs is all that is needed.

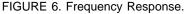

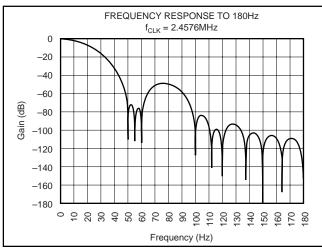

To help see the response at lower frequencies, Figure 7 illustrates the response out to 180Hz. Notice that both 50Hz and 60Hz signals are rejected. This feature is very useful for eliminating power line cycle interference during measurements. Figure 8 shows the ADS1244's response around these frequencies.

FIGURE 7. Frequency Response to 180Hz.

FIGURE 8. Frequency Response Near 50Hz and 60Hz.

The ADS1244's data rate and frequency response scale directly with CLK frequency. For example, if  $f_{CLK}$  increases from 2.4576MHz to 4.9152MHz, the data rate increases from 15sps to 30sps while the notches in the response at 50Hz and 60Hz move out to 100Hz and 120Hz.

#### SETTLING TIME

The ADS1244 has single-cycle settling. That is, the output data is fully settled after a single conversion—there is no need to wait for additional conversions before retrieving the data when there is a change on the analog inputs.

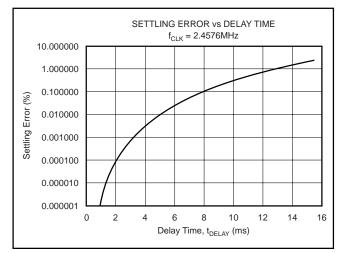

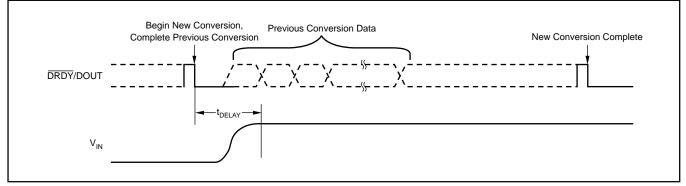

In order to realize single-cycle settling, synchronize changes on the analog inputs to the conversion beginning, which is indicated by the falling edge of  $\overline{DRDY}/DOUT$ . For example, when using a multiplexer in front of the ADS1244, change the multiplexer's inputs when  $\overline{DRDY}/DOUT$  goes LOW. Increasing the time between the conversion beginning and the change on the analog inputs ( $t_{DELAY}$ ) will result in a settling error in the conversion data, as shown in Figure 9. The settling error versus delay time is shown in Figure 10. If the input change is delayed to the point where the settling error is too high, simply ignore the first data result and wait for the second conversion which will be fully-settled.

FIGURE 10. Settling Error vs Delay Time.

FIGURE 9. Analog Input Change Timing.

#### **POWER-UP**

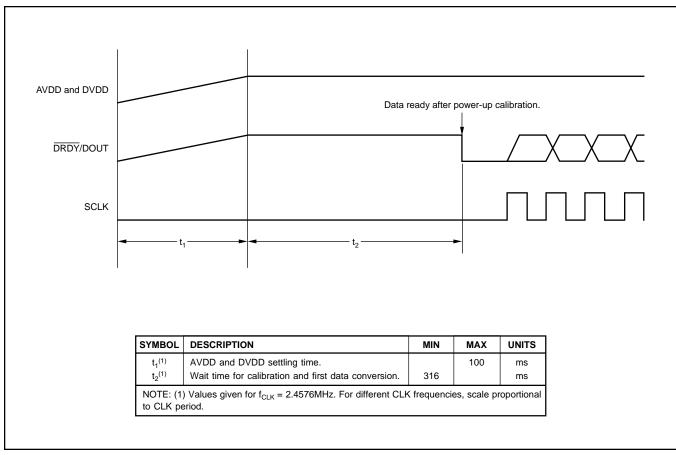

Self-calibration is performed at power-up to minimize offset and gain errors. In order for the self-calibration at power-up to work properly, make sure that both AVDD and DVDD increase monotonically and are settled by  $t_1$ , as shown in Figure 11. SCLK must be held LOW during this time. Once calibration is complete,  $\overline{DRDY}/DOUT$  will go LOW indicating data is ready for retrieval. The time required before the first data is ready ( $t_6$ ) depends on how fast AVDD and DVDD ramp to their final value ( $t_1$ ). For most ramp rates,  $t_1 + t_2 \approx 350$ ms ( $f_{CLK} = 2.4576$ MHz). If the system environment is not stable during power-up (the temperature is varying or the supply voltages are moving around), it is recommended that a self-calibration be issued after everything is stable.

#### DATA FORMAT

The ADS1244 outputs 24 bits of data in Binary Two's Complement format. The Least Significant Bit (LSB) has a weight of  $(2V_{REF})/(2^{23} - 1)$ . A positive full-scale input pro-

duces an output code of  $7FFFF_H$  and the negative full-scale input produces an output code of  $800000_H$ . The output clips at these codes for signals exceeding full-scale. Table I summarizes the ideal output codes for different input signals.

| INPUT SIGNAL V <sub>IN</sub> (AINP – AINN)                         | IDEAL OUTPUT CODE <sup>(1)</sup> |  |  |  |

|--------------------------------------------------------------------|----------------------------------|--|--|--|

| $\geq$ +2V <sub>REF</sub>                                          | 7FFFF <sub>H</sub>               |  |  |  |

| $\frac{+2V_{REF}}{2^{23}-1}$                                       | 000001 <sub>H</sub>              |  |  |  |

| 0                                                                  | 000000 <sub>H</sub>              |  |  |  |

| $\frac{-2V_{REF}}{2^{23}-1}$                                       | FFFFF <sub>H</sub>               |  |  |  |

| $\leq -2V_{REF}\left(\frac{2^{23}}{2^{23}-1}\right)$               | 800000 <sub>H</sub>              |  |  |  |

| NOTE: (1) Excludes effects of noise, INL, offset, and gain errors. |                                  |  |  |  |

TABLE I. Ideal Output Code versus Input Signal.

FIGURE 11. Power-Up Timing.

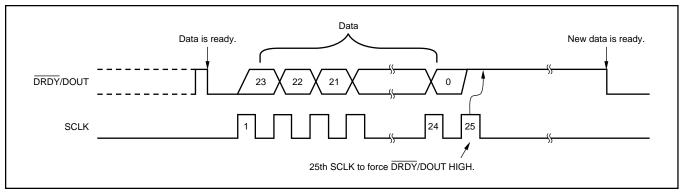

#### DATA RETRIEVAL

The ADS1244 continuously converts the analog input signal. To retrieve data, wait until  $\overline{DRDY}/DOUT$  goes LOW, as shown in Figure 12. After this occurs, begin shifting out the data by applying SCLKs. Data is shifted out Most Significant Bit (MSB) first. It is not required to shift out all the 24 bits of data, but the data must be retrieved before the new data is updated (see t<sub>3</sub>) or else it will be overwritten. Avoid data

retrieval during the update period.  $\overline{DRDY}/DOUT$  will remain at the state of the last bit shifted out until it is taken HIGH (see  $t_7$ ), indicating that new data is being updated.

To avoid having  $\overline{DRDY}/DOUT$  remain in the state of the last bit, shift a 25th SCLK to force  $\overline{DRDY}/DOUT$  HIGH, see Figure 13. This technique is useful when a host controlling the ADS1244 is polling  $\overline{DRDY}/DOUT$  to determine when data is ready.

FIGURE 12. Data Retrieval Timing.

FIGURE 13. Data Retrieval with DRDY/DOUT Forced HIGH Afterwards.

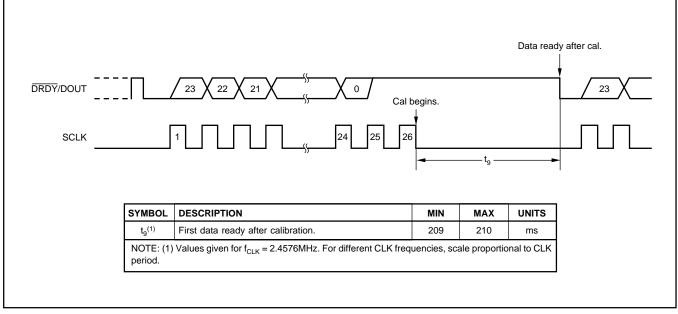

#### **SELF-CALIBRATION**

The user can initiate self-calibration at any time, though in many applications the ADS1244's drift performance is good enough that the self-calibration performing automatically at power-up is all that is needed. To initiate a self-calibration, apply at least two additional SCLKs after retrieving 24 bits of data. Figure 14 shows the timing pattern. The 25th SCLK will send  $\overline{DRDY}/DOUT$  HIGH. The falling edge of the 26th SCLK will begin the calibration cycle. Additional SCLK pulses may be sent after the 26th SCLK, but try to minimize activity on SCLK during calibration for best results.

When the calibration is complete,  $\overline{DRDY}/DOUT$  will go LOW indicating that new data is ready. There is no need to alter the analog input signal applied to the ADS1244 during calibration, the inputs pins are disconnected within the A/D converter and the appropriate signals applied internally automatically. The first conversion after a calibration is fully settled and valid for use. The time required for a calibration depends on two independent signals: the falling edge of SCLK and an internal clock derived from CLK. Variations in the internal calibration values will change the time required for calibration (t<sub>9</sub>) within the range given by the MIN/MAX specs. t<sub>12</sub> and t<sub>13</sub> described in the next section are affected likewise.

FIGURE 14. Self-Calibration Timing.

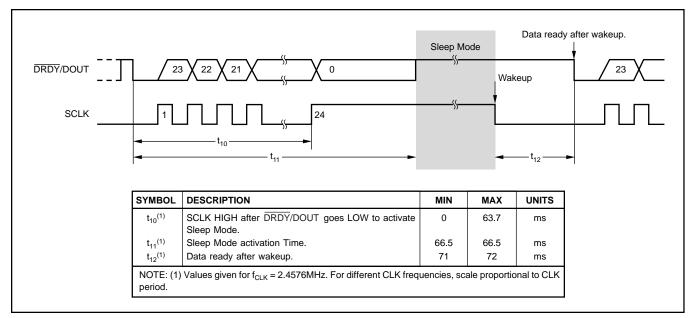

#### SLEEP MODE

Sleep Mode dramatically reduces power consumption (typically < 1 $\mu$ W with CLK stopped) by shutting down all of the active circuitry. To enter Sleep Mode, simply hold SCLK HIGH after DRDY/DOUT goes LOW, as shown in Figure 15. Sleep Mode can be initiated at any time during read back; it is not necessary to retrieve all 24 bits of data beforehand. Once t<sub>11</sub> has passed with SCLK held HIGH, Sleep Mode will activate. DRDY/DOUT stays HIGH once Sleep Mode begins. SCLK must remain HIGH to stay in Sleep Mode. To exit Sleep Mode ("wakeup"), set SCLK LOW. The first data after exiting Sleep Mode, but doing so will further reduce the digital supply current.

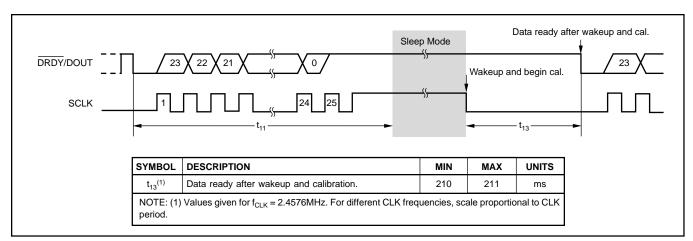

#### Sleep Mode With Self-Calibration

Self-calibration can be set to run immediately after exiting Sleep Mode. This is useful when the ADS1244 is put in Sleep Mode for long periods of time and self-calibration is desired afterwards to compensate for temperature or supply voltage changes. To force a self-calibration with Sleep Mode, shift 25 bits out before taking SCLK HIGH to enter Sleep Mode. Self-calibration will then begin after wakeup. Figure 16 shows the appropriate timing. Note the extra time needed after wakeup for calibration before data is ready. The first data after Sleep Mode with self-calibration is fully-settled and can be used.

#### SINGLE CONVERSIONS

When only single conversions are needed, Sleep Mode can be used to start and stop the ADS1244. To make a single conversion, first enter the Sleep Mode holding SCLK HIGH. Now, when ready to start the conversion, take SCLK LOW. The ADS1244 will wake up and begin the conversion. Wait for  $\overline{DRDY}/DOUT$  to go LOW, and then retrieve the data. Afterwards, take SCLK HIGH to stop the ADS1244 from converting and re-enter Sleep Mode. Continue to hold SCLK HIGH until ready to start the next conversion. Operating in this fashion greatly reduces power consumption since the ADS1244 is shut down while idle between conversions. Selfcalibrations can be performed prior to the start of the single conversions by using the waveform shown in Figure 16.

FIGURE 15. Sleep Mode Timing; Can be Used for Single Conversions.

FIGURE 16. Sleep Mode with Self-Calibration on Wakeup Timing; Can be Used for Single Conversions.

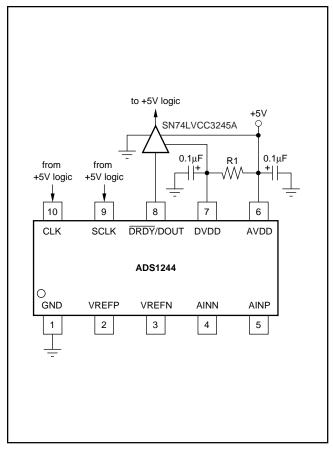

#### SINGLE-SUPPLY OPERATION

It is possible to operate the ADS1244 with a single supply. For a 3V supply, simply connect AVDD and DVDD together. Figure 17 shows an example of the ADS1244 running on a single 5V supply. An external resistor, R1, is used to drop 5V supply down to a desired voltage level of DVDD. For example, if the desired DVDD supply voltage is 3V and AVDD is 5V, the value of R1 should be:

#### $\mathsf{R1} = (5\mathsf{V} - 3\mathsf{V})/4.5\mu\mathsf{A} \approx 440\mathsf{k}\Omega$

where  $4.5\mu$ A is a typical digital current consumption when DVDD = 3V (refer to the typical characteristic "Digital Current vs Digital Supply"). A buffer on DRDY/DOUT can provide level-shifting if required.

DVDD can be set to a desired voltage by choosing a proper value of R1, but keep in mind that DVDD must be set between 1.8V and 3.6V. Note that the maximum logic HIGH output of  $\overline{DRDY}/DOUT$  is equal to DVDD, but both CLK and SCLK inputs can be driven with 5V logic regardless of the DVDD or AVDD voltage. Use 0.1µF capacitors to bypass both AVDD and DVDD.

FIGURE 17. Example of the ADS1244 Running on a Single 5V Supply.

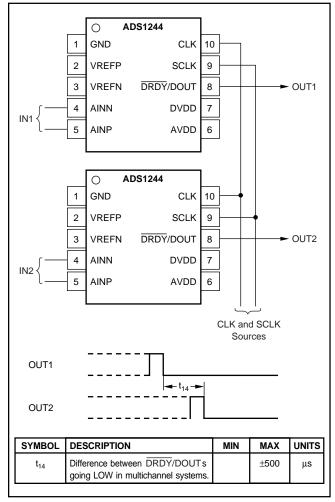

#### **MULTICHANNEL SYSTEMS**

Multiple ADS1244s can be operated in parallel to measure multiple input signals. Figure 18 shows an example of a 2-channel system. For simplicity, the supplies and reference circuitry were not included. The same CLK signal should be applied to all devices. To be able to synchronize the ADS1244s, connect the same SCLK signal to all devices as well. When ready to synchronize, place all the devices in Sleep Mode. Afterwards, "wakeup" and all the ADS1244s will be synchronized. That is, they will sample the input signals simultaneously.

The  $\overline{DRDY}/DOUT$  outputs will go LOW at approximately the same time after synchronization. The falling edges indicating that new data is ready will vary with respect to each other no more than timing specification  $t_{14}$ . This variation is due to posible differences in the ADS1244's internal calibration settings. To account for this when using multiple devices, either wait for  $t_{14}$  to pass after seeing one device's  $\overline{DRDY}/DOUT$  go LOW, or wait until all  $\overline{DRDY}/DOUT$ s have gone LOW before retrieving data.

FIGURE 18. Example of Using Multiple ADS1244s in Parallel.

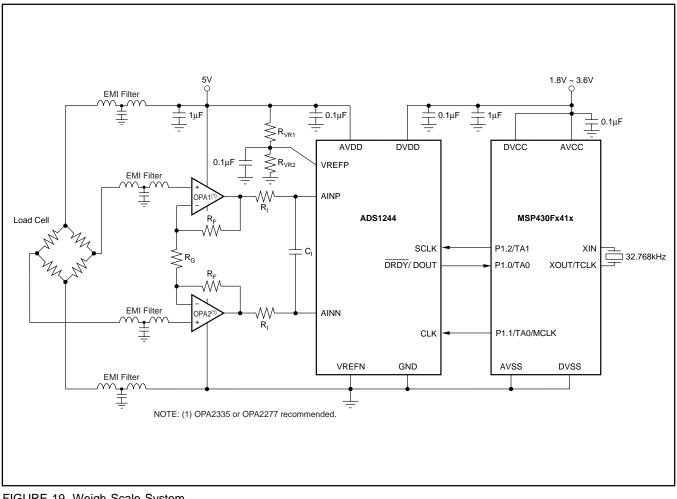

#### WEIGH SCALE SYSTEM

Figure 19 shows an example of a weigh scale system. OPA1, OPA2, R<sub>G</sub>, and R<sub>F</sub> form a differential gain stage to amplify the load cell output. The gain is equal to  $(1 + 2 R_F/R_G)$ . Depending on the load cell, the typical gain setting is from 100 to 250. R<sub>1</sub> and C<sub>1</sub> form a single-pole low-pass filter to band-limit the

differential gain stage noise and reduce mechanical vibration noise from the load cell. The cutoff frequency of the low-pass filter should be as low as possible to minimize the overall system noise. The reference voltage is typically generated by dividing down the supply voltage (R $_{VR1}$ , R $_{VR2}$ ). Use a bypass capacitor located as close to VREFP as possible.

FIGURE 19. Weigh Scale System.

## SUMMARY OF SERIAL INTERFACE WAVEFORMS

| DRDY/DOUT                                                                                                         |

|-------------------------------------------------------------------------------------------------------------------|

| DRDY/DOUT 23 22 21 % 0 % 24 25 SCLK 1 24 25 SCLK D. Data Retrieval with DRDY/DOUT Forced HIGH Afterwards.         |

| DRDY/DOUT 23 22 21 5 0 Begin cal.<br>SCLK 24 25 26 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5                              |

| Data ready.<br>DRDY/DOUT23 22 21 0 0 Vakeup and start conversion.<br>SCLK124<br>d. Sleep Mode/Single Conversions. |

| DRDY/DOUT                                                                                                         |

FIGURE 20. Summary of Serial Interface Waveforms.

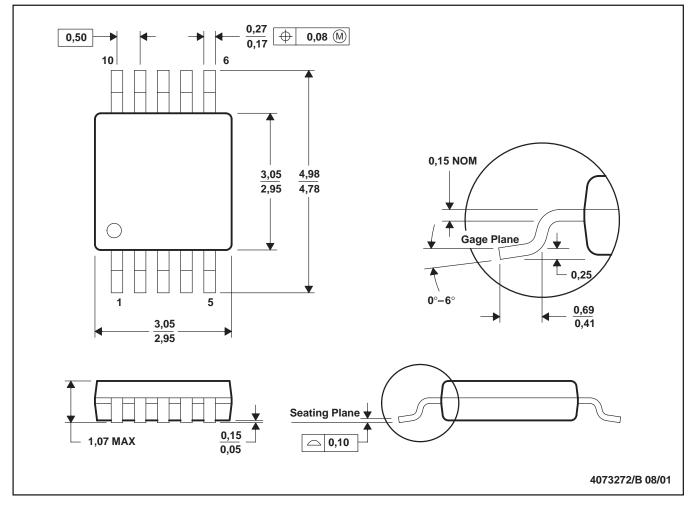

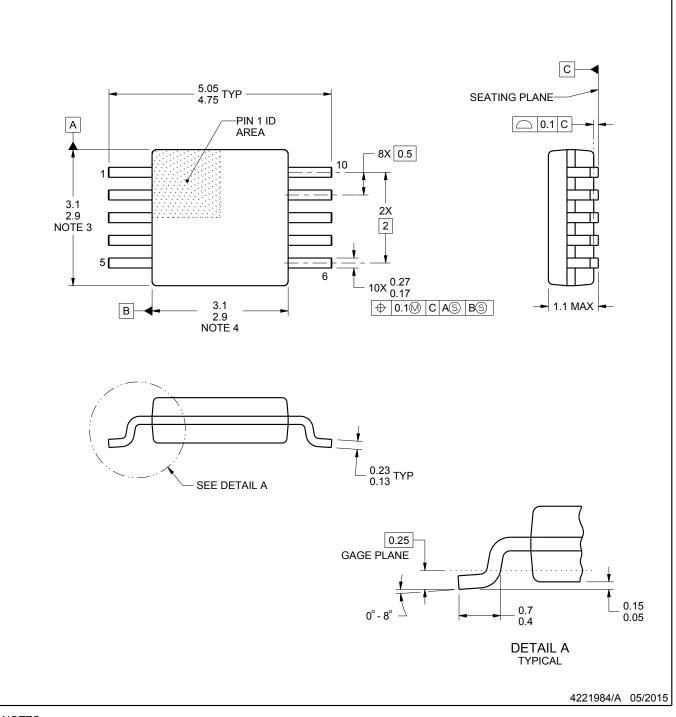

#### PACKAGE DRAWING

#### DGS (S-PDSO-G10)

#### PLASTIC SMALL-OUTLINE PACKAGE

- NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion.

- A. Falls within JEDEC MO-187

#### **PACKAGING INFORMATION**

| Orderable part number | Status | Material type | Package   Pins   | Package qty   Carrier | RoHS | Lead finish/       | MSL rating/         | Op temp (°C) | Part marking |

|-----------------------|--------|---------------|------------------|-----------------------|------|--------------------|---------------------|--------------|--------------|

|                       | (1)    | (2)           |                  |                       | (3)  | Ball material      | Peak reflow         |              | (6)          |

|                       |        |               |                  |                       |      | (4)                | (5)                 |              |              |

| ADS1244IDGSR          | Active | Production    | VSSOP (DGS)   10 | 2500   LARGE T&R      | Yes  | Call TI   Nipdauag | Level-2-260C-1 YEAR | -40 to 85    | BHG          |

| ADS1244IDGSR.B        | Active | Production    | VSSOP (DGS)   10 | 2500   LARGE T&R      | Yes  | Call TI            | Level-2-260C-1 YEAR | -40 to 85    | BHG          |

| ADS1244IDGST          | Active | Production    | VSSOP (DGS)   10 | 250   SMALL T&R       | Yes  | Call TI   Nipdauag | Level-2-260C-1 YEAR | -40 to 85    | BHG          |

| ADS1244IDGST.B        | Active | Production    | VSSOP (DGS)   10 | 250   SMALL T&R       | Yes  | Call TI            | Level-2-260C-1 YEAR | -40 to 85    | BHG          |

| ADS1244IDGSTG4        | Active | Production    | VSSOP (DGS)   10 | 250   SMALL T&R       | Yes  | Call TI            | Level-2-260C-1 YEAR | -40 to 85    | BHG          |

<sup>(1)</sup> **Status:** For more details on status, see our product life cycle.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

## **DGS0010A**

## **PACKAGE OUTLINE**

### VSSOP - 1.1 mm max height

SMALL OUTLINE PACKAGE

NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M. 2. This drawing is subject to change without notice. 3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

- exceed 0.15 mm per side.

- 4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm per side.

- 5. Reference JEDEC registration MO-187, variation BA.

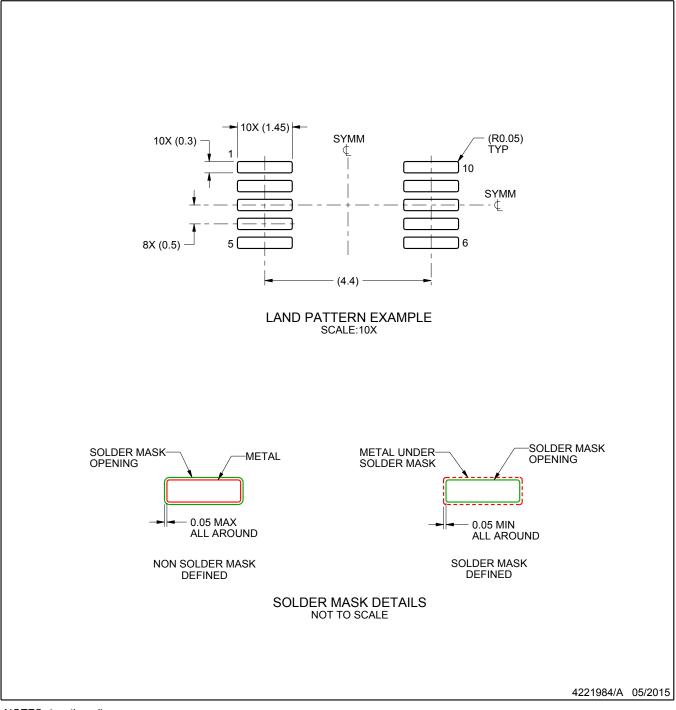

## DGS0010A

## **EXAMPLE BOARD LAYOUT**

### VSSOP - 1.1 mm max height

SMALL OUTLINE PACKAGE

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

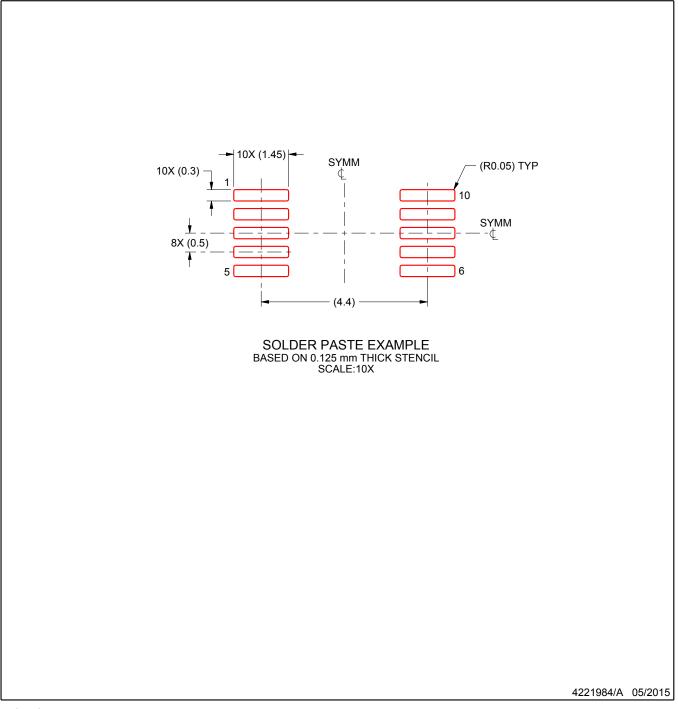

## DGS0010A

## **EXAMPLE STENCIL DESIGN**

### VSSOP - 1.1 mm max height

SMALL OUTLINE PACKAGE

NOTES: (continued)

9. Board assembly site may have different recommendations for stencil design.

<sup>8.</sup> Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2025, Texas Instruments Incorporated