ADS1148-Q1

SBAS674A - JULY 2014-REVISED SEPTEMBER 2016

# ADS1148-Q1 Automotive,16-Bit, 2-kSPS, Analog-to-Digital Converter with Integrated Programmable Gain Amplifier (PGA), Reference, and Oscillator

## **Features**

- Qualified for Automotive Applications

- AEC-Q100 Qualified with the Following Results:

- Temperature Grade 1: –40°C to +125°C

- HBM ESD Classification 2

- CDM ESD Classification C5

- Programmable Gain: 1 V/V to 128 V/V

- Programmable Data Rates: 5 SPS to 2 kSPS

- Single-Cycle Settling for All Data Rates

- Analog Multiplexer With 8 Independently Selectable Inputs

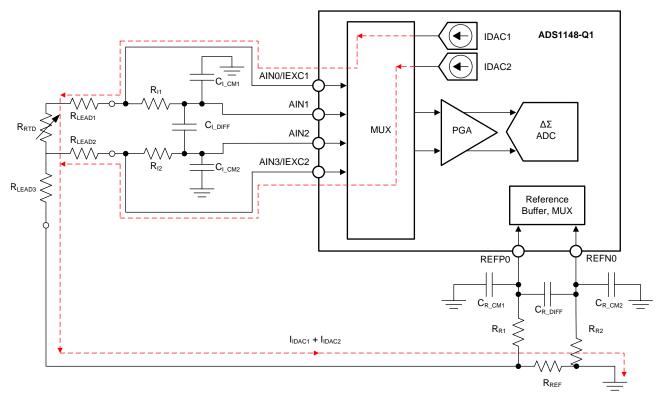

- **Dual-Matched Programmable Excitation Current** Sources: 50 µA to 1.5 mA

- Internal 2.048-V Voltage Reference

- Internal 4.096-MHz Oscillator

- Internal Temperature Sensor

- Open Sensor Detection

- Power-Supply and External Reference Monitoring

- Self and System Calibration

- 8 General-Purpose I/Os

- SPI-Compatible Serial Interface

- Analog Supply: Unipolar (2.7 V to 5.25 V) or Bipolar (±2.5 V)

- Digital Supply: 2.7 V to 5.25 V

# Applications

- Thermocouple-, RTD- and Thermistor-Based Temperature Measurement Systems

- Exhaust Gas Sensing (Soot, NO<sub>x</sub>, NH<sub>3</sub>, O2)

- Battery Management Systems (BMS)

- Multichannel Voltage and Current Monitoring

# 3 Description

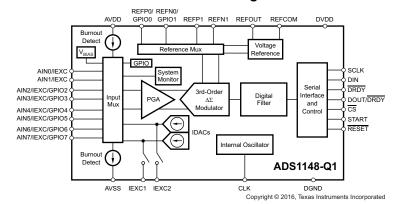

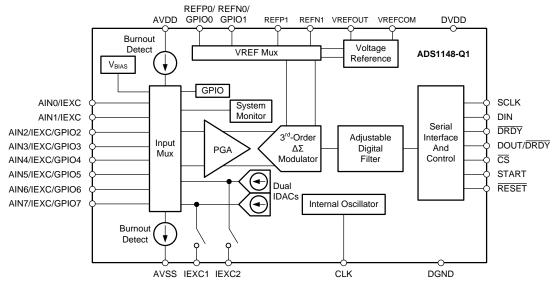

The ADS1148-Q1 is a highly-integrated, precision, 16-bit analog-to-digital converter (ADC) that includes many integrated features to reduce system cost and count for sensor measurement component The device features a low-noise, applications. programmable gain amplifier (PGA), a precision delta-sigma ( $\Delta\Sigma$ ) ADC with a single-cycle settling digital filter, and an internal oscillator. ADS1148-Q1 integrates a low-drift voltage reference, and two matched programmable excitation current sources (IDACs).

The device offers a fully flexible multiplexer that allows both positive and negative inputs to be selected independently. In addition, the multiplexer integrates sensor burn-out detection, voltage bias for thermocouples, system monitoring, and eight generalpurpose digital I/Os (GPIOs). The PGA provides selectable gains up to 128 V/V. These features provide a complete front-end solution for temperature measurement applications, sensor including thermistors, resistance thermocouples. and temperature detectors (RTDs), and other small-signal measurements. The digital filter settles in a single cycle to support fast channel cycling when using the input multiplexer and provides data rates up to 2 kSPS. For data rates of 20 SPS or less, both the 50-Hz and 60-Hz interference are rejected by the filter.

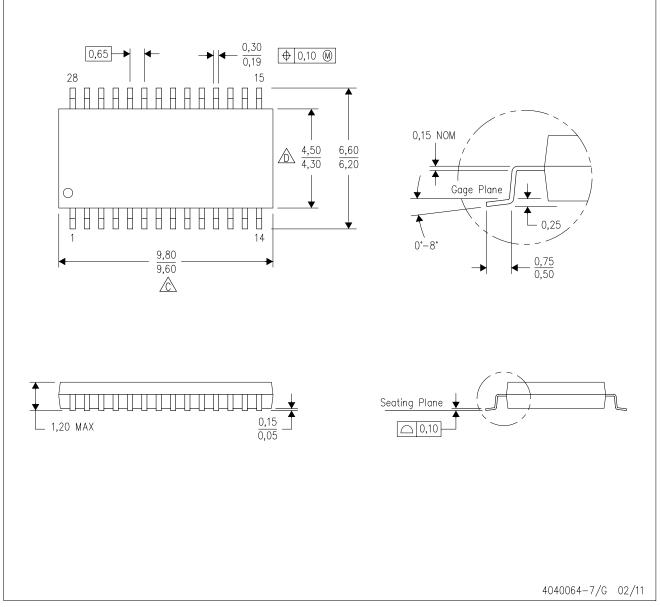

#### Device Information<sup>(1)</sup>

| PART NUMBER PACKAGE |            | BODY SIZE (NOM)   |

|---------------------|------------|-------------------|

| ADS1148-Q1          | TSSOP (28) | 9.70 mm × 4.40 mm |

(1) For all available packages, see the orderable addendum at the end of the datasheet.

# **Functional Block Diagram**

# **Table of Contents**

| 1 | Features                             | 1   | 8.5 Programming                                      |      |

|---|--------------------------------------|-----|------------------------------------------------------|------|

| 2 | Applications                         | 1   | 8.6 Register Maps                                    |      |

| 3 | Description                          | 1 9 | Application and Implementation                       | . 5  |

| 4 | Revision History                     | 2   | 9.1 Application Information                          |      |

| 5 | Pin Configuration and Functions      |     | 9.2 Typical Applications                             | 5    |

| 6 | Specifications                       |     | 9.3 Do's and Don'ts                                  | 68   |

| • | 6.1 Absolute Maximum Ratings         | 10  | Power Supply Recommendations                         | . 70 |

|   | 6.2 ESD Ratings                      |     | 10.1 Power Supply Sequencing                         | 70   |

|   | 6.3 Recommended Operating Conditions |     | 10.2 Power Supply Decoupling                         | 70   |

|   | 6.4 Thermal Information              | 44  | Layout                                               | . 7  |

|   | 6.5 Electrical Characteristics       |     | 11.1 Layout Guidelines                               | 7    |

|   | 6.6 Timing Requirements              |     | 11.2 Layout Example                                  | 72   |

|   | 6.7 Switching Characteristics        | 40  | Device and Documentation Support                     | . 73 |

|   | 6.8 Typical Characteristics          |     | 12.1 Documentation Support                           | 7:   |

| 7 | Parameter Measurement Information 1  |     | 12.2 Receiving Notification of Documentation Updates | s 7  |

| - | 7.1 Noise Performance                |     | 12.3 Community Resources                             | 7:   |

| 8 | Detailed Description                 |     | 12.4 Trademarks                                      | 7:   |

| • | 8.1 Overview                         |     | 12.5 Electrostatic Discharge Caution                 | 7:   |

|   | 8.2 Functional Block Diagram         |     | 12.6 Glossary                                        | 73   |

|   | 8.3 Feature Description              | 12  | Mechanical, Packaging, and Orderable                 | 7    |

|   | 8.4 Device Functional Modes          | 26  | Information                                          | . /, |

# 4 Revision History

| Cł | Changes from Original (July 2014) to Revision A |   |  |  |

|----|-------------------------------------------------|---|--|--|

| •  | First public release of datasheet               | 1 |  |  |

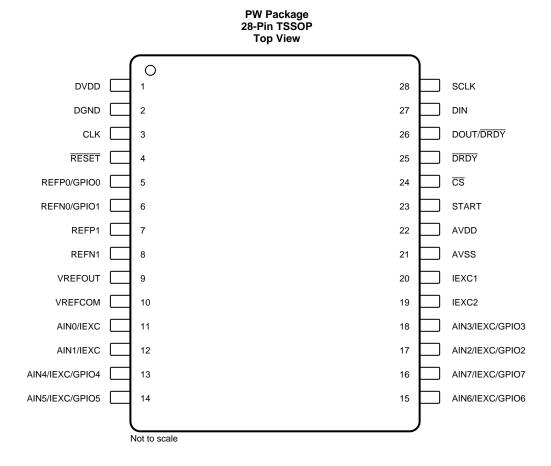

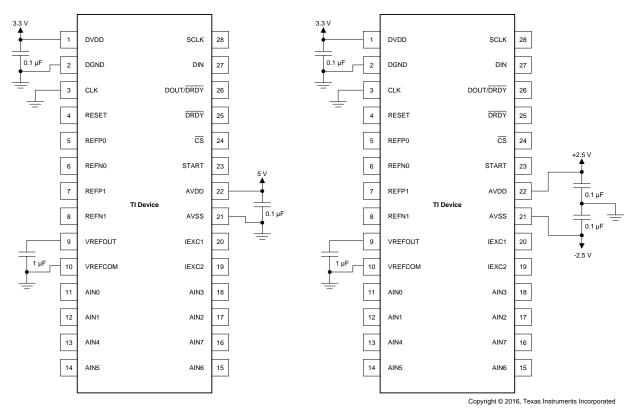

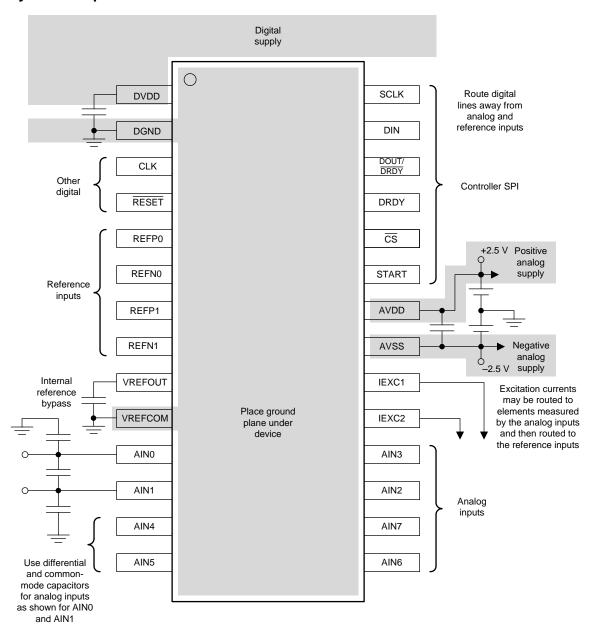

# 5 Pin Configuration and Functions

# **Pin Functions**

| PIN             |     | TVDE(1)             | DESCRIPTION(2)                                                                                                                                    |

|-----------------|-----|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME            | NO. | TYPE <sup>(1)</sup> | DESCRIPTION <sup>(2)</sup>                                                                                                                        |

| AIN0/IEXC       | 11  | I                   | Analog input 0, optional excitation current output                                                                                                |

| AIN1/IEXC       | 12  | I                   | Analog input 1, optional excitation current output                                                                                                |

| AIN2/IEXC/GPIO2 | 17  | I/O                 | Analog input 2, optional excitation current output, or general-purpose digital input/output pin 2                                                 |

| AIN3/IEXC/GPIO3 | 18  | I/O                 | Analog input 3, optional excitation current output, or general-purpose digital input/output pin 3                                                 |

| AIN4/IEXC/GPIO4 | 13  | I/O                 | Analog input 4, optional excitation current output, or general-purpose digital input/output pin 4                                                 |

| AIN5/IEXC/GPIO5 | 14  | I/O                 | Analog input 5, optional excitation current output, or general-purpose digital input/output pin 5                                                 |

| AIN6/IEXC/GPIO6 | 15  | I/O                 | Analog input 6, optional excitation current output, or general-purpose digital input/output pin 6                                                 |

| AIN7/IEXC/GPIO7 | 16  | I/O                 | Analog input 7, optional excitation current output, or general-purpose digital input/output pin 7                                                 |

| AVDD            | 22  | Р                   | Positive analog power supply, connect a 0.1-µF capacitor to AVSS                                                                                  |

| AVSS            | 21  | Р                   | Negative analog power supply                                                                                                                      |

| CLK             | 3   | I                   | External clock input, tie to DGND to activate the internal oscillator                                                                             |

| CS              | 24  | I                   | Chip select (active low)                                                                                                                          |

| DGND            | 2   | G                   | Digital ground                                                                                                                                    |

| DIN             | 27  | I                   | Serial data input                                                                                                                                 |

| DOUT/DRDY       | 26  | 0                   | Serial data output, or data out combined with data ready                                                                                          |

| DRDY            | 25  | 0                   | Data ready (active low)                                                                                                                           |

| DVDD            | 1   | Р                   | Digital power supply, connect a 0.1-µF capacitor to DGND                                                                                          |

| IEXC1           | 20  | 0                   | Excitation current output 1                                                                                                                       |

| IEXC2           | 19  | 0                   | Excitation current output 2                                                                                                                       |

| REFN0/GPIO1     | 6   | I/O                 | Negative external reference input 0, or general-purpose digital input/output pin 1                                                                |

| REFN1           | 8   | I                   | Negative external reference input 1                                                                                                               |

| REFP0/GPIO0     | 5   | I/O                 | Positive external reference input 0, or general-purpose digital input/output pin 1                                                                |

| REFP1           | 7   | I                   | Positive external reference input 1                                                                                                               |

| RESET           | 4   | Į.                  | Reset (active low)                                                                                                                                |

| SCLK            | 28  | I                   | Serial clock input                                                                                                                                |

| START           | 23  | Į.                  | Conversion start                                                                                                                                  |

| VREFCOM         | 10  | 0                   | Negative internal reference voltage output, connect to AVSS when using a unipolar supply or to the mid-voltage ground when using a bipolar supply |

| VREFOUT         | 9   | 0                   | Positive internal reference voltage output, connect a capacitor in the range of 1 μF to 47 μF to VREFCOM                                          |

<sup>(1)</sup> G = ground, I = input, O = output, P = and power.

(2) See the *Unused Inputs and Outputs* section for unused pin connections.

# 6 Specifications

# 6.1 Absolute Maximum Ratings<sup>(1)</sup>

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                    | MIN        | MAX        | UNIT |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|------------|------------|------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | AVDD to AVSS                                       | -0.3       | 5.5        |      |

| Power-supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | AVSS to DGND                                       | -2.8       | 0.3        | V    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | DVDD to DGND                                       | -0.3       | 5.5        |      |

| Analog input voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | AINx, REFPx, REFNx, VREFOUT, VREFCOM, IEXC1, IEXC2 | AVSS - 0.3 | AVDD + 0.3 | V    |

| Digital input voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | SCLK, DIN, DOUT/DRDY, DRDY, CS, START, RESET, CLK  | DGND - 0.3 | DVDD + 0.3 | V    |

| In a set of the set of | Continuous, any pin except power-supply pins       | -10        | 10         | A    |

| Input current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Momentary, any pin except power-supply pins        | -100       | 100        | mA   |

| T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Junction, T <sub>J</sub>                           |            | 150        | °C   |

| Temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Storage, T <sub>stg</sub>                          | -60        | 150        | ٠.   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 6.2 ESD Ratings

|                    |                         |                                                         | VALUE | UNIT |

|--------------------|-------------------------|---------------------------------------------------------|-------|------|

| V                  | Floatroototic discharge | Human-body model (HBM), per AEC Q100-002 <sup>(1)</sup> | ±2000 | \/   |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per AEC Q100-011            | ±750  | V    |

<sup>(1)</sup> AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

Product Folder Links: ADS1148-Q1

# 6.3 Recommended Operating Conditions

over operating ambient temperature range (unless otherwise noted)

|                      |                                      |                                                  | MIN                      | NOM MAX                    | UNIT |

|----------------------|--------------------------------------|--------------------------------------------------|--------------------------|----------------------------|------|

| POWER                | SUPPLY                               |                                                  |                          |                            |      |

|                      |                                      | AVDD to AVSS                                     | 2.7                      | 5.25                       |      |

|                      | Analog power supply                  | AVSS to DGND                                     | -2.65                    | 0.1                        | V    |

|                      |                                      | AVDD to DGND                                     | 2.25                     | 5.25                       |      |

|                      | Digital power supply                 | DVDD to DGND                                     | 2.7                      | 5.25                       | V    |

| ANALOG               | S INPUTS <sup>(1)</sup>              |                                                  |                          |                            |      |

| V <sub>IN</sub>      | Differential input voltage           | $V_{(AINP)} - V_{(AINN)}^{(2)}$                  | –V <sub>REF</sub> / Gain | V <sub>REF</sub> / Gain    | V    |

| V <sub>CM</sub>      | Common-mode input voltage            | (V <sub>(AINP)</sub> + V <sub>(AINN)</sub> ) / 2 |                          | See Equation 3             |      |

| VOLTAG               | E REFERENCE INPUTS <sup>(3)</sup>    |                                                  |                          |                            |      |

| $V_{REF}$            | Differential reference input voltage | $V_{(REFPx)} - V_{(REFNx)}$                      | 0.5                      | (AVDD – AVSS) – 1          | V    |

| V <sub>(REFNx)</sub> | Absolute negative reference voltage  |                                                  | AVSS - 0.1               | V <sub>(REFPx)</sub> – 0.5 | V    |

| $V_{(REFPx)}$        | Absolute positive reference voltage  |                                                  | $V_{(REFNx)} + 0.5$      | AVDD + 0.1                 | V    |

| EXTERN               | AL CLOCK INPUT <sup>(4)</sup>        |                                                  |                          |                            |      |

| f <sub>CLK</sub>     | External clock frequency             |                                                  | 1                        | 4.5                        | MHz  |

|                      | External clock duty cycle            |                                                  | 25%                      | 75%                        |      |

| GENERA               | AL-PURPOSE INPUTS AND OUTPUTS (C     | SPIO)                                            |                          |                            |      |

|                      | GPIO input voltage                   |                                                  | AVSS                     | AVDD                       | V    |

| DIGITAL              | INPUTS                               | ,                                                |                          |                            |      |

|                      | Digital input voltage                |                                                  | DGND                     | DVDD                       | V    |

| TEMPER               | ATURE RANGE                          | ,                                                |                          |                            |      |

| T <sub>A</sub>       | Operating ambient temperature        |                                                  | -40                      | 125                        | °C   |

- $\rm AIN_{P}$  and  $\rm AIN_{N}$  denote the positive and negative inputs of the PGA. For  $\rm V_{REF} > 2.7~V$ , the differential input voltage must not exceed 2.7 V / Gain. REFPx and REFNx denote one of the two available differential reference input pairs.

- The external clock is only required if the internal oscillator is not used.

# 6.4 Thermal Information

|                        |                                              | ADS1148-Q1 |      |

|------------------------|----------------------------------------------|------------|------|

|                        | THERMAL METRIC <sup>(1)</sup>                | PW (TSSOP) | UNIT |

|                        |                                              | 28 PINS    |      |

| $R_{\theta JA}$        | Junction-to-ambient thermal resistance       | 74.2       | °C/W |

| $R_{\theta JC(top)}$   | Junction-to-case (top) thermal resistance    | 20.2       | °C/W |

| $R_{\theta JB}$        | Junction-to-board thermal resistance         | 31.8       | °C/W |

| ΨЈТ                    | Junction-to-top characterization parameter   | 0.8        | °C/W |

| ΨЈВ                    | Junction-to-board characterization parameter | 31.3       | °C/W |

| R <sub>0</sub> JC(bot) | Junction-to-case (bottom) thermal resistance | n/a        | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

# 6.5 Electrical Characteristics

Minimum and maximum specifications apply from  $T_A = -40^{\circ}\text{C}$  to +125°C. Typical specifications are at  $T_A = 25^{\circ}\text{C}$ . All specifications are at AVDD = 5 V, DVDD = 3.3 V, AVSS = 0 V,  $V_{REF} = 2.048$  V, and  $f_{CLK} = 4.096$  MHz (unless otherwise noted).

| noted).          | DADAMETER                             | TEST COMPITIONS                                                  | MINI               | TVD                     | MAY   | LINUT   |

|------------------|---------------------------------------|------------------------------------------------------------------|--------------------|-------------------------|-------|---------|

|                  | PARAMETER                             | TEST CONDITIONS                                                  | MIN                | TYP                     | MAX   | UNIT    |

| ANALO            | G INPUTS                              |                                                                  |                    |                         |       | _       |

|                  | Differential input current            |                                                                  | _                  | 100                     |       | pA      |

|                  | Absolute input current                |                                                                  | Se                 | ee Table 4              |       |         |

| PGA              |                                       |                                                                  |                    |                         |       |         |

|                  | PGA gain settings                     |                                                                  | 1, 2, 4, 8         | , 16, 32, 64, 128       |       | V/V     |

| SYSTEM           | I PERFORMANCE                         |                                                                  |                    |                         |       |         |

|                  | Resolution                            | No missing codes                                                 | 16                 |                         |       | Bits    |

| DR               | Data rate                             |                                                                  | 5, 10, 20, 40, 80, | 160, 320, 640, 1000, 20 | 000   | SPS     |

|                  | ADC conversion time                   | Single-cycle settling                                            | Se                 | e Table 10              |       |         |

| INL              | Integral nonlinearity                 | Differential input, end point fit,<br>Gain = 1, $V_{CM}$ = 2.5 V | -1                 | 0.5                     | 1     | LSB     |

|                  | Offset error                          | After calibration                                                | -1                 |                         | 1     | LSB     |

|                  | O#+ -l-'#                             | Gain = 1                                                         |                    | 100                     |       | nV/°C   |

|                  | Offset drift                          | Gain = 128                                                       |                    | 15                      |       | nV/°C   |

|                  | Gain error                            | Excluding V <sub>REF</sub> errors                                | -0.5%              |                         | 0.5%  |         |

|                  |                                       | Gain = 1, excludes V <sub>REF</sub> drift                        |                    | 1                       |       | ppm°C   |

|                  | Gain drift                            | Gain = 128, excludes V <sub>REF</sub> drift                      |                    | -3.5                    |       | ppm/°C  |

|                  | Noise                                 |                                                                  | See Tab            | le 1 and Table 2        |       |         |

| NMRR             | Normal mode rejection                 |                                                                  | See Table 6        |                         |       |         |

| -                |                                       | At dc, gain = 1                                                  |                    | 90                      |       |         |

| CMRR             | Common-mode rejection ratio           | At dc, gain = 32                                                 |                    | 100                     |       | dB      |

| PSRR             | Power-supply rejection ratio          | AVDD, DVDD at dc                                                 |                    | 100                     |       | dB      |

| VOLTAG           | SE REFERENCE INPUTS                   | · · · · · · · · · · · · · · · · · · ·                            |                    |                         |       |         |

|                  | Reference input current               |                                                                  |                    | 30                      |       | nA      |

| INTERN           | AL VOLTAGE REFERENCE                  |                                                                  |                    |                         |       |         |

| V <sub>REF</sub> | Internal reference voltage            |                                                                  | 2.038              | 2.048                   | 2.058 | V       |

| INLI             | Reference drift <sup>(1)</sup>        | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$             |                    | 20                      | 50    | ppm/°C  |

|                  | Output current <sup>(2)</sup>         | 1,4 10 0 10 1 120 0                                              | -10                |                         | 10    | mA      |

|                  | Load regulation                       |                                                                  |                    | 50                      |       | μV/mA   |

| INTERN           | AL OSCILLATOR                         |                                                                  |                    |                         |       | μν/ιιστ |

|                  | Internal oscillator frequency         |                                                                  | 3.85               | 4.096                   | 4.3   | MHz     |

| EXCITA:          | TION CURRENT SOURCES (IDACs           | <u> </u>                                                         | 0.00               | 4.000                   |       | IVII IZ |

| 2,(011)(         | Output current settings               |                                                                  | 50 100 250         | 500, 750, 1000, 1500    |       | μA      |

|                  | Compliance voltage                    | All currents                                                     |                    | e 9 and Figure 10       |       | μπ      |

|                  | Absolute error                        | All currents, each IDAC                                          | -6%                | ±1%                     | 6%    |         |

|                  | Absolute mismatch                     | *                                                                | -076               | ±0.2%                   | 078   |         |

|                  | Temperature drift                     | All currents, between IDACs  Each IDAC                           |                    | 200                     |       | ppm/°C  |

|                  | · · · · · · · · · · · · · · · · · · · |                                                                  |                    |                         |       | • • •   |

| DUDN 6           | Temperature drift matching            | Between IDACs                                                    |                    | 10                      |       | ppm/°C  |

| BURN-U           | OUT CURRENT SOURCES                   |                                                                  |                    | 0.5.0.40                |       |         |

| DIAC V           | Burn-out current source settings      |                                                                  |                    | 0.5, 2, 10              |       | μA      |

| BIAS VC          | DLTAGE                                |                                                                  | , <del>.</del>     | D 41/00\ / 2            |       | .,      |

|                  | Bias voltage                          |                                                                  | (AVD               | D + AVSS) / 2           |       | V       |

|                  | Bias voltage output impedance         |                                                                  |                    | 400                     |       | Ω       |

| TEMPER           | RATURE SENSOR                         | T                                                                |                    |                         |       |         |

|                  | Output voltage                        | T <sub>A</sub> = 25°C                                            |                    | 118                     |       | mV      |

|                  | Temperature coefficient               |                                                                  |                    | 405                     |       | μV/°C   |

Specified by the combination of design and final production test. Do not exceed this loading on the internal voltage reference.

# **Electrical Characteristics (continued)**

Minimum and maximum specifications apply from  $T_A = -40^{\circ}\text{C}$  to +125°C. Typical specifications are at  $T_A = 25^{\circ}\text{C}$ . All specifications are at AVDD = 5 V, DVDD = 3.3 V, AVSS = 0 V,  $V_{REF} = 2.048$  V, and  $f_{CLK} = 4.096$  MHz (unless otherwise noted).

|                   | PARAMETER                  | TEST CONDITIONS                                                                 | MIN        | TYP MAX    | UNIT  |

|-------------------|----------------------------|---------------------------------------------------------------------------------|------------|------------|-------|

| GENER             | RAL-PURPOSE INPUTS AND OUT | PUTS (GPIO)                                                                     |            |            |       |

| V <sub>IL</sub>   | Low-level input voltage    |                                                                                 | AVSS       | 0.3 × AVDD | V     |

| $V_{IH}$          | High-level input voltage   |                                                                                 | 0.7 × AVDD | AVDD       | V     |

| V <sub>OL</sub>   | Low-level output voltage   | I <sub>OL</sub> = 1 mA                                                          | AVSS       | 0.2 × AVDD | V     |

| V <sub>OH</sub>   | High-level output voltage  | I <sub>OH</sub> = 1 mA                                                          | 0.8 × AVDD |            | V     |

| DIGITA            | L INPUTS AND OUTPUTS (OTHE | R THAN GPIO)                                                                    |            |            |       |

| $V_{IL}$          | Low-level input voltage    |                                                                                 | DGND       | 0.3 × DVDD | V     |

| $V_{IH}$          | High-level input voltage   |                                                                                 | 0.7 x DVDD | DVDD       | V     |

| V <sub>OL</sub>   | Low-level output voltage   | I <sub>OL</sub> = 1 mA                                                          | DGND       | 0.2 × DVDD | V     |

| $V_{OH}$          | High-level output voltage  | I <sub>OH</sub> = 1 mA                                                          | 0.8 × DVDD |            | V     |

|                   | Input leakage              | DGND < V <sub>IN</sub> < DVDD                                                   | -10        | 10         | μA    |

| POWE              | R SUPPLY                   |                                                                                 |            |            |       |

|                   |                            | Power-down mode                                                                 |            | 0.1        |       |

|                   |                            | Converting, AVDD = 3.3 V,<br>DR = 20 SPS, external reference                    |            | 212        |       |

| I <sub>AVDD</sub> | Analog supply current      | Converting, AVDD = 5 V,<br>DR = 20 SPS, external reference                      |            | 225        | μA    |

|                   |                            | Additional current with internal reference enabled                              |            | 180        |       |

|                   |                            | Power-down mode                                                                 |            | 0.2        |       |

| I <sub>DVDD</sub> | Digital supply current     | Normal operation, DVDD = 3.3 V,<br>DR = 20 SPS, internal oscillator             |            | 210        | μA    |

|                   |                            | Normal operation, DVDD = 5 V,<br>DR = 20 SPS, internal oscillator               |            | 230        |       |

| D                 | Down dissipation           | AVDD = DVDD = 3.3 V,<br>DR = 20 SPS, internal oscillator, external<br>reference |            | 1.4        | mW    |

| $P_D$             | Power dissipation          | AVDD = DVDD = 5 V,<br>DR = 20 SPS, internal oscillator, external<br>reference   |            | 2.3        | IIIVV |

Submit Documentation Feedback

Copyright © 2014–2016, Texas Instruments Incorporated

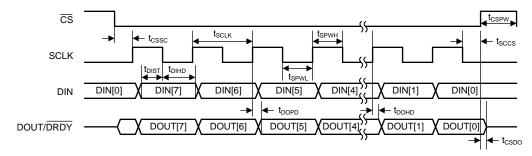

# 6.6 Timing Requirements

at  $T_A = -40$ °C to +125°C and DVDD = 2.7 V to 5.5 V (unless otherwise noted)

|                    |                                                                                                | MIN                | NOM | MAX | UNIT                            |

|--------------------|------------------------------------------------------------------------------------------------|--------------------|-----|-----|---------------------------------|

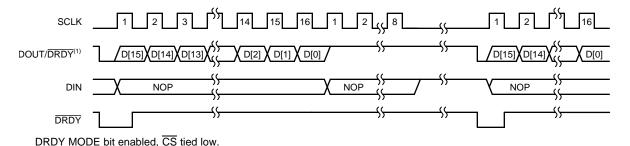

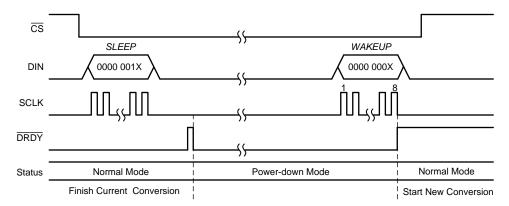

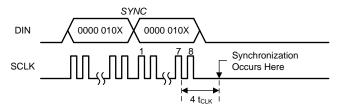

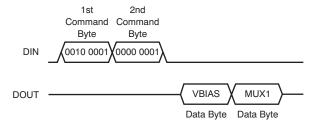

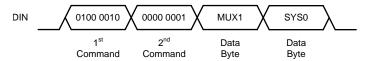

| SERIAL             | INTERFACE (See Figure 1 and Figure 2)                                                          |                    |     |     |                                 |

| t <sub>CSSC</sub>  | Delay time, first SCLK rising edge after CS falling edge                                       | 10                 |     |     | ns                              |

| t <sub>SCCS</sub>  | Delay time, CS rising edge after final SCLK falling edge                                       | 7                  |     |     | t <sub>CLK</sub> <sup>(1)</sup> |

| t <sub>CSPW</sub>  | Pulse duration, CS high                                                                        | 7                  |     |     | t <sub>CLK</sub>                |

|                    | SCLK pariod                                                                                    | 488                |     |     | ns                              |

| t <sub>SCLK</sub>  | SCLK period                                                                                    |                    |     | 64  | Conversions                     |

| t <sub>SPWH</sub>  | Pulse duration, SCLK high                                                                      | 0.3                |     | 0.7 | t <sub>SCLK</sub>               |

| t <sub>SPWL</sub>  | Pulse duration, SCLK low                                                                       | 0.3                |     | 0.7 | t <sub>SCLK</sub>               |

| t <sub>DIST</sub>  | Setup time, DIN valid before SCLK falling edge                                                 | 25                 |     |     | ns                              |

| t <sub>DIHD</sub>  | Hold time, DIN valid after SCLK falling edge                                                   | 25                 |     |     | ns                              |

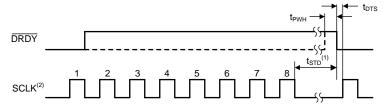

| t <sub>STD</sub>   | Setup time, SCLK low before DRDY rising edge                                                   | 7                  |     |     | t <sub>CLK</sub>                |

| t <sub>DTS</sub>   | Delay time, SCLK rising edge after DRDY falling edge                                           | 1                  |     |     | t <sub>CLK</sub>                |

| MINIMUN            | // START TIME PULSE DURATION (See Figure 3)                                                    |                    |     |     |                                 |

| t <sub>START</sub> | Pulse duration, START high                                                                     | 3                  |     |     | t <sub>CLK</sub>                |

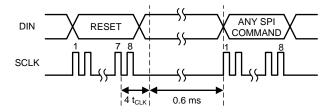

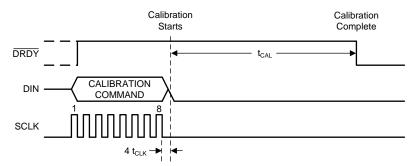

|                    | PULSE DURATION, SERIAL INTERFACE COMMUNICATION AFTER RES                                       | SET (See Figure 4  | )   |     |                                 |

| t <sub>RESET</sub> | Pulse duration, RESET low                                                                      | 4                  |     |     | t <sub>CLK</sub>                |

| t <sub>RHSC</sub>  | Delay time, SCLK rising edge (start of serial interface communication) after RESET rising edge | 0.6 <sup>(2)</sup> |     |     | ms                              |

# 6.7 Switching Characteristics

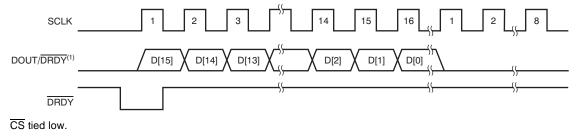

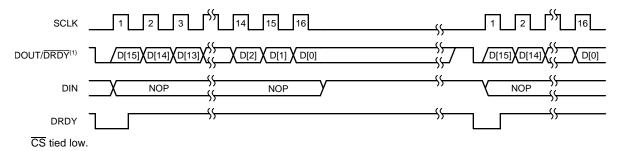

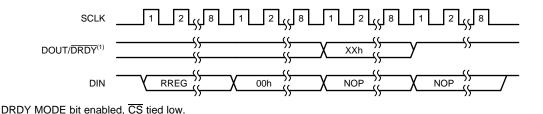

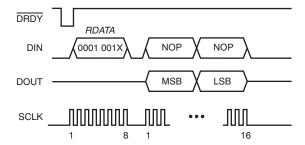

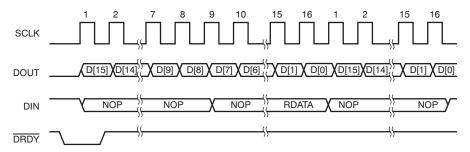

at  $T_A = -40$ °C to +125°C and DVDD = 2.7 V to 5.5 V (unless otherwise noted); see Figure 1 and Figure 2

|                   | PARAMETER                                                     | TEST CONDITIONS | MIN | TYP | MAX | UNIT             |

|-------------------|---------------------------------------------------------------|-----------------|-----|-----|-----|------------------|

|                   | Propagation delay time,                                       | DVDD ≤ 3.6 V    |     |     | 50  | no               |

| t <sub>DOPD</sub> | SCLK rising edge to valid new DOUT                            | DVDD > 3.6 V    |     |     | 180 | ns               |

| $t_{DOHD}$        | DOUT hold time                                                |                 | 0   |     |     | ns               |

| t <sub>CSDO</sub> | Propagation delay time, CS rising edge to DOUT high impedance |                 |     |     | 25  | ns               |

| t <sub>PWH</sub>  | Pulse duration, DRDY high                                     |                 | 3   |     |     | t <sub>CLK</sub> |

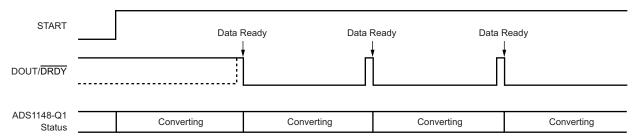

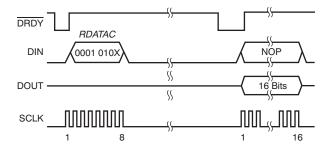

Figure 1. Serial Interface Timing, DRDY MODE Bit = 0

- (1) This timing diagram is applicable only when the \(\overline{CS}\) pin is low. SCLK does not need to be low during t<sub>STD</sub> when \(\overline{CS}\) is high.

- (2) SCLK must only be sent in multiples of eight during partial retrieval of output data.

Figure 2. Serial Interface Timing to Allow Conversion Result Loading

Figure 3. Minimum Start Pulse Duration

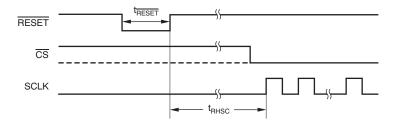

Figure 4. Reset Pulse Duration and Serial Interface Communication After Reset

# 6.8 Typical Characteristics

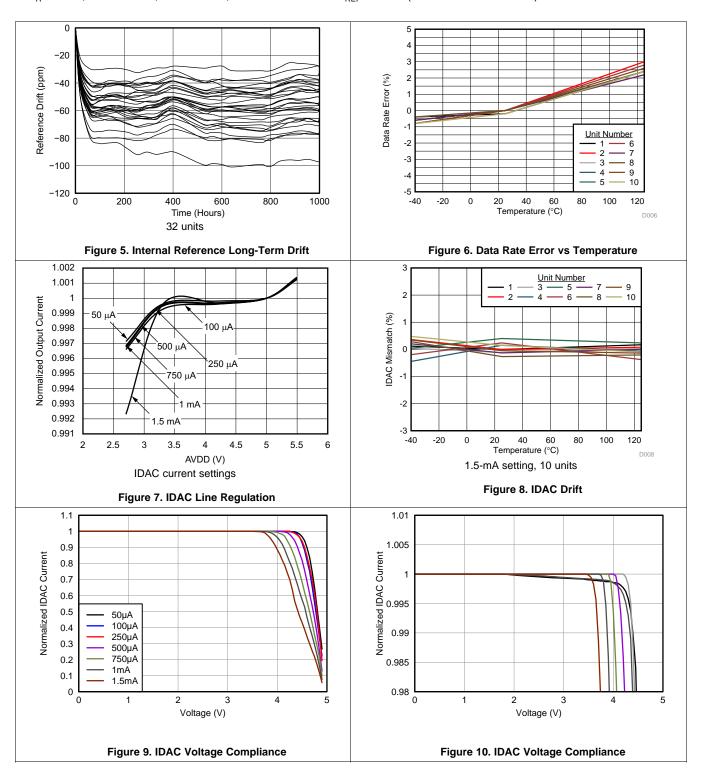

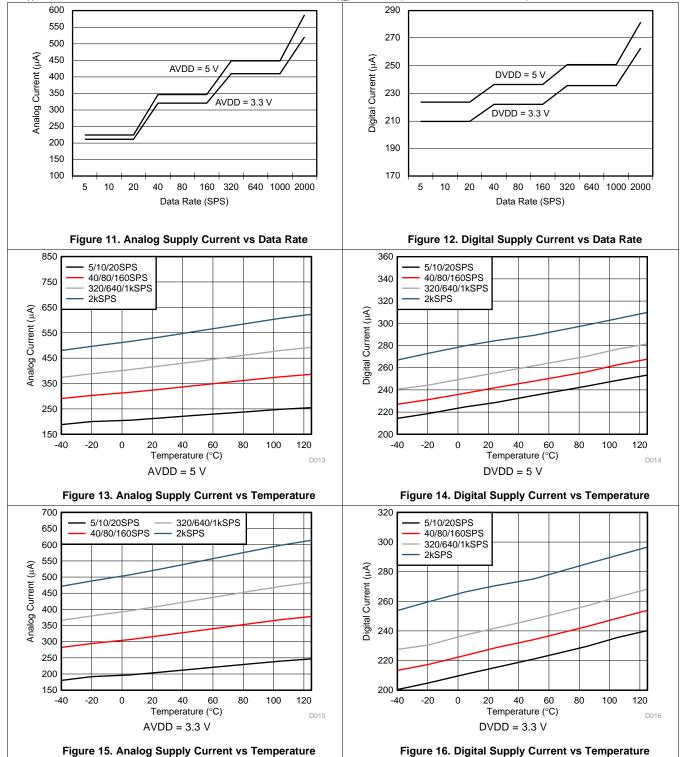

at  $T_A = 25$ °C, AVDD = 5 V, AVSS = 0 V, DVDD = 3.3 V and  $V_{REF} = 2.5$  V (unless otherwise noted)

# TEXAS INSTRUMENTS

# **Typical Characteristics (continued)**

at  $T_A = 25$ °C, AVDD = 5 V, AVSS = 0 V, DVDD = 3.3 V and  $V_{REF} = 2.5$  V (unless otherwise noted)

#### 7 Parameter Measurement Information

#### 7.1 Noise Performance

The ADC noise performance is optimized by adjusting the data rate and PGA setting. Generally, the lowest input-referred noise is achieved using the highest gain possible, consistent with the input signal range. Do not set the gain too high or the result is an ADC overrange. Noise also depends on the output data rate. When the data rate reduces, the ADC bandwidth correspondingly reduces. This reduction in total bandwidth results in lower overall noise. Table 1 and Table 2 summarize the noise performance of the device. The data are representative of typical noise performance at  $T_A = 25$ °C. The data shown are the result of averaging the readings from multiple devices and were measured with the inputs shorted together.

Table 1 lists the input-referred noise in units of  $\mu V_{PP}$  for the conditions shown. Table 2 lists the corresponding data in units of effective number of bits (ENOB), where ENOB for the peak-to-peak noise is defined in Equation 1.

$ENOB = \ln((2 \times V_{REF} / Gain) / V_{NPP}) / \ln(2)$

where

V<sub>NPP</sub> is the input-referred peak-to-peak noise voltage

(1)

Table 1. Noise in  $\mu V_{PP}$  At  $V_{REF}$  = 2.048 V, AVDD = 5 V, AVSS = 0 V

|           |                     |                      | 1121                 |                     |                     |                     |                     |                     |

|-----------|---------------------|----------------------|----------------------|---------------------|---------------------|---------------------|---------------------|---------------------|

| DATA RATE | PGA SETTING         |                      |                      |                     |                     |                     |                     |                     |

| (SPS)     | 1                   | 2                    | 4                    | 8                   | 16                  | 32                  | 64                  | 128                 |

| 5         | 62.5 <sup>(1)</sup> | 31.25 <sup>(1)</sup> | 15.63 <sup>(1)</sup> | 7.81 <sup>(1)</sup> | 3.91 <sup>(1)</sup> | 1.95 <sup>(1)</sup> | 0.98(1)             | 0.49 <sup>(1)</sup> |

| 10        | 62.5 <sup>(1)</sup> | 31.25 <sup>(1)</sup> | 15.63 <sup>(1)</sup> | 7.81 <sup>(1)</sup> | 3.91 <sup>(1)</sup> | 1.95 <sup>(1)</sup> | 0.98 <sup>(1)</sup> | 0.49 <sup>(1)</sup> |

| 20        | 62.5 <sup>(1)</sup> | 31.25 <sup>(1)</sup> | 15.63 <sup>(1)</sup> | 7.81 <sup>(1)</sup> | 3.91 <sup>(1)</sup> | 1.95 <sup>(1)</sup> | 0.98 <sup>(1)</sup> | 0.55                |

| 40        | 62.5 <sup>(1)</sup> | 31.25 <sup>(1)</sup> | 15.63 <sup>(1)</sup> | 7.81 <sup>(1)</sup> | 3.91 <sup>(1)</sup> | 1.95 <sup>(1)</sup> | 0.98 <sup>(1)</sup> | 0.75                |

| 80        | 62.5 <sup>(1)</sup> | 31.25 <sup>(1)</sup> | 15.63 <sup>(1)</sup> | 7.81 <sup>(1)</sup> | 3.91 <sup>(1)</sup> | 1.95 <sup>(1)</sup> | 1.09                | 0.98                |

| 160       | 62.5 <sup>(1)</sup> | 31.25 <sup>(1)</sup> | 15.63 <sup>(1)</sup> | 7.81 <sup>(1)</sup> | 3.91 <sup>(1)</sup> | 1.95 <sup>(1)</sup> | 1.88                | 1.57                |

| 320       | 62.5 <sup>(1)</sup> | 35.3                 | 17.52                | 8.86                | 4.35                | 3.03                | 2.44                | 2.34                |

| 640       | 93.06               | 45.2                 | 18.73                | 12.97               | 6.51                | 4.2                 | 3.69                | 3.5                 |

| 1000      | 284.59              | 129.77               | 61.3                 | 33.04               | 16.82               | 9.08                | 5.42                | 4.65                |

| 2000      | 273.39              | 130.68               | 67.13                | 36.16               | 19.22               | 9.87                | 6.93                | 6.48                |

<sup>(1)</sup> Peak-to-peak noise rounded up to 1 LSB.

Table 2. Effective Number of Bits From Peak-to-Peak Noise At  $V_{REF}$  = 2.048 V, AVDD = 5 V, AVSS = 0 V

| DATA RATE |      | PGA SETTING |      |      |      |      |      |      |

|-----------|------|-------------|------|------|------|------|------|------|

| (SPS)     | 1    | 2           | 4    | 8    | 16   | 32   | 64   | 128  |

| 5         | 16   | 16          | 16   | 16   | 16   | 16   | 16   | 16   |

| 10        | 16   | 16          | 16   | 16   | 16   | 16   | 16   | 16   |

| 20        | 16   | 16          | 16   | 16   | 16   | 16   | 16   | 15.8 |

| 40        | 16   | 16          | 16   | 16   | 16   | 16   | 16   | 15.4 |

| 80        | 16   | 16          | 16   | 16   | 16   | 16   | 15.8 | 15   |

| 160       | 16   | 16          | 16   | 16   | 16   | 16   | 15.1 | 14.3 |

| 320       | 16   | 15.8        | 15.8 | 15.8 | 15.8 | 15.4 | 14.7 | 13.7 |

| 640       | 15.4 | 15.5        | 15.7 | 15.3 | 15.3 | 14.9 | 14.1 | 13.2 |

| 1000      | 13.8 | 13.9        | 14   | 13.9 | 13.9 | 13.8 | 13.5 | 12.7 |

| 2000      | 13.9 | 13.9        | 13.9 | 13.8 | 13.7 | 13.7 | 13.2 | 12.3 |

# 8 Detailed Description

#### 8.1 Overview

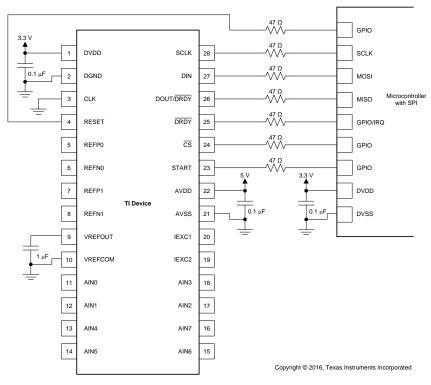

The ADS1148-Q1 includes a low-noise, high-input impedance programmable gain amplifier (PGA), a delta-sigma ( $\Delta\Sigma$ ) analog-to-digital converter (ADC) with an adjustable single-cycle settling digital filter, an internal oscillator, and an SPI-compatible serial interface.

The ADS1148-Q1 also includes a flexible input multiplexer with system monitoring capability and general-purpose I/O settings, a low-drift voltage reference, and two matched current sources for sensor excitation. The *Functional Block Diagram* section shows the various functions incorporated into ADS1148-Q1.

# 8.2 Functional Block Diagram

Copyright © 2016, Texas Instruments Incorporated

# 8.3 Feature Description

# 8.3.1 ADC Input and Multiplexer

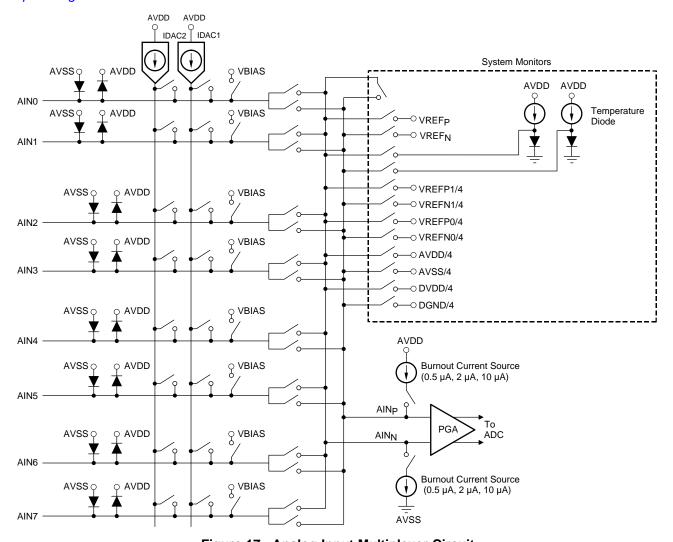

The ADC measures the input signal through the onboard PGA. All analog inputs are connected to the internal AIN<sub>P</sub> or AIN<sub>N</sub> analog inputs through the analog multiplexer. Figure 17 shows a block diagram of the analog input multiplexer.

The input multiplexer connects to eight analog inputs. Any analog input pin can be selected as the positive input or negative input through the MUX0 register. The multiplexer also allows the on-chip excitation current and bias voltage to be selected to a specific channel.

Through the input multiplexer, the ambient temperature (internal temperature sensor), AVDD, DVDD, and the external reference can all be selected for measurement. See the System Monitor section for more details.

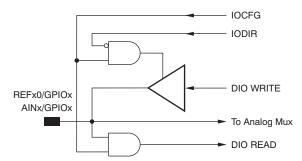

The analog inputs can also be configured as general-purpose inputs and outputs (GPIOs). See the General-Purpose Digital I/O section for more details.

Figure 17. Analog Input Multiplexer Circuit

Product Folder Links: ADS1148-Q1

## **Feature Description (continued)**

ESD diodes protect the ADC inputs. To prevent these diodes from turning on, make sure the voltages on the input pins do not go below AVSS by more than 100 mV, and do not exceed AVDD by more than 100 mV, as shown in Equation 2. Note that the same caution is true if the inputs are configured to be GPIOs.

$$AVSS - 100 \text{ mV} < V_{\text{(AINX)}} < AVDD + 100 \text{ mV}$$

(2)

#### 8.3.2 Low-Noise PGA

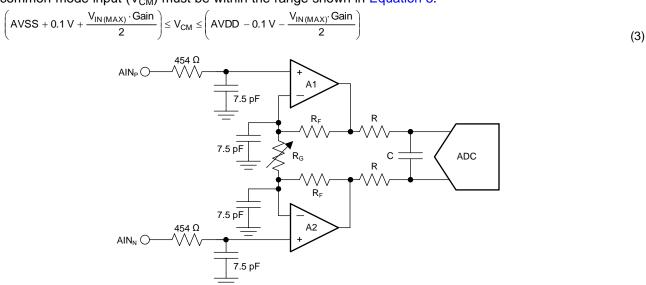

The ADS1148-Q1 features a low-drift, low-noise, high input impedance programmable gain amplifier (PGA). The PGA can be set to gains of 1, 2, 4, 8, 16, 32, 64, or 128 by the SYS0register. Figure 18 shows a simplified diagram of the PGA.

The PGA consists of two chopper-stabilized amplifiers (A1 and A2) and a resistor feedback network that sets the gain of the PGA. The PGA input is equipped with an electromagnetic interference (EMI) filter, as shown in Figure 18. As with any PGA, ensure that the input voltage stays within the specified common-mode input range. The common-mode input (V<sub>CM</sub>) must be within the range shown in Equation 3.

Figure 18. Simplified Diagram of the PGA

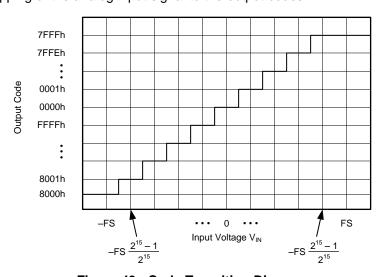

Gain is changed inside the device using a variable resistor, R<sub>G</sub>. The differential full-scale input voltage range (FSR) of the PGA is defined by the gain setting and the reference voltage used, as shown in Equation 4.

$$FSR = \pm V_{REF} / Gain$$

(4)

Table 3 shows the corresponding full-scale input ranges when using the internal 2.048-V reference.

Table 3. PGA Full-Scale Range

| PGA GAIN SETTING | FSR      |

|------------------|----------|

| 1                | ±2.048 V |

| 2                | ±1.024 V |

| 4                | ±0.512 V |

| 8                | ±0.256 V |

| 16               | ±0.128 V |

| 32               | ±0.064 V |

| 64               | ±0.032 V |

| 128              | ±0.016 V |

#### 8.3.2.1 PGA Common-Mode Voltage Requirements

To stay within the linear operating range of the PGA, the input signals must meet certain requirements that are discussed in this section.

The outputs of both amplifiers (A1 and A2) in Figure 18 cannot swing closer to the supplies (AVSS and AVDD) than 100 mV. If the outputs  $OUT_P$  and  $OUT_N$  are driven to within 100 mV of the supply rails, the amplifiers saturate and consequently become nonlinear. To prevent this nonlinear operating condition, the output voltages must meet Equation 5.

$$AVSS + 0.1 V \le V_{(OUTN)}, V_{(OUTP)} \le AVDD - 0.1 V$$

(5)

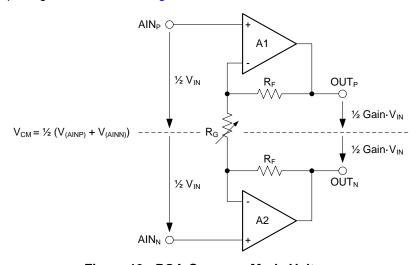

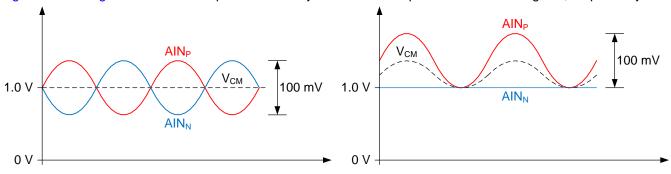

Translating the requirements of Equation 5 into requirements referred to the PGA inputs  $(AIN_P \text{ and } AIN_N)$  is beneficial because there is no direct access to the outputs of the PGA. The PGA employs a symmetrical design; therefore, the common-mode voltage at the output of the PGA can be assumed to be the same as the common-mode voltage of the input signal, as shown in Figure 19.

Figure 19. PGA Common-Mode Voltage

The common-mode voltage is calculated using Equation 6.

$$V_{CM} = \frac{1}{2} \left( V_{(AINP)} + V_{(AINN)} \right) = \frac{1}{2} \left( V_{(OUTP)} + V_{(OUTN)} \right) \tag{6}$$

The voltages at the PGA inputs (AIN<sub>P</sub> and AIN<sub>N</sub>) can be expressed as Equation 7 and Equation 8.

$$V_{(AINP)} = V_{CM} + \frac{1}{2} V_{IN} \tag{7}$$

$$V_{(AINN)} = V_{CM} - \frac{1}{2} V_{IN} \tag{8}$$

The output voltages ( $V_{(OUTP)}$  and  $V_{(OUTN)}$ ) can then be calculated as Equation 9 and Equation 10.

$$V_{(OUTP)} = V_{CM} + \frac{1}{2} Gain \times V_{IN}$$

(9)

$$V_{(O|ITN)} = V_{CM} - \frac{1}{2} Gain \times V_{IN}$$

(10)

The requirements for the output voltages of amplifiers A1 and A2 (Equation 5) can now be translated into requirements for the input common-mode voltage range using Equation 9 and Equation 10, which are given in Equation 11 and Equation 12.

$$V_{CM (MIN)} \ge AVSS + 0.1 \text{ V} + \frac{1}{2} \text{ Gain} \times V_{IN (MAX)}$$

$$\tag{11}$$

$$V_{CM (MAX)} \le AVDD - 0.1 V - \frac{1}{2} Gain \times V_{IN (MAX)}$$

(12)

To calculate the minimum and maximum common-mode voltage limits, the maximum differential input voltage  $(V_{IN\ (MAX)})$  that occurs in the application must be used.  $V_{IN\ (MAX)}$  can be less than the maximum possible full-scale value.

#### 8.3.2.2 PGA Common-Mode Voltage Calculation Example

The following paragraphs explain how to apply Equation 11 and Equation 12 to a hypothetical application. The setup for this example is AVDD = 3.3 V, AVSS = 0 V, and gain = 16, using an external reference of  $V_{REF}$  = 2.5 V. The maximum possible differential input voltage  $V_{IN} = (V_{(AINP)} - V_{(AINN)})$  that can be applied is then limited to the full-scale range of FSR = ±2.5 V / 16 = ±0.156 V. Consequently, Equation 11 and Equation 12 yield an allowed  $V_{CM}$  range of 1.35 V  $\leq V_{CM} \leq 1.95$  V.

If the sensor signal connected to the inputs in this hypothetical application does not make use of the entire full-scale range but is limited to  $V_{IN~(MAX)} = \pm 0.1~V$ , for example, then this reduced input signal amplitude relaxes the  $V_{CM}$  restriction to  $0.9~V \le V_{CM} \le 2.4~V$ .

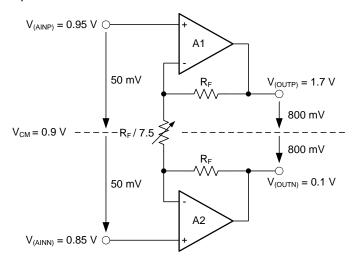

In the case of a fully differential sensor signal, each input (AIN<sub>P</sub>, AIN<sub>N</sub>) can swing up to  $\pm 50$  mV around the common-mode voltage (V<sub>(AINP)</sub> + V<sub>(AINN)</sub>) / 2, which must remain between the limits of 0.9 V and 2.4 V. The output of a symmetrical wheatstone bridge is an example of a fully differential signal. Figure 20 shows a situation where the common-mode voltage of the input signal is at the lowest limit. V<sub>(OUTN)</sub> is exactly at 0.1 V in this case. Any further decrease in common-mode voltage (V<sub>CM</sub>) or increase in differential input voltage (V<sub>IN</sub>) drives V<sub>(OUTN)</sub> below 0.1 V and saturates amplifier A2.

Figure 20. Example Where V<sub>CM</sub> is at the Lowest Limit

In contrast, the signal of a resistance temperature detector (RTD) is of a pseudo-differential nature (if implemented as in the *3-Wire RTD Measurement System* section), where the negative input is held at a constant voltage other than 0 V and only the voltage on the positive input changes. When a pseudo-differential signal must be measured, the negative input in this example must be biased at a voltage from 0.85 V to 2.35 V. The positive input can then swing up to  $V_{IN \ (MAX)} = 100 \ mV$  above the negative input. In this case, the common-mode voltage changes at the same time that the voltage on the positive input changes. That is, when the input signal swings between 0 V  $\leq$  V<sub>IN</sub>  $\leq$  V<sub>IN</sub> (MAX), the common-mode voltage swings between V<sub>(AINN)</sub>  $\leq$  V<sub>CM</sub>  $\leq$  V<sub>(AINN)</sub> +  $\frac{1}{2}$  V<sub>IN</sub> (MAX). Satisfying the common-mode voltage requirements for the maximum input voltage V<sub>IN</sub> (MAX) ensures the requirements are met throughout the entire signal range.

Figure 21 and Figure 22 show examples of both fully differential and pseudo-differential signals, respectively.

Figure 21. Fully Differential Input Signal

Figure 22. Pseudo-Differential Input Signal

#### **NOTE**

With a unipolar power supply, the input range does not extend to the ground. Equation 11 and Equation 12 show the common-mode voltage requirements.

- $V_{CM (MIN)} \ge AVSS + 0.1 V + \frac{1}{2} Gain \times V_{IN (MAX)}$

- $V_{CM (MAX)} \le AVDD 0.1 V \frac{1}{2} Gain \times V_{IN (MAX)}$

#### 8.3.2.3 Analog Input Impedance

The device inputs are buffered through a high-input impedance PGA before reaching the  $\Delta\Sigma$  modulator. For the majority of applications, the input current is minimal and can be neglected. However, because the PGA is chopper-stabilized for noise and offset performance, the input impedance is best described as a small absolute input current. The absolute input current for selected channels is approximately proportional to the selected modulator clock. Table 4 shows the typical values for these currents with a differential voltage coefficient and the corresponding input impedances over data rate.

Table 4. Typical Values for Analog Input Current Over Data Rate<sup>(1)</sup>

| CONDITION                     | ABSOLUTE INPUT CURRENT | EFFECTIVE INPUT IMPEDANCE |

|-------------------------------|------------------------|---------------------------|

| DR = 5 SPS, 10 SPS, 20 SPS    | ± (0.5 nA + 0.1 nA/V)  | 5000 MΩ                   |

| DR = 40 SPS, 80 SPS, 160 SPS  | ± (2 nA + 0.5 nA/V)    | 1200 MΩ                   |

| DR = 320 SPS, 640 SPS, 1 kSPS | ± (4 nA + 1 nA/V)      | 600 MΩ                    |

| DR = 2 kSPS                   | ± (8 nA + 2 nA/V)      | 300 ΜΩ                    |

<sup>(1)</sup> Input current with  $V_{CM} = 2.5 \text{ V}$ ,  $T_A = 25^{\circ}\text{C}$ , AVDD = 5 V, and AVSS = 0 V.

#### 8.3.3 Clock Source

The device can use either the internal oscillator or an external clock. Connect the CLK pin to DGND before power-on or reset to activate the internal oscillator. Connecting an external clock to the CLK pin at any time deactivates the internal oscillator, with the device then operating on the external clock. After switching to the external clock, the device cannot be switched back to the internal oscillator without cycling the power supplies or resetting the device.

Copyright © 2014–2016, Texas Instruments Incorporated

#### 8.3.4 Modulator

A third-order, delta-sigma modulator is used in the ADS1148-Q1. The modulator converts the analog input voltage into a pulse code modulated (PCM) data stream. To save power, the modulator clock runs from 32 kHz up to 512 kHz for different data rates, as shown in Table 5.

Table 5. Modulator Clock Frequency for Different Data Rates

| DATA RATE<br>(SPS) | MODULATOR RATE (f <sub>MOD</sub> ) <sup>(1)</sup> (kHz) | f <sub>CLK</sub> / f <sub>MOD</sub> |

|--------------------|---------------------------------------------------------|-------------------------------------|

| 5, 10, 20          | 32                                                      | 128                                 |

| 40, 80, 160        | 128                                                     | 32                                  |

| 320, 640, 1000     | 256                                                     | 16                                  |

| 2000               | 512                                                     | 8                                   |

<sup>(1)</sup> When using the internal oscillator or an external 4.096-MHz clock.

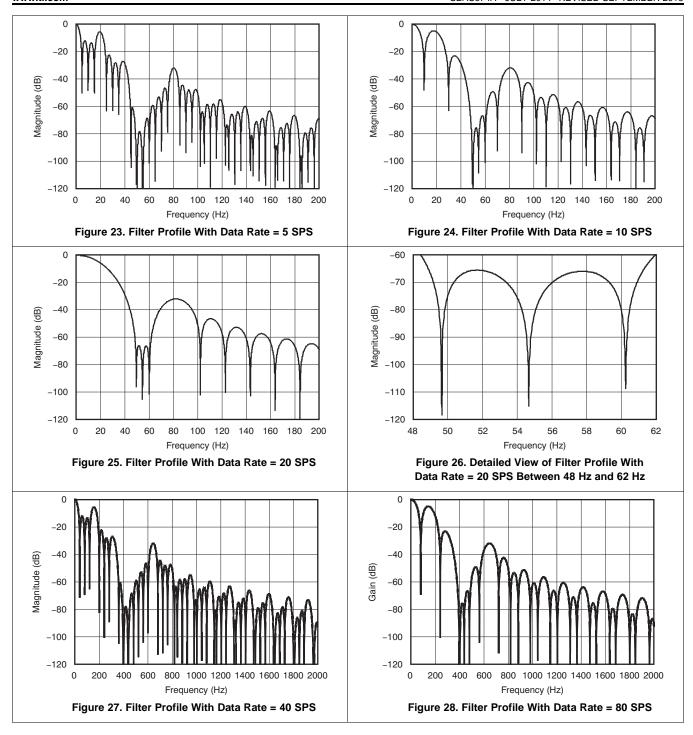

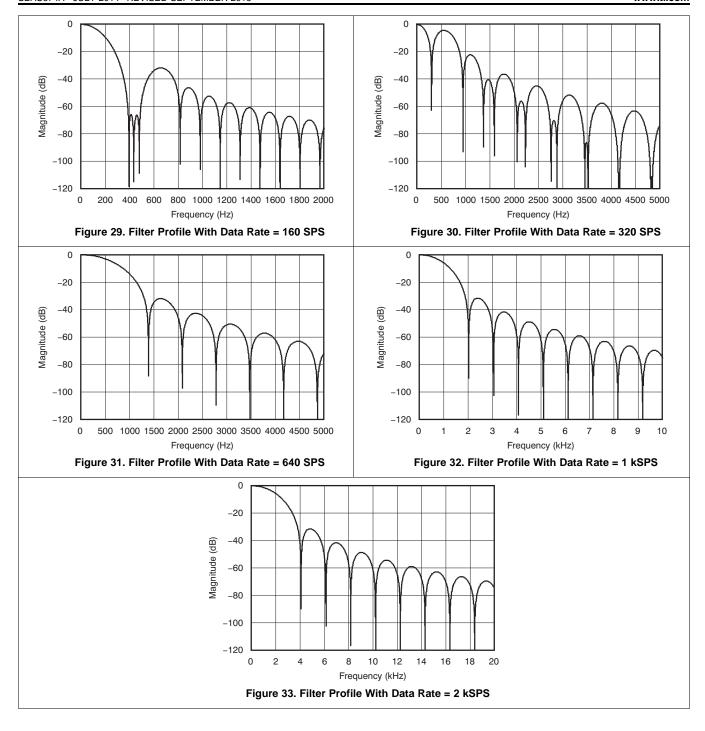

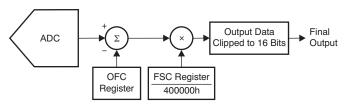

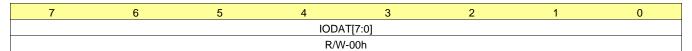

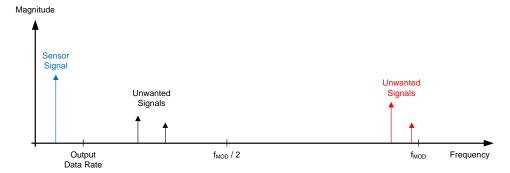

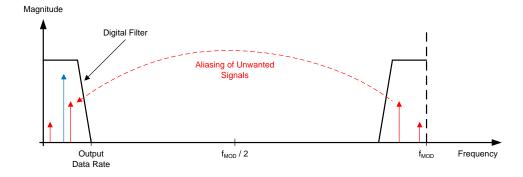

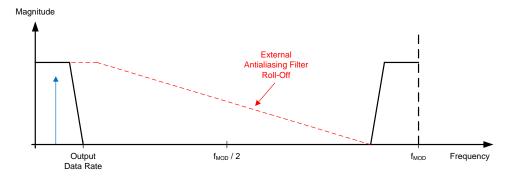

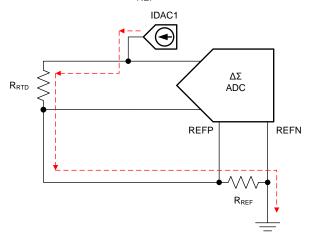

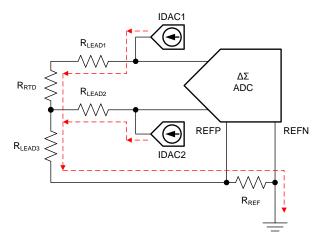

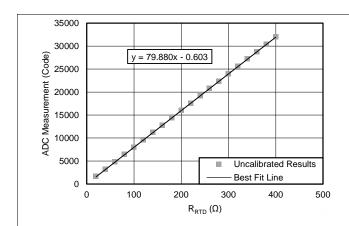

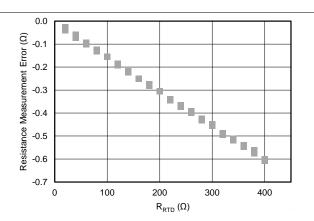

#### 8.3.5 Digital Filter

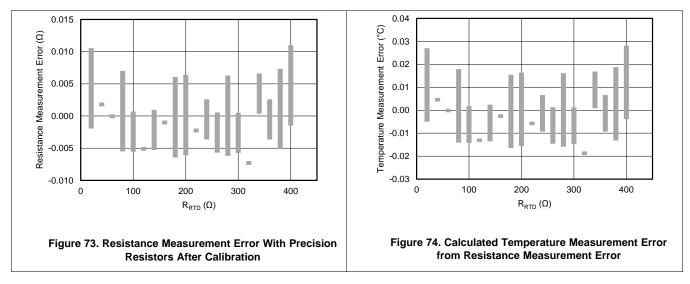

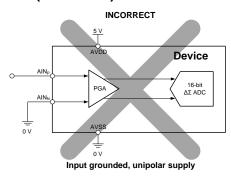

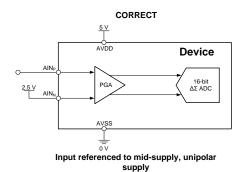

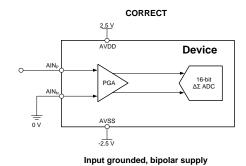

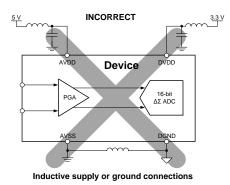

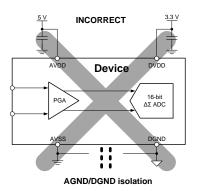

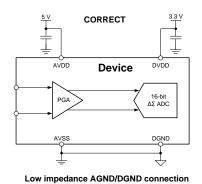

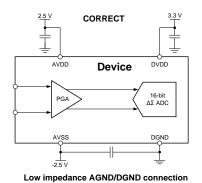

The ADC uses linear-phase finite impulse response (FIR) digital filters that can be adjusted for different output data rates. The digital filter always settles in a single cycle.