Design Guide: TIDA-010973

# 100Mbps Industrial Ethernet Communication Module Reference Design for Multiprotocol Applications

# **Description**

This reference design accelerates development of multiprotocol 100Mbps industrial Ethernet nodes. The design allows engineers to quickly prototype and deploy EtherCAT®, PROFINET®, EtherNet/IP, and Modbus® Transmission Control Protocol (TCP) on AM261x with Integrated Industrial Communication Subsystem (ICSS). The approach cuts hardware spins, simplifies clocking and power, and delivers deterministic, time-synchronized factory automation performance.

#### Resources

TIDA-010973 Design Folder

AM2612, DP83826Al Product Folder

TPS65214, LMK3C0105 Product Folder

#### **Features**

- Supports multiple industrial Ethernet protocols: EtherCAT®, PROFINET® Real-Time (RT) and Isochronous Real-Time (IRT), EtherNet/IP®, and Modbus® TCP

- ICSS enabling software-selectable multiprotocol operation

- Synchronize and latch real-time Ethernet signals for precise timing control

- Flexible Host Port Interface (HPI) for connection to an external application processor or for use with a daughter card

- Effective reference design for reduced bill of materials (BOM) and compact form factor

- Electromagnetic Compatibility (EMC) and Electromagnetic Interference (EMI) compatible PCB layout

# **Applications**

- · Communication module

- Stand-alone remote IO

- · Robot communication module

- · Mobile robot communication module

- CPU (PLC controller)

# 1 System Description

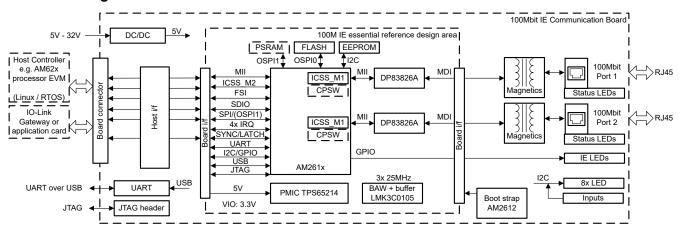

This reference design implements a two-port 100BASE-TX industrial Ethernet communication module based on the AM261x Arm® Cortex®-R microcontroller. The design provides a compact and flexible platform for adding real-time industrial Ethernet connectivity to embedded systems that require protocols such as EtherCAT, PROFINET RT, PROFINET IRT, EtherNet/IP, and Modbus TCP.

The design integrates two Ethernet ports, 11 user-controllable status LEDs, a rotary switch, DIP switch, and a user push button for configuration and diagnostics.

A Host Port Interface (HPI) enables connection to an external microprocessor for system integration and can be used to attach a function add-on card, such as an 8-port IO-Link controller.

With the optimized layout, BOM efficiency, and EMC-compliant design, this module serves as a ready-to-use building block for developing scalable, multiprotocol industrial communication systems.

## 1.1 Terminology

ICSS Industrial Communication Subsystem

PRU Programmable Real-Time Unit

SKU Stock Keeping Units

# 2 System Overview

Industrial automation equipment manufacturers face several challenges when designing networked devices for global markets. This reference design demonstrates how the AM261x microcontroller provides a unified, scalable approach for multiprotocol industrial Ethernet communication.

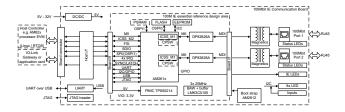

## 2.1 Block Diagram

www.ti.com System Overview

## 2.2 Design Considerations

### 2.2.1 Industrial Protocol Fragmentation

To sell equipment globally, vendors must support multiple industrial Ethernet standards such as EtherCAT, PROFINET RT, PROFINET IRT, EtherNet/IP and Modbus TCP.

**Challenge:** Developing and maintaining separate hardware and software implementations for each protocol significantly increases engineering cost and time-to-market. Additionally, certification and maintenance efforts multiply with each product variant.

**Solution:** The AM261x provides a single hardware and software platform supporting multiple industrial Ethernet protocols. Protocols can be switched through software by loading different firmware images onto the integrated Industrial Communication Subsystem (ICSS).

The unified platform reduces design complexity, accelerates certification using pre-certified protocol stacks from the TI Industrial SDK, and minimizes the number of SKU variants.

#### 2.2.2 Real-Time Performance and Determinism

Industrial Ethernet protocols impose different timing constraints for cycle times, jitter, and synchronization accuracy. EtherCAT and PROFINET IRT require sub-microsecond synchronization. EtherNet/IP and Modbus TCP use standard TCP/IP communication but often need to coexist with deterministic real-time traffic.

**Challenge:** General-purpose microcontrollers and Linux-based processors often cannot provide deterministic real-time performance under varying CPU load conditions.

**Solution:** The AM261x integrates a dedicated PRU-based Industrial Communication Subsystem (ICSS) that provides deterministic, low-latency response independent of the host CPU workload. This design enables precise real-time communication for all supported industrial Ethernet standards.

## 2.2.3 Component Cost and PCB Space Constraints

Many current designs require a high-performance microprocessor unit (MPU) for the application layer plus an external Application-Specific IC (ASIC), Field-Programmable Gate Array (FPGA), and communication coprocessor for industrial Ethernet.

**Challenge:** Such multi-chip architectures increase BOM cost, power consumption, and printed circuit board (PCB) area.

**Solution:** The AM261x can operate as a standalone microcontroller for industrial Ethernet and as a communication companion subsystem connected to an external MPU through Quad Serial Peripheral Interface (QSPI) target host interface. This design eliminates the need for external FPGAs or ASICs, simplifies PCB layout, and reduces overall system cost.

#### 2.2.4 Protocol Certification and Software Maintenance

Each industrial Ethernet standard has a specific certification process (ETG, PI, ODVA, and so forth). Maintaining certifications across silicon revisions and firmware updates can be time-consuming and costly.

Challenge: Certification failures often occur late in the product development cycle, causing schedule delays.

**Solution:** The TI Industrial SDK for AM261x includes pre-certified protocol stacks and reference examples, reducing certification risk and ongoing maintenance effort.

System Overview Www.ti.com

# 2.3 Highlighted Products

### 2.3.1 AM2612 Microcontroller

The AM2612 is a 500MHz dual-core Arm Cortex-R5F microcontroller designed for real-time control, functional safety, and industrial communication applications. The device integrates two Industrial Communication Subsystems (ICSS) that support a wide range of real-time industrial Ethernet and field communication protocols, including EtherCAT, PROFINET RT, PROFINET IRT, EtherNet/IP, Modbus TCP, and up to eight-port IO-Link controller.

The AM2612 also supports encoder interfaces such as EnDat®, Hiperface DSL®, and BiSS®, along with PWM outputs for precision motor control.

Communication interfaces include CAN-FD, Ethernet, OSPI, SPI, I2C, UART, ePWM, eCAP, and eQEP.

In this reference design, the AM2612 functions as an industrial Ethernet communication controller or as a gateway between industrial Ethernet and external interfaces such as OSPI or IO-Link.

The AM261x Sitara<sup>™</sup> microcontroller (MCU) family is part of Tl's new-generation real-time microcontroller platform, combining scalable Arm Cortex-R5F performance with advanced safety and security features to meet the complex real-time processing requirements of modern industrial and automotive applications.

#### 2.3.2 DP83826A Ethernet PHY

The DP83826A is a low-latency, low-power, 10/100-Mbps industrial Ethernet PHY optimized for real-time and deterministic communication in industrial systems. The device supports both 10BASE-Te and 100BASE-TX standards and includes hardware bootstraps for fast link-up and rapid link-drop detection (< 10µs).

The device is designed for robust EMC and EMI performance, enabling compact and reliable network implementations.

## Key Features:

- Enhanced EMC performance with integrated filtering circuitry

- IEC 61000-4-2 ESD: ±8V contact, ±15kV air (Criteria A)

- IEC 61000-4-4 EFT: ±4kV at 5kHz, 100kHz (Criteria A)

- · CISPR 22 conducted and radiated emissions Class B

- Fast link-drop detection < 10µs</li>

- Cable reach > 150m

- Integrated voltage-mode line driver integrated terminations on MAC interface

These features make the DP83826A an excellent choice for compact, cost-optimized, and EMC-compliant industrial Ethernet modules.

www.ti.com System Overview

#### 2.3.3 TPS65214 Power Management IC

The TPS65214 represents a flexible Power Management IC (PMIC) featuring three synchronous step-down DC-DC converters and two low-dropout (LDO) regulators. This configuration makes the device an excellent choice for powering system on chips (SoC) and MCUs in industrial systems.

- Output capabilities:

- 1 × 2A buck converter

- 2 × 1A buck converters

- 1 × 300mA LDO

- 1 × 500mA LDO

- Wide operating temperature range: –40°C to +105°C

- · Compact design size with small 470nH inductors and minimal external components

- Configurable through the I<sup>2</sup>C interface, with additional GPIO and multifunction pins for sequencing and power-rail monitoring

The TPS65214 delivers a complete and efficient power approach for the AM2612 and the device peripherals, optimized for industrial temperature range and reliability.

#### 2.3.4 LMK3C0105 Clock Generator

The LMK3C0105 represents a five-output reference-less clock generator built on TI Bulk Acoustic Wave (BAW) technology. The device provides ±25ppm frequency stability without requiring any crystal and external clock reference, simplifying design, and improving reliability.

Key capabilities include:

- · Generates up to five clock outputs, configurable as spread-spectrum (SSC) and non-SSC

- Supports up to three independent output frequencies simultaneously

- · Each output channel can use an internal Fractional Output Divider (FOD) to generate precise frequencies

- Provides four LVCMOS clock outputs and one REF\_CTRL-selectable LVCMOS output

In this design, the LMK3C0105 provides a precise, low-jitter LVCMOS clock for the AM2612 and Ethernet PHY, providing deterministic timing and synchronization in industrial networks.

# 3 System Design Theory

This section describes the hardware architecture, design considerations, and implementation details of the 100Mbps Industrial Ethernet Communication Module Reference Design. The section covers key hardware components, memory and interface configurations, layout and EMC guidelines, power design, and debug connectivity.

# 3.1 Key Requirements and Design Considerations

The industrial Ethernet reference design integrates a set of components optimized for low BOM cost, compact PCB area, and robust real-time Ethernet performance.

Reference Design Components:

- AM2612 500MHz, dual-core Arm® Cortex®-R5F MCU with real-time control, safety, and security

- DP83826AI Low-latency 10/100-Mbps Ethernet PHY optimized for EtherCAT® and industrial-temperature operation

- TPS65214 Power Management IC (PMIC) with integrated DC/DC converters and LDOs for MCU and peripherals

- LMK3C0105 Five-output reference-less clock generator using Bulk Acoustic Wave (BAW) technology

- OSPI flash (256Mb) Non-volatile memory for application and protocol software images

Optional Components (application dependent):

- I<sup>2</sup>C EEPROM (1Mb) Stores user configuration or factory calibration data

- OSPI PSRAM (128Mb, OPI 8 x, DDR 200MHz) Optional external memory for large user applications

#### 3.1.1 Operating Modes

The reference design can be configured in two system modes:

- 1. **Standalone Mode:** The user application and the industrial Ethernet stack run on the same AM2612 device. Process data is exchanged internally through shared RAM or PRU-ICSS memory. The fast internal bus connection enables very fast process data exchange between the industrial Ethernet stack and the user application.

- An excellent choice for compact, cost-optimized devices such as remote I/O or sensors.

- 2. **Companion Mode (Host Interface Mode):** The AM2612 acts as a communication companion connected to an external MPU through a Host Port Interface (HPI) such as SPI, QSPI, or FSI. Sideband signals (For example, interrupts, SYNC, and LATCH) provide real-time coordination between the external MPU and the industrial Ethernet reference design.

- Appropriate for mid- and high-performance PLCs, servo drives, or gateway modules requiring higherlevel control on a separate processor.

## 3.2 Software Architecture and Boot Flow

At start-up, the industrial protocol stack and user application load from external OSPI flash into the internal RAM of the AM2612 MCU, where execution takes place.

The TI Industrial Communication SDK protocol examples operate entirely from internal RAM. If additional memory is required, use one of the following:

AM2612 can extend memory using external OSPI PSRAM

Operate in execute-in-place (XiP) mode directly from OSPI flash, reducing boot-time and RAM usage.

Supported protocols include EtherCAT, PROFINET RT, PROFINET IRT, EtherNet/IP, and Modbus TCP, all running on top of the TI Industrial SDK.

#### 3.3 Industrial Communication Subsystem (ICSS)

The ICSS, which represents integrated peripheral inside the AM2612 MCU, runs the industrial Ethernet protocol stack. The ICSS runs real-time critical applications like the MAC layer of the industrial Ethernet protocols

www.ti.com System Design Theory

and provides high flexibility as the component loads firmware of the Industrial Ethernet MAC during runtime. Therefore, the firmware can be changed during the runtime to enable multiprotocol industrial Ethernet.

#### Note

The integrated three-port Common Platform Ethernet Switch (CPSW) cannot be used for industrial Ethernet protocols.

However, ICSS and CPSW share the same MII signal pins with AM2612, allowing the application to dynamically multiplex between ICSS and CPSW modes if standard Ethernet functionality is required. Note that ICSS and CPSW use different Management Data IO (MDIO) and Management Data Clock (MDC) peripheral intellectual property (IP) inside AM2612. The reference design selects either the MDIO or the MDC from ICSS or from CPSW for this purpose of switching the Ethernet peripheral.

## 3.4 Clocking and Synchronization

The LMK3C0105 generates a common 25MHz clock for both Ethernet PHYs and the MCU.

For protocols such as EtherCAT, a shared and phase-aligned clock source is required to provide deterministic real-time packet forwarding and prevent TX-FIFO under- or over-runs. See the *How and Why to Use the DP83826 for EtherCAT® Applications* application note.

The industrial Ethernet interface also supports SYNC and LATCH timing signals for real-time synchronization tasks.

#### 3.5 Power Supply

#### 3.5.1 Multiprotocol Industrial Ethernet Subsystem Power Supply

The multiprotocol industrial Ethernet subsystem operates from a single 5V input. All required voltage rails are generated by the TPS65214 PMIC, which powers the MCU, Ethernet PHYs, memory, and supporting logic. The voltage rails that the PMIC generates are 1.25V for the MCU core, 1.8V, and 3.3V.

#### 3.5.2 System Power Supply

The main power input accepts a wide operation voltage between 5V to 32V through a barrel-jack connector J1.

- Reverse-polarity protection: LM74700-Q1 effective diode controller

- ESD protection: TVS3301 and common-mode choke

- Main converter: TLVM13630 buck-boost module generating 5V for the subsystem

- Alternate power path: USB-C port with ORing using a second LM74700-Q1 to VIN

This configuration provides robust industrial power input, flexible supply options, and compliance with IEC 61000-4-xx surge and ESD immunity standards.

## 3.6 Real-Time Ethernet Media Independent Interface (MII)

For 100Mbps industrial Ethernet, Media Independent Interface (MII) is recommended for minimum latency on the Ethernet signal path. The ICSS supports MII natively; RGMII is not supported in this implementation. MII provides lower transmit and receive latency than RGMII. Especially for networks with long daisy chain devices in the network, latency accumulates. Therefore, MII is the preferred interface when using industrial Ethernet.

The ICSS-to-PHY signals must follow length-matching and impedance-control guidelines from the *AM261x* Sitara™ Microcontrollers and *DP83826Ax Deterministic*, Low-Latency, Low-Power, 10/100 Mbps, Industrial Ethernet PHY datasheets.

System Design Theory www.ti.com

Table 3-1. ICSSG0 MII MUX Mode: Port 0 and Port 1

| PORT NUMBER  | ZFG BALL NUMBER | BALL NAME | MUX MODE        | ICSS_GPCFG0_REG[29-26] PR <k>_PRU0_GP_MUX_SEL = 2 (MII MODE)</k> | NOTES                                         |

|--------------|-----------------|-----------|-----------------|------------------------------------------------------------------|-----------------------------------------------|

| Port 0       | B20             | GPIO113   | PR0_PRU1_GPIO16 | pr <k>_mii_mt0_clk</k>                                           |                                               |

| Port 0       | E18             | GPIO114   | PR0_PRU1_GPIO15 | pr <k>_mii0_txen</k>                                             |                                               |

| Port 0       | F17             | GPIO115   | PR0_PRU1_GPIO11 | pr <k>_mii0_txd[0]</k>                                           |                                               |

| Port 0       | D20             | GPIO116   | PR0_PRU1_GPIO12 | pr <k>_mii0_txd[1]</k>                                           |                                               |

| Port 0       | C20             | GPIO117   | PR0_PRU1_GPIO13 | pr <k>_mii0_txd[2]</k>                                           |                                               |

| Port 0       | D19             | GPIO118   | PR0_PRU1_GPIO14 | pr <k>_mii0_txd[3]</k>                                           |                                               |

| Port 0       | N20             | GPIO91    | PR0_PRU0_GPI06  | pr <k>_mii_mr0_clk</k>                                           |                                               |

| Port 0       | L20             | GPIO92    | PR0_PRU0_GPIO4  | pr <k>_mii0_rxdv</k>                                             |                                               |

| Port 0       | N17             | GPIO93    | PR0_PRU0_GPI00  | pr <k>_mii0_rxd[0]</k>                                           |                                               |

| Port 0       | N19             | GPIO94    | PR0_PRU0_GPI01  | pr <k>_mii0_rxd[1]</k>                                           |                                               |

| Port 0       | M18             | GPIO95    | PR0_PRU0_GPI02  | pr <k>_mii0_rxd[2]</k>                                           |                                               |

| Port 0       | M20             | GPIO96    | PR0_PRU0_GPIO3  | pr <k>_mii0_rxd[3]</k>                                           |                                               |

| Port 0       | J18             | GPIO90    | PR0_PRU0_GPI08  | pr <k>_mii0_rxlink</k>                                           |                                               |

| Port 0       | K19             | GPIO87    | PR0_PRU0_GPIO5  | pr <k>_mii0_rxer</k>                                             |                                               |

| Port 0       | J19             | GPIO88    | PR0_PRU0_GPIO9  | pr <k>_mii0_col</k>                                              | Optional signal, for half-<br>duplex Ethernet |

| Port 0       | J20             | GPIO89    | PR0_PRU0_GPIO10 | pr <k>_mii0_crs</k>                                              | Optional signal, for half-<br>duplex Ethernet |

| Port 0       | A10             | GPIO22    | GPIO22          | GPIO22                                                           | Optional, PHY0 Interrupt                      |

| Port 1       | M19             | GPIO97    | PR0_PRU0_GPIO16 | pr <k>_mii_mt1_clk</k>                                           |                                               |

| Port 1       | P18             | GPIO98    | PR0_PRU0_GPIO15 | pr <k>_mii1_txen</k>                                             |                                               |

| Port 1       | P20             | GPIO99    | PR0_PRU0_GPIO11 | pr <k>_mii1_txd[0]</k>                                           |                                               |

| Port 1       | P19             | GPIO100   | PR0_PRU0_GPIO12 | pr <k>_mii1_txd[1]</k>                                           |                                               |

| Port 1       | K20             | GPIO101   | PR0_PRU0_GPIO13 | pr <k>_mii1_txd[2]</k>                                           |                                               |

| Port 1       | L19             | GPIO102   | PR0_PRU0_GPIO14 | pr <k>_mii1_txd[3]</k>                                           |                                               |

| Port 1       | F19             | GPIO107   | PR0_PRU1_GPI06  | pr <k>_mii_mr1_clk</k>                                           |                                               |

| Port 1       | G19             | GPIO108   | PR0_PRU1_GPIO4  | pr <k>_mii1_rxdv</k>                                             |                                               |

| Port 1       | H20             | GPIO109   | PR0_PRU1_GPI00  | pr <k>_mii1_rxd[0]</k>                                           |                                               |

| Port 1       | H19             | GPIO110   | PR0_PRU1_GPI01  | pr <k>_mii1_rxd[1]</k>                                           |                                               |

| Port 1       | H17             | GPIO111   | PR0_PRU1_GPI02  | pr <k>_mii1_rxd[2]</k>                                           |                                               |

| Port 1       | G20             | GPIO112   | PR0_PRU1_GPIO3  | pr <k>_mii1_rxd[3]</k>                                           |                                               |

| Port 1       | G18             | GPIO106   | PR0_PRU1_GPI08  | pr <k>_mii1_rxlink</k>                                           |                                               |

| Port 1       | F20             | GPIO103   | PR0_PRU1_GPI05  | pr <k>_mii1_rxer</k>                                             |                                               |

| Port 1       | E20             | GPIO104   | PR0_PRU1_GPIO9  | pr <k>_mii1_col</k>                                              | Optional signal, for half-<br>duplex Ethernet |

| Port 1       | E19             | GPIO105   | PR0_PRU1_GPIO10 | pr <k>_mii1_crs</k>                                              | Optional signal, for half-<br>duplex Ethernet |

| Port 1       | B4              | GPOP83    | GPOP83          | GPOP83                                                           | Optional, PHY1 interrupt                      |

| Port 0 and 1 | R19             | GPIO85    | PR0_MDIO0_MDIO  | PR0_MDIO0_MDIO                                                   |                                               |

| Port 0 and 1 | R20             | GPIO85    | PR0_MDIO0_MDC   | PR0_MDIO0_MDC                                                    |                                               |

## 3.6.1 SYNC/LATCH Pins for Real-Time Tasks

The reference design includes dedicated SYNC and LATCH signals to align industrial Ethernet timing with I/O and process-data capture.

Table 3-2. SYNC and LATCH Pins for Real-Time Tasks

| PORT NUMBER | ZFG BALL<br>NUMBER | BALL NAME | MUX MODE               | ICSS_GPCFG0_REG[29-26] PR <k>_<br/>PRU0_GP_MUX_SEL = 2 (MII MODE)</k> | NOTES                          |

|-------------|--------------------|-----------|------------------------|-----------------------------------------------------------------------|--------------------------------|

| SYNC0       | C18                | GPIO119   | PR0_IEP0_EDC_SYNC_OUT0 | PR0_IEP0_EDC_SYNC_OUT0                                                |                                |

| SYNC1       | T19                | GPIO40    | PR0_IEP0_EDC_SYNC_OUT1 | PR0_IEP0_EDC_SYNC_OUT1                                                |                                |

| LATCH0      | A14                | GPIO137   | GPIO137                | GPIO137                                                               | Any GPIO can be MUXed to LATCH |

| LATCH1      | T19                | GPIO122   | GPIO122                | GPIO122                                                               | Any GPIO can be MUXed to LATCH |

www.ti.com System Design Theory

#### 3.6.2 Layout Considerations

To provide effective performance, particularly EMC and EMI immunity and signal integrity for reliable 100Mbps industrial Ethernet communication, this reference design utilizes an eight-layer PCB stack-up.

**Table 3-3. Layout Considerations**

| LAYER | FUNCTION                          |

|-------|-----------------------------------|

| 1     | Top signal and component layer    |

| 2     | Ground reference (GND)            |

| 3     | Signal routing                    |

| 4     | Ground reference (GND)            |

| 5     | Power distribution                |

| 6     | Signal routing                    |

| 7     | Ground reference (GND)            |

| 8     | Bottom signal and component layer |

#### 3.6.2.1 Layout Guidelines

| Component<br>Datasheet<br>Compliance   | Strictly adhere to the layout recommendations outlined in the datasheets for all components, particularly the AM261x microcontroller and DP83826A PHY.                                                                                          |

|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Decoupling and<br>Bypass               | Position bypass and decoupling capacitors <i>directly</i> beneath the AM261x microcontroller as close as possible to the power pins. Use capacitors with appropriate capacitance values to minimize high-frequency noise.                       |

| Short Vias                             | Employ short vias to connect decoupling capacitors to both the ground plane and the power supply planes, reducing inductance and improving signal integrity.                                                                                    |

| Earth-Ground<br>Planes                 | Implement robust earth-ground planes surrounding all Ethernet connectors and the PHY circuitry. This helps to shield against common-mode noise.                                                                                                 |

| Common-Mode<br>Chokes and<br>Isolation | Integrate common-mode chokes between Ethernet connectors and the PHY circuitry. Crucially, maintain a physical separation (isolation) between the digital ground plane and the chassis earth ground to mitigate ground bounce and noise issues. |

| Signal Trace Routing                   | Route signal traces with controlled impedance, minimizing trace lengths and using appropriate trace widths to maintain signal integrity across the 100Mbps bandwidth.                                                                           |

## 3.6.3 EMI and EMC Considerations

Minimizing electromagnetic interference (EMI) and providing compliance with relevant EMI and EMC standards are paramount for reliable operation. This reference design incorporates the following measures:

| Robust Earth<br>Grounding                  | Establish robust earth ground connections directly beneath all Ethernet connectors and power components to provide a low-impedance return path for conducted emissions.                                                                                                                 |

|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Digital Ground<br>Isolation                | Implement RC or ferrite-based coupling networks between the digital ground plane and the chassis earth ground. This isolation prevents ground bounce and minimizes the coupling of digital noise into the Ethernet circuitry, aligning with CISPR 22, EN 55022 Class B emission limits. |

| Impedance-<br>Controlled Signal<br>Routing | Design all signal traces with controlled impedance, meticulously matching trace lengths to maintain signal integrity and minimize reflections across the 100Mbps frequency range.                                                                                                       |

| CISPR 22, EN 55022<br>Compliance           | This design is targeted to meet CISPR 22, EN 55022 Class B conducted and radiated emission limits. Proper grounding, shielding, and impedance control are crucial for achieving this compliance.                                                                                        |

System Design Theory Www.ti.com

#### 3.6.4 AM2612 Bootstrap Interface

The bootstrap interface of the AM2612 microcontroller enables various boot modes, providing flexibility for development, debugging, and firmware updates. Table 3-4 describes the supported boot modes.

| Table 3 | -4. Boo | ot Mode | Descri | ptions |

|---------|---------|---------|--------|--------|

|---------|---------|---------|--------|--------|

| BOOT MODE | DESCRIPTION                                                                                                                                                            | TYPICAL USE CASE                           |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| OSPI Boot | Loads the application image from external OSPI flash. This is the primary boot mode for standalone operation.                                                          | Production, standalone applications        |

| UART Boot | Loads the software image through UART, allowing for programming the OSPI flash or recovery in case of errors.                                                          | Development, initial programming, recovery |

| DEV Boot  | Enables debugging using Code Composer Studio (CCS). Requires a configuration script or a pre-loaded null bootloader in OSPI flash to initialize basic system settings. | Debugging with CCS                         |

| DFU Boot  | Facilitates firmware updates through USB using the DFU bootloader and UniFlash flash programming tool.                                                                 | Firmware updates                           |

For detailed instructions and setup procedures, see the MCU+ SDK Getting Started Guide and the EVM Setup section.

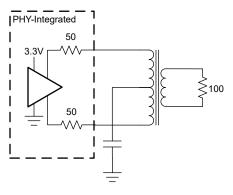

## 3.6.5 RJ45 Ethernet Interface

This reference design incorporates RJ45 connectors with integrated magnetics from Würth Elektronik to facilitate robust and reliable 100Mbps Ethernet communication.

The DP83826A PHY requires voltage-mode magnetics for effective operation. Critically, the center taps of the magnetics are connected individually to ground and not shorted together or connected to VCC. This voltage-mode configuration offers several advantages over current-mode magnetics, including reduced bill of materials (BOM), lower power dissipation, and improved radio frequency (RF) performance.

The A-version PHY is recommended for achieving the lowest EtherCAT latency and effective electromagnetic interference (EMI) performance.

Figure 3-1. Voltage Mode

#### 3.6.6 Industrial User Interface

The industrial user interface (IUI) provides essential configurability and diagnostic capabilities during development and compliance testing. The IUI enables users to monitor system status and adjust settings for effective performance. The IUI typically includes the following elements:

**Protocol Status LEDs** These LEDs – such as EtherCAT RUN/ERR indicators – provide immediate visual feedback on the status of the Ethernet communication.

**8-bit User LED Array** This array maps process-data bytes from the Programmable Logic Controller (PLC) to

visual indicators, allowing for a quick overview of key data values.

**4-bit DIP Switch** This switch enables the selection of configuration options or operating modes, offering

flexibility for different application needs.

www.ti.com System Design Theory

16-Position Rotary

**Switch**

This switch is used to set device or network addresses, facilitating precise

configuration and network integration.

**User Push Button**

The push button can trigger defined test or interaction events – for example, during

plug-fest validation or diagnostic routines.

## 3.6.7 Programming and Debugging Options

The reference design with AM2612 supports two primary programming and debugging options, and only one can be enabled at a time. The selection is made using jumper J17.

Onboard XDS110

When jumper J17 is set to the *XDS110* position, the integrated XDS110 JTAG debugger is enabled. This provides a plug-and-play connection with Code Composer Studio (CCS),

simplifying the development process.

20-pin JTAG Header

Setting jumper J17 to the *20-pin JTAG header* position enables the external 20-pin JTAG header. This allows for connection with external emulators or production test equipment,

providing flexibility for diverse debugging and validation scenarios.

#### 3.6.8 USB 2.0 Interface

The reference design incorporates two USB connectors to provide flexible connectivity options.

USB Type-AB Connector

This connector connects to the USB 2.0 port of the AM2612, supporting Host, Device, and Dual-Role operation – enabling versatile connectivity for development and testing.

USB Type-C® Connector

This connector provides an optional power input path. USB Type-C includes a

Configuration Channel (CC) logic controller that negotiates up to 5V, 3A from a USB-C

power adapter, providing reliable power delivery.

# 4 Design and Documentation Support

# 4.1 Design Files

#### 4.1.1 Schematics

To download the schematics, see the design files at TIDA-010973.

#### 4.1.2 BOM

To download the bill of materials (BOM), see the design files at TIDA-010973.

#### 4.2 Tools and Software

#### **Tools**

CCSTUDIO Code Composer Studio™ integrated development environment (IDE)

#### **Software**

UNIFLASH UniFlash flash programming tool

## 4.3 Documentation Support

- 1. Texas Instruments, AM261x Sitara™ Microcontrollers Datasheet

- 2. Texas Instruments, DP83826Ax Deterministic, Low-Latency, Low-Power, 10/100 Mbps, Industrial Ethernet PHY Datasheet

- 3. Texas Instruments, TPS65214 Power Management IC with 3 BUCKs and 2 LDOs for Industrial Applications

Datasheet

- 4. Texas Instruments, LMK3C0105 Reference-less 5-LVCMOS-Output Programmable BAW Clock Generator Datasheet

#### 4.4 Support Resources

TI E2E<sup>™</sup> support forums are an engineer's go-to source for fast, verified answers and design help — straight from the experts. Search existing answers or ask your own question to get the quick design help you need.

Linked content is provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

#### **Trademarks**

TI E2E™, Sitara™, and Code Composer Studio™ are trademarks of Texas Instruments.

EtherCAT® is a registered trademark of Beckhoff Automation GmbH.

PROFINET® is a registered trademark of PROFIBUS Nutzerorganisation e.V..

Modbus® is a registered trademark of Schneider Electric USA, Inc.

EtherNet/IP® is a registered trademark of ODVA. INC.

Arm® and Cortex® are registered trademarks of Arm Limited.

EnDat® is a registered trademark of Dr. Johannes Heidenhain GmbH.

Hiperface DSL® is a registered trademark of SICK AG.

BiSS® is a registered trademark of iC-Haus GmbH.

USB Type-C® is a registered trademark of USB Implementers Forum.

All trademarks are the property of their respective owners.

www.ti.com About the Author

## **5 About the Author**

**THOMAS MAUER** serves as a System Engineer in the Industrial Automation Team at Texas Instruments Freising. He develops reference design methods for the industrial segment. Thomas contributes extensive experience in industrial communications like Industrial Ethernet, fieldbuses, and industrial applications. Thomas earned his electrical engineering degree (Dipl. Ing. (FH)) at the University of Applied Sciences in Wiesbaden, Germany.

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you fully indemnify TI and its representatives against any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale, TI's General Quality Guidelines, or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products. Unless TI explicitly designates a product as custom or customer-specified, TI products are standard, catalog, general purpose devices.

TI objects to and rejects any additional or different terms you may propose.

Copyright © 2025, Texas Instruments Incorporated

Last updated 10/2025