Design Guide: TIDA-050088

# Radiation-Tolerant Power Reference Design for the Versal™ AI Edge

# **Description**

This is a radiation-tolerant power architecture reference design for the Versal<sup>™</sup> AI Edge XQRVE2302 from AMD. The Versal Edge is an adoptive system-on-chip (SoC) for space applications which enables high levels of performance in a small form factor. Robust power delivery is critical to fully use this design in a space environment. This power design has multiple devices to power the various rails along with a sequencer to properly order and monitor the rails.

### Resources

TIDA-050088 Design Folder

TPS7H5006-SEP, TPS7H6025-SEP Product Folder

TPS7H1111-SEP, TPS7H4010-SEP Product Folder

TPS73801-SEP, TPS7H3302-SEP Product Folder

TPS7H3014-SP, TPS7H2221-SEP Product Folder

SN54SC6T14-SEP Product Folder

Ask our TI E2E™ support experts

### **Features**

- Radiation-tolerant power architecture by TI

- Designed to power the Versal AI Edge XQRVE2302 from AMD

- Power sequencing and discharge circuitry to sequence up and down all rails

- Core rail capable of 0.8V at 44A

- Regulators for all auxiliary rails along with DDR memory termination

# **Applications**

- Satellite electric power system (EPS)

- · Communications payload

System Description www.ti.com

# 1 System Description

A radiation-tolerant power architecture is described for the Versal<sup>™</sup> Al Edge XQRVE2302 from AMD. The Versal Edge is an adoptive SoC for space applications which enables high levels of performance in a small form factor. Robust power delivery is critical to fully utilize this design in a space environment. This power design uses multiple devices to power the various rails along with a sequencer to properly order and monitor the rails.

# 1.1 Key System Specifications

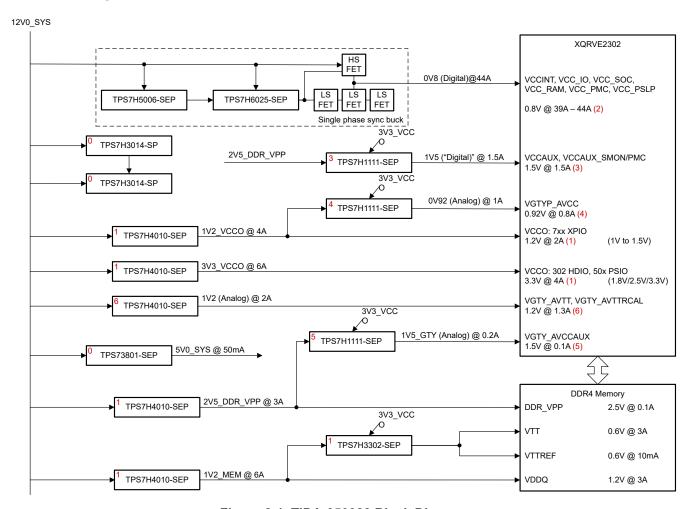

The rails in the system, listed in Table 1-1, are all powered from a 12V input called the 12V0 SYS rail.

Table 1-1. Versal™ Edge and DDR4 Specifications

| Table 1-1. Versal Luge and DDR4 Specifications |              |                                         |                 |                  |                         |                                     |                 |                                              |

|------------------------------------------------|--------------|-----------------------------------------|-----------------|------------------|-------------------------|-------------------------------------|-----------------|----------------------------------------------|

| RAIL<br>SEQUENCE                               | RAIL NAME(1) | VERSAL EDGE PINS,<br>DDR POWERED        | RAIL<br>CURRENT | DC<br>ACCURACY   | AC<br>ACCURACY          | COMBINED<br>ACCURACY <sup>(2)</sup> | LOAD STEP       | PARTS                                        |

| 0(3)                                           | 5V0_SYS      | -                                       | -               | -                | -                       | -                                   | -               | TPS73801-SEP                                 |

|                                                | 3V3_VCCO     | HDIO (bank 302)<br>PSIO (bank 50x)      | 4A              | ±1%              | <b>-5%</b> , <b>+3%</b> | -6%, +4%                            | 4A at 10A/μs    | TPS7H4010-SEP                                |

|                                                | 2V5_DDR_VPP  | DDR_VPP                                 | 0.1A            | -5%, +10%        | -                       | N/A                                 | -               | TPS7H4010-SEP                                |

| 1                                              | 1V2_MEM      | DDR_VDDQ                                | 3A              | ±5%              | -                       | N/A                                 | -               | TPS7H4010-SEP                                |

|                                                | 1V2_VCCO     | XPIO (bank 7xx)                         | 2A              | ±1%              | ±5%                     | ±6%                                 | 2A at 10A/µs    | TPS7H4010-SEP                                |

|                                                | VTT (0V6)    | DDR4_VTT                                | ±3A             | ±5%              | -                       | N/A                                 | -               |                                              |

|                                                | VTTREF (0V6) | DDR4_VTTREF                             | ±10mA           | ±1% to<br>VTTSNS | ±1%                     | N/A                                 | -               | TPS7H3302-SEP                                |

| 2                                              | 0∨80         | VCC_IO VCC_SOC VCC_RAM VCC_PMC VCC_PSLP | 44A             | ±1%              | ±17mV                   | ±3.125%                             | 11A at 200A/μs  | TPS7H5006-SEP<br>TPS7H6025-SEP<br>5xEPC7019G |

| 3                                              | 1V5          | VCCAUX_SMON VCCAUX_PMC                  | 1.5A            | ±1%              | ±2%                     | ±3%                                 | 900mA at 10A/µs | TPS7H1111-SEP                                |

| 4                                              | 0V92         | VGTYP_AVCC                              | 1A              | ±2%              | ±10mV                   | ±3.09%                              | 195mA at 10A/μs | TPS7H1111-SEP                                |

| 5                                              | 1V5_GTY      | VGTY_AVCCAUX                            | 0.1A            | ±2%              | ±10mV                   | ±2.67%                              |                 | TPS7H1111-SEP                                |

| 6                                              | 1V2          | VGTY_AVTT VGTY_AVTTRCAL                 | 1.3A            | ±2%              | ±10mV                   | ±2.83%                              | 330mA at 10A/µs | TPS7H4010-SEP                                |

<sup>(1)</sup> This is the maximum expected current for the FPGA or DDR. See the power tree in Table 2-1 for the designed current which can be greater than this rail current for margin and powering of other loads. As rail requirements can differ by application, consult the AMD Power Design Manager (PDM) and the DDR specifications for additional information.

<sup>(2)</sup> This is the combined AC and DC accuracy that is targeted for the Versal Edge rails.

<sup>(3)</sup> This is not part of the sequencing, the rail comes up as soon as 12V0\_SYS is applied.

www.ti.com System Overview

# 2 System Overview

# 2.1 Block Diagram

Figure 2-1. TIDA-050088 Block Diagram

System Overview www.ti.com

# 2.2 Design Considerations

Using the sequencing and loads described in Table 1-1, a power tree is created as described in Table 2-1.

**Table 2-1. Power Tree Specifications**

| RAIL<br>SEQUENCE | RAIL NAME    | PARTS         | TOTAL RAIL<br>DESIGN<br>CURRENT <sup>(1)</sup> | LOADS                              | EXPECTED<br>MAXIMUM<br>LOAD<br>CURRENTS |

|------------------|--------------|---------------|------------------------------------------------|------------------------------------|-----------------------------------------|

|                  |              | TPS73801-SEP  | 50mA                                           | Sequencers pullups                 | 10mA                                    |

| 0(2)             | 5V0_SYS      |               |                                                | TPS7H2221 input                    | 0.2mA                                   |

|                  |              |               |                                                | SN54SC6T14-SEP input               | 15mA                                    |

|                  |              |               |                                                | Versal HDIO and PSIO               | 4A                                      |

|                  | 3V3_VCCO     | TPS7H4010-SEP | 6A                                             | TPS7H1111-SEP Bias rails           | 81mA                                    |

|                  |              |               |                                                | TPS7H3302-SEP VDD                  | 30mA                                    |

|                  |              | TPS7H4010-SEP |                                                | DDR_VPP                            | 0.1A                                    |

|                  | 2V5_DDR_VPP  |               | 3A                                             | TPS7H1111-SEP input for 1V5        | 1.5A                                    |

|                  |              |               |                                                | TPS7H1111-SEP input for 1V5_GTY    | 0.2A                                    |

| 1                | 1V2_MEM      | TPS7H4010-SEP | 6A                                             | DDR_VDDQ                           | 3A                                      |

|                  |              |               |                                                | TPS7H3302-SEP VLDOIN               | 3A                                      |

|                  | 1V2 VCCO     | TPS7H4010-SEP | 4A                                             | Versal XPIO                        | 2A                                      |

|                  | 102_0000     |               | 4A                                             | TPS7H1111-SEP input for 0V92       | 1A                                      |

|                  | VTT (0V6)    | TPS7H3302-SEP | ±3A                                            | DDR4_VTT                           | ±3A                                     |

|                  | VTTREF (0V6) | 1P5/H3302-SEP | ±10mA                                          | DDR4_VTTREF                        | ±10mA                                   |

|                  |              | TPS7H5006-SEP |                                                |                                    |                                         |

| 2                | 0V80         | TPS7H6025-SEP | 44A                                            | Versal VCCINT and associated rails | 44A                                     |

|                  |              | 5xEPC7019G    |                                                |                                    |                                         |

| 3                | 1V5          | TPS7H1111-SEP | 1.5A                                           | Versal VCCAUX_SMON and VCCAUX_PMC  | 1.5A                                    |

| 4                | 0V92         | TPS7H1111-SEP | 1A                                             | Versal VGTYP_AVCC                  | 0.8A                                    |

| 5                | 1V5_GTY      | TPS7H1111-SEP | 0.2A                                           | Versal VGTY_AVCCAUX                | 0.1A                                    |

| 6                | 1V2          | TPS7H4010-SEP | 2A                                             | Versal VGTY_AVTT and VGTY_AVTTRCAL | 1.3A                                    |

<sup>(1)</sup> This is the maximum design current which can be larger than the expected load currents due to adding design margin.

This design uses radiation-tolerant parts rated to at least a total ionizing dose (TID) of 20krad(Si) and singleevent effects (SEE) of at least 43MeV-cm<sup>2</sup>/mg. These ratings provide an excellent choice for many satellite power systems in Low Earth Orbit (LEO). For higher radiation needs, many of the TI parts have radiationhardened equivalents.

<sup>(2)</sup> This is not part of the sequencing, the rail comes up as soon as 12V0\_SYS is applied.

www.ti.com System Overview

# 2.3 Highlighted Products

The following sections describe key features of the devices utilized for this power design.

#### 2.3.1 TPS7H5006-SEP

The TPS7H5006-SEP is a radiation-tolerant PWM controller which is part of the TPS7H500x-SP and TPS7H500x-SEP family of high-speed controllers. The controllers provide a number of features that are beneficial for the design of DC-DC converter topologies intended for space applications. The controllers have a 0.613V +0.7%, -1% accurate internal reference and configurable switching frequency up to 2MHz. Each device offers programmable slope compensation and soft-start.

The TPS7H500x-SP series can be driven using an external clock through the SYNC pin or by using the internal oscillator at a frequency programmed by the user. The controller family offers the user various options for switching outputs, synchronous rectification capability, dead time (fixed or configurable), leading edge blank time (fixed or configurable), and duty cycle limit.

The TPS7H5006-SEP is used in this design as the buck controller for the high-current, VCCINT rail. The radiation-hardened TPS7H500x-SP is also available in both QMLV ceramic packages and QMLP plastic packages.

#### 2.3.2 TPS7H6025-SEP

The TPS7H6025-SEP is a radiation-tolerant GaN FET gate driver which is designed for high-frequency, high-efficiency, and high-current applications. The TPS7H6025-SEP is part of the TPS7H60x5 series of gate drivers which consists of the TPS7H6005 (200V rating), the TPS7H6015 (60V rating), and the TPS7H6025 (22V rating). The drivers feature adjustable dead-time capability, small 30ns propagation delay, and 5.5ns high-side and low-side matching. These parts also include internal high-side and low-side LDOs, which provide a drive voltage of 5V regardless of supply voltage. The TPS7H60x5 drivers all have split-gate outputs, providing flexibility to adjust the turn-on and turn-off strength of the outputs independently.

The TPS7H60x5 drivers feature two control input modes: independent input mode (IIM) and PWM mode. In IIM each of the outputs is controlled by a dedicated input. In PWM mode, two complementary outputs signals are generated from a single input and the user can adjust the dead time for each edge. The drivers can also be utilized for both half-bridge and dual-low side converter applications.

The TPS7H6025-SEP is used in this design to drive the GaN FETs which are part of the buck regulator for the high-current, VCCINT rail. The radiation-hardened TPS7H60x5-SP is also available in QMLP plastic packages. Additionally, the radiation-hardened TPS7H60x3-SP is available in QMLV ceramic packages.

### 2.3.3 TPS7H1111-SEP

The TPS7H1111 is a radiation-tolerant ultra-low noise, high PSRR, low dropout linear regulator (LDO) optimized for powering radio-frequency (RF) devices. The device is capable of sourcing up to 1.5A over a 0.85V to 7V input range with a 2.2V to 14V bias supply.

The high performance of the device limits power-supply generated phase noise and clock jitter, making this device an excellent choice for powering high-performance ADCs, DACs, VCOs, PLLs, SerDes, and other RF components in satellites. For digital loads (such as FPGAs and DSPs) requiring low-voltage operation, the exceptional accuracy and excellent transient performance provide optimized system perform.

The radiation-tolerant TPS7H1111-SEP is utilized in this design whenever an LDO is required for one of the Versal rails. The radiation-hardened TPS7H1111-SP is also available in both a QMLV ceramic package and QMLP plastic package.

System Overview Www.ti.com

#### 2.3.4 TPS7H4010-SEP

The TPS7H4010-SEP is a radiation-tolerant synchronous buck converter capable of outputting up to 6A of load current from a supply voltage ranging from 3.5V to 32V. The TPS7H4010-SEP provides exceptional efficiency and output accuracy in a very small size. Peak current-mode control is employed.

Additional features such as adjustable switching frequency, synchronization to an external clock, FPWM option, power-good flag, precision enable, adjustable soft start, and tracking provide both flexible and easy-to-use designs for a wide range of applications. Automatic frequency foldback at light load and optional external bias improve efficiency over the entire load range. The device requires few external components and has a pinout designed for simple PCB layout with optimized EMI and thermal performance. Protection features include thermal shutdown, input undervoltage lockout, cycle-by-cycle current limiting, and hiccup short-circuit protection.

#### 2.3.5 TPS73801-SEP

The TPS73801-SEP is a radiation-tolerant low-dropout (LDO) linear regulator optimized for fast transient response. The device can supply 1A of output current with a dropout voltage of 300mV. Operating quiescent current is 1mA and drops to less than 1µA in shutdown.

The TPS73801-SEP regulator is available with an adjustable 1.21V reference voltage and an output voltage range from 1.21V to 20V. Internal protection circuitry includes current limiting, thermal limiting, and reverse-current protection.

The TPS73801-SEP is utilized in this design to create a low current, auxiliary 5V rail that is used for various housekeeping tasks.

#### 2.3.6 TPS7H3302-SEP

The TPS7H3302 is a radiation-hardened double data rate (DDR) 3A termination regulator with built-in VTTREF buffer. The regulator is specifically designed to provide a compact, low-noise design for space-grade DDR termination applications such as single board computers, solid-state recorders, and payload processing.

The TPS7H3302 supports DDR VTT termination applications using DDR, DDR2, DDR3, DDR3L, and DDR4. The fast transient response of the TPS7H3302 VTT regulator allows for a stable supply during read and write conditions. The TPS7H3302 also includes a built-in VTTREF supply that tracks VTT to further reduce the design size. To enable simple power sequencing, both an enable input and a power-good output (PGOOD) have been integrated into the TPS7H3302.

The radiation-tolerant TPS7H3302-SEP is utilized in this design to power the DDR4 memory. The radiation-hardened TPS7H3302-SP is also available in a QMLP plastic package, and the TPS7H3301-SP is available in a QMLV plastic package.

#### 2.3.7 TPS7H3014-SEP

The TPS7H3014 is an integrated, 3V to 14V, four-channel radiation-hardened power-supply sequencer. Channel count can be expanded by connecting multiple devices in a daisy-chain configuration. The device provides sequence up and down control signals for integrated circuits with active high (*on*) inputs. In addition SEQ\_DONE and PWRGD flags are provided to monitor the sequence and power status of the monitored power tree.

An accurate  $599mV \pm 1\%$  threshold voltage and a  $24\mu A \pm 3\%$  hysteresis current provide programmable rise and fall monitoring voltages. The rise and fall delay time is globally programmed using a single resistor. Also, a time-to-regulation timer is provided to track the rising voltage on SENSEx. In addition to these features, a FAULT detection pin is incorporated to monitor internally generated faults and provide increased system level reliability for power sequencing space applications.

The radiation-hardened TPS7H3014-SP is utilized in this design to sequence the power rails. The radiation-tolerant TPS7H3014-SEP in a plastic package is also available (this part is not utilized in this TI design due to part availability during initial design).

www.ti.com System Overview

#### 2.3.8 TPS7H2221-SEP

The TPS7H2221-SEP device is a small, single channel load switch with controlled slew rate. The device contains an N-channel MOSFET that can operate over an input voltage range of 1.6V to 5.5V and can support a maximum continuous current of 1.25A.

The switch ON state is controlled by a digital input that is capable of interfacing directly with low-voltage control signals. When power is first applied, a Smart Pull Down is used to keep the ON pin from floating until system sequencing is complete. Once the pin is deliberately driven high  $(V_{ON} > V_{IH})$ , the Smart Pull Down is disconnected to prevent unnecessary power loss. The TPS7H2221-SEP load switch is also self-protected against short circuit events on the output of the device.

The TPS7H2221-SEP is used in this design as an output discharge for various voltage rails. This active discharge is needed to meet the sequence down timing specification for the Versal FPGA.

#### 2.3.9 SN54SC6T14-SEP

The SN54SC6T14-SEP is a radiation-tolerant hex Schmitt-Trigger inverter. The device contains six independent inputs and the output voltage is referenced to the supply voltage. The device supports 1.2V, 1.8V, 2.5V, 3.3V, and 5V CMOS levels.

The input is designed with a lower threshold circuit to support up translation for lower voltage CMOS inputs. Additionally, the 5V tolerant input pins enable down translation.

The inverter is utilized in conjunction with the TPS7H3014-SP sequencer to drive the GaN FET which discharges the 0V8 (VCCINT) rail during shutdown.

# 3 System Design Theory

### 3.1 0V8 Discrete Buck Regulator (VCCINT)

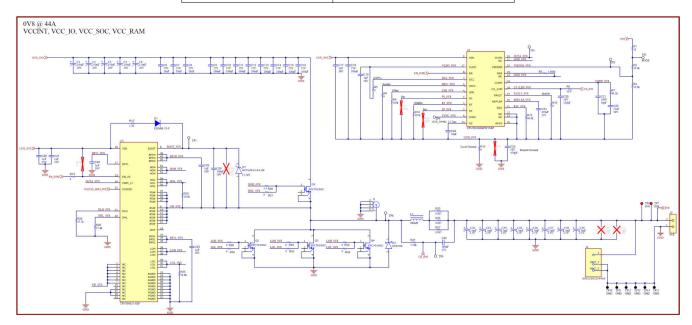

The 0V8 rails is primarily used to power VCCCINT, sometimes called the core rail voltage. This high-current rail uses a discrete buck converter made of the TPS7H5006-SEP PWM controller, TPS7H6025-SEP GaN half-bridge driver, and EPC Space EPC7019GC GaN FETs.

These GaN FETs are selected due to the low on-resistance and availability as radiation-hardened devices. To support the low duty cycle of the 12V to 0.8V conversion ratio, three low-side FETs are used and one high-side FET. This asymmetric FET selection helps optimize the on-resistance and switching losses. The FETs are driven by the TPS7H6025-SEP gate driver. For the low-side FETs,  $0\Omega$  LOH and LOL gate resistors are determined to provide the fastest turn-on and turn-off times. For the high-side FET, a  $0\Omega$  HOL gate resistor is selected to provided the fastest turn-off time; however, a  $3.3\Omega$  HOH gate resistor is determined to be required to prevent excessive turn-on speed which can couple into the low-side gate.

The buck converter is operated in peak-current mode control using DCR current sensing. To provide a sufficient current signal, additional resistance is added in series with the inductor. Additionally, more slope compensation than traditionally required is added to provide additional noise mitigation and prevent excessive switch node iitter.

The buck regulator switches at 270kHz as a compromise between switching fast enough to result in a high enough crossover frequency and a reasonably small-sized inductor while not switching too fast which can cause minimum on-time issues and reduced efficiency. The output capacitor network is primarily sized based on the load step requirements of the Versal FPGA.

The output voltage is configured utilizing a resistor divider connected to the feedback pin. An  $R_{FB\_TOP}$  of  $10.05k\Omega$  ( $10k\Omega$  in series with a  $50\Omega$ ) and  $R_{FB\_BOT}$  of  $33k\Omega$  are selected which results in a nominal output voltage of 0.7997V. Utilizing the data sheet reference voltage parameter 0.607V minimum and 0.617V maximum along with 0.1% resistor tolerances (using a sum of squares to get  $\pm 0.14\%$  error contribution), the overall DC accuracy can be approximated using Equation 1 and Equation 2. The accuracy is calculated to be -1.16% and  $\pm 0.75\%$ .

$$Error_{(positive)} = \frac{V_{FB(max)} \times \frac{R_{FB\_TOP} + R_{FB\_BOT}}{R_{FB\_BOT}} - V_{OUT(ideal)}}{V_{OUT(ideal)}} + R_{(error)}$$

(1)

$$Error_{(negative)} = \frac{V_{FB(min)} \times \frac{R_{FB\_TOP} + R_{FB\_BOT}}{R_{FB\_BOT}} - V_{OUT(ideal)}}{V_{OUT(ideal)}} - R_{(error)}$$

(2)

Table 3-2 shows a summary of these calculations.

The layout of the GaN FETs and power loops is critical for optimized performance. The high-side FET is centered above the three low-side FETs for a balanced return path. The input capacitors are placed near the high-side FET and a ground return is provided on a second layer plane. This minimizes the return loop inductance and provides mutual inductance cancellation during FET turn-on.

Table 3-1. 0V8 Rail Design Values

| PARAMETER                             | DESCRIPTION OR TYPICAL VALUE                        |

|---------------------------------------|-----------------------------------------------------|

| V <sub>IN</sub>                       | 12V                                                 |

| V <sub>OUT</sub>                      | 0.8V                                                |

| I <sub>OUT(max)</sub>                 | 44A                                                 |

| f <sub>SW</sub> , switching frequency | 270kHz                                              |

| DC Accuracy                           | -1.16%, +0.75%                                      |

| Output ripple                         | 3.8mVpp                                             |

| L <sub>SW</sub> , output inductor     | 680nH XAL1010-681MEB                                |

| C <sub>OUT</sub> , output capacitance | 8x1.5mF (T520X) + 2x22μF ceramic<br>+ 2x1μF ceramic |

Table 3-1. 0V8 Rail Design Values (continued)

| PARAMETER                           | DESCRIPTION OR TYPICAL VALUE                          |

|-------------------------------------|-------------------------------------------------------|

| C <sub>IN</sub> , input capacitance | 5x150μF (T521D) + 3x10μF ceramic<br>+ 8x100nF ceramic |

| t <sub>SS</sub> , soft start time   | 12.7ms                                                |

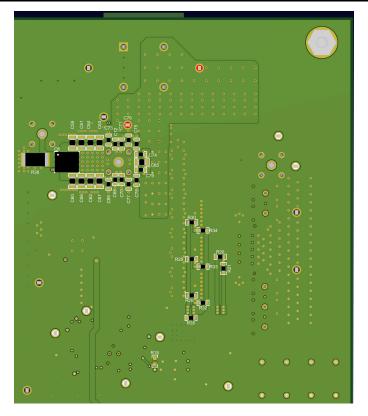

Figure 3-1. 0V8 (VCCINT) Schematic

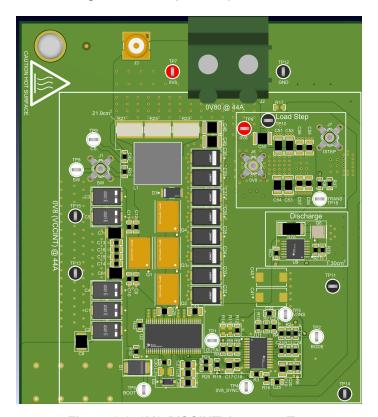

Figure 3-2. 0V8 (VCCINT) Layout - Top

Figure 3-3. 0V8 (VCCINT) Layout - Bottom

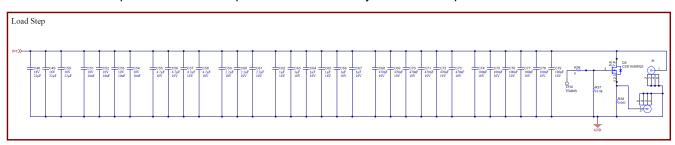

# 3.1.1 VCCINT Load Step

A load step circuit is added to the design to be able to replicate the fast load steps from the Versal FPGA. This circuit is composed of a TI MOSFET that can be driven by a function generator and a load resistor. The MOSFET resistance and load resistor are sized to support an 11A load step. This load step and the resulting slew rate can be fine-tuned by adjusting the function generator applied voltage levels and slew rates.

In addition to the load step circuitry, decoupling capacitors are added. This additional capacitance is required to keep the impedance minimized at higher frequencies. In a final system design, place these capacitors near the FPGA. Additional optimization for the specific FPGA board layout can be required.

Figure 3-4. Load Step and Decoupling Capacitors Schematic

### 3.2 Buck Regulators (Integrated)

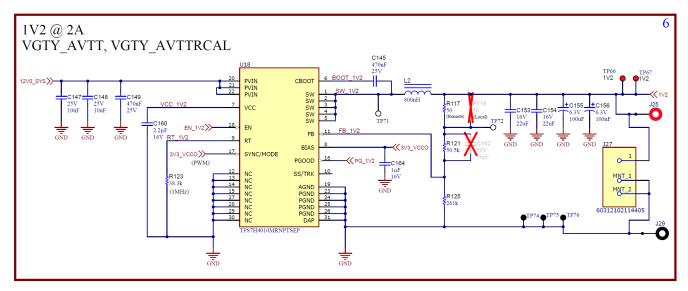

#### 3.2.1 1V2

The TPS7H4010-SEP synchronous buck converter is selected to generate the required 1.2V directly from the 12V rail. While the TPS7H4010-SEP is capable of 6A, the Versal Edge VGTY\_AVTT and VGTY\_AVTTRCAL rails are estimated to only require 1.3A. Therefore, the buck converter is sized for 2A to provide reasonable margin.

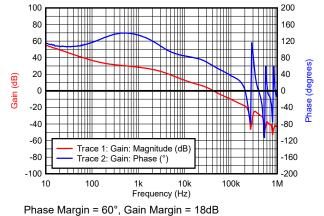

A switching frequency of 1MHz and a  $0.8\mu H$  XAL5030-801ME\_ inductor are selected to provide a reasonable balance of design size and efficiency. Additionally, the *typical component selection* table in the *TPS7H4010-SEP Radiation Hardened 3.5V to 32V, 6A Synchronous Step-Down Voltage Converter in Space Enhanced Plastic* data sheet is consulted to make sure the values are close to the recommended selection. This is confirmed through a load step and Bode plot measurement as shown in Section 4.3.2. A  $50\Omega$  resistor is placed in series with the top feedback resistor and an option for a feed-forward capacitor is implemented to enable easier measuring and optimization of the control loop.

Next, output voltage ripple is determined. First the inductor ripple is calculated as shown in Equation 3. 1.35A of inductor ripple current is calculated.

$$I_{L(ripple)} = \frac{VIN - VOUT}{L} \times \frac{VOUT}{VIN \times f_{SW}}$$

(3)

#### where

- VIN is the input voltage, 12V

- VOUT is the configured output voltage, 1.2V

- L is the selected inductor, 0.8µH

- f<sub>SW</sub> is the selected operating frequency, 1MHz

Next, two 100 $\mu$ F electrolytic capacitors and two 22 $\mu$ F ceramic capacitors are selected. Using the K-SIM tool from Kemet<sup>TM</sup>, the output impedance of these parallel capacitors at 1MHz is determined to be approximately 2.5m $\Omega$ . Multiplying the impedance by the inductor ripple current gives the approximated output ripple of  $\pm 3.4$ mV.

Finally, the output voltage is configured using a resistor divider connected to the feedback pin. An  $R_{FB\_TOP}$  of  $50.55 k\Omega$  ( $50.5 k\Omega$  in series with a  $50\Omega$ ) and  $R_{FB\_BOT}$  of  $261 k\Omega$  are selected which results in a nominal output voltage of 1.201V. Using the data sheet feedback voltage parameter, 0.987V minimum and 1.017V maximum along with 0.1% resistor tolerances (using a sum of squares to get  $\pm 0.14\%$  error contribution), the overall DC accuracy can be approximated using Equation 4 and Equation 5. The accuracy is calculated to be -1.96% and  $\pm 1.30\%$ .

$$Error_{(positive)} = \frac{V_{FB(max)} \times \frac{R_{FB\_TOP} + R_{FB\_BOT}}{R_{FB\_BOT}} - V_{OUT(ideal)}}{V_{OUT(ideal)}} + R_{(error)}$$

(4)

$$Error_{(negative)} = \frac{V_{FB(min)} \times \frac{R_{FB\_TOP} + R_{FB\_BOT}}{R_{FB\_BOT}} - V_{OUT(ideal)}}{V_{OUT(ideal)}} - R_{(error)}$$

(5)

One additional consideration for accuracy is if auto mode is enabled. Auto mode results in higher efficiency at light loads at the expense of worse load regulation. Consulting the TPS7H4010-SEP *load and line regulation* figure in the *TPS7H4010-SEP* data sheet and looking at the approximate 0.08V increase at light load for a 5V application, auto mode is approximated to add an additional error of +1.6%. Therefore, if auto mode is enabled, the accuracy is –1.96% and +2.90%. This is too much error for this rail and therefore auto mode is disabled.

Table 3-2 shows a summary of these calculations.

Table 3-2. 1V2 Rail Design Values

| PARAMETER        | DESCRIPTION OR TYPICAL<br>VALUE |

|------------------|---------------------------------|

| V <sub>IN</sub>  | 12V                             |

| V <sub>OUT</sub> | 1.2V                            |

Table 3-2. 1V2 Rail Design Values (continued)

| PARAMETER                             | DESCRIPTION OR TYPICAL<br>VALUE |

|---------------------------------------|---------------------------------|

| I <sub>OUT(max)</sub>                 | 2A                              |

| f <sub>SW</sub> , switching frequency | 1MHz                            |

| DC Accuracy                           | _1.96%, +1.30%                  |

| Output ripple                         | 3.4mVpp                         |

| L <sub>SW</sub> , output inductor     | 0.8μH, XAL5030-801ME_           |

| C <sub>OUT</sub> , output capacitance | 2x100μF T520B, 2x22μF ceramic   |

| C <sub>IN</sub> , input capacitance   | 3x10µF ceramic, 1x470nF ceramic |

| t <sub>SS</sub> , soft start time     | 6.3ms (SS float)                |

| Bias connection                       | Connected to external 3V3_VCCO  |

| Mode                                  | Forced PWM (auto disabled)      |

Figure 3-5. 1V2 Schematic

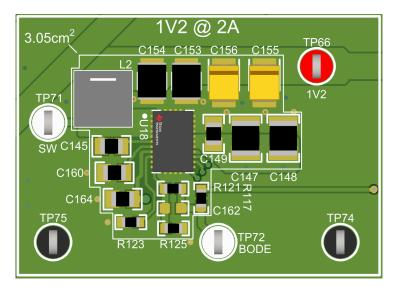

Figure 3-6. 1V2 Layout

### 3.2.2 1V2 VCCO

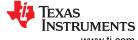

The TPS7H4010-SEP synchronous buck converter is selected to generate the required 1.2V directly from the 12V rail. While the TPS7H4010-SEP is capable of 6A, the Versal Edge XPIO (bank 7xx) rails only require 2A. Additionally, the 1V2\_VCCO output feeds the input of the TPS7H1111-SEP for the 0V92 rail which is up to another 1A. Therefore, the design decision is to size this design for 4A to provide reasonable margin.

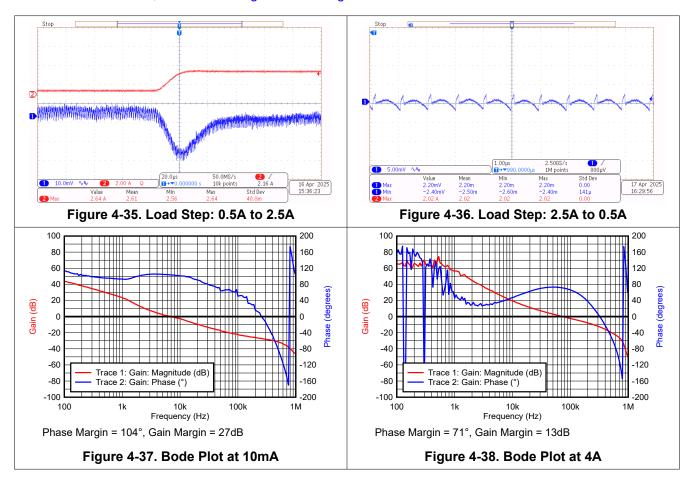

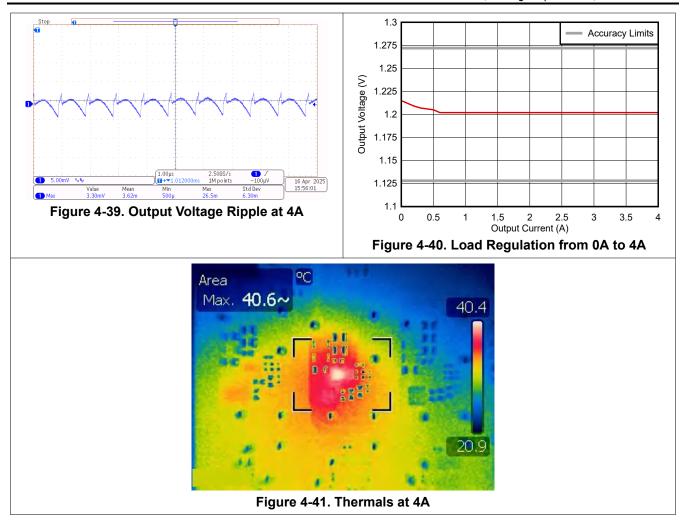

A switching frequency of 1MHz and a  $0.8\mu H$  XAL5030-801ME\_ inductor are selected to provide a reasonable balance of design size and efficiency. Additionally, the *typical component selection* table in the *TPS7H4010-SEP* data sheet is consulted to make sure the values are close to the recommended selection. This is confirmed through a load step and Bode plot measurement as shown in Section 4.3.2. A  $50\Omega$  resistor is placed in series with the top feedback resistor and an option for a feed-forward capacitor is implemented to enable easier measuring and optimization of the control loop.

Next output voltage ripple is determined. First the inductor ripple is calculated as shown in Equation 6. An inductor ripple current of 1.35A is calculated.

$$I_{L(ripple)} = \frac{VIN - VOUT}{L} \times \frac{VOUT}{VIN \times f_{SW}}$$

(6)

#### where

- VIN is the input voltage, 12V

- VOUT is the configured output voltage, 1.2V

- L is the selected inductor, 0.8µH

- f<sub>SW</sub> is the selected operating frequency, 1MHz

Next, two  $100\mu\text{F}$  electrolytic capacitors and one  $22\mu\text{F}$  ceramic capacitor are selected. Using the K-SIM tool from Kemet, the output impedance of these parallel capacitors at 1MHz is determined to be approximately  $4.2\text{m}\Omega$ . Multiplying the impedance by the inductor ripple current gives the approximated output ripple of  $\pm 5.7\text{mV}$ .

Finally, the output voltage is configured using a resistor divider connected to the feedback pin. An  $R_{FB\_TOP}$  of  $50.55k\Omega$  ( $50.5k\Omega$  in series with a  $50\Omega$ ) and  $R_{FB\_BOT}$  of  $261k\Omega$  are selected which results in a nominal output voltage of 1.201V. Using the data sheet feedback voltage parameter 0.987V minimum and 1.017V maximum along with 0.1% resistor tolerances (using a sum of squares to get  $\pm 0.14\%$  error contribution), the overall DC accuracy can be approximated using Equation 7 and Equation 8. The accuracy is calculated to be -1.96% and +1.30%.

$$Error_{(positive)} = \frac{V_{FB(max)} \times \frac{R_{FB\_TOP} + R_{FB\_BOT}}{R_{FB\_BOT}} - V_{OUT(ideal)}}{V_{OUT(ideal)}} + R_{(error)}$$

(7)

$$Error_{(negative)} = \frac{V_{FB(min)} \times \frac{R_{FB\_TOP} + R_{FB\_BOT}}{R_{FB\_BOT}} - V_{OUT(ideal)}}{V_{OUT(ideal)}} - R_{(error)}$$

(8)

One additional consideration for accuracy is if auto mode is enabled. Auto mode results in higher efficiency at light loads at the expense of worse load regulation. Consulting the TPS7H4010-SEP load and line regulation figure in the TPS7H4010-SEP data sheet and looking at the approximate 0.08V increase at light load for a 5V application, auto mode is approximated to add an additional error of +1.6%. Therefore, if auto mode is enabled, the accuracy is -1.96% and +2.90%. This error is acceptable for this rail, and therefore auto mode is enabled.

Note that the output connector shows a current of 2A. This is because when all rails are fully loaded, 2A is outputted for the Versal Edge 1V2\_VCCO rail while the other 2A is provided to other internal rails. The board connectors themselves are sized to support 4A.

Table 3-3 shows a summary of these calculations.

Table 3-3. 1V2 VCCO Rail Design Values

| PARAMETER                             | DESCRIPTION OR TYPICAL VALUE    |

|---------------------------------------|---------------------------------|

| V <sub>IN</sub>                       | 12V                             |

| V <sub>OUT</sub>                      | 1.2V                            |

| I <sub>OUT(max)</sub>                 | 4A                              |

| f <sub>SW</sub> , switching frequency | 1MHz                            |

| DC Accuracy                           | -1.96%, +2.90%                  |

| Output ripple                         | 5.7mVpp                         |

| L <sub>SW</sub> , output inductor     | 0.8µH, XAL5030-801ME_           |

| C <sub>OUT</sub> , output capacitance | 2x100μF T520B, 1x22μF ceramic   |

| C <sub>IN</sub> , input capacitance   | 3x10μF ceramic, 1x470nF ceramic |

| t <sub>SS</sub> , soft start time     | 6.3ms (SS float)                |

| Bias connection                       | Connected to external 3V3_VCCO  |

| Mode                                  | Auto enabled                    |

Figure 3-7. 1V2\_VCCO Schematic

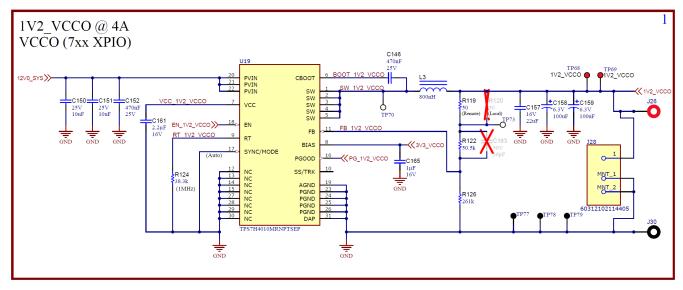

Figure 3-8. 1V2\_VCCO Layout

14

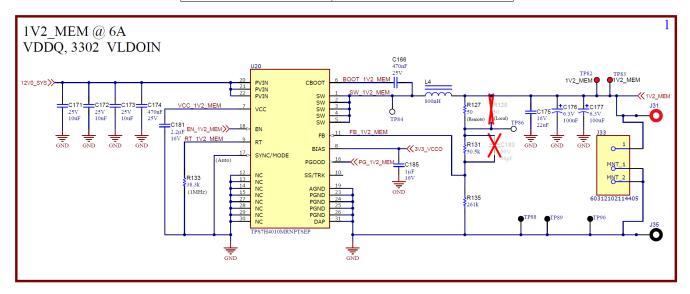

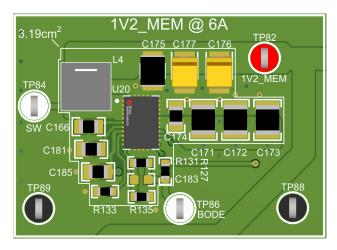

### 3.2.3 1V2 MEM

The TPS7H4010-SEP synchronous buck converter is selected to generate the required 1.2V directly from the 12V rail. Tl's estimate is that the DDR\_VDDQ rail for DDR4 requires up to 3A and the VLDOIN of the downstream TPS7H3302-SEP requires up to 3A; therefore, the full 6A capability of the TPS7H4010-SEP is used.

A switching frequency of 1MHz and a  $0.8\mu H$  XAL5030-801ME\_ inductor are selected to provide a reasonable balance of design size and efficiency. Additionally, the *typical component selection* table in the *TPS7H4010-SEP* data sheet is consulted to make sure the values are close to the recommended selection. This is confirmed through a load step and Bode plot measurement as shown in Section 4.3.2. A  $50\Omega$  resistor is placed in series with the top feedback resistor and an option for a feed-forward capacitor is implemented to enable easier measuring and optimization of the control loop.

Next, the output voltage ripple is determined. First the inductor ripple is calculated as shown in Equation 9. An inductor ripple current of 1.35A is calculated.

$$I_{L(ripple)} = \frac{VIN - VOUT}{L} \times \frac{VOUT}{VIN \times f_{SW}}$$

(9)

#### where

- VIN is the input voltage, 12V

- VOUT is the configured output voltage, 1.2V

- L is the selected inductor, 0.8µH

- f<sub>SW</sub> is the selected operating frequency, 1MHz

Next, two 100 $\mu$ F electrolytic capacitors and *one* 22 $\mu$ F ceramic capacitor is selected. Using the K-SIM tool from Kemet, the output impedance of these parallel capacitors at 1MHz is determined to be approximately 4.2m $\Omega$ . Multiplying the impedance by the inductor ripple current gives the approximated output ripple of  $\pm 5.7$ mV.

Finally, the output voltage is configured using a resistor divider connected to the feedback pin. An  $R_{FB\_TOP}$  of  $50.55 k\Omega$  ( $50.5 k\Omega$  in series with a  $50\Omega$ ) and  $R_{FB\_BOT}$  of  $261 k\Omega$  are selected which results in a nominal output voltage of 1.201V. Using the data sheet feedback voltage parameter 0.987V minimum and 1.017V maximum along with 0.1% resistor tolerances (using a sum of squares to get  $\pm 0.14\%$  error contribution), the overall DC accuracy can be approximated using Equation 10 and Equation 11. The accuracy is calculated to be -1.96% and  $\pm 1.30\%$ .

$$Error_{(positive)} = \frac{V_{FB(max)} \times \frac{R_{FB\_TOP} + R_{FB\_BOT}}{R_{FB\_BOT}} - V_{OUT(ideal)}}{V_{OUT(ideal)}} + R_{(error)}$$

(10)

$$Error_{(negative)} = \frac{V_{FB(min)} \times \frac{R_{FB\_TOP} + R_{FB\_BOT}}{R_{FB\_BOT}} - V_{OUT(ideal)}}{V_{OUT(ideal)}} - R_{(error)}$$

(11)

One additional consideration for accuracy is if auto mode is enabled. Auto mode results in higher efficiency at light loads at the expense of worse load regulation. Consulting the TPS7H4010-SEP load and line regulation image in the TPS7H4010-SEP data sheet and looking at the approximate 0.08V increase at light load for a 5V application, auto mode is approximated to add an additional error of +1.6%. Therefore, if auto mode is enabled, the accuracy is -1.96% and +2.90%. This error is acceptable for this rail, and therefore auto mode is enabled.

Table 3-4 shows a summary of these calculations.

Table 3-4. 1V2 Rail Design Values

| PARAMETER                             | DESCRIPTION OR TYPICAL VALUE |

|---------------------------------------|------------------------------|

| V <sub>IN</sub>                       | 12V                          |

| V <sub>OUT</sub>                      | 1.2V                         |

| I <sub>OUT(max)</sub>                 | 6A                           |

| f <sub>SW</sub> , switching frequency | 1MHz                         |

Table 3-4. 1V2 Rail Design Values (continued)

| PARAMETER                             | DESCRIPTION OR TYPICAL VALUE    |

|---------------------------------------|---------------------------------|

| DC Accuracy                           | -1.96%, +2.90%                  |

| Output ripple                         | 5.7mVpp                         |

| L <sub>SW</sub> , output inductor     | 0.8μH, XAL5030-801ME_           |

| C <sub>OUT</sub> , output capacitance | 2x100µF T520B, 1x22µF ceramic   |

| C <sub>IN</sub> , input capacitance   | 3x10μF ceramic, 1x470nF ceramic |

| t <sub>SS</sub> , soft start time     | 6.3ms (SS float)                |

| Bias connection                       | Connected to external 3V3_VCCO  |

| Mode                                  | Auto enabled                    |

Figure 3-9. 1V2\_MEM Schematic

Figure 3-10. 1V2\_MEM Layout

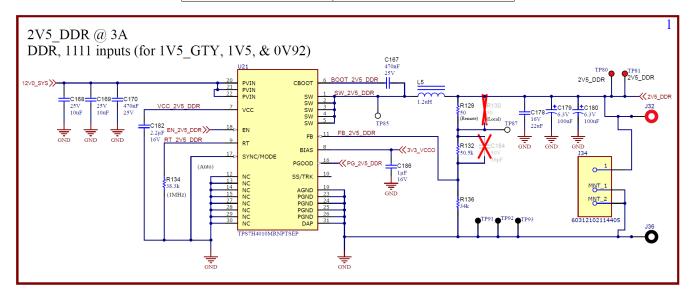

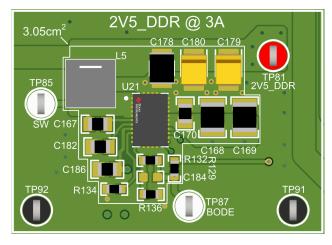

# 3.2.4 2V5\_DDR\_VPP

The TPS7H4010-SEP synchronous buck converter is selected to generate the required 2.5V directly from the 12V rail. The DDR\_VPP rail for DDR4 is estimated to require up to 0.1A, the TPS7H1111-SEP input for the 1V5\_GTY rail is estimated to require up to 0.2A, and the TPS7H1111-SEP input for the 1V5 rail is estimated to require up to 1.5A. Therefore, the design decision is for 3A to provide reasonable margin.

A switching frequency of 1MHz and a  $1.2\mu H$  XAL5030- $122ME_{inductor}$  inductor are selected to provide a reasonable balance of design size and efficiency. Additionally, the *typical component selection* table in the *TPS7H4010-SEP* data sheet is consulted to make sure the values are close to the recommended selection. This is confirmed through a load step and Bode plot measurement as shown in Section 4.3.2. A  $50\Omega$  resistor is placed in series with the top feedback resistor and an option for a feed-forward capacitor is implemented to enable easier measuring and optimization of the control loop.

Next, the output voltage ripple is determined. First the inductor ripple is calculated as shown in Equation 12. An inductor ripple current of 1.65A is calculated.

$$I_{L(ripple)} = \frac{VIN - VOUT}{L} \times \frac{VOUT}{VIN \times f_{SW}}$$

(12)

#### where

- VIN is the input voltage, 12V

- VOUT is the configured output voltage, 2.5V

- L is the selected inductor, 1.2μH

- f<sub>SW</sub> is the selected operating frequency, 1MHz

Next, two  $100\mu\text{F}$  electrolytic capacitors and one  $22\mu\text{F}$  ceramic capacitor are selected. Using the K-SIM tool from Kemet, the output impedance of these parallel capacitors at 1MHz is determined to be approximately  $4.2\text{m}\Omega$ . Multiplying the impedance by the inductor ripple current gives the approximated output ripple of  $\pm 6.9\text{mV}$ .

Finally, the output voltage is configured using a resistor divider connected to the feedback pin. An  $R_{FB\_TOP}$  of  $50.55k\Omega$  ( $50.5k\Omega$  in series with a  $50\Omega$ ) and  $R_{FB\_BOT}$  of  $34k\Omega$  are selected which results in a nominal output voltage of 2.502V. Using the data sheet feedback voltage parameter 0.987V minimum and 1.017V maximum along with 0.1% resistor tolerances (using a sum of squares to get  $\pm 0.14\%$  error contribution), the overall DC accuracy can be approximated using Equation 13 and Equation 14. The accuracy is calculated to be -1.96% and +1.30%.

$$Error_{(positive)} = \frac{V_{FB(max)} \times \frac{R_{FB\_TOP} + R_{FB\_BOT}}{R_{FB\_BOT}} - V_{OUT(ideal)}}{V_{OUT(ideal)}} + R_{(error)}$$

(13)

$$Error_{(negative)} = \frac{V_{FB(min)} \times \frac{R_{FB\_TOP} + R_{FB\_BOT}}{R_{FB\_BOT}} - V_{OUT(ideal)}}{V_{OUT(ideal)}} - R_{(error)}$$

(14)

One additional consideration for accuracy is if auto mode is enabled. Auto mode results in higher efficiency at light loads at the expense of worse load regulation. Consulting the TPS7H4010-SEP *load and line regulation* image in the *TPS7H4010-SEP* data sheet and looking at the approximate 0.08V increase at light load for a 5V application, auto mode is approximated to add an additional error of +1.6%. Therefore, if auto mode is enabled, the accuracy is –1.96% and +2.90%. This error is acceptable for this rail, and therefore auto mode is enabled.

Note that the output connector shows a current of 0.1A. This is because when all rails are fully loaded, 0.1A is outputted for the DDR\_VPP rail, while the other 2.9A is provided to other internal rails. The board connectors themselves are sized to support 3A.

Table 3-5 shows a summary of these calculations.

Table 3-5. 2V5\_DDR\_VPP Rail Design Values

| PARAMETER                             | DESCRIPTION OR TYPICAL<br>VALUE |

|---------------------------------------|---------------------------------|

| V <sub>IN</sub>                       | 12V                             |

| V <sub>OUT</sub>                      | 2.5V                            |

| I <sub>OUT(max)</sub>                 | 3A                              |

| f <sub>SW</sub> , switching frequency | 1MHz                            |

| DC Accuracy                           | -1.96%, <b>+</b> 2.90%          |

| Output ripple                         | 6.9mVpp                         |

Table 3-5. 2V5\_DDR\_VPP Rail Design Values (continued)

| PARAMETER                             | DESCRIPTION OR TYPICAL VALUE    |

|---------------------------------------|---------------------------------|

| L <sub>SW</sub> , output inductor     | 1.2µH, XAL5030-122ME_           |

| C <sub>OUT</sub> , output capacitance | 2x100µF T520B, 1x22µF ceramic   |

| C <sub>IN</sub> , input capacitance   | 3x10µF ceramic, 1x470nF ceramic |

| t <sub>SS</sub> , soft start time     | 6.3ms (SS float)                |

| Bias connection                       | Connected to external 3V3_VCCO  |

| Mode                                  | Auto enabled                    |

Figure 3-11. 2V5\_DDR\_VPP Schematic

Figure 3-12. 2V5\_DDR\_VPP Layout

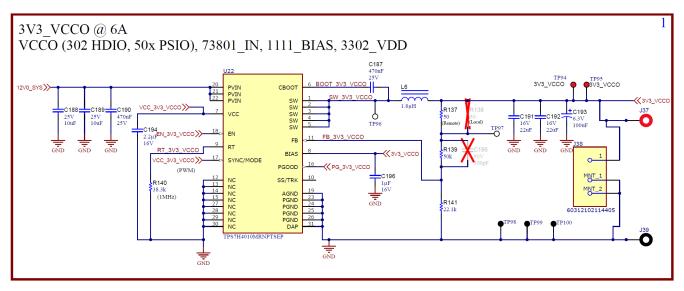

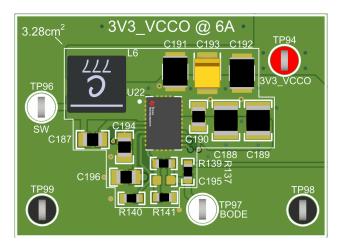

# 3.2.5 3V3\_VCCO

The TPS7H4010-SEP synchronous buck converter is selected to generate the required 3.3V directly from the 12V rail. The Versal Edge VCCO HDIO (bank 302) rails are estimated to require 2A, the VCCO 500, VCCO\_501, and VCCO\_503 (PSIO banks) and VCCO\_502 (PSIO bank) are estimated to require 2A, the TPS7H3302-SEP VDD input is estimated to require 30mA, and the TPS7H1111-SEP bias rails are estimated to require 81mA. Therefore, TPS7H4010-SEP is sized for 6A to provide reasonable margin.

A switching frequency of 1MHz and a  $1.8\mu H$  XAL6030- $182ME_{inductor}$  is selected to provide a reasonable balance of design size and efficiency. Additionally, the *typical component selection* table in the *TPS7H4010-SEP* data sheet is consulted to make sure the values are close to the recommended selection. This is confirmed through a load step and Bode plot measurement as shown in Section 4.3.2. A  $50\Omega$  resistor is placed in series with the top feedback resistor and an option for a feed-forward capacitor is implemented to enable easier measuring and optimization of the control loop.

Next, the output voltage ripple is determined. First the inductor ripple is calculated as shown in Equation 15. An inductor ripple current of 1.33A is calculated.

$$I_{L(ripple)} = \frac{VIN - VOUT}{L} \times \frac{VOUT}{VIN \times f_{SW}}$$

(15)

#### where

- VIN is the input voltage, 12V

- VOUT is the configured output voltage, 3.3V

- L is the selected inductor, 1.8µH

- f<sub>SW</sub> is the selected operating frequency, 1MHz

Next, one  $100\mu\text{F}$  electrolytic capacitor and two  $22\mu\text{F}$  ceramic capacitors are selected. Using the K-SIM tool from Kemet, the output impedance of these parallel capacitors at 1MHz is determined to be approximately  $12.2\text{m}\Omega$ . Multiplying the impedance by the inductor ripple current gives the approximated output ripple of  $\pm 16.2\text{mV}$ .

Finally, the output voltage is configured using a resistor divider connected to the feedback pin. An  $R_{FB\_TOP}$  of  $50.55k\Omega$  ( $50.5k\Omega$  in series with a  $50\Omega$ ) and  $R_{FB\_BOT}$  of  $22.1k\Omega$  are selected which results in a nominal output voltage of 3.307V. Using the data sheet feedback voltage parameter 0.987V minimum and 1.017V maximum along with 0.1% resistor tolerances (using a sum of squares to get  $\pm 0.14\%$  error contribution), the overall DC accuracy can be approximated using Equation 16 and Equation 17. The accuracy is calculated to be -1.82% and +1.45%.

$$Error_{(positive)} = \frac{V_{FB(max)} \times \frac{R_{FB\_TOP} + R_{FB\_BOT}}{R_{FB\_BOT}} - V_{OUT(ideal)}}{V_{OUT(ideal)}} + R_{(error)}$$

(16)

$$Error_{(negative)} = \frac{V_{FB(min)} \times \frac{R_{FB\_TOP} + R_{FB\_BOT}}{R_{FB\_BOT}} - V_{OUT(ideal)}}{V_{OUT(ideal)}} - R_{(error)}$$

(17)

One additional consideration for accuracy is if auto mode is enabled. Auto mode results in higher efficiency at light loads at the expense of worse load regulation. Consulting the TPS7H4010-SEP *load and line regulation* image in the *TPS7H4010-SEP* data sheet and looking at the approximate 0.08V increase at light load for a 5V application, auto mode is approximated to add an additional error of +1.6%. Therefore, if auto mode is enabled, the accuracy is –1.82% and +3.05%. This error is acceptable for this rail, and therefore auto mode is enabled.

Table 3-6 shows a summary of these calculations.

Table 3-6. 3V3\_VCCO Rail Design Values

| PARAMETER                             | DESCRIPTION OR TYPICAL VALUE    |

|---------------------------------------|---------------------------------|

| V <sub>IN</sub>                       | 12V                             |

| V <sub>OUT</sub>                      | 3.3V                            |

| I <sub>OUT(max)</sub>                 | 6A                              |

| f <sub>SW</sub> , switching frequency | 1MHz                            |

| DC Accuracy                           | -1.82%, +3.05%                  |

| Output ripple                         | 16.2mVpp                        |

| L <sub>SW</sub> , output inductor     | 1.8µH XAL6030-182ME_            |

| C <sub>OUT</sub> , output capacitance | 1x100μF T520B, 2x22μF ceramic   |

| C <sub>IN</sub> , input capacitance   | 2x10µF ceramic, 1x470nF ceramic |

Table 3-6. 3V3\_VCCO Rail Design Values (continued)

| PARAMETER                         | DESCRIPTION OR TYPICAL<br>VALUE |  |  |

|-----------------------------------|---------------------------------|--|--|

| t <sub>SS</sub> , soft start time | 6.3ms (SS float)                |  |  |

| Bias connection                   | Connected to output 3V3_VCCO    |  |  |

| Mode                              | Auto enabled                    |  |  |

Figure 3-13. 3V3\_VCCO Schematic

Figure 3-14. 3V3\_VCCO Layout

# 3.3 Linear Regulators

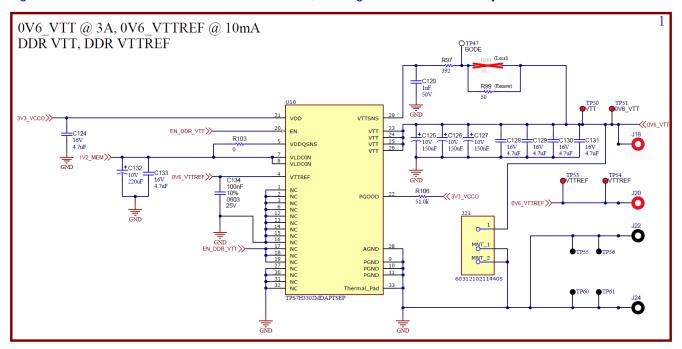

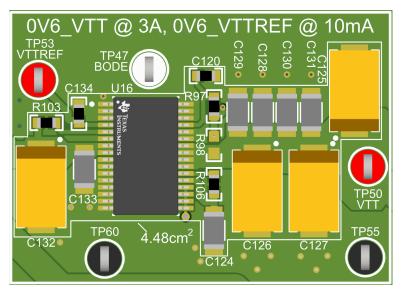

### 3.3.1 DDR Termination

The TPS7H3302-SEP is selected for the termination of the DDR4 memory. This part generates the  $\pm$ 3A for VTT and  $\pm$ 10mA for VTTREF. The VLDOIN input comes from the 1V2\_MEM rail and the VDD comes from the 3V3\_VCCO rail. The output capacitors are selected to be  $3x150\mu$ F +  $4x4.7\mu$ F, which is the same as the EVM. From the TPS7H3302-SEP data sheet, the VTT accuracy is -2.5% and +5.0% (for  $\pm$ 1A).

Figure 3-15 shows the TPS7H3302-SEP schematic, and Figure 3-16 shows the layout.

Figure 3-15. DDR Termination Schematic

Figure 3-16. DDR Termination Layout

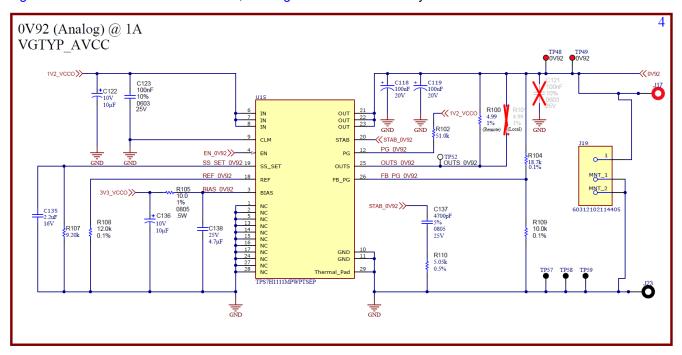

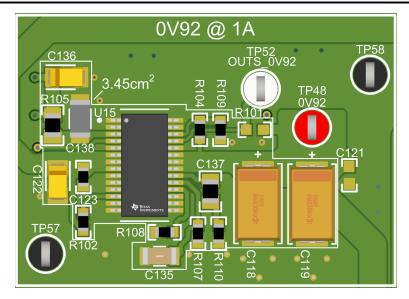

#### 3.3.2 OV92

The TPS7H1111-SEP is selected to generate the 0.92V rail from the 1V2\_VCCO rail (and 3V3\_VCCO for the bias). While the TPS7H1111-SEP is capable of 1.5A, the Versal Edge VTYP\_AVCC rail is estimated to only require 0.75A. Therefore, the LDO is designed for 1A maximum to provide reasonable margin.

The  $2x100\mu F$  output capacitors used on the EVM are selected for this design. No additional ceramic decoupling capacitors are added as the TPS7H1111-SEP does not require them for good performance. However, if desired, a 100nF capacitor can be added near the FPGA load (a placeholder in the layout is provided for this purpose). The FB\_PG resistors are sized so that the PG assert threshold occurs at 95.5% of VOUT. This threshold must be carefully selected to make sure that during start-up the TPS7H1111-SEP voltage ramps up within the maximum sequencing timing requirements of the Versal FPGA. Additionally, a  $2.2\mu F$  C<sub>SS</sub> capacitor is selected instead of the typical  $4.7\mu F$  capacitor to provide additional timing margin during start-up. The lower noise that is provided by the  $4.7\mu F$  capacitor is determined to not be critical for the Versal FPGA.

Figure 3-17 shows the 0V92 schematic, and Figure 3-18 shows the layout.

Figure 3-17. 0V92 Schematic

Figure 3-18. 0V92 Layout

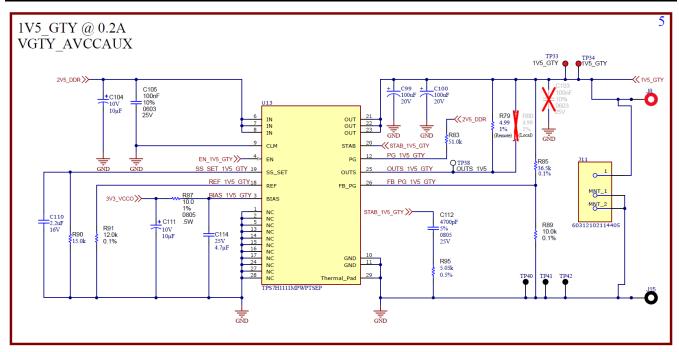

# 3.3.3 1V5\_GTY

The TPS7H1111-SEP is selected to generate the 1.5V rail from the 2V5\_DDR rail (and 3V3\_VCCO for the bias). While the TPS7H1111-SEP is capable of 1.5A, the Versal Edge VGTY\_AVCCAUX rail is estimated to only require 0.05A. Therefore, the LDO is designed for 0.2A maximum to provide reasonable margin.

The  $2x100\mu F$  output capacitors used on the EVM are selected for this design. No additional ceramic decoupling capacitors are added as the TPS7H1111-SEP does not require them for good performance. However, if desired, a 100nF capacitor can be added near the FPGA load (a placeholder in the layout is provided for this purpose). The FB\_PG resistors are sized so that the PG assert threshold occurs at 94.9% of VOUT. This threshold must be carefully selected to make sure that during start-up the TPS7H1111-SEP voltage ramps up within the maximum sequencing timing requirements of the Versal FPGA. Additionally, a  $2.2\mu F$  C<sub>SS</sub> capacitor is selected instead of the typical  $4.7\mu F$  capacitor to provide additional timing margin during start-up. The lower noise that is provided by the  $4.7\mu F$  capacitor is determined to not be critical for the Versal FPGA.

Figure 3-19 shows the 1V5\_GTY schematic and Figure 3-20 shows the layout.

Figure 3-19. 1V5\_GTY Schematic

Figure 3-20. 1V5\_GTY Layout

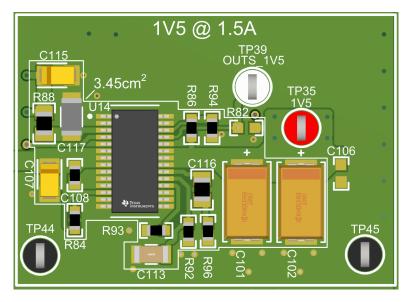

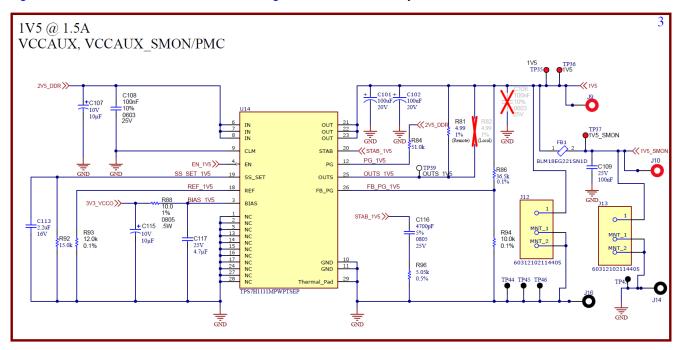

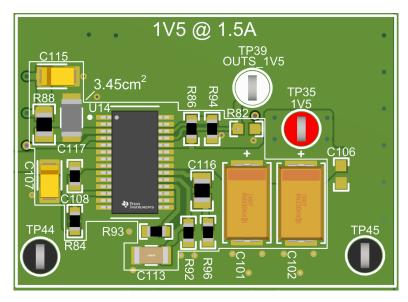

#### 3.3.4 1V5

The TPS7H1111-SEP is selected to generate the 1.5V rail from the 2V5\_DDR rail (and 3V3\_VCCO for the bias). The Versal Edge VCCAUX requires 0.7A and the VCCAUX\_SMON and VCCAUX\_PMC requires 0.3A. To provide margin, the LDO is designed for the maximum current of 1.5A.

The  $2x100\mu F$  output capacitors used on the EVM are selected for this design. No additional ceramic decoupling capacitors are added at the output of the TPS7H1111-SEP. The VCCAUX\_SMON rail is recommended to have an additional ferrite bead filter. After the ferrite bead, a single 100nF capacitor is placed to stay well within the recommended output filter of the TPS7H1111-SEP. With this filter and the high PSRR of the TPS7H1111-SEP, a low-noise SMON rail is created. The FB\_PG resistors are sized so that the PG assert threshold occurs at 94.9% of VOUT. This threshold must be carefully selected to make sure that during start-up the TPS7H1111-SEP voltage ramps up within the maximum sequencing timing requirements of the Versal FPGA. Additionally, a  $2.2\mu F$  C<sub>SS</sub> capacitor is selected instead of the typical  $4.7\mu F$  capacitor to provide additional timing margin during

start-up. The lower noise that is provided by the  $4.7\mu F$  capacitor is determined to not be critical for the Versal FPGA.

Note that the output connector for 1V5 shows a maximum current of 1.5A and the 1V5\_SMON connector shows a maximum current of 0.4A . If these connectors are loaded at the same time, it is important to make sure the connectors are not loaded at more than 1.5A combined.

Figure 3-21 shows the 1V5 schematic and Figure 3-22 shows the layout.

Figure 3-21. 1V5 Schematic

Figure 3-22. 1V5 Layout

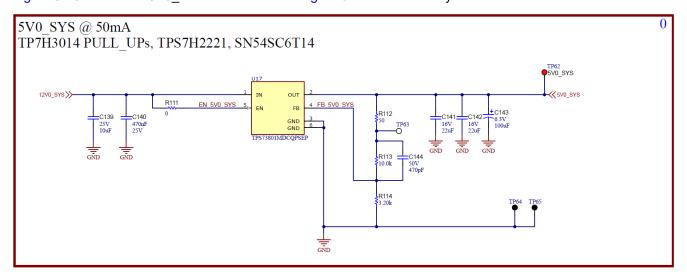

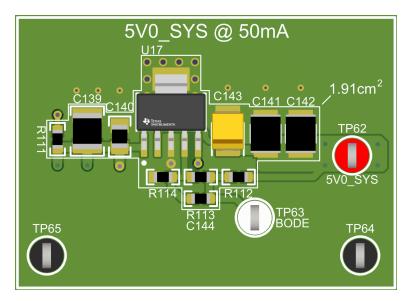

# 3.3.5 5V0\_SYS

The TPS73801-SEP is selected to generate the 5.0V rail from the 12V0\_SYS rail. This rail is used to power the TPS7H3014-SP pullup inputs and power for the TPS7H2221-SEP devices. These are all relatively low power. The TPS73801 is sized for 50mA for plenty of margin.

Output capacitors of 1x100µF + 2x22µF are selected for the output. EN is tied high to start-up right away so that this rail is usable for the TPS7H2221 and TPS7H3014 as soon as possible.

Figure 3-23 shows the 5V0\_SYS schematic and Figure 3-24 shows the layout.

Figure 3-23. 5V0\_SYS Schematic

Figure 3-24. 5V0\_SYS Layout

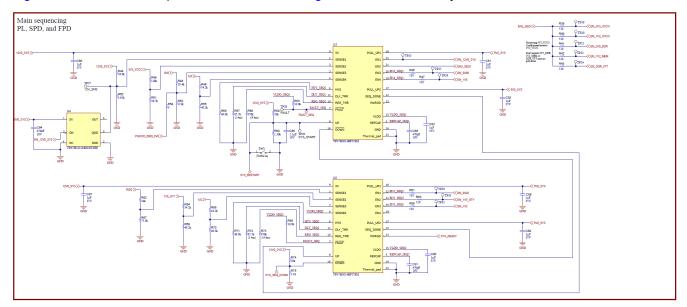

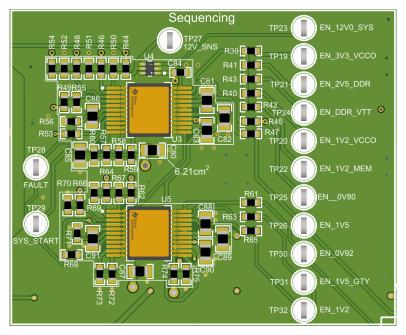

### 3.4 Sequencing

### 3.4.1 TPS7H3014-SP Sequencer

The Versal Edge has specific sequence up and sequence down requirements. Two TPS7H3014-SP devices are utilized in a daisy chain configuration to sequence the six Versal rails up in order and sequence down in reverse order. Table 3-7 shows the sequencer number of each rail. Since the TPS7H3014-SP devices monitor the rail voltage, the actual voltage thresholds for on and off can be programmed with a resistor divider as also shown in the table.

Table 3-7. Sequencing Order

| SEQUENCE<br>NUMBER | RAIL MONITORED AND SEQUENCED | OTHER RAILS<br>SEQUENCED                          | R <sub>TOP</sub> | R <sub>BOTTOM</sub> | V <sub>ON-NOMINAL</sub> (V) | V <sub>ON-NOMINAL</sub> (%) | V <sub>OFF-NOMINAL</sub> (V) | V <sub>OFF-NOMINAL</sub> (%) |

|--------------------|------------------------------|---------------------------------------------------|------------------|---------------------|-----------------------------|-----------------------------|------------------------------|------------------------------|

| 1                  | 3V3_VCCO                     | 1V2_VCCO,<br>2V5_DDR_VPP,<br>1V2_MEM,<br>VTT(DDR) | 118kΩ            | 28.7kΩ              | 3.064V                      | 92.84% ± 0.93%              | 0.226V                       | 6.85% ± 2.74%                |

| 2                  | VCCINT (0V80)                | None                                              | 29.4kΩ           | 111kΩ               | 0.758V                      | 94.76% ± 0.95%              | 0.051V                       | 6.39% ± 2.82%                |

| 3                  | 1V5                          | None                                              | 54.2kΩ           | 40.2kΩ              | 1.407V                      | 93.83% ± 0.94%              | 0.104V                       | 6.93% ± 2.77%                |

| 4                  | 0V92                         | None                                              | 34kΩ             | 75kΩ                | 0.871V                      | 94.68% ± 0.95%              | 0.053V                       | 5.81% ± 2.83%                |

| 5                  | 1V5_GTY                      | None                                              | 54.2kΩ           | 40.2kΩ              | 1.407V                      | 93.83% ± 0.94%              | 0.104V                       | 6.93% ± 2.77%                |

| 6                  | 1V2                          | None                                              | 44.2kΩ           | 49.3kΩ              | 1.137V                      | 94.72% ± 0.95%              | 0.074V                       | 6.15% ± 2.82%                |

| 7 <sup>(1)</sup>   | 12V0_SYS                     | None                                              | 56.9kΩ           | 3.61kΩ              | 10.046V                     | 83.72% ± 0.84%              | 8.678V                       | 72.32% ± 0.90%               |

<sup>(1)</sup> This rail is used to supervise the 12V0\_SYS rail and the TPS7H2221-SEP is used to hold down the SENSE1 during start-up.

The TPS7H3014-SP begins a sequence up when a rising voltage on 12V0\_SYS is detected (after a small delay). Similarly, when the 12V0\_SYS is falling, a sequence down is started. This sequence down helps protect the supplies in a brownout event. Table 3-8 shows these details.

Table 3-8. Up and Down Sequencing

| SEQUENCE | R <sub>TOP</sub> | R <sub>BOTTOM</sub> | VIN, min | VIN, typ | VIN, max | COMMENT                                                                                                                                            |

|----------|------------------|---------------------|----------|----------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| UP       | 20kΩ             | 1.3kΩ               | 9.50V    | 9.80V    | 10.08V   | Sequence up begins before VIN > approximately 10V. 1.5µF capacitor for delay (1.9ms time constant)                                                 |

| DOWN     | 20kΩ             | 1.1kΩ               | 9.26V    | 9.55V    | 9.82V    | Sequence down when VIN falls < approximately 9.6V. If not completed before VIN < approximately 8.678V, shutdown to protect core and other supplies |

Figure 3-25 shows the sequencer schematic and Figure 3-26 shows the layout.

Figure 3-25. Sequencing Schematic

Figure 3-26. Sequencing Layout

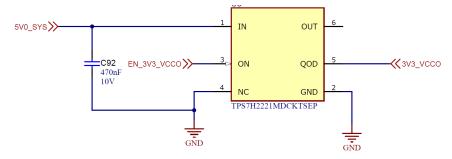

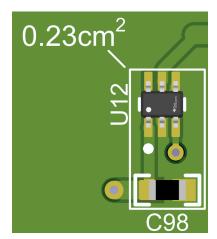

### 3.4.2 TPS7H2221-SEP Discharge Circuit

The Versal FPGA requires rails to sequence up within a specific amount of time. This is easily attainable with typical soft start times used for the voltage regulators. However, when sequencing down these rails, without an active discharge, the rails can take too long to sequence off.

To implement an active discharge, typically an additional MOSFET can be used. However, depending on the specific implementation, additional support circuitry can be required and radiation-tolerant MOSFETs can be fairly large. Instead, the TPS7H2221-SEP load switch with a quick output discharge (QOD) is used to accomplish the active discharge. This small design only makes use of the QOD pin and a small decoupling capacitor to power the device. This design is used for all auxiliary power rails that have discharge requirements.

Figure 3-27. Discharge Schematic

Figure 3-28. Discharge Layout

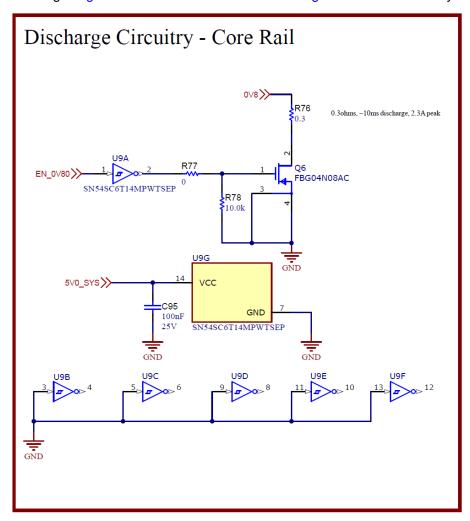

### 3.4.3 VCCINT Discharge Circuit

Similar to many of the auxiliary rails, the 0V8 (VCCINT) core rail also requires an active discharge to shutdown within the required time. However, due to the large capacitance on this rail, the TPS7H2221-SEP design does not discharge the rail in a sufficient time.

Instead, an inverter and a GaN FET is used to discharge this rail. A resistor is used to prevent large current peaks during this discharge. Figure 3-29 shows the schematic and Figure 3-30 shows the layout.

Figure 3-29. VCCINT Discharge Schematic

Figure 3-30. VCCINT Discharge Layout

# 4 Hardware, Testing Requirements, and Test Results

# 4.1 Hardware Requirements

- TIDA-050088 Reference Design Board

- DC Power Supply capable of 12V and 7A (4A sufficient if not fully loading the TIDA)

- Electronic Load (44A)

- Multimeter

- Oscilloscope

- Function generator (for VCCINT load steps)

### 4.2 Test Setup

Connect the power supply to the input terminals (labeled 12V0\_SYS) and make sure the 12V is connected to the red connector and GND is connected to the black connector. To automatically start-up when the power is applied, make sure the sequencer is enabled with SW1 set to Enable. After the power supplies are all sequenced up, the supplies can then be sequenced down with the sequence down button, SW3. The supplies can again be sequenced up with the sequence up button (SW2).

To test individual power supplies, connect the electronic load to the desired output terminals. Multiple loads can be applied simultaneously if desired. The loads are not intended to go above the rated output listed on the board.

#### **CAUTION**

Caution Hot surface. Contact can cause burns. Do not touch!

Some components can reach high temperatures > 55°C when the board is powered on. Do not touch the board at any point during operation or immediately after operating, as high temperatures can be present.

# 4.3 Test Results

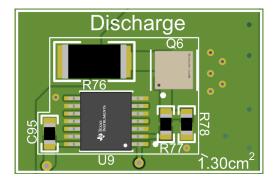

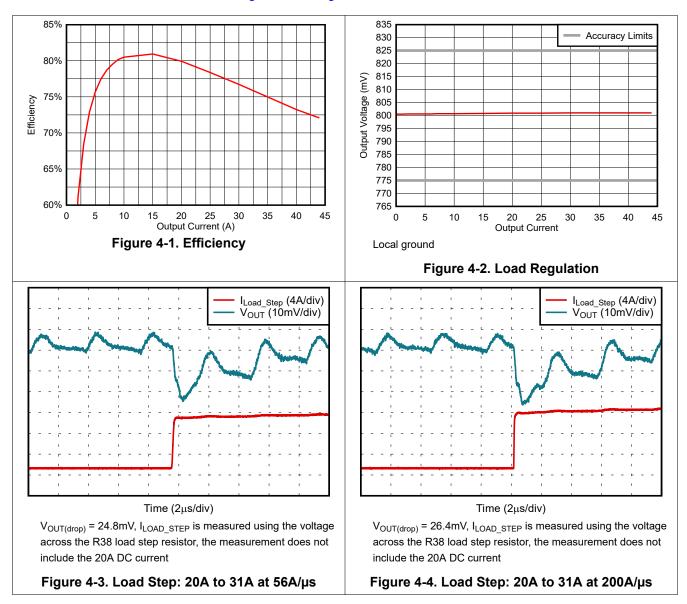

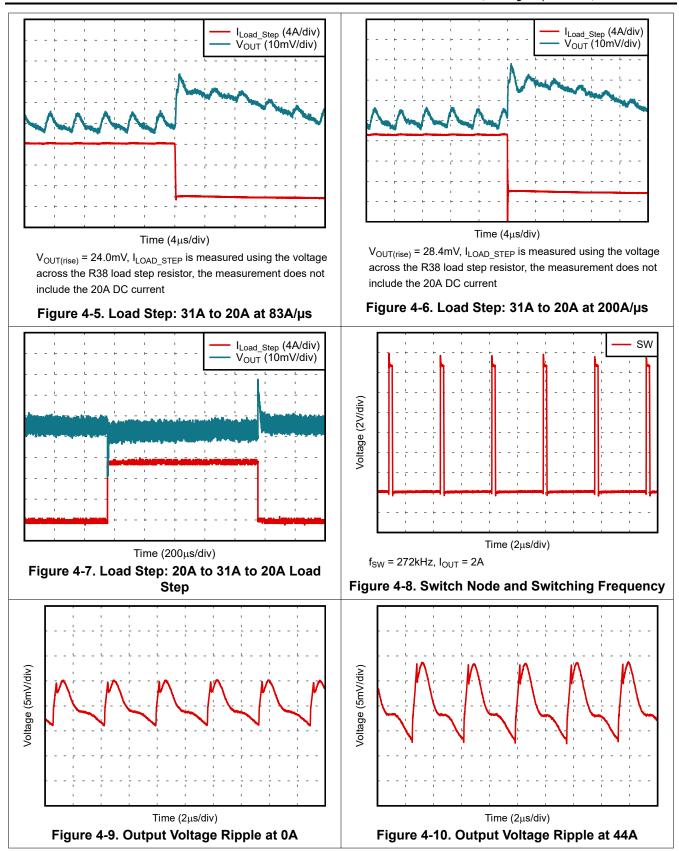

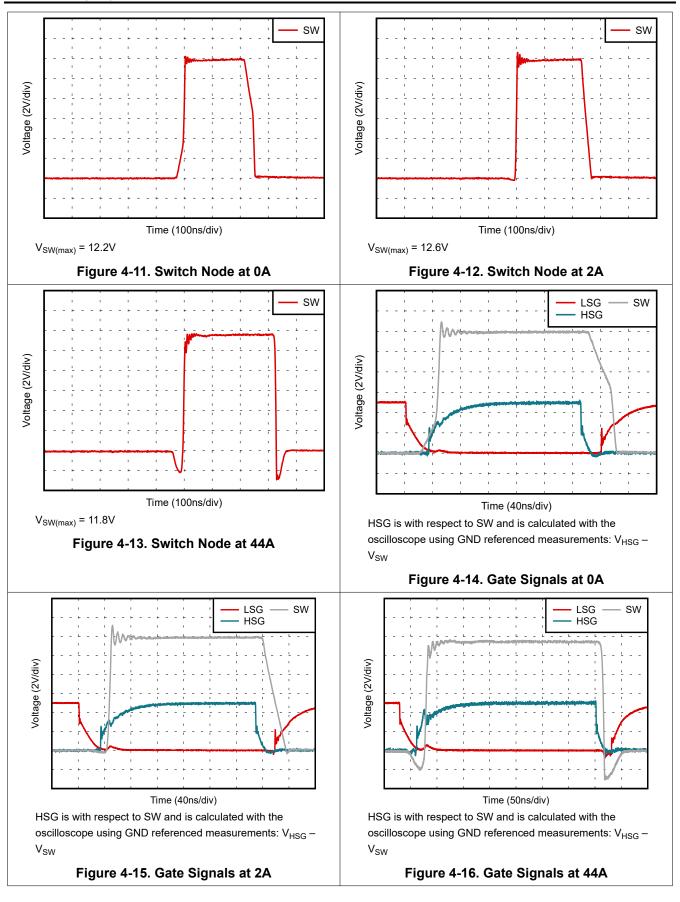

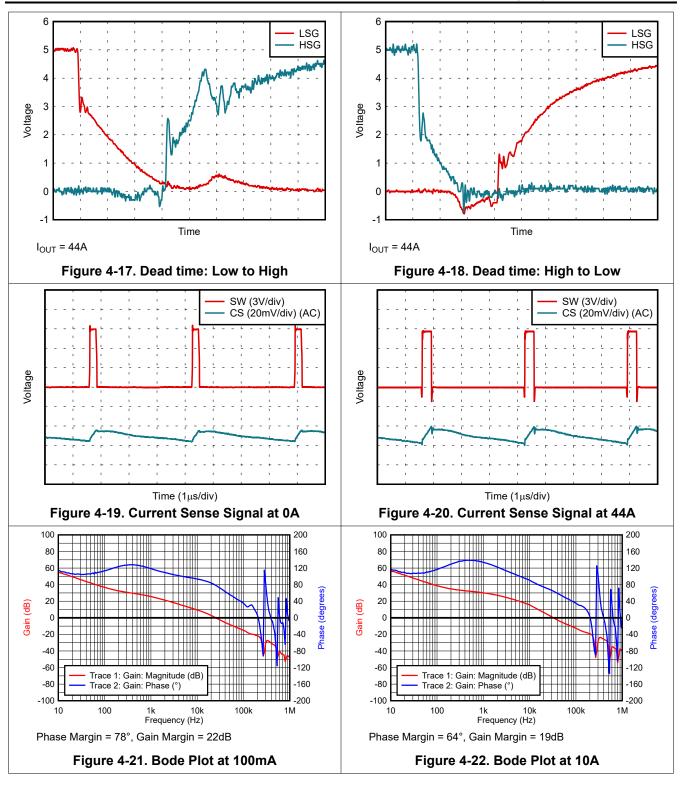

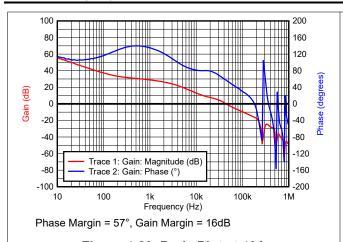

### 4.3.1 Discrete Buck Regulator (VCCINT)

### 4.3.1.1 0V8

Unless otherwise noted, VIN = 12V in Figure 4-1 to Figure 4-27.

Figure 4-24. Bode Plot at 44A

Figure 4-23. Bode Plot at 40A

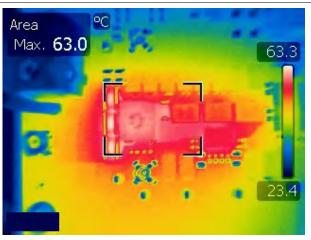

Figure 4-25. Thermals at 30A

Figure 4-26. Thermals at 40A

Figure 4-27. Thermals at 44A

## 4.3.2 Buck Regulators (Integrated)

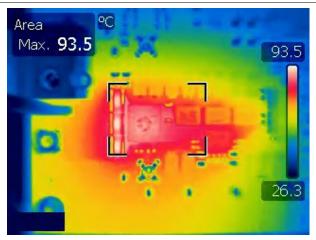

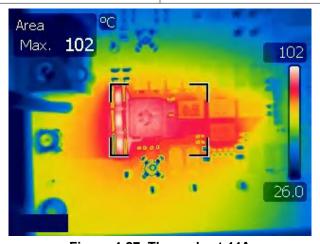

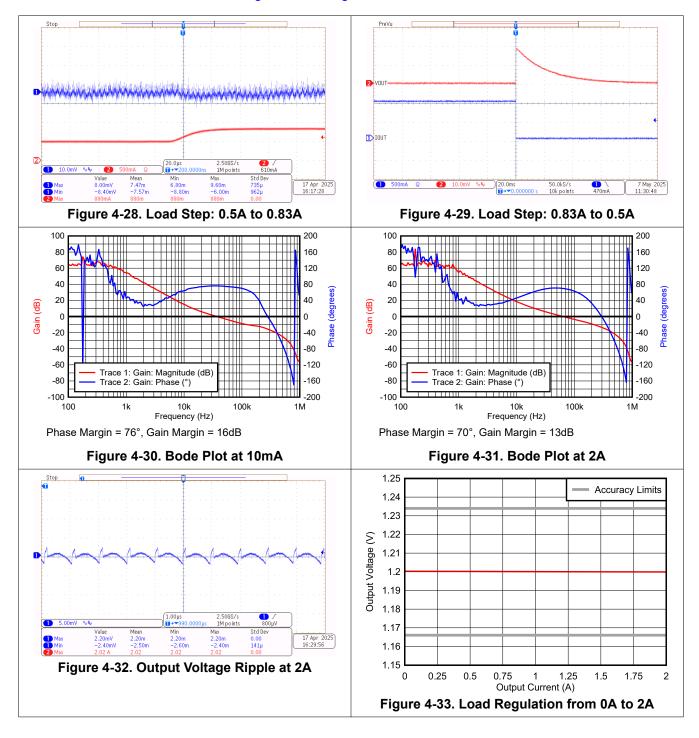

### 4.3.2.1 1V2

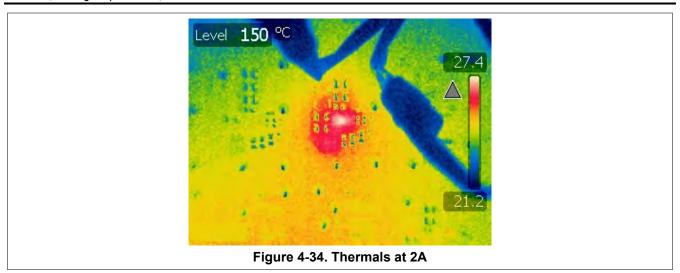

Unless otherwise noted, VIN = 12V in Figure 4-28 to Figure 4-34.

# 4.3.2.2 1V2\_VCCO

Unless otherwise noted, VIN = 12V in Figure 4-35 to Figure 4-41.

# 4.3.2.3 1V2\_MEM

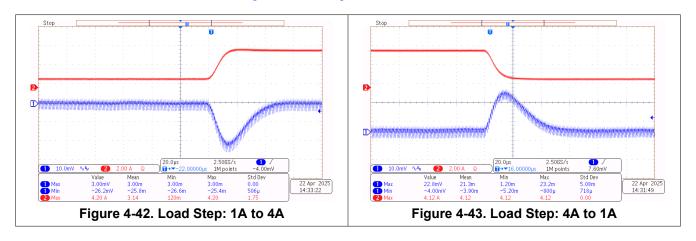

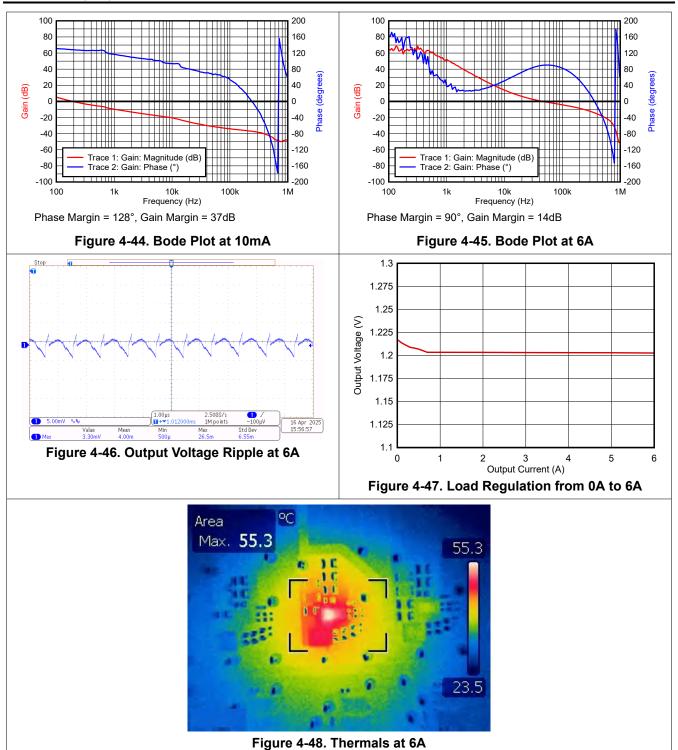

Unless otherwise noted, VIN = 12V in Figure 4-42 to Figure 4-48.

### 4.3.2.4 2V5\_DDR\_VPP

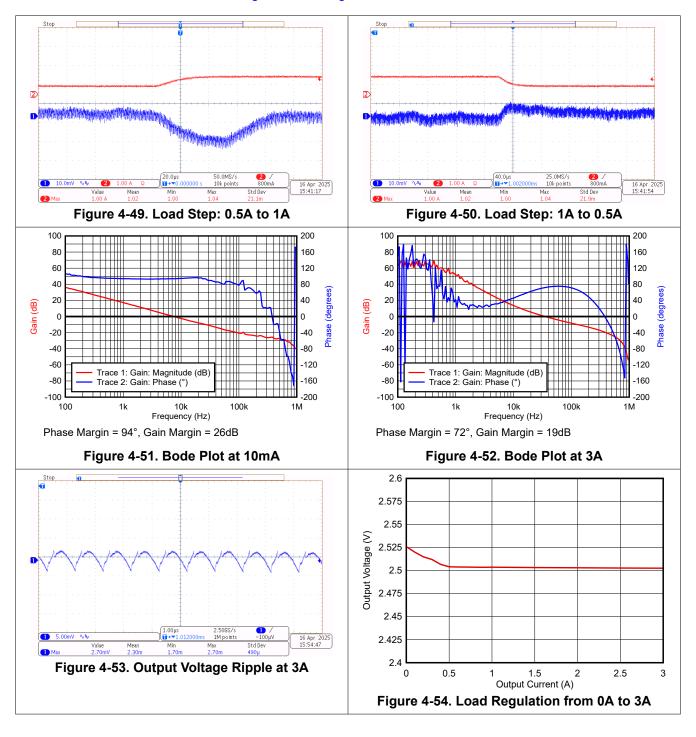

Unless otherwise noted, VIN = 12V in Figure 4-49 to Figure 4-55.

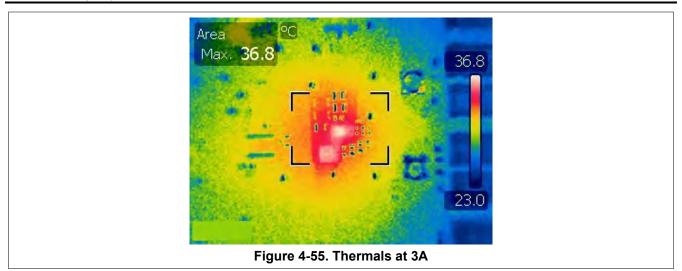

# 4.3.2.5 3V3\_VCCO

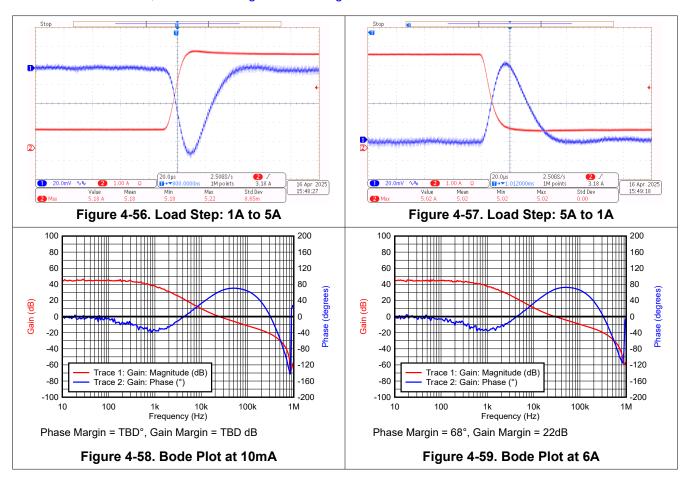

Unless otherwise noted, VIN = 12V in Figure 4-56 to Figure 4-62.

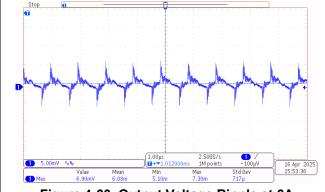

Figure 4-60. Output Voltage Ripple at 6A

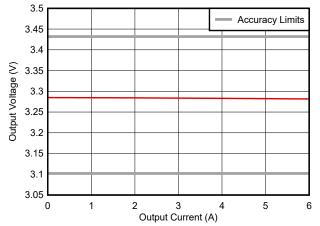

Figure 4-61. Load Regulation from 0A to 6A

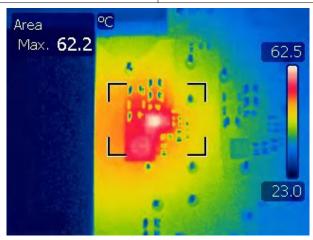

Figure 4-62. Thermals at 6A

# 4.3.3 Linear Regulators

# 4.3.3.1 0V6\_VTT

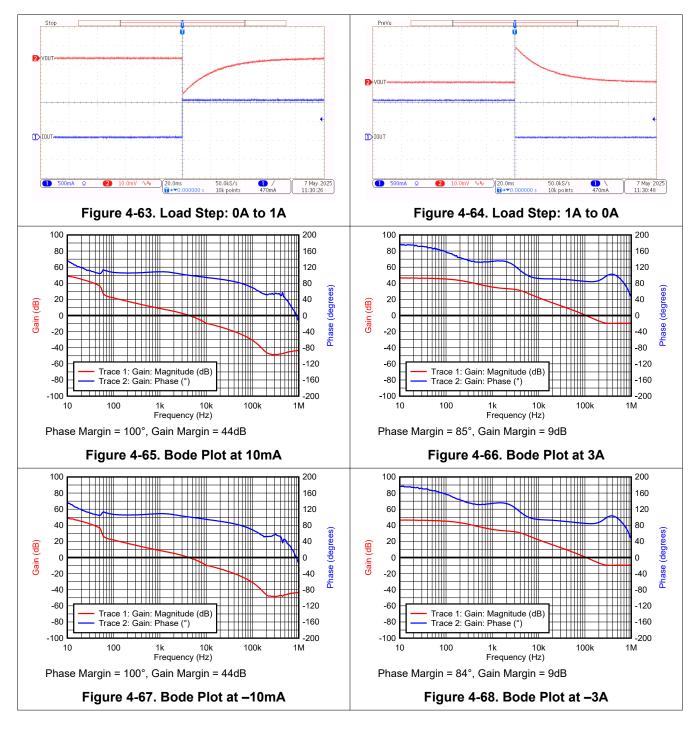

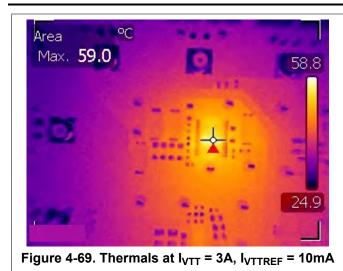

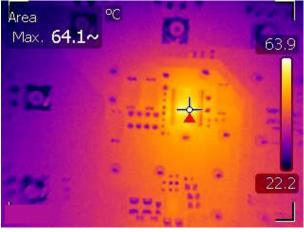

Unless otherwise noted, VIN = 12V in Figure 4-63 to Figure 4-70.

Figure 4-70. Thermals at  $I_{VTT}$  = -3A,  $I_{VTTREF}$  = -10mA

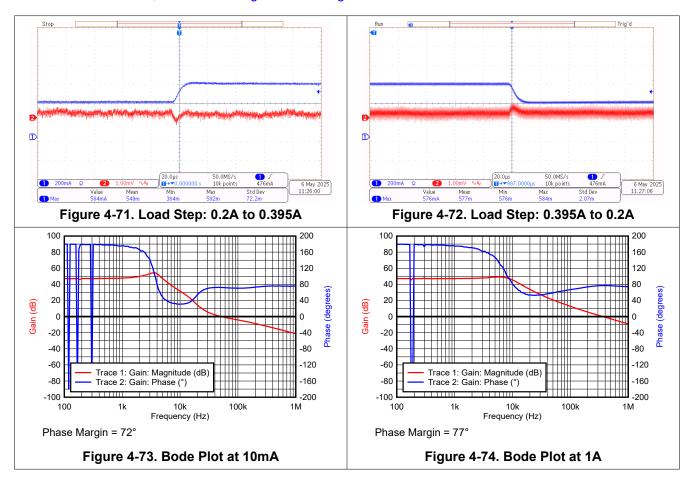

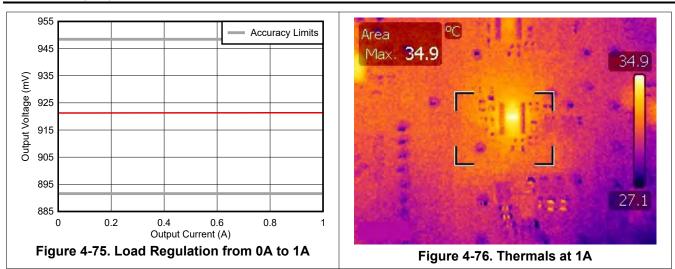

### 4.3.3.2 0V92

Unless otherwise noted, VIN = 12V in Figure 4-71 to Figure 4-76.

# 4.3.3.3 1V5\_GTY

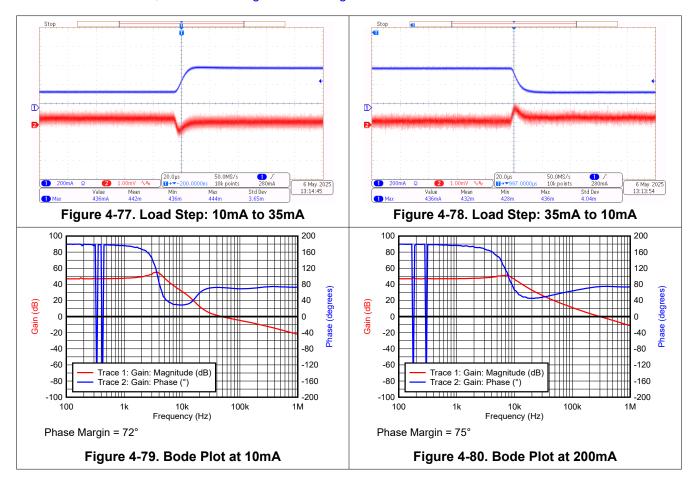

Unless otherwise noted, VIN = 12V in Figure 4-77 to Figure 4-82.

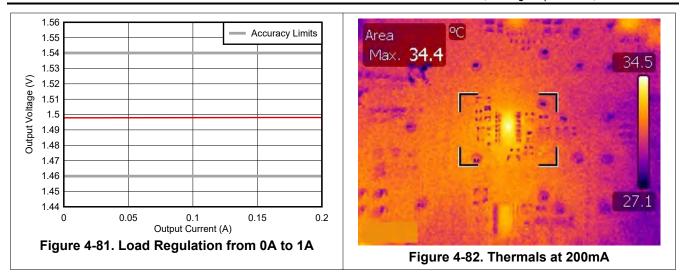

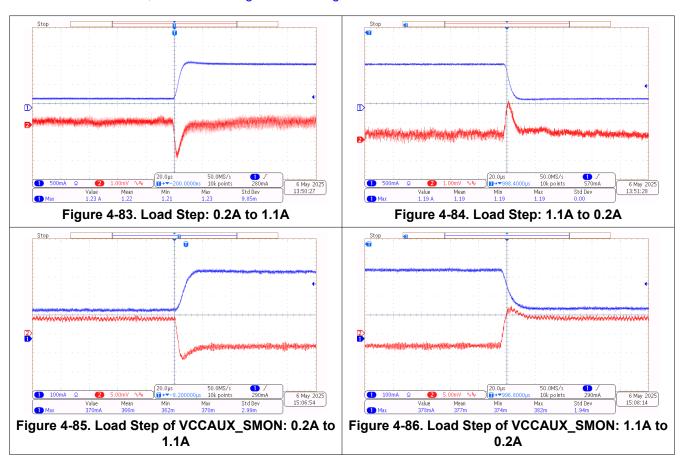

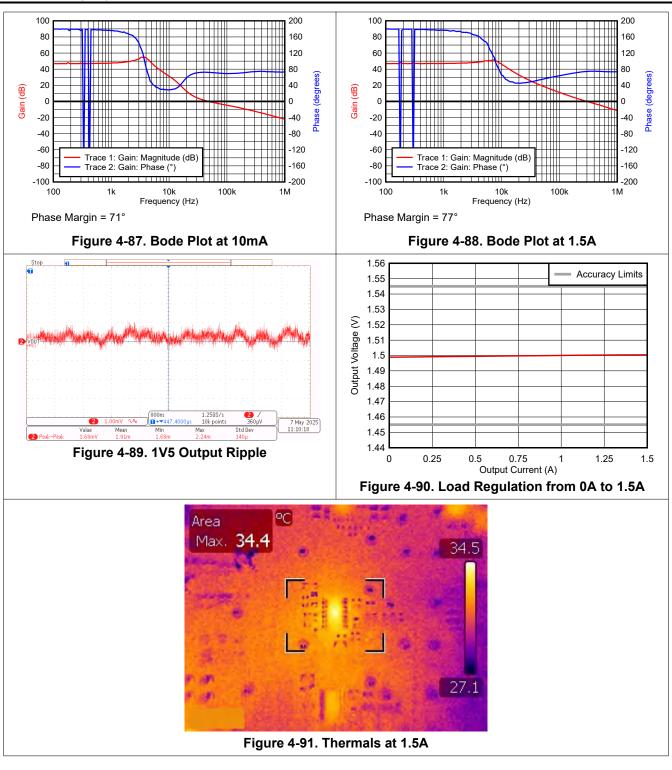

## 4.3.3.4 1V5

Unless otherwise noted, VIN = 12V in Figure 4-83 to Figure 4-91.

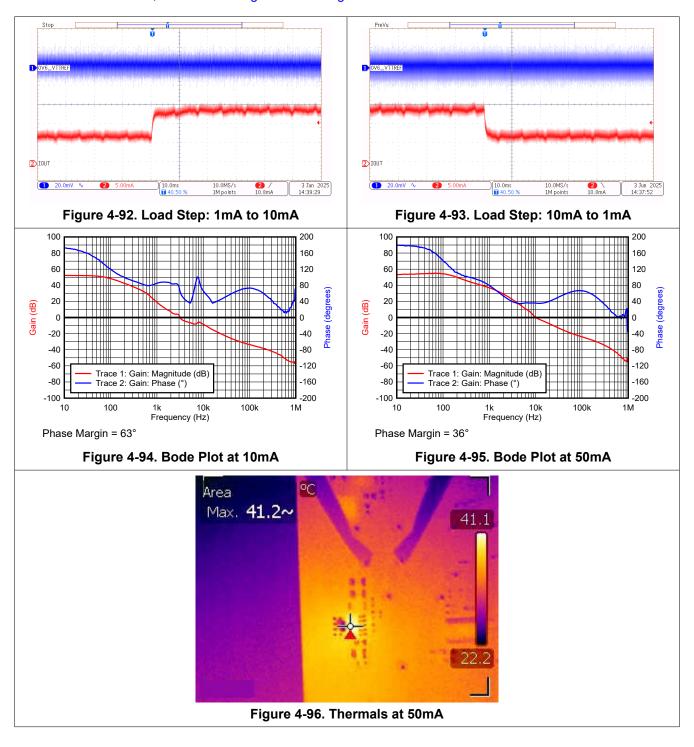

### 4.3.3.5 5V0\_SYS

Unless otherwise noted, VIN = 12V in Figure 4-92 to Figure 4-96.

# 5 Design and Documentation Support

# 5.1 Design Files

### 5.1.1 Schematics

To download the schematics, see the design files at TIDA-050088.

### 5.1.2 BOM

To download the bill of materials (BOM), see the design files at TIDA-050088.

### 5.1.3 Layout Prints

To download the layer plots, see the design files at TIDEP-01036.

# **5.2 Documentation Support**

- 1. Texas Instruments, TPS7H500x-SEP Radiation-Tolerant 2MHz Current Mode PWM Controllers in Space Enhanced Plastic Data Sheet

- 2. Texas Instruments, TPS7H60x5-SP and TPS7H60x5-SEP Radiation-Hardness-Assured Half Bridge GaN FET Gate Drivers Data Sheet

- 3. Texas Instruments, TPS7H1111-SP and TPS7H1111-SEP 1.5-A, Ultra-Low Noise, High PSRR Radiation Hardened Low Dropout (LDO) Linear Regulator Data Sheet

- 4. Texas Instruments, TPS7H4010-SEP Radiation Hardened 3.5-V to 32-V, 6-A Synchronous Step-Down Voltage Converter in Space Enhanced Plastic Data Sheet

- 5. Texas Instruments, TPS73801-SEP 1-A Low-Noise Fast-Transient-Response Low-Dropout Regulator in Space Enhanced Plastic Data Sheet

- 6. Texas Instruments, TPS7H3302-SP and TPS7H3302-SEP 3-A DDR Radiation Hardened Termination Regulator Data Sheet

- 7. Texas Instruments, TPS7H3014-SP and TPS7H3014-SEP Radiation-Hardened, 14V, 4-Channel Sequencer Data Sheet

- 8. Texas Instruments, TPS7H2221-SEP Radiation Tolerant 5.5-V, 1.25-A, 115-mΩ Load Switch Data Sheet

- 9. Texas Instruments, SN54SC6T14-SEP Radiation Tolerant, Hex Schmitt-Trigger Inverters With Integrated Translation Data Sheet

# **5.3 Support Resources**

TI E2E<sup>™</sup> support forums are an engineer's go-to source for fast, verified answers and design help — straight from the experts. Search existing answers or ask your own question to get the quick design help you need.

Linked content is provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

### 5.4 Trademarks

Versal<sup>™</sup> is a trademark of AMD.

TI E2E<sup>™</sup> is a trademark of Texas Instruments.

Kemet<sup>™</sup> is a trademark of Kemet Electronics Corporation.

All trademarks are the property of their respective owners.

### 6 About the Author

**KYLE RAKOS** is the Systems Manager for the Space Power Product Line at Texas Instruments where he is responsible for the road map of radiation-hardened and radiation-tolerant power parts. He earned his Bachelors of Science degree in Computer Engineering from Purdue University in 2017. Kyle thanks Daniel Hartung, Bhavika Kagathi, and Elizabeth Ann Won for the assistance on this design and paper.

notice of the need to comply with such laws and regulations to any person, firm, or entity which it has reason to believe is obtaining any such Hardware from Designer with the intention of exportation. If government approvals cannot be obtained by TI, TI may terminate, cancel, or otherwise be excused from performing any obligations it may have under these terms.

Without limiting the generality of the foregoing, Designer further agrees that Hardware may not be exported, re-exported, transferred, purchased, or resold for a military end-use or to a military end-user in a country listed in EAR Supplement No. 1 to Part 740, Country Group D1, without prior authorization from BIS, OFAC, or any other responsible U.S. Government agency and in compliance with the EAR and any other applicable U.S. Government regulation. The term "military end-use" means incorporation into a military item described on the U.S. Munitions List ("USML") (22 Code of Federal Regulations Part 121, International Traffic in Arms Regulations) or the International Munitions List ("IML") (as set out on the Wassenaar Arrangement website at www.wassenaar.org); or commodities classified under Export Control Classification Numbers ("ECCNs") ending in "A018" or under "600 series" ECCNs. The term "military end-user" means the national guard and national police, government intelligence or reconnaissance organizations, or any person or entity whose actions or functions are intended to support a military end-use. Designer further acknowledges and agrees that Hardware may not be exported, re-exported, transferred, or resold, directly or indirectly, for the design, development, fabrication, or use of nuclear, chemical, or biological weapons or missile technology without U.S. Government authorization.

Requests by Designer for TI to provide assistance or services in connection with the integration of Hardware into any military end-use item must be approved in advance by TI in writing for export control purposes and TI's ability to provide any such assistance to Designer is conditioned upon obtaining any U.S. government export authorization that may be required. TI is not obligated to provide such assistance or services. SSZZ034 Page 3

Any Hardware export classification made by TI will be for TI's internal use only and will not be construed as a representation or warranty regarding the proper export classification for such Hardware or whether an export authorization is required for the exportation of such Hardware.

TI HARDWARE IS PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING THE HARDWARE OR USE OF THE HARDWARE, INCLUDING BUT NOT LIMITED TO ANY IMPLIED WARRANTIES OF FITNESS FOR A PARTICULAR PURPOSE AND NON- INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY DESIGNER AGAINST ANY CLAIMS RELATED TO THE USE, HANDLING, OR DISPOSITION OF THE HARDWARE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF THE HARDWARE OR USE OF THE HARDWARE, REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

Designer will fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of Designer's non-compliance with the terms and provisions of this Notice

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2025, Texas Instruments Incorporated

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2025. Texas Instruments Incorporated