Test Report: PMP21519

# Wide input voltage SEPIC converter power supply reference design for industrial applications

#### **Description**

This SEPIC converter operates over an input voltage range of 10 V - 100 V and provides a non-isolated output of 12 V/1 A. Once operating, the 12-V output supplies bias power to the control circuit, allowing operation below 10 Vin. With efficiency greater than 85%, this converter can tolerate multiple input rail ranges, allowing one converter to satisfy many applications.

TIDT069 - January 2019

# 1 Test Prerequisites

## 1.1 Voltage and Current Requirements

Table 1.

Voltage and Current Requirements

| PARAMETER            | SPECIFICATIONS |

|----------------------|----------------|

| Input voltage range  | 10 V – 100 V   |

| SEPIC output voltage | 12 V           |

| SEPIC output current | 1 A            |

| Switching frequency  | 200kHz         |

# 1.2 Required Equipment

- Power supply capable of 100 V and 3 A

- 5 A Active or resistive load

- Digital Multimeters

- 500 MHz oscilloscope and probes

- Stability measurement device (Venable)

# 2 Testing and Results

## 2.1 Efficiency and Regulation Graphs

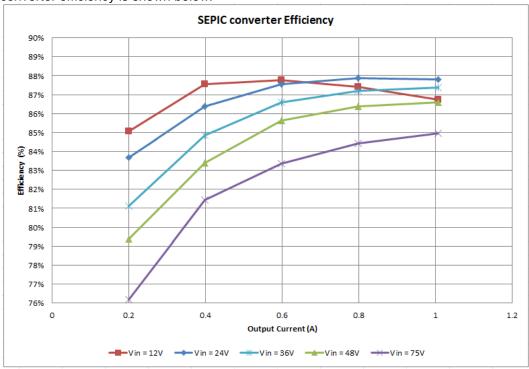

The SEPIC converter efficiency is shown below.

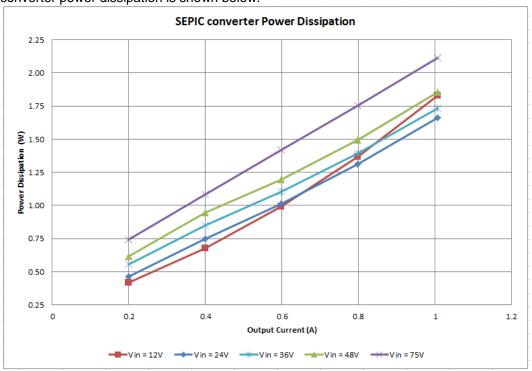

The SEPIC converter power dissipation is shown below.

## 2.2 SEPIC Loop Gain

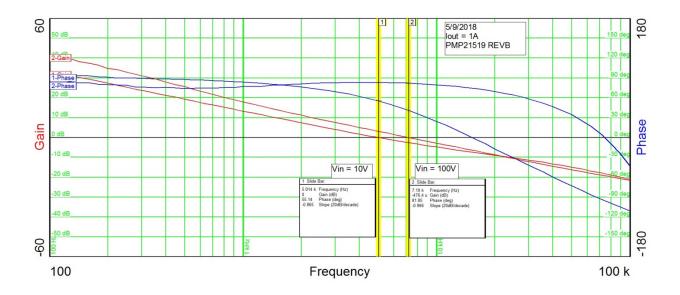

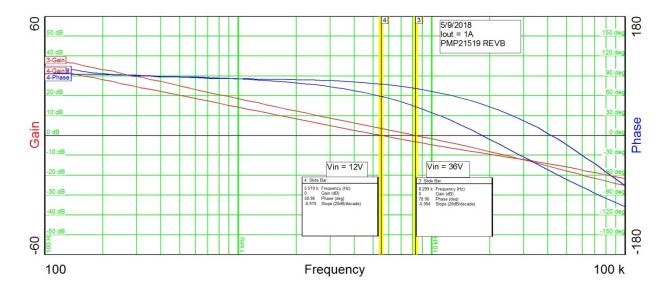

The plots below shows the loop gain with the output loaded at 1 A.

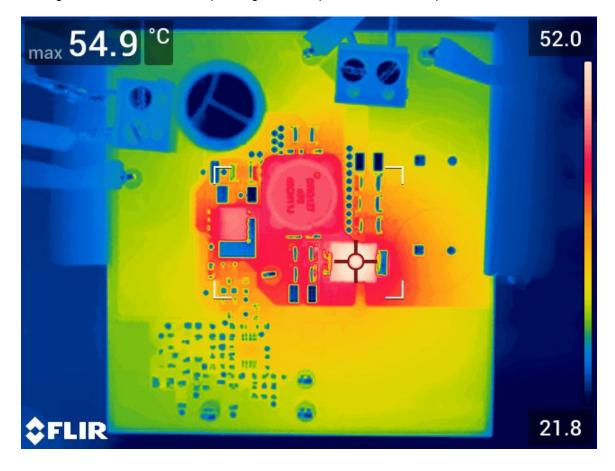

# 2.3 Thermal Image

A thermal image is shown below when operating at 36 V input, 12 V @ 1 A output and no air flow.

## 3 Waveforms

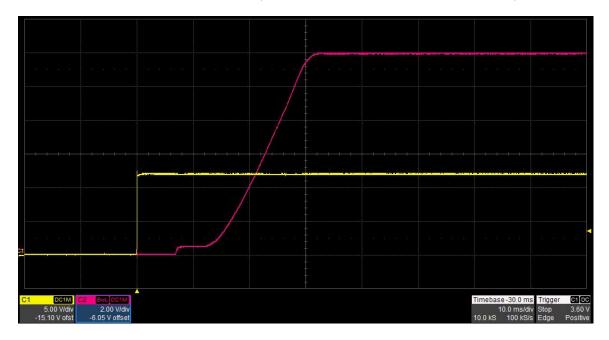

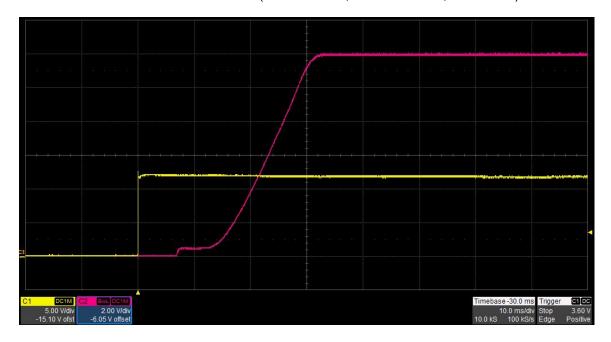

### 3.1 Startup

The photo below shows the 12 V output voltage startup waveforms after the application of 12 Vdc input. The output was loaded with to 0 A. (Vin is 5 V/DIV, Vout is 2 V/DIV, 10 mS/DIV)

The photo below shows the 12 V output voltage startup waveforms after the application of 12 Vdc input. The output was loaded with to 1 A. (Vin is 5 V/DIV, Vout is 2 V/DIV, 10 mS/DIV)

## 3.2 Output Ripple Voltage

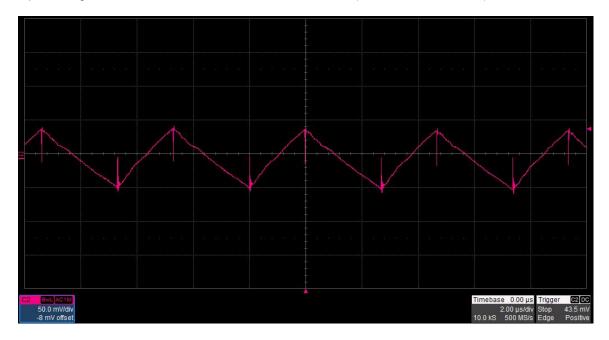

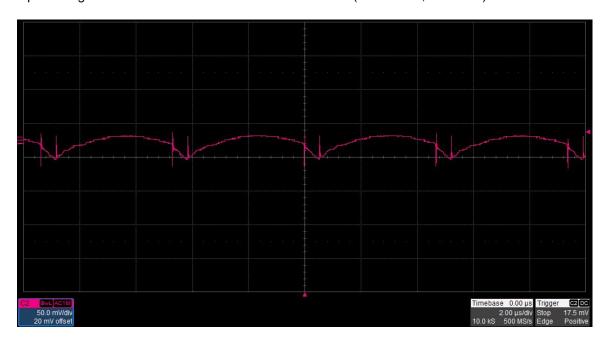

The 12 V output ripple voltage is shown in the figure below. The image was taken with the output loaded to 1 A and the input voltage set to 10 Vdc. (50 mV/DIV, 2 uS/DIV)

The 12 V output ripple voltage is shown in the figure below. The image was taken with the output loaded to 1 A and the input voltage set to 100 Vdc. (50 mV/DIV, 2 uS/DIV)

#### 3.3 Switch Node Waveforms

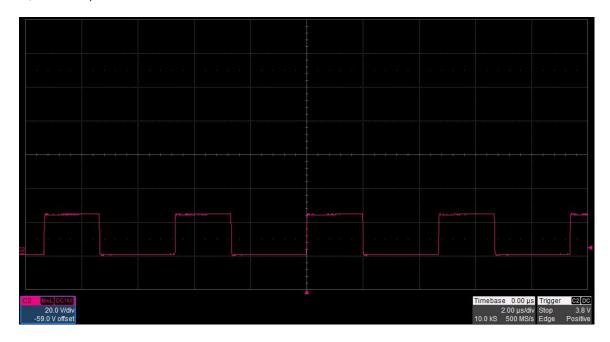

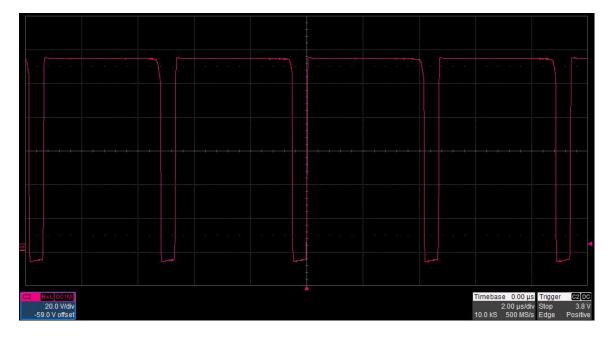

The photo below is the N-ch FET drain waveform. The input voltage is 10 V and the output is loaded to 1 A. (20 V/DIV, 2 uS/DIV)

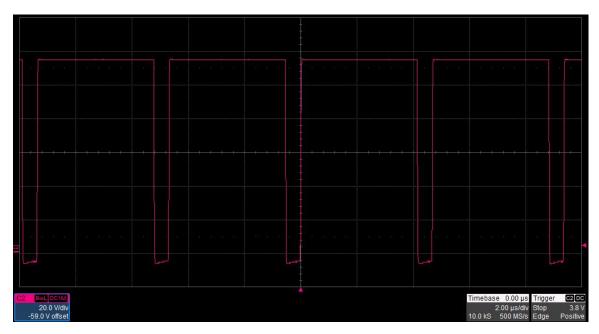

The photo below is the N-ch FET drain waveform. The input voltage is 100 V and the output is loaded to 1 A. (20 V/DIV, 2 uS/DIV)

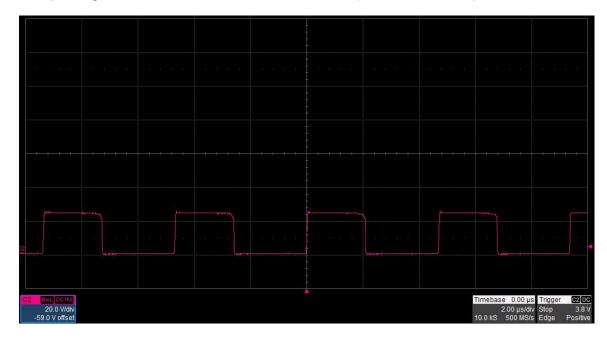

The photo below is the N-ch FET drain waveform. The input voltage is 10 V and the output is loaded to 0.1 A. The converter is operating in DCM. (20 V/DIV, 2 uS/DIV)

The photo below is the N-ch FET drain waveform. The input voltage is 100 V and the output is loaded to 0.45 A. The converter is operating in DCM. (20 V/DIV, 2 uS/DIV)

#### 3.4 Load Transient

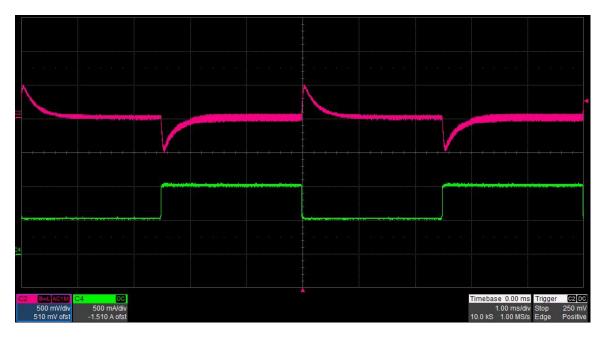

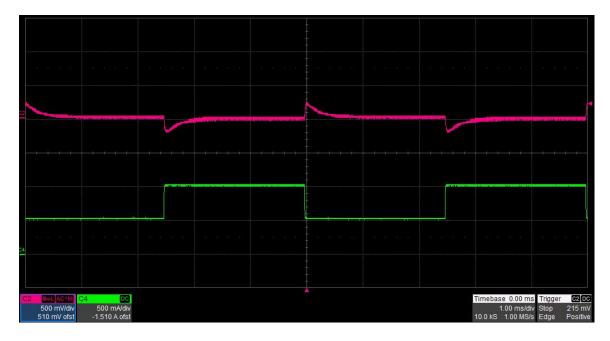

The photo below shows the 12 V output voltage (top, ac coupled) when the load current is stepped between 0.5 A to 1 A. Vin = 10 Vdc (500 mV/DIV, 500 mA/DIV, 1 mS/DIV)

The photo below shows the 12 V output voltage (top, ac coupled) when the load current is stepped between 0.5 A to 1 A. Vin = 100V dc (500 mV/DIV, 500 mA/DIV, 1 mS/DIV)

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale (https://www.ti.com/legal/termsofsale.html) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2021, Texas Instruments Incorporated