# **KeyStone II Architecture 10 Gigabit Ethernet Subsystem**

# **User Guide**

Literature Number: SPRUHJ5 February 2013

# **Release History**

| Release | Date          | Description/Comments |

|---------|---------------|----------------------|

| SPRUHJ5 | February 2013 | Initial Release.     |

www.ti.com Contents

# **Contents**

|           | Release History.<br>List of Tables<br>List of Figures<br>List of Procedures                               | ø-iz<br>ø-xiv     |

|-----------|-----------------------------------------------------------------------------------------------------------|-------------------|

|           | Preface About This Manual Notational Conventions Related Documentation from Texas Instruments Trademarks. | ø-xix             |

| Chapter 1 |                                                                                                           |                   |

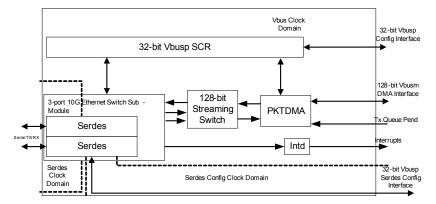

|           | Introduction  1.1 Purpose of the Peripheral                                                               | 1-2<br>1-3<br>1-4 |

| Chapter 2 |                                                                                                           |                   |

|           | Architecture                                                                                              | 2-1               |

|           | 2.1 Clock Control                                                                                         |                   |

|           | 2.1.1 10GbE Subsystem Clock & SerDes Configuration Clock                                                  |                   |

|           | 2.1.2 SerDes Clock Domain                                                                                 |                   |

|           | 2.1.3 MDIO Clock                                                                                          |                   |

|           | 2.1.4 CPTS reference clock                                                                                | 2-2               |

|           | 2.1.5 MAC-MII Clocks                                                                                      |                   |

|           | 2.2 Memory Map                                                                                            |                   |

|           | 2.3 Packet DMA Architecture                                                                               |                   |

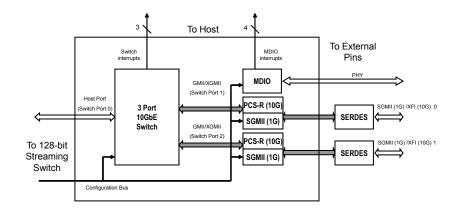

|           | 2.4 10 Gigabit Ethernet Switch Architecture                                                               |                   |

|           | 2.4.1 Streaming Packet Interface                                                                          |                   |

|           | 2.4.1.1 Transmit Streaming Packet Interface                                                               |                   |

|           | 2.4.1.3 Receive Streaming Packet Interface                                                                |                   |

|           | 2.4.2 Media Access Controller Module Architecture                                                         |                   |

|           | 2.4.2.1 Data Receive Operations                                                                           |                   |

|           | 2.4.2.2 Data Transmission                                                                                 | 2-9               |

|           | 2.4.3 MAC FIFO Architecture                                                                               |                   |

|           | 2.4.4 Statistics Module Architecture                                                                      |                   |

|           | 2.4.4.1 Accessing Statistics Registers                                                                    |                   |

|           | 2.4.4.2 Statistics Interrupts                                                                             |                   |

|           | 2.4.4.4 Transmit (only) Statistics Descriptions                                                           |                   |

|           | 2.4.4.5 Receive and Transmit (shared) Statistics Descriptions                                             |                   |

|           | 2.4.5 Time Synchronization Module Architecture                                                            |                   |

|           | 2.4.5.1 Time Synchronization Submodule Components                                                         |                   |

|           | 2.4.5.2 Time Synchronization Events                                                                       | 2-2               |

|           | 2.4.5.3 Time Synchronization Initialization                                                               |                   |

|           | 2.4.5.4 Detecting and Processing Time Synchronization Events                                              |                   |

|           | 2.4.6 Address Lookup Engine (ALE) Module Architecture                                                     |                   |

|           | 2.4.6.1 ALE Table                                                                                         | 2-34              |

www.ti.com

| 2.4.6.2 Reading Entries from the ALE Table                                       |      |

|----------------------------------------------------------------------------------|------|

| 2.4.6.3 Writing Entries to the ALE Table                                         |      |

| 2.4.6.4 ALE Table Entry Types                                                    |      |

| 2.4.6.5 ALE Packet Forwarding Process                                            |      |

| 2.4.6.6 ALE Learning Process                                                     |      |

| 2.4.7 10GbE Additional Features                                                  |      |

| 2.4.7.1 Packet Priority Handling                                                 |      |

| 2.4.7.2 Rate Limiting                                                            |      |

| 2.4.7.4 Flavy Control                                                            |      |

| 2.4.7.4 Flow Control                                                             |      |

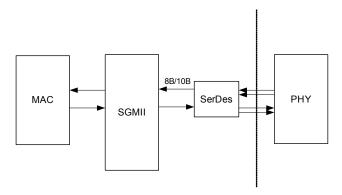

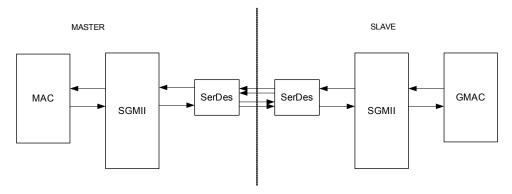

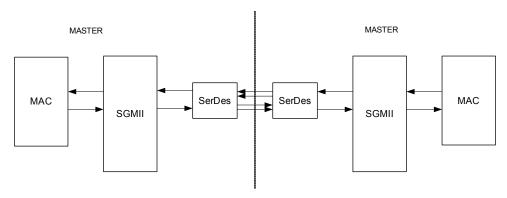

| 2.5 Serial Gigabit Media Independent Interface (SGMII) Architecture              |      |

| 2.5.1 SGMII Receive Interface                                                    |      |

| 2.5.2 SGMII Transmit Interface                                                   |      |

| 2.5.3 Modes of Operation.                                                        |      |

| 2.5.3.1 Digital Loopback                                                         |      |

| 2.5.3.2 SGMII to PHY Configuration                                               |      |

| 2.5.3.3 SGMII to SGMII with Autonegotiation Configuration                        |      |

| 2.5.3.4 SGMII to SGMII with Forced Link Configuration                            |      |

| 2.6 PCS-R                                                                        | 2-54 |

| 2.7 MACSEC Module                                                                | 2-54 |

| 2.7.0.1 MACSEC Architecture                                                      |      |

| 2.7.0.2 MACSEC Egress/Ingress Operations                                         |      |

| 2.8 Management Data Input/Output (MDIO) Architecture                             |      |

| 2.8.1 Global PHY Detection and Link State Monitoring                             |      |

| 2.8.2 PHY Register User Access                                                   |      |

| 2.8.2.1 Writing Data to a PHY Register                                           | 2-57 |

| 2.8.2.2 Reading Data from a PHY Register                                         | 2-58 |

| 2.8.3 MDIO Interrupts                                                            |      |

| 2.8.3.1 MDIO Link Status Interrupts                                              |      |

| 2.8.3.2 MDIO User Access Interrupts                                              |      |

| 2.8.4 Initializing the MDIO Module                                               |      |

| 2.9 Serializer/Deserializer (SerDes) Architecture                                |      |

| 2.10 Reset Considerations                                                        |      |

| 2.11 Initialization                                                              |      |

| 2.12 Interrupt Support                                                           |      |

| 2.12.1 Interrupt Events                                                          |      |

| 2.13 Power Management                                                            | 2-60 |

|                                                                                  |      |

| Registers                                                                        | 3-1  |

| 3.1 Summary of Modules                                                           |      |

| 3.2  10 Gigabit Ethernet (                                                       |      |

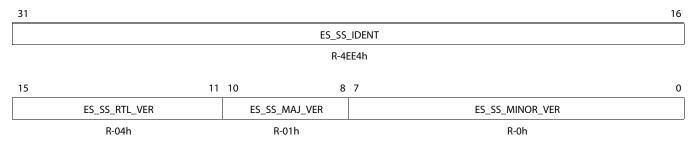

| 3.2.1 10Gigabit Ethernet Switch Submodule Identification and Version Register (E |      |

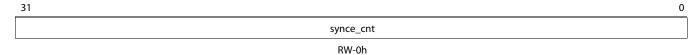

| 3.2.2 Synchronous Ethernet Count Register (SyncE Count)                          |      |

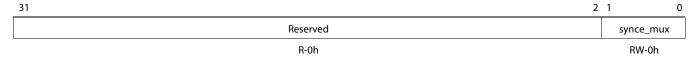

| 3.2.3 Synchronous Ethernet Mux Register (SyncE Mux)                              |      |

| 3.2.4 Submodule Control Register (Control)                                       |      |

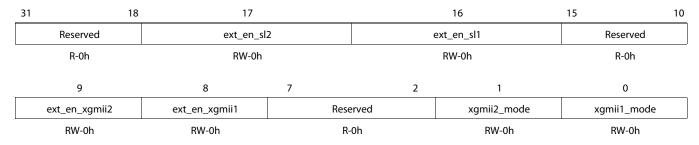

| 3.3 Serial Gigabit Media Independent Interface (SGMII) module                    |      |

| 3.3.1 SGMII Identification and Version Register (SGMII_IDVER)                    |      |

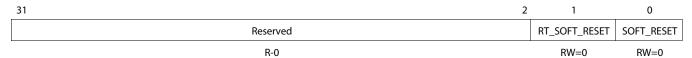

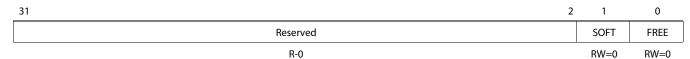

| 3.3.2 Software Reset Register (SOFT_RESET)                                       |      |

| 3.3.3 SGMII Control Register (SGMII_CONTROL)                                     |      |

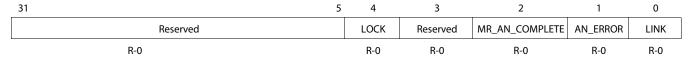

| 3.3.4 Status Register (STATUS)                                                   |      |

| 3.3.5.1 SGMII MODE                                                               |      |

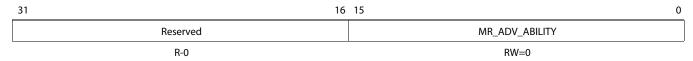

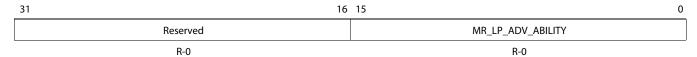

| 3.3.6 Link Partner Advertised Ability Register (MR_LP_ADV_ABILITY)               |      |

| 3.3.0 Ellik Faltilei Advertised Ability Register (MIN_EF_ADV_ABIETT)             |      |

|                                                                                  |      |

Chapter 3

www.ti.com Contents

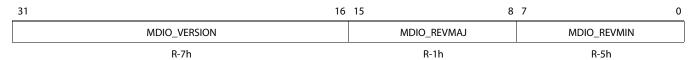

|     | 3.4.1 MDIO Version Register (MDIO_VERSION)                                                        |      |

|-----|---------------------------------------------------------------------------------------------------|------|

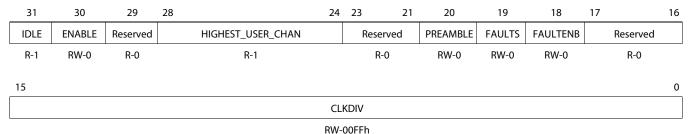

|     | 3.4.2 MDIO Control Register (MDIO_CONTROL)                                                        | 3-19 |

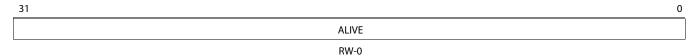

|     | 3.4.3 PHY Alive Status Register (ALIVE)                                                           | 3-20 |

|     | 3.4.4 PHY Link Status Register (LINK)                                                             |      |

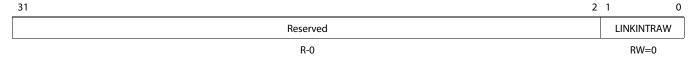

|     | 3.4.5 MDIO Link Status Change Interrupt (Unmasked) Register (LINKINTRAW)                          | 3-21 |

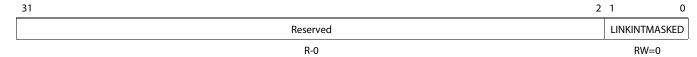

|     | 3.4.6 MDIO Link Status Change Interrupt (Masked) Register (LINKINTMASKED)                         | 3-22 |

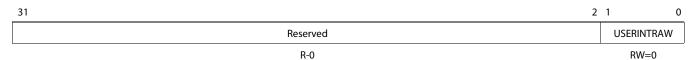

|     | 3.4.7 MDIO User Command Complete Interrupt (Unmasked) Register (USERINTRAW)                       | 3-22 |

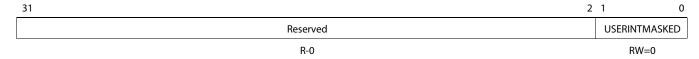

|     | 3.4.8 MDIO User Command Complete Interrupt (Masked) Register (USERINTMASKED)                      | 3-22 |

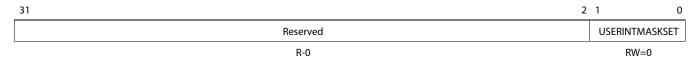

|     | 3.4.9 MDIO User Command Complete Interrupt Mask Set Register (USERINTMASKSET)                     | 3-23 |

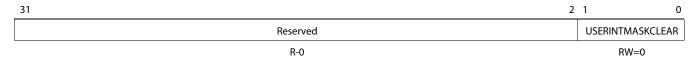

|     | 3.4.10 MDIO User Command Complete Interrupt Mask Clear Register (USERINTMASKCLEAR)                |      |

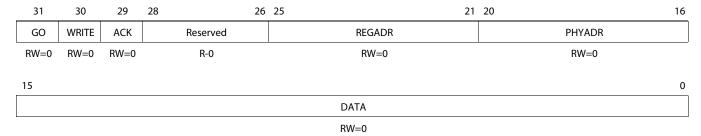

|     | 3.4.11 MDIO User Access Register 0 (USERACCESSO)                                                  | 3-24 |

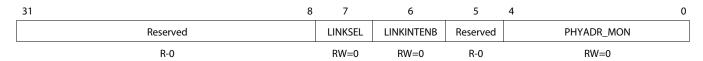

|     | 3.4.12 MDIO User PHY Select Register 0 (USERPHYSEL0)                                              |      |

|     | 3.4.13 MDIO User Access Register 1 (USERACCESS1)                                                  |      |

|     | 3.4.14 MDIO User PHY Select Register 1 (USERPHYSEL1)                                              |      |

| 3.5 | PCS-R Module                                                                                      |      |

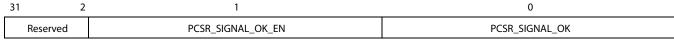

| 0.0 | 3.5.1 PCSR Transmit Control Register (PCSR_TX_CTL)                                                |      |

|     | 3.5.2 PCSR Transmit Status Register (PCSR_Tx_Status)                                              |      |

|     | 3.5.3 PCSR Receive Control Register (PCSR_Rx_Ctl)                                                 |      |

|     | 3.5.4 PCSR Receive Status Register (PCSR_Rx_Status)                                               |      |

|     | 3.5.5 PCSR Seed A Low Register (PCSR_Seed_A_LO)                                                   |      |

|     | 3.5.6 PCSR Seed A Hi Register (PCSR_Seed_A_Hi).                                                   |      |

|     | 3.5.7 PCSR Seed A Til Register (PCSR_Seed_A_TII)  3.5.7 PCSR Seed B Low Register (PCSR_Seed_B_LO) |      |

|     | 3.5.8 PCSR Seed B Hi Register (PCSR_Seed_B_Hi)                                                    |      |

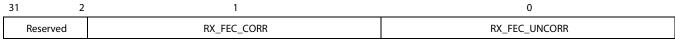

|     | 3.5.9 PCSR Forward Error Correction Register (PCSR_FEC)                                           |      |

|     | 3.5.10 PCSR Control Register (PCSR_CTL)                                                           |      |

|     | 3.5.11 PCSR FEC Count Register (PCSR_FEC_CNT).                                                    |      |

|     |                                                                                                   |      |

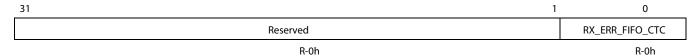

| 2.0 | 3.5.12 PCSR Error FIFO Register (PCSR_ERR_FIFO)                                                   |      |

| 3.6 | 10 Gigabit Ethernet Switch                                                                        |      |

|     | 3.6.1 10Gigabit Ethernet (10GbE) Switch                                                           |      |

|     | 3.6.1.1 10GbE switch Identification and Version Register (CPSW_IDVER)                             |      |

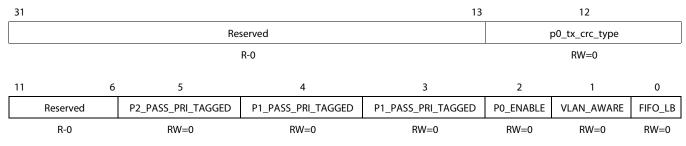

|     | 3.6.1.2 10 GbE switch Control Register (CPSW_CONTROL)                                             |      |

|     | 3.6.1.3 Emulation Control Register (EM_CONTROL)                                                   |      |

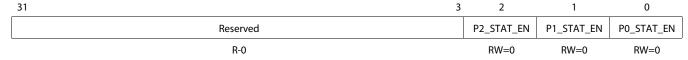

|     | 3.6.1.4 Statistics Port Enable (STAT_PORT_EN)                                                     |      |

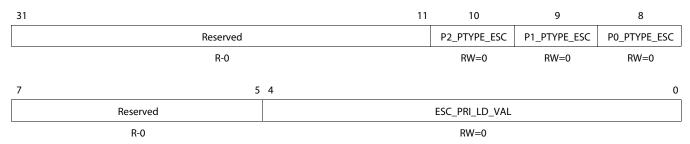

|     | 3.6.1.5 Priority Type Register (PTYPE)                                                            |      |

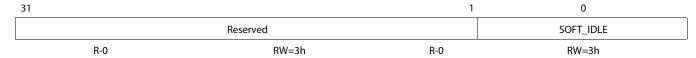

|     | 3.6.1.6 10GbE switch Software Idle Register (CPSW_SOFT_IDLE)                                      |      |

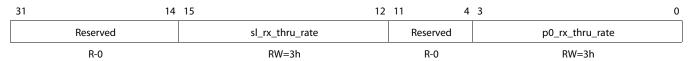

|     | 3.6.1.7 10GbE switch Thru Rate Register (THRU_RATE)                                               |      |

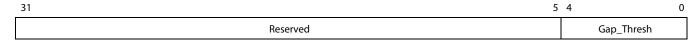

|     | 3.6.1.8 MAC Short Gap Threshold Register (GAP_THRESH)                                             |      |

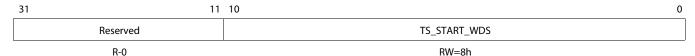

|     | 3.6.1.9 Transmit FIFO Start Words Register (TX_START_WDS)                                         |      |

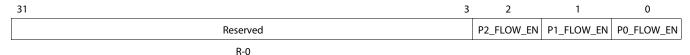

|     | 3.6.1.10 Flow Control Register (FLOW_CONTROL)                                                     |      |

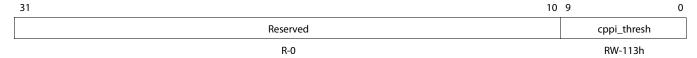

|     | 3.6.1.11 CPPI Threshold                                                                           |      |

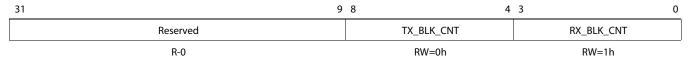

|     | 3.6.1.12 Port0 Block Count (P0_BLK_CNT)                                                           |      |

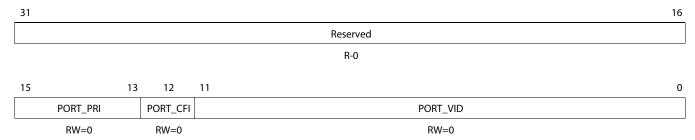

|     | 3.6.1.13 Port 0 VLAN Register (P0_PORT_VLAN)                                                      |      |

|     | 3.6.1.14 Port 0 TX Header Priority to Switch Priority Mapping Register (P0_TX_PRI_MAP)            | 3-41 |

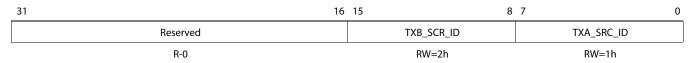

|     | 3.6.1.15 Port0 Source Identification Register (P0_CPPI_SRC_ID)                                    |      |

|     | 3.6.1.16 Port 0 Receive Packet Priority to Header Priority Mapping Register (P0_RX_PRI_MAP)       | 3-42 |

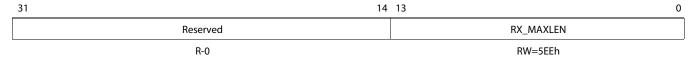

|     | 3.6.1.17 Port 0 Receive Maximum Length Register (P0_RX_MAXLEN)                                    | 3-43 |

|     | 3.6.1.18 Port 1 Block Count Register (P1_BLK_CNT)                                                 | 3-44 |

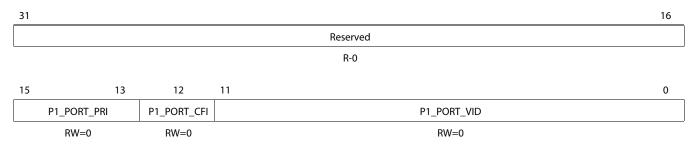

|     | 3.6.1.19 Port 1 VLAN Register (P1_PORT_VLAN)                                                      | 3-44 |

|     | 3.6.1.20 Port 1 Transmit Header Priority to switch Priority Mapping Register (P1_TX_PRI_MAP)      |      |

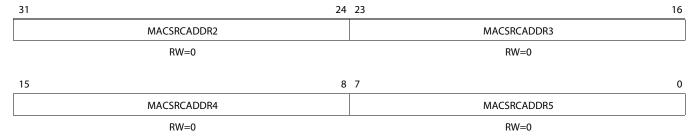

|     | 3.6.1.21 MAC1 Source Address Low Register (MAC1_SA_LO)                                            | 3-46 |

|     | 3.6.1.22 MAC1 Source Address High Register (MAC1_SA_HI)                                           | 3-46 |

|     | 3.6.1.23 Port 1 Time Sync Control Register (P1_TS_CTL)                                            | 3-47 |

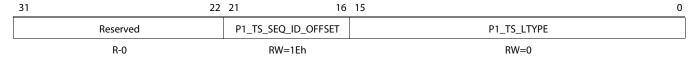

|     | 3.6.1.24 Port 1 Time Sync Sequence ID and LTYPE Register (P1_TS_SEQ_LTYPE)                        | 3-47 |

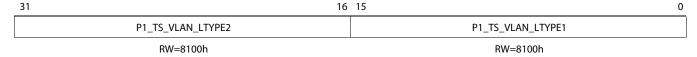

|     | 3.6.1.25 Port 1 Time Sync VLAN LTYPE Register (P1_TS_VLAN_LTYPE)                                  |      |

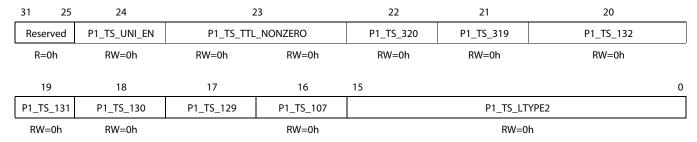

|     | 3.6.1.26 Port 1 Time Sync Control LTYPE2 Register (P1_TS_CTL_LTYPE2)                              |      |

|     | 3.6.1.27 Port 1 Time Sync Control 2 Register (P1_TS_CTL2)                                         |      |

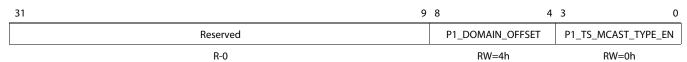

|     | 3.6.1.28 Port 1 Control Register (P1_CTL)                                                         |      |

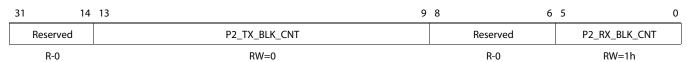

|     | 3.6.1.29 Port 2 Block Count Register (P2 BLK CNT)                                                 |      |

www.ti.com

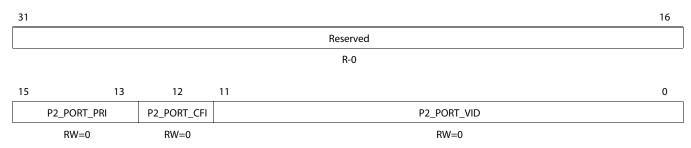

| 3.6.1.30 Port 2 VLAN Register (P2_PORT_VLAN)                                               |         |

|--------------------------------------------------------------------------------------------|---------|

| 3.6.1.31 Port 2 Transmit Header Priority to switch Priority Mapping Register (P2_TX_PRI_MA | ιP)3-51 |

| 3.6.1.32 MAC2 Source Address Low Register (MAC2_SA_LO)                                     |         |

| 3.6.1.33 MAC2 Source Address High Register (MAC2_SA_HI)                                    | 3-53    |

| 3.6.1.34 Port 2 Time Sync Control Register (P2_TS_CTL)                                     | 3-53    |

| 3.6.1.35 Port 2 Time Sync Sequence ID and LTYPE Register (P2_TS_SEQ_LTYPE)                 |         |

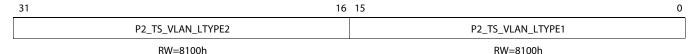

| 3.6.1.36 Port 2 Time Sync VLAN LTYPE Register (P2_TS_VLAN_LTYPE)                           |         |

| 3.6.1.37 Port 2 Time Sync Control LTYPE2 Register (P2_TS_CTL_LTYPE2)                       |         |

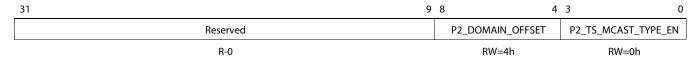

| 3.6.1.38 Port 2 Time Sync Control 2 Register (P2_TS_CTL2)                                  |         |

| 3.6.1.39 Port 2 Control Register (P2_CTL)                                                  |         |

| 3.6.2 Ethernet Media Access Controller (EMAC) submodule                                    |         |

| 3.6.2.1 MAC Identification and Version Register (MAC_IDVER)                                |         |

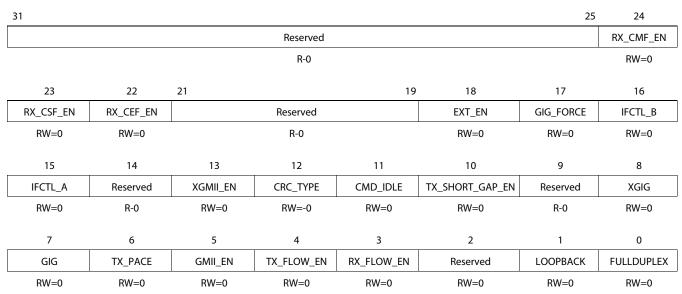

| 3.6.2.2 MAC Control Register (MAC_CONTROL)                                                 |         |

| 3.6.2.3 MAC Status Register (MACSTATUS)                                                    |         |

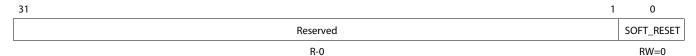

| 3.6.2.4 Software Reset Register (SOFT_RESET)                                               |         |

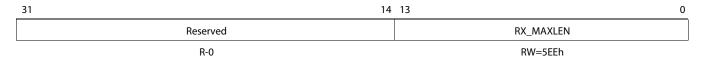

| 3.6.2.5 Receive Maximum Length Register (RX_MAXLEN)                                        |         |

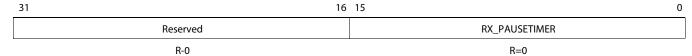

| 3.6.2.6 Receive Pause Timer Register (RX_PAUSE)                                            |         |

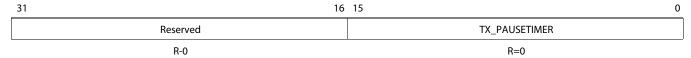

| 3.6.2.7 Transmit Pause Timer Register (TX_PAUSE)                                           |         |

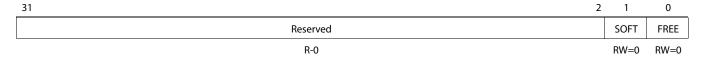

| 3.6.2.8 Emulation Control Register (EM_CONTROL)                                            |         |

| 3.6.2.9 TX Inter-Packet Gap Register (MAC_TX_GAP)                                          |         |

| 3.6.3 Statistics (STATS) Submodule                                                         |         |

| 3.6.3.1 Good Receive Frames Register (RXGOODFRAMES)                                        |         |

| 3.6.3.2 Broadcast Receive Frames Register (RXBROADCASTFRAMES)                              |         |

| 3.6.3.3 Multicast Receive Frames Register (RXMULTICASTFRAMES)                              |         |

| 3.6.3.4 Pause Receive Frames Register (RXPAUSEFRAMES)                                      | 3-66    |

| 3.6.3.5 Receive CRC Errors Register (RXCRCERRORS)                                          |         |

| 3.6.3.6 Receive Align/Code Errors Register (RXALIGNCODEERRORS)                             |         |

| 3.6.3.7 Oversize Receive Frames Register (RXOVERSIZEDFRAMES)                               |         |

|                                                                                            |         |

| 3.6.3.8 Receive Jabber Frames Register (RXJABBERFRAMES)                                    |         |

| 3.6.3.9 Undersize (Short) Receive Frames Register (RXUNDERSIZEDFRAMES)                     |         |

| 3.6.3.10 Receive Fragment Register (RXFRAGMENTS)                                           |         |

| 3.6.3.11 Overrun Type 4                                                                    |         |

| 3.6.3.12 Overrun Type 5                                                                    |         |

| 3.6.3.13 Receive Octets Register (RXOCTETS)                                                |         |

| 3.6.3.14 Good Transmit Frames Register (TXGOODFRAMES)                                      |         |

| 3.6.3.15 Broadcast Transmit Frames Register (TXBROADCASTFRAMES)                            |         |

| 3.6.3.16 Multicast Transmit Frames (TXMULTICASTFRAMES)                                     |         |

| 3.6.3.17 Pause Transmit Frames (TXPAUSEFRAMES)                                             |         |

| 3.6.3.18 Deferred Transmit Frames Register (TXDEFERREDFRAMES)                              |         |

| 3.6.3.19 Transmit Frames Collision Register (TXCOLLISIONFRAMES)                            |         |

| 3.6.3.20 Transmit Frames Single Collision Register (TXSINGLECOLLFRAMES)                    |         |

| 3.6.3.21 Transmit Frames Multiple Collision Register (TXMULTCOLLFRAMES)                    |         |

| 3.6.3.22 Excessive Collision Register (TXEXCESSIVECOLLISIONS)                              |         |

| 3.6.3.23 Late Collisions Register (TXLATECOLLISIONS)                                       |         |

| 3.6.3.24 Inter-Packet Gap Register (IPGERR)                                                |         |

| 3.6.3.25 Carrier Sense Errors Register (TXCARRIERSENSEERRORS)                              |         |

| 3.6.3.26 Transmit Octets Register (TXOCTETS)                                               |         |

| 3.6.3.27 Receive and Transmit 64 Octet Frames Register (64OCTETFRAMES)                     |         |

| 3.6.3.28 Receive and Transmit 65-127 Octet Frames Register (65T127OCTETFRAMES)             |         |

| 3.6.3.29 Receive and Transmit 128-255 Octet Frames Register (128T255OCTETFRAMES)           |         |

| 3.6.3.30 Receive and Transmit 256-511 Octet Frames Register (256T511OCTETFRAMES)           |         |

| 3.6.3.31 Receive and Transmit 512-1023 Octet Frames Register (512T1023OCTETFRAMES)         |         |

| 3.6.3.32 Receive and Transmit 1024 and Up Octet Frames Register (1024TUPOCTETFRAMES)       | )3-79   |

| 3.6.3.33 Net Octets Register (NETOCTETS)                                                   | 3-80    |

| 3.6.3.34 Receive Start of Frame Overruns Register (RXSOFOVERRUNS)                          | 3-80    |

| 3.6.3.35 Receive Middle of Frame Overruns Register (RXMOFOVERRUNS)                         |         |

| 3.6.3.36 Receive DMA Overruns Register (RXDMAOVERRUNS)                                     | 3-81    |

| 3.6.4 Time Synchronization (CPTS) submodule                                                |         |

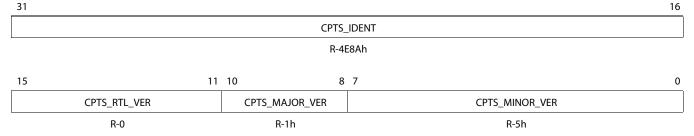

| 3.6.4.1 CPTS Identification and Version Register (CPTS IDVER)                              | 3-82    |

www.ti.com Contents

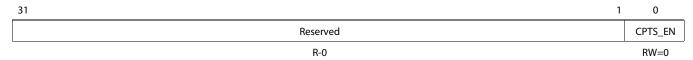

|     | 3.6.4.2 Time Sync Control Register (TS_CTL)                            |       |

|-----|------------------------------------------------------------------------|-------|

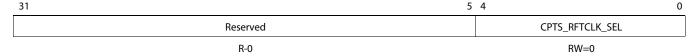

|     | 3.6.4.3 RFTCLK Select Register (CPTS_RFTCLK_SEL)                       |       |

|     | 3.6.4.4 Time Stamp Event Push Register (TS_PUSH)                       |       |

|     | 3.6.4.5 Time Stamp Load Value Register (TS_Load_Val)                   |       |

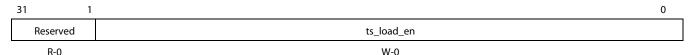

|     | 3.6.4.6 Time Stamp Load Enable Register (TS_Load_En)                   |       |

|     | 3.6.4.7 Time Stamp Comparison Value Register (TS_Comp_Val)             |       |

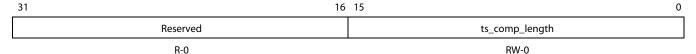

|     | 3.6.4.8 Time Stamp Comparison Length Register (TS_Comp_Length)         |       |

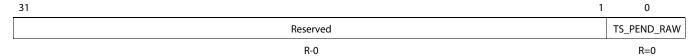

|     | 3.6.4.9 Interrupt Status Raw Register (INTSTAT_RAW)                    |       |

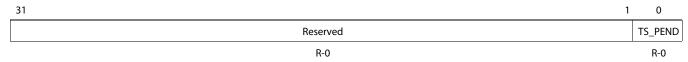

|     | 3.6.4.10 Interrupt Status Masked Register (INTSTAT_MASKED)             |       |

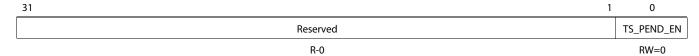

|     | 3.6.4.11 Interrupt Enable Register (INT_ENABLE)                        |       |

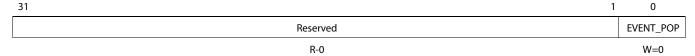

|     | 3.6.4.12 Event Pop Register (EVENT_POP).                               |       |

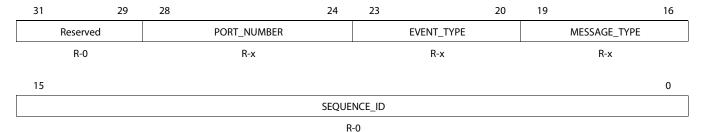

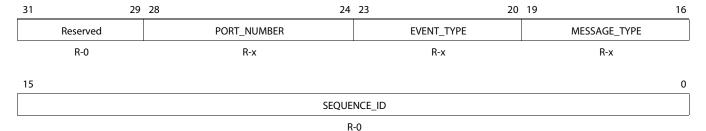

|     | 3.6.4.13 Event Low Register (EVENT_LOW)                                |       |

|     | 3.6.4.14 Event Mid Register (EVENT_MID)                                |       |

|     | 3.6.4.15 Event High Register (EVENT_HIGH)                              |       |

|     | 3.6.5 Address Lookup Engine (ALE) submodule                            |       |

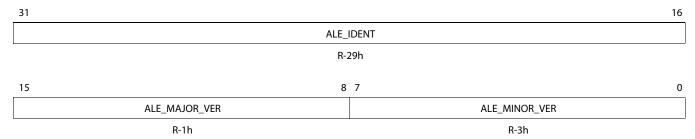

|     | 3.6.5.1 ALE Identification and Version Register (ALE_IDVER)            |       |

|     | 3.6.5.2 ALE Control Register (ALE_CONTROL)                             |       |

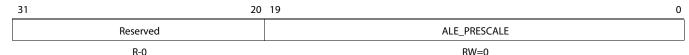

|     | 3.6.5.3 ALE Prescale Register (ALE_PRESCALE)                           |       |

|     | 3.6.5.4 ALE Unknown VLAN Register (UNKNOWN_VLAN)                       |       |

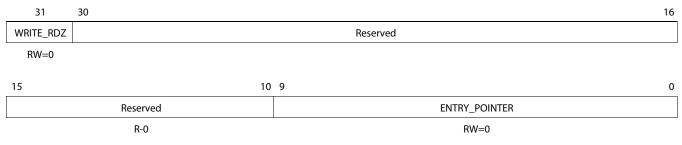

|     | 3.6.5.5 ALE Table Control Register (ALE_TBLCTL)                        |       |

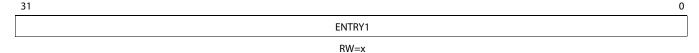

|     | 3.6.5.6 ALE Table Word 2 Register (ALE_TBLW2)                          |       |

|     | 3.6.5.7 ALE Table Word 1 Register (ALE_TBLW1)                          |       |

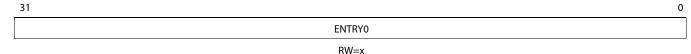

|     | 3.6.5.8 ALE Table Word 0 Register (ALE_TBLW0)                          |       |

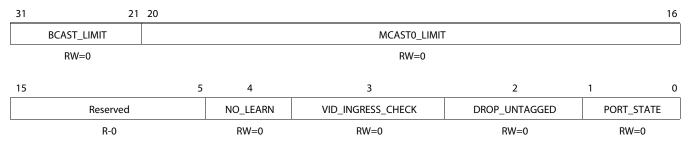

|     | 3.6.5.9 ALE Port Control Register 0 (ALE_PORTCTL0)                     |       |

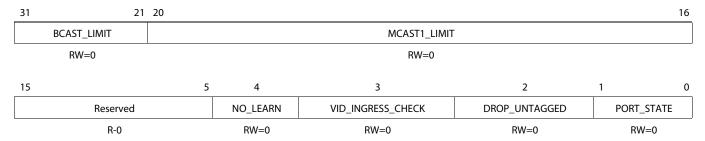

|     | 3.6.5.10 ALE Port Control Register 1 (ALE_PORTCTL1)                    |       |

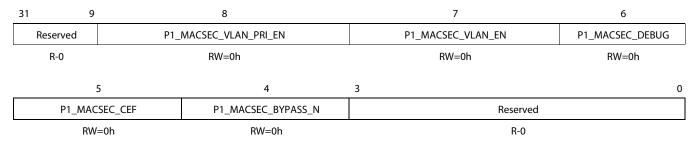

| . 7 | MACSEC Module                                                          |       |

| 0./ |                                                                        |       |

|     | 3.7.1 Transform Records Area                                           |       |

|     | 3.7.1.1 Transform Record N (offset 0x0000 + (n * 64))                  |       |

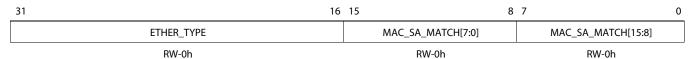

|     | 3.7.2.1 SAM_MAC_SA_MATCH_LO_N (offset 0x4000 + (n*64)).                |       |

|     | 3.7.2.2 SAM_MAC_SA_MATCH_LO_N (offset 0x4000 + (n*64))                 |       |

|     | 3.7.2.3 SAM_MAC_DA_MATCH_LO_N (offset 0x4004 + (n*64))                 |       |

|     | 3.7.2.4 SAM_MAC_DA_MATCH_LO_N (offset 0x4000 + (n*64))                 |       |

|     | 3.7.2.5 SAM_MISC_MATCH_N (offset 0x4010 + (n*64))                      |       |

|     | 3.7.2.6 SAM_SCI_MATCH_LO_N (offset 0x4010 + (n*64))                    |       |

|     | 3.7.2.7 SAM_SCI_MATCH_LO_N (offset 0x4014 + (if 04))                   |       |

|     | 3.7.2.8 SAM_MASK_N (offset 0x401C + (n*64))                            |       |

|     | 3.7.2.9 SAM_ENTRY_ENABLE1                                              |       |

|     | 3.7.2.10 SAM_ENTRY_ENABLE2                                             |       |

|     | 3.7.2.11 SAM_ENTRY_TOGGLE1                                             |       |

|     | 3.7.2.12 SAM_ENTRY_TOGGLE2                                             |       |

|     | 3.7.2.13 SAM_ENTRY_SET1                                                |       |

|     | 3.7.2.14 SAM_ENTRY_SET2                                                |       |

|     | 3.7.2.15 SAM_ENTRY_CLEAR1                                              |       |

|     | 3.7.2.16 SAM_ENTRY_CLEAR2                                              |       |

|     | 3.7.2.17 SAM_IN_FLIGHT.                                                |       |

|     | 3.7.3 Flow Control Words for frames that matched an SA parameter set   |       |

|     | 3.7.3.1 SAM_FLOW_CTRL_N (Ingress) Byte Address Offset 0x7000 + (n * 4) |       |

|     | 3.7.3.2 SAM_FLOW_CTRL_N (Egress) Byte Address Offset 0x7000 + (n * 4)  |       |

|     | 3.7.4 Security statistics counters of 40 bits each                     |       |

|     | 3.7.4.1 SA related statistics counters                                 |       |

|     | 3.7.4.2 8 sets of VLAN Related Statistics Counters                     |       |

|     | 3.7.4.3 Global Statistics Counters                                     |       |

|     | 3.7.5 Security Statistics Counter Control and Debug                    |       |

|     | 3.7.5.1 Count Control                                                  |       |

|     | 3.7.6 Consistency Check Parameters Sets Control Bits and Debug Status  |       |

|     | 3.7.6.1 IG_CC_CONTROL                                                  | 3-115 |

|     | 3.7.6.2 IG CC TAGS                                                     | 3-115 |

|     |                                                                         | www.ti.com |

|-----|-------------------------------------------------------------------------|------------|

|     | 3.7.7 9 MTU Check Control Words for VLAN packets and Non-VLAN Packets   | 3-116      |

|     | 3.7.7.1 NON_VLAN_MTU_CHECK                                              | 3-116      |

|     | 3.7.8 Security Fail Control Masks and Debug Registers for Packet Engine | 3-116      |

|     | 3.7.8.1 COUNT_SECFAIL1                                                  | 3-117      |

|     | 3.7.9 Access space for Packet Engine                                    | 3-117      |

|     | 3.7.9.1 CONTEXT_CONTROL                                                 | 3-118      |

|     | 3.7.9.2 BLOCK_CONTEXT_UPDATE                                            | 3-118      |

| 3.8 | 10 Gigabit Ethernet Subsystem Registers                                 | 3-120      |

|     | 3.8.1 Identification and Verification Register (IDVER)                  |            |

|     | 3.8.2 CPPI Timestamp Register (CPPI_TS)                                 | 3-121      |

|     | 3.8.3 CPPI Timestamp Enable Register (CPPI_TS_EN)                       | 3-121      |

|     | 3.8.4 CPPI Timestamp Divider Register (CPPL TS, DIV)                    | 3-121      |

# **List of Tables**

| Tabla 2 1                                                                                                                                                                                                                           | 10 Circulate Table arrant Curbourgetone Mendulos                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2.2                                                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| Table 2-1<br>Table 2-1                                                                                                                                                                                                              | 10 Gigabit Ethernet Subsystem Modules                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                      |

| Table 2-1                                                                                                                                                                                                                           | SRC_TAG for 10GbE Switch Egress Packets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                      |

| Table 2-2                                                                                                                                                                                                                           | PS_FLAGS for 10GbE Switch Ingress Packets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                      |

| Table 2-3                                                                                                                                                                                                                           | DST_TAG for 10GbE Switch Ingress Packets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                      |

| Table 2-4                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                      |

| Table 2-5                                                                                                                                                                                                                           | Time Synchronization Selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                      |

| Table 2-6                                                                                                                                                                                                                           | Time Synchronization Event Fields                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                      |

| Table 2-7                                                                                                                                                                                                                           | Free Table Entry Field Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                      |

| Table 2-6                                                                                                                                                                                                                           | Multicast Address Table Entry Field Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                      |

| Table 2-9                                                                                                                                                                                                                           | VLAN/Multicast Address Table Entry Field Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                      |

| Table 2-10                                                                                                                                                                                                                          | Unicast Address Table Entry Field Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                      |

| Table 2-11                                                                                                                                                                                                                          | OUI Unicast Address Table Entry Field Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                      |

| Table 2-12                                                                                                                                                                                                                          | VLAN/Unicast Table Entry Field Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                      |

| Table 2-13                                                                                                                                                                                                                          | VLAN Table Entry Field Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                      |

| Table 2-14                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                      |

|                                                                                                                                                                                                                                     | ALE Table Entry Field Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                      |

| Table 2-16                                                                                                                                                                                                                          | Gigabit Ethernet Switch Subsystem Descriptor Error Flags                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                      |

| Table 2-17                                                                                                                                                                                                                          | ALE Ingress Filtering Process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                      |

| Table 2-18                                                                                                                                                                                                                          | VLAN Aware Lookup Process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                      |

| Table 2-19                                                                                                                                                                                                                          | VLAN Unaware Lookup Process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                      |

| Table 2-20                                                                                                                                                                                                                          | ALE Lorging Process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                      |

| Table 2-21                                                                                                                                                                                                                          | ALE Learning Process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                      |

| Table 2-22                                                                                                                                                                                                                          | VLAN Aware Mode Non Tagged Transmit Packet Processing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                      |

| Table 2-23                                                                                                                                                                                                                          | VLAN Aware Mode Priority Tagged Transmit Packet Processing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                      |

| Table 2-24                                                                                                                                                                                                                          | VLAN Aware Mode VLAN Tagged Transmit Packet Processing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                      |

| Table 3-1                                                                                                                                                                                                                           | 10 Gigabit Ethernet Subsystem Modules                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                      |

| Table 3-2                                                                                                                                                                                                                           | 10 Gigabit Ethernet Subsystem Complete Register Listing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                      |

| Table 3-3                                                                                                                                                                                                                           | Ethernet switch subsystem module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                      |

| Table 3-4                                                                                                                                                                                                                           | Ethernet Switch Subsystem Identification and Version Register (ES_SS_IDVER) Field Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3-10                                                                 |

| Table 3-5                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                      |