# **KeyStone Architecture Universal Parallel Port (uPP)**

# **User Guide**

Literature Number: SPRUHG9 June 2012

www.ti.com

# **Release History**

| Release | Date     | Chapter/Topic | Description/Comments                           |

|---------|----------|---------------|------------------------------------------------|

| SPRUHG9 | May 2012 | All           | Initial Release for the KeyStone Architecture. |

www.ti.com Contents

# **Contents**

|           | Release History. List of Tables List of Figures List of Procedures                                  | Ø-V  |

|-----------|-----------------------------------------------------------------------------------------------------|------|

|           | Preface                                                                                             | Ø-i> |

|           | About This Manual  Notational Conventions  Related Documentation from Texas Instruments  Trademarks | ø-i› |

| Chapter 1 |                                                                                                     |      |

|           | Introduction                                                                                        | 1-1  |

|           | 1.1 Purpose of the Peripheral                                                                       | 1-2  |

|           | 1.2 Features                                                                                        | 1-2  |

| Chapter 2 |                                                                                                     |      |

|           | Architecture                                                                                        | 2-1  |

|           | 2.1 Clock Generation and Control                                                                    | 2-2  |

|           | 2.1.1 Transmit Mode (Single Data Rate)                                                              |      |

|           | 2.1.2 Receive Mode (Single Data Rate)                                                               |      |

|           | 2.1.3 Double Data Rate                                                                              | 2-3  |

|           | 2.2 Signal Description                                                                              | 2-4  |

|           | 2.3 Pin Multiplexing                                                                                | 2-5  |

|           | 2.4 Internal DMA Controller Description                                                             |      |

|           | 2.4.1 DMA Programming Concepts                                                                      |      |

|           | 2.4.2 Data Interleave Mode                                                                          |      |

|           | 2.4.3 Interface and DMA Channel Mapping                                                             |      |

|           | 2.5 Protocol Description                                                                            |      |

|           | 2.5.1 DATA[7:0] Signals                                                                             |      |

|           | 2.5.2 DATA[15:8] Signals                                                                            |      |

|           | 2.5.3 START Signal                                                                                  |      |

|           | 2.5.5 WAIT Signal                                                                                   |      |

|           | 2.5.6 CLOCK Signal                                                                                  |      |

|           | 2.5.7 Signal Timing Diagrams                                                                        |      |

|           | 2.5.8 Data Format                                                                                   |      |

|           | 2.6 Initialization and Operation                                                                    | 2-14 |

|           | 2.6.1 Step-by-Step Procedure                                                                        | 2-14 |

|           | 2.6.2 Sample Configuration Settings                                                                 | 2-1  |

|           | 2.6.3 System Tuning Tips                                                                            |      |

|           | 2.6.4 Sample Interrupt Service Routine                                                              |      |

|           | 2.7 Reset Considerations                                                                            |      |

|           | 2.7.1 Software Reset                                                                                |      |

|           | 2.7.2 Hardware Reset                                                                                |      |

|           | 2.8 Interrupt Support                                                                               |      |

|           | 2.8.1 End of Line (EOL) Event.                                                                      |      |

|           | 2.8.2 End of Window (EOW) Event                                                                     |      |

|           | 2.8.4 Underrun or Overflow (UOR) Event                                                              |      |

|           | Zio. Cindentali of Overlion (COII) Event                                                            |      |

www.ti.com

|           | 2.8.5 DMA Programming Error (DPE) Event 2.9 Power Management 2.10 Emulation Considerations. 2.11 Transmit and Receive FIFOs | 2-20<br>2-21 |

|-----------|-----------------------------------------------------------------------------------------------------------------------------|--------------|

| Chapter 3 |                                                                                                                             |              |

|           | Registers                                                                                                                   | 3-1          |

|           | 3.1 Introduction                                                                                                            | 3-2          |

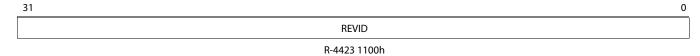

|           | 3.2 uPP Peripheral Identification Register (UPPID)                                                                          | 3-3          |

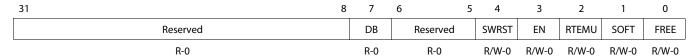

|           | 3.3 uPP Peripheral Control Register (UPPCR)                                                                                 | 3-4          |

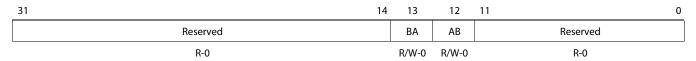

|           | 3.4 uPP Digital Loopback Register (UPDLB)                                                                                   | 3-5          |

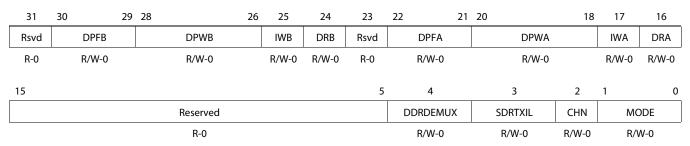

|           | 3.5 uPP Channel Control Register (UPCTL)                                                                                    | 3-6          |

|           | 3.6 uPP Interface Configuration Register (UPICR)                                                                            |              |

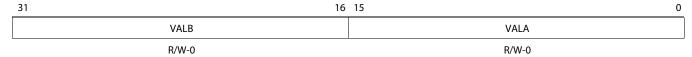

|           | 3.7 uPP Interface Idle Value Register (UPIVR)                                                                               |              |

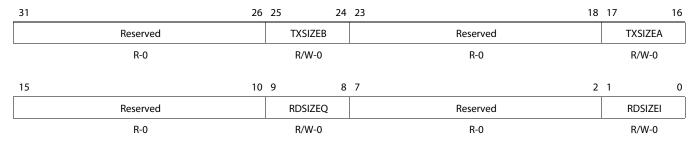

|           | 3.8 uPP Threshold Configuration Register (UPTCR)                                                                            |              |

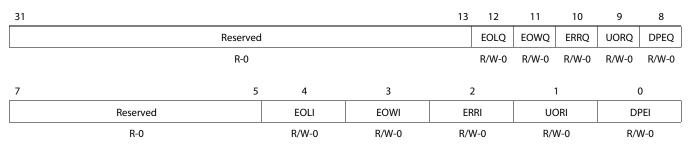

|           | 3.9 uPP Interrupt Raw Status Register (UPISR)                                                                               |              |

|           | 3.10 uPP Interrupt Enabled Status Register (UPIER)                                                                          |              |

|           | 3.11 uPP Interrupt Enable Set Register (UPIES)                                                                              |              |

|           | 3.12 uPP Interrupt Enable Clear Register (UPIEC)                                                                            |              |

|           | 3.13 uPP End of Interrupt Register (UPEOI)                                                                                  |              |

|           | 3.14 uPP DMA Channel I Descriptor 0 Register (UPID0)                                                                        |              |

|           | 3.15 uPP DMA Channel I Descriptor 1 Register (UPID1)                                                                        |              |

|           | 3.16 uPP DMA Channel I Descriptor 2 Register (UPID2)                                                                        |              |

|           | 3.17 uPP DMA Channel I Status 0 Register (UPIS0)                                                                            |              |

|           | 3.18 uPP DMA Channel I Status 1 Register (UPIS1)                                                                            |              |

|           | 3.19 uPP DMA Channel I Status 2 Register (UPIS2)                                                                            |              |

|           | 3.20 uPP DMA Channel Q Descriptor 0 Register (UPQD0)                                                                        |              |

|           | 3.21 uPP DMA Channel Q Descriptor 1 Register (UPQD1)                                                                        |              |

|           | 3.22 uPP DMA Channel Q Descriptor 2 Register (UPQD2)                                                                        |              |

|           | 3.23 uPP DMA Channel Q Status 0 Register (UPQS0)                                                                            |              |

|           | 3.24 uPP DMA Channel Q Status 1 Register (UPQS1)                                                                            |              |

|           | 3.25 uPP DMA Channel Q Status 2 Register (UPQS2)                                                                            | 3-33         |

www.ti.com List of Tables

# **List of Tables**

| Table 2-1  | I/O Clock Speeds for Channel in Transmit Mode Given 150 MHz Transmit Clock     | 2-3  |

|------------|--------------------------------------------------------------------------------|------|

| Table 2-2  | uPP Signal Descriptions                                                        | 2-4  |

| Table 2-3  | DATA and XDATA Pin Assignments to Channels A and B According to Operating Mode | 2-4  |

| Table 2-4  | Interface and DMA Channel Mapping for Various Operating Modes                  | 2-8  |

| Table 2-5  | Required Signals for Various Modes                                             | 2-9  |

| Table 2-6  | Data Packing Examples for 12-Bit Data Words                                    | 2-13 |

| Table 2-7  | Basic Operating Mode Selection                                                 | 2-15 |

| Table 2-8  | Sample uPP Parameters for Duplex Mode 0                                        |      |

| Table 2-9  | uPP Parameters Useful for System Tuning                                        | 2-16 |

| Table 3-1  | uPP Registers                                                                  | 3-2  |

| Table 3-2  | uPP Peripheral Identification Register (UPPID) Field Descriptions              | 3-3  |

| Table 3-3  | uPP Peripheral Control Register (UPPCR) Field Descriptions                     | 3-4  |

| Table 3-4  | uPP Digital Loopback Register (UPDLB) Field Descriptions                       | 3-5  |

| Table 3-5  | uPP Channel Control Register (UPCTL) Field Descriptions                        | 3-6  |

| Table 3-6  | uPP Interface Configuration Register (UPICR) Field Descriptions                | 3-8  |

| Table 3-7  | uPP Interface Idle Value Register (UPIVR) Field Descriptions                   | 3-11 |

| Table 3-8  | uPP Threshold Configuration Register (UPTCR) Field Descriptions                | 3-12 |

| Table 3-9  | uPP Interrupt Raw Status Register (UPISR) Field Descriptions                   | 3-13 |

| Table 3-10 | uPP Interrupt Enabled Status Register (UPIER) Field Descriptions               | 3-15 |

| Table 3-11 | uPP Interrupt Enable Set Register (UPIES) Field Descriptions                   | 3-17 |

| Table 3-12 | uPP Interrupt Enable Clear Register (UPIEC) Field Descriptions                 | 3-19 |

| Table 3-13 | uPP End of Interrupt Register (UPEOI) Field Descriptions                       | 3-21 |

| Table 3-14 | uPP DMA Channel I Descriptor 0 Register (UPID0) Field Descriptions             | 3-22 |

| Table 3-15 | uPP DMA Channel I Descriptor 1 Register (UPID1) Field Descriptions             | 3-23 |

| Table 3-16 | uPP DMA Channel I Descriptor 2 Register (UPID2) Field Descriptions             | 3-24 |

| Table 3-17 | uPP DMA Channel I Status 0 Register (UPIS0) Field Descriptions                 | 3-25 |

| Table 3-18 | uPP DMA Channel I Status 1 Register (UPIS1) Field Descriptions                 | 3-26 |

| Table 3-19 | uPP DMA Channel I Status 2 Register (UPIS2) Field Descriptions                 | 3-27 |

| Table 3-20 | uPP DMA Channel Q Descriptor 0 Register (UPQD0) Field Descriptions             | 3-28 |

| Table 3-21 | uPP DMA Channel Q Descriptor 1 Register (UPQD1) Field Descriptions             | 3-29 |

| Table 3-22 | uPP DMA Channel Q Descriptor 2 Register (UPID2) Field Descriptions             | 3-30 |

| Table 3-23 | uPP DMA Channel Q Status 0 Register (UPQS0) Field Descriptions                 | 3-31 |

| Table 3-24 | uPP DMA Channel Q Status 1 Register (UPQS1) Field Descriptions                 | 3-32 |

| Table 3-25 | uPP DMA Channel Q Status 2 Register (UPQS2) Field Descriptions                 | 3-33 |

List of Figures www.ti.com

# **List of Figures**

| Figure 1-1  | uPP Functional Block Diagram                                                                                          | 1-3  |

|-------------|-----------------------------------------------------------------------------------------------------------------------|------|

| Figure 1-2  | Data Flow for Single-Channel Receive Mode                                                                             | 1-3  |

| Figure 1-3  | Data Flow for Single-Channel Transmit Mode.                                                                           | 1-4  |

| Figure 1-4  | Data Flow for Digital Loopback (DLB) Mode (Duplex Mode 0)                                                             | 1-4  |

| Figure 1-5  | Data Flow for Single-Channel Transmit with Data Interleave                                                            | 1-4  |

| Figure 2-1  | Clock Generation for a Channel Configured in Transmit Mode                                                            | 2-2  |

| Figure 2-2  | Clock Generation for a Channel Configured in Receive Mode                                                             | 2-2  |

| Figure 2-3  | Structure of DMA Window and Lines in Memory                                                                           | 2-6  |

| Figure 2-4  | Signal Timing for uPP Channel in Receive Mode with Single Data Rate                                                   | 2-11 |

| Figure 2-5  | Signal Timing for uPP Channel in Transmit Mode with Single Data Rate                                                  | 2-11 |

| Figure 2-6  | Signal Timing for uPP Channel in Receive Mode with Double Data Rate                                                   | 2-11 |

| Figure 2-7  | Signal Timing for uPP Channel in Transmit Mode with Double Data Rate                                                  | 2-12 |

| Figure 2-8  | Signal Timing for uPP Channel in Receive Mode with Double Data Rate and Data Interleave Enabled (via UPCTL.DDRDEMUX). | 2-12 |

| Figure 2-9  | Signal Timing for uPP Channel in Transmit Mode with Double Data Rate and Data Interleave Enabled (via                 |      |

| ga. c = >   | UPCTL.DDRDEMUX)                                                                                                       | 2-12 |

| Figure 2-10 | Signal Timing for uPP Channel in Transmit Mode with Single Data Rate and Data Interleave Enabled (via UPCTL.S 2-13    |      |

| Figure 3-1  | uPP Peripheral Identification Register (UPPID) REVID.                                                                 | 3-3  |

| Figure 3-2  | uPP Peripheral Control Register (UPPCR)                                                                               |      |

| Figure 3-3  | uPP Digital Loopback Register (UPDLB)                                                                                 |      |

| Figure 3-4  | uPP Channel Control Register (UPCTL)                                                                                  |      |

| Figure 3-5  | uPP Interface Configuration Register (UPICR)                                                                          |      |

| Figure 3-6  | uPP Interface Idle Value Register (UPIVR)                                                                             |      |

| Figure 3-7  | uPP Threshold Configuration Register (UPTCR)                                                                          |      |

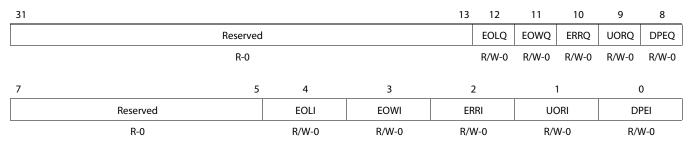

| Figure 3-8  | uPP Interrupt Raw Status Register (UPISR)                                                                             |      |

| Figure 3-9  | uPP Interrupt Enabled Status Register (UPIER)                                                                         |      |

| Figure 3-10 | uPP Interrupt Enable Set Register (UPIES).                                                                            |      |

| Figure 3-11 | uPP Interrupt Enable Clear Register (UPIEC)                                                                           |      |

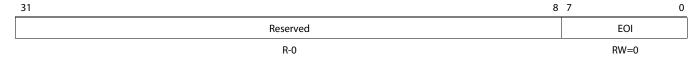

| Figure 3-12 | uPP End of Interrupt Register (UPEOI)                                                                                 |      |

| Figure 3-13 | uPP DMA Channel I Descriptor 0 Register (UPID0).                                                                      |      |

| Figure 3-14 | uPP DMA Channel I Descriptor 1 Register (UPID1).                                                                      |      |

| Figure 3-15 | uPP DMA Channel I Descriptor 2 Register (UPID2).                                                                      |      |

| Figure 3-16 | uPP DMA Channel I Status 0 Register (UPIS0)                                                                           |      |

| Figure 3-17 | uPP DMA Channel I Status 1 Register (UPIS1)                                                                           |      |

| Figure 3-18 | uPP DMA Channel I Status 2 Register (UPIS2)                                                                           |      |

| Figure 3-19 | uPP DMA Channel Q Descriptor 0 Register (UPQD0)                                                                       |      |

| Figure 3-20 | uPP DMA Channel Q Descriptor 1 Register (UPQD1)                                                                       |      |

| Figure 3-21 | uPP DMA Channel Q Descriptor 2 Register (UPID2)                                                                       |      |

| Figure 3-22 | uPP DMA Channel Q Status 0 Register (UPQS0)                                                                           |      |

| Figure 3-22 | uPP DMA Channel Q Status 1 Register (UPQS1)                                                                           |      |

| Figure 3-23 | uPP DMA Channel Q Status 2 Register (UPQS2)                                                                           |      |

| inguic J-2+ | an i Divir Chamile Q Status & negister (or QSA)                                                                       |      |

www.ti.com List of Procedures

## **List of Procedures**

| Procedure 2-1 | 2-14 |

|---------------|------|

| Procedure 2-2 | 2-18 |

List of Procedures www.ti.com

# **Preface**

#### **About This Manual**

This user guide describes the universal parallel port (uPP) peripheral.

**IMPORTANT NOTE**—The information in this document should be used in conjunction with information in the device-specific Keystone Architecture data manual that applies to the part number of your device.

#### **Notational Conventions**

This document uses the following conventions:

- Commands and keywords are in **boldface** font.

- Arguments for which you supply values are in *italic* font.

- Terminal sessions and information the system displays are in screen font.

- Information you must enter is in **boldface screen font**.

- Elements in square brackets ([]) are optional.

Notes use the following conventions:

**Note**—Means reader take note. Notes contain helpful suggestions or references to material not covered in the publication.

The information in a caution or a warning is provided for your protection. Please read each caution and warning carefully.

**CAUTION**—Indicates the possibility of service interruption if precautions are not taken.

**WARNING**—Indicates the possibility of damage to equipment if precautions are not taken.

Preface www.ti.com

#### **Related Documentation from Texas Instruments**

The following documents describe the TMS320C66x Digital Signal Processors (DSPs). Copies of these documents are available on the Internet at <a href="https://www.ti.com">www.ti.com</a>.

*Tip*: Enter the literature number in the search box provided at www.ti.com.

C66x CorePac User Guide

SPRUGW0

C66x CPU and Instruction Set Reference Guide

SPRUGH7

#### **Trademarks**

TMS320C66x and C6000 are trademarks of Texas Instruments Incorporated.

All other brand names and trademarks mentioned in this document are the property of Texas Instruments Incorporated or their respective owners, as applicable.

# **Chapter 1**

# Introduction

**IMPORTANT NOTE**—The information in this document should be used in conjunction with information in the device-specific Keystone Architecture data manual that applies to the part number of your device.

This chapter includes the following information:

- 1.1 "Purpose of the Peripheral" on page 1-2

- 1.2 "Features" on page 1-2

- 1.3 "Functional Block Diagram" on page 1-3

# 1.1 Purpose of the Peripheral

The universal parallel port (uPP) peripheral is a multichannel, high-speed parallel interface with dedicated data lines and minimal control signals. It is designed to interface cleanly with high-speed analog-to-digital converters (ADCs) or digital-to-analog converters (DACs) with up to 16-bit data width (per channel). It may also be interconnected with field-programmable gate arrays (FPGAs) or other uPP devices to achieve high-speed digital data transfer. It can operate in receive mode, transmit mode, or duplex mode, in which its individual channels operate in opposite directions.

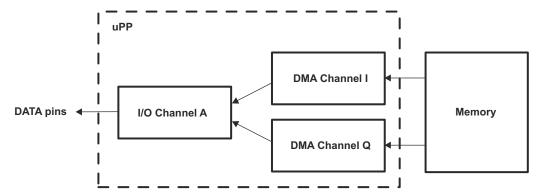

The uPP peripheral includes an internal DMA controller to maximize throughput and minimize CPU overhead during high-speed data transmission. All uPP transactions use the internal DMA to feed data to or retrieve data from the I/O channels. The DMA controller includes two DMA channels, which typically service separate I/O channels. The uPP peripheral also supports data interleave mode, in which all DMA resources service a single I/O channel. In this mode, only one I/O channel may be used.

#### 1.2 Features

The uPP peripheral offers a high-speed parallel data bus with several important features:

- Two independent channels with separate data buses

- Channels can operate in same or opposing directions simultaneously

- I/O speeds up to 75 MHz with 8-16 bit data width per channel

- Internal DMA leaves CPU EDMA free

- Simple protocol with few control pins (configurable: 2-4 per channel)

- Single and double data rates (use one or both edges of clock signal)

- Double data rate imposes a maximum clock speed of 37.5 MHz

- Multiple data packing formats for 9-15 bit data widths

- Data interleave mode (single channel only)

For additional information on the features and performance supported by the uPP peripheral, see your device-specific data manual.

# 1.3 Functional Block Diagram

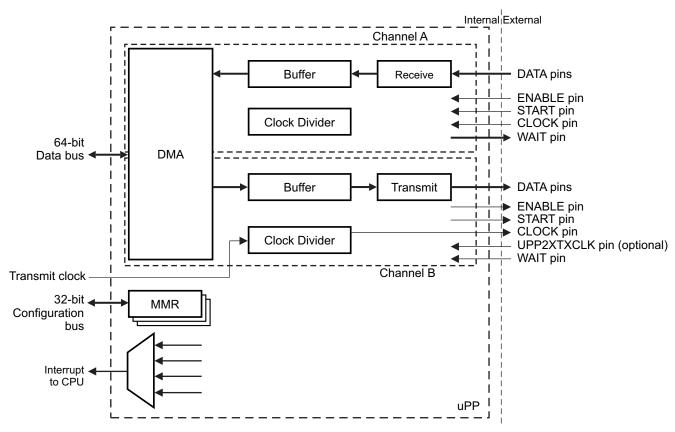

Figure 1-1 provides a high-level view of the uPP peripheral internal logic. Note that this figure shows one particular configuration: Channel A receives and Channel B transmits. However, each channel may operate in either direction.

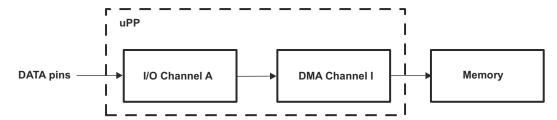

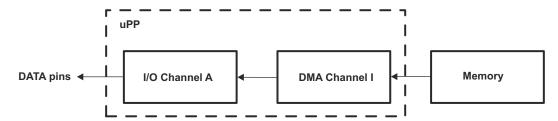

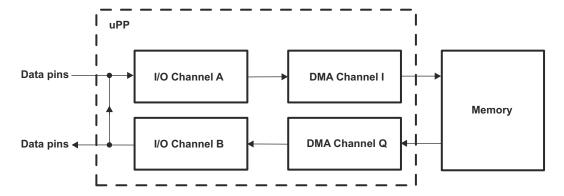

Figure 1-2, Figure 1-3, Figure 1-4, and Figure 1-5 show simplified data paths through the uPP peripheral for various configurations. Note that these figures are examples and do not represent all possible configurations. More information on these and other modes of operation is given in subsequent sections.

Figure 1-1 uPP Functional Block Diagram

Figure 1-2 Data Flow for Single-Channel Receive Mode

Figure 1-3 Data Flow for Single-Channel Transmit Mode

Figure 1-4 Data Flow for Digital Loopback (DLB) Mode (Duplex Mode 0)

Figure 1-5 Data Flow for Single-Channel Transmit with Data Interleave

# **Chapter 2**

# **Architecture**

- 2.1 "Clock Generation and Control" on page 2-2

- 2.2 "Signal Description" on page 2-4

- 2.3 "Pin Multiplexing" on page 2-5

- 2.4 "Internal DMA Controller Description" on page 2-6

- 2.5 "Protocol Description" on page 2-9

- 2.6 "Initialization and Operation" on page 2-14

- 2.7 "Reset Considerations" on page 2-18

- 2.8 "Interrupt Support" on page 2-19

- 2.9 "Power Management" on page 2-20

- 2.10 "Emulation Considerations" on page 2-21

- 2.11 "Transmit and Receive FIFOs" on page 2-21

## 2.1 Clock Generation and Control

The uPP peripheral uses two separate clocks: a module clock that controls its internal logic, and a transmit clock that runs either interface channel in transmit mode. The source for each of these clocks may be configurable. Neither the module clock nor the transmit clock can be faster than one-half the device CPU clock speed. See the device-specific *data manual* for more information.

Each channel's Clock pin, or I/O clock, is obtained independently based on its operating direction.

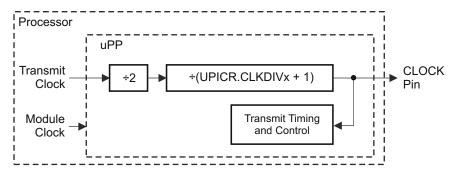

## 2.1.1 Transmit Mode (Single Data Rate)

The channel drives a clock signal on its Clock pin. The uPP transmit clock is divided by a fixed value of 2, then divided again by a user-specified value between 1 and 16 (UPICR.CLKDIVn + 1). The resulting signal then drives the Clock pin. The following formula determines the final I/O clock speed:

I/O Clock = Transmit Clock/ $(2 \times (UPICR.CLKDIVn + 1))$

The fixed divisor restricts the maximum speed of the I/O clock to one-fourth the device CPU clock speed.

Figure 2-1 shows the clock generation system for a channel configured in transmit mode.

Figure 2-1 Clock Generation for a Channel Configured in Transmit Mode

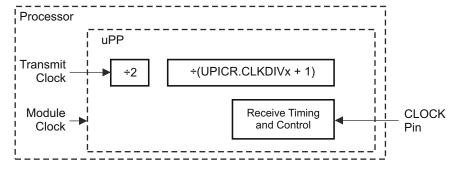

#### 2.1.2 Receive Mode (Single Data Rate)

The channel requires an external clock to drive its Clock pin. The incoming clock is not divided, and its maximum allowed speed is one fourth  $(\frac{1}{4})$  the device CPU clock speed.

Figure 2-2 shows the clock generation system for a channel configured in receive mode.

Figure 2-2 Clock Generation for a Channel Configured in Receive Mode

#### 2.1.3 Double Data Rate

The uPP peripheral supports two I/O clocking schemes:

- SDR Single Data Rate

- DDR Double Data Rate

SDR clocks data from the DATA pins on either the rising edge or the falling edge (depending on UPICR.CLKINV*n*) of the I/O clock.

With DDR, data is clocked on both the rising and falling edges of the I/O clock. However, DDR mode imposes a lower I/O clock speed limit of one eighth ( $^{1}/_{8}$ ) the device CPU clock for both transmit and receive modes. The operating speeds for transmit mode with various divisors in each data rate are summarized in Table 2-1.

**Note**—In this table, a data word is defined as the data represented on the DATA pins; uPP supports data words in the 8-bit to 16-bit range.

In receive mode, a channel I/O clock is generated by an external source, but the same speed limit applies.

Table 2-1 I/O Clock Speeds for Channel in Transmit Mode Given 150 MHz Transmit Clock

|               |                 | Word Rate (Mw/s) |                  |  |

|---------------|-----------------|------------------|------------------|--|

| UPICR.CLKDIVn | I/O Clock (MHz) | Single Data Rate | Double Data Rate |  |

| 0             | 75.00           | 75.00            |                  |  |

| 1             | 37.50           | 37.50            | 75.00            |  |

| 2             | 25.00           | 25.00            | 50.00            |  |

| 3             | 18.75           | 18.75            | 37.50            |  |

|               |                 |                  |                  |  |

| 15            | 4.69            | 4.69             | 9.38             |  |

Additional restrictions may apply, check the device data manual to see if the particular uPP peripheral has any additional clock requirements.

# 2.2 Signal Description

Each uPP channel has its own set of control and data signals. Table 2-2 lists every signal and briefly describes their functions. The signal names are slightly different from device to device. Refer to the device specific data manual for exact signal names. Section 2.5 explains the uPP protocol.

Table 2-2 uPP Signal Descriptions

|                  |             | Туре       | Туре      |                                                          |

|------------------|-------------|------------|-----------|----------------------------------------------------------|

| Signal           | I/O Channel | (Transmit) | (Receive) | Description                                              |

| DATA[15:0]       | _           | Output     | Input     | Parallel data bus                                        |

| XDATA[15:0]      | _           | Output     | Input     | Extended parallel data bus                               |

| CHA_START        | А           | Output     | Input     | Indicates first data word per line of data               |

| CHA_ENABLE       | А           | Output     | Input     | Indicates data transmission active                       |

| CHA_WAIT         | А           | Input      | Output    | Requests transmitter halt temporarily                    |

| CHA_CLOCK        | Α           | Output     | Input     | Source-synchronous clock signal                          |

| CHB_START        | В           | Output     | Input     | Indicates first data word per line of data               |

| CHB_ENABLE       | В           | Output     | Input     | Indicates data transmission active                       |

| CHB_WAIT         | В           | Input      | Output    | Requests transmitter halt temporarily                    |

| CHB_CLOCK        | В           | Output     | Input     | Source-synchronous clock signal                          |

| UPP_2xTXCLK      | _           | Input      | _         | Optional external source for transmit clock <sup>1</sup> |

| End of Table 2-2 |             |            |           |                                                          |

<sup>1.</sup> This clock can only be used in transmit mode, and must be twice the speed of the desired I/O clock. See Section 2.1 and the device-specific data manual for more information.

Note that the DATA and XDATA pins are not dedicated to a single I/O channel in the same way as the control signals. For practical reasons, uPP data pin channel assignments are not static. Instead, the data pins used by each I/O channel (A, B) depend on the operating mode of the uPP peripheral.

Table 2-3 summarizes the assignment of the DATA and XDATA pins to each channel for various operating modes, along with the relevant register settings. For more information on these pins, see the device-specific data manual.

Table 2-3 DATA and XDATA Pin Assignments to Channels A and B According to Operating Mode

| uPP Channel Control Register (UPCTL) Bit |     |     | Assigned Channel |           |             |            |

|------------------------------------------|-----|-----|------------------|-----------|-------------|------------|

| CHN                                      | IWA | IWB | DATA[15:8]       | DATA[7:0] | XDATA[15:8] | XDATA[7:0] |

| 0                                        | 0   | х   | _                | A[7:0]    | _           | _          |

| 0                                        | 1   | х   | A[15:8]          | A[7:0]    | _           | _          |

| 1                                        | 0   | 0   | B[7:0]           | A[7:0]    | _           | _          |

| 1                                        | 0   | 1   | B[7:0]           | A[7:0]    | B[15:8]     | _          |

| 1                                        | 1   | 0   | B[7:0]           | A[7:0]    | _           | A[15:8]    |

| 1                                        | 1   | 1   | B[7:0]           | A[7:0]    | B[15:8]     | A[15:8]    |

| End of Table 2-3                         |     |     |                  |           |             |            |

# 2.3 Pin Multiplexing

Extensive pin multiplexing is used to accommodate the largest number of peripheral functions in the smallest possible package. Pin multiplexing is controlled using a combination of hardware configuration at device reset and software programmable register settings. To determine how pin multiplexing affects the uPP peripheral, see the device-specific data manual.

# 2.4 Internal DMA Controller Description

The uPP peripheral includes an internal DMA controller separate from any device-level DMA, such as EDMA. The internal DMA controller consists of two DMA channels, I and Q, which move data to/from the uPP peripheral interface (I/O) channels in all operating modes. This section describes how to program the internal DMA channels.

# 2.4.1 DMA Programming Concepts

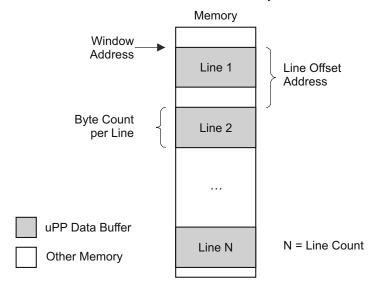

The uPP internal DMA controller uses a simplified programming model similar to 2D transfers performed by the EDMA. (See the *KeyStone Architecture Communications Infrastructure Digital Processor Enhanced Direct Memory Access (EDMA3) Controller User's Guide* (SPRUGS5) for more information). Each DMA channel may be configured with four parameters: window address, byte count, line count, and line offset address. Figure 2-3 shows a typical DMA window defined by these parameters.

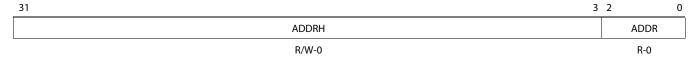

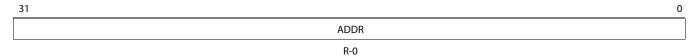

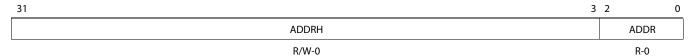

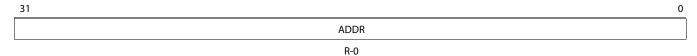

- Window Address (UPxD0.ADDR) The location in memory of the first byte in the data buffer. When the uPP operates in receive mode, the DMA channel begins writing to this address as it takes incoming data from the uPP I/O channel. When the uPP operates in transmit mode, the DMA channel begins reading from this address and passes the data to the uPP I/O channel. The window address can reside in any available memory space (including EMIF), but it must be aligned to a 64-bit boundary (that is, the 3 LSBs must equal 0). Nonaligned addresses are automatically adjusted to a properly aligned value when written to UPxD0.

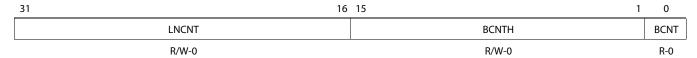

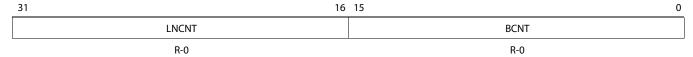

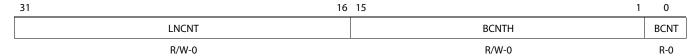

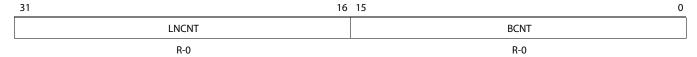

- **Byte Count** (UPxD1.BCNT) The number of bytes per line. The byte count must be an even number.

- **Line Count** (UPxD1.LNCNT) The number of lines per window. The total number of bytes transferred equals B × L, where B is the byte count per line and L is the line count.

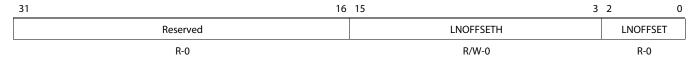

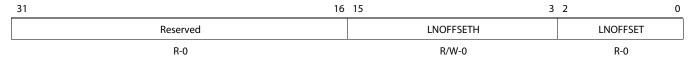

- Line Offset Address (UPxD2.LNOFFSET) The offset address between the first byte in successive lines. The line offset address cannot exceed 65528 (FFF8h) bytes, and must be aligned to a 64-bit boundary in memory (that is, the 3 LSBs must equal 0).

Figure 2-3 Structure of DMA Window and Lines in Memory

Certain values of the line offset address have special implications on the structure of the data buffer:

- Line Offset Address = Byte Count Data buffer is a contiguous block in memory with size equal to (Line Count)  $\times$  (Byte Count).

- Line Offset Address = 0 Data buffer consists of a single line, with total size equal to Byte Count. If the I/O channel is configured in transmit mode, this line is transmitted (Line Count) consecutive times before the DMA transfer completes. If the I/O channel is configured in receive mode, the buffer is repeatedly written and overwritten by incoming data.

To program a DMA transfer, write the appropriate fields in the DMA channel descriptor registers, UPID*n* for DMA Channel I or UPQD*n* for DMA Channel Q. If the associated I/O channel is initialized and idle, the DMA transfer and I/O transaction begins immediately. Section 2.6 describes a step-by-step process for configuring the I/O and DMA channels and starting a uPP transfer.

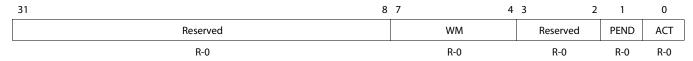

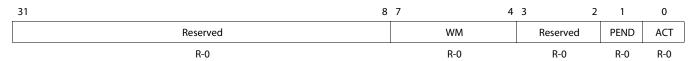

Each DMA channel allows a second descriptor to be queued while the previously programmed DMA transfer is still running. The UPxS2.PEND bit reports whether a new set of DMA parameters may be written to the DMA descriptor registers. Each DMA channel can have at most one active transfer and one queued transfer. This allows each I/O channel to perform uninterrupted, consecutive transactions across DMA transfer boundaries.

The internal DMA controller does not support automatically reloading DMA transfer descriptors. Each successive descriptor set must be explicitly written to the UPxDn registers by software.

All uPP interrupt events originate in the internal DMA controller. Section 2.8 lists and explains all uPP interrupt events.

The internal DMA controller always writes data in bursts of 64 bytes. However, DMA read operations have configurable burst size, which may be set per channel using the RDSIZEI and RDSIZEQ bits in the uPP threshold configuration register (UPTCR). A DMA channel waits until the specified number of bytes leaves its internal buffer before performing another burst read from memory.

Note that the TXSIZEA and TXSIZEB bits in UPTCR are not DMA parameters; instead, they control transmit thresholds for the uPP interface channels.

#### 2.4.2 Data Interleave Mode

The data interleave mode is a special configuration that maps both DMA channels to a single interface channel. Since there are only two DMA channels in the uPP peripheral, data interleave mode can only be used when the uPP peripheral is operated in single-channel mode. There are two variants on data interleave mode, each with special conditions:

- Single Data Rate (SDR) Interleave Transmit Only

- UPCTL.CHN = 0 (single-channel mode)

- UPCTL.DRA = 0 (single data rate)

- UPCTL.MODE = 1 (transmit mode)

- UPCTL.SDRTXIL = 1 (enable SDR transmit interleave)

- UPCTL.DDRDEMUX = 0 (disable DDR interleave)

- Double Data Rate (DDR) Interleave Transmit or Receive

- UPCTL.CHN = 0 (single-channel mode)

- UPCTL.DRA = 1 (double data rate)

- UPCTL.MODE = 0 or 1 (receive or transmit mode; not duplex)

- UPCTL.SDRTXIL = 0 (disable SDR transmit interleave)

- UPCTL.DDRDEMUX = 1 (enable DDR interleave)

Section 2.1 describes the differences between single data rate (SDR) and double data rate (DDR).

In data interleave mode, only I/O Channel A is used. This single channel is associated with two data buffers, each serviced by its own DMA channel (I and Q). In SDR interleave mode, the START signal is used as a buffer selection line: START = 1 indicates that the current word comes from DMA Channel I; START = 0 indicates that the current word comes from DMA Channel Q.

In DDR interleave mode, the data buffers alternate every word beginning with Channel I: Channel I Word 0, Channel Q Word 0, Channel I Word 1, Channel Q Word 1, etc.

Section 2.5 shows signal diagrams for both data interleave modes.

# 2.4.3 Interface and DMA Channel Mapping

Typically, DMA Channels I and Q are mapped to interface Channels A and B, respectively. Data interleave mode is the exception, since it allocates both DMA channels to service interface Channel A. Table 2-4 summarizes DMA channel mapping for various modes of operation.

Table 2-4 Interface and DMA Channel Mapping for Various Operating Modes

|                                 | I/O Channel Serviced |       |  |

|---------------------------------|----------------------|-------|--|

| Operating Mode                  | DMA I                | DMA Q |  |

| 1-Channel Receive               | Α                    |       |  |

| 1-Channel Transmit              | Α                    |       |  |

| 2-Channel Receive               | Α                    | В     |  |

| 2-Channel Transmit              | Α                    | В     |  |

| 2-Channel Duplex                | Α                    | В     |  |

| 1-Channel Transmit (Interleave) | Α                    | Α     |  |

| 1-Channel Receive (Interleave)  | A                    | A     |  |

| End of Table 2-4                |                      |       |  |

# 2.5 Protocol Description

The uPP peripheral consists of two independent channels, each possessing its own data lines and control signals. A channel may be configured to run in transmit or receive mode and to use either 8 or 16 data lines (8-bit or 16-bit mode) using the uPP channel control register (UPCTL). A channel may also be configured to ignore certain control signals using the uPP interface configuration register (UPICR). Each uPP defaults to 8-bit mode and uses all four control signals, unless otherwise configured. Table 2-5 summarizes the signals that are required for basic operation in receive and transmit modes. The following subsections describe the role of each signal.

Table 2-5 Required Signals for Various Modes

|                  | Signal Required? |              |

|------------------|------------------|--------------|

| Signal Name      | Transmit Mode    | Receive Mode |

| DATA[7:0]        | $\checkmark$     | $\checkmark$ |

| DATA[15:8]       |                  |              |

| START            | $\checkmark$     |              |

| ENABLE           | √                |              |

| WAIT             |                  | √            |

| CLOCK            | √                | √            |

| End of Table 2-5 |                  |              |

## 2.5.1 DATA[7:0] Signals

In 8-bit mode, DATA[7:0] comprise the channel's entire data bus. In 16-bit mode, DATA[7:0] comprise the least-significant bits of the 16-bit word. The channel's data width is selected using the IWx bit in UPCTL.

In transmit mode, these pins are outputs that transmit data supplied by the channel's associated DMA channel. While the channel is idle, their behavior depends on the TRISx bit in UPICR. These pins can be configured to drive an idle value (TRISx = 0, VALx field in the uPP interface idle value register (UPIVR)) or be in a high-impedance state while idle (TRISx = 1).

In receive mode, these pins are inputs that provide data to the channel's associated DMA channel.

Note that the DATA signals map differently to the DATA and XDATA pins for various uPP configurations. See Section 2.2 for more information.

## 2.5.2 DATA[15:8] Signals

In 8-bit mode, DATA[15:8] are not used. In 16-bit mode, DATA[15:8] comprise the most-significant bits of the 16-bit word. The channel's data width is selected using the IWx bit in UPCTL. A channel may be further configured to use only part of its DATA[15:8] pins, which allows any total data width from 8 to 16 bits. Section 2.5.8 describes data format and packing in the 9-bit to 15-bit configurations.

While in use, the direction and behavior of DATA[15:8] in transmit and receive modes are the same as the direction and behavior of DATA[7:0].

Note that the DATA signals map differently to the DATA and XDATA pins for various uPP configurations. See Section 2.2 for more information.

## 2.5.3 START Signal

The uPP transmitter asserts the START signal when it transfers the first word of a data line. A line is defined in terms of the channel's associated DMA channel; for more on DMA programming concepts, see Section 2.4. The START signal is active-high by default, but its polarity is controlled by the STARTPOLx bit in UPICR.

In transmit mode, START is an output signal and is always driven; in receive mode, START is an input signal and may be disabled using the STARTx bit in UPICR.

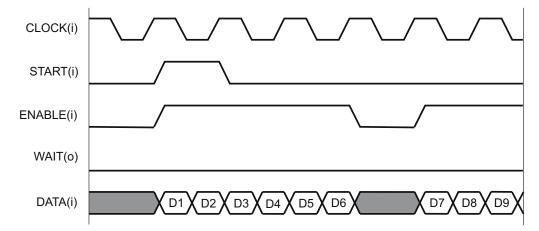

When the channel is configured in transmit mode with data interleave enabled (SDRTXIL = 1 in UPCTL), the START signal function changes completely. The START signal now asserts on every data word that is provided by DMA Channel I. See Section 2.5.7 for this alternative behavior.

## 2.5.4 ENABLE Signal

The uPP transmitter asserts the ENABLE signal when it transfers a valid data word. The ENABLE signal is active-high by default, but its polarity is controlled by the ENAPOLx bit in UPICR.

In transmit mode, ENABLE is an output signal and is always driven; in receive mode, ENABLE is an input signal and may be disabled using the ENAx bit in UPICR.

#### 2.5.5 WAIT Signal

The WAIT signal allows the receiver to request a temporary halt in data transmission. When the receiver asserts WAIT, the transmitter responds by stopping transmission (starting with the next word) until WAIT is released. The receiver ignores all incoming data until WAIT is released. Once WAIT is released, the transmitter can resume transmission on the next word. Figure 2-5 shows WAIT signal timing. The WAIT signal is active-high by default, but its polarity is controlled by the WAITPOLx bit in UPICR.

In transmit mode, WAIT is an input signal and may be disabled using the WAITx bit in UPICR; in receive mode, WAIT is an output signal.

## 2.5.6 CLOCK Signal

The uPP transmitter drives the CLOCK signal to align all other uPP signals. By default, other signals align on the rising edge of CLOCK, but its polarity is controlled by the CLKINVx bit in UPICR. The active edge(s) of CLOCK should always slightly precede transitions of other uPP signals.

In transmit mode, CLOCK is an output signal; in receive mode, CLOCK is an input signal. See Section 2.1 for more information on clock generation and allowed frequencies.

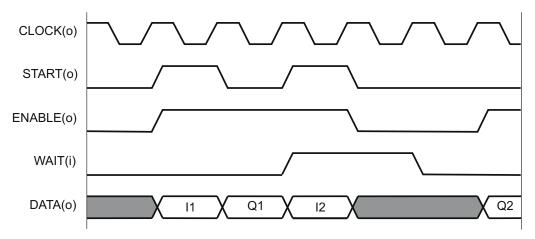

#### 2.5.7 Signal Timing Diagrams

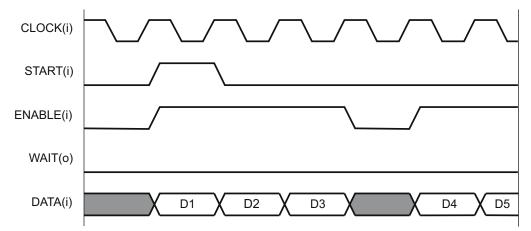

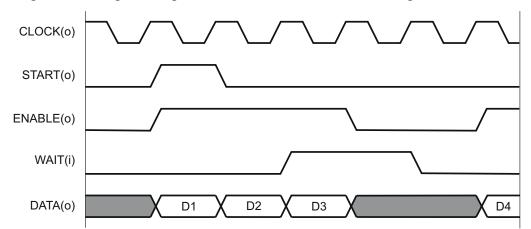

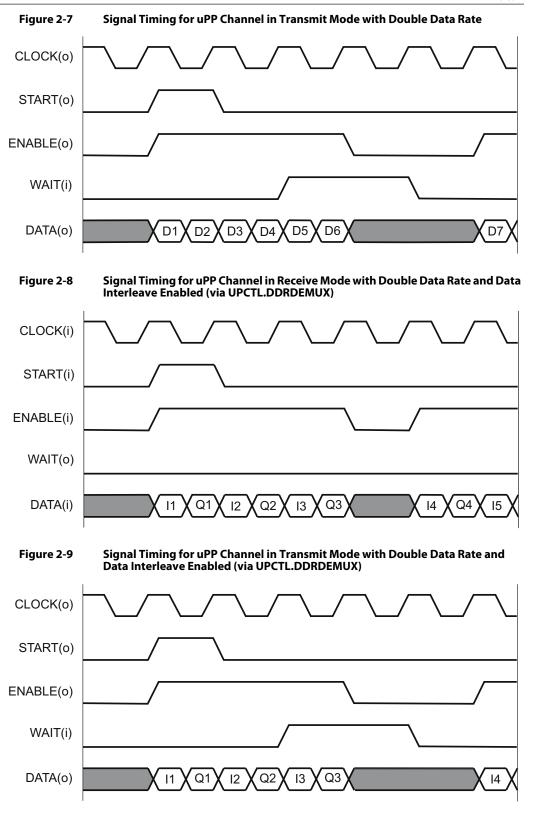

In the following diagrams, signals are marked (I) to indicate that they are inputs to the uPP peripheral and (o) to indicate that they are outputs from the uPP peripheral. Data words from a single DMA channel are designated Dx, while data words that must come from a specific DMA channel are designated Ix or Qx to indicate DMA Channel I or Q, respectively. For more information on DMA channels and data interleave mode, see Section 2.4.

NSTRUMENTS

All signal diagrams are drawn with signal polarities in their default states. All signals except DATA are independently configurable in the uPP interface configuration register (UPICR).

Figure 2-4 Signal Timing for uPP Channel in Receive Mode with Single Data Rate

Figure 2-5 Signal Timing for uPP Channel in Transmit Mode with Single Data Rate

Figure 2-6 Signal Timing for uPP Channel in Receive Mode with Double Data Rate

Figure 2-10 Signal Timing for uPP Channel in Transmit Mode with Single Data Rate and Data Interleave Enabled (via UPCTL.SDRTXIL)

Note—START asserts on every data word from DMA Channel I.

#### 2.5.8 Data Format

The uPP peripheral supports any data word width between 8 to 16 bits using the IWx and DPWx bits in the uPP channel control register (UPCTL). For 8-bit operation, uPP reads/writes 8-bit words in memory; for 16-bit operation, uPP reads/writes 16-bit words in memory.

For N-bit operation (8 < N < 16), the uPP peripheral reads/writes 16-bit words in memory. The "extra" bits are filled by the uPP according to a data packing scheme, selected by the DFWx bit in UPCTL. There are three selectable data packing modes:

- Right-Justify, Zero Extend Data occupies N LSBs. The (16 N) MSBs are cleared to 0.

- Right-Justify, Sign Extend Data occupies N LSBs. The (16 N) MSBs are the same value as the (N 1) bit.

- Left-Justify, Zero Fill Data occupies N MSBs. The (16 N) LSBs are cleared to 0.

Table 2-6 lists some example data for N = 12 (that is, 12-bit operation). In transmit mode, the packed version of each data word from memory is transmitted using all 16 data pins allotted to the uPP channel. In receive mode, the packed version of each incoming data word (using only N data pins) is stored in memory.

Table 2-6 Data Packing Examples for 12-Bit Data Words

| 12-Bit Data Word | Right-Justify, Zero Extend | Right-Justify, Sign Extend | Left-Justify, Zero Fill |  |  |

|------------------|----------------------------|----------------------------|-------------------------|--|--|

| 123h             | 0123h                      | 0123h                      | 1230h                   |  |  |

| ABCh             | 0ABCh                      | FABCh                      | ABC0h                   |  |  |

| 000h             | 0000h                      | 0000h                      | 0000h                   |  |  |

| 800h             | 0800h                      | F800h                      | 8000h                   |  |  |

| FFFh             | 0FFFh                      | FFFFh                      | FFF0h                   |  |  |

| End of Table 2-6 |                            |                            |                         |  |  |

# 2.6 Initialization and Operation

The uPP must be initialized properly to ensure the operation.

# 2.6.1 Step-by-Step Procedure

**Note**—When initializing the uPP peripheral, the uPP interface configuration register (UPICR) must be programmed using a single, 32-bit write. Writing UPICR fields one-by-one can lead to unexpected results.

This section provides step-by-step instructions for initializing and running the uPP peripheral in various modes. These instructions are given assuming that the device has just come out of a power-on reset (POR) state.

#### **Procedure 2-1**

#### Step - Action

- 1 Apply the appropriate pin multiplexing settings. See the device-specific data manual, and/or pin multiplexing utility for more information.

- 2 Enable the power and clocks to the uPP peripheral. See the device-specific data manual for more information.

- 3 Set the SWRST bit in the uPP peripheral control register (UPPCR) to 1 to place uPP in software reset.

- 4 Wait at least 200 device clock cycles, then clear the SWRST bit to 0 to bring the module out of reset.

- **5** Program the uPP configuration registers: UPCTL, UPICR, UPIVR, UPTCR, and UPDLB. The basic function of each register is summarized here; for more information, see Section 3.

- 5a UPCTL Transmit/receive selection (see Table 2-7), data width, data format, data rate, data interleave enable

- **5b** UPICR Signal enable, signal inversion, clock divisor (transmit only)

- **5c** UPIVR Idle value (transmit only)

- 5d UPTCR I/O transmit threshold (transmit only), DMA read burst size

- **5e** UPDLB Digital loopback (see Table 2-7)

- Program the uPP interrupt enable set register (UPIES) to interrupt generation for the desired events. Register an interrupt service routine (ISR) if desired; otherwise, polling is required.

- 7 Set the EN bit in the uPP peripheral control register (UPPCR) to 1 to turn on the uPP peripheral.

- 8 Allocate and/or initialize data buffers for use with uPP.

- 9 Program the DMA channels with their first transfers using the uPP DMA channel descriptor registers: UPID0-2 and/or UPQD0-2.

- Watch for interrupt events. Reprogram the DMA as necessary (checking that the PEND bit in the uPP DMA channel status register (UPxS2) is 0).

- **10a** If polling, check UPIES. Reading a bit as 1 indicates the corresponding event has occurred. Write the corresponding bit with 1 to clear.

- **10b** If using ISR, check UPIES inside the ISR. Structure the ISR according to the pseudo-code in Section 2.6.4.

#### **End of Procedure 2-1**

## 2.6.2 Sample Configuration Settings

The uPP peripheral is flexible, with several orthogonal configuration choices. Table 2-7 summarizes selecting the fundamental operating mode of the module.

**Note**—Digital loopback (DLB) mode is a configuration that the uPP peripheral internally routes data and control signals from one channel to the other. DLB can only be used when the peripheral is configured in duplex mode (that is, UPCTL.MODE = 2h or 3h). DLB is primarily useful for debug purposes, and requires no physical connections between channels. The standard uPP pin multiplexing must be applied, however, even though the pins are not used.

Table 2-7 Basic Operating Mode Selection

|                          | uPP Channel Contro | l Register (UPCTL) Bit | uPP Digital Loopback Register (UPDLB) Bit |    |

|--------------------------|--------------------|------------------------|-------------------------------------------|----|

| Operating Mode           | CHN                | MODE                   | AB                                        | ВА |

| 1-Channel Transmit       | 0                  | 1                      | 0                                         | 0  |

| 1-Channel Receive        | 0                  | 0                      | 0                                         | 0  |

| 2-Channel Transmit       | 1                  | 1                      | 0                                         | 0  |

| 2-Channel Receive        | 1                  | 0                      | 0                                         | 0  |

| 2-Channel Duplex 0       | 1                  | 2h                     | 0                                         | 0  |

| 2-Channel Duplex 1       | 1                  | 3h                     | 0                                         | 0  |

| 2-Channel Duplex 0 (DLB) | 1                  | 2h                     | 0                                         | 1  |

| 2-Channel Duplex 1 (DLB) | 1                  | 3h                     | 1                                         | 0  |

| End of Table 2-7         |                    |                        |                                           |    |

Other than Table 2-7, there are several more choices to make (per channel):

- Data width 8-bit, 9-bit to 16-bit

- Data packing 9-bit to 15-bit data width only

- Data rate single, double

- Data interleave single channel only

- Clock divisor transmit only

- Individual control signal enable

- Individual control signal polarity

- Idle value transmit only

- Transmit threshold transmit only

- DMA read burst size

Table 2-8 lists an example set of uPP parameters for duplex mode 0. This configuration places the uPP peripheral in duplex mode with Channel A receiving and Channel B transmitting. Each channel uses a 16-bit interface with a different data format.

Table 2-8 Sample uPP Parameters for Duplex Mode 0 (Part 1 of 2)

| Register | Register Field <sup>1</sup> | Setting | Description                             |  |

|----------|-----------------------------|---------|-----------------------------------------|--|

| UPCTL    | DPFB                        | 2h      | Data packing: left-justified, zero fill |  |

|          | DPWB                        | 4h      | 12-bit data format                      |  |

|          | IWB                         | 1       | 16-bit                                  |  |

|          | DRB                         | 0       | Single data rate                        |  |

|          | DPFA                        | _       | Unused                                  |  |

Table 2-8 Sample uPP Parameters for Duplex Mode 0 (Part 2 of 2)

| Register         | Register Field <sup>1</sup> | Setting | Description                                          |

|------------------|-----------------------------|---------|------------------------------------------------------|

|                  | DPWA                        | 0       | 16-bit data format                                   |

|                  | IWA                         | 1       | 16-bit                                               |

|                  | DRA                         | 0       | Single data rate                                     |

|                  | CHN                         | 1       | 2-Channel                                            |

|                  | MODE                        | 2h      | Duplex 0: A receive, B transmit                      |

| UPICR            | CLKDIVB                     | 1       | Divide by 2 (total division of transmit clock: 4)    |

|                  | CLKDIVA                     | _       | Unused                                               |

| UPIVR            | VALB                        | 0BBBh   | Note idle value is 12-bit data format; 4 MSBs unused |

|                  | VALA                        | _       | Unused                                               |

| UPIES            | EOLQ                        | 1       | Turn on EOL interrupt for Channel B (DMA Channel Q)  |

|                  | EOWQ                        | 1       | Turn on EOW interrupt for Channel B (DMA Channel Q)  |

|                  | EOLI                        | 1       | Turn on EOL interrupt for Channel A (DMA Channel I)  |

|                  | EOWI                        | 1       | Turn on EOW interrupt for Channel A (DMA Channel I)  |

| End of Table 2-8 | 3                           |         |                                                      |

<sup>1.</sup> Unlisted register fields are left at their default values (typically 0), see Section 3.

# 2.6.3 System Tuning Tips

The uPP peripheral can operate at high speed and transfer data at a very high rate. When operating the uPP near its upper limits, tuning certain parameters can help decrease the incidence of errors and the software overhead incurred servicing uPP data. Table 2-9 lists several parameters that can be useful in system tuning. A parameter is defined as a "coarse" adjustment, if changing the parameter directly alters the peripheral throughput. A "fine" adjustment does not change the peripheral throughput, but it does affect general system performance.

Table 2-9 uPP Parameters Useful for System Tuning

| Desilet and |                            |                                                                               |                                                                                                                                                                                                               |                                                                                                                                                                                                                                                              |  |

|-------------|----------------------------|-------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Register    | Field                      | Edge Value                                                                    | Safe Value                                                                                                                                                                                                    | Description                                                                                                                                                                                                                                                  |  |

| UPCTL       | DRB DRA                    | 1                                                                             | 0                                                                                                                                                                                                             | Double data rate increases data transfer by a factor of 2 and greatly increases system loading for the same clock divisor. This is a coarse adjustment and is probably fixed due to design constraints.                                                      |  |

| UPICR       | CLKDIVB<br>CLKDIVA         | 0                                                                             | 1+                                                                                                                                                                                                            | Increasing clock division is the most straight-forward way to decrease system loading. This is a coarse adjustment; the difference between CLKDIVx = 0 and 1 is the same (in terms of data rate) as the difference between single and double data rate.      |  |

| UPTCR       | RDSIZEQ<br>RDSIZEI         | 0                                                                             | 3h                                                                                                                                                                                                            | Increasing the DMA read threshold decreases system loading by generating fewer, larger DMA events. This is a fine adjustment.                                                                                                                                |  |

| UPxD1       | LNCNT BCNT                 |                                                                               | 1                                                                                                                                                                                                             | Condensing uPP transfers into fewer, larger lines generates fewer end-of-line interrupts and, thus, invokes fewer ISR calls. This is a fine adjustment.                                                                                                      |  |

| UPxD1       | LNCNT BCNT                 | 1                                                                             | 1                                                                                                                                                                                                             | Performing many small uPP transfers can require excessive software overhead (programming DMA descriptors, handling interrupts, etc.) at high data rates. This is a fine adjustment.                                                                          |  |

|             |                            | 2                                                                             | 2                                                                                                                                                                                                             | When the uPP operates in parallel with other data masters, such as EDMA, assigning higher priority to the uPP may help the uPP avoid underflow or overflow conditions. This is a fine adjustment.                                                            |  |

|             | UPCTL  UPICR  UPTCR  UPXD1 | UPCTL DRB DRA  UPICR CLKDIVB CLKDIVA  UPTCR RDSIZEQ RDSIZEI  UPxD1 LNCNT BCNT | Register     Field     Edge Value       UPCTL     DRB DRA     1       UPICR     CLKDIVB CLKDIVA     0       UPTCR     RDSIZEQ RDSIZEI     0       UPxD1     LNCNT BCNT     1       UPxD1     LNCNT BCNT     1 | Register     Field     Edge Value     Safe Value       UPCTL     DRB DRA     1     0       UPICR     CLKDIVB CLKDIVA     0     1+       UPTCR     RDSIZEQ RDSIZEI     0     3h       UPxD1     LNCNT BCNT     1     1       UPxD1     LNCNT BCNT     1     1 |  |

<sup>1.</sup> These values vary per application. One example could be a 16-KB transfer. The same total data could be transferred as 16 1-KB lines or 2 8-KB lines.

<sup>2.</sup> System priority settings are not set within the uPP peripheral. See the device-specific data manual for more information.

#### 2.6.4 Sample Interrupt Service Routine

The following pseudo-code serves as a template for writing a uPP interrupt service routing (ISR) function. Note that the uPP combines all events into a single CPU interrupt, and a new interrupt does not call the ISR if the previous interrupt still has not returned from the ISR. To allow future ISR calls, the uPP end-of-interrupt register (UPEOI) must be written with a zero value. Thus, the ISR should check for multiple events, and should continue rechecking after handling each individual event until no more events are found. Then, it must write UPEOI = 0 before returning.

```

Function upp isr

interrupt status = UPIER

while (interrupt_status != 0)

if (interrupt_status.EOLI)

UPIER.EOLI = 1 // clear EOLI

// Handle EOLI...

if (interrupt status.EOWI)

UPIER.EOWI = 1 // clear EOWI

// Handle EOWI...

if (interrupt_status.ERRI)

UPIER.ERRI = 1 // clear ERRI

// Handle ERRI...

if (interrupt_status.UORI)

UPIER.UORI = 1 // clear UORI

// Handle UORI...

if (interrupt status.DPEI)

UPIER.DPEI = 1 // clear DPEI

// Handle DPEI...

if (interrupt status.EOLQ)

UPIER.EOLQ = 1 // clear EOLQ

// Handle EOLQ...

if (interrupt_status.EOWQ)

UPIER.EOWQ = 1 // clear EOWQ

// Handle EOWQ...

if (interrupt status.ERRQ)

UPIER.ERRQ = 1 // clear ERRQ

// Handle ERRQ...

if (interrupt_status.UORQ)

UPIER.UORQ = 1 // clear UORQ

// Handle UORQ...

if (interrupt_status.DPEQ)

UPIER.DPEQ = 1 // clear DPEQ

// Handle DPEQ...

// loop again if any interrupts are left

interrupt_status = UPIER

// end of while

// write end of interrupt vector to allow future calls

UPEOI = 0

} // end of function

```

Chapter 2—Architecture www.ti.com

#### 2.7 Reset Considerations

The following sections discuss the behaviors of the software and hardware resets.

#### 2.7.1 Software Reset

Software reset clears the uPP internal state machines but does not reset the contents of the uPP registers. The following procedure performs a software reset on the uPP peripheral.

#### **Procedure 2-2**

#### Step - Action

- 1 Write the EN bit in the uPP peripheral control register (UPPCR) to 0 (disables the uPP).

- Poll the DB bit in UPPCR for activity; wait until DMA controller is inactive/idle.

- **3** Write the SWRST bit UPPCR to 1 (places uPP in software reset).

- **4** Write the SWRST bit UPPCR to 0 to (brings uPP out of software reset).

#### **End of Procedure 2-2**

#### 2.7.2 Hardware Reset

When the processor RESET pin is asserted, the entire processor is reset and is held in the reset state until the RESET pin is released. As part of a device reset, the uPP state machines are reset, and the uPP registers are forced to their default states (see Section 3).

## 2.8 Interrupt Support

The uPP peripheral generates eight interrupt events, all tied to internal DMA Channels I and Q. The uPP peripheral automatically combines all interrupt events into a single chip-level interrupt. Individual events may be enabled using the uPP interrupt enable set register (UPIES) and disabled using the uPP interrupt enable clear register (UPIEC). Only enabled events generate interrupts and assert bits in the interrupt enabled status register (UPIER). Disabled events do not generate interrupts but do assert bits in the interrupt raw status register (UPISR).

An interrupt service routine (ISR) may be assigned to handle uPP chip-level interrupts using the interrupt controller module. If uPP events occur in close proximity to one another, a single CPU interrupt (and a single call to the ISR) may represent multiple interrupt events. Thus, the uPP ISR must meet certain structural requirements:

- The ISR must be able to handle multiple events before returning.

- The ISR must handle any subsequent events that occur after it is called but before it returns.

- The ISR must write 00h to the uPP end-of-interrupt register (UPEOI) just before it returns. This allows future uPP events to generate a CPU interrupt.

Section 2.6 provides a sample ISR that demonstrates these requirements.

#### 2.8.1 End of Line (EOL) Event

This event occurs each time that the DMA channel reaches the end of a line in the data window. Note that if the associated uPP interface channel is operating in transmit mode, this event may occur before the line's final bytes are actually transmitted over the data pins.

For small line size and fast data transfer, it is possible to "miss" EOL events if they occur faster than the user's code can handle them. This does not hinder uPP operation; the uPP peripheral continue processing data uninterrupted until the EOW event or some error condition is encountered.

#### 2.8.2 End of Window (EOW) Event

This event occurs when the DMA channel reaches the end of its current data window. Note that if the associated uPP interface channel is operating in transmit mode, this event may occur shortly before the window's final bytes are actually transmitted over the data pins.

When an EOW event occurs, the DMA channel automatically begins the next DMA transfer if one has been pre-programmed into the channel descriptor registers. If no new transfer is preprogrammed, the DMA channel becomes idle. For small window size and fast data transfer, code overhead may make it impossible to maintain a constant flow of data through the uPP interface channel. This problem can be solved by increasing the DMA window size or decreasing the peripheral clock speed.

## 2.8.3 Internal Bus Error (ERR) Event

This event occurs when the uPP peripheral or its internal DMA controller encounters an internal bus error. After encountering this error, the uPP peripheral should be reset to avoid further problem.

hapter 2—Architecture www.ti.com

#### 2.8.4 Underrun or Overflow (UOR) Event

This event occurs when the DMA channel fails to keep up with incoming or outgoing data on its associated interface channel. Typically, this error indicates that background system activity has interfered with normal operation of the peripheral. It does not occur simply when a channel is allowed to idle. After encountering this error, the uPP peripheral should be reset when this event occurs.

This error should primarily occur when operating the uPP at high speed with significant system loading. To avoid this error, run the uPP at slower speeds or reduce background activity, such as non-uPP peripheral or DMA transactions. Additional tuning tips are given in Section 2.6.3.

## 2.8.5 DMA Programming Error (DPE) Event

This event occurs when the DMA channel descriptors are programmed while its PEND bit in the uPP DMA channel status register (UPxS2) is set to 1. A channel's descriptors should only be programmed while the channel's PEND bit is cleared to 0.

## 2.9 Power Management

The uPP peripheral can be placed in reduced-power modes to conserve power during periods of inactivity. For information on power management, see the device-specific *data manual*.

#### 2.10 Emulation Considerations

The uPP peripheral stops running if any of three conditions are met:

- Peripheral Disable EN bit in the uPP peripheral control register (UPPCR) is 0.

- Clock Stop uPP acknowledges a clock stop request from the device power management module.

- Emulation Suspend JTAG emulator halts chip while FREE = 0 and SOFT = 1 in UPPCR.

For other settings of FREE and SOFT, the uPP peripheral continues running during emulation halt.

When the uPP encounters a stop condition, it completes the current DMA burst transaction (if one is active) before stopping.

An I/O channel configured in transmit mode immediately places its pins in a high-impedance state and preserves the state of its internal state machines. Unless some reset event occurs (see Section 2.7), the channel can resume where it left off when the stop condition is cleared.

An I/O channel configured in receive mode immediately asserts its WAIT signal (see Section 2.5.5) and captures one additional data word. Further incoming data words are ignored as long as the stop condition persists.

#### 2.11 Transmit and Receive FIFOs

Each of the uPP peripheral I/O channels has a 512-byte FIFO. In receive mode, the FIFO is divided into eight 64-byte blocks. In transmit mode, the FIFO is divided into blocks that can be set to 64, 128, or 256 bytes, configured by the TXSIZEA or TXSIZEB field in the uPP threshold configuration register (UPTCR). Transmission will not begin until the channel has loaded enough data to fill at least one full FIFO block.

The internal DMA channels may also be configured to use a read threshold of 64, 128, or 256 bytes using the RDSIZEI or RDSIZEQ field in UPTCR. The DMA write threshold is fixed at 64 bytes.

# Registers

"Introduction" on page 3-2 "uPP Peripheral Identification Register (UPPID)" on page 3-3 "uPP Peripheral Control Register (UPPCR)" on page 3-4 "uPP Digital Loopback Register (UPDLB)" on page 3-5 "uPP Channel Control Register (UPCTL)" on page 3-6 3.5 "uPP Interface Configuration Register (UPICR)" on page 3-8 "uPP Interface Idle Value Register (UPIVR)" on page 3-11 "uPP Threshold Configuration Register (UPTCR)" on page 3-12 "uPP Interrupt Raw Status Register (UPISR)" on page 3-13 "uPP Interrupt Enabled Status Register (UPIER)" on page 3-15 3.10 "uPP Interrupt Enable Set Register (UPIES)" on page 3-17 3.11 3.12 "uPP Interrupt Enable Clear Register (UPIEC)" on page 3-19 "uPP End of Interrupt Register (UPEOI)" on page 3-21 3.13 "uPP DMA Channel I Descriptor 0 Register (UPID0)" on page 3-22 "uPP DMA Channel I Descriptor 1 Register (UPID1)" on page 3-23 3.15 "uPP DMA Channel I Descriptor 2 Register (UPID2)" on page 3-24 3.16 "uPP DMA Channel I Status 0 Register (UPIS0)" on page 3-25 3.17 "uPP DMA Channel I Status 1 Register (UPIS1)" on page 3-26 3.18 "uPP DMA Channel I Status 2 Register (UPIS2)" on page 3-27 3.19 "uPP DMA Channel Q Descriptor 0 Register (UPQD0)" on page 3-28 3.20 "uPP DMA Channel Q Descriptor 1 Register (UPQD1)" on page 3-29 3.21 "uPP DMA Channel Q Descriptor 2 Register (UPQD2)" on page 3-30 3.22 "uPP DMA Channel Q Status 0 Register (UPQS0)" on page 3-31 3.23 "uPP DMA Channel Q Status 1 Register (UPQS1)" on page 3-32 3.24 3.25 "uPP DMA Channel Q Status 2 Register (UPQS2)" on page 3-33

Chapter 3—Registers www.ti.com

#### 3.1 Introduction

The system programmer has access to and control over any of the uPP registers that are listed in Table 3-1. These registers, which control uPP I/O and DMA operations, are available at 32-bit addresses in the device memory-map. The device-specific data manual lists the base memory address of these registers.

Table 3-1 uPP Registers

| Address Offset   | Acronym | Register Description                    | Section      |

|------------------|---------|-----------------------------------------|--------------|

| 0                | UPPID   | uPP Peripheral Identification Register  | Section 3.2  |

| 4h               | UPPCR   | uPP Peripheral Control Register         | Section 3.3  |

| 8h               | UPDLB   | uPP Digital Loopback Register           | Section 3.4  |

| 10h              | UPCTL   | uPP Channel Control Register            | Section 3.5  |

| 14h              | UPICR   | uPP Interface Configuration Register    | Section 3.6  |

| 18h              | UPIVR   | uPP Interface Idle Value Register       | Section 3.7  |

| 1Ch              | UPTCR   | uPP Threshold Configuration Register    | Section 3.8  |

| 20h              | UPISR   | uPP Interrupt Raw Status Register       | Section 3.9  |

| 24h              | UPIER   | uPP Interrupt Enabled Status Register   | Section 3.10 |

| 28h              | UPIES   | uPP Interrupt Enable Set Register       | Section 3.11 |

| 2Ch              | UPIEC   | uPP Interrupt Enable Clear Register     | Section 3.12 |

| 30h              | UPEOI   | uPP End-of-Interrupt Register           | Section 3.13 |

| 40h              | UPID0   | uPP DMA Channel I Descriptor 0 Register | Section 3.14 |

| 44h              | UPID1   | uPP DMA Channel I Descriptor 1 Register | Section 3.15 |

| 48h              | UPID2   | uPP DMA Channel I Descriptor 2 Register | Section 3.16 |

| 50h              | UPIS0   | uPP DMA Channel I Status 0 Register     | Section 3.17 |

| 54h              | UPIS1   | uPP DMA Channel I Status 1 Register     | Section 3.18 |

| 58h              | UPIS2   | uPP DMA Channel I Status 2 Register     | Section 3.19 |

| 60h              | UPQD0   | uPP DMA Channel Q Descriptor 0 Register | Section 3.20 |

| 64h              | UPQD1   | uPP DMA Channel Q Descriptor 1 Register | Section 3.21 |

| 68h              | UPQD2   | uPP DMA Channel Q Descriptor 2 Register | Section 3.22 |

| 70h              | UPQS0   | uPP DMA Channel Q Status 0 Register     | Section 3.23 |

| 74h              | UPQS1   | uPP DMA Channel Q Status 1 Register     | Section 3.24 |

| 78h              | UPQS2   | uPP DMA Channel Q Status 2 Register     | Section 3.25 |