Preliminary

# TMS320C6452 Telecom Serial Interface Port (TSIP)

# **User's Guide**

Literature Number: SPRUF96A October 2007–Revised September 2008 Preliminary

# Contents

| 1       Introduction/Feature Overview.       9         1.1       Overview/Purpose of the Peripheral.       9         1.2       Features.       9         1.3       Functional Block Diagram       10         1.4       Terminology Used       11         1.5       Memory Map       11         2       Features/Common Architecture       12         2.1       Interface       12         2.2       Receive Operation       12         2.3       Bitmap Context       12         2.4       Serial Link Processing and Buffering       14         2.5       Multi-Channel Operation       16         2.6       Transmit Operation       19         2.7       Interrupts       20         2.8       Endianness       23         2.9       Priority Control       24         3       Clocks, Frames and Data       25         3.1       Frame and Clock Operation       25         3.3       Clock and Frame Sync Redundancy       25         3.4       Single and Double Data Rate       26         3.5       Clock and Frame Sync Selection and Polarity       26         3.6       Data Delay       27     <                                                                                   | Pref | ace     |                                                       | 7   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|-------------------------------------------------------|-----|

| 1.2       Features       9         1.3       Functional Block Diagram       10         1.4       Terminology Used       11         1.5       Memory Map       11         2       Features/Common Architecture       12         2.1       Interface       12         2.2       Receive Operation       12         2.3       Bitmap Context.       12         2.4       Serial Link Processing and Buffering       14         2.5       Multi-Channel Operation       16         2.6       Transmit Operation       16         2.7       Interrupts.       20         2.8       Endianness       23         2.9       Priority Control       24         3       Clocks, Frames and Data       25         3.1       Frame and Clock Operation       25         3.2       Data Rate Options       25         3.3       Clock and Frame Sync Redundancy       25         3.4       Single and Double Data Rate       26         3.5       Clock and Frame Sync Selection and Polarity       26         3.6       Data Palay       27         3.7       Data and Frames       28         3.8<                                                                                                        | 1    | Introdu | uction/Feature Overview                               | 9   |

| 1.3       Functional Block Diagram       10         1.4       Terminology Used       11         1.5       Memory Map       11         2       Features/Common Architecture       12         2.1       Interface       12         2.3       Bitmap Context.       12         2.3       Bitmap Context.       12         2.4       Serial Link Processing and Buffering       14         2.5       Multi-Channel Operation       16         2.6       Transmit Operation       16         2.7       Interrupts.       20         2.8       Endianness       23         2.9       Priority Control       24         3       Clocks, Frames and Data.       25         3.1       Frame and Clock Operation       25         3.2       Data Rate Options       25         3.3       Clock and Frame Sync Redundancy       25         3.4       Single and Double Data Rate       26         3.5       Clock and Frames       28         3.6       Data Paley       27         3.7       Data and Frames       28         3.8       Data Synchronization       26         3.8                                                                                                                        |      | 1.1     | Overview/Purpose of the Peripheral                    | . 9 |

| 1.4       Terminology Used       11         1.5       Memory Map       11         2       Features/Common Architecture       12         2.1       Interface.       12         2.2       Receive Operation       12         2.3       Bitmap Context       12         2.4       Serial Link Processing and Buffering       14         2.5       Multi-Channel Operation       16         2.6       Transmit Operation       16         2.7       Interrupts       20         2.8       Endianness       23         2.9       Priority Control       24         3       Clocks, Frames and Data       25         3.1       Frame and Clock Operation       25         3.2       Data Rate Options       25         3.3       Clock and Frame Sync Redundancy       26         3.4       Single and Double Data Rate       26         3.5       Clock and Frame Sync Redundancy       26         3.6       Data Delay       27         3.7       Data and Frames       26         3.8       Data Synchronization       29         4       Reset and Powerdown Modes       30       30 <t< td=""><td></td><td>1.2</td><td>Features</td><td>. 9</td></t<>                                           |      | 1.2     | Features                                              | . 9 |

| 1.5       Memory Map       11         2       Features/Common Architecture       12         2.1       Interface       12         2.2       Receive Operation       12         2.3       Bitmap Context       12         2.4       Serial Link Processing and Buffering       14         2.5       Multi-Channel Operation       16         2.6       Transmit Operation       19         2.7       Interrupts       20         2.8       Endianness       23         2.9       Priority Control       24         3       Clocks, Frames and Data       25         3.1       Frame and Clock Operation       25         3.3       Clock and Frame Sync Redundancy       25         3.4       Single and Double Data Rate       26         3.5       Clock and Frame Sync Selection and Polarity       26         3.6       Data Synchronization       28         3.8       Data Synchronization       29         4       Reset and Powerdown Modes       30         4.1       SIU Reset and Shutdown Operation       30         4.2       TDMU and DMATCU Software Reset and Shutdown Operation       31         4.3                                                                            |      | 1.3     | Functional Block Diagram                              | 10  |

| 2       Features/Common Architecture.       12         2.1       Interface.       12         2.2       Receive Operation.       12         2.3       Bitmap Context.       12         2.4       Serial Link Processing and Buffering.       14         2.5       Multi-Channel Operation.       16         2.6       Transmit Operation.       19         2.7       Interrupts.       20         2.8       Endianness       23         2.9       Priority Control       24         3       Clocks, Frames and Data.       25         3.1       Frame and Clock Operation.       25         3.2       Data Rate Options.       25         3.3       Clock and Frame Sync Redundancy.       25         3.4       Single and Double Data Rate.       26         3.5       Clock and Frame Sync Selection and Polarity.       26         3.6       Data Delay.       27         3.7       Data and Frames.       28         3.8       Data Synchronization.       29         4       Reset and Powerdown Modes       30         4.1       SIU Reset and Shutdown Operation.       31         5.1       Emulation - Free Run <td></td> <td>1.4</td> <td>Terminology Used</td> <td>11</td>           |      | 1.4     | Terminology Used                                      | 11  |

| 2.1       Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      | 1.5     | Memory Map                                            | 11  |

| 2.2       Receive Operation       12         2.3       Bitmap Context.       12         2.4       Serial Link Processing and Buffering       14         2.5       Multi-Channel Operation       16         2.6       Transmit Operation       16         2.7       Interrupts       20         2.8       Endianness       23         2.9       Priority Control       24         3       Clocks, Frames and Data       25         3.1       Frame and Clock Operation       25         3.1       Frame and Clock Operation       25         3.2       Data Rate Options       25         3.3       Clock and Frame Sync Redundancy       25         3.4       Single and Double Data Rate       26         3.5       Clock and Frame Sync Selection and Polarity       26         3.6       Data Delay       27         3.7       Data and Frames       28         3.8       Data Synchronization       29         4       Reset and Powerdown Modes       30         4.1       SU Reset and Shutdown Operation       30         4.1       SU Reset and Shutdown Operation       31         4.3       Powerdown                                                                                | 2    | Featur  | es/Common Architecture                                | 12  |

| 2.3       Bitmap Context.       12         2.4       Serial Link Processing and Buffering       14         2.5       Multi-Channel Operation       16         2.6       Transmit Operation       19         2.7       Interrupts       20         2.8       Endianness       23         2.9       Priority Control       24         3       Clocks, Frames and Data       25         3.1       Frame and Clock Operation       25         3.2       Data Rate Options       25         3.3       Clock and Frame Sync Redundancy       25         3.4       Single and Double Data Rate       26         3.5       Clock and Frame Sync Redundancy       25         3.6       Data Data Rate       26         3.5       Clock and Frame Sync Redundancy       25         3.4       Single and Double Data Rate       26         3.5       Clock and Frame Sync Selection and Polarity       26         3.6       Data Pata Parmes       27         3.7       Data and Frames       28         3.8       Data Synchronization       29         4       Reset and Powerdown Modes       30         4.1       SU Reset and Sh                                                                     |      | 2.1     | Interface                                             | 12  |

| 2.4       Serial Link Processing and Buffering       14         2.5       Multi-Channel Operation       16         2.6       Transmit Operation       19         2.7       Interrupts       20         2.8       Endianness       23         2.9       Priority Control       24         3       Clocks, Frames and Data       25         3.1       Frame and Clock Operation       25         3.2       Data Rate Options       25         3.3       Clock and Frame Sync Redundancy       25         3.4       Single and Double Data Rate       26         3.5       Clock and Frame Sync Redundancy       25         3.4       Single and Double Data Rate       26         3.5       Clock and Frame Sync Selection and Polarity       26         3.6       Data Delay       27         3.7       Data and Frames       28         3.8       Data Synchronization       29         4       Reset and Powerdown Modes       30         4.1       SIU Reset and Shutdown Operation       30         4.2       TDMU and DMATCU Software Reset and Shutdown Operation       31         4.3       Powerdown       31         5.4 <td></td> <td>2.2</td> <td>Receive Operation</td> <td>12</td> |      | 2.2     | Receive Operation                                     | 12  |

| 2.5       Multi-Channel Operation       16         2.6       Transmit Operation       19         2.7       Interrupts       20         2.8       Endianness       23         2.9       Priority Control       24         3       Clocks, Frames and Data.       25         3.1       Frame and Clock Operation       25         3.2       Data Rate Options       25         3.3       Clock and Frame Sync Redundancy       25         3.4       Single and Double Data Rate       26         3.5       Clock and Frame Sync Redundancy       25         3.4       Single and Double Data Rate       26         3.5       Clock and Frame Sync Selection and Polarity       26         3.6       Data Delay       27         3.7       Data and Frames       28         3.8       Data Synchronization       29         4       Reset and Powerdown Modes       30         4.1       SIU Reset and Shutdown Operation       30         4.2       TDMU and DMATCU Software Reset and Shutdown Operation       31         4.3       Powerdown       31         5       Emulation - Free Run       32         5.1       Emul                                                                     |      | 2.3     | Bitmap Context                                        | 12  |

| 2.6       Transmit Operation       19         2.7       Interrupts       20         2.8       Endianness       23         2.9       Priority Control       24         3       Clocks, Frames and Data       25         3.1       Frame and Clock Operation       25         3.2       Data Rate Options       25         3.3       Clock and Frame Sync Redundancy       25         3.3       Clock and Frame Sync Redundancy       25         3.4       Single and Double Data Rate       26         3.5       Clock and Frame Sync Selection and Polarity       26         3.6       Data Palay       27         3.7       Data and Frames       28         3.8       Data Synchronization       29         4       Reset and Powerdown Modes       30         4.1       SIU Reset and Shutdown Operation       30         4.1       SIU Reset and Shutdown Operation       31         4.3       Powerdown       31         5       Emulation and Loopback Modes       32         5.1       Emulation - Free Run       32         5.2       Emulation - Halt       32         5.3       Loopback Modes       33                                                                              |      | 2.4     | Serial Link Processing and Buffering                  | 14  |

| 2.7       Interrupts.       20         2.8       Endianness       23         2.9       Priority Control       24         3       Clocks, Frames and Data       25         3.1       Frame and Clock Operation       25         3.2       Data Rate Options       25         3.3       Clock and Frame Sync Redundancy       25         3.4       Single and Double Data Rate       26         3.5       Clock and Frame Sync Redundancy       25         3.4       Single and Double Data Rate       26         3.5       Clock and Frame Sync Selection and Polarity       26         3.6       Data Delay       27         3.7       Data and Frames       28         3.8       Data Synchronization       29         4       Reset and Powerdown Modes       30         4.1       SIU Reset and Shutdown Operation       30         4.2       TDMU and DMATCU Software Reset and Shutdown Operation       31         4.3       Powerdown       31         5.4       Emulation - Free Run       32         5.1       Emulation - Free Run       32         5.2       Emulation - Halt       32         5.3       Loopbac                                                                     |      | 2.5     | Multi-Channel Operation                               | 16  |

| 2.8       Endianness       23         2.9       Priority Control       24         3       Clocks, Frames and Data       25         3.1       Frame and Clock Operation       25         3.2       Data Rate Options       25         3.3       Clock and Frame Sync Redundancy       25         3.4       Single and Double Data Rate       26         3.5       Clock and Frame Sync Selection and Polarity       26         3.6       Data Delay       27         3.7       Data and Frames       28         3.8       Data Synchronization       29         4       Reset and Powerdown Modes       30         4.1       SIU Reset and Shutdown Operation       30         4.2       TDMU and DMATCU Software Reset and Shutdown Operation       31         4.3       Powerdown       31         5.4       Emulation - Free Run       32         5.1       Emulation - Free Run       32         5.2       Emulation - Halt       32         5.3       Loopback Modes       33                                                                                                                                                                                                              |      | 2.6     | Transmit Operation                                    | 19  |

| 2.9       Priority Control       24         3       Clocks, Frames and Data.       25         3.1       Frame and Clock Operation.       25         3.2       Data Rate Options.       25         3.3       Clock and Frame Sync Redundancy.       25         3.4       Single and Double Data Rate       26         3.5       Clock and Frame Sync Redundancy.       26         3.6       Data Data Rate       26         3.7       Dick and Frame Sync Selection and Polarity.       26         3.6       Data Delay.       27         3.7       Data and Frames       28         3.8       Data Synchronization       29         4       Reset and Powerdown Modes       30         4.1       SIU Reset and Shutdown Operation       30         4.2       TDMU and DMATCU Software Reset and Shutdown Operation       31         4.3       Powerdown       31         5.4       Emulation - Free Run       32         5.1       Emulation - Free Run       32         5.2       Emulation - Halt       32         5.3       Loopback Modes       33                                                                                                                                         |      | 2.7     | Interrupts                                            | 20  |

| 3       Clocks, Frames and Data.       25         3.1       Frame and Clock Operation.       25         3.2       Data Rate Options.       25         3.3       Clock and Frame Sync Redundancy.       25         3.4       Single and Double Data Rate.       26         3.5       Clock and Frame Sync Redundancy.       26         3.6       Data Data Rate       26         3.5       Clock and Frame Sync Selection and Polarity.       26         3.6       Data Delay.       27         3.7       Data and Frames       28         3.8       Data Synchronization       29         4       Reset and Powerdown Modes       30         4.1       SIU Reset and Shutdown Operation       30         4.2       TDMU and DMATCU Software Reset and Shutdown Operation       31         4.3       Powerdown       31         4.3       Powerdown       32         5.1       Emulation - Free Run       32         5.2       Emulation - Halt       32         5.3       Loopback Modes       33                                                                                                                                                                                              |      | 2.8     | Endianness                                            | 23  |

| 3.1       Frame and Clock Operation       25         3.2       Data Rate Options       25         3.3       Clock and Frame Sync Redundancy       25         3.4       Single and Double Data Rate       26         3.5       Clock and Frame Sync Selection and Polarity       26         3.6       Data Delay       27         3.7       Data and Frames       28         3.8       Data Synchronization       29         4       Reset and Powerdown Modes       30         4.1       SIU Reset and Shutdown Operation       30         4.2       TDMU and DMATCU Software Reset and Shutdown Operation       31         4.3       Powerdown       31         5.4       Emulation - Free Run       32         5.1       Emulation - Halt       32         5.3       Loopback Modes       33                                                                                                                                                                                                                                                                                                                                                                                                 |      | 2.9     | Priority Control                                      | 24  |

| 3.2       Data Rate Options.       25         3.3       Clock and Frame Sync Redundancy.       25         3.4       Single and Double Data Rate       26         3.5       Clock and Frame Sync Selection and Polarity.       26         3.6       Data Delay.       27         3.7       Data and Frames       28         3.8       Data Synchronization       29         4       Reset and Powerdown Modes       30         4.1       SIU Reset and Shutdown Operation       30         4.2       TDMU and DMATCU Software Reset and Shutdown Operation       31         4.3       Powerdown       31         5       Emulation and Loopback Modes       32         5.1       Emulation - Free Run       32         5.2       Emulation - Halt       32         5.3       Loopback Modes       33                                                                                                                                                                                                                                                                                                                                                                                            | 3    | Clocks  | s, Frames and Data                                    | 25  |

| 3.3       Clock and Frame Sync Redundancy.       25         3.4       Single and Double Data Rate       26         3.5       Clock and Frame Sync Selection and Polarity.       26         3.6       Data Delay.       27         3.7       Data and Frames       28         3.8       Data Synchronization       29         4       Reset and Powerdown Modes       30         4.1       SIU Reset and Shutdown Operation       30         4.2       TDMU and DMATCU Software Reset and Shutdown Operation       31         4.3       Powerdown       31         5       Emulation and Loopback Modes       32         5.1       Emulation - Free Run       32         5.2       Emulation - Halt       32         5.3       Loopback Modes       33                                                                                                                                                                                                                                                                                                                                                                                                                                          |      | 3.1     | Frame and Clock Operation                             | 25  |

| 3.4       Single and Double Data Rate       26         3.5       Clock and Frame Sync Selection and Polarity       26         3.6       Data Delay       27         3.7       Data and Frames       28         3.8       Data Synchronization       29         4       Reset and Powerdown Modes       30         4.1       SIU Reset and Shutdown Operation       30         4.2       TDMU and DMATCU Software Reset and Shutdown Operation       31         4.3       Powerdown       31         5       Emulation and Loopback Modes       32         5.1       Emulation - Free Run       32         5.2       Emulation - Halt       32         5.3       Loopback Modes       33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      | 3.2     | Data Rate Options                                     | 25  |

| 3.5       Clock and Frame Sync Selection and Polarity.       26         3.6       Data Delay.       27         3.7       Data and Frames .       28         3.8       Data Synchronization .       29         4       Reset and Powerdown Modes .       30         4.1       SIU Reset and Shutdown Operation .       30         4.2       TDMU and DMATCU Software Reset and Shutdown Operation .       31         4.3       Powerdown .       31         5       Emulation and Loopback Modes .       32         5.1       Emulation - Free Run .       32         5.2       Emulation - Halt .       32         5.3       Loopback Modes .       33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      | 3.3     | Clock and Frame Sync Redundancy                       | 25  |

| 3.6       Data Delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      | 3.4     | Single and Double Data Rate                           | 26  |

| 3.7       Data and Frames       28         3.8       Data Synchronization       29         4       Reset and Powerdown Modes       30         4.1       SIU Reset and Shutdown Operation       30         4.2       TDMU and DMATCU Software Reset and Shutdown Operation       31         4.3       Powerdown       31         5       Emulation and Loopback Modes       32         5.1       Emulation - Free Run       32         5.2       Emulation - Halt       32         5.3       Loopback Modes       33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      | 3.5     | Clock and Frame Sync Selection and Polarity           | 26  |

| 3.8       Data Synchronization       29         4       Reset and Powerdown Modes       30         4.1       SIU Reset and Shutdown Operation       30         4.2       TDMU and DMATCU Software Reset and Shutdown Operation       31         4.3       Powerdown       31         5       Emulation and Loopback Modes       32         5.1       Emulation - Free Run       32         5.2       Emulation - Halt       32         5.3       Loopback Modes       33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      | 3.6     | Data Delay                                            | 27  |

| 4       Reset and Powerdown Modes       30         4.1       SIU Reset and Shutdown Operation       30         4.2       TDMU and DMATCU Software Reset and Shutdown Operation       31         4.3       Powerdown       31         5       Emulation and Loopback Modes       32         5.1       Emulation - Free Run       32         5.2       Emulation - Halt       32         5.3       Loopback Modes       33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      | 3.7     | Data and Frames                                       | 28  |

| 4.1       SIU Reset and Shutdown Operation       30         4.2       TDMU and DMATCU Software Reset and Shutdown Operation       31         4.3       Powerdown       31         5       Emulation and Loopback Modes       32         5.1       Emulation - Free Run       32         5.2       Emulation - Halt       32         5.3       Loopback Modes       33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      | 3.8     | Data Synchronization                                  | 29  |

| 4.2       TDMU and DMATCU Software Reset and Shutdown Operation.       31         4.3       Powerdown       31         5       Emulation and Loopback Modes       32         5.1       Emulation - Free Run       32         5.2       Emulation - Halt       32         5.3       Loopback Modes       33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4    | Reset   | and Powerdown Modes                                   | 30  |

| 4.3       Powerdown       31         5       Emulation and Loopback Modes       32         5.1       Emulation - Free Run       32         5.2       Emulation - Halt       32         5.3       Loopback Modes       33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      | 4.1     | SIU Reset and Shutdown Operation                      | 30  |

| 5         Emulation and Loopback Modes         32           5.1         Emulation - Free Run         32           5.2         Emulation - Halt         32           5.3         Loopback Modes         33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      | 4.2     | TDMU and DMATCU Software Reset and Shutdown Operation | 31  |

| 5.1       Emulation - Free Run       32         5.2       Emulation - Halt       32         5.3       Loopback Modes       33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      | 4.3     | Powerdown                                             | 31  |

| 5.2Emulation - Halt325.3Loopback Modes33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5    | Emulat  | tion and Loopback Modes                               | 32  |

| 5.3 Loopback Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      | 5.1     | Emulation - Free Run                                  | 32  |

| ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      | 5.2     | Emulation - Halt                                      | 32  |

| 6 TSIP Initialization Procedure 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      | 5.3     | Loopback Modes                                        | 33  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6    | TSIP Ir | nitialization Procedure                               | 35  |

| 7 Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 7    | Regist  | ers                                                   | 37  |

| 7.1 TSIP Memory Map 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      | -       |                                                       |     |

| 7.2 Register Description 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      | 7.2     | Register Description                                  | 39  |

# List of Figures

| 1  | TSIP Block Diagram                                                 | 10        |

|----|--------------------------------------------------------------------|-----------|

| 2  | First Active Frame Sync                                            | 12        |

| 3  | Channel Bitmap                                                     | 13        |

| 4  | 8 Mbps Channel Definition (2 Links with 2 Active Links)            | 14        |

| 5  | 16-Mbps Channel Bitmap Definition (Two Links With One Active Link) | 15        |

| 6  | Channel Configuration                                              | 16        |

| 7  | Example Timeslot List by the TSIP Serial Link for 1 Channel        | 18        |

| 8  | Channel Buffer (BEND=1)                                            | 18        |

| 9  | Channel Buffer (BEND=0)                                            | 19        |

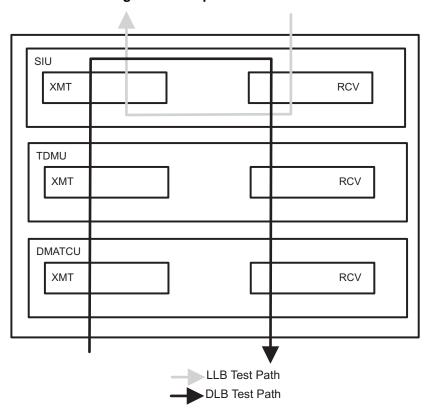

| 10 | Loopback Test Modes                                                | 33        |

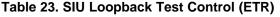

| 11 | TSIP Connected to TEMUX                                            | 35        |

| 12 | PID Register (0x0000000)                                           | 40        |

| 13 | Emulation and Test Register (0x00000004)                           | 40        |

| 14 | Reset Register (0x0000008)                                         | 42        |

| 15 | SIU Global Control Register (0x0000080)                            | 43        |

| 16 | Transmit Clock Source Register (0x000000A0)                        | 43        |

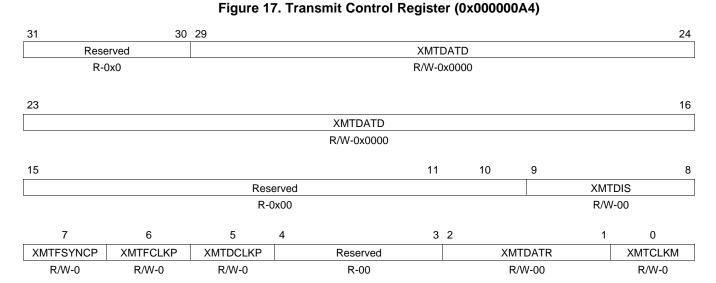

| 17 | Transmit Control Register (0x000000A4)                             | 45        |

| 18 | Transmit Size Register (0x000000A8)                                | 47        |

| 19 | Receive Clock Source Register (0x000000C0)                         | 47        |

| 20 | Receive Control Register (0x000000C4)                              | 48        |

| 21 | Receive Size Register (0x000000C8)                                 | 49        |

| 22 | TDMU Global Control Register (0x000000C0)                          | 49        |

| 23 | Transmit Free Running Frame Counter (0x00000104)                   | 50        |

| 24 | Receive Free Running Frame Counter (0x00000108)                    | 50        |

| 25 | TDMU Global Configuration Register (0x0000010C)                    | 50        |

| 26 | Transmit Channel Bitmap Active Status Register (0x00000110)        | 51        |

| 27 | Receive Channel Bitmap Active Status Register (0x00000114)         | 51        |

| 28 | DMATCU Global Control Register (0x00000180)                        | 53        |

| 29 | Transmit Timeslot Delay Register (0x00000184)                      | 54        |

| 30 | Receive Timeslot Delay Register (0x00000188)                       | 55        |

| 31 | Transmit Channel Configuration Active Status Register (0x00000190) | 56        |

| 32 | Receive Channel Configuration Active Status Register (0x00000194)  | <b>56</b> |

| 33 | Channel <i>n</i> Error Control Register                            | 58        |

| 34 | Channel <i>n</i> Error Count Register                              | 59        |

| 35 | Channel <i>n</i> Error Queue Register                              | 59        |

| 36 | CAT-0 Error Code Format Register                                   | <b>60</b> |

| 37 | CAT-1 Error Code Format Register                                   | 60        |

| 38 | CAT-2 Error Code Format Register                                   | 60        |

| 39 | CAT-3 Error Code Format Register                                   | 61        |

| 40 | Channel <i>n</i> Enable Register                                   | 61        |

| 41 | Channel n Memory Address Register                                  |           |

| 42 | Channel <i>n</i> Frame Allocation Register                         |           |

| 43 | Channel <i>n</i> Frame Size Register                               |           |

| 44 | Channel <i>n</i> Frame Count Register                              | 64        |

# List of Tables

| 1  | TSIP Memory Map                                         |    |

|----|---------------------------------------------------------|----|

| 2  | Interface Pins                                          | 12 |

| 3  | Channel Configuration Active Status                     | 17 |

| 4  | Channel Enable Register                                 | 17 |

| 5  | Transmit Disabled State                                 | 19 |

| 6  | Enable Output Delay Selection (XCR)                     | 20 |

| 7  | Frame Interrupt Control (RTDR and XTDR)                 | 20 |

| 8  | Timeslot Delay Counter (RTDR and XTDR)                  | 20 |

| 9  | Superframe Interrupt Control (RTDR and XTDR)            | 21 |

| 10 | Error Codes                                             | 21 |

| 11 | Endian Mode Selection                                   | 23 |

| 12 | DMATCU Transfer Priority (DMATCU_CGR)                   | 24 |

| 13 | Data Rate Options                                       | 25 |

| 14 | Clock Redundancy Selection (SIU_GCR)                    | 25 |

| 15 | Single Rate and Double Rate Clock Options               | 26 |

| 16 | Clock and Frame Sync Source Selection (RCLKR and XCLKR) | 26 |

| 17 | Frame Sync Polarity (RCR and XCR)                       | 27 |

| 18 | Data Delay (RCR and XCR)                                | 27 |

| 19 | Timeslot Counter (RSR and XSR)                          | 28 |

| 20 | Frame Sync Counter (RSR and XSR)                        | 28 |

| 21 | SIU Reset                                               | 30 |

| 22 | Emulation Control (ETR)                                 | 32 |

| 23 | SIU Loopback Test Control (ETR)                         | 33 |

| 24 | TSIP Module Registers                                   | 37 |

| 25 | Serial Interface Registers                              | 37 |

| 26 | TDMU Global Registers                                   | 37 |

| 27 | DMATCU Global Registers                                 | 38 |

| 28 | TDMU Channel Error Registers                            | 38 |

| 29 | TX/RX Channel 0 Error Registers                         | 38 |

| 30 | TDMU Channel Registers                                  | 38 |

| 31 | TDMU Transmit Channel 0 Registers                       | 38 |

| 32 | TDMU Receive Channel 0 Registers                        | 38 |

| 33 | DMATCU Channel Registers                                | 38 |

| 34 | DMATCU Transmit Channel 0 Registers                     | 39 |

| 35 | DMATCU Receive Channel 0 Registers                      | 39 |

| 36 | TDMU Channel Bitmap Registers                           | 39 |

| 37 | PID Register Field Descriptions                         |    |

| 38 | Emulation and Test Register Field Descriptions          | 40 |

| 39 | Reset Register Field Descriptions                       | 42 |

| 40 | SIU Global Control Register Field Descriptions          |    |

| 41 | Transmit Clock Source Register Field Descriptions       | 43 |

| 42 | Transmit Control Register Field Descriptions            |    |

| 43 | Transmit Size Register Field Descriptions               |    |

| 44 | Transmit Clock Source Register Field Descriptions       | 47 |

| 45 | Receive Control Register Field Descriptions             |    |

| 46 | Receive Size Register Field Descriptions                |    |

| 47 | TDMU Global Control Register Field Descriptions         |    |

| 48 | Transmit Free Running Frame Counter Field Descriptions  |    |

| 49 | Receive Free Running Frame Counter Field Descriptions   |    |

|    |                                                         |    |

| 50       | TDMU Global Configuration Register Field Descriptions                    | 50 |

|----------|--------------------------------------------------------------------------|----|

| 51       | Transmit Channel Bitmap Active Status Register Field Descriptions        |    |

| 52       | Receive Channel Bitmap Active Status Register Field Descriptions         |    |

| 53       | DMATCU Global Control Register Field Descriptions                        |    |

| 53<br>54 | Transmit Timeslot Register Field Descriptions                            |    |

| 55       | Receive Timeslot Delay Register Field Descriptions                       |    |

|          |                                                                          |    |

| 56       | Transmit Channel Configuration Active Status Register Field Descriptions | 56 |

| 57       | Receive Channel Configuration Active Status Register Field Descriptions  | 56 |

| 58       | Channel <i>n</i> Error Control Register Field Descriptions               | 58 |

| 59       | Channel <i>n</i> Error Count Register Field Descriptions                 | 59 |

| 60       | Channel <i>n</i> Error Queue Register Field Descriptions                 | 59 |

| 61       | CAT-0 Error Code Format Register Field Descriptions                      | 60 |

| 62       | CAT-1 Error Code Format Register Field Descriptions                      | 60 |

| 63       | CAT-2 Error Code Format Register Field Descriptions                      | 60 |

| 64       | CAT-3 Error Code Format Register Field Descriptions                      | 61 |

| 65       | Channel <i>n</i> Enable Register Field Descriptions                      | 61 |

| 66       | Channel n Memory Address Register Field Descriptions                     | 62 |

| 67       | Channel <i>n</i> Frame Allocation Register Field Descriptions            | 62 |

| 68       | Channel <i>n</i> Frame Size Register Field Descriptions                  | 62 |

| 69       | Channel <i>n</i> Frame Count Register Field Descriptions                 | 64 |

|          |                                                                          |    |

Preliminary

Preface SPRUF96A–October 2007–Revised September 2008

# **Read This First**

# About This Manual

This document describes the operation of the Telecom Serial Interface Port (TSIP) in the TMS320C6452.

#### **Notational Conventions**

This document uses the following conventions.

- Hexadecimal numbers are shown with the suffix h. For example, the following number is 40 hexadecimal (decimal 64): 40h.

- Registers in this document are shown in figures and described in tables.

- Each register figure shows a rectangle divided into fields that represent the fields of the register.

Each field is labeled with its bit name, its beginning and ending bit numbers above, and its read/write properties below. A legend explains the notation used for the properties.

- Reserved bits in a register figure designate a bit that is used for future device expansion.

- **Note:** Acronyms 3PSW, CPSW, CPSW\_3G, and 3pGSw are interchangeable and all refer to the 3 port gigabit switch.

### **Related Documents From Texas Instruments**

The following documents describe the TMS320C6452 Digital Signal Processor (DSP). Copies of these documents are available on the Internet at <u>www.ti.com</u>. *Tip:* Enter the literature number in the search box provided at <u>www.ti.com</u>.

#### Data Manual—

#### CPU—

SPRU732 — TMS320C64x/C64x+ DSP CPU and Instruction Set Reference Guide describes the CPU architecture, pipeline, instruction set, and interrupts for the TMS320C64x and TMS320C64x+ digital signal processors (DSPs) of the TMS320C6000 DSP family. The C64x/C64x+ DSP generation comprises fixed-point devices in the C6000 DSP platform. The C64x+ DSP is an enhancement of the C64x DSP with added functionality and an expanded instruction set.

#### Reference Guides—

- <u>SPRUF85</u> C6452 DSP DDR2 Memory Controller User's Guide describes the DDR2 memory controller in the TMS320C6452 Digital Signal Processor (DSP). The DDR2/mDDR memory controller is used to interface with JESD79D-2A standard compliant DDR2 SDRAM devices and standard Mobile DDR SDRAM devices.

- SPRUF86 C6452 Peripheral Component Interconnect (PCI) User's Guide describes the peripheral component interconnect (PCI) port in the TMS320C6452 Digital Signal Processor (DSP). The PCI port supports connection of the C642x DSP to a PCI host via the integrated PCI master/slave bus interface. The PCI port interfaces to the DSP via the enhanced DMA (EDMA) controller. This architecture allows for both PCI master and slave transactions, while keeping the EDMA channel resources available for other applications.

7

<sup>&</sup>lt;u>SPRS371</u> — *TMS320C6452 Digital Signal Processor Data Manual* describes the signals, specifications and electrical characteristics of the device.

- SPRUF87 C6452 DSP Host Port Interface (UHPI) User's Guide describes the host port interface (HPI) in the TMS320C6452 Digital Signal Processor (DSP). The HPI is a parallel port through which a host processor can directly access the CPU memory space. The host device functions as a master to the interface, which increases ease of access. The host and CPU can exchange information via internal or external memory. The host also has direct access to memory-mapped peripherals. Connectivity to the CPU memory space is provided through the enhanced direct memory access (EDMA) controller.

- SPRUF89 C6452 DSP VLYNQ Port User's Guide describes the VLYNQ port in the TMS320C6452 Digital Signal Processor (DSP). The VLYNQ port is a high-speed point-to-point serial interface for connecting to host processors and other VLYNQ compatible devices. It is a full-duplex serial bus where transmit and receive operations occur separately and simultaneously without interference.

- SPRUF90 C6452 DSP 64-Bit Timer User's Guide describes the operation of the 64-bit timer in the C6452 Digital Signal Processor (DSP). The timer can be configured as a general-purpose 64-bit timer, dual general-purpose 32-bit timers, or a watchdog timer.

- SPRUF91 C6452 DSP Multichannel Audio Serial Port (McASP) User's Guide describes the multichannel audio serial port (McASP) in the C6452 Digital Signal Processor (DSP). The McASP functions as a general-purpose audio serial port optimized for the needs of multichannel audio applications. The McASP is useful for time-division multiplexed (TDM) stream, Inter-Integrated Sound (I2S) protocols, and intercomponent digital audio interface transmission (DIT).

- <u>SPRUF92</u> C6452 DSP Serial Port Interface (SPI) User's Guide discusses the Serial Port Interface (SPI) in the C6452 Digital Signal Processor (DSP). This reference guide provides the specifications for a 16-bit configurable, synchronous serial peripheral interface. The SPI is a programmable-length shift register, used for high speed communication between external peripherals or other DSPs.

- SPRUF93 C6452 DSP Universal Asynchronous Receiver/Transmitter (UART) User's Guide describes the universal asynchronous receiver/transmitter (UART) peripheral in the C6452 Digital Signal Processor (DSP). The UART peripheral performs serial-to-parallel conversion on data received from a peripheral device, and parallel-to-serial conversion on data received from the CPU.

- SPRUF94 C6452 DSP Inter-Integrated Circuit (I2C) Module User's Guide describes the inter-integrated circuit (I2C) peripheral in the C6452 Digital Signal Processor (DSP). The I2C peripheral provides an interface between the DSP and other devices compliant with the I2C-bus specification and connected by way of an I2C-bus. External components attached to this 2-wire serial bus can transmit and receive up to 8-bit wide data to and from the DSP through the I2C peripheral. This document assumes the reader is familiar with the I2C-bus specification.

- SPRUF95 C6452 DSP General-Purpose Input/Output (GPIO) User's Guide describes the general-purpose input/output (GPIO) peripheral in the C6452 Digital Signal Processor (DSP). The GPIO peripheral provides dedicated general-purpose pins that can be configured as either inputs or outputs. When configured as an input, you can detect the state of the input by reading the state of an internal register. When configured as an output, you can write to an internal register to control the state driven on the output pin.

- SPRUF96 C6452 DSP Telecom Serial Interface Port (TSIP) User's Guide is a multi-link serial interface consisting of a maximum of two transmit data signals (or links), two receive data signals (or links), two frame sync input signals, and two serial clock inputs. Internally the TSIP offers single channel of timeslot data management and single DMA capability that allow individual timeslots to be selectively processed.

- <u>SPRUF97</u> TMS320C6452 DSP 3 Port Switch (3PSW) Ethernet Subsystem User's Guide describes the operation of the 3 port switch (3PSW) ethernet subsystem in the TMS320C6452 Digital Signal Processor (DSP). The 3 port switch gigabit ethernet subsystem provides ethernet packet communication and can be configured as an ethernet switch. It provides the serial gigabit media independent interface (SGMII), the management data input output (MDIO) for physical layer device (PHY) management.

Preliminary

User's Guide SPRUF96A–October 2007–Revised September 2008

# TMS320C6452 TSIP

# 1 Introduction/Feature Overview

This document describes the operation of the Telecom Serial Interface Port (TSIP).

### 1.1 Overview/Purpose of the Peripheral

The TSIP is a multi-link serial interface consisting of a maximum of two transmit data signals (or links), two receive data signals (or links), two frame sync input signals, and two serial clock inputs. Internally, the TSIP offers single channel of timeslot data management and single direct memory access (DMA) capability that allow individual timeslots to be processed selectively.

The module can be configured to use the frame sync signals and the serial clocks as redundant sources for all transmit and receive data signals, or one frame sync and serial clock for transmit and the second frame sync and clock for receive. The standard serial data rate for each TSIP transmit and receive data signal is 8.192 Mbps. The standard frame sync is a one or more bit-wide pulse that occurs once every 125  $\mu$ s or a minimum of one serial clock period every 1024 serial clocks.

At the standard rate and default configuration there are two transmit and two receive links that are active. Each serial interface link supports up to 128 8-bit timeslots. This corresponds to an H-MVIP or H.110 serial data rate interface. The serial interface clock frequency can be either 16.384 MHz (default) or 8.192 MHz. The data rate for the serial interface links can also be set to 16.384 Mbps. The maximum number of active serial links is reduced to two in this configuration. The serial interface clock frequency can be either 32.768 MHz or 16.384 MHz for 16.384 Mbps serial links. Maximum occupation of the serial interface links for the entire TSIP is 1024 transmit and receive timeslots in all configurations.

### 1.2 Features

The TSIP is a serial interface peripheral that connects directly to TEMUX devices with timeslot data management and an integrated DMA capability. The peripheral provides a glueless interface to common telecom serial data streams and efficient internal routing of the data to designated memories in a multi-CPU device. The TSIP provides these functions:

- Direct interface to H-MVIP devices such as TEMUX, ST BUS devices, TSI devices and H.110 compatible devices

- Dual Transmit and Receive Telecom Serial Interface Ports (TSIP)

- Each TSIP module supports a transmit/receive data rate of 16.384Mbps

- One transmit/receive data lane per module at 16.384Mbps each

- Two transmit/receive data lane per module at 8.192Mbps each

- Each TSIP supports 256 TDM timeslots for voice data or signaling data

- Flexible Clock and Frame Sync Inputs

- Configurable for independent TX and RX clock and frame Sync

- Configurable for common TX and RX clock and Frame Sync

- Second clock and Frame Sync can be used as a redundant source

- Independent clock polarity selection for data and frame Sync

- Selection of 2X or 1X data clock frequency

- Timeslot Data Management and Multi-Channel DMA Capability

Preliminary

www.ti.com

- Independent timeslot enable/disable per DMA channel

- Selectively unpacks and packs timelot data for transmit and receive based on a channel timeslot definition

- A-law and  $\mu$ -law support on a per timeslot basis

- Frame and SuperFrame Interrupts

- 12 pin External Interface(6 pins/TSIP x 2 ports)

# 1.3 Functional Block Diagram

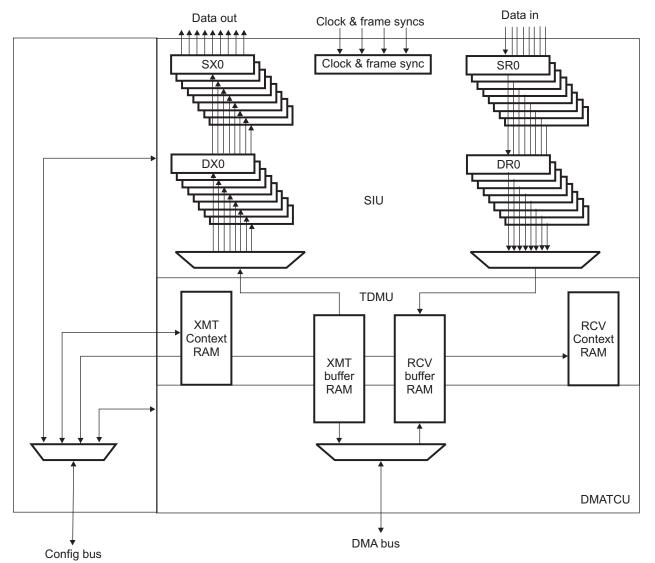

The TSIP consists of three functional sub-modules as shown in Figure 1:

- Serial Interface Unit (SIU) The SIU provides parallel to serial and serial to parallel conversion for transmit and receive, respectively.

- *Timeslot Data Management Unit (TDMU)* The TDMU selectively packs and unpacks timeslot data for receive and transmit based on a channel timeslot definition. There is one transmit and one receive TDMU channel. Each channel is capable of selecting and transferring all of the possible 1024 timeslots in the respective direction.

- *DMA Transfer Control Unit (DMATCU)* The DMATCU initiates the data transfers between the channel buffers used by the TDMU and the memory buffers used by the CPU.

### Figure 1. TSIP Block Diagram

# 1.4 Terminology Used

The following are brief explanations of some terms used in this document:

| Term   | Meaning                       |

|--------|-------------------------------|

| DMA    | Direct Memory Access          |

| DMATCU | DMA Transfer Control Unit     |

| SIU    | Serial Interface Unit         |

| TDM    | Timeslot Data Management      |

| TDMU   | Timeslot Data Management Unit |

| TEMUX  | T1-E1 Mux Device              |

| TSIP   | Telecom Serial Interface Port |

# 1.5 Memory Map

Table 1 lists the summary memory map for the registers for the TSIP.

| <br>Offset Address       | Register Description             |

|--------------------------|----------------------------------|

| <br>0x0000000 0x0000007C | TSIP Module Registers            |

| 0x0000080 0x000000FC     | Serial Interface Registers       |

| 0x00000100 0x0000017C    | TDMU Registers                   |

| 0x00000180 0x000001FC    | DMATCU Registers                 |

| 0x00000200 0x000003FC    | TDMU channel Error Log Registers |

| 0x00000400 0x000007FC    | Reserved                         |

| 0x00000800 0x00000FFC    | TDMU channel Registers           |

| 0x00001000 0x00001FFC    | DMATCU channel Registers         |

| 0x00002000 0x00007FFC    | Reserved                         |

| 0x00008000 0x0000FFFC    | TDMU channel Bitmaps             |

| 0x00010000 0x0001FFFC    | TDMU channel Buffers             |

| 0x00020000 0x0003FFFC    | Reserved                         |

#### Table 1. TSIP Memory Map

#### Features/Common Architecture

#### 2 Features/Common Architecture

This section describes the major features of the TSIP and how it works.

#### 2.1 Interface

The external pin interface of TSIP consists of eight pins: two clock input pins, two frame sync input pins, two data input pins, and two data output pins. The pins are listed in Table 2. The module has eight additional control signals to control the output state of the eight data output pins.

| Pin     | Direction | Description                                                                                                                                             |

|---------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK_A   | Input     | TSIP serial data clock A                                                                                                                                |

| CLK_B   | Input     | TSIP serial data clock B                                                                                                                                |

| FS_A    | Input     | TSIP frame sync A                                                                                                                                       |

| FS_B    | Input     | TSIP frame sync B                                                                                                                                       |

| TR[1:0] | Input     | TSIP serial data receive. Up to two serial data streams may be received simultaneously. The serial data clock and frame sync is common for all two.     |

| TX[1:0] | Output    | TSIP serial data transmit. Up to two serial data streams may be transmitted simultaneously. The serial data clock and frame sync is common for all two. |

Table 2. Interface Pins

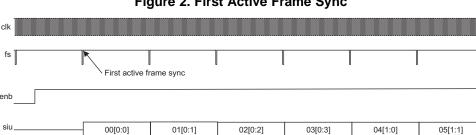

On the first frame sync, after the TSIP is enabled, the TSIP starts receiving/transmitting on the TR/TX data lane as denoted by the SIU data lanes in Figure 2.

#### Figure 2. First Active Frame Sync

#### 2.2 Receive Operation

Data that is received by the TSIP is assembled in a serial-to-parallel register (DRn) with the most significant bit first, one 8-bit register per serial interface input. The data for timeslot 0 is recognized on the first eight serial data clocks following the recognition of the frame sync signal that signals the start of the frame and the programmed delay. The data for timeslot 1 is recognized on the next eight serial data clocks immediately following timeslot 0. Data for successive timeslots is continuously received and recognized on subsequent serial data clocks. The number of data samples processed and buffered depends on the timeslot enable/disable definition in the channel bitmap for each of the receive channels.

## 2.3 Bitmap Context

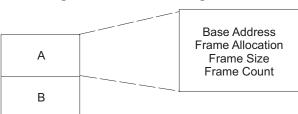

The receive operation of the TSIP reads and processes the data in the DRn registers and stores the results in the channel buffer based on the channel bitmap context. The registers are read sequentially with the sequence order defined in the SIU by the selected data rate option. Data received on each of the receive serial links can be stored in none, some, or all of the channel buffers. On reaching a watermark in the channel buffer, its DMA engine transfers the data from the channel buffers to the memory buffers outside the system. Each transmit/receive channel has dual buffers, PING and PONG, that are shared with the DMATCU. Each of the buffers is managed as a FIFO memory and consists of 64 32-bit words of memory. During the processing of a given frame the TSIP processes the data from one of the FIFO memories based on whether the PING or PONG buffer is active. The channel buffers are not software accessible once the TDMU has been enabled.

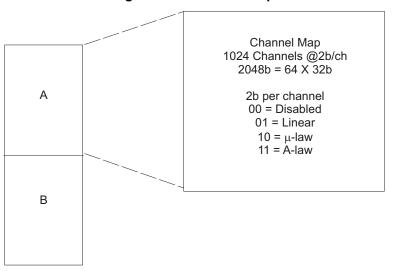

The channel bitmap consists of 64 32-bit words of memory for a total of 2048 bits. Each pair of bits controls the enable/disable state of a physical timeslot. When a given di-bit value is 00b the corresponding physical timeslot is disabled for that channel. Any other di-bit value represents an enabled channel: 01b indicates that the data is 8-bit linear, 10b indicates that the data should be  $\mu$ -law expanded, and 11b indicates that the data should be A-law expanded.

Figure 3. Channel Bitmap

For a given physical timeslot the corresponding di-bits are read from the channel bitmap for each of the channels. If the physical timeslot is enabled for the channel the data, either 8 or 16 bits, is read from the FIFO memory. If 16-bit data is read from the FIFO memory, the data is compressed to 8 bits using either  $\mu$ -law or A-law compression. depending on the enable selection. At the transmit side, data samples from multiple timeslots can be loaded from the channel buffer (FIFO memory) into a channel register and unpacked for enabled timeslots. The resulting 8-bit sample data for each of the enabled channels is then OR'd together to create a single 8-bit sample value that is written to the appropriate transmit data register (DXn). Any 8-bit data is read/written from/to the next byte location in the FIFO memory. Any 16-bit data is read/written from/to the next 16-bit word location in the FIFO memory.

#### 2.3.1 A-law and µ-law Companding

When receive data is  $\mu$ -law or A-law expanded it is stored left-justified in a 16-bit word. The two or three least significant bits are always zero for  $\mu$ -law and A-law, respectively. Likewise, transmit data that is to be  $\mu$ -law or A-law compressed should be left justified. The two or three least significant bits are truncated for the compression. Expansion and compression is completed based on the G.711 standard including the channel coding (bit inversions for ones density).

Since the G.711 standard does not distinguish the  $\mu$ -law expansion of 0xFF and 0x7F, a special case is created in the TSIP. Both normally result in a 16-bit linear value of 0x0000. For data that undergoes signal processing, this is not a problem. However, for data that is compressed and looped back, the compression results in 0xFF and the original 0x7F code is lost wherever it existed. To prevent this from occurring, the expansion of 0x7F is redefined to be 0xFFFF and the algorithmic compression of the 16-bit value 0xFFFF, which normally results in 0x7E, is treated as a special case to allow 0x7F to be produced. This does not result in any loss in the coding based on the G.711 standard since the G.711 standard only defines the data conversion for 14-bit linear data values and the two least significant bits of the left-justified value in a 16-bit linear format otherwise would be truncated.

#### Features/Common Architecture

# 2.4 Serial Link Processing and Buffering

When the selected data rate option is one of the 8 Mbps options, both the two serial interface inputs are active. Links refer to the number of transmit and receive I/Os supported by the TSIP module. Active links refer to the number of transmit and receive I/Os that are usable at a given data rate. Figure 4 illustrates the channel bitmap definition for both 8 Mbps data rate options. The nomenclature defines the logical timeslot, LTSxxx, and physical timeslot, Ln-xxx, where n represents the link number and xxx represents the physical timeslot. When the selected data rate option is the 16 Mbps option one serial interface inputs is active, but data is read from all of the DRn/Dxn registers.

|        | L0-000 | Reserved |        |        |        |        |        |