# Five-Ethernet-Port Enablement on AM64x and AM243x

Ashwani Goel, Teja Rowthu

Sitara MPU

#### **ABSTRACT**

This document provides guidelines for the design, development, implementation, and performance metrics of five Ethernet® ports support using R5F and A53 cores available on Texas Instruments' Arm® based system-on-chip (SoC) AM64x and AM243x devices. Currently, the implementation is only available with RTOS based multicore implementation as both Common Platform Ethernet Switch (CPSW3G) and Industrial Communication Subsystem (PRU-ICSSG) Ethernet ports work simultaneously.

Currently, this implementation is not supported in public MCU+ SDK release. Please follow FAQ for more updated details.

## **Table of Contents**

| 1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 3                                                                    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| 1.1 AM64x and AM243x EVMs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                      |

| 1.2 SoC Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                      |

| 1.3 Peripherals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5                                                                    |

| 1.4 Ethernet Software Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 6                                                                    |

| 1.5 Prerequisite                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 7                                                                    |

| 2 Multicore 5-Ethernet Ports Realization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 11                                                                   |

| 3 Supported Configurations on PRU-ICSSG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 12                                                                   |

| 4 Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                      |

| 4.1 System Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                      |

| 5 Debug Steps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 15                                                                   |

| 6 Reference Logs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 19                                                                   |

| 7 Testing for the ICSSG0 and ICSSG1 Functionality                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 22                                                                   |

| 8 ICSSG and CPSW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 22                                                                   |

| 9 Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 23                                                                   |

| 10 References                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 23                                                                   |

| List of Figures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                      |

| Figure 1-1. AM64x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                      |

| Figure 1-2. AM243x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5                                                                    |

| Figure 1-2. AM243xFigure 1-3. Ethernet Networking Layers                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5                                                                    |

| Figure 1-2. AM243xFigure 1-3. Ethernet Networking LayersFigure 1-4. EVM Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                      |

| Figure 1-2. AM243xFigure 1-3. Ethernet Networking LayersFigure 1-4. EVM Block DiagramFigure 1-5. HSE Connector: ICSSG0 pin out                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                      |

| Figure 1-2. AM243x Figure 1-3. Ethernet Networking Layers Figure 1-4. EVM Block Diagram Figure 1-5. HSE Connector: ICSSG0 pin out Figure 1-6. SysConfig: Packet DMA                                                                                                                                                                                                                                                                                                                                                                   |                                                                      |

| Figure 1-2. AM243x Figure 1-3. Ethernet Networking Layers Figure 1-4. EVM Block Diagram Figure 1-5. HSE Connector: ICSSG0 pin out Figure 1-6. SysConfig: Packet DMA Figure 1-7. SysConfig: Packet DMA Ring Accelerator                                                                                                                                                                                                                                                                                                                |                                                                      |

| Figure 1-2. AM243x Figure 1-3. Ethernet Networking Layers Figure 1-4. EVM Block Diagram Figure 1-5. HSE Connector: ICSSG0 pin out Figure 1-6. SysConfig: Packet DMA Figure 1-7. SysConfig: Packet DMA Ring Accelerator Figure 4-1. SysConfig: IPC settings                                                                                                                                                                                                                                                                            | 5<br>                                                                |

| Figure 1-2. AM243x  Figure 1-3. Ethernet Networking Layers  Figure 1-4. EVM Block Diagram  Figure 1-5. HSE Connector: ICSSG0 pin out  Figure 1-6. SysConfig: Packet DMA  Figure 1-7. SysConfig: Packet DMA Ring Accelerator.  Figure 4-1. SysConfig: IPC settings  Figure 4-2. ICSSG and CPSW Allocation                                                                                                                                                                                                                              | 5<br>6<br>7<br>8<br>9<br>10<br>12                                    |

| Figure 1-2. AM243x  Figure 1-3. Ethernet Networking Layers  Figure 1-4. EVM Block Diagram  Figure 1-5. HSE Connector: ICSSG0 pin out  Figure 1-6. SysConfig: Packet DMA  Figure 1-7. SysConfig: Packet DMA Ring Accelerator.  Figure 4-1. SysConfig: IPC settings  Figure 4-2. ICSSG and CPSW Allocation  Figure 4-3. Simplified Flow Chart of the Example                                                                                                                                                                            | 55<br>66<br>77<br>88<br>99<br>10<br>12<br>13                         |

| Figure 1-2. AM243x  Figure 1-3. Ethernet Networking Layers  Figure 1-4. EVM Block Diagram  Figure 1-5. HSE Connector: ICSSG0 pin out  Figure 1-6. SysConfig: Packet DMA  Figure 1-7. SysConfig: Packet DMA Ring Accelerator  Figure 4-1. SysConfig: IPC settings  Figure 4-2. ICSSG and CPSW Allocation  Figure 4-3. Simplified Flow Chart of the Example  Figure 5-1. SysConfig: ICSSG0 and ICSSG1: MII mode: Allocation to R5FSS0-0                                                                                                 | 5<br>6<br>7<br>7<br>8<br>9<br>10<br>12<br>13<br>13                   |

| Figure 1-2. AM243x  Figure 1-3. Ethernet Networking Layers  Figure 1-4. EVM Block Diagram  Figure 1-5. HSE Connector: ICSSG0 pin out  Figure 1-6. SysConfig: Packet DMA  Figure 1-7. SysConfig: Packet DMA Ring Accelerator  Figure 4-1. SysConfig: IPC settings  Figure 4-2. ICSSG and CPSW Allocation  Figure 4-3. Simplified Flow Chart of the Example  Figure 5-1. SysConfig: ICSSG0 and ICSSG1: MII mode: Allocation to R5FSS0-0  Figure 5-2. SysConfig: INTC CONFIG: PRU Pin-41                                                 | 56 66 77 78 88 99 10 12 13 13 14 15 15 16                            |

| Figure 1-2. AM243x  Figure 1-3. Ethernet Networking Layers  Figure 1-4. EVM Block Diagram  Figure 1-5. HSE Connector: ICSSG0 pin out  Figure 1-6. SysConfig: Packet DMA  Figure 1-7. SysConfig: Packet DMA Ring Accelerator  Figure 4-1. SysConfig: IPC settings  Figure 4-2. ICSSG and CPSW Allocation  Figure 4-3. Simplified Flow Chart of the Example  Figure 5-1. SysConfig: ICSSG0 and ICSSG1: MII mode: Allocation to R5FSS0-0  Figure 5-2. SysConfig: INTC CONFIG: PRU Pin-41  Figure 5-3. SysConfig: INTC CONFIG: PRU Pin-53 | 56<br>66<br>77<br>88<br>99<br>10<br>12<br>13<br>14<br>15             |

| Figure 1-2. AM243x  Figure 1-3. Ethernet Networking Layers  Figure 1-4. EVM Block Diagram  Figure 1-5. HSE Connector: ICSSG0 pin out  Figure 1-6. SysConfig: Packet DMA  Figure 1-7. SysConfig: Packet DMA Ring Accelerator  Figure 4-1. SysConfig: IPC settings  Figure 4-2. ICSSG and CPSW Allocation  Figure 4-3. Simplified Flow Chart of the Example  Figure 5-1. SysConfig: ICSSG0 and ICSSG1: MII mode: Allocation to R5FSS0-0  Figure 5-2. SysConfig: INTC CONFIG: PRU Pin-41                                                 | 56<br>66<br>77<br>88<br>99<br>10<br>12<br>13<br>14<br>15<br>16<br>16 |

Trademarks www.ti.com

## **Trademarks**

Sitara<sup>™</sup> is a trademark of Texas Instruments. Yocto Project<sup>™</sup> is a trademark of The Linux Foundation.

Ethernet<sup>®</sup> is a registered trademark of Xerox Corporation. Arm<sup>®</sup> and Cortex<sup>®</sup> are registered trademarks of Arm Limited.

EtherCAT® is a registered trademark of Beckhoff Automation GmbH.

PROFINET® is a registered trademark of PROFIBUS Nutzerorganisation e.V. (PNO).

All trademarks are the property of their respective owners.

#### 1 Introduction

### 1.1 AM64x and AM243x EVMs

AM64x and AM243x are industrial grade devices from the Sitara<sup>™</sup> MCU family.

The AM64x device is built for industrial applications, such as motor drives and remote I/O modules, which require a combination of real-time communications and processing.

The AM64x family provides scalable performance with up to two instances of gigabit TSN-enabled PRU\_ICSSG in Sitara. For more information, see the *AM64x and AM243x Technical Reference Manual*.

#### 1.2 SoC Architecture

This section describes the SOC-level description of SITARA MPU devices AM64x and AM243x.

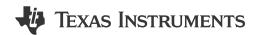

#### 1.2.1 AM64x

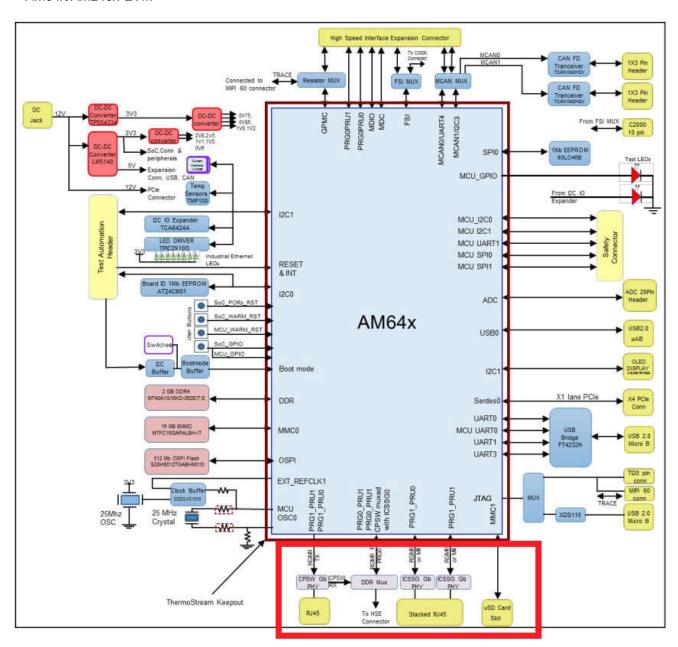

The AM64x devices are an extension of the Sitara MCU industrial-grade family of heterogeneous Arm processors. AM64x is built for industrial applications, such as motor drives and Programmable Logic Controllers (PLC), which require a unique combination of real-time processing and communications with applications processing. AM64x combines two instances of the gigabit TSN-enabled PRU-ICSSG of the Sitara device with up to two Arm® Cortex®-A53 cores, up to four Cortex-R5F MCUs, and a Cortex-M4F MCU. AM64x is built to provide real-time performance through the high-performance R5Fs, tightly-coupled memory banks, configurable SRAM partitioning, and dedicated low-latency paths to and from peripherals for rapid data movement in and out of the SoC. This deterministic architecture allows for AM64x to handle the tight control loops found in servo drives while the peripherals such as Fast Serial Interface (FSI), General Purpose Memory Controller (GPMC), Pulse-Width Modulation (PWM), sigma-delta decimation filters, and absolute encoder interfaces help enable a number of different architectures found in these systems.

The Cortex-A53s provide the powerful computing elements necessary for Linux applications. Linux, and Real-Time (RT) Linux, is provided through Tl's Processor SDK Linux which stays updated to the latest Long Term Support (LTS) Linux kernel, bootloader, and Yocto Project™ file system on an annual basis. AM64x enables isolation between Linux applications and real-time streams through configurable memory partitioning. The Cortex-A53s can be assigned to work strictly out of DDR for Linux, and the internal SRAM can be broken up into various sizes for the Cortex-R5Fs to use together or independently. The AM64x provides flexible industrial communications capability including full protocol stacks for EtherCAT® subdevices, PROFINET® devices, Ethernet, image prompt (IP) adapter, and IO-Link controllers. The PRU-ICSSG further provides capability for gigabit and TSN-based protocols. The PRU-ICSSG also enables additional interfaces in the SoC including sigma-delta decimation filters and absolute encoder interfaces. Functional safety features can be enabled through the integrated Cortex-M4F along with dedicated peripherals that can be isolated from the rest of the SoC. AM64x also supports secure boot.

Introduction www.ti.com

Figure 1-1. AM64x

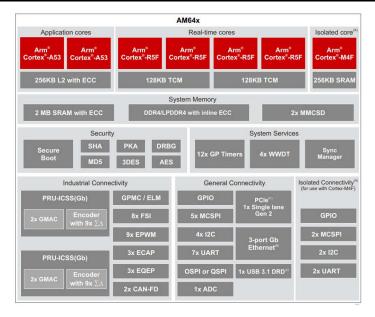

#### 1.2.2 AM243x

AM243x is an extension of the industrial-grade portfolio from the Sitara technology into high-performance microcontrollers. The AM243x device is built for industrial applications, such as motor drives and remote I/O modules which require a combination of real-time communications and processing. The AM243x family provides scalable performance with up to four Cortex-R5F MCUs, one Cortex-M4F, and two instances of the gigabit TSN-enabled PRU\_ICSSG in the Sitara microcontroller. The AM243x SoC architecture was designed to provide best-in-class real-time performance through the high-performance Arm Cortex-R5F cores, Tightly-Coupled Memory (TCM) banks, configurable SRAM partitioning, and dedicated low-latency paths to and from peripherals for rapid data movement in and out of the SoC.

This deterministic architecture allows for AM243x to process the tight control loops found in servo drives, while the peripherals such as FSI, GPMC, Enhanced Capture Modules (eCAP), PWMs, and encoder interfaces help enable a number of different architectures found in these systems. The SoC provides flexible industrial communications capability including full protocol stacks for EtherCAT targets, PROFINET devices, EtherNet or IP adapters, and IO-Link controllers. The PRU\_ICSSG further provides capability for gigabit and TSN-based protocols. The PRU\_ICSSG enables additional interfaces including a UART interface, sigma-delta decimation filters, and absolute encoder interfaces. Functional safety features can be enabled through the integrated Cortex-M4F along with dedicated peripherals that can be isolated from the rest of the SoC. AM243x also supports secure boot.

Figure 1-2. AM243x

## 1.3 Peripherals

A brief description about PRU-ICSSG and CPSW3G peripherals available on AM64x/AM243x is described in this section.

#### 1.3.1 CPSW3G

**CPSW (Common Platform Switch):** CPSW subsystem provides IEEE 802.3 standard Ethernet gigabit speed packet communication for the device and can also be configured as an Ethernet switch.

#### CAUTION

CPSW is shown as 3-port Gb Ethernet in Figure 1-1and Figure 1-2.

## **CAUTION**

CPSW3G on AM64x and AM243x supports RGMII and RMII interfaces.

## 1.3.2 PRU-ICSSG

Programmable Real-Time Unit and Industrial Communication Subsystem Gigait (PRU-ICSSG): PRU-ICSSG is firmware programmable and can take on various personalities like Industrial Communication Protocol Switch (for protocols like EtherCAT, Profinet, Ethernet/IP), Ethernet Switch, Ethernet MAC, Industrial Drives, and so forth.

## **CAUTION**

PRU-ICSSG on AM64x/AM243x supports RGMII and MII mode only.

#### **CAUTION**

PRU-ICSSG is shown as PRU-ICSSG in Figure 1-1 and Figure 1-2.

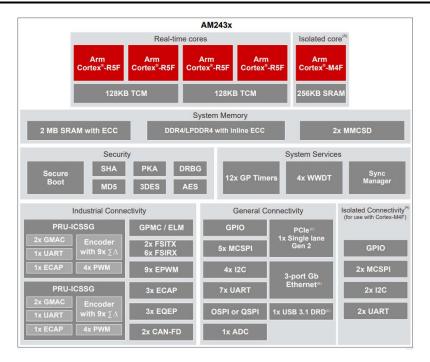

## 1.4 Ethernet Software Architecture

The software components overview highlighting the components used in the networking software development is shown in Figure 1-3.

Figure 1-3. Ethernet Networking Layers

## 1.5 Prerequisite

These are the prerequisites for enablement of five Ethernet ports using AM64x-EVM and a SEM board.

## 1.5.1 HW Prerequisite

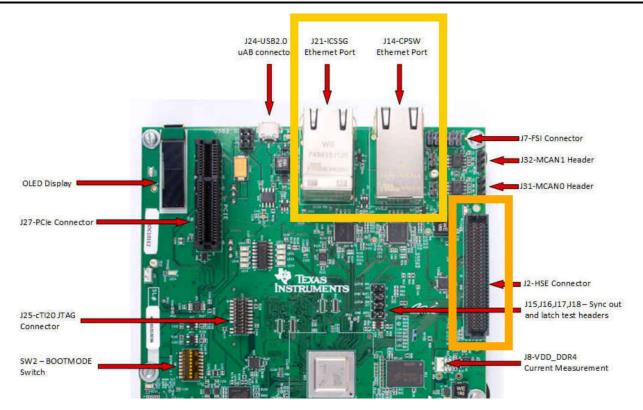

AM64x/AM243x-EVM

Figure 1-4. EVM Block Diagram

- · SEM Board connected over HSE connector

- DP83826e PHY

- Only 100M is supported for testing purpose.

Introduction Www.ti.com

Figure 1-5. HSE Connector: ICSSG0 pin out

## 1.5.2 SW Prerequisite

- Install MCU-PLUS-SDK for AM64x or AM243x and dependent tools. For more information, see Getting Started.

- SYSCONFIG

## **CAUTION**

Make sure to make SBL updates before running this example on the board. The default SBL does not allow CPSW to run on R5FSS\_0-1.

#### 1.5.2.1 Resource Allocation - AM64x

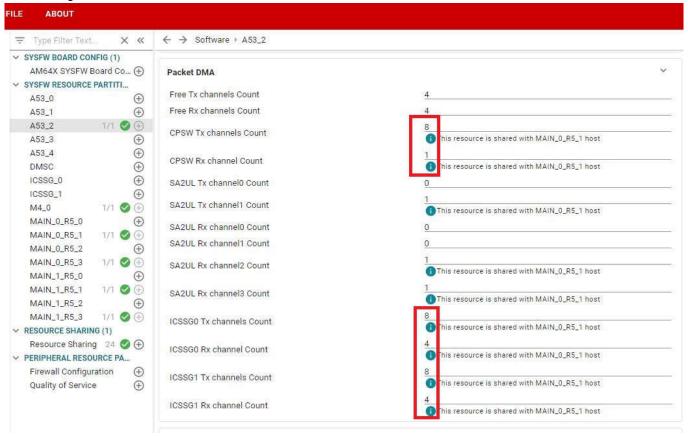

Resource manager must be asked first to allocate any peripheral to any core. Users can configure ICSSG0, ICSSG1 and CPSW Ethernet ports with different modes (MII, RMII, RGMII) using sysconfig tool and attach to the core as per need.

#### CAUTION

These are the examples given for AM64x which has A53 core:

AM243x does not have A53 core.

Use resource allocation as per use case.

Use the following steps to enable this feature:

- Navigate to the MCU-PLUS-SDK installation directory (In this document, this is referred to as MCU\_SDK\_HOME).

- For example: C:\ti\mcu\_plus\_sdk\_am64x\_09\_01\_00\_41

- 2. Open the command prompt and run the following command:

gmake -s -C tools/sysfw/boardcfg configure SOC=am64x

- 3. Change the Tx and Rx channel count for CPSW, ICSSG0, and ICSSG1 to 0 in the A53 core.

Figure 1-6. SysConfig: Packet DMA

Introduction Www.ti.com

- 4. After the channel counts are updated, the values are as follows:

- CPSW Tx channel count = 0

- CPSW Rx channel count = 0

- ICSSG0 Tx channel count = 0

- ICSSG0 Rx channel count = 0

- ICSSG1 Tx channel count = 0

- ICSSG1 Rx channel count = 0

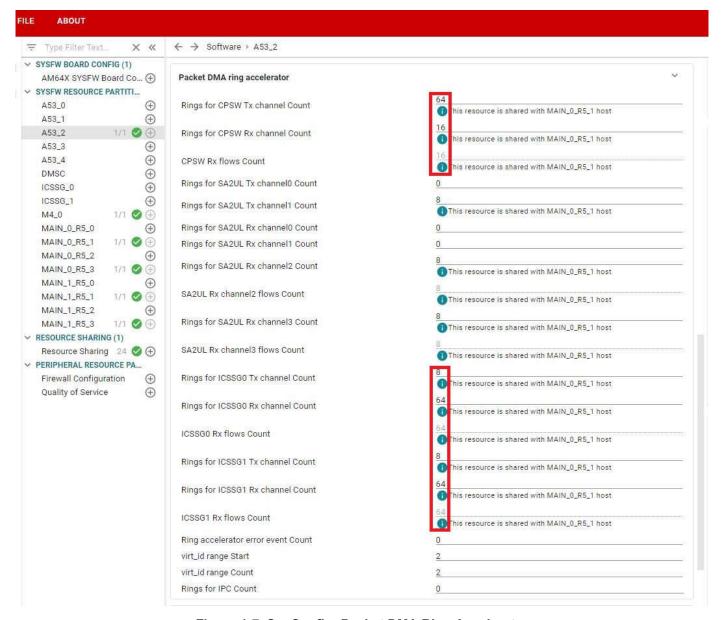

Figure 1-7. SysConfig: Packet DMA Ring Accelerator

- Rings for CPSW Tx channel count = 0

- Rings for CPSW Rx channel count = 0

- Rings for CPSW Rx flows count = 0

- Rings for ICSSG0 Tx channel count = 0

- Rings for ICSSG0 Rx channel count = 0

- Rings for ICSSG0 Rx flows count = 0

- Rings for ICSSG1 Tx channel count = 0

- Rings for ICSSG1 Rx channel count = 0

- Rings for ICSSG1 Rx flows count = 0

- 5. From (0,0) to (8,1) in R5-non secure 0-1 core (main-0-r5-0-1).

- 6. Change resource sharing from A52 -> r5\_ss\_0-1 to r5\_ss\_0-1 -> r5\_ss\_0-3.

- 7. gmake -s -C tools/sysfw/boardcfg configure-gen SOC=am64x

- Navigate to the following file. source/drivers/sciclient/sciclient\_default\_boardcfg/am64x/ sciclient\_defaultBoardcfg\_rm.c

- 9. Change the core allocations from A53 -> r5\_ss\_0-1 to r5\_ss\_0-1 -> r5\_ss\_0-3 for CPSW-related changes. There are three A53 changes and three r5-0-1 changes.

#### 1.5.2.2 SBL update

#### CAUTION

This part is applicable only in the case of sbl boot is used.

Follow the steps below:

· For compiling SBL:

```

gmake -s -C tools/sysfw/boardcfg sciclient_boardcfg SOC=am64x

gmake -j -s -f makefile.am64x sbl-clean

gmake -j -s -f makefile.am64x sbl

```

For flashing SBL:

```

cd tools/boot/

python3 uart_uniflash.py -p /dev/ttyUSBO --cfg=sbl_prebuilt/am64x-evm/default_sbl_null.cfg

```

## 2 Multicore 5-Ethernet Ports Realization

Multicore 5-Ethernet ports can be realized by one of the two methods shown below:

2-Ethernet ports from ICSSG0, 2-Ethernet ports from ICSSG1, and 1-Ethernet port from CPSW.

or

2-Ethernet ports from ICSSG0, 1-Ethernet port from ICSSG1, and 2-Ethernet ports from CPSW.

These are the details on the method that can be realized using a SEM extension card with an HSE port, which adds two additional Ethernet ports for ICSSG0.

## 3 Supported Configurations on PRU-ICSSG

Here is a link to show the supported Ethernet configurations on ICSSG0/1: What are the possible Ethernet configurations on ICSSG0/1?.

## 4 Implementation

A SEM extension card on HSE port was used for adding two additional Ethernet ports for ICSSG0 and two Ethernet ports for the existing ICSSG1 Ethernet port. These four ICSSG Ethernet ports are controlled by R5FSS\_0-0. This is enabled by ICSSG0 and ICSSG1 implementation. For more information, see the *Ethernet PRU\_ICSSG Instance-0 (PRU\_ICSSG0) Usage Guide*.

Users can release up to four Ethernet ports using ICSSG0 and ICSSG1. This can be either:

- 2-pairs of (2-port Ethernet switch mode),

- · or four Ethernet ports in MAC mode,

- · or any other combination.

This particular implementation uses all four Ethernet ports of ICSSG. A user can configure two Ethernet ports from ICSSG0 and one to ISSG1.

Driver that controls CPSW shall run on R5FSS\_0-1 CPU core controls a single Ethernet port in MAC mode. This implementation can be changed based on requirements and can operate two on-board RGMII Ethernet ports.

Both the cores communicate over the IPC.

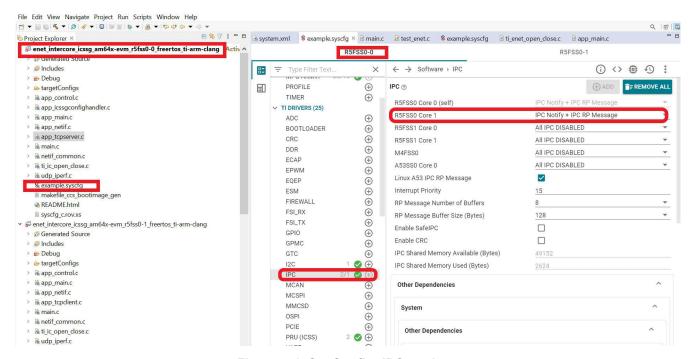

Figure 4-1. SysConfig: IPC settings

#### **CAUTION**

Note that the system project is required to run and trigger the IPC-related code inclusions.

IPC Examples must be build as System Projects. Single core build fails since IPC code generation depends on all core contexts in the application.

www.ti.com Implementation

## 4.1 System Example

A system example is available at this link: TI Test. This example is applicable for AM243x and AM64x devices. The procedure was tested on the AM64x series. AM64x is configured as  $4 \times (MAC \text{ mode}) + 1 \times (MAC \text{ mode})$  Ethernet ports.

# CAUTION During testing, AM243x was configured as 2 × (2-port Ethernet switch) mode + 1 × (MAC mode).

Use the system make command to build the examples. Load the .out files to the respective cores or flash the combined application image in either UART or OSPI mode.

```

Example:

make -s -C test/networking/lwip/enet_icssg_tcpserver/am64x-evm/system_cpsw_icssg clean

make -s -C test/networking/lwip/enet_icssg_tcpserver/am64x-evm/system_cpsw_icssg

make -s -C test/networking/lwip/enet_icssg_tcpserver/am64x-evm/system_cpsw_icssg all

```

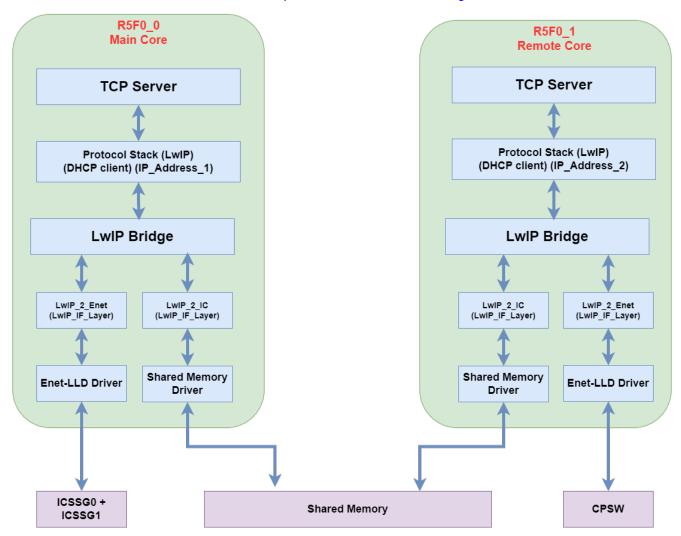

#### 4.1.1 Software Architecture

An overall software architecture for 5-ethernet port allocations is shown in Figure 4-2.

Figure 4-2. ICSSG and CPSW Allocation

Implementation www.ti.com

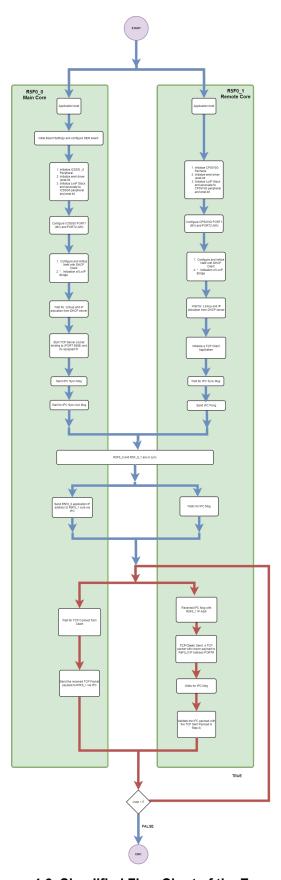

## 4.1.2 5-Ethernet Port Example

Figure 4-3. Simplified Flow Chart of the Example

www.ti.com Debug Steps

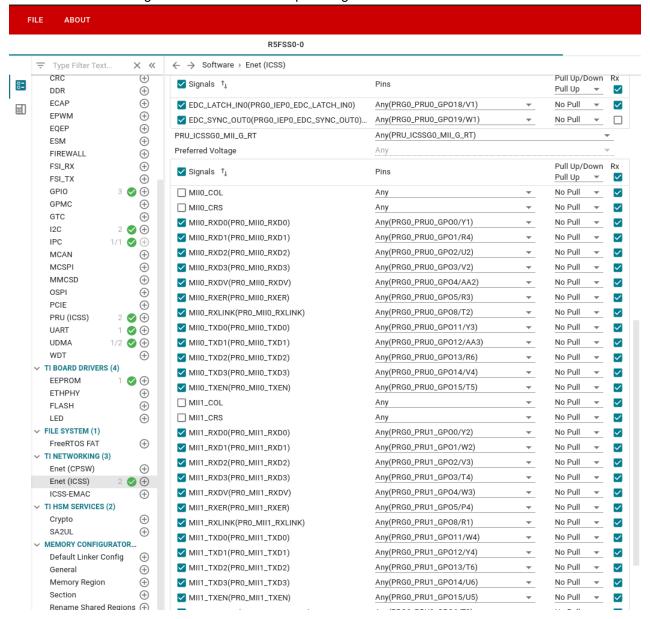

## 5 Debug Steps

- 1. The linker.cmd file must have the inclusions required for the uncached shared memory region.

- a. This region must be specified in the syscfg.

- Open the ICSSG1 modules first in the syscfg-GUI.

- a. Next, open the ICSSG0 modules.

- 3. The ICSSG0 MII pinconfig and the CPSW RGMII1 pinconfig share four pins.

- a. The pins are used for collision detection and CRS for two MII Ethernet ports.

- b. Disable the two signals on the ICSSG0 MII pinconfig.

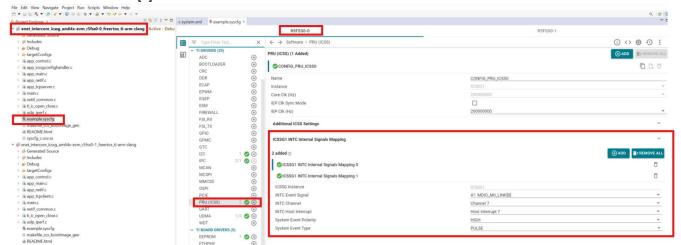

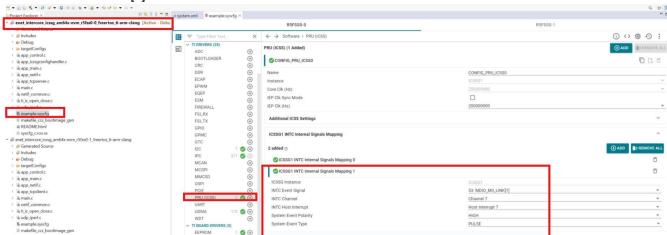

Figure 5-1. SysConfig: ICSSG0 and ICSSG1: MII mode: Allocation to R5FSS0-0

Debug Steps Www.ti.com

4. Declare the INTC config for the PRUSS module in the syscfg-GUI as follows:

a.  $\rightarrow$  Pin 41: MII[0]  $\rightarrow$  Channel 7

Figure 5-2. SysConfig: INTC CONFIG: PRU Pin-41

b.  $\rightarrow$  Pin 53: MII[1]  $\rightarrow$  Channel 7

Figure 5-3. SysConfig: INTC CONFIG: PRU Pin-53

- 5. Make sure to open LwIP in all modules.

- 6. SEM boards support MII PHYs only (DP83826e).

- a. As a result, only 100M is supported for testing purposes.

www.ti.com Debug Steps

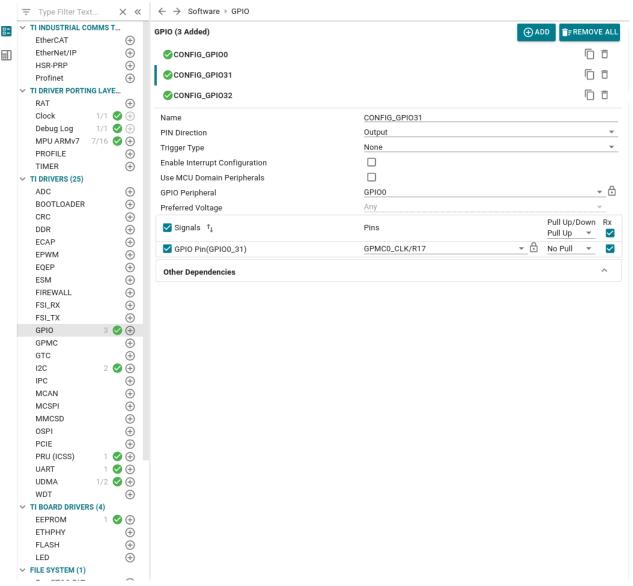

7. DP83826e PHYs need reset Pins to be declared in syscfg-GUI with the following configuration:

a.  $\rightarrow$  AM64x: CONFIG\_GPIO\_31  $\rightarrow$  Output  $\rightarrow$  GPIO0  $\rightarrow$  Pin R17  $\rightarrow$  Pull Up

Figure 5-4. SysConfig: GPIO Pin 31: DP83826e PHYs Reset Pins

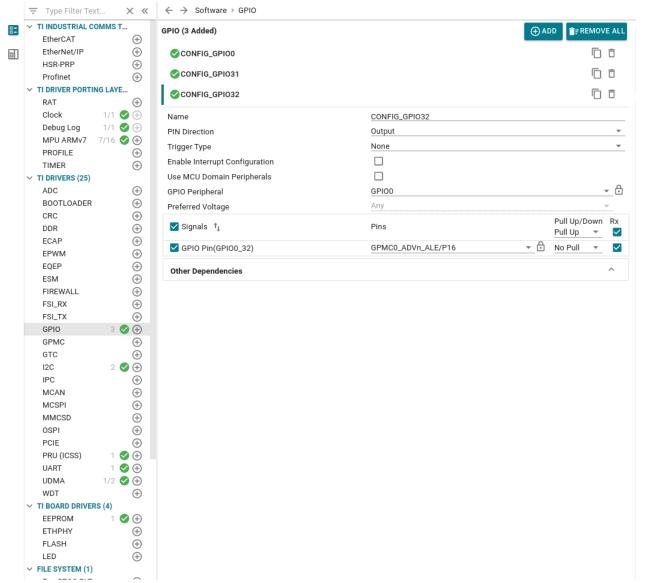

STRUMENTS Debug Steps www.ti.com

b.  $CONFIG\_GPIO\_32 \rightarrow Output \rightarrow GPIO0 \rightarrow Pin~P16 \rightarrow Pull~Up$

Figure 5-5. SysConfig: GPIO Pin 32: DP83826e PHYs Reset Pins

- 8. Enable the IPC for the active cores only.

- a. Do not have mismatched IPC configurations open for different cores.

- Make sure that the IPC is configured the same way for all cores.

www.ti.com Reference Logs

## **6 Reference Logs**

Main Core:

```

ICSSG LWIP TCP ECHO SERVER

EXT PHY Reset

Enabling clocks!

Enabling clocks!

Enabling clocks!

Enabling clocks!

Init configs EnetType:1, InstId :2

PHY 3 is alive

Init configs EnetType:1, InstId :3

EnetPhy_bindDriver: PHY 3: OUI:080028 Model:0f Ver:01 <-> 'dp83869' : OK

PHY 3 is alive

PHY 15 is alive

Init configs EnetType:1, InstId :0

EnetPhy_bindDriver: PHY 15: OUI:080028 Model:0f Ver:01 <-> 'dp83869' : OK

PHY 1 is alive PHY 3 is alive

Init configs EnetType:1, InstId :1

EnetPhy_bindDriver: PHY 3: OUI:080028 Model:11 Ver:01 <-> 'generic' : OK

PHY 1 is alive

PHY 3 is alive

Starting lwIP, local interface IP is dhcp-enabled [LWIPIF_LWIP] NETIF INIT SUCCESS

Host MAC address-0 : 34:08:e1:80:a9:36

[LWIPIF_LWIP] Enet has been started successfully

[0]Enet IF UP Event. Local interface IP:0.0.0.0

[LWIPIF_LWIP] NETIF INIT SUCCESS

HOST MAC address-1 : 70:ff:76:1e:9c:4e

[1]Enet IF UP Event. Local interface IP:0.0.0.0

[LWIPIF_LWIP] NETIF INIT SUCCESS

Host MAC address-2 : 70:ff:76:1e:9c:4f

[2] Enet IF UP Event. Local interface IP:0.0.0.0

[LWIPIF_LWIP] NETIF INIT SUCCESS

HOST MAC address-3: 70:ff:76:1e:9c:50

[3]Enet IF UP Event. Local interface IP:0.0.0.0

[0]waiting for network UP ..

EnetPhy_bindDriver: PHY 1: OUI:080028 Model:11 Ver:01 <-> 'generic' : OK

ICSSg_handleLinkUp: icssg0-1: Port 1: Link up: 100-Mbps Full-Duplex

[2]Network Link UP Event

[1]Waiting for network UP

Icssg_handleLinkUp: icssg1-1: Port 1: Link up: 1-Gbps Full-Duplex

[0]Network Link UP Event

[2]Waiting for network UP ...

[3]Waiting for network UP ...

[0]Waiting for network UP ...

[1]Waiting for network UP ...

[2]Enet IF UP Event. Local interface IP:10.24.68.135

[0]Enet IF UP Event. Local interface IP:10.24.68.74

[3]Waiting for network UP ...

[1]Waiting for network UP ...

[3]Waiting for network UP ...

[1]Waiting for network UP ...

[3]Waiting for network UP ...

Network is UP .

[IPC RPMSG ECHO] Main core start !!!

[IPC RPMSG ECHO] Message exchange started by main core !!!

[IPC RPMSG ECHO] All echoed messages received by main core from 1 remote cores !!!

[IPC RPMSG ECHO] Messages sent to each core = 100

[IPC RPMSG ECHO] Number of remote cores = 1

[IPC RPMSG ECHO] Total execution time = 3332 usecs

[IPC RPMSG ECHO] One way message latency = 16660 nsec

All tests have passed!!

[IPC txn]Remote Server interface IP:10.24.68.74

30. 59s : CPU load = 8.08 %

```

Reference Logs www.ti.com

```

35. 60s: CPU load = 8.41 %

40. 61s: CPU load = 8.30 %

accepted new connection 810c4280

[IPC_ECHO_BACK] Sent Packet number 0

[IPC_ECHO_BACK] Sent Packet number 0

[IPC_ECHO_BACK] Sent Packet number 0

45. 62s: CPU load = 8.54 %

[IPC_ECHO_BACK] Sent Packet number 0

[IPC_ECHO_BACK] Sent Packet number 0

accepted new connection 810c4280

[IPC_ECHO_BACK] Sent Packet number 0

[OBTO_ECHO_BACK] SENT PACKET NUMBER

```

www.ti.com Reference Logs

#### Remote Core:

```

Remote Core:

[IPC RPMSG ECHO] Remote core start !!!

[IPC RPMSG ECHO] Remote Core Sending sync messages to main core ... !!!

[IPC RPMSG ECHO] Remote Core waiting for messages from main core ... !!!

Closing Remote Core!!

[IPC txn]Remote Server interface IP:10.24.68.74

CPSW LWIP TCP ECHO SERVER

-===========

Enabling clocks!

EnetAppUtils_reduceCoreMacAllocation: Reduced Mac Address Allocation for CoreId:2 From 4 To 1

Mdio_open: MDIO Manual_Mode enabled

EnetPhy_bindDriver: PHY 0: OUI:080028 Model:23 Ver:01 <-> 'dp83867' : OK

PHY 0 is alive

Starting lwIP, local interface IP is dhcp-enabled [LWIPIF_LWIP] NETIF INIT SUCCESS

Host MAC address-0 : 70:ff:76:1e:9c:51

[0]Enet IF UP Event. Local interface IP:0.0.0.0

[LWIPIF_LWIP] Enet has been started successfully

[0]Waiting for network UP

[0]Waiting for network UP ...

Cpsw_handleLinkUp: Port 1: Link up: 1-Gbps Full-Duplex

MAC Port 1: link up

[0]Network Link UP Event

[0]Waiting for network UP ...

[0]Waiting for network UP ...

[0]Waiting for network UP ...

[0]Waiting for network UP .

[0] Enet IF UP Event. Local interface IP:10.24.69.120

Network is UP ..

IP eneterd is: 10.24.68.74

<<< ITERATION 1 >>>>

Connecting to: :8888

Connection with the server is established

"Hello over TCP 1" was sent to the Server

[IPC_ECHO_BACK]"Hello over TCP 1" was received from the Server: Packet num 1 Successfully received the packet 1

"Hello over TCP 2" was sent to the Server

[IPC_ECHO_BACK]"Hello over TCP 2" was received from the Server: Packet num 2

Successfully received the packet 2

"Hello over TCP 3" was sent to the Server

[IPC_ECHO_BACK]"Hello over TCP 3" was received from the Server: Packet num 3

Successfully received the packet 3

"Hello over TCP 4" was sent to the Server

[IPC_ECHO_BACK]"Hello over TCP 4" was received from the Server: Packet num 4

"Hello over TCP 5" was sent to the Server

[IPC_ECHO_BACK]"Hello over TCP 5" was received from the Server: Packet num 5

Successfully received the packet 5

Connection closed

<<<< ITERATION 2 >>>>

Connecting to: :8888

Connection with the server is established

"Hello over TCP 1" was sent to the Server

[IPC_ECHO_BACK]"Hello over TCP 1" was received from the Server: Packet num 1

"Hello over TCP 2" was sent to the Server

[IPC_ECHO_BACK]"Hello over TCP 2" was received from the Server: Packet num 2

Successfully received the packet 2

"Hello over TCP 3" was sent to the Server

[IPC_ECHO_BACK]"Hello over TCP 3" was received from the Server: Packet num 3

Successfully received the packet 3

"Hello over TCP 4" was sent to the Server

[IPC_ECHO_BACK]"Hello over TCP 4" was received from the Server: Packet num 4 Successfully received the packet 4

"Hello over TCP 5" was sent to the Server

[IPC_ECHO_BACK]"Hello over TCP 5" was received from the Server: Packet num 5

Successfully received the packet 5 Connection closed

```

## 7 Testing for the ICSSG0 and ICSSG1 Functionality

- 1. Locate the PHY addresses of the add-on board with an MDIO scan or check the corresponding registers in the MDIO-PHY interface.

- 2. Change the PHY addresses in the SysConfig-GUI for instances of ICSSG0 in the Board Config section to the PHY address locations found on the specific board.

- 3. Build the following example in the test folder:

make -s -C test/networking/lwip/enet\_icssg\_tcpserver/am64x-evm/

r5fss0-0\_freertos/ti-arm-clang clean all

#### 8 ICSSG and CPSW

ICSSG and CPSW can run together on different cores. The current example uses the ICSSG on core R5Fss\_0-0 as the main core and CPSW as the remote core. This example uses an independent LwIP stack and consumes more memory than the typical case. This can be replaced with CPSW running a Layer2 test case and ICSSG acting as a remote controller with only one LwIP stack running, and an interface layer between ICSSG and CPSW with IPC as the transfer medium.

make -s -C test/networking/lwip/enet\_icssg\_tcpserver/am64x-evm/system\_cpsw\_icssg clean all

This results in two .out files in the respective test folders.

- 1. Load the file through CCS and start the ICSSG core first.

- 2. Start the CPSW core.

- a. Four IPs on the UART console by ICSSG

- b. and one IP on the CCS console are then visible.

- 3. All ports are in MAC mode out of box.

This example was tested with CPSW, the default LwIP example running on R5Fss\_0-1 independently, and tested with iPerf software. Now, Ported the CPSW TCP server example into the Test folder and added IPC remote core functions. This cannot be used in parallel with the default IPC example testing as this uses different Vring config in the ti\_drivers\_config.c file. Make sure to allocate the correct number of cores to the example combo for testing, and to allocate the correct number of gcounts for the number of RPmessages.

Load this onto R5Fss\_0-1 core and test for functionality.

www.ti.com Summary

## 9 Summary

This document details the implementation of how to use five Ethernet ports on AM64x/AM243x using MCU+SDK for users. Users can use two Ethernet ports of ICSSG0, two Ethernet ports of ICSSG1, and one Ethernet port of CPSW3G available on AM64x/AM243x SoC.

## 10 References

- Texas Instruments, Ethernet PRU\_ICSSG Instance-0 (PRU\_ICSSG0) Usage Guide, webpage.

- AM243x-Academy

- AM64x-Academy

- MCU-PLUS-SDK-AM64x-Ethernet-Networking-Documentation

- MCU-PLUS-SDK-AM64x-Ethernet-Networking-Examples

- MCU-PLUS-SDK-AM243x-Ethernet-Networking-Documentation

- MCU-PLUS-SDK-AM243x-Ethernet-Networking-Examples

- MCU-PLUS-SDK-Git

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2024, Texas Instruments Incorporated