# Troubleshooting Guidelines when Display Not Available to DS90UB936-Q1

Peter Xu

#### Introduction

DS90UB936-Q1 is a vehicle-grade FPD-LINK III camera-side deserializer chip that enables two serializers to transmit data simultaneously, supporting up to 3Gbps per port. In the automotive industry, it is widely used in related applications such as e-mirrors and surround-view cameras. This document mainly describes the situation under which the display is not properly seen when debugging the system. For this reason, you need to troubleshoot the hardware design, signal link, power management, and software configuration in multiple dimensions and provide the corresponding solutions.

## Description of the faults

In a practical application case, the problem can be mainly described as that the rear-level SoC does not properly display the image transmitted from the camera side. The situation where this problem occurs shall be considered from both the hardware and software perspectives, and the specific problem points shall be gradually investigated and confirmed.

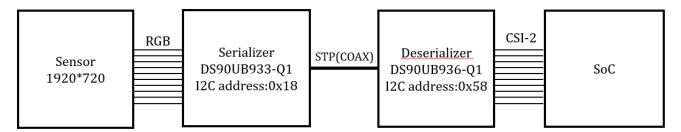

Figure 1. Block diagram of the system

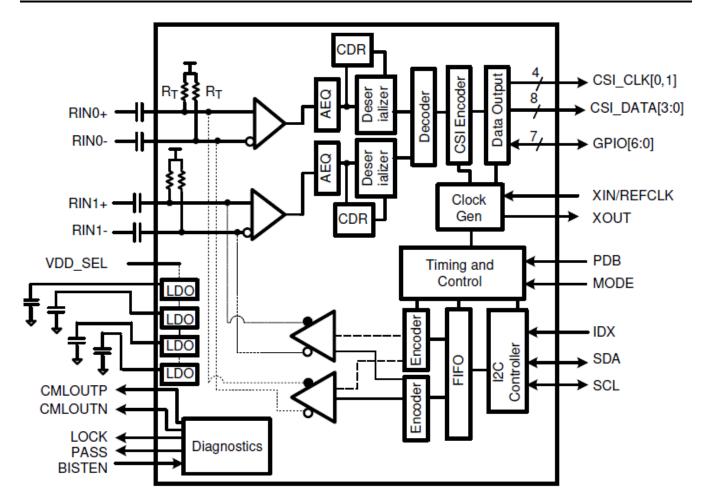

Figure 2. DS90UB936-Q1 block diagram

## Hardware perspective

1. Power-up sequencing, and power stability

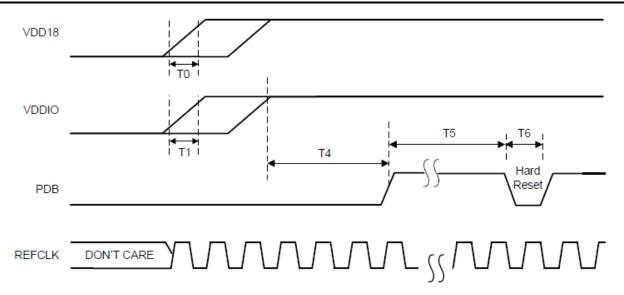

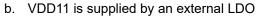

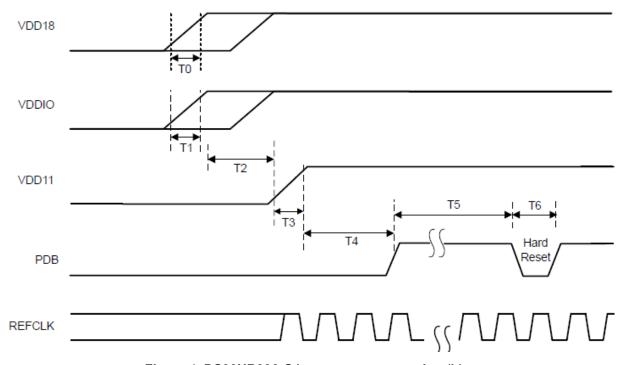

The detailed requirements for power-up sequencing, are proposed for DS90UB936-Q1, as shown in the following diagram. All power supplies can be probed with an oscilloscope to meet sequencing requirements. One of the key troubleshooting issues to be addressed is whether the PDB powers up after VDD18/VDDIO. DS90UB936-Q1 can be powered up in two ways:

a. VDD11 is supplied by an internal LDO

Figure 3. DS90UB936-Q1 power-up sequencing (a)

Figure 4. DS90UB936-Q1 power-up sequencing (b)

In addition to the sequencing between different voltage rails, check if the power-up time of each rail meets the requirements. If VDD18 requires that a power-up time shall not be less than 0.05ms, the too fast power-up time may cause an internal module error.

|    | PARAMETER                                   | MIN  | TYP | MAX | UNIT | NOTES                     |

|----|---------------------------------------------|------|-----|-----|------|---------------------------|

| T0 | VDD18 rise time                             | 0.05 |     |     | ms   | at 10/90%                 |

| T1 | VDDIO rise time                             | 0.2  | 1   |     | ms   | at 10/90%                 |

| T2 | VDD18 High to VDD11 applied                 | 0    |     |     | ms   | N/A when VDD_SEL<br>= LOW |

| T3 | VDD11 rise time                             | 0.2  | 1   |     | ms   | at 10/90%                 |

| T4 | VDD to PDB                                  | 0    |     |     | ms   | After all VDD are stable  |

| T5 | PDB high time before PDB hard reset         | 1    |     |     | ms   |                           |

| T6 | PDB high to low pulse width                 | 2    |     |     | ms   | Hard reset (optional)     |

| Т7 | PDB to I2C ready (IDX and MODE valid) delay | 2    |     |     | ms   |                           |

Figure 5. Power-up sequencing requirements of DS90UB936-Q1 power

In addition to the corresponding sequencing, during the troubleshooting, check if the individual power rails are working properly, for example, VDD18 being 1.8V or within the required range. VDD18 mainly powers the internal LDO and output modules, so the ripple of VDD18 is required to be 50mV. VDD11 primarily powers digital modules and requires a ripple within 25mV if VDD11 is supplied externally. In practical applications, VDD18 requires a maximum of 279mA and is recommended to be powered by LDO (such as the TPS745-Q1); To prevent excessive ripple in VDD11 from affecting the digital module, it is recommended that VDD11 shall be powered by an internal LDO. The corresponding power voltages are shown in Figure 6.

|                             |                                                            | MIN   | NOM | MAX   | UNIT              |

|-----------------------------|------------------------------------------------------------|-------|-----|-------|-------------------|

| Supply voltage              | V <sub>(VDD18)</sub>                                       | 1.71  | 1.8 | 1.89  | ٧                 |

| Supply voltage              | V <sub>(VDD11)</sub> (VDD_SEL = HIGH ONLY)                 | 1.045 | 1.1 | 1.155 | ٧                 |

| Supply voltage offset       | $V_{(VDD11)} - V_{(VDDIO)}, V_{(VDDIO)} = 1.8V$            | -50   |     | 50    | mV                |

| LVCMOS supply voltage       | V <sub>(VDDIO)</sub> = 1.8 V                               | 1.71  | 1.8 | 1.89  | ٧                 |

| LVCWIOS supply voltage      | $\overrightarrow{OR} V_{(VDDIO)} = 3.3 V$                  | 3     | 3.3 | 3.6   | ٧                 |

| Open-drain voltage          | GPIO3/INTB = $V_{(INTB)}$ , I2C_SDA, I2C_SCL = $V_{(I2C)}$ | 1.71  |     | 3.6   | ٧                 |

|                             | V <sub>(VDD11)</sub>                                       |       |     | 25    | mV <sub>P-P</sub> |

|                             | V <sub>(VDD18)</sub>                                       |       |     | 50    | $mV_{P\text{-}P}$ |

| Supply noise <sup>(1)</sup> | $V_{(VDDIO)} = 1.8 \text{ V}$                              |       |     | 50    | mV <sub>P-P</sub> |

|                             | V <sub>(VDDIO)</sub> = 3.3 V                               |       |     | 100   | III v P-P         |

|                             | RIN0+, RIN1+                                               |       | 10  |       | $mV_{P\text{-}P}$ |

Figure 6. DS90UB936-Q1 power voltage and ripple requirements

Please verify with an oscilloscope that the VDD power meets the voltage range and ripple requirements. When the voltage range and ripple do not meet the requirements, the internal modules may operate in an improper status, then resulting in abnormal output.

#### 2. Clock status

DS90UB936-Q1 requires a stable clock signal input. The clock source can be either an active crystal oscillator or a passive crystal. DS90UB936-Q1 proposes accuracy and error requirements for the clock signal, as shown in Figure 7. If the clock source is a crystal oscillator, you shall note the high and low levels of the crystal oscillator circuit output. When VDDIO is set to 3.3V, it requires that the high level of clock signal is more than 2V and a low level less than 0.8V. And the duty cycle shall be between 40%-60%. A wrong clock signal can cause an abnormal or no CSI output.

| PARAMETER                                    | TEST CONDITIONS                | MIN  | TYP  | MAX                  | UNIT   |

|----------------------------------------------|--------------------------------|------|------|----------------------|--------|

| REFERENCE CLOCK                              |                                |      |      |                      |        |

| Frequency tolerance                          | -40°C ≤ T <sub>A</sub> ≤ 105°C |      |      | ±50                  | ppm    |

| Frequency stability                          | Aging                          |      |      | ±50                  | ppm    |

| Amplitude                                    |                                | 800  | 1200 | V <sub>(VDDIO)</sub> | mVp-p  |

| Symmetry                                     | Duty Cycle                     | 40%  | 50%  | 60%                  |        |

| Rise and fall time                           | 10% – 90%                      |      |      | 6                    | ns     |

| Jitter                                       | 200 kHz – 10 MHz               |      | 50   | 200                  | ps p-p |

| Frequency                                    |                                | 23   | 25   | 26                   | MHz    |

| Enroad apostaria alosk modulation persontage | Center Spread                  | -0.5 |      | +0.5                 | %      |

| Spread-spectrum clock modulation percentage  | Down Spread                    | -1   |      | 0                    | %      |

| Spread-spectrum clock modulation frequency   |                                |      |      | 33                   | KHz    |

Figure 7. DS90UB936-Q1 clock signal requirements

## Software perspective

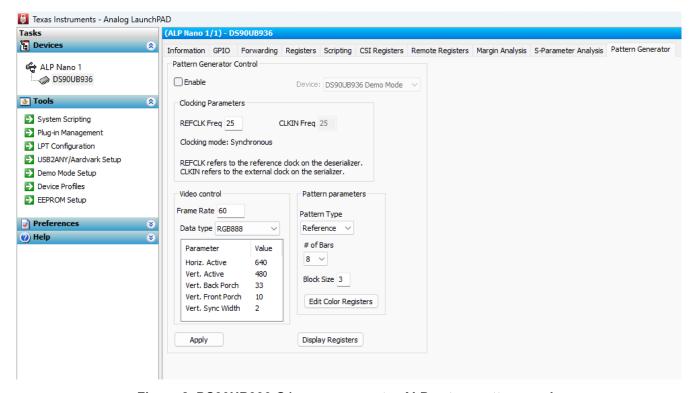

1. Check if pattern mode is displayed

The pattern mode of DS90UB936-Q1 can be used to troubleshoot the problems from DS90UB936-Q1 to SoC section when the problem occurs. Enable pattern mode via the upper computer software ALP of DS90UB936-Q1, as shown in Figure 8. Once the parameters are set, SoC receiving can be used to confirm whether the signal is normal, while the dedicated CSI software can be used to monitor whether the signal flow is normal.

Figure 8. DS90UB936-Q1 upper computer ALP enters pattern mode

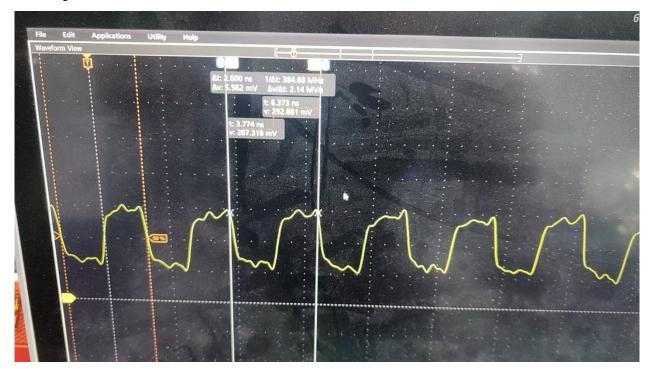

If pattern mode is normal, you shall see a color bar on the screen. If there is no picture, you shall verify that the settings at the SoC receiving end match those of the pattern. On the hardware troubleshooting, CSI clock signal (PIN11/PIN12) is tested by a high-speed oscilloscope (bandwidth greater than 2G). If CSI clock is set to 800MHz, you shall see a clock signal at 400MHz frequency on the oscilloscope, as shown in Figure

9. If no similar signal is available, please verify through a register whether DS90UB936-Q1 receives a stable clock signal, and troubleshoot the clock circuits.

Figure 9. DS90UB936-Q1 CSI clock test

## 2. Related configuration of DS90UB936-Q1

After the pattern mode is displayed normally, since some serializers do not support pattern mode by themselves, a complete test is usually performed directly with the camera. Configuration codes of DS90UB936-Q1 are given in the annex at the end of the document and the code parameters can be adjusted as required actually. Next, the key points of configuration in those codes are mainly introduced as follows:

## a. CSI mode configuration

The protocol needs to be negotiated from the Sensor to the serializer, and from the deserializer to the SoC before data transmission, otherwise the receiving end will not receive data correctly. The specific protocol between DS90UB936-Q1 and SoC needs to be configured, and the data format for all protocols is given in Figure 10. Populate this data format into the register in Figure 11. If the data format for sensor and serializer is RAW10, populate the data format of Figure 10 into the RAW10 register. If it is RAW12 or CSI-2 format, it shall be populated into RAW12 or CSI-2 register respectively, as shown in Figure 11.

As an example, if Sensor transfers data to DS90UB933-Q1 via RAW10 format and DS90UB936-Q1 via YUV422 10BIT format to SoC, 0x1F shall be written to 0x70 register of DS90UB936-Q1. If the Sensor is transferred to the DS90UB935-Q1 via CSI-2 format, simply adjust 0x72 register to meet actual needs.

Incorrect register configuration can also cause that SoC cannot receive signals properly.

## **Table 19 YUV Image Data Types**

| Data Type | Description                                   |

|-----------|-----------------------------------------------|

| 0x18      | YUV420 8-bit                                  |

| 0x19      | YUV420 10-bit                                 |

| 0x1A      | Legacy YUV420 8-bit                           |

| 0x1B      | Reserved                                      |

| 0x1C      | YUV420 8-bit (Chroma Shifted Pixel Sampling)  |

| 0x1D      | YUV420 10-bit (Chroma Shifted Pixel Sampling) |

| 0x1E      | YUV422 8-bit                                  |

| 0x1F      | YUV422 10-bit                                 |

# Table 25 RGB Image Data Types

| Data Type | Description |

|-----------|-------------|

| 0x20      | RGB444      |

| 0x21      | RGB555      |

| 0x22      | RGB565      |

| 0x23      | RGB666      |

| 0x24      | RGB888      |

| Data Type | Description           |

|-----------|-----------------------|

| 0x27      | RAW24                 |

| 0x28      | RAW6                  |

| 0x29      | RAW7                  |

| 0x2A      | RAW8                  |

| 0x2B      | RAW10                 |

| 0x2C      | RAW12                 |

| 0x2D      | RAW14                 |

| 0x2E      | RAW16                 |

| 0x2F      | RAW20 CSDN @亦枫Leonlew |

Figure 10. Image transfer data format

#### 7.6.104 RAW10\_ID Register

RX port specific register. The FPD-Link III Port Select register 0x4C configures which unique RX port registers can be accessed by I2C read and write commands.

RAW10 virtual channel mapping only applies when FPD-Link III operating in RAW10 input mode. See register 0x71 for RAW12 and register 0x72 for CSI-2 mode operation.

Table 7-122. RAW10\_ID (Address 0x70)

| BIT | FIELD    | TYPE | DEFAULT                | DESCRIPTION                                                                                                                                                                                        |

|-----|----------|------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6 | RAW10_VC | R/W  | <rx #="" port=""></rx> | RAW10 Mode Virtual Channel This field configures the CSI Virtual Channel assigned to the port when receiving RAW10 data. The field value defaults to the FPD-Link III receive port number (0 or 1) |

| 5:0 | RAW10_DT | R/W  | 0x2B                   | RAW10 DT This field configures the CSI data type used in RAW10 mode. The default of 0x2B matches the CSI specification.                                                                            |

#### 7.6.105 RAW12\_ID Register

RX port specific register. The FPD-Link III Port Select register 0x4C configures which unique RX port registers can be accessed by I2C read and write commands.

RAW12 virtual channel mapping only applies when FPD-Link III operating in RAW12 input mode. See register 0x70 for RAW10 and register 0x72 for CSI-2 mode operation.

Table 7-123. RAW12\_ID (Address 0x71)

| BIT | FIELD    | TYPE | DEFAULT                | DESCRIPTION                                                                                                                                                                                        |

|-----|----------|------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6 | RAW12_VC | R/W  | <rx #="" port=""></rx> | RAW12 Mode Virtual Channel This field configures the CSI Virtual Channel assigned to the port when receiving RAW12 data. The field value defaults to the FPD-Link III receive port number (0 or 1) |

## 7.6.106 CSI\_VC\_MAP Register

RX port specific register. The FPD-Link III Port Select register 0x4C configures which unique RX port registers can be accessed by I2C read and write commands.

CSI virtual channel mapping only applies when FPD-Link III operating in CSI-2 input mode. See registers 0x70 and 0x71 for RAW mode operation.

Table 7-124. CSI\_VC\_MAP (Address 0x72)

| _ |     |            |      |         | •                                                                                                                                                                                                                                                                                    |

|---|-----|------------|------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | BIT | FIELD      | TYPE | DEFAULT | DESCRIPTION                                                                                                                                                                                                                                                                          |

|   | 7:0 | CSI_VC_MAP | R/W  | 0xE4    | CSI-2 Virtual Channel Mapping Register This register provides a method for replacing the Virtual Channel Identifier (VC-ID) of incoming CSI packets. [7:6]: Map value for VC-ID of 3 [5:4]: Map value for VC-ID of 2 [3:2]: Map value for VC-ID of 1 [1:0]: Map value for VC-ID of 0 |

## Figure 11. The data format corresponds to the register

#### b. 10bit to 8bit conversion

In practice, there may be a possibility that the input is 10bit format and the output is 8bit format. For example, Sensor transfers data to the DS90UB933-Q1 via RAW10 format and DS90UB936-Q1 via YUV422 8BIT format to SoC. At this moment, the input format is 10bit, and the output format is 8bit, which means that DS90UB936-Q1 needs to convert 10bit to 8bit. In this case, the sensor at the previous stage is required to confirm whether the high or low 8bit in the transmitted 10bit is significant, and 0x7C register in the DS90UB936-Q1 is modified accordingly. When it is set to be 10, high 8bit is significant. When it is set to be 11, low 8bit is significant.

## 7.6.116 PORT\_CONFIG2 Register

RX port specific register. The FPD-Link III Port Select register 0x4C configures which unique RX port registers can be accessed by I2C read and write commands.

Table 7-134. PORT\_CONFIG2 (Address 0x7C)

|     | Table 7-134. PORT_CONFIG2 (Address 0x7C) |      |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|-----|------------------------------------------|------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| BIT | FIELD                                    | TYPE | DEFAULT | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| 7:6 | RAW10_8BIT_CTL                           | R/W  | 0x0     | Raw10 8-bit mode When Raw10 Mode is enabled for the port, the input data is processed as 8-bit data and packed accordingly for transmission over CSI.  00: Normal Raw10 Mode 01: Reserved 10: 8-bit processing using upper 8 bits. When selecting this value, change CSI data type value RAW10_DT in register 0x70[5:0] 11: 8-bit processing using lower 8 bits. When selecting this value, change CSI data type value RAW10_DT in register 0x70[5:0] |  |  |  |  |

| 5   | DISCARD_ON<br>_PAR_ERR                   | R/W  | 0x1     | Discard frames on Parity Error 0 : Forward packets with parity errors 1 : Truncate Frames if a parity error is detected                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| 4   | DISCARD_ON<br>_LINE_SIZE                 | R/W  | 0x0     | Discard frames on Line Size 0 : Allow changes in Line Size within packets 1 : Truncate Frames if a change in line size is detected                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| 3   | DISCARD_ON<br>_FRAME_SIZE                | R/W  | 0x0     | Discard frames on change in Frame Size When enabled, a change in the number of lines in a frame will result in truncation of the packet. The device will resume forwarding video frames based on the PASS_THRESHOLD setting in the PORT_PASS_CTL register. 0: Allow changes in Frame Size 1: Truncate Frames if a change in frame size is detected                                                                                                    |  |  |  |  |

| 2   | RESERVED                                 | R/W  | 0x0     | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| 1   | LV_POLARITY                              | R/W  | 0x0     | LineValid Polarity This register indicates the expected polarity for the LineValid indication received in Raw mode.  1 : LineValid is low for the duration of the video line  0 : LineValid is high for the duration of the video line                                                                                                                                                                                                                |  |  |  |  |

| 0   | FV_POLARITY                              | R/W  | 0x0     | FrameValid Polarity This register indicates the expected polarity for the FrameValid indication received in Raw mode. 1 : FrameValid is low for the duration of the video frame 0 : FrameValid is high for the duration of the video frame                                                                                                                                                                                                            |  |  |  |  |

## Figure 12. x7C register

## c. Hsync/Vsync settings

If the serializer is a DS90UB933-Q1, Sensor may input Hsync/Vsync signal. Hsync/Vsync of some sensors is highly significant and some are lowly significant. This shall be set in 0x7C register of the DS90UB936-Q1 as shown in Figure 12. Bit1/bit0 is set with the corresponding significant level. LV\_POLARITY corresponds to Hsync, while FV\_POLARITY corresponds to Vsync. Both bits are set to 1, it enables low, while being set to 0, it enables high. Incorrect setting results in no output.

#### 3. SoC configuration

When DS90UB936-Q1 is fully set up correctly, LINE\_COUNT and LINE\_LEN registers of DS90UB936-Q1 can be checked as shown in Figure 13. LINE\_COUNT represents the number of active lines received by the DS90UB936-Q1 in one frame and the LINE\_LEN register represents the active length received by the DS90UB936-Q1 in one line. When these two numbers match the data transmitted by the Sensor, DS90UB936-Q1 is proven to receive valid data and output.

If you do not see the normal picture at this point, you shall check whether configuration at SoC receiving end matches the requirements: the length and width set at the receiving end shall match exactly with the actual values, and the data format set at the receiving end shall match exactly with DS90UB936-Q1 setting.

#### 7.6.107 LINE COUNT HI Register

RX port specific register. The FPD-Link III Port Select register 0x4C configures which unique RX port registers can be accessed by I2C read and write commands.

#### Table 7-125. LINE\_COUNT\_HI (Address 0x73)

| BIT | FIELD         | TYPE | DEFAULT | DESCRIPTION                                                                                                                                                                                                                                   |

|-----|---------------|------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | LINE_COUNT_HI | R    | 0x0     | High byte of Line Count<br>The Line Count reports the line count for the most recent<br>video frame. When interrupts are enabled for the Line Count<br>(via the IE_LINE_COTT_CHG register bit), the Line Count<br>value is frozen until read. |

#### 7.6.108 LINE\_COUNT\_LO Register

RX port specific register. The FPD-Link III Port Select register 0x4C configures which unique RX port registers can be accessed by I2C read and write commands.

Table 7-126. LINE\_COUNT\_LO (Address 0x74)

|     | Table 1 Test Ente_openin_tes (Fidances on 1) |      |         |                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|-----|----------------------------------------------|------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| BIT | FIELD                                        | TYPE | DEFAULT | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| 7:0 | LINE_COUNT_LO                                | R    | UXU     | Low byte of Line Count The Line Count reports the line count for the most recent video frame. When interrupts are enabled for the Line Count (via the IE_LINE_ONT_CHG register bit), the Line Count value is frozen until read. In addition, when reading the LINE_COUNT_Fegisters, the LINE_COUNT_LO is latched upon reading LINE_COUNT_HI to ensure consistency between the two portions of the Line Count. |  |  |

#### 7.6.109 LINE\_LEN\_1 Register

RX port specific register. The FPD-Link III Port Select register 0x4C configures which unique RX port registers can be accessed by I2C read and write commands.

Table 7-127. LINE\_LEN\_1 (Address 0x75)

| BIT | FIELD       | TYPE | DEFAULT | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                |

|-----|-------------|------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | LINE_LEN_HI | R    | 0×0     | High byte of Line Length The Line Length reports the line length recorded during the most recent video frame. If line length is not stable during the frame, this register will report the length of the last line in the video frame. When interrupts are enabled for the Line Length (via the IE_LINE_LEN_CHG register bit), the Line Length value is frozen until read. |

110 Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

D\$90UB936-Q1

#### 7.6.110 LINE\_LEN\_0 Register

RX port specific register. The FPD-Link III Port Select register 0x4C configures which unique RX port registers can be accessed by I2C read and write commands.

Table 7-128. LINE\_LEN\_0 (Address 0x76)

| BIT | FIELD       | TYPE | DEFAULT | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|-----|-------------|------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 7:0 | LINE_LEN_LO | R    | 0×0     | Low byte of Line Length The Line Length reports the length of the most recent video line. When interrupts are enabled for the Line Length (via the IE_LINE_LEN_CHG register bit), the Line Length value is frozen until read. In addition, when reading the LINE_LEN registers, the LINE_LEN_LO is latched upon reading LINE_LEN_HI to ensure consistency between the two portions of the Line Length. |  |  |  |

Figure 13. LINE\_COUNT register and LINE\_LEN register

#### **Summary**

This document analyzes the causes of the DS90UB936-Q1 black screen in application, proposes troubleshooting guidelines from the hardware and software perspective, and provides appropriate solutions to help engineers troubleshoot problems faster. In addition, an actual configuration code is given for reference.

#### References

DS90UB936-Q1 Dual 3 Gbps FPD-Link III Deserializer Hub With MIPI CSI-2 Outputs datasheet (Rev. C)

#### Reference codes

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2025. Texas Instruments Incorporated