# Second-sourcing options for small-package amplifiers

### By Tim Claycomb

Applications Engineer, General-Purpose Amplifiers

#### Introduction

The increase in demand for low-cost end products has caused designers to come up with innovative ways to stay below system price targets, while still meeting their product's performance specifications. For example, in addition to amplifier performance, designers must consider all amplifier characteristics, including cost and package size.

It's important to consider package size in low-cost designs because different amplifier packages may have different cost implications in the system. Many new devices are offered in innovative small packages that can help designers meet their goals. However, if multiple semiconductor manufacturers aren't offering an amplifier in a small package, that limits the options for second sourcing. Second sources are often required to prevent product manufacturing complications should a supplier have trouble meeting demand. Not having a second source can cost the end-product manufacturer large amounts of money if the semiconductor manufacturer is not able to meet their supply demand.

This article discusses how to provide a second-source option for small-package amplifiers that do not have a direct pin-to-pin-compatible second source. Also covered are the possible manufacturing and design challenges the designer may face during printed-circuit board (PCB) layout.

#### **PCB-Layout Modifications**

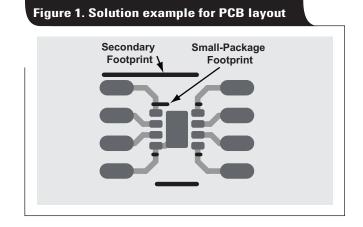

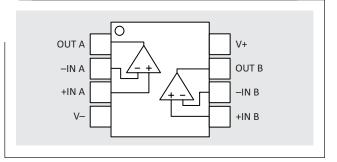

Modifying the PCB layout of the operational amplifier (op amp) to include two different op-amp package footprints provides a second source for small-package amplifiers by including a secondary, commonly used, industry-standard package footprint on the PCB that encompasses the smallpackage footprint. Figure 1 illustrates how this works in a PCB layout. Small-outline integrated circuits (SOICs), thin-shrink small-outline packages (TSSOPs) and very-thin-shrink small-outline packages (VSSOPs) are the industry's most common packages. These packages therefore make for an excellent secondary footprint because many second sources are available. This article focuses on the PCB layout of dual amplifiers packaged with the industrystandard pinout (Figure 2) in relationship to dual smallpackage amplifiers such as small-outline no-lead (SON) and small-outline transistor (SOT) packages. However, the designer can use this method with any channel count and any package.

#### Figure 2. Industry-standard package pinout

#### **SOIC** package layout

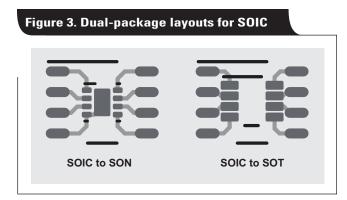

The spacing between the pads of the SOIC footprint allow many small-package amplifiers to fit between the pads of the footprint, making the SOIC package an excellent choice to use as a secondary package. Figure 3 shows PCB layouts for a dual-package amplifier for both the SON and SOT small-package amplifiers inside of an industrystandard pinout of a SOIC package.

Designers can easily replicate this layout by routing pin 1 through pin 8 of the SOIC package to pin 1 through pin 8 of the small-package amplifier. However, there are limitations and some possible manufacturing considerations the designer should take into account when using the SOIC package with the SOT package.

# **TSSOP** package layout

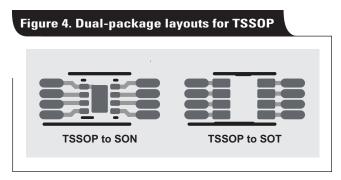

Although the TSSOP package and SOIC package offer similar benefits, the TSSOP package offers more spacing between the pads of the footprint. This extra spacing allows the use of wider small-package amplifiers in the design and eliminates limitations and possible manufacturing concerns introduced with the SOIC and SOT package combination. The TSSOP package also has a smaller form factor, which requires less PCB area than the SOIC package—a benefit for space-constrained PCBs.

Figure 4 illustrates PCB layouts for a dual-package amplifier for both the SON and SOT small-package amplifiers inside of an industry-standard pinout of a TSSOP package. The PCB layout is similar to the SOIC package, with pin 1 through pin 8 of the TSSOP package routing to pin 1 through pin 8 of the small-package amplifier.

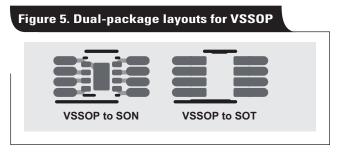

#### **VSSOP** package layout

The VSSOP package has a smaller form factor than the TSSOP and SOIC packages, making it the smallest secondary common-package option to use as a second source. The VSSOP package does not have as much space between the pads of the footprint, reducing the number of smallpackage devices that the designer can use with the VSSOP package. However, the VSSOP package can still be used with the SOT package because the two devices have the same pitch, which allows the pads of the two footprints to align.

Figure 5 illustrates PCB layouts for a dual-package amplifier for both the SON and SOT small-package amplifiers inside of an industry-standard pinout of a VSSOP package. Again, pin 1 through pin 8 of the VSSOP package route to pin 1 through pin 8 of the small-package amplifier.

### Manufacturing and design considerations

There are a few manufacturing and design effects to consider when including the secondary footprint. The main manufacturing concern is insufficient spacing between the pads of the secondary footprint and the pads of the small-package amplifier footprint. Insufficient spacing between the pads results in insufficient or no solder mask to fill the space between the pads of the two footprints.

During the reflow soldering process, the lack of solder mask can cause the amplifier to move and short circuit, or leave the device pins floating. Allowing at least four mils of space between the pads of the devices minimizes the risk of this occurring. The four mils of space is a common design rule among PCB manufacturers and provides enough spacing to place the solder mask between the two device pads. Figure 6 shows how the device may shift during the reflow process if proper solder mask clearances aren't maintained.

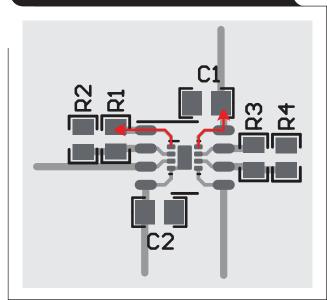

Designers must also consider that using a secondary footprint in the PCB layout may cause additional trace length in the routing. For example, components such as decoupling capacitors and other passive components must be placed further away from the pin of the device when populating a small-package amplifier in the end product. Not placing decoupling capacitors next to the device pin can cause noise to easily couple into the device when placed in noisy environments. Also, placing passive components that set the gain of the amplifier further away from the inverting pin of the small-package amplifier can also cause noise to couple into the circuit. Figure 7 shows the additional trace length that occurs when populating the small-package amplifier.

#### Conclusion

The SOIC, TSSOP, and VSSOP packages commonly used throughout the industry have an industry-standard pinout that equips designers with many options for a second source. The SOIC package offers many second-sourcing options and the footprint is large enough for use with most small-package amplifiers. The TSSOP package has more spacing between the footprint pads, enabling the use of wider small-package amplifiers and minimizing potential manufacturing issues. The VSSOP package has the smallest secondary-footprint option, benefitting spaceconstrained designs.

Although modifying the PCB to include a secondary footprint will not reduce total PCB area, it is an effective yet simple way to provide a second source for small-package amplifiers and reduce the cost of an end product.

#### **Related Web site**

Product information: **TI operational amplifiers**

#### Figure 7. Additional trace length in layout

# **TI Worldwide Technical Support**

# TI Support

Thank you for your business. Find the answer to your support need or get in touch with our support center at

www.ti.com/support

- China: http://www.ti.com.cn/guidedsupport/cn/docs/supporthome.tsp

- Japan: http://www.tij.co.jp/guidedsupport/jp/docs/supporthome.tsp

#### **Technical support forums**

Search through millions of technical questions and answers at TI's E2E™ Community (engineer-to-engineer) at

e2e.ti.com China: http://www.deyisupport.com/ Japan: http://e2e.ti.com/group/jp/

# TI Training

From technology fundamentals to advanced implementation, we offer on-demand and live training to help bring your next-generation designs to life. Get started now at

#### training.ti.com

- China: http://www.ti.com.cn/general/cn/docs/gencontent.tsp?contentId=71968

- Japan: https://training.ti.com/jp

**Important Notice:** The products and services of Texas Instruments Incorporated and its subsidiaries described herein are sold subject to TI's standard terms and conditions of sale. Customers are advised to obtain the most current and complete information about TI products and services before placing orders. TI assumes no liability for applications assistance, customer's applications or product designs, software performance, or infringement of patents. The publication of information regarding any other company's products or services does not constitute TI's approval, warranty or endorsement thereof.

A011617

E2E is a trademark of Texas Instruments. All other trademarks are the property of their respective owners.

© 2018 Texas Instruments Incorporated. All rights reserved.

SLYT744

#### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ('TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your noncompliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2018, Texas Instruments Incorporated