# HDQ Communication Basics for TI's Battery Monitor ICs

Battery Management

#### Introduction

Most battery monitor ICs from TI, including the bq2018 and bq2019, includes a single-wire HDQ serial data interface. Host controllers, configured for either polled or interrupt processing, use the interface to access various IC registers. The purpose of this application note is to cover most of the communication related topics for these devices.

# HDQ BASICS

The HDQ pin requires an external pullup or pulldown resistor. The interface uses a commandbased protocol, where the host processor sends a command byte to the battery monitor. The command directs the battery monitor either to store the next eight bits of data received to a register specified by the command byte or to output the eight bits of data from a register specified by the command byte. The communication protocol is asynchronous return-to-one and is referenced to Vss, which is typically tied to the battery pack's negative terminal.

There is no need to update register values in the battery monitor each time a run time computation is made. Local variables in the host processor can be kept up to date with pertinent data so that minimal communication is required for most computations. Update of registers in the battery monitor can be done at events like full or empty, after some predefined interval, when a self-discharge estimation is performed, or prior to a power down operation. The host may find that it only needs to read the CCR and DCR registers at frequent intervals (30 seconds, perhaps) to update the user with the latest runtime computation.

A GPIO or UART (on the host) can be used to communicate with the battery monitors. A microcode example is provided at the end of this application note.

#### Servicing High Priority Interrupts while Receiving HDQ Data

Normal host processing of communication with the battery monitors may encounter a high priority interrupt that needs to be serviced prior to completion of a communication transaction. The time between any bits sent from the host to the battery monitors is not time critical and as long as the HDQ line is high, the host processor may pause the communication and service an interrupt for any extended period and then resume the communication. However, when reading bits from the battery monitors, the host cannot allow any interruption, as the data is transmitted at a fixed rate and the host must know the exact timing to determine whether individual bits are ones or zeroes. Provision must be made for the host to flag any interruption

while receiving data. The host should then hold the HDQ line low, long enough to cause a break (no need to wait until transmission is complete from the battery monitor) and then retry the communication to avoid potential misreads of the data.

## Using a UART for HDQ Communication

The host may be able to avoid the issue with communication repeats due to an inopportune interrupt if the host has a spare UART port to dedicate to the bq2019 communication. The UART may be set up to send and receive an 8-bit word for each bit of the communication. The UART may be set for a baud rate of 57,600 with no parity and 2 stop bits. This timing will send or receive a single word in 190  $\mu$ sec and meet the maximum bit rate of the HDQ timing. The user could load the UART with 0xc0 to transmit a logic zero and with 0xfe to transmit a logic one. When receiving data, the host could interpret any data greater than or equal to 0xf0 as a logic one and any data less than 0xf0 as a logic zero.

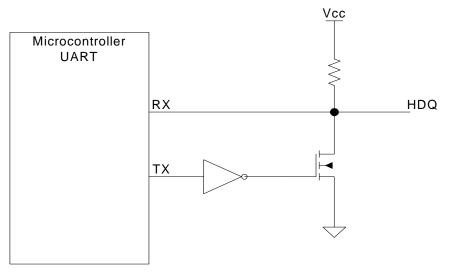

Also note that the TX and RX of the UART must be tied together. In case the TX output is not an open-drain output, it will need to be inverted and then drive the gate of an NFET with the open drain tied to the RX input. See Figure 1.

HDQ Comunication Circuit For UART Without Open Drain Outputs

# Sending a Break before Each Communication

If the battery pack is removed or some intermittent connection occurs on the HDQ line, the battery monitor may become out of sync with the host communication. A safe practice would be to issue a break prior to each communication to insure that communication was always in sync. An alternative procedure might be to always send a break at the start of a communication block and then not send it again unless there was a need to abort the communication or if the battery monitor did not respond within the expected time.

## **APPENDIX A: HDQ Assembly Code Example**

; hdq routines: receives and transmits 1 byte using HDQ protocall ;timed bit out routine ;timer 1 is setup as 1 micro second timer. ;this is written for a PIC 16c66 using a 8051 macro compiler. ;There are 2 HDQ ports on this example. Either one can be eliminated if not required. ;hdq\_d1 rc.3 = ;hdq d rc.4 = hdq\_read\_byte hdq\_break ;send a break before each communication call mov hdq\_buf,hdq\_cmd ;put hdg\_cmd into hdg\_buf clrb hdq\_buf.7 ;set for read call hdq\_tx ;transmit command hdq\_error\_flg,hdq\_finish\_error ;if error then jump jb w,hdq mode mov ; w,#11011000b ;turn port to input xor mov !rc,w ; call hdq\_rx ;read data hdq\_error\_flg,hdq\_finish\_error ;if error then jump jb !rc,#11000000b ;done so reinit port (all outputs) mov ret hdq\_write\_byte ;send a break before each communication call hdq break hdq\_buf,hdq\_cmd ;put hdq\_cmd into hdq\_buf mov hdq\_buf.7 ;set for write setb call hdq\_tx ;transmit command jb hdq\_error\_flg,hdq\_finish\_error ;jump if error clr tmr11 ;reset timer tmr1on setb hdq\_write\_byte1 cjb tmr11,#190,hdq\_write\_byte1 ;wait correct time before transmit byte clrb tmr1on hdq\_buf,hdq\_data mov ;transmit byte call hdq tx mov !rc,#11000000b ;reinit port ret hdq\_tx mov count,#8 hdq\_txlp setb do1

hdq\_buf.0 sb clrb do1 hdq\_bit\_out call hdq\_buf rrf decfsz count goto hdq\_txlp retlw 0 ;reciev data routine hdq\_rx ;need to check for stop to start transition here mov count,#8 clr hdq\_data bcf status,0 hdq data hdq rxlp rrf call hdq\_bitin clrb hdq\_data.7 di1 ;skip if not a 1 snb setb hdq data.7 decfsz count goto hdq\_rxlp retlw 0 hdq\_bit\_out clrb tmr1on clr tmr1h tmr11 clr clrb hdq\_d clrb hdq\_d1 mov w,hdq\_mode ;hdq\_d1 = rc.3 ;hdq\_d rc.4 command 52 = xor w,#11011000b !rc,w mov tmrlon setb hdq\_bitout\_init\_start\_wait cjb tmr1l,#14,hdq\_bitout\_init\_start\_wait do1 sb hdq\_bitout\_low goto setb hdq\_d1 hdq\_d setb hdq\_data\_hold goto hdq\_bitout\_low hdq\_d clrb clrb hdq\_d1 hdq\_data\_hold jnb do1,hdq\_data\_hold1 ;if hdq is supposed to be set

mov w,rc and w,hdq mode z, send hdg error ; but its not then there is an error jb hdq\_data\_hold1 cjb tmr11,#107,hdq\_data\_hold ;wait for 110 micro seconds setb hdq d setb hdq\_d1 cje count,#1,hdq\_bit\_out\_end ; if this is last bit then skip the wait to make sure we get the input stop\_bit\_hold mov w,rc and w,hdq\_mode jb z,send\_hdq\_error ; if the stop bit did not go high then there is an error cjb tmr1l,#200,stop\_bit\_hold hdq\_bit\_out\_end clrb tmrlon ret hdq bitin setb di1 mov w,hdq mode xor w,#1100000b mov !rc,w clr tmr11 setb tmr1on hdq\_init\_start\_wait cja tmrll,#250,send\_hdq\_error ; if line stays high greater than 250 micros then there is an error mov w,rc and w,hdq\_mode jnb z,hdq\_init\_start\_wait ;wait for start bit to sync clr tmr11 hdq\_start\_wait cjb tmrll,#12,hdq\_start\_wait ;test at about 12 micro seconds mov w,rc w,hdq\_mode and z,send\_hdq\_error jnb hdq data wait tmr11,#65,hdq\_data\_wait ;test at 65 micro seconds cjb mov w,rc and w,hdq\_mode snb z clrb di1 ;clear data bit hdq\_stop\_wait cjb tmr11,#155,hdq\_stop\_wait mov w,rc and w,hdq\_mode jb z,send\_hdq\_error clrb tmrlon ret

#### TEXAS INSTRUMENTS

hdq\_break

```

;hdq_d1

=

rc.3

rc.4 command 52

;hdq_d

=

this is command 52: hdq_mode,#00010000b so 52 is rc.

;

mov

setb

hdq_d

setb

hdq_d1

mov

w,#11011000b

!rc,w

mov

clrb

hdq_d

clrb

hdq_d1

w,hdq_mode

mov

w,#11011000b

; just make sure that the rs232 lines are enabled

xor

and correct hdq is output while other

!rc,w

is imput

mov

;

hdq d

clrb

clrb

hdq d1

clr

tmr11

setb

tmr1on

hdq_break_low_wait

cjb

tmr11,#220,hdq_break_low_wait

setb

hdq_d

setb

hdq_d1

clr

tmr11

hdq_break_low_wait1

cjb

tmr1l,#60,hdq_break_low_wait1

ret

hdq_finish_error

mov

rc,#00000000b

!rc,#11011000b

mov

ret

send_hdq_error

setb

hdq_error_flg

ret

```

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products         |                        | Applications       |                           |

|------------------|------------------------|--------------------|---------------------------|

| Amplifiers       | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters  | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP              | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface        | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic            | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt       | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers | microcontroller.ti.com | Security           | www.ti.com/security       |

|                  |                        | Telephony          | www.ti.com/telephony      |

|                  |                        | Video & Imaging    | www.ti.com/video          |

|                  |                        | Wireless           | www.ti.com/wireless       |

Mailing Address:

Texas Instruments

Post Office Box 655303 Dallas, Texas 75265

Copyright © 2003, Texas Instruments Incorporated