# Application Note Understanding EN to VCC Start-Up Time and EN Internal Pull-Down Current in TPS56C230 Step-Down Converter

Savith Kumar Rayakanti and Tahar Allag

#### ABSTRACT

Modern computing and processing circuits have multiple power rails and requires a precise power-up sequence. Incorrect power sequencing of these rails can cause serious problems and can lead to system level damages. This application note explains the EN, VCC signals, EN to VCC delay time and EN currents in the TPS56C230 point of load (POL) step-down converter. Detailed plots are also provided in the document to help engineers understand how to use the TPS56C230 in various systems.

# **Table of Contents**

| 1 Introduction                  | <br>2 |

|---------------------------------|-------|

| 2 EN to VCC Start-up Time       | <br>2 |

| 3 EN Internal Pull-down Current |       |

| 4 Summary                       |       |

| 5 References                    |       |

|                                 | <br>1 |

### **List of Figures**

| Figure 1-1. TPS56C230 Typical Application Schematic | . 2 |

|-----------------------------------------------------|-----|

| Figure 2-1. EN to VCC Start-up Delay                | . 2 |

| Figure 3-1. EN Internal Pull-down Current           | 3   |

|                                                     |     |

#### Trademarks

All trademarks are the property of their respective owners.

1

# **1** Introduction

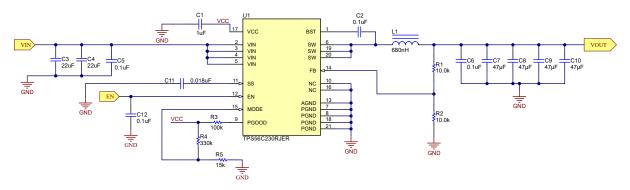

This application note details the EN signal to VCC start-up timing and EN pin internal pull-down current in the TPS56C230 synchronous step-down converter. Figure 1-1 shows the typical application schematic of TPS56C230.

Figure 1-1. TPS56C230 Typical Application Schematic

# 2 EN to VCC Start-up Time

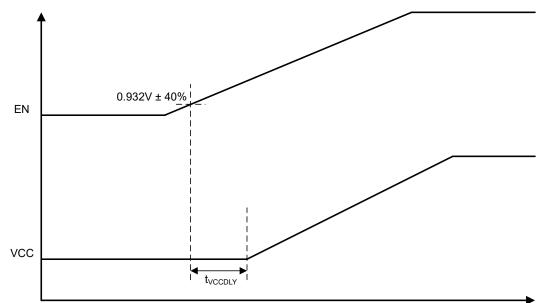

Figure 2-1 below shows the typical timing diagram of VCC rising of the device, once the enable signal crosses 0.932V typical threshold, VCC start rising after  $t_{VCCDLY}$  time. Typical value of  $t_{VCCDLY}$  = 13.5us and can vary from 6.35us to 25.6us.

Figure 2-1. EN to VCC Start-up Delay

# 3 EN Internal Pull-down Current

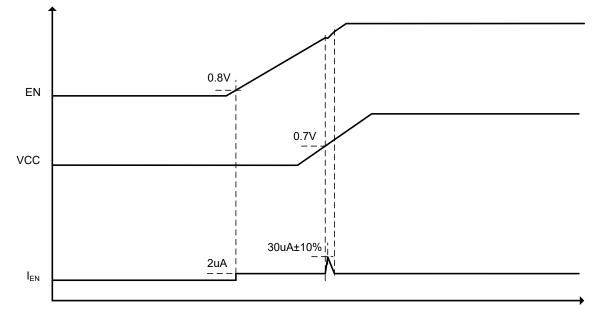

Figure 3-1 below shows the typical EN internal pull down current of the device, once EN  $\ge$  0.8V there is a 2uA EN internal pull down current. If VCC  $\ge$  0.7V and EN-VCC  $\ge$  0.7V, there is an additional momentary 28uA internal pulldown current seen on EN as shown in Figure 3-1 and EN internal pulldown current recovers back to 2uA as EN-VCC < 0.7V. All the voltages and currents shown in Figure 3-1 are typical values.

Figure 3-1. EN Internal Pull-down Current

## 4 Summary

This application note details the important sequencing signals, voltage thresholds, time delays, such as EN to VCC start-up time and EN internal pull-down, and voltage thresholds for sequencing using the TPS56C230. VCC starts rising after  $t_{VCCDLY}$  = 13.5us (typical) delay from EN crossing 0.932V (typical) threshold as detailed in EN to VCC Start-up Time. A 2uA internal pull-down current is seen on EN once EN  $\ge$  0.8V. If VCC  $\ge$  0.7V and EN-VCC  $\ge$  0.7V, then an additional momentary 28uA internal pull-down current is seen on EN. Internal pull-down current recovers to 2uA as EN-VCC < 0.7V, which is detailed in EN Internal Pull-down Current.

# 5 References

- Texas Instruments, TPS56C230 4.5V to 18V, 12A Synchronous Step Down Converter, data sheet

- Texas Instruments, TPS56C230 Buck Converter Evaluation Module User's Guide

- Texas Instruments, Power Supply Sequencing Solutions for Dual Supply Voltage DSPs, application note

- Texas Instruments, Sequencing With TPS54x80 and TPS54x73 SWIFT DC/DC Converters, application note

- Texas Instruments, A Smart Solution to Sequence and Monitor Multiple Power Rails in a System, technical article

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2025, Texas Instruments Incorporated