# How to Properly Evaluate Junction Temperature with Thermal Metrics

Andy Chen

#### **ABSTRACT**

With the technology development of the semiconductor process, the chip integration level continuously increases while the package size gets smaller, so the semiconductor devices face higher thermal stress challenges. The high junction temperature not only derate the device electrical characteristics, but increases the metal migration and other degeneration changes which cause accelerated aging and higher failure rate. According to the electronic design rules, every 10°C rise in temperature reduces the average life by 50%, so it is important to properly evaluate the thermal stress or junction temperature of the semiconductor devices.

|   | Contents                                                                             |    |

|---|--------------------------------------------------------------------------------------|----|

| 1 | Common Thermal Metrics for Junction Temperature Estimation                           | 2  |

| 2 | Why Thermal Resistance Parameters Are Often Misused                                  | 3  |

| 3 | Using The $\psi$ Thermal Characterization Parameter to Estimate Junction Temperature | 7  |

| 4 | About Temperature Measurement                                                        |    |

| 5 | Conclusion                                                                           |    |

| 6 | References                                                                           | 10 |

|   | List of Figures                                                                      |    |

| 1 | Older Device in Metal Can Package                                                    | 3  |

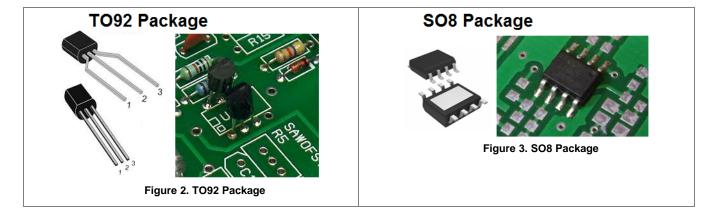

| 2 | TO92 Package                                                                         | 3  |

| 3 | SO8 Package                                                                          | 3  |

| 4 | R <sub>0JA</sub> Vs PCB Size                                                         | 2  |

| 5 | R <sub>UC</sub> Measurement                                                          | 5  |

| 6 | R <sub>UB</sub> Measurement                                                          | 6  |

| 7 | Complex Model                                                                        | 7  |

| 8 | Ψ Versus PCB Size                                                                    | 8  |

|   | List of Tables                                                                       |    |

| 1 | Typical Thermal Metrics                                                              | 2  |

| 2 | Quick Summary                                                                        | 10 |

#### **Trademarks**

# 1 Common Thermal Metrics for Junction Temperature Estimation

Some semiconductor devices are integrated with a dedicated thermal diode precisely measure the junction temperature according to the calibrated forward voltage versus the temperature curve. Since most devices do not have this design, the estimation of the junction temperature depends on the external reference point temperature and the thermal metric of the package. The commonly used package thermal metrics are the thermal resistance and thermal characterization parameter. Table 1 shows the typical thermal metrics of LMR14030, which is a 40-V, 3.5-A step-down converter in the SO8 package with thermal pad.

**Table 1. Typical Thermal Metrics**

| THERMAL METRIC                                                   | LMR14030SDDA | UNIT |

|------------------------------------------------------------------|--------------|------|

| R <sub>eJA</sub> Junction-to-ambient thermal resistance          | 42.5         | °C/W |

| R <sub>eJC (top)</sub> Junction-to-case (top) thermal resistance | 56.1         | °C/W |

| R <sub>eJB</sub> Junction-to-board thermal resistance            | 25.5         | °C/W |

| Ψ <sub>JT</sub> Junction-to-top characterization parameter       | 9.9          | °C/W |

| Ψ <sub>JB</sub> Junction-to-board characterization parameter     | 25.4         | °C/W |

- Thermal resistance parameters, such as R<sub>θJA</sub> and R<sub>θJC</sub>, are the most common thermal metrics, almost all of the semiconductor device specifications provide such information, although it is the most common and misused metrics to the engineers.

- Thermal characterization parameter, such as  $\Psi_{JT}$  and  $\Psi_{JB}$ , are the thermal metrics defined by the Solid State Technology Association (JEDEC) in the 1990s. These metrics are more convenient to estimate the junction temperature of devices in modern package type. More semiconductor manufacturers are providing these thermal metrics.

# 2 Why Thermal Resistance Parameters Are Often Misused

The early generation semiconductor devices are normally packaged in a metal can. Figure 1 shows an example a device in a metal can.

Figure 1. Older Device in Metal Can Package

The device with lead stands on the PCB after assembly, so the device heat is almost completely distributed through the metal case to the air environment. The heat conduction has a single path and less relationship with the PCB, so the thermal resistance parameters  $R_{\theta JA}$  and  $R_{\theta JC}$  are defined on this kind of application conditions. Nowadays, many new packaging types, especially in the SMD packages, have diverse heat conduction paths and more relationship with the PCB design, leading to erroneous results if you continue to simply estimate the junction temperature with the resistance parameter.

$R_{\scriptscriptstyle \theta JA}$  is the thermal resistance of the junction to the environment in still air conditions and is the most common thermal parameter for the semiconductor package. In most cases, the total heat of the device is eventually distributed into the air, so the air temperature is easy to measure or pre-determined and the junction temperature can be easily estimated with  $R_{\scriptscriptstyle \theta JA}$  as long as the power consumption is known.

Figure 2 shows a normal transistor in a TO-92 package that is assembled on a PCB.

The heat is mainly conducted through the package body and has less relationship with the PCB as it stands off the PCB. Using its typical  $R_{\tiny \theta,JA}$ , you can get accurate estimation results of junction temperature based on the ambient temperature (or case temperature) and device power consumption. Figure 3 shows the results from the  $R_{\tiny \theta,JA}$  versus the PCB size. Since the bottom exposed pad of the package is soldered to the PCB, most of the heat is conducted through the PCB. The device and the PCB form a thermal subsystem, then  $R_{\tiny \theta,JA}$  is a system-level thermal resistance parameter. Any PCB design differences, such as board type, size, layer, copper foil thickness, number of vias, and so forth have a significant effect on the final thermal performance.

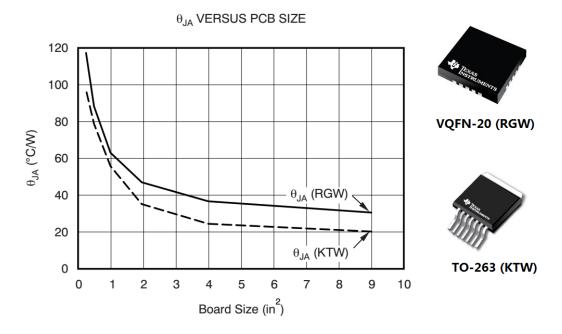

Figure 4. R<sub>0JA</sub> Vs PCB Size

Figure 4 shows the relationship between the  $R_{\theta JA}$  and the PCB size of TI package type TO-263 (KTW) and VQFN-20 (RGW). Figure 4 clearly shows how the board size affects the  $R_{\theta JA}$ .

The  $R_{\theta JA}$  provided on data sheet specification is usually measured or simulated on a standard PCB defined by JEDEC or device vendor. If your PCB design and application environment are similar to the conditions defined by JEDEC or device vendor, then you can use the data sheet  $R_{\theta JA}$  parameter, or use the actual  $R_{\theta JA}$  parameter. These are measured in a previous similar product system to an estimated junction temperature. Otherwise, the difference in the PCB design can result in a large error on junction temperature estimation and a higher estimated junction temperature results in a design constraint. A lower estimated value directly leads to poor reliability.

According to the recommendations of JEDEC, the  $R_{\theta JA}$  parameter is not suitable for estimating junction temperature in actual applications. It is more suitable for comparing the thermal performance of different devices in the same package type, and it must be noted that the comparison is based on a similar PCB design. Never just compare the value.

$R_{\theta JC}$  is defined as the thermal resistance between the junction to the case surface (top or bottom), as defined by JEDEC.

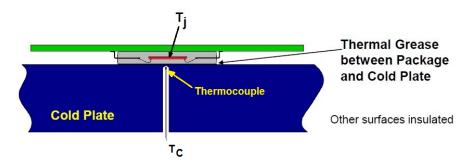

Figure 5. R<sub>e.IC</sub> Measurement

The testing method forces almost all of the dissipated heat through the single surface of the device (case top or bottom of package), so  $R_{\theta JC}$  applies to the condition that the chip dissipated power conducts through the single surface of the device package (case top or bottom). This means that the  $R_{\theta JC}$  parameter is generally suitable for the condition that the only heatsinking is attached at the top (or bottom) of the package where more than 90% of the heat is distributed from the top (or bottom), which is very similar to JEDEC test conditions. For a package with bottom thermal pad, the bottom metal pad is allowed to be soldered onto the PCB, but for the  $R_{\theta JC\text{-top}}$  parameter, it must be ensured that the top is the main path of heat sinking.

For a SMD device in typical plastic package without top heatsinking, it is incorrect to estimate the junction temperature with  $R_{\theta JC}$  by simply measuring the case top temperature and calculated device power dissipation. This can result in a much higher result than the actual junction temperature.

The difficulty of using the  $R_{\theta JC}$  parameter is how to accurately measure the surface temperature of the package attached with the heatsink. The general method is to drill a  $\leq 1$  mm diameter through hole in the central portion of the heatsink where it contacts with the chip package. Insert a thin thermocouple wire and well contact with the package surface to measure the case temperature.

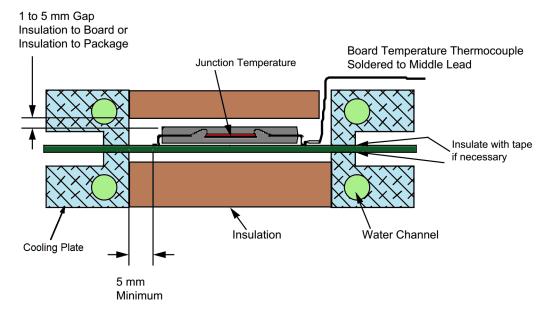

$R_{\theta JB}$  parameter is defined later than the above two parameters.  $R_{\theta JB}$  is defined as the junction to the PCB (NOT package bottom) thermal resistance, which means that the PCB must be the main path of the device heat dissipation. Figure 6 shows the JEDEC test method. It uses the circular cooling plate to clamp PCB top and bottom side. It also uses a thermal insulation material to cover the chip top and bottom position to ensure that almost all of the heat flow to the PCB.

Figure 6. R<sub>BJB</sub> Measurement

The  $R_{\text{OJB}}$  parameter is more suitable for devices in SMD package types to estimate the junction temperature, especially the package bottom that has an exposed thermal pad. Pay attention to the PCB design in an actual application since JEDEC tests  $R_{\text{OJB}}$  with high-thermal conductivity PCB (High-K PCB) with Material FR4, 4 layers, and 1.6 mm thickness. The top layer of the bottom layer of copper foil is 2 oz. The middle two layers of is 1 oz. The board size is normally 11.4-cm x 7.6-cm or 11.4-cm x 10.2-cm. If the PCB design in the actual application is similar or more optimized, then use this parameter to estimate the junction temperature. Sometimes it is not convenient to measure the PCB temperature since the thermalcouple needs to be placed close to the edge of the package in 1 mm space, so the JEDEC defined  $\Psi$  parameters to be more easy to use.

#### 3 Using The ψ Thermal Characterization Parameter to Estimate Junction Temperature

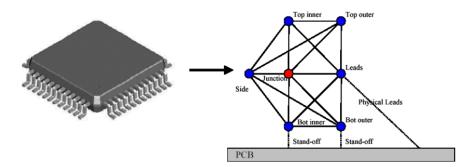

According to the definition of thermal resistance, it is the ratio of the temperature difference and the actual conducted thermal power between the two points. Figure 7 shows that the actual application system has diverse cooling path.

Figure 7. Complex Model

The model is equivalent to a complex series/parallel circuit network since it is difficult to simply calculate or determine the actual thermal power conducted in one certain path. JEDEC tests the thermal resistance in a way that always forces almost all of the device heat flow to the reference point. The simple reason is that it uses the total power consumption of the chip to calculate thermal resistance. The complexity of the thermal conduction path in an actual system determines that junction temperature cannot be simply estimated by the total dissipation power and thermal resistance parameters. For this purpose, JEDEC defines the thermal characterization parameter,  $\Psi$ , which only represents the ratio of the temperature difference (between the junction and reference point ) and the total dissipated power of the chip. It is only a coefficient, although the calculation formula and the units (°C/W) is very similar to  $R_{\theta}$ , but  $\Psi$  is not the true thermal resistance parameters.

Now there are two common thermal characterizations parameters:  $\Psi_{JT}$  for junction to the package top and  $\Psi_{JB}$  for junction to PCB.  $\Psi_{JT}$  is more often used because:

- It is more convenient to measure case top temperature.

- The SMD chip spreads heat mainly through PCB and only a small amount of the heat flows to the top. The temperature difference between the junction to the top is usually smaller than junction to the PCB. In other words,  $\Psi_{JT}$  is smaller than  $\Psi_{JB}$ , so using the  $\Psi_{JT}$  parameter has relatively smaller error. Table 1 shows the quick summary data.

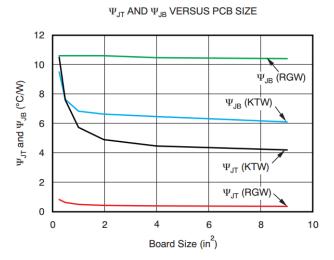

If you compare thermal resistances, one of the key advantages of  $\Psi$  parameter is the smaller dependency to PCB size. Figure 8 shows this relationship. The  $\Psi$  parameter overcomes the  $\theta$  parameter dependency to PCB, so it is more convenient in the thermal design and has more accurate estimation results.

Figure 8. Ψ Versus PCB Size

Note that if the chip is attached to heat-sinking, then  $R_{\theta JC}$  or  $\Psi_{JS}$  (junction to the heat sink) must be used to estimate the junction temperature.

#### 4 About Temperature Measurement

Thermocouple and infrared thermal imager are commonly used for temperature measurement. When a thermocouple measures the temperature, a fine gauge wire (36 to 40 gauge, J or K type wire) must be used to minimize the local cooling from the thermocouple. It must be attached to the center of the package surface (± 1 mm) with a bead of thermally conductive epoxy no larger than 2-mm x 2-mm on a side. Taping the thermocouple to the package surface is not recommended. To minimize the heat sinking impact of the thermocouple, the wire must be dressed along the diagonal of the package, down to the PCB surface, and over a minimum distance of 25 mm before lifting from the PCB. The thermocouple wire can be tacked to the PCB for this routing purpose with tape. Use of improper thermocouple wire gauge can create errors in the measurements of 5-50%.

Temperature measurement with an infrared thermal imager is simple, convenient, fast, and accurate. Depending on the ambient temperature or test environment changes, the machine requires a sufficient preheat stability time before the test. Be sure to correct the reading for the emissivity of the surface being investigated. Choose a high emissivity surface (non-metal, rough, low reflective) on the measured object as a test point. For low emissivity surfaces, apply black insulating tape, spray paint, or apply it with a black water-based stylus pen. Test it vertically at the top of the test point where the test area is well-focused and filled with full display windows.

Regarding air ambient temperature measurement, the PCB must be placed horizontally. Measure the air temp at point 2.54 cm underneath the PCB center and 2.54 cm to the horizontal side. Take the average temperature of two points.

Regarding the PCB temperature testing point, choose the middle position of package side closest to the inside chip. Measure the board temp within 1 mm to the edge of the package, or at the test point recommended by the device vendor. It is best to choose a point where the copper foil is routed and connected to the package. Scratch the solder mask before measurement. For practical operation with a leaded package device, select the center pin on the package long side, measuring temperature at the lead end that is soldered to PCB. If the pin solder pad space to the package edge is larger than 1.5 mm, directly measure the temperature on the board as described above.

Conclusion www.ti.com

#### 5 Conclusion

The theory of thermal is correct. The thermal resistance parameter can be used to estimate the temperature difference if the heat conduction path and the thermal power conducted between the two points of the system is clear. In actual applications, the thermal conduction path is diverse, and the heat spreads through multiple channels. Unlike the total power consumption, it is difficult to estimate the power consumption of a particular path. For these reasons, the thermal characterization parameter  $\Psi$  is more suitable for estimating the junction temperature. Table 2 shows a summary.

**Table 2. Quick Summary**

| THERMAL<br>METRIC                 | TYPE                               | USAGE FORMULA                                | REMARK                                                                                                                                                                                              |

|-----------------------------------|------------------------------------|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $R_{\scriptscriptstyle{	hetaJA}}$ | Thermal Resistance                 | $T_{J} = T_{A} + R_{\theta JA} \times P_{T}$ | <ol> <li>P<sub>T</sub> is the total chip dissipated power</li> <li>Used to rank package thermal performance</li> </ol>                                                                              |

| R <sub>eJC</sub>                  | Thermal Resistance                 | $T_{J} = T_{C} + R_{\theta JC} \times P_{D}$ | <ol> <li>P<sub>D</sub> is the thermal power conducted from junction to case (top or bottom) surface</li> <li>Used to rank package thermal performance</li> </ol>                                    |

| $R_{	heta JB}$                    | Thermal Resistance                 | $T_{J} = T_{B} + R_{\theta JB} \times P_{D}$ | <ol> <li>P<sub>D</sub> is the thermal power conducted from junction to board.</li> <li>Used to rank package thermal performance and estimate T<sub>J</sub> of devices on application PCB</li> </ol> |

| $\Psi_{JT}$                       | Thermal Characterization Parameter | $T_{J} = T_{C-top} + \Psi_{JT} \times P_{T}$ | <ol> <li>P<sub>T</sub> is the total chip dissipated power</li> <li>Used to estimate T<sub>J</sub> of devices on application PCB</li> </ol>                                                          |

| $\Psi_{JB}$                       | Thermal Characterization Parameter | $T_{J} = T_{B} + \Psi_{JB} \times P_{T}$     | <ol> <li>P<sub>T</sub> is the total chip dissipated power</li> <li>Used to estimate T<sub>J</sub> of devices on application PCB</li> </ol>                                                          |

#### 6 References

- 1. Darvin Edwards, Semiconductor and IC Package Thermal Metrics

- 2. Masashi Nogawa, Using New Thermal Metrics.

- 3. JESD51-1, Integrated Circuits Thermal Measurement Method Electrical Test Method

- 4. JESD51-2, Integrated Circuits Thermal Test Method Environmental Conditions Natural Convection

- 5. JESD51-5, Extension of Thermal Test Board Standards for Packages with Direct Thermal Attachment Mechanisms

- 6. JESD51-12, Guidelines for Reporting and Using Electronic Package Thermal Information

www.ti.com Revision History

# **Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Changes from A Revision (March 2018) to B Revision  |      |  |

|-----------------------------------------------------|------|--|

| Edited application report for clarity.              | 1    |  |

|                                                     |      |  |

| Changes from Original (December 2017) to A Revision | Page |  |

| Changed Typical Thermal Metrics table               | 2    |  |

### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated