# Biasing GaN and LDMOS RF Power Amplifiers in Aerospace Applications Using AFE11612-SEP

#### Erin Bowrie

#### **ABSTRACT**

This application note details the basic functions and benefits of the AFE11612-SEP in voltage biasing for radio frequency power amplifiers in space-rated applications. This report reviews the fundamentals of power amplifier biasing and supporting circuitry.

#### **Table of Contents**

| 1 LDMOS and GaN Power Amplifier FET PA Basics                                                       | 2              |

|-----------------------------------------------------------------------------------------------------|----------------|

| 2 V <sub>GS</sub> Compensation                                                                      |                |

| 3 Sequencing                                                                                        | 4              |

| 4 An Integrated PA Biasing Solution                                                                 |                |

| 5 Negative Biasing for GaN PAs                                                                      |                |

| 6 Fast Switching for TDD Applications                                                               |                |

| 7 V <sub>DRAIN</sub> Switching Circuit                                                              |                |

| 8 Controlled Gate-Sequencing Circuit                                                                |                |

| 9 V <sub>DRAIN</sub> Monitoring                                                                     |                |

| 10 External Negative Power Supply Monitoring                                                        |                |

| 11 PA Temperature Monitoring                                                                        |                |

| 12 Summary                                                                                          |                |

| 13 References                                                                                       | 11             |

| 14 Revision History                                                                                 | 12             |

|                                                                                                     |                |

| List of Figures                                                                                     |                |

| Figure 1-1. GaN and LDMOS FETs                                                                      | 2              |

| Figure 1-2. FET V <sub>DRAIN</sub> , I <sub>DS</sub> , and V <sub>GS</sub> Behavior                 | 2              |

| Figure 2-1. GaN PA V <sub>GS</sub> Bias Voltage vs Temperature to maintain constant I <sub>DS</sub> | 3              |

| Figure 3-1. GaN Power Sequencing                                                                    | 4              |

| Figure 4-1. AFE11612-SEP Typical Application                                                        | 5              |

| Figure 5-1. Differential Operational Amplifier Circuit                                              | 5              |

| Figure 5-2. Differential Operational Amplifier Output                                               | 6              |

| Figure 6-1. Gate Switching Circuit                                                                  | <mark>7</mark> |

| Figure 7-1. V <sub>DRAIN</sub> Enable Circuit                                                       | <mark>7</mark> |

| Figure 7-2. V <sub>DRAIN</sub> Enable Plot                                                          | <mark>7</mark> |

| Figure 8-1. PA_ON AND Gate                                                                          |                |

| Figure 8-2. PA_ON Power Sequence Control                                                            |                |

| Figure 9-1. V <sub>DRAIN</sub> Monitor Circuit                                                      | <u>9</u>       |

| Figure 10-1. V <sub>SS</sub> Monitor Circuit                                                        |                |

| Figure 11-1. Remote Temperature Circuit                                                             | 10             |

| List of Tables                                                                                      |                |

| List of Tables  Table 8-1. PA ON Truth Table                                                        | o              |

| <del>-</del>                                                                                        |                |

| Table 12-1. Device Recommendations                                                                  | 10             |

| Trademarks                                                                                          |                |

|                                                                                                     |                |

All trademarks are the property of their respective owners.

#### 1 LDMOS and GaN Power Amplifier FET PA Basics

Most radio frequency (RF) antenna systems feature power amplifiers (PA) for their RF transmitter design. Many aerospace and space applications include antenna systems, such as:

- Radar

- · Radar Imaging Payload

- · Communications Payload

- Telemetry

PA biasing circuits are implemented in RF antenna systems to ensure two things. First, that the power output of the amplifier is known and controlled, and second, that the system is powered on and off safely to reduce the risk of damaging the PA. PAs are commonly designed with gallium nitride (GaN), gallium arsenide (GaAs), or laterally diffused MOSFET (LDMOS) transistors. Power output in both GaN and LDMOS FETs (field-effect transistors) is dependent on the current that flows through the device from the drain to the source (I<sub>DS</sub>).

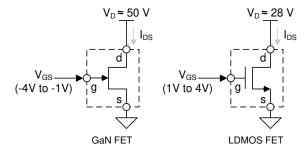

Figure 1-1. GaN and LDMOS FETs

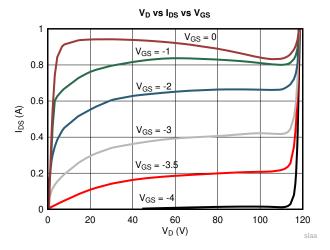

$I_{DS}$  is determined by a few variables: the drain voltage ( $V_{DRAIN}$ ), the gate voltage ( $V_{GS}$ ), and temperature. Figure 1-2 shows an example of  $I_{DS}$  values against the  $V_{DRAIN}$  for a selection of  $V_{GS}$  voltages for a GaN PA. The higher  $V_{GS}$  voltages result in a higher  $I_{DS}$ , or more power from the amplifier. When  $V_{GS}$  is sufficiently low, the PA allows virtually zero  $I_{DS}$  current. This  $V_{GS}$  voltage is called the *pinch-off* voltage.  $I_{DS}$  is also dependent on the  $V_{DRAIN}$ , but most designers do not vary the  $V_{DRAIN}$ . Instead, designers use optimized  $V_{DRAIN}$  voltages for the desired power levels. The  $V_{DRAIN}$  values are usually about 50 V for GaN PAs and 28 V for LDMOS PAs.

Figure 1-2. FET V<sub>DRAIN</sub>, I<sub>DS</sub>, and V<sub>GS</sub> Behavior

www.ti.com V<sub>GS</sub> Compensation

# 2 V<sub>GS</sub> Compensation

$I_{DS}$  is dependent on the temperature of the PA. The  $I_{DS}$  variations due to thermal drift create the need to compensate the PA by adjusting one of the other two variables in the system:  $V_{DRAIN}$  or  $V_{GS}$ . Although there are many reasons why adjusting  $V_{DRAIN}$  is implemented in different RF applications, the response of the output power is minimal compared to the change in the  $V_{DRAIN}$  voltage, as shown in Figure 1-2. Adjusting  $V_{GS}$  allows for faster response time and total amplitude of the output power making it more practical for temperature compensation and other applications.

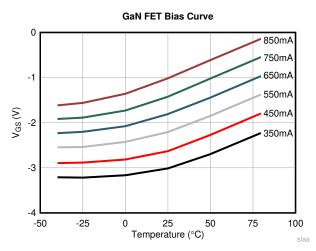

Figure 2-1. GaN PA V<sub>GS</sub> Bias Voltage vs Temperature to maintain constant I<sub>DS</sub>

Figure 2-1 shows  $V_{GS}$  needs to be adjusted to ensure a static  $I_{DS}$  due to thermal drift. Applications utilizing these PAs require implementing this kind of compensation to ensure that the power of the antenna system is tightly controlled.  $V_{GS}$  compensation can be implemented by either measuring the temperature of the PA, or measuring the  $I_{DS}$  using a current shunt and adjusting the  $V_{GS}$  accordingly.

Sequencing Www.ti.com

#### 3 Sequencing

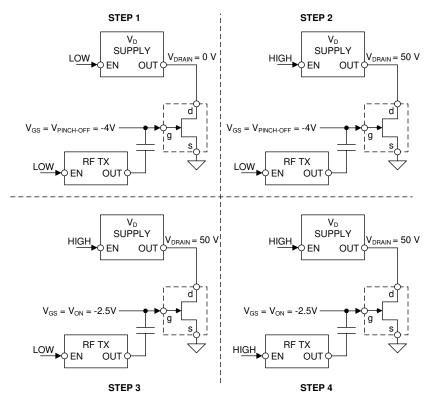

Powering the PA on and off in a controlled routine is necessary to prevent the  $V_{GS}$  voltage from being too high when the  $V_{DRAIN}$  is applied. Such a state causes the PA to operate in saturation mode which may result in thermal damage in the PA or the board it is mounted on. Powering on a PA requires the following steps:

- 1. First, apply the  $V_{GS}$  signal to the PA. The  $V_{GS}$  voltage must transition to the  $V_{GS}$  pinch-off voltage or lower. This ensures that when the  $V_{DRAIN}$  voltage is applied, the gate is already low.

- 2. Next, enable the drain voltage supply and allow the  $V_{DRAIN}$  to be powered to the nominal value (50 V, for example). As the  $V_{GS}$  is at the pinch-off voltage,  $I_{DS}$  must be minimal.

- 3. After the V<sub>DRAIN</sub> is applied, increase the V<sub>GS</sub> bias voltage to set the desired power output of the PA.

- 4. Finally, enable the RF signal. This allows the PA to transmit a signal.

Figure 3-1. GaN Power Sequencing

The PA can be safely shut down by reversing the power-on steps.

- 1. Disable the RF signal from the PA.

- 2. Reduce the V<sub>GS</sub> voltage to the pinch-off value, eliminating the power output of the PA.

- 3. Disable the  $V_{DRAIN}$  voltage by sending a disable signal to the drain supply.

- 4. Finally, the V<sub>GS</sub> voltage can be allowed to collapse to ground as the PA is fully disabled.

#### 4 An Integrated PA Biasing Solution

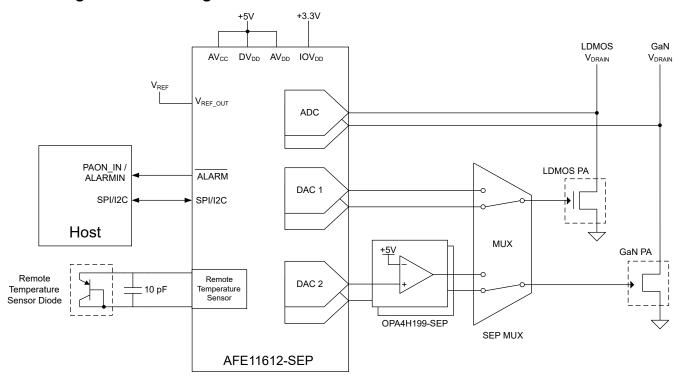

Figure 4-1. AFE11612-SEP Typical Application

The AFE11612-SEP is an integrated power-amplifier biasing solution that features twelve 12-bit precision Digital-to-Analog Converters (DACs), a sixteen-input 12-bit Analog-to-Digital Converter (ADC), and two pairs of remote temperature sensor inputs. The DAC outputs enable  $V_{\rm GS}$  control of up to twelve LDMOS PAs. GaN PAs can be supported with additional circuitry. The device also features robust PA monitoring and protection with programmable thresholds for the two remote temperature sensors and four of the ADC inputs.

## **5 Negative Biasing for GaN PAs**

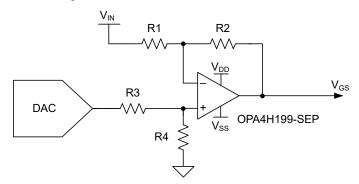

The AFE11612-SEP has an internal 2.5V reference that scales the DAC output range from 0V to 5V. GaN PAs require negative gate voltage to be properly biased, with pinch-off voltages being more negative than the on voltages. The DAC output can be shifted to a negative voltage through the use of a differential op-amp circuit. The circuit example in Figure 5-1 uses the radiation hardened op-amp OPA4H199-SEP to offset and scale the DAC output to the negative range. A differential op-amp circuit is used to protect the PA in case of an alarm shutdown. In an alarm state, the DAC drives the voltage to 0V. The differential circuit outputs the most negative voltage to the GaN gate, thus ensuring the GaN PA turns off.

Figure 5-1. Differential Operational Amplifier Circuit

Resistor values are chosen based on the desired op-amp output, V<sub>IN</sub>, and DAC range. The following equations provide a guideline for selecting the resistor values:

$$V_{GS} = -\left(V_{IN} \times \frac{R2}{R1}\right) + DAC \times \left(\frac{R4}{R4 + R3}\right) \times \left(\frac{R1 + R2}{R1}\right) \tag{1}$$

When DAC = 0V:

$$V_{GS}(MIN) = -\left(V_{IN} \times \frac{R2}{R1}\right) \tag{2}$$

$V_{GS}(MIN)$  is selected to be -7.5V, and  $V_{IN}$  is selected to be 5V.

$$-7.5V = -\left(5 \times \frac{R2}{R1}\right) \tag{3}$$

$$\frac{R2}{R1} = 1.5\tag{4}$$

Select R2 and R1 values in accordance with this ratio. In this example, R1 =  $10k\Omega$  and R2 =  $15k\Omega$ . To calculate R3 and R4, use the maximum desired DAC value and  $V_{GS}$  value. In this example, DAC = 5V, and  $V_{GS}(MAX)$  = 0V.

$$V_{GS}(MAX) = -\left(V_{IN} \times \frac{R2}{R1}\right) + DAC \times \left(\frac{R4}{R4 + R3}\right) \left(\frac{R1 + R2}{R1}\right)$$

(5)

$$0 = -\left(5 \times \frac{15k}{10k}\right) + 5 \times \left(\frac{R4}{R4 + R3}\right) \times \left(\frac{10k + 15k}{10k}\right) \tag{6}$$

$$7.5 = 12.5 \times \left(\frac{R4}{R4 + R3}\right) \tag{7}$$

Reducing the equation gives the resistor ratio in Equation 8.

$$\frac{R4}{R3} = 1.5$$

(8)

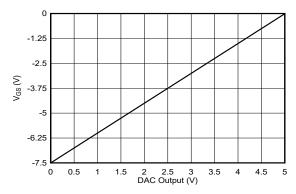

Since this is the same ratio as R2/R1, the same values will be used for R3 and R4 : R3 =  $10k\Omega$  and R4 =  $15k\Omega$ . Figure 5-2 shows the DAC vs V<sub>GS</sub> output with these resistor values.

Figure 5-2. Differential Operational Amplifier Output

# **6 Fast Switching for TDD Applications**

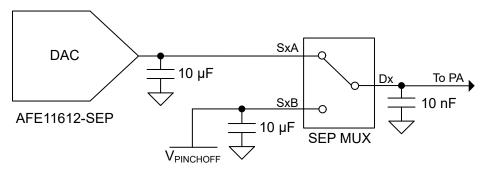

Some PA biasing applications such as time division duplexing require fast on-off gate switching. Fast gate switching is achieved by using the a low resistance space-rated MUX and capacitive charge sharing.

Capacitive charge sharing is used to achieve fast output switching. Figure 6-1 shows suggested capacitance of input and output capacitors. The two input voltages have large capacitors, an the output must have a small capacitor. When the MUX switches, the input capacitor quickly charges the smaller output capacitor, giving the required fast switching.

Figure 6-1. Gate Switching Circuit

# 7 V<sub>DRAIN</sub> Switching Circuit

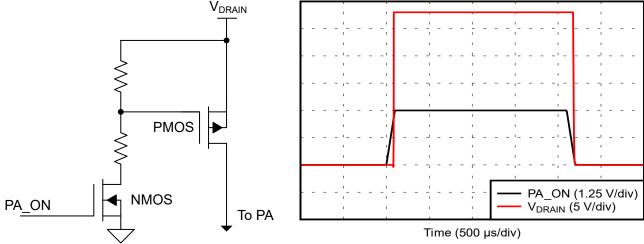

The  $V_{DRAIN}$  protection circuit uses NMOS and PMOS transistors to disable the voltage being applied to the PA drain. This PA\_ON circuit functions as a high-voltage switch. The  $V_{DRAIN}$  needs to be disabled at key times during startup, shutdown, and alarm events. This is achieved in this design by an NMOS and PMOS circuit. When the PA\_ON voltage is applied to the NMOS gate, the circuit turns on to allow  $V_{DRAIN}$  through the PMOS.

Figure 7-1. V<sub>DRAIN</sub> Enable Circuit

Figure 7-2. V<sub>DRAIN</sub> Enable Plot

# 8 Controlled Gate-Sequencing Circuit

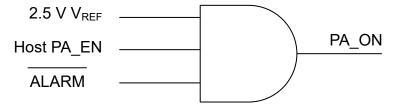

There is importance to control the PA during start-up, shutdown, and alarm conditions, to make sure that the PA is not damaged during these events. This is accomplished by creating a three input logic AND gate of key signals:  $V_{REE}$  HOST PA\_EN, and  $\overline{ALARM}$ .

Figure 8-1. PA ON AND Gate

$V_{REF}$  is used as the *device good* signal for the PA\_ON output. This makes sure that the PA never has the drain voltage applied at start-up, as the  $V_{REF}$  must be enabled by the host controller after the AFE11612-SEP starts up. The  $\overline{ALARM}$  signal from the AFE11612-SEP circuit can force the PA\_ON to 0 V if the AFE11612-SEP detects any alarms. Finally, the host micro controller has the option of turning off PA\_ON. Table 8-1 shows how all of the digital outputs interact with the PA\_ON.

| Table 6-1: 1 A_ON Tradit |       |       |       |  |  |

|--------------------------|-------|-------|-------|--|--|

| VREF                     | PA_EN | ALARM | PA_ON |  |  |

| 0V                       | X     | X     | Low   |  |  |

| Х                        | 0V    | X     | Low   |  |  |

| Х                        | X     | 0V    | Low   |  |  |

| 2.5V                     | High  | High  | High  |  |  |

Table 8-1. PA ON Truth Table

Here is an example of the PA\_ON power on sequence:

- 1. The AFE11612-SEP is initialized. The host sends the command to turn on the V<sub>REF</sub>. With no alarm state at startup, the ALARM pin is High-Z. The host keeps PA\_EN Low to keep the PA off.

- 2. Next, the drain power is turned on. The host sets PA\_EN High, enabling the PA\_ON signal.

- 3. Third, an alarm condition is shown. The ALARM goes to 0V, turning off the PA\_ON and thus turning off the PA to protect the PA.

- 4. Fourth, the alarm condition is cleared. ALARM returns to High-Z, and the PA\_ON is on.

- 5. Lastly, before the part powers off, disable PA EN to turn off the PA ON. Power down the AFE11612-SEP.

Figure 8-2. PA\_ON Power Sequence Control

www.ti.com V<sub>DRAIN</sub> Monitoring

# 9 V<sub>DRAIN</sub> Monitoring

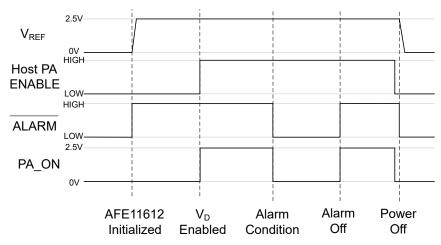

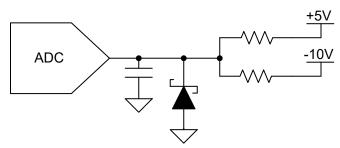

It is important to monitor the  $V_{DRAIN}$  voltage to ensure the PA Drain supply is operating at the expected voltage. This can be accomplished using the ADC in the AFE11612-SEP. A resistor divider is required to properly scale the  $V_{DRAIN}$  voltage to the 5V ADC range. The impedance of the resistor divider must be limited, ideally under  $10k\Omega$ , to allow sufficient current to charge the sampling capacitor. An external capacitor ( $C_{FILT}$ ) of approximately 1nF is required to quickly charge the ADC sampling capacitor.

Figure 9-1. V<sub>DRAIN</sub> Monitor Circuit

# 10 External Negative Power Supply Monitoring

GaN PAs can be damaged if the  $V_{GS}$  potential is too high, resulting in PA saturation. If the  $V_{SS}$  supply collapses the differential op-amp output will slew to 0V. Thus, it is critical to monitor the  $V_{SS}$  supply for collapse events. Monitoring can be done using a simple resistor divider biased by an external reference voltage, such as the 5V used for the device analog supply. A zener diode can be added for additional protection in case of the external 5V supply collapsing.

Figure 10-1. V<sub>SS</sub> Monitor Circuit

PA Temperature Monitoring www.ti.com

# 11 PA Temperature Monitoring

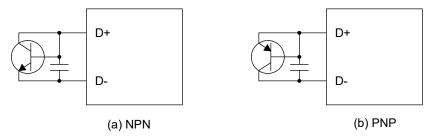

The AFE11612-SEP has two sets of remote temperature sensor inputs that can be used to monitor the temperature of two diode-connected transistors placed near the PAs. The two temperature sensors have programmable alarm thresholds that can trigger an alarm state and disable the DAC outputs.

Figure 11-1. Remote Temperature Circuit

## 12 Summary

Power amplifier behavioral nuances make discrete  $V_{GS}$  compensation solutions complex and costly. The AFE11612-SEP simplifies the solution while adding beneficial features, such as gate monitoring,  $V_{DRAIN}$  monitoring, temperature monitoring, and supply collapse detection for start-up and shutdown sequence control, to make the device an excellent value.

**Table 12-1. Device Recommendations**

| Device       | Optimized Parameters                                          | Total lonizing Dose (TID)<br>Characterized | Single Event Latch-Up (SEL)<br>Characterized  |

|--------------|---------------------------------------------------------------|--------------------------------------------|-----------------------------------------------|

| AFE11612-SEP | Space enhanced 12 12-bit DACs with 16 12-bit ADC inputs.      | 20 krad(SI)                                | Immune to 43 MeV-cm <sup>2</sup> /mg at 125°C |

|              | Space enhanced high voltage quadoutput operational amplifier. | 30 krad(SI)                                | Immune to 43 MeV-cm2 /mg at 125°C             |

www.ti.com References

#### 13 References

• Texas Instruments, AFE11612-SEP Radiation-Tolerant, Analog Monitor and Controller With Multichannel ADC, DACs, and Temperature Sensors, data sheet.

- Texas Instruments, OPA4H199-SEP 40-V, Radiation Hardened, Rail-to-Rail Input/Output, Low Offset Voltage, Low Noise Op Amp in Space Enhanced Plastic

- Texas Instruments, Temperature Compensation of Power Amplifier FET Bias Voltages, application note.

Revision History Www.ti.com

# **14 Revision History**

| CI | hanges from Revision * (June 2023) to Revision A (September 2025)                              | Page |

|----|------------------------------------------------------------------------------------------------|------|

| •  | Updated the numbering format for tables, figures, and cross-references throughout the document |      |

| •  | Removed references to unreleased products                                                      |      |

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2025. Texas Instruments Incorporated