## How Far, How Fast Can You Operate LVDS Drivers and Receivers?

## TEXAS INSTRUMENTS

Low Voltage Differential Signaling (LVDS) connects a driver and a receiver together with a closely coupled differential pair that is terminated with a 100  $\Omega$  resistor as shown in Figure 1. The simple termination, low power, and low noise generation generally makes LVDS the technology of choice for reducing noise in many applications. In this technical note, we discuss performance in maximum data rates and distances connecting LVDS drivers and receivers together.

**Figure 1. LVDS Typical Application**

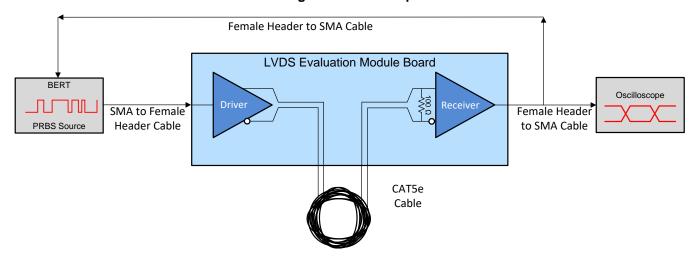

The test setup shown in Figure 3 connects a pseudorandom binary sequence (PRBS) source with LVDS Evaluation Module Boards (EVM) to an oscilloscope. The LVDS EVMs used in this experiment are DS90LV011-12A (1 channel), SN65LVDS31-33 (4 channel, wide common input mode), and DS90LV047-48A (4 channel). The tests were conducted at the following cable lengths: 1m, 5m, 10m, 50m, and 100m and each Cat5e cable was modified with female headers to connect to the male headers on the EVM boards. A Bit Error Rate Tester (BERT) generates a 2<sup>31</sup>-1 PRBS pattern, sends it through the system and loops back to the analyzer, which compares the generated signal. If the pattern matches, the system is said to have no errors. The error margin to not be surpassed in this lab experiment was 1 x 10<sup>-12</sup> for the bit error rate.

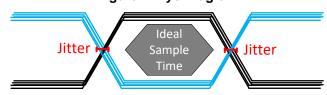

The signal passing through the driver and receiver is connected to an oscilloscope to be observed as an eye diagram. Eye diagrams are made when a signal is repeatedly sampled over itself and is used to measure jitter. Jitter is the measured "error" in time difference of when a system cannot tell the difference between a high or a low bit. It is measured at the crossing point of the bits in an eye diagram as shown in Figure 2.

Figure 2. Eye Diagram

This document focuses on jitter percentage and what maximum percentage can be achieved in a potentially error free environment. Jitter percentage is the measured jitter in a given period, as shown in the example below.

$$Jitter (\%) = \frac{Measured Jitter (s)}{Period (s)} \times 100\%$$

$$= \frac{290 ps}{2.5 ns} \times 100\% = 11.6\%$$

Figure 3. Test Setup

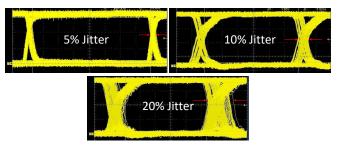

Jitter percentage is valuable when seeing what percentage of the eye will be open, providing a window of bit time to correctly sample the signal. To have a better understanding of jitter, Figure 4 shows examples of what 5%, 10%, 20% jitter can look like. Up to 20% jitter, the signal should be clean enough to get readings with no errors. Above 20% it is not guaranteed that the signal will be error free; however, higher jitter percentages were shown to be below the error margin of 1 x 10<sup>-12</sup> bit error rate using the BERT.

Figure 4. Example of 5%, 10%, and 20% Jitter

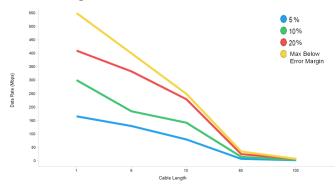

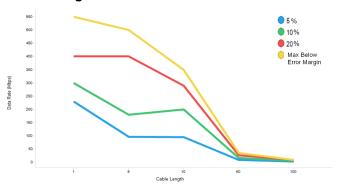

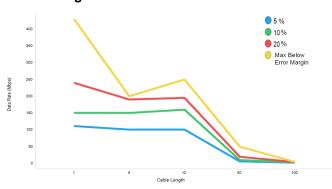

All of the parts chosen for this experiment (DS90LV011A, DS90LV012A, SN65LVDS31, SN65LVDS33, DS90LV047A, DS90LV048A) have data sheet specifications of being able to achieve signaling rates up to 400 Mbps. As you can see, in Figure 5, Figure 6, and Figure 7, all devices meet and exceed the specified up to 400 Mbps signaling rates from the data sheets.

Figure 5. DS90LV011-12A Results

For a one channel application, the DS90LV011-12A EVM allows for data rates as high as 500 Mbps for short distances and for longer distances, like 50m, can operate around 50 Mbps.

Figure 6. DS90LV047-48A Results

For a four channel application, the DS90LV047-48A EVM provides higher than the data sheet specified signaling rate of 400 Mbps for cable lengths up to 5m.

Figure 7. SN65LVDS31-33 Results

For an application that requires wide common mode input range, the SN65LVDS31-33 EVM allows for data rates as high as 400 Mbps at short distances and for longer distances, like 50m, can also operate around 50 Mbps.

Table 1. Final Results (1)(2)

| Jitter | 5%  |     |     | 10% |     |     | 20% |     |     | Max Below Error Margin |     |     |

|--------|-----|-----|-----|-----|-----|-----|-----|-----|-----|------------------------|-----|-----|

| EVM    | 48  | 33  | 12  | 48  | 33  | 12  | 48  | 33  | 12  | 48                     | 33  | 12  |

| 1m     | 230 | 111 | 166 | 300 | 150 | 300 | 400 | 240 | 410 | 550                    | 430 | 550 |

| 5m     | 98  | 100 | 130 | 180 | 150 | 185 | 400 | 190 | 333 | 500                    | 200 | 400 |

| 10m    | 95  | 100 | 885 | 200 | 160 | 142 | 300 | 195 | 230 | 350                    | 250 | 250 |

| 50m    | 9   | 6   | 8   | 17  | 10  | 15  | 27  | 20  | 25  | 35                     | 50  | 35  |

| 100m   | 3   | 2   | 2.5 | 5   | 3   | 4   | 9   | 4   | 7   | 9                      | 4   | 7   |

<sup>(1)</sup> All data values are in Mbps.

<sup>(2) &#</sup>x27;48' is representative of the DS90LV047-48A EVM; '33' is representative of the SN65LVDS31-33 EVM; '12' is representative of the DS90LV011-12A EVM

## IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ('TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications that include TI products, you will thoroughly test such applications and the functionality of such TI products as used in such applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your non-compliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/sampterms.htm">http://www.ti.com/sc/docs/sampterms.htm</a>).

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2018, Texas Instruments Incorporated