# Interfacing the TLV1562 Parallel AD-Converter to the TMS320C54x DSP

# Application Report

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1999, Texas Instruments Incorporated

# **Contents**

| 1 | Introd                                 | uction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 1                                                      |

|---|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| 2 | 2.1<br>2.2<br>2.3                      | TMS320C54x Starter Kit TLV1562EVM ADC TLV1562 Overview 2.3.1 Suggestions for the 'C54x to TLV1562 Interface 2.3.2 Recyclic Architecture 2.3.3 Note on the Interface, Using an External ADC Clock Drive Onboard Components 2.4.1 TLC5618 – Serial DAC 2.4.2 TLV5651 – Parallel DAC                                                                                                                                                                                                      | . 1                                                      |

| 3 | 3.1<br>3.2                             | Reference Voltage Inputs Input Data Bits Connections Between the DSP and the EVM 3.3.1 Jumpers Used on the TLV1562EVM                                                                                                                                                                                                                                                                                                                                                                  | . 6                                                      |

| 4 | The S                                  | erial DAC/DSP System                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 9                                                      |

| 5 | The D                                  | SP Serial Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 10                                                       |

| 6 | Other                                  | DSP/TLV1562 Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 11                                                       |

| • | 6.1                                    | DSP Internal Serial Port Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                          |

| 7 | 7.1<br>7.2<br>7.3<br>7.4<br>7.5<br>7.6 | Writing to the ADC  Mono Interrupt Driven Mode Using RD  Mono Interrupt Driven Mode Using CSTART  Dual Interrupt Driven Mode  Mono Continuous Mode  Dual Continuous Mode                                                                                                                                                                                                                                                                                                               | 12<br>12<br>14<br>15<br>16<br>17                         |

| 8 | 8.1<br>8.2<br>8.3                      | Software Development tools DSP Memory Map Programming Strategies for the 'C54x, Explanations 8.3.1 Optimizing CPU Resources for Maximum Data Rates 8.3.2 Address and Data Bus for I/O Tasks 8.3.3 Timer Output 8.3.4 Data Page Pointer 8.3.5 Generating the Chip Select Signal and the CSTART Signal 8.3.6 Interfacing the Serial DAC 5618 to the DSP 8.3.7 Interrupt Latency 8.3.8 Branch Optimization (goto/dgoto, call/dcall,) 8.3.9 Enabling Software Modules (.if/.elseif/.endif) | 18<br>20<br>20<br>20<br>21<br>21<br>21<br>22<br>22<br>23 |

|   | 8.4                                    | Software Code Explanation                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                          |

|   | 8.5                                    | Flow Charts and Comments for All Software Modes                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                          |

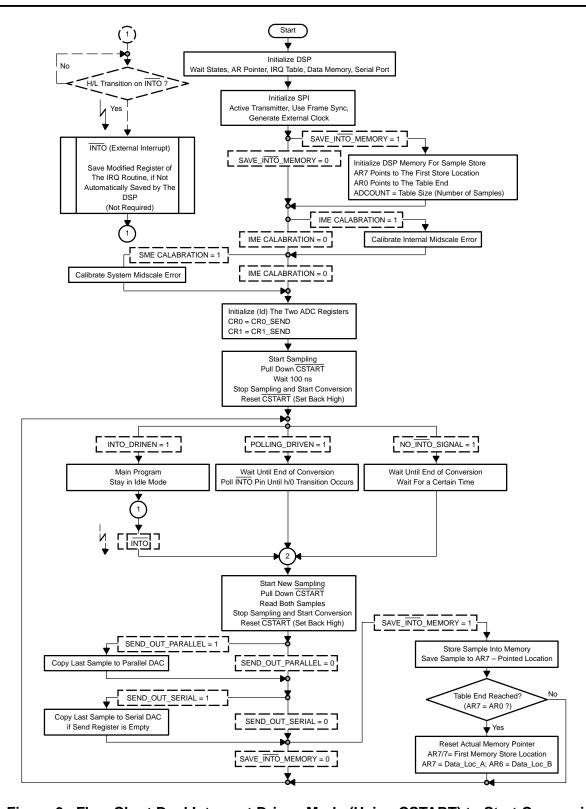

|   | 0.0                                    | 8.5.1 The Mono Interrupt Driven Mode Using RD to Start Conversion                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                          |

|   |                                        | 8.5.2 Mono Interrupt Driven Mode Using CSTART to Start Conversion                                                                                                                                                                                                                                                                                                                                                                                                                      | 30                                                       |

|   |                                        | 8.5.3 Dual Interrupt Driven Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                          |

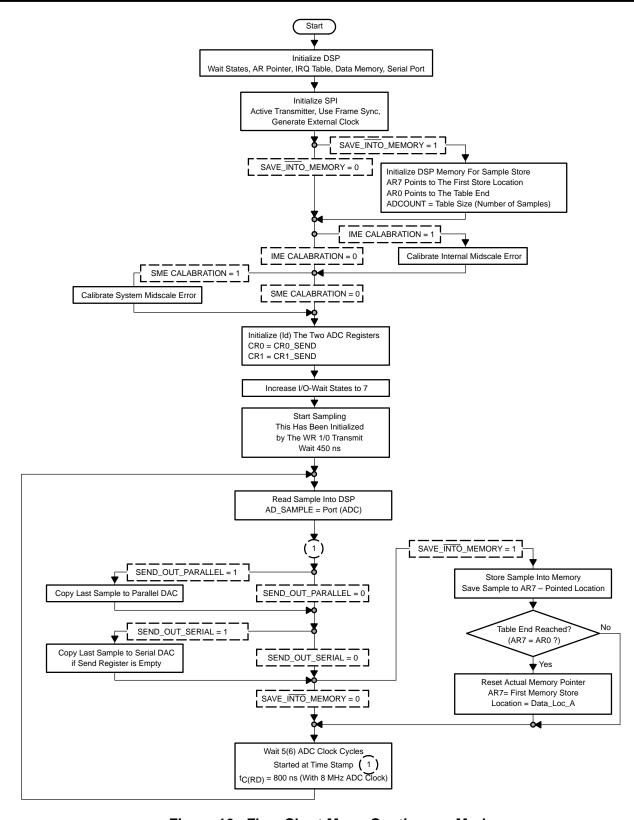

|   |                                        | 8.5.4 Mono Continuous Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 36                                                       |

# Contents

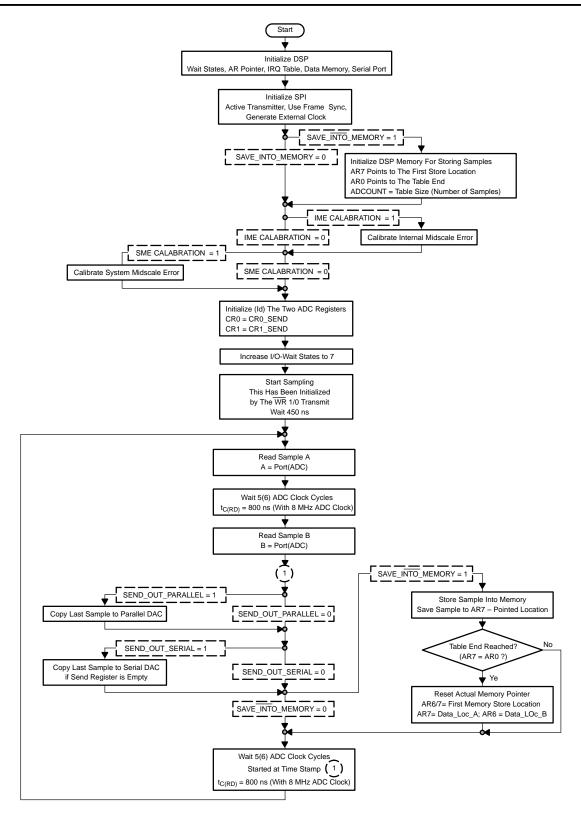

|    |       | 8.5.5  | Dual Continuous Mode                                                        | 38 |

|----|-------|--------|-----------------------------------------------------------------------------|----|

|    |       |        | C-Callable With Mono Interrupt Driven Mode Using CSTART to Start Conversion |    |

|    | 8.6   | Source | Code                                                                        | 41 |

|    |       | 8.6.1  | Common Software for all Modes (except C-Callable)                           | 41 |

|    |       | 8.6.2  | Mono Mode Interrupt Driven Software Using RD to Start Conversion            | 46 |

|    |       | 8.6.3  | Calibration of the ADC                                                      | 53 |

|    |       | 8.6.4  | Mono Mode Interrupt Driven Software Using CSTART to Start Conversion        | 58 |

|    |       | 8.6.5  | Dual Interrupt Driven Mode                                                  | 66 |

|    |       | 8.6.6  |                                                                             |    |

|    |       |        | Dual Continuous Mode                                                        |    |

|    |       | 8.6.8  | C-Callable                                                                  | 86 |

| 9  | Summ  | ary    |                                                                             | 93 |

| 10 | Refer | rences |                                                                             | 93 |

# **List of Figures**

| 1 TLV1562 - DSP Interface of the EVM, Using $\overline{RD}$ or the $\overline{CSTART}$ \$ | Signal to Start Conversion |

|-------------------------------------------------------------------------------------------|----------------------------|

| 2 TLV1562 - DSP Interface of the EVM, Using RD or the CSTART S                            | Signal to Start Conversion |

| 3 TLC5618 – DSP Interface                                                                 |                            |

| 4 TLC5651 – DSP Interface                                                                 |                            |

| 5 Memory Map                                                                              |                            |

| 6 Software Flow of the Mono Interrupt Driven Solution                                     |                            |

| 7 Flow Chart Mono Interrupt Driven Mode Using CSTART to Start C                           |                            |

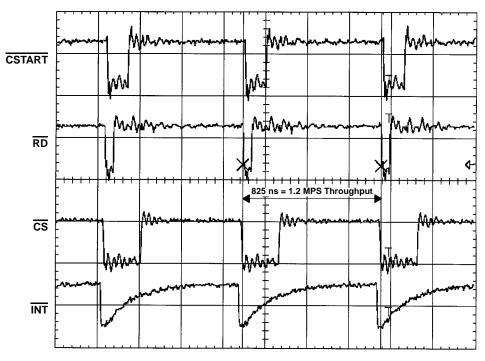

| 8 Time Optimization (monocst1) Maximum Performance at 12 MSPS                             | S with Internal Clock      |

| 9 Flow Chart Dual Interrupt Driven Mode (Using CSTART) to Start C                         |                            |

| 10 Flow Chart Mono Continuous Mode                                                        |                            |

| 11 Flow Chart Dual Continuous Mode                                                        |                            |

| List of Tables  1 Signal Connections                                                      | -                          |

| 1 Signal Connections                                                                      |                            |

| 2 3-Position Jumpers                                                                      | 8                          |

| 3 2-Position Jumpers                                                                      |                            |

| 4 DSP/DAC Interconnection                                                                 | 9                          |

| 5 DSP Serial Port Signals and Registers                                                   |                            |

| 6 DSP Algorithm for Writing to the ADC                                                    |                            |

| 7 DSP Algorithm for Mono Interrupt Driven Mode Using RD                                   |                            |

| 8 DSP Algorithm for Mono Interrupt Driven Mode Using CSTART                               |                            |

| 9 DSP Algorithm for Dual Interrupt Driven Mode                                            |                            |

| 10 DSP Algorithm for Mono Continuous Mode                                                 |                            |

| 11 DSP Algorithm for Dual Continuous Mode                                                 |                            |

| 12 Switch Settings                                                                        |                            |

| 13 Instruction in the Program Header (Step 1)                                             |                            |

| 14 Instruction in the Program Header (Step 1)                                             |                            |

# Interfacing the TLV1562 Parallel ADC to the TMS320C54x DSP

Falk Alicke and Perry Miller

#### **ABSTRACT**

In this application report we discuss the hardware and software interface of the TLV1562, 10-bit parallel-output analog-to-digital converter (ADC) to the TMS320C54x digital signal processor (DSP). The hardware interface board, or evaluation module (EVM) consists of the TLV1562 10-bit ADC, a THS5651 10-bit parallel output communication digital-to-analog converter (CommsDAC™) and a TLC5618A serial-output digital-to-analog converter (DAC).

Following the discussion of the ADC we explain the need for both the THS5651 CommsDAC and the TLC5618A serial DAC.

The application report concludes with several software application examples and recommendations for simplifying the software through modifications of the DSP hardware interface circuit.

# 1 Introduction

The analog-to-digital (A/D) interface can present a significant design problem because hardware and software must work together across the interface to produce a usable, complete design. This application report provides a design solution for the interface between the TLV1562 10-bit parallel-output analog-to-digital converter (ADC) and the TMS320C54x digital signal processor (DSP).

The report describes the hardware and software needed to interface the 'C54x DSP to the TLV1562 ADC, which is intended for applications, such as industrial control and signal intelligence in which large amounts of data must be processed quickly. The first sections describe the basic operation of the TLV1562. For additional information see the *References* section at the end of this report.

# 2 The Board

The TLV1562 evaluation module (EVM) is a four-layer printed circuit board (PCB) constructed from FR4 material. The PCB dimensions are 180 mm  $\times$  112 mm  $\times$  12 mm. Ribbon cables are used to interface the TLV1562EVM to the TMS320C54x DSK plus starter kit.

#### 2.1 TMS320C54x Starter Kit

The starter kit simplifies the task of interfacing to the 'C54x processor. It comes with an ADC for voice bandwidth, and GoDSP code explorer as the software tool. A 10-MHz oscillator provides the clock signal to allow 40-MHz internal DSP clock cycles generated by the internal DSP PLL. Therefore, the board provides 40 MIPS of processing power.

Ribbon cables are used to connect the DSP with the EVM. Detailed descriptions of all connections are given later in this report.

#### 2.2 TLV1562EVM

The TLV1562EVM gives customers an easy start with employing many of the features of this converter. A serial DAC (TLC5618A), a parallel DAC (THS5651), and the ADC (TLV1562) make this EVM flexible enough to test the features of the TLV1562. It also helps show how this ADC can be implemented.

#### 2.3 ADC TLV1562 Overview

The TLV1562 is a CMOS 10-bit high-speed programmable resolution analog-todigital converter, using a low-power recyclic architecture.

The converter provides two differential or four single-ended inputs to interface the analog input signals.

On the digital side, the device <u>has a chip-select</u> ( $\overline{CS}$ ), input clock (CLKIN), sample/conversion start signal ( $\overline{CSTART}$ ), read signal input ( $\overline{RD}$ ), write signal input ( $\overline{WR}$ ), and 10 parallel data I/O lines (D9:0).

The converter integrates the  $\overline{\text{CSTART}}$  signal to coordinate sampling and conversion timing without using the parallel bus. Since the TMS320C542 DSP has no second general-purpose output, this signal is generated with the signal ( $\overline{\text{CSTART}}$ ) from the address decoder.

# 2.3.1 Suggestions for the 'C54x to TLV1562 Interface

The following paragraphs describe two suggested interfaces between the 'C54x and the TLV1562.

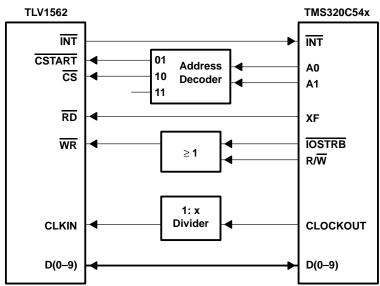

#### 2.3.1.1 The Universal Interface

The schematic in Figure 1 shows the pin-to-pin connections between the TLV1562 and 'C54x, realized on the EVM. This routing can test the converter in each mode. One I/O-wait state is required for write operations to the ADC. The read sequence from the ADC does not require any wait states because the  $\overline{\text{RD}}$  signal is generated with XF.

Figure 1. TLV1562 to 'C54x DSP Interface of the EVM, Using RD or the CSTART Signal to Start Conversion

# 2.3.1.2 Simplification of Software Requirements Through Modified Interface

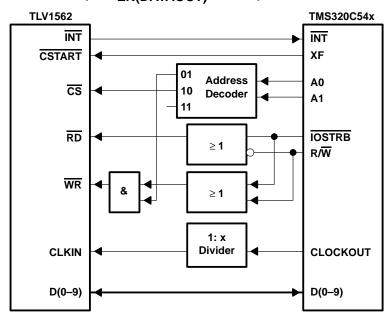

Of all the TLV1562 modes of operation, only the mono interrupt driven mode uses the  $\overline{\text{RD}}$  signal to start the conversion. This requires a very flexible handling of the read signal and therefore has to be performed by a general-purpose output signal. If the application excludes using the  $\overline{\text{RD}}$  signal to start the conversion (using  $\overline{\text{CSTART}}$  instead). The TLV1562  $\overline{\text{RD}}$  input signal can be generated with an OR gate, whose inputs are driven by  $\overline{\text{IOSTRB}}$  and  $\overline{\text{R/W}}$  signals from the DSP (see Figure 2).

Using these connections saves the programming steps of setting/resetting  $\overline{RD}$  with the XF signal. Another advantage is having XF available to control the  $\overline{CSTART}$  signal. This saves busy times on the address bus (in Figure 1,  $\overline{CSTART}$  was generated through A0/A1.) and simplifies the software code.

#### **CAUTION:**

The time  $t_{\text{EN(DATAOUT)}}$  between the  $\overline{\text{RD}}$  high-to-low transition (generated by the DSP) and the arrival of valid ADC output data on the data bus is related to the capacitive load of the bus. In most cases, the ADC come out of the 3-state mode and supplies the correct voltage levels onto the bus lines in less than 50 ns. Thus, the minimum number of I/O-wait states becomes two (for  $t_{\text{EN(DATAOUT)}} \leq 50$  ns).

Figure 2. TLV1562 to 'C54x DSP Interface of the EVM, Using RD or the CSTART Signal to Start Conversion

## 2.3.2 Recyclic Architecture

One specialty of this ADC is its recyclic architecture. Instead of limiting the device power by the highest possible resolution at the fastest speed, this converter is able to work at three maximum speeds for three resolutions. The highest resolution runs at 2MSPS maximum throughput rate; 8-bit resolution corresponds to 3MSPS, and 4-bit resolution to 7MSPS.

This feature fits well into monitoring application. For example, the ADC may have to trigger on one event out of some channels inside an extremely small time window and then sample the correct channel with a higher resolution, but lower throughput to analyze this process. This feature also fits well into home security applications or applications that must monitor several inputs simultaneously.

# 2.3.3 Note on the Interface, Using an External ADC Clock Drive

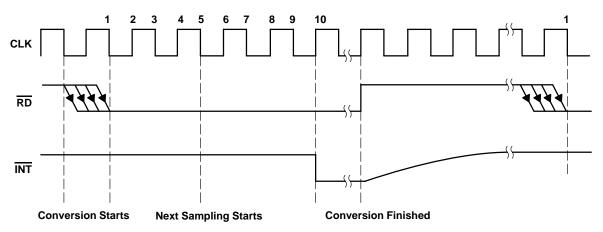

The TLV1562data sheet (Figure 9) shows that  $\overline{RD}$  has to fall as close as possible to the falling edge of the clock signal. The user must adhere to this timing, otherwise the conversion result may be wrong. The user may not recognize the erroneous result, since the ADC will signal that the conversion has finished during the logic low transition of the  $\overline{INT}$  signal. The following timing diagram shows the interface behavior of the ADC whether the timing is correct or not. The following figure shows what happens when the  $\overline{RD}$  falling edge is timed wrong. Although  $\overline{RD}$  falls nearly 1/2 of one cycle too late, the conversion result is valid on the 5<sup>th</sup> clock cycle.

#### 2.4 Onboard Components

These sections describe the EVM onboard components.

## 2.4.1 TLC5618A - Serial DAC

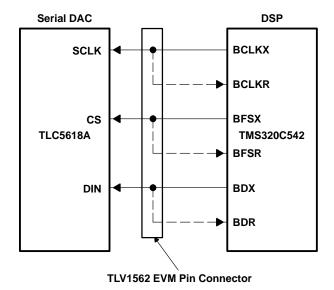

This 12-bit DAC has a serial interface that can run at 20-MHz clock; therefore, it can update the output at 1.21 MSPS. Two outputs are available on the 8-pin package. The buffered SPI of the DSP provides the DSP interface. Using the auto-buffer mode, updating the data on the DAC requires only four CPU instructions/samples.

Figure 3. TLC5618A to 'C542 DSP Interface

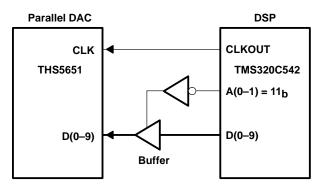

# 2.4.2 THS5651 – Parallel Output CommsDAC

This 10-bit data converter has a parallel interface and is able to update its output with 100 MSPS. The two outputs on the 28-pin package can each drive a current between 2 mA and 20 mA with an output resistance >100 k $\Omega$  (ideal current source: output impedance  $\rightarrow \infty$ ). The data bus and the address decoder provide the interface to the DSP.

Figure 4. THS5651 to C542 DSP Interface

# 3 Operational Overview

This chapter discusses the software and hardware interface for the TLV1562. Plus the overall operational sequence of the A/D interface is described.

# 3.1 Reference Voltage Inputs

The voltage difference between the VREFP and VREFM terminals determines the analog input range, i.e., the upper and lower limits of the analog inputs that produce the full-scale (output data all 1s) and zero-scale (output data all 0s) readings, respectively.

For design reasons, this high-speed sampling ADC does not have a ground-referenced input voltage range. Hence, level shifting is required unless the application allows the signal to be ac coupled. Level shifting could be done with single-supply op amps.

The absolute voltage values applied to VREFP, VREFM, and the analog input should not be greater than the  $AV_{DD}$  supply minus 1 V, or lower than 0.8 V. Other input restrictions apply so consult the TLV1562 data sheet for further information. The digital output is full scale when the analog input is equal to or greater than the voltage on VREFP, and is zero scale when the input signal is equal to or lower than VREFM.

# 3.2 Input Data Bits

The ADC contains the two user-accessible registers, CR0 and CR1. All user defined features such as conversion mode, data output format or sample size are programmed in CR0 and CR1. The data acquisition process must be started by writing to these two registers. After this initialization, the converter processes data in the same configuration until these registers are overwritten.

# 3.3 Connections Between the DSP and the EVM

The following connections provide the interface between the DSP and the EVM:

**Table 1. Signal Connections**

| DSP Signal    | Connector/Pin on the DSKplus circuit board                                                           | Connector/Pin on the TLV1562EVM                | ADC Signal                      |

|---------------|------------------------------------------------------------------------------------------------------|------------------------------------------------|---------------------------------|

| General       |                                                                                                      |                                                |                                 |

| GND           | Connector JP4: Pin 1, 10, 11, 12, 14, 15, 19, 20, 21, 27, 34, 35<br>Connector JP5: Pin 6, 10, 11, 12 | <br>J10/2,J10/4,,J10/34<br>J11/4,J11/6,,J11/26 | GND                             |

| VCC           | JP1/32                                                                                               | <br>N/A                                        | VCC                             |

| Parallel Inte | erface                                                                                               |                                                |                                 |

| CLKOUT        | JP3/2                                                                                                | <br>J11/11                                     | CLKIN                           |

| INT0          | JP5/1                                                                                                | <br>J11/5                                      | ĪNT                             |

| XF            | JP4/8                                                                                                | <br>J11/3                                      | RD                              |

| R/W           | JP4/30                                                                                               | <br>J11/9                                      | decoded to the WR line          |

| IOSTRB        | JP4/36                                                                                               | <br>J11/7                                      | decoded to the WR line          |

| A0            | JP5/34                                                                                               | <br>J11/2                                      | addr. decoder for CS and CSTART |

| A1            | JP5/35                                                                                               | <br>J11/1                                      | addr. decoder for CS and CSTART |

| D0            | JP3/35                                                                                               | <br>J10/13                                     | D0                              |

| D1            | JP3/34                                                                                               | <br>J10/15                                     | D1                              |

| D2            | JP3/8                                                                                                | <br>J10/17                                     | D2                              |

| D3            | JP3/12                                                                                               | <br>J10/19                                     | D3                              |

| D4            | JP3/11                                                                                               | <br>J10/21                                     | D4                              |

| D5            | JP3/15                                                                                               | <br>J10/23                                     | D5                              |

| D6            | JP3/14                                                                                               | <br>J10/25                                     | D6                              |

| D7            | JP3/18                                                                                               | <br>J10/27                                     | D7                              |

| D8            | JP3/17                                                                                               | <br>J10/29                                     | D8                              |

| D9            | JP3/21                                                                                               | <br>J10/31                                     | D9                              |

| Serial Interf | ace to the DAC TLC5618A                                                                              |                                                |                                 |

| BCLKR         | JP1/14                                                                                               | <br>J11/25                                     | SCLK                            |

| BCLKX         | JP1/17                                                                                               | <br>J11/23                                     | SCLK                            |

| BFSR          | JP1/20                                                                                               | <br>J11/21                                     | CS                              |

| BFSX          | JP1/23                                                                                               | <br>J11/19                                     | CS                              |

| BDR           | JP1/26                                                                                               | <br>J11/17                                     | DIN                             |

| BDX           | JP1/29                                                                                               | <br>J11/15                                     | DIN                             |

Signals D[9–0] of the TLV1562 and D[9–0] of the DSP are tied together in this application to simplify hardware debugging during the development phase. However, if the 2s complement feature of the DAC is to be used, it is easier to connect D[15-6] of the DSP with D[9–0] of the ADC. A simple right shift of the result then evaluates the result when sign extension mode (SXM) is enabled.

# 3.3.1 Jumpers Used on the TLV1562EVM

Table 2. 3-Position Jumpers

| JUMPER         | GENERAL DESCRIPTION                                                                                           | PIN 1-2                                                                           | PIN 2-3                                                                                  |

|----------------|---------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| W1             | Connects BP/CH3 (ADC) to R45 or GND;                                                                          | Input not in use, grounded to reduce noise                                        | Use as single input channel3 or differential input positive channel B                    |

| W2             | Connects BM/CH4 (ADC) to R44 or GND;                                                                          | Input not in use, grounded to reduce noise                                        | Use as single input channel4 or differential input negative channel B                    |

| W3             | Connects RD to XF or /RD1                                                                                     | Logic generator is connected to the ADC                                           | DSP is connected to the ADC                                                              |

| W4             | WR + WR1 is connected with DSP_WR or U12-J9/3                                                                 | Logic generator is connected to the ADC                                           | DSP is connected to the ADC                                                              |

| W5<br>W6<br>W7 | The three Jumpers define the prescaling of the CLKOUT signal to the MCB_CLK Pin, if W8 is set to Counter-Mode |                                                                                   |                                                                                          |

| W8             | MCB_CLK is connected to BUFCLK (U14) or RD1 (U11)                                                             | Counter-Mode (MCB_CLK signal is divided by the counter, set-up with Jumper W(5-7) | Counter-Mode disabled (MCB_CLK is synchronize with the CLKOUT signal)                    |

| W9             | CLK input of the Counter (U2) is connected with CLKOUT or CLKOUT/2                                            | The counter is toggled by the DSP system clock (signal BUFF_CLK)                  | The counter's clock is prescaled by two (toggled by half the DSP system clock (CLKOUT2)) |

| W10            | ADC CLKIN is connected to CLK/2 or CLK/4                                                                      | The ADC clock runs at a quarter of the DSP clock frequency (10 MHz)               | The ADC clock runs at half the DSP clock frequency (20 MHz)                              |

| W11            | Connects AP/CH1 (ADC) to R48 or GND;                                                                          | Input not in use, grounded to reduce noise                                        | Use as single input channel 1 or differential input positive channel A                   |

| W12            | Connects AM/CH2 (ADC) to R47 or GND;                                                                          | Input not in use, grounded to reduce noise                                        | Use as single input channel 2 or differential input negative channel A                   |

| W13            | Connects REFLO (TLV5651) to Vcc or GND                                                                        | Disable internal reference                                                        | Enable internal reference                                                                |

| W14            | Connects SCLK (TLC5618AA) to BCLKX or J8 (BNC)                                                                | Normal DSP mode                                                                   | An external clock source drives the SCLK pin instead of the DSP                          |

| W15            | Connects CLK (TLV5651) to CLKOUT (DSP) or J7 (BNC)                                                            | Normal DSP mode                                                                   | An external clock source drives the CLK pin instead of the DSP                           |

| W23            | Connects CSTART to A0, A1, or XF                                                                              | A0 and A1 used to generate ADC CSTART signal                                      | XF signal connects to CSTART pin                                                         |

| W24            | Connects DSP_RD to XF or IOSTRB, ORed with R/W from the DSP                                                   | XF signal connected to ADC RD pin                                                 | RD pin driven by IOSTRB ORed with R/W                                                    |

# **Table 3. 2-Position Jumpers**

| JUMPER | GENERAL DESCRIPTION                                                                                  | PINS SHORTED                                                                        | PINS OPEN                                                                                        |

|--------|------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| W16    | Connects Mode input (TLV 5651) to GND                                                                | MODE 0 is chosen (binary data input)                                                | MODE 1 is chosen (2s complement data input)                                                      |

| W17    | Connects REFIO (TLV5651) to VREF1 or leaves the REFIO pin decoupled to GND via a 0.1 μF capacitor    | Use as external reference voltage input                                             | Use as internal reference voltage output with this pin terminated into GND in series with 0.1 pF |

| W18    | Connects DIR (U19) to GND or leaves the DIR pin connected to WR                                      | ADC can only write but not read to the data bus                                     | Normal operation mode                                                                            |

| W19    | Connects $\overline{OE}$ (U19) to GND or leaves the $\overline{OE}$ pin connected to $\overline{CS}$ | Output driver is isolated and disabled (no signal can bus trough the data bus)      | Normal operation mode                                                                            |

| W20    | Connects BDX to BDR or leaves BDR open                                                               | DSP BDR pin gets a shortcuted feedback from the BDX (transmit) pin; normal mode     | BDR remains open                                                                                 |

| W21    | Connects BSFX to BSFR or leaves BCLKR open                                                           | DSP BSFR pin gets a shortcuted feedback from the BSFX (transmit) pin; normal mode   | BSFR remains open                                                                                |

| W22    | Connects BCLKX backwards with BCLKR or leaves it open                                                | DSP BCLKR pin gets a shortcuted feedback from the BCLKX (transmit) pin; normal mode | BCLKR remains open                                                                               |

| W28    | Connect Sleep input (TLV5651/5 GND                                                                   | Normal mode of operation                                                            | Sleep mode seleted                                                                               |

# 4 The Serial DAC/DSP System

The software configures the buffered DSP serial port to the 16-bit master mode so that the DSP generates the frame sync signal at BFSX and the data clock at BCLKX serial port terminals. Table 4 shows the connections between the DSP and the DAC TLC5618A.

Table 4. DSP/DAC Interconnection

| FROM DSP | M DSP TO DSP |         |

|----------|--------------|---------|

| BFSX     | BFSR         | CS      |

| BCLKX    | CLKR         | I/O CLK |

| BDX      | BDR          | DATA IN |

The following statements describe the generation and application of the configuration and control signals.

- The DSP BCLKX output provides a 20-MHz data clock, which is a divide-by-2 of the DSP master clock.

- The DSP BDX output supplies the 16-bit control and data move to the TLC5618A at DATA IN.

- The DSP BFSX frame synchronization signal, connected to  $\overline{CS}$ , triggers the start of a new frame of data.

After the falling edge of FSX, the next 16 data clocks transfer data into the DSP DR terminal and out of the DX terminal. Since this DSP/DAC interface is synchronous, the FSX signal is sent to the FSR terminal, and the CLKX is sent to the CLKR terminal.

# 5 The DSP Serial Port

The buffered serial port provides direct communication with serial I/O devices and consists of six basic signals and five registers. The DSP internal serial port operation section discusses the registers.

The six signals are:

- BCLKX The serial transmit clock. This signal clocks the transmitted data from the BDX terminal to the DIN terminal of the TLC5618A.

- BCLKR The serial receive clock. This signal clocks data into the DSP BDR terminal. Since the DAC does not send any information back to the DSP, this signal is not important.

- BDX Data transmit. From this terminal the DSP transmits 16-bit data to the DIN terminal of the TLC5618A.

- BDR Data receive not in use

- BFSX Frame sync transmit. This signal frames the transmit data. The DSP begins to transmit data from BDX on the falling edge of BFSX and continues to transmit data for the next 16 clock cycles from the BCLKX terminal. The BFSX signal is applied to the TLC5618A CS terminal.

- BFSR Frame sync receive. This signal frames the receive data. The DSP begins to receive data on the falling edge of BFSR and continues to recognize valid data for the following 16 clocks from BCLKR. This signal is not important for this application.

Table 5 lists the serial port pins and registers.

Table 5. DSP Serial Port Signals and Registers

| PINS                                                | DESCRIPTION REGISTERS DESCRIPTION                |                        | DESCRIPTION                  |

|-----------------------------------------------------|--------------------------------------------------|------------------------|------------------------------|

| BCLKX                                               | XX Transmit clock signal BSPC Serial port contro |                        | Serial port control register |

| BCLKR                                               | BCLKR Receive clock signal BSPCE extended BSPC   |                        | extended BSPC                |

| BDX Transmitted serial data signal BDXR Data transn |                                                  | Data transmit register |                              |

| BDR                                                 | Received serial data signal BDRR Data receive re |                        | Data receive register        |

| BFSX                                                | Transmit frame synchronization signal            | BXSR                   | Transmit shift register      |

| BFSR Receive frame synchronization signal           |                                                  | BRSR                   | Receive shift register       |

|                                                     |                                                  | AXR                    | Buffer start location        |

|                                                     |                                                  | BKX                    | Buffer size                  |

For this application the DSP buffered serial port is programmed as the master, so the BCLKX output is fed to the BCLKR terminal and the BFSX output is fed to the BFSR terminal.

# 6 Other DSP/TLV1562 Signals

These paragraphs describe other DSP and TLV1562 signals.

# 6.1 DSP Internal Serial Port Operation

Three signals are necessary to connect the transmit pins of the transmitting device with the receive pins of the receiving device for data transmission. The transmitted serial data signal (BDX) sends the actual data. BFSX initiates the transfer (at the beginning of the packet), and BCLKX clocks the bit transfer. The corresponding pins on the receive device are BDR, BFSR and BCLKR, respectively.

The transmit is executed by the autobuffer mode. This means there is no need to write to the serial port output buffer. Instead, the DSP continuously sends the data, located in the memory beginning on AXR. When all data are sent (defined by the buffer length in BXR), the first word (pointed to by AXR) is sent again. Therefore, the program has only to store the samples into this memory location. The rest of the task is handled in the background, using no CPU power.

# 7 Conversation Between the TLV1562 and the DSP

The complexity of the TLV1562 ADC may be confusing because of the number of possible modes to drive the protocol between DSP and ADC. The following paragraphs explain more about the data sheet descriptions for interfacing the 'C54x to the ADC.

# 7.1 Writing to the ADC

Registers CR0 and CR1 must be set to choose any of the modes the TLV1562 offers. Therefore, a write sequence must be performed from the DSP to the ADC.

After selecting the ADC ( $\overline{\text{CS}}$  low), a high-low transition of the  $\overline{\text{WR}}$  line tells the converter that something is to be written to the data port.

| STEPS       |                           | TIMING, NOTES                                                   |

|-------------|---------------------------|-----------------------------------------------------------------|

| 1.          | Set one DSP I/O waitstate | Make timing between 40 MHz C54x CPU compatible with the TLV1562 |

| 2. Clear CS |                           | Select ADC                                                      |

| 3.          | Send out data on the bus  | The signal WR is automatically handled by the DSP               |

| 4.          | Set CS                    | Deselect ADC                                                    |

Table 6. DSP Algorithm for Writing to the ADC

# 7.2 Mono Interrupt Driven Mode Using RD

This mode is used when the application needs to sample one channel at a time and performs the sampling, conversion, and serial transmission steps only once. Although this mode produces continuous sampling data, the use of other modes is recommended. One reason is the  $\overline{\text{CS}}$  signal has to stay low during the whole sampling/conversion time. An interesting advantage of this mode is its ability to control the start-sample time.

The  $\overline{RD}$  signal controls the sampling and converting. Every falling edge of  $\overline{RD}$  stops the sampling process (disconnects the capacitor from the input signal) and starts the signal conversion. After two ADCSYSSCLKs, the sampling capacitor gets connected back to the input signal to do the next sampling. The conversion time needs five ADCSYSCLKs to finish the conversion before it gets written to the data port.

During configuration, the rising edge of WR starts the sampling.

Also, when conversion is finished, the ADC clears the INT signal purposes. Next the ADC writes the conversion result to the data port. The rising edge of  $\overline{\text{RD}}$  resets this status; in other words, the  $\overline{\text{INT}}$  signal goes back to logic high and the conversion result on the data port becomes invalid (the ADC data port gets 3-stated).

The configuration data needs to be written only once to the ADC. After this, toggling the  $\overline{RD}$  signal runs the ADC in a sampling/conversion/sending mode and the  $\overline{RD}$  signal releases every new cycle.

# Table 7. DSP Algorithm for Mono Interrupt Driven Mode Using RD

|    |                                                                  |                                                                                                                                                      | Wait cycles fo                 | or the DSP inte               | ernally (40 MHz               | DSPCLK):                      |

|----|------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|-------------------------------|-------------------------------|-------------------------------|

|    | STEPS                                                            | TIMING, NOTES                                                                                                                                        | APD=0<br>ADCSYCLK<br>= 7.5 MHz | APD=0<br>ADCSYCLK<br>= 10 MHz | APD=1<br>ADCSYCLK<br>= 10 MHz | APD=1<br>ADCSYCLK<br>= 10 MHz |

| 0. | Initialization                                                   |                                                                                                                                                      |                                |                               |                               |                               |

|    | Write all configuration data to the ADC                          | activate the mono interrupt-driven mode in CR0(2;3)                                                                                                  |                                |                               |                               |                               |

| 1. | set CS                                                           | deselect ADC (optional with APD=0)                                                                                                                   |                                |                               |                               |                               |

| 2. | clear CS                                                         | Select ADC (Note: if Hardware Auto power down is enabled, Chip select has to be used, otherwise CS can be left high)                                 |                                |                               |                               |                               |

| 3. | Wait for t <sub>D(CSL-sample)</sub> +1ADCSYSCLK                  | $\begin{aligned} &t_{D(CSL\text{-sample})} = 5\text{ns} & \text{(APD=0)} \\ &t_{D(CSL\text{-sample})} = 500\text{ns} & \text{(APD=1)} \end{aligned}$ | ≥6                             | ≥5                            | ≥26                           | ≥25                           |

| 4. | Clear RD                                                         | ADC goes over from sampling into conversion                                                                                                          |                                |                               |                               |                               |

| 5. | Wait until INT goes low                                          | alternative: ignore the INT signal, wait 49 ns+5(6) ADCSYSCLK and goto step number 7                                                                 | ≥34                            | ≥22                           | ≥34                           | ≥22                           |

| 6. | Wait the time t <sub>EN(DATAOUT)</sub>                           | t <sub>EN(DATAOUT)</sub> = 41 ns                                                                                                                     | ≥2                             | ≥2                            | ≥2                            | ≥2                            |

| 7. | Read sample out from the data port; Reset $\overline{RD}$ signal |                                                                                                                                                      |                                |                               |                               |                               |

| 8. | Goto step 1 or step 3 (if APD=0) for more samples                |                                                                                                                                                      |                                |                               |                               |                               |

# 7.3 Mono Interrupt Driven Mode Using CSTART

Use the  $\overline{\text{CSTART}}$  signal when two or more ADCs must sample/convert signals at the same time. Instead of the  $\overline{\text{RD}}$  signal, the timing for sampling and converting is started with the edges of the  $\overline{\text{CSTART}}$  signal. The  $\overline{\text{RD}}$  signal is still required to get the data out of the ADC and onto the bus.

Table 8. DSP Algorithm for Mono Interrupt Driven Mode Using CSTART

|     |                                                                  | TIMING, NOTES                                                                          | Wait cycles for the DSP internally (40MHz DSPCLK): |                               |                               |                               |

|-----|------------------------------------------------------------------|----------------------------------------------------------------------------------------|----------------------------------------------------|-------------------------------|-------------------------------|-------------------------------|

|     | STEPS                                                            |                                                                                        | APD=0<br>ADCSYCLK<br>= 7.5 MHz                     | APD=0<br>ADCSYCLK<br>= 10 MHz | APD=1<br>ADCSYCLK<br>= 10 MHz | APD=1<br>ADCSYCLK<br>= 10 MHz |

| 1.  | Set CS                                                           | Deselect ADC                                                                           |                                                    |                               |                               |                               |

| 2.  | Clear CSTART                                                     | tTis starts sampling                                                                   |                                                    |                               |                               |                               |

| 3.  | Wait for tw(cstartL)                                             | $t_{W(CSTARTL)} = 100 \text{ ns (APD=0)}$<br>$t_{W(CSTARTL)} = 600 \text{ ns (APD=1)}$ | ≥4                                                 | ≥4                            | ≥24                           | ≥24                           |

| 4.  | Set CSTART                                                       | This starts the conversion                                                             |                                                    |                               |                               |                               |

| 5.  | Wait until INT goes low                                          | Alternative: ignore the INT signal, wait 14ns+5 ADCSYSCLK and goto step number 7       | ≥33                                                | ≥21                           | ≥33                           | ≥21                           |

| 6.  | Wait the time t <sub>D(INTL-CSI)</sub>                           | $t_{D(INTL-CSI)} = 10 \text{ ns}$                                                      | ≥1                                                 | ≥1                            | ≥1                            | ≥1                            |

| 7.  | Clear CS                                                         | Select the ADC                                                                         |                                                    |                               |                               |                               |

| 8.  | Clear RD                                                         | Start communication                                                                    |                                                    |                               |                               |                               |

| 9.  | Wait the time t <sub>EN(DATAOUT)</sub>                           | $t_{EN(DATAOUT)} = 41 \text{ ns}$                                                      | ≥2                                                 | ≥2                            | ≥2                            | ≥2                            |

| 10. | Read sample out from the data port; Reset $\overline{RD}$ signal |                                                                                        |                                                    |                               |                               |                               |

| 11. | Set CS                                                           | Deselect ADC                                                                           |                                                    |                               |                               |                               |

| 12. | Go to step 2 for the next samples                                |                                                                                        |                                                    |                               |                               |                               |

# 7.4 Dual Interrupt Driven Mode

Using techniques similar to those described in the first two modes for sampling/converting/sending tasks, the dual mode samples two channels at the same time and sends out the results in series to the data port. The CSTART pin is used to start sampling and converting.

Table 9. DSP Algorithm for Dual Interrupt Driven Mode

|     |                                                     |                                                                                     |                               |                              | ernally (40MHz               | DSPCLK):                     |

|-----|-----------------------------------------------------|-------------------------------------------------------------------------------------|-------------------------------|------------------------------|------------------------------|------------------------------|

|     | STEPS                                               | TIMING, NOTES                                                                       | APD=0<br>ADCSYCLK<br>= 7.5MHz | APD=0<br>ADCSYCLK<br>= 10MHz | APD=1<br>ADCSYCLK<br>= 10MHz | APD=1<br>ADCSYCLK<br>= 10MHz |

| 1.  | Set CS                                              | Deselect ADC                                                                        |                               |                              |                              |                              |

| 2.  | Clear CSTART                                        | This starts sampling                                                                |                               |                              |                              |                              |

| 3.  | Wait for t <sub>W(CSTARTL)</sub>                    | $t_{W(CSTARTL)}$ = 100ns (APD=0)<br>$t_{W(CSTARTL)}$ = 600ns (APD=1)                | ≥4                            | ≥4                           | ≥24                          | ≥24                          |

| 4.  | Set CSTART                                          | This starts the conversion                                                          |                               |                              |                              |                              |

| 5.  | Wait until INT goes low                             | Alternative: ignore the INT signal, wait 210ns+10 ADCSYSCLK and go to step number 7 | ≥62                           | ≥48                          | ≥62                          | ≥48                          |

| 6.  | Wait the time t <sub>D(INTL-CSL)</sub>              | t <sub>D(INTL-CSI)</sub> = 10 ns                                                    | ≥1                            | ≥1                           | ≥1                           | ≥1                           |

| 7.  | Clear CS                                            | Select the ADC                                                                      |                               |                              |                              |                              |

| 8.  | Clear RD                                            | Start communication                                                                 |                               |                              |                              |                              |

| 9.  | Wait the time t <sub>EN(DATAOUT)</sub>              | t <sub>EN(DATAOUT)</sub> = 41 ns                                                    | ≥2                            | ≥2                           | ≥2                           | ≥2                           |

| 10. | Read sample out from the data port; reset RD signal |                                                                                     |                               |                              |                              |                              |

| 11. | Wait t <sub>W(CSH)</sub>                            | $t_{W(CSH)} = 50 \text{ ns}$                                                        | ≥2                            | ≥2                           | ≥2                           | ≥2                           |

| 12. | Clear RD-                                           | Start communication                                                                 |                               |                              |                              |                              |

| 13. | Wait the time t <sub>EN(DATAOUT)</sub>              | t <sub>EN(DATAOUT)</sub> = 41 ns                                                    | ≥2                            | ≥2                           | ≥2                           | ≥2                           |

| 14. | Read sample out from the data port; reset RD signal |                                                                                     |                               |                              |                              |                              |

| 15. | Set CS                                              | Deselect ADC                                                                        |                               |                              |                              |                              |

| 16. | Goto step 2 for the next samples                    |                                                                                     |                               |                              |                              |                              |

# 7.5 Mono Continuous Mode

This mode simplifies data acquisition, since there is no need to generate a signal to sample or convert data. Instead, initializing this mode once, the ADC sends out the data continuously and will be read by the DSP with the RD signal.

#### **CAUTION:**

In this mode, the sampling result sent out by the ADC is the value of the sample from the last cycle. Therefore, the first sample after initialization is trash.

Table 10. DSP Algorithm for Mono Continuous Mode

|    | STEPS                                                                                      | TIMING, NOTES                                                                                                                 | Wait cycles for the DSP internally (40MHz DSPCLK): |                               |                               |                               |

|----|--------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|-------------------------------|-------------------------------|-------------------------------|

|    |                                                                                            |                                                                                                                               | APD=0<br>ADCSYCLK<br>= 7.5 MHz                     | APD=0<br>ADCSYCLK<br>= 10 MHz | APD=1<br>ADCSYCLK<br>= 10 MHz | APD=1<br>ADCSYCLK<br>= 10 MHz |

| 0. | Initialization                                                                             |                                                                                                                               |                                                    |                               | N/A                           | N/A                           |

|    | Write all configuration data to the ADC                                                    | Activate the mono continuous mode in CR0(2;3)                                                                                 |                                                    |                               | N/A                           | N/A                           |

| 1. | Set CS                                                                                     | Deselect ADC                                                                                                                  |                                                    |                               | N/A                           | N/A                           |

| 2. | wait for t <sub>(SAMPLE1)</sub>                                                            | t <sub>(SAMPLE1)</sub> = 100 ns                                                                                               | ≥4                                                 | ≥4                            | N/A                           | N/A                           |

| 3. | Clear CS                                                                                   | Select ADC                                                                                                                    |                                                    |                               | N/A                           | N/A                           |

| 4. | Clear RD                                                                                   | Start conversion                                                                                                              |                                                    |                               | N/A                           | N/A                           |

| 5. | Wait the time t <sub>EN(DATAOUT)</sub>                                                     | t <sub>EN(DATAOUT)</sub> = 41 ns                                                                                              | ≥2                                                 | ≥2                            | N/A                           | N/A                           |

| 6. | Read sample out from the data port; reset $\overline{\text{RD}}$ signal                    | (Caution: the first result after initialization is trash)                                                                     |                                                    |                               | N/A                           | N/A                           |

| 7. | Wait for the time t <sub>(CONV1)</sub> minus<br>step 7 and 8 to ensure 5(6) ADC-<br>SYSCLk | $t_{(CONV1)}$ = 5(6) ADCSYSCLK; since step 7 and 8 take at least 4 DSPSYSCLK, the calculation are 5(6) ADCSYSCLK minus 100 ns | ≥23                                                | ≥16                           | N/A                           | N/A                           |

| 8. | Go to step 4 for more samples                                                              |                                                                                                                               |                                                    |                               | N/A                           | N/A                           |

# 7.6 Dual Continuous Mode

The dual continuous mode provides a data stream of two input signals. The characteristic of the data protocol is similar to the mono continuous mode but with the use of two  $\overline{RD}$  cycles for one sample/hold cycle.

#### **CAUTION:**

In this mode, the sampling result sent out by the ADC is the value of the sample from the last cycle. Therefore, the first sample after initialization is trash.

Table 11. DSP Algorithm for Dual Continuous Mode

|     |                                                                                            |                                                                                                                                              | Wait cycles for the DSP internally (40MHz DSPCLK): |                               |                               |                               |

|-----|--------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|-------------------------------|-------------------------------|-------------------------------|

|     | STEPS                                                                                      | TIMING, NOTES                                                                                                                                | APD=0<br>ADCSYCLK<br>= 7.5 MHz                     | APD=0<br>ADCSYCLK<br>= 10 MHz | APD=1<br>ADCSYCLK<br>= 10 MHz | APD=1<br>ADCSYCLK<br>= 10 MHz |

| 0.  | Initialization                                                                             |                                                                                                                                              |                                                    |                               | N/A                           | N/A                           |

|     | Write all configuration data to the ADC                                                    | Activate the dual continuous mode in CR0(2;3)                                                                                                |                                                    |                               | N/A                           | N/A                           |

| 1.  | Set CS                                                                                     | deselect ADC                                                                                                                                 |                                                    |                               | N/A                           | N/A                           |

| 2.  | Wait for t <sub>(SAMPLE1)</sub>                                                            | $t_{(SAMPLE1)} = 100 \text{ ns}$                                                                                                             | ≥4                                                 | ≥4                            | N/A                           | N/A                           |

| 3.  | Clear CS                                                                                   | Select ADC                                                                                                                                   |                                                    |                               | N/A                           | N/A                           |

| 4.  | Clear RD                                                                                   | Start conversion                                                                                                                             |                                                    |                               |                               |                               |

| 5.  | Wait the time t <sub>EN(DATAOUT)</sub>                                                     | $t_{EN(DATAOUT)} = 41 \text{ ns}$                                                                                                            | ≥2                                                 | ≥2                            | N/A                           | N/A                           |

| 6.  | Read first sample out from the data port; reset RD signal                                  | (Caution: the first result after initialization is trash)                                                                                    |                                                    |                               | N/A                           | N/A                           |

| 7.  | Wait for the time t <sub>(CONV1)</sub> minus<br>step 7 and 8 to ensure 5(6) ADC-<br>SYSCLk | t <sub>(CONV1)</sub> = 5(6) ADCSysclk; since step 7<br>and 8 take at least 4 DSPSYSCLK, the<br>calculation are 5(6)ADCSYSCLK minus<br>100 ns | ≥23                                                | ≥16                           | N/A                           | N/A                           |

| 8.  | Clear RD                                                                                   | Start conversion                                                                                                                             |                                                    |                               |                               |                               |

| 9.  | Wait the time t <sub>EN(DATAOUT)</sub>                                                     | t <sub>EN(DATAOUT)</sub> = 41 ns                                                                                                             | ≥2                                                 | ≥2                            | N/A                           | N/A                           |

| 10. | Read second sample out from the data port; reset $\overline{RD}$ signal                    | (Caution: the first result after initialization is trash)                                                                                    |                                                    |                               | N/A                           | N/A                           |

| 11. | Wait for the time t <sub>(CONV1)</sub> minus<br>step 7 and 8 to ensure 5(6) ADC-<br>SYSCLk | t <sub>(CONV1)</sub> = 5(6) ADCSysclk; since step 7<br>and 8 take at least 4 DSPSYSCLK, the<br>calculation are 5(6)ADCSYSCLK minus<br>100ns  | ≥23                                                | ≥16                           | N/A                           | N/A                           |

| 12. | Go to step 4 for more samples                                                              |                                                                                                                                              |                                                    |                               | N/A                           | N/A                           |

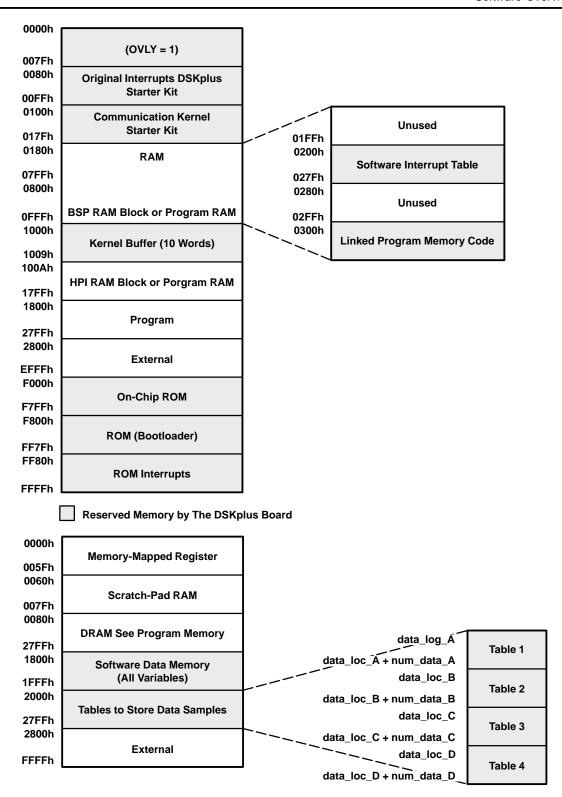

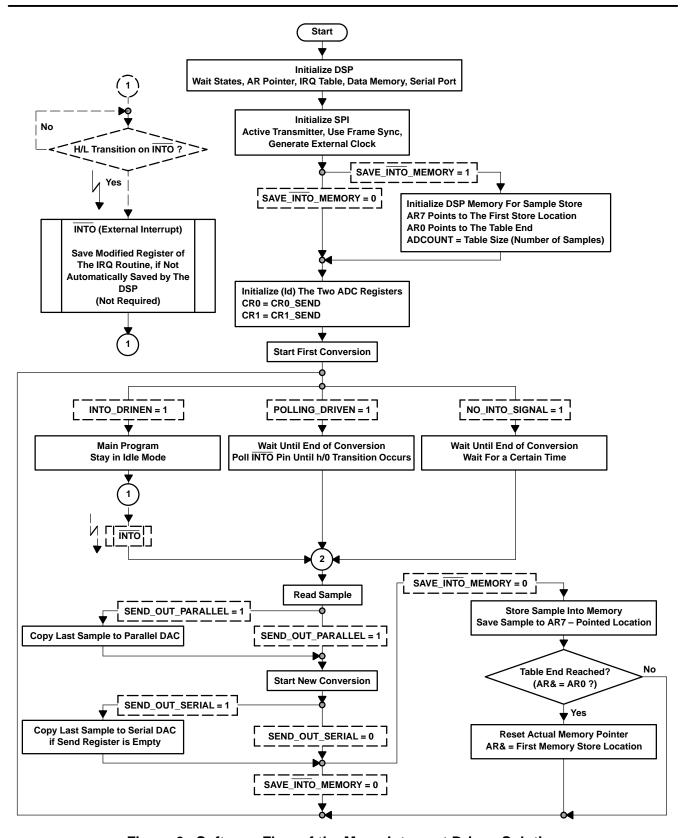

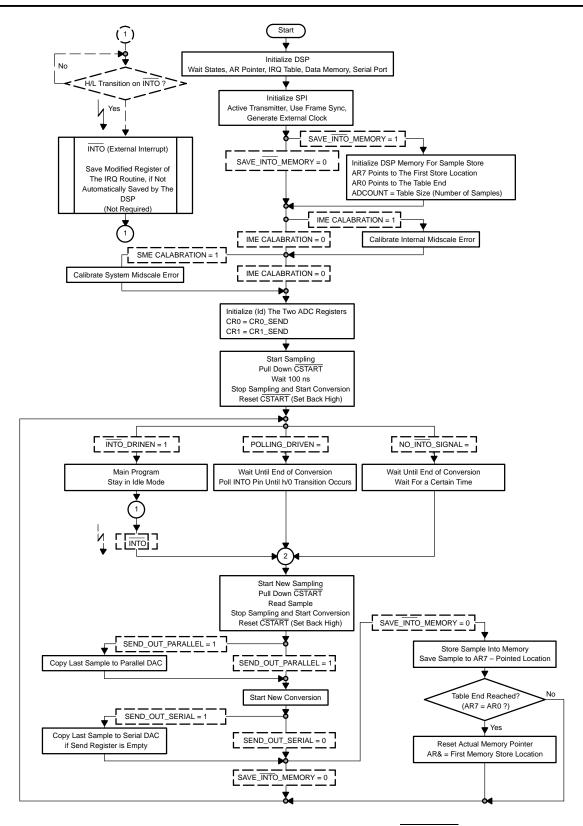

# 8 Software Overview

The software in this report shows how to use all modes of the TLV1562 and useful variations for each mode. It also includes a C program to start data acquisition from a C level. To limit the number of programs, the report supplies five files for running the ADC in five modes; a sixth program shows the C-callable function. Each program can enable different software blocks to give the user a large choice for generating the data acquisition. For more details, see paragraph 8.3.9.