# Optimizing String Inverter Systems Using Logic and Translation

#### **Functional Block Diagram**

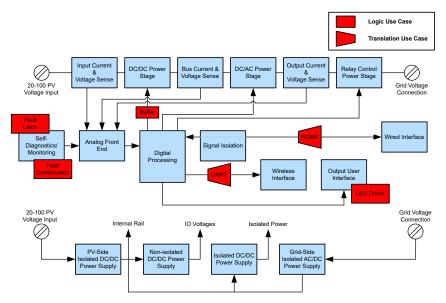

For the purpose of this report, a simplified string inverter block diagram is used to illustrate the logic and translation use cases, see Figure 1. Each red block has an associated use-case document. Links are provided in Table 1 and Table 2. For a more complete block diagram, see the interactive online end equipment reference diagram for string inverters.

Figure 1. Simplified Block Diagram for String Inverters

## **Logic and Translation Use Cases**

Each use case is linked to a separate short document that provides additional details including a block diagram, design tips, and part recommendations. The nearest block and use-case identifiers are listed to match up exactly to the use cases shown in the provided *simplified block diagram*.

**Table 1. Logic Use Cases**

| Nearest Block               | Use-Case Identifier | Use Case                                           |

|-----------------------------|---------------------|----------------------------------------------------|

| Self-Diagnostics/Monitoring | Fault Latch         | Catch a Digital Pulse<br>Multiple Fault Monitoring |

|                             | Fault Combination   | Use Fewer Inputs to Monitor Error Signals          |

| Digital Processing          | Buffer              | Redrive Digital Signals                            |

| Output User Interface       | LED Driver          | Drive Indicator LEDs                               |

**Table 2. Translation Use Cases**

| Nearest Block      | Use-Case Identifier | Use Case                     |

|--------------------|---------------------|------------------------------|

| Wireless Interface | UART                | Translate Voltages for UART  |

| Wired Interface    | RGMII               | Translate Voltages for RGMII |

#### **Multiple Fault Monitoring**

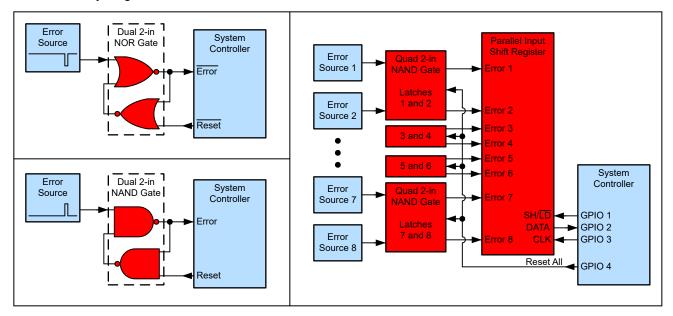

It is common to see string inverters utilizing multiple sensors that could indicate fault conditions. Each fault signal can be individually monitored utilizing individual pins of a system controller; however, another approach is to utilize a combination of digital latches and a shift register to reduce the number of system controller pins required to monitor for issues. This has the added advantage that the controller can only occasionally poll for errors and will not miss anything due to the added latches.

Figure 2. [Left top] Single Negative Pulse Latch, [Left bottom] Single Positive Pulse Latch, [Right] Monitoring Multiple Latches Using Parallel-Input Shift Register to Reduce Controller Pin Count

See more about similar use cases in the *Logic Minute* videos *Design an Alarm / Tamper Circuit with an S-R Latch* and *Increase the Number of Inputs on a Microcontroller*.

- · Dedicated logic latches catch even extremely short events that could otherwise be missed by the controller

- Positive and negative latches can be combined as needed depending on the output of the sensor

- Eight or more sensors can be monitored by utilizing only 4 GPIO pins

- Ensure that all input signals are digital; use comparators or Schmitt-trigger buffers to convert analog signals

- [FAQ] How does a slow or floating input affect a CMOS device?

- Need additional assistance? Ask our engineers a question on the TI E2E™ Logic Support Forum

**Table 3. Recommended Parts**

| Part Number | Automotive Qualified | Operating Voltage<br>Range | Features                                                                     |  |  |

|-------------|----------------------|----------------------------|------------------------------------------------------------------------------|--|--|

| SN74AUP2G00 |                      | 0.8 V to 3.6 V             | AUP family logic devices are extremely low power; $I_{CC} < 0.9 \mu\text{A}$ |  |  |

|             |                      |                            | One latch per device (2 × 2-input gates)                                     |  |  |

| SN74AUP2G02 |                      |                            | ('00) NAND-based positive pulse detectors                                    |  |  |

|             |                      |                            | ('02) NOR-based negative pulse detectors                                     |  |  |

**Table 3. Recommended Parts (continued)**

| rabio di recommenda i arte (continuou) |                      |                            |                                                                                                                                |  |

|----------------------------------------|----------------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------|--|

| Part Number                            | Automotive Qualified | Operating Voltage<br>Range | Features                                                                                                                       |  |

| SN74HCS00-Q1                           | 1                    |                            | HCS family logic has integrated Schmitt-trigger inputs allowing for slow input signals                                         |  |

| SN74HCS00                              |                      |                            | Up to two latches per device (4 × 2-input gates)                                                                               |  |

| SN74HCS02-Q1                           | ✓                    |                            | Low power consumption - I <sub>CC</sub> < 2 μA                                                                                 |  |

| SN74HCS02                              |                      | 2 V to 6 V                 | ('00) NAND-based positive pulse detectors                                                                                      |  |

| SN74HCS165-Q1                          | ✓                    |                            | ('02) NOR-based negative pulse detectors                                                                                       |  |

| SN74HCS165                             |                      |                            | ('165) Parallel-input shift registers increase the number of inputs; can be daisy-chained for 16+ inputs from only 4 GPIO pins |  |

For more devices, browse through the *online parametric tool* where you can sort by desired voltage, channel numbers, and other features.

## **IMPORTANT NOTICE AND DISCLAIMER**

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated