# Common Risks of Discrete FET Voltage Translation and Advantages of TI's Integrated 2N7001T Level Shifter

Shreyas Rao

#### **ABSTRACT**

Discrete Field Effect transistors (FET) are commonly considered for level translation. This application note provides an overview of the common discrete push-pull level shifter implementations and the potential drawbacks. Finally, the 2N7001T solution from TI is discussed to show how the discrete level shifter implementation drawbacks are overcome.

|   | Contents                                                |   |

|---|---------------------------------------------------------|---|

| 1 | Introduction                                            | 2 |

| 2 | 2N7001T: Unidirectional Level Shifter                   | 2 |

| 3 | Discrete Implementation Comparison                      | 3 |

| 4 | Additional Resources                                    | 6 |

|   | List of Figures                                         |   |

| 1 | Texas Instruments Voltage Translation Portfolio         | 2 |

| 2 | 2N7001T DCK Package                                     |   |

| 3 | NMOS Solution                                           |   |

| 4 | HyperLynx Simulation of Open drain buffer and 2N7001T   | 4 |

| 5 | 73ns Rise time for an Open Drain buffer                 | 4 |

| 6 | 2.2ns Rise time for 2N7001T                             | 4 |

| 7 | BJT Solution                                            | 5 |

| 8 | Push-Pull Solution                                      | 6 |

| 9 | Size Comparison of 2N7001T vs Push-Pull Solution        | 6 |

|   | List of Tables                                          |   |

| 1 | Design Considerations For NMOS Solution vs 2N7001T      | 3 |

| 2 | Design Considerations For BJT Solution vs 2N7001T       | 5 |

| 3 | Design Considerations For Push-Pull Solution vs 2N7001T | 6 |

#### **Trademarks**

All trademarks are the property of their respective owners.

Introduction www.ti.com

### 1 Introduction

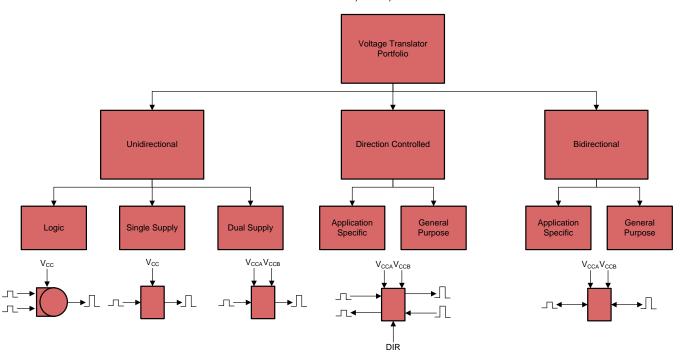

Texas Instruments' voltage translation devices can be categorized into three major families: unidirectional, direction-controlled bidirectional, and the auto-bidirectional.

Unidirectional translators are designed to facilitate a one-way communication between a host and a peripheral device. Popular related devices include SN74AUP1T34, SN74LV1T34, SN74AUP1T57, SN74AVC2T244, and the new 2N7001T solution.

Direction controlled translators contain one or more direction control pins that allow the directional flow of the data lines to be manually configured. Popular device families include LVC, AVC, and the newly released AXC.

Auto-bidirectional translators are designed for communication interfaces with bidirectional data lines, and do not require any additional external control signals to manage the direction flow of data. Common device families for auto-bidirectional translators include TXS, TXB, and LSF.

Figure 1. Texas Instruments Voltage Translation Portfolio

## 2 2N7001T: Unidirectional Level Shifter

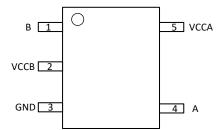

Figure 2 shows TI's 2N7001T device which is a low-power single channel unidirectional level shifter with configurable dual power supply rails that operate from 1.65 V to 3.6 V. The device is fully specified for  $I_{\text{off}}$  partial power-down applications. The device provides ESD (electrostatic discharge) protection on all the pins along with an ambient temperature support range from  $-40^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$ .

Figure 2. 2N7001T DCK Package

# 3 Discrete Implementation Comparison

## 3.1 NMOS Implementation

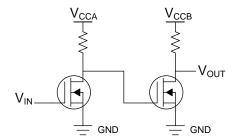

Figure 3 shows the discrete level shifter implementation using NFET (N-channel Field Effect Transistor) and two resistors. Table 1 lists the common design considerations for the NMOS solution.

Figure 3. NMOS Solution

Table 1. Design Considerations For NMOS Solution vs 2N7001T

| DESIGN<br>CONSIDERATION<br>S | NMOS SOLUTION                                                                    | 2N7001T                                                                                                                                                                                                                             |  |

|------------------------------|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Speed                        | Higher speed requires lower PU resistors. This increases current consumption.    | No speed vs power trade off; Higher data rate is supported because of the active drive structure.                                                                                                                                   |  |

| Power<br>Consumption         | Lower power requires higher pull-up resistors resulting in lower speed.          | No power vs speed trade-off; Low-power and low leakage is due to dual supplies and push-pull structure.                                                                                                                             |  |

| Ease of Use                  | Multiple components increase both the debugging time and probability of failure. | A single component reduces the probability of failure and reduces the debugging time.                                                                                                                                               |  |

| Solution Size                | Solution size is larger than TI Solution.                                        | The solution size is compact, and it is easy to debug. Leaded (DCK) and non-leaded packages (DPW) are available.                                                                                                                    |  |

| Vcc isolation                | No Vcc isolation. When the power supply is at 0V, the IO pins are not in Hi-Z.   | Turning off either supply places the IO pins in high impedance (Hi-Z). This results in power savings.                                                                                                                               |  |

| ESD protection               | There is no built-in ESD protection.                                             | The ESD ratings are 2-kV HBM and 1-kV CDM.                                                                                                                                                                                          |  |

| Rise/Fall time               | The rising edges are slow due to the RC charging time.                           | The rise and fall time is fast because of the push pull structure. Hence, the systems downstream does not have issues with slow rising edges. For more information, see the <i>Solving CMOS Transition Rate Issues</i> white paper. |  |

| Power sequencing             | Supply sequencing may be required. Glitches may occur while power sequencing.    | Supply sequencing is not required. Glitches may occur while power sequencing.                                                                                                                                                       |  |

| Fab and<br>Assembly          | Multiple components increase the manufacturing time and cost.                    | A single component reduces the manufacturing time and cost.                                                                                                                                                                         |  |

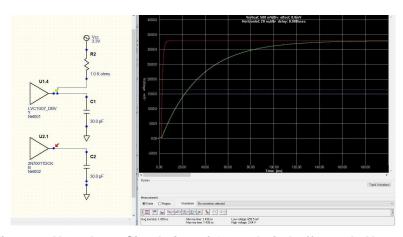

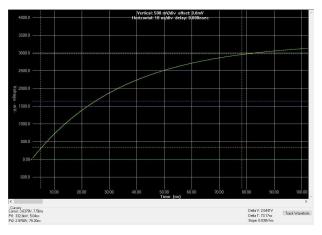

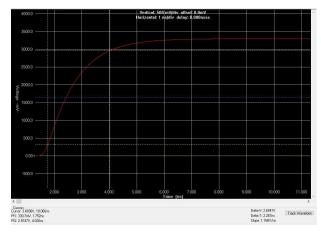

An example for the rise time analysis, a simulation of NMOS structure using an open drain buffer, and the 2N7001T device was done as shown in Figure 4. The open drain output with a pull-up resistor of 1-kOhm driving a 30-pF cap load resulted in a rise time of about 73ns as shown in Figure 5. Using the 2N7001T to drive the same 30-pF cap load, resulted in 2.3ns rise time as shown in Figure 6. The application note *Implications of Slow Floating CMOS* explains the effects of slow rising edge inputs to a CMOS system.

Figure 4. HyperLynx Simulation of Open drain buffer and 2N7001T

Figure 5. 73ns Rise time for an Open Drain buffer

Figure 6. 2.2ns Rise time for 2N7001T

## 3.2 BJT Implementation

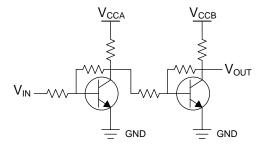

BJT (Bipolar Junction Transistor) based discrete implementation uses NPN transistors, and the accompanying resistor network for level translation as shown in the Figure 7. Table 2 lists the common design considerations for the BJT solution.

Figure 7. BJT Solution

Table 2. Design Considerations For BJT Solution vs 2N7001T

| DESIGN<br>CONSIDERATIONS | BJT SOLUTION                                                                              | 2N7001T                                                                                                                                                                                                                            |

|--------------------------|-------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Speed                    | The speed is higher compared to CMOS. However, speed is limited by the pull-up resistors. | The speed is fast because of the active drive structure.                                                                                                                                                                           |

| Power<br>Consumption     | With the BJT solution, the leakage current is very high.                                  | Low-power and low leakage is due to dual supplies and push-pull structure.                                                                                                                                                         |

| Ease of Use              | Multiple components increase both the debugging time and probability of failure.          | A single component reduces the probability of failure and reduces the debugging time.                                                                                                                                              |

| Solution Size            | Solution size is larger than TI Solution.                                                 | The solution size is compact, and it is easy to debug.<br>Leaded (DCK) and non-leaded packages (DPW) are<br>available.                                                                                                             |

| Vcc isolation            | No Vcc isolation. When the power supply is at 0V, the IO pins are not in Hi-Z.            | Turning off either supply places the IO pins in high impedance (Hi-Z). This results in power savings.                                                                                                                              |

| ESD protection           | There is no built-in ESD protection.                                                      | The ESD ratings are 2-kV HBM and 1-kV CDM.                                                                                                                                                                                         |

| Rise/Fall time           | The rising edges are slow due to the RC charging time.                                    | Fast rising and falling edges because of the push pull structure. Hence, the systems downstream does not have issues with slow rising edges. For more information, see the <i>Solving CMOS Transition Rate Issues</i> white paper. |

| Power sequencing         | Supply sequencing maybe required. Glitches may occur while power sequencing.              | Supply sequencing is not required. Glitches may occur while power sequencing.                                                                                                                                                      |

| Fab and Assembly         | Multiple components increase the manufacturing time and cost.                             | A single component reduces the manufacturing time and cost.                                                                                                                                                                        |

## 3.3 Push-Pull Implementation

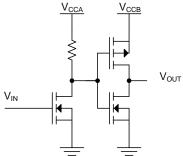

Figure 8 shows a push-pull implementation using the NFET (N-channel Field Effect Transistor) and PFET (P-channel Field Effect Transistor) along with the pull-up resistor network. Table 3 lists the common design considerations for the push-pull solution.

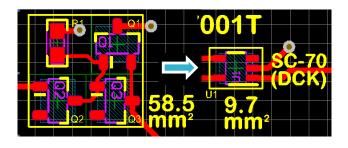

Figure 9 shows the solution size comparison between the push-pull solution and using the 2N7001T solution.

Figure 9. Size Comparison of 2N7001T vs Push-Pull Solution

Table 3. Design Considerations For Push-Pull Solution vs 2N7001T

| DESIGN<br>CONSIDERATIONS | PUSH-PULL SOLUTION                                                                                                                                                                                    | 2N7001T                                                                                                                                                                                                                                        |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Speed                    | Speed vs power trade off; higher speed requires lower PU resistors. This increases current consumption.                                                                                               | The speed is fast because of the active drive structure.                                                                                                                                                                                       |

| Power<br>Consumption     | Power vs speed trade-off; lower power requires higher pull-up resistors resulting in lower speed.                                                                                                     | Low-power and low leakage is due to dual supplies and push-pull structure.                                                                                                                                                                     |

| Ease of Use              | Multiple components increase both the debugging time and probability of failure.                                                                                                                      | A single component reduces the probability of failure and reduces the debugging time.                                                                                                                                                          |

| Solution Size            | Solution size is larger than TI Solution.                                                                                                                                                             | The solution size is compact, and it is easy to debug. Leaded (DCK) and non-leaded packages (DPW) are available.                                                                                                                               |

| Vcc isolation            | No Vcc isolation. When the power supply is at 0V, the IO pins are not in Hi-Z.                                                                                                                        | Turning off either supply places the IO pins in high impedance (Hi-Z). This results in power savings.                                                                                                                                          |

| ESD protection           | There is no built-in ESD protection.                                                                                                                                                                  | The ESD ratings are 2-kV HBM and 1-kV CDM.                                                                                                                                                                                                     |

| Rise/Fall time           | Overall, the rise and fall time is quicker. However, due to the pull-up resistor in the initial stage, there may be a large propagation delay (tpd) and other related issues due to a slow rise time. | The rise and fall time is fast because of the push pull structure. Hence, the systems downstream does not have issues with slow rising edges. For more information, see the <i>Implications</i> of <i>Slow Floating CMOS</i> application note. |

| Power sequencing         | Supply sequencing may be required. Glitches may occur while power sequencing.                                                                                                                         | Supply sequencing is not required. Glitches may occur while power sequencing.                                                                                                                                                                  |

| Fab and Assembly         | Multiple components increase the manufacturing time and cost.                                                                                                                                         | A single component reduces the manufacturing time and cost.                                                                                                                                                                                    |

#### 4 Additional Resources

- Texas Instruments, 2N7001TEVM user's guide

- Texas Instruments, 2N7001T sample page

- Texas Instruments, *Introducing the 2N7001T* video

- Texas Instruments, Implications of Slow Floating CMOS Inputs application report

- Texas Instruments, Solving CMOS transition rate issues with Schmitt trigger white paper

#### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ('TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications that include TI products, you will thoroughly test such applications and the functionality of such TI products as used in such applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your non-compliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/sampterms.htm">http://www.ti.com/sc/docs/sampterms.htm</a>).

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2018, Texas Instruments Incorporated