# Biasing Requirements for TXS, TXB, and LSF Auto-Bidirectional Translators

Shreyas Rao, Adrian Ozer

#### **ABSTRACT**

The TXS and LSF families of translators differ from the TXB translator family, because the outputs of the TXS and LSF families are not driven by buffers. Instead, the TXS and LSF families use internal or external pullup resistors to drive logic high, and an internal pass transistor that lets the host device drive logic low. This application report discusses the specific requirements of bidirectional translators for a minimum voltage separation between  $V_{\rm CCA}$  and  $V_{\rm CCB}$ . For TXS and TXB-type translators,  $V_{\rm CCA}$  must be less than or equal to  $V_{\rm CCB}$ . For translators from the LSF family,  $V_{\rm ref\_A}$  must be at least 0.8 V less than  $V_{\rm ref\_B}$ . This application report also examines the reason for these requirements and the implications when they are violated.

#### Contents

| 1 | V <sub>CCA</sub> and V <sub>CCB</sub> Bias Requirements for Bidirectional Translators | 2 |

|---|---------------------------------------------------------------------------------------|---|

|   | 1.1 V <sub>CCA</sub> and V <sub>CCB</sub> Separation of TXS and TXB-Type Translators  |   |

|   | 1.2 V <sub>ref_A</sub> and V <sub>ref_B</sub> Bias for LSF Type Translators           | 5 |

| 2 | References                                                                            | 6 |

|   | List of Figures                                                                       |   |

|   | C                                                                                     |   |

| 1 | Simplified TXS Architecture                                                           |   |

| 2 | Simplified TXB010X Architecture                                                       | 3 |

| 3 | TXS and TXB V <sub>CCA</sub> and V <sub>CCB</sub> Separation Test Setup               | 3 |

| 4 | TXS0101 V <sub>CCA</sub> > V <sub>CCB</sub> Leakage                                   | 4 |

| 5 | TXS0108E V <sub>CCA</sub> > V <sub>CCB</sub> Leakage                                  | 4 |

| 6 | TXB0108 V <sub>CCA</sub> > V <sub>CCB</sub> Leakage                                   | 4 |

| 7 | LSF010x Simplified Architecture                                                       | 5 |

| 8 | LSF010x Voltage Clamping                                                              | 6 |

# 1 V<sub>CCA</sub> and V<sub>CCB</sub> Bias Requirements for Bidirectional Translators

# 1.1 $V_{CCA}$ and $V_{CCB}$ Separation of TXS and TXB-Type Translators

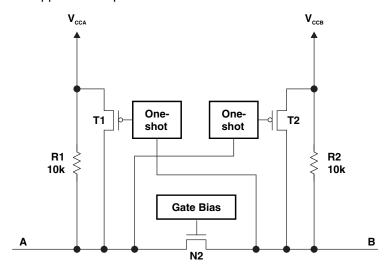

The internal architecture of the TXS family of translators contains a pass transistor, internal pullup resistors on both the I/O ports, and One-shot edge accelerator circuitry. Figure 1 shows a simplified diagram of this internal architecture. For more information, see the A Guide to Voltage Translation With TXS-Type Translators application report.

Figure 1. Simplified TXS Architecture

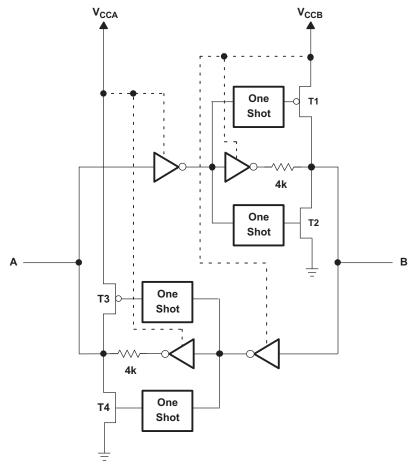

The TXB family of translators has a weak, buffered architecture with one-shot edge accelerator circuitry to improve the data rate. The devices can translate the CMOS push-pull logic, however, they are not suitable for open-drain signals.

Figure 2 shows a simplified diagram of this internal architecture. For more information, see the A Guide to Voltage Translation With TXB-Type Translators application report.

Figure 2. Simplified TXB010X Architecture

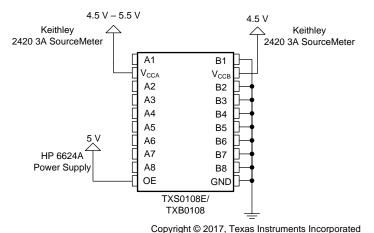

TXS and TXB-type translators require that  $V_{\text{CCA}}$  is less than or equal to  $V_{\text{CCB}}$ . This is due to an internal protection diode that can become forward biased when the voltage on  $V_{\text{CCA}}$  exceeds the voltage on  $V_{\text{CCB}}$ . When this occurs, large amounts of current flows through  $V_{\text{CCA}}$  and into the diode, increasing power consumption and potentially damaging the device. Figure 3 shows the test setup.

Figure 3. TXS and TXB  $V_{\text{CCA}}$  and  $V_{\text{CCB}}$  Separation Test Setup

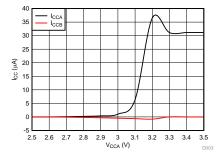

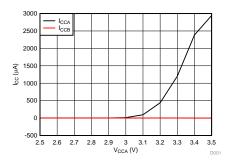

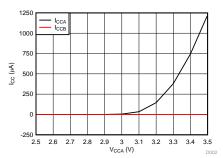

$V_{\text{CCA}}$  and  $V_{\text{CCB}}$  were supplied and measured through Keithley 2420 3-A source meters, with  $V_{\text{CCB}}$  fixed at 2.5 V and  $V_{\text{CCA}}$  swept from 2.5 V to 3.5 V. Figure 4, Figure 5, and Figure 6 show the resulting current through the supply pins.

Figure 4. TXS0101  $V_{CCA} > V_{CCB}$  Leakage

Figure 5. TXS0108E  $V_{CCA} > V_{CCB}$  Leakage

Figure 6. TXB0108 V<sub>CCA</sub> > V<sub>CCB</sub> Leakage

As shown in Figure 4, Figure 5, and Figure 6, when the voltage on  $V_{CCA}$  exceeds the voltage on  $V_{CCB}$  by roughly 0.6 V, the diode begins to conduct and the  $I_{CCA}$  current begins to drastically increase as  $V_{CCA}$  increases.

### 1.1.1 Summary: Bias Requirements for TXS and TXB Translators

TXS and TXB translators require that  $V_{\text{CCA}}$  be less than or equal to  $V_{\text{CCB}}$ . When this requirement is violated, there is potential for the internal protection diode to become forward biased, resulting in increased current consumption and potential damage to the device. When using separate power supplies for  $V_{\text{CCA}}$  and  $V_{\text{CCB}}$ , special care must be taken if  $V_{\text{CCA}}$  and  $V_{\text{CCB}}$  will operate at the same voltage node. The system designer must ensure that power supply tolerances will not result in a potential difference between  $V_{\text{CCA}}$  and  $V_{\text{CCB}}$  large enough to bias the internal protection diode.

## 1.2 $V_{ref,A}$ and $V_{ref,B}$ Bias for LSF Type Translators

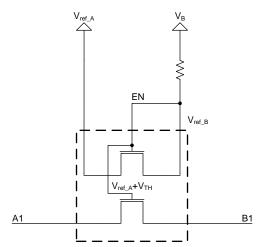

For translators from the LSF family, TI recommends that  $V_{ref\_A}$  is at least 0.8 V lower than  $V_{ref\_B}$ . Figure 7 shows a simplified diagram of the LSF architecture. See the *Voltage Translation With the LSF Family* application report, and watch the LSF Logic Minute videos to understand the LSF device operation and it's applications.

Figure 7. LSF010x Simplified Architecture

As shown in Figure 7, the LSF010x device contains a reference FET between  $V_{ref\_A}$  and  $V_{ref\_B}$ , as well as a pass FET on each channel. The reference FET is designed to set the gate bias voltage of each pass transistor equal to Equation 1.

$$V_{\text{ref A}} + V_{\text{TH}}$$

(1)

When the proper bias of Equation 2 is maintained, the reference FET conducts, allowing  $V_B$  to pull the voltage at EN to that of Equation 1, and setting the gate voltage on the pass transistor of the channel to that of Equation 1. The result is that the output port clamps at Equation 3.

$$V_{\text{ref\_A}} \le V_{\text{ref\_B}} - 0.8 \text{ V} \tag{2}$$

$$V_{ref A} + V_{TH} - V_{TH} = V_{ref A}$$

(3)

When the proper bias between  $V_{\text{ref\_A}}$  and  $V_{\text{ref\_B}}$  is not maintained, the gate bias of the pass transistor can no longer be accurately predicted and the voltage at which the pass transistor turns off is no longer known. By maintaining the proper bias between  $V_{\text{ref\_A}}$  and  $V_{\text{ref\_B}}$ , the system designer can accurately set the gate voltage of the pass transistor, allowing for predictable down-translation from the B-port to the A-port without the use of external pullup resistors.

References www.ti.com

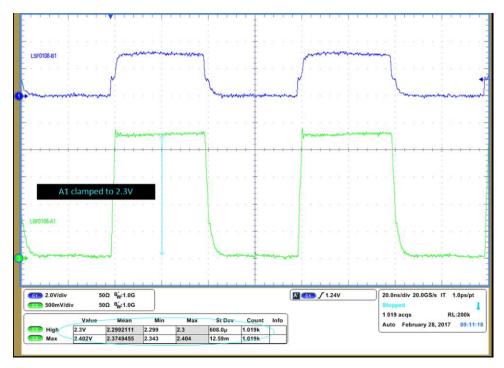

As an example, the LSF0108 device was tested with  $V_{ref\_A} = V_{ref\_B} = 3.3 \text{ V}$ . A 25-MHz, 3.3-V square wave was applied to B1 (blue) and the output was measured at A1 (green). Figure 8 shows the resulting waveform.

Figure 8. LSF010x Voltage Clamping

When the 3.3 V signal is applied to B1, the output A1 clamps at 2.3 V even though  $V_{ref\_A}$  is set to 3.3 V. When the bias between  $V_{ref\_A}$  and  $V_{ref\_B}$  is not maintained, the system designer can no longer accurately set the gate voltage of the pass transistor. Therefore, the system designer can no longer accurately predict the voltage at which the pass transistor stops conducting. This can result in reduced flexibility and reduced signal integrity.

## 1.2.1 Bias Requirements Summary for LSF Translators

When the proper bias between  $V_{\text{ref\_A}}$  and  $V_{\text{ref\_B}}$  is not maintained, the gate bias of the pass transistor can no longer be accurately predicted, and the voltage at which the pass transistor turns off can no longer be known. By maintaining the proper bias between  $V_{\text{ref\_A}}$  and  $V_{\text{ref\_B}}$ , the system designer can accurately set gate voltage of the pass transistor, allowing for predictable down-translation from the B-port to the A-port without the use of external pullup resistors.

#### 2 References

- Texas Instruments, Basics of Voltage-Level Translation, application report

- Texas Instruments, Voltage Translation With the LSF Family, application report

- Texas Instruments, A Guide to Voltage Translation With TXB-Type Translators, application report

- Texas Instruments, A Guide to Voltage Translation With TXS-Type Translators, application report

- Texas Instruments, Effects of External Pullup and Pulldown Resistors on TXS and TXB Devices, application report

#### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ('TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications that include TI products, you will thoroughly test such applications and the functionality of such TI products as used in such applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your non-compliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/sampterms.htm">http://www.ti.com/sc/docs/sampterms.htm</a>).

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2017, Texas Instruments Incorporated