# Simplify Isolation Designs Using an Enhanced-SPI ADC Interface

### Rahul Kulkarni, Data Converter Products

In applications such as power supplies, inverters, protection relays, etc. the system controller is isolated from the high-voltage circuit. In a high voltage system, the analog-to-digital converter (ADC) can be placed closer to the sensor for improved performance. The ADC data output, typically SPI communication, is interfaced to the system controller using a digital isolator. Isolators are typically chosen to ensure compliance with safety and regulatory standards. However, an isolator which meets the safety and regulatory standards may not always meet the timing requirements of a high-speed SPI interface at low cost; this is common in protection relays and power quality monitoring systems.

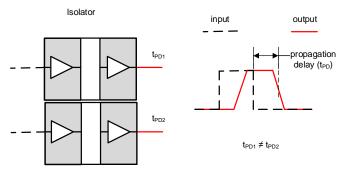

Figure 1. Effect of Isolation on Digital Lines

An isolator can have propagation delays of several nano-seconds, as shown in Figure 1, and are prone to have significant timing variation across channels. Thus the isolator can limit the maximum SPI clock speed for reliable timing, which in turn may limit the ADC sampling rate. It may not be possible to operate the ADC at full sampling rate if the SPI interface clock speed is limited. Hence the system design must factor in the propagation delay and channel-to-channel variation of the isolator to avoid limiting the ADC throughput.

### **Effects of Propagation Delay**

The propagation delay of an isolator is the time it takes for a logic change at the input to be reflected at the output. The propagation delay of isolators can be of the order of 10s of nano-seconds.

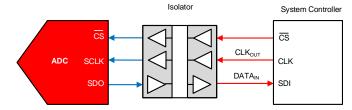

An ADC is a slave entity on the SPI bus which sends data in response to  $\overline{CS}$  and SCLK from the system controller. When working with an isolator, as shown in Figure 2, the propagation delay causes the ADC to receive the serial clock later than when the processor sent it, as shown in Figure 3.

Figure 2. ADC SPI Interface with Isolator

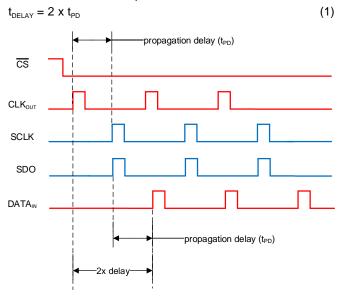

The ADC sends data bits with respect to the serial clock at the ADC clock input. This data output of the ADC is connected through an isolator channel to the processor. In Figure 3 it can be seen that the data output also gets shifted by an amount equal to the propagation delay of the isolator. From the processor's perspective, there is 2x the  $t_{\text{PD}}$  delay between  $\text{CLK}_{\text{OUT}}$  and  $\text{DATA}_{\text{IN}}$  because of the propagation delay on serial clock and data path.

Figure 3. Effect of Propagation Delay on SPI Timings

The delay in receiving data DATA<sub>IN</sub> with respect to CLK<sub>OUT</sub> can lead to data bits being lost or latched incorrectly. The minimum SCLK period cannot exceed the total propagation delay between DATA<sub>IN</sub> and CLK<sub>OUT</sub> i.e. t<sub>DELAY</sub>. Hence the isolator's propagation delay imposes a maximum clock speed limit on the SPI data bus.

$$t_{SPl\_CLK} \ge t_{DELAY}$$

(2)

$$f_{SPICLK} \le (t_{SPICLK})^{-1} \tag{3}$$

There can be other sources of propagation delay such as routing delay caused by the printed circuit board. All these propagation delays put together impose an upper limit on the maximum clock speed in the system.

## Using Long Data Read Time of Enhanced-SPI Devices

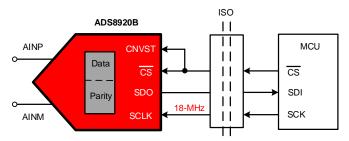

Table 1 lists the device families which support the Enhanced-SPI interface. Figure 4 shows the ADS8920B's 3-wire SPI interface with an isolator. The ADC's CONV (conversion start) and  $\overline{CS}$  pins can be tied together and driven by the  $\overline{CS}$  line of the SPI bus.

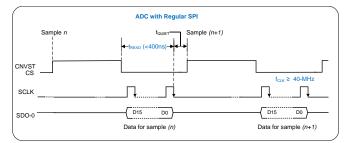

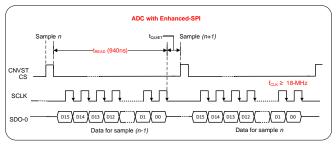

The Enhanced-SPI interface allows the conversion data to be read out from the ADC during an on-going conversion, as shown in Figure 5.

Figure 4. ADS8920B Isolated 3-wire SPI

Table 1 lists the ADC device families which support the Enhanced-SPI interface. The Wide Read Cycle using Enhanced-SPI interface allows for a 18-MHz SPI clock when the ADC sampling rate is 1-MSPS. This reduction in clock speed is achieved by pulling  $\overline{CS}$  low after start of conversion and reading data, as shown in Figure 5.

The reduction in SCLK speed enables the use of highspeed ADCs with an isolated digital interface having significant propagation delays. As there is no register configuration required to achieve low SCLK speeds, the SDI line of ADC can be left unconnected. Only SCLK, CS, and SDO pins of the ADC need to be interfaced using an isolator. As the SPI clock speeds are very low, there is no need to route an additional SCLK back from the isolator to compensate for delays.

Figure 5. Enhanced-SPI vs. Regular SPI Comparison

Hence the Enhanced-SPI interface with Wide Read Cycle enables 3-wire SPI communication over generic isolators that may not have the low propagation delays or channel-to-channel delay matching that are often required for ADCs that require faster SCLK rates.

### Resources

- 20-Bit, 1-MSPS Isolated Data Acquisition Reference Design Optimizing Jitter for Maximum SNR and Sample Rate

- 20-bit, 1-MSPS Isolator Optimized Data Acquisition Reference Design Maximizing SNR and Sample Rate

- TI Precision Labs Comprehensive ADC Trainings

Table 1. High Speed Devices with Wide Read Cycle Feature of Enhanced-SPI

| Device   | Description      | Regular SPI SCLK Speed | Enhanced-SPI SCLK Speed |

|----------|------------------|------------------------|-------------------------|

| ADS8920B | 16-bit, 1-MSPS   | 52-MHz                 | 18-MHz                  |

| ADS8910B | 18-bit, 1-MSPS   | 58-MHz                 | 20-MHz                  |

| ADS8900B | 20-bit, 1-MSPS   | 70-MHz                 | 22-MHz                  |

| ADS9120  | 16-bit, 2.5-MSPS | 200-MHz                | 45-MHz                  |

| ADS9110  | 18-bit, 2-MSPS   | 140-MHz                | 40-MHz                  |

#### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ('TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications that include TI products, you will thoroughly test such applications and the functionality of such TI products as used in such applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your non-compliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/sampterms.htm">http://www.ti.com/sc/docs/sampterms.htm</a>).

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2017, Texas Instruments Incorporated