# 以低雜訊電源裝置簡化電源架構

**Marcoo Zamora**System Engineer

Linear Power

減少固有雜訊與系統雜訊,是在要求嚴格的電子系統中實現高密 度訊號鏈的關鍵。低雜訊電源裝置的創新有助於減少系統雜訊, 提升準確度與精密度。

# 摘要

# 定義電源架構中的雜訊和精密度

1

雜訊通常是特定於應用的,但在本文中,雜訊是指源自熱雜訊、1/f 雜訊和低頻振蕩 (最高約 100kHz)的任何不必要的訊號。

## 低雜訊和低功耗電壓參考的創新

減少電源架構中的雜訊有助於提高類比數位轉換器的解析度和精密度,但會帶來功耗、印刷電路板 (PCB) 尺寸、製造流程和成本方面的設計挑戰。

#### 精密電池監控的創新

擁有矽晶片技術的創造性解決方案,讓設計人員得 以將電源架構和電池系統最佳化。

3

隨著業界趨勢不斷突碰解析度與精密度的界限,在訊號鏈中實現最低雜訊就更形重要。突破這些限制時,不僅必須考慮類比轉數位轉換器 (ADC) 及放大器等訊號鏈元件的雜訊,也必須考慮開關及低壓降穩壓器 (LDO) 等電源產品的雜訊。矽晶片技術的進步減少了在電源拓撲中實現低雜訊和高精密度時的權衡取捨。

24 位元 delta-sigma ADC 的最新趨勢提高了取樣速度並降低了功耗。新型低雜訊電源供應器和低雜訊電壓參考可善用這些趨勢,並協助 ADC 在低功耗應用中實現高解析度量測。

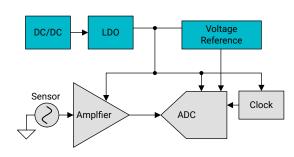

為了實現最低雜訊,我們來回顧一下訊號鏈和電源架構中的雜訊來源。图 1 顯示了一個典型的訊號鏈應用,該應用以 ADC 為中心,需要外部電壓參考、時脈和訊號調節電

路。图 1 中的每個元件都會產生系統雜訊,需要進行最佳化。

图 1. 常見訊號鏈電源架構。

# 雜訊與 ADC

ADC 中的雜訊可能會在精確的電壓量測中造成誤差。您必須考量訊號鏈中來自內部及外部來源雜訊的整體影響。總雜訊通常結合了 ADC 熱雜訊、ADC 量化雜訊、放大器雜訊、電壓參考雜訊及電源雜訊。

方程式 1 描述了 ADC 輸入端 (全刻度電壓下) 量測感測器時的總參考雜訊,如图 1 所示。主要的設計挑戰是將所有雜訊來源最佳化,以實現應用所需的雜訊目標。在方程式 1 中,ADC 的電源抑制比 (PSRR) 降低了電源雜訊,繪製為 1MHz:

ADC 總計 雜訊 =

$$\sqrt{\text{ADC 散熱 雜訊}^2 + \text{ADC 量化 雜訊}^2 + \left( \text{電源 供應 雜訊} \times 10^{\frac{\text{PSRR}}{20}} \right)^2 + \text{電壓 參考 雜訊}^2}$$

(1)

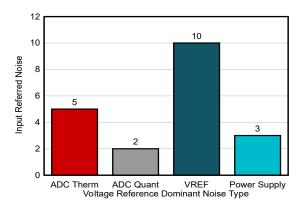

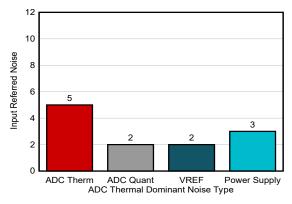

由於存在不相關的雜訊來源,因此總雜訊為所有雜訊來源的平方根,這非常有利於最大的雜訊來源。其中一個有雜訊的元件會嚴重扭曲量測結果。例如,如果電壓參考比ADC和電源產生更大的雜訊,則降低電壓參考上的雜訊將是降低系統雜訊的最佳方法,如图 2 和图 3 所示。此外,ADC雜訊類型會因解析度而異:量化雜訊對 16 位元 ADC而言相當重要,但對 24 位元 ADC而言則可忽略。

图 2. 電壓參考主要雜訊。

图 3. ADC 主要熱雜訊。

# 定義電源架構中的雜訊和精密度

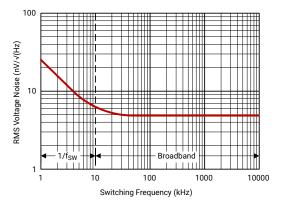

電源雜訊是隨機的,出現在所有半導體功率元件和電源拓撲中。本白皮書的重點在低於 100kHz 的訊號,因為高於此頻率的訊號通常可歸因於切換漣波或電磁干擾 (EMI)。您也可以將雜訊進一步區分為低頻雜訊 (0.1Hz 至 10Hz) 和高

頻雜訊 (100Hz 至 100kHz),它們各自有不同的要求和設計 挑戰,如图 4 中所示。

图 4. 雜訊頻譜。

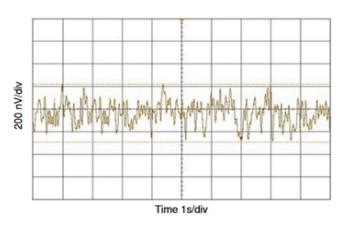

低頻雜訊通常指定為 0.1Hz 至 10Hz 之間的峰值對峰值雜訊,這是由半導體元件結合其矽晶特性與設計架構所自然產生。當以高解析度放大電壓軌時,這種低頻雜訊通常在示波器中可見,如图 5 中所示,通常是精密直流量測中出現誤差的原因。低頻雜訊被視為關鍵規格的 ADC 應用包括電池量測、能源量測、地震量測,甚至是半導體測試量測。

图 5. 示波器上的低頻雜訊。

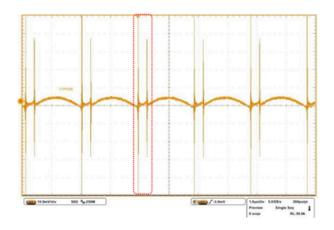

另一種是高頻雜訊,其頻率範圍為 100Hz 至 100kHz,可能包括白雜訊、切換雜訊和時脈抖動,如图 6 中所示。高頻雜訊源也可能來自環境,透過 EMI 耦合。例如,ADC 可能會因電源雜訊而出現錯誤。來自相同雜訊電源的 EMI 可

能會導致時脈抖動增加,如果抖動過多,則會降低訊噪比 性能。

減少數位電路中由時脈頻率上升所引起的高頻雜訊變得越來越重要,因為數位電路更容易受到抖動影響。高頻雜訊被視為關鍵規格的 ADC 應用包括電力線品質監控器、數位訊號處理應用和射頻 (RF) 通訊設備。

图 6. 降壓穩壓器切換雜訊。

# 低雜訊和低功耗電壓參考的創新

降低雜訊的其中一種方式是增加系統功率,但系統通常有功率預算,因此必須在有限的功率下最大限度地提高雜訊性能。TI 的低雜訊電壓參考產品組合包括 REF33、REF34 和 REF35 系列等低功耗選項,這些選項以高精密度突破了低功耗 ADC 的功耗和雜訊界限。較低的靜態電流 (I<sub>Q</sub>) 電壓參考有利於功率預算有限的便攜式或邊緣應用,例如兩線制發射器。

高效率能隙電路和輸出緩衝器的創新改善了電壓參考的功率雜訊比。REF33、REF34 和 REF35 是 TI 低雜訊和低功耗電壓參考產品組合中的主要元件。图 7 比較了它們的雜訊和功耗,並標示了 REF35 的創新。

图 7. 電壓參考功率和雜訊。

低雜訊的一個常見應用是可攜式醫療設備,例如可攜式心電圖機。ADS124S08 系列 24 位元 ADC 的功耗低至 280μA,可最大限度地降低功率預算有限的現場儀器和邊緣設備的功耗。表 1 將 REF35 與內部 ADS124S08 電壓參考進行了比較,並突顯了 IQ 帶來的準確度提升。REF35 的低雜訊和高準確度可改善量化和增益誤差,同時降低系統功率。彈性電壓參考電壓的優勢在於可進一步進行最佳化,使 ADS124S08 的全刻度範圍最大化。

| 裝置   | REF35               | ADS124S08 內部電壓<br>參考 |

|------|---------------------|----------------------|

| 電壓電平 | 1.25 V 至 5 V        | 2.5 V                |

| 低頻雜訊 | 8.5μV <sub>PP</sub> | 9μV <sub>PP</sub>    |

| IQ   | 0.65 μΑ             | 280 μΑ               |

表 1. 外部電壓參考與內部電壓參考的比較。

REF35 還與 ADS127L11 搭配使用,後者是一款專注於低功耗直流精密度的 ADC。與 REF34 相比,REF35 的電源電流減少到只有十分之一,這使其在低速模式下能與 ADS127L11 更好地搭配。這種搭配使 ADS127L11 能夠在需要高精度的電源品質分析儀系統或需要低功耗的機器振動系統中實現準確度,以平衡解決方案尺寸、解析度與頻寬。

# 埋入式稽納電壓參考的創新

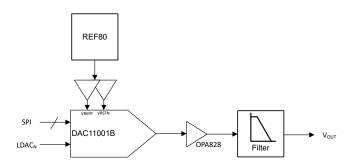

目前有許多類型的電壓參考都可提供超低雜訊電壓位準。 然而,埋入式稽納電壓參考的雜訊特別地低,因此能脫穎 而出。埋入式稽納電壓參考通常不需要增益來產生輸出電 壓,因此可減少雜訊。埋入式稽納電壓參考常用於為高精 密度系統提供「黃金級」電壓位準。電壓參考用於校準或 與超精密資料轉換器 (如 DAC11001B) 配合使用,如图8中所示。

图 8. REF80 作為具有參考緩衝器的 DAC11001B 電壓參考使用。

在使用埋入式稽納裝置進行校準時,有三個重要參數需要考量:溫度漂移、長期漂移和雜訊。在校準期間,系統資料轉換器會使用由埋入式稽納電壓參考 (如 REF80) 提供的穩定和低雜訊電壓來確定 ADC 或 DAC 的增益和偏移誤差。REF80 具有超低的 0.16ppm<sub>p-p</sub> 雜訊規格。為了準確校準,電壓位準不能隨時間或溫度而變化,並且提供的值必須是低雜訊,以確保在校準期間觀察到的誤差能夠得到有效補償。

當 REF80 與 DAC11001B 一起使用時,必須對其進行緩衝以獲得良好的動態性能。這些緩衝器會為參考電路增加更多雜訊,進而增加整個訊號鏈的雜訊。因此,必須使用低雜訊運算放大器來維持低雜訊。OPA828 是一款低雜訊運算放大器,在 1kHz 時具有 4nV/√Hz 雜訊,常用於參考緩衝器電路。

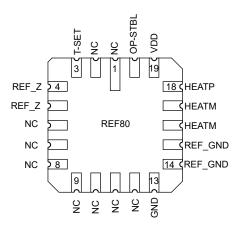

為確保 REF80 的雜訊大部分僅來自電壓參考,使用低雜訊低壓差 (LDO) 為 REF80 供電也十分重要。REF80 的獨特之處在於其具有內部加熱器。無論周圍環境如何,此加熱器都能使晶粒保持在恆定的溫度。此加熱器可達到 REF80 的低漂移規格。加熱器和參考電源彼此獨立。因此,加熱器 (HEATP) 和 VDD (汲極電源) 都需要電源供應器。REF80 針腳配置如 图 9 所示。

图 9. REF80 LCCC 20 針腳封裝針腳配置。

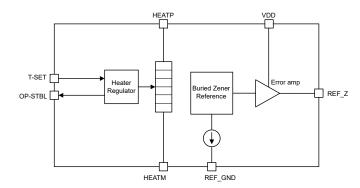

REF80 的加熱器在啟動時通常消耗高達 335mA 的電流,穩定至 18mA 至 75mA,而 VDD 通常只需要 15mA 的靜態電流。此外,REF80 (REF\_Z) 電壓輸出上的雜訊取決於埋入式稽納電路,而不是加熱器。REF80 的架構會使得只有埋入式稽納參考對輸出雜訊產生重大影響,而加熱器的影響最小。图 10 顯示簡化的原理圖。

图 10. REF80 功能原理圖。

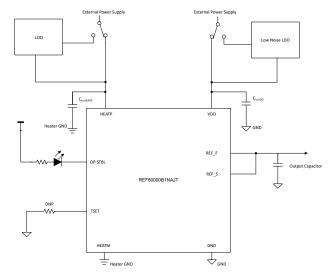

因此,為了盡可能降低雜訊,為埋入式稽納參考供電的 VDD 針腳必須使用低雜訊 LDO 來供電。在 REF80 評估模 組 REF8EVM 中,VDD 會使用寬輸入電壓、超低雜訊 LDO TPS7A49。對於加熱器,則會使用電流輸出較高,但 雜訊也較高的 LM317。图 11 展示了 REF8EVM 電源配置 的原理圖。

图 11. REF80 一般應用和電源樹狀原理圖。

您也可選擇將一個 LDO 同時用於 VDD 和加熱器。如果需要,另一個不錯的選擇是 TPSA4701,其具有超低雜訊和更高的輸出電流能力,可同時為 VDD 和 HEATP 供電。

為了實現最高精確度的技術和應用,埋入式稽納電壓參考 是值得考慮的最佳選擇之一。當訊號鏈和校準雜訊是主要 考量時,埋入式稽納裝置 (如 REF80) 的低漂移和低雜訊便 極為重要。

# 超低雜訊電壓參考的創新

高解析度 ADC 對電壓參考雜訊更為敏感,由於它們直接連接資料轉換電路,所以會直接影響電壓量測。超低雜訊電壓參考有助於高解析度 ADC 充分發揮其解析度潛力。

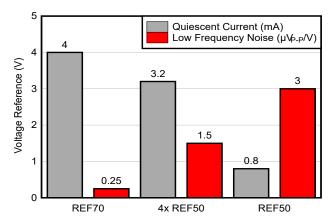

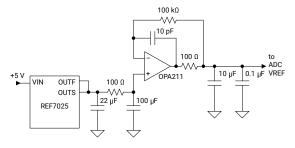

REF70 具有超低的 1/f 雜訊,可與需要超低雜訊的產品 (例如高解析度 ADC) 或多通道類比前端 (例如 AFE2256) 連接。在電壓參考的輸出端增加低通濾波器可降低寬頻雜訊,從而降低系統雜訊,如图 12 所示。

在設計低通濾波器時,務必確保輸出阻抗不會降低 AC 性能。這可能發生在電阻電容低通濾波器中,其中較大的串聯電阻會影響由輸出電流波動引起的負載瞬變。選擇低於10Hz 的低通濾波器頻寬截止頻率以限制寬頻雜訊的影響。

图 12. 帶有外部低通濾波器的 REF7025 應用。

## 透過簡化的電源架構改善雜訊和熱性能

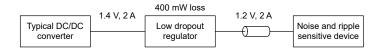

為時脈、資料轉換器或放大器供電的傳統設定是使用 DC/DC 轉換器 (或模組),後面是 LDO,接著是鐵氧體磁珠 濾波器,如图 13 中所示。此設計方法可最大限度地減少 電源的雜訊與漣波,且在大約 2 A 以下負載電流能夠正常 運作。但隨著負載增加,LDO 中的功率損耗會帶來效率與 熱管理方面的問題。例如,在典型的類比前端應用中,後 穩壓 LDO 可能會增加 1.5W 的功率損耗。

图 13. 使用 DC/DC 轉換器、LDO 和鐵氧體磁珠濾波器的典型低 雜訊架構。

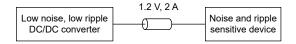

在典型的電源架構中,LDO 的優勢在於提供精確的電壓軌,同時以高 PSRR 減少高頻雜訊區域中的切換雜訊。使用 LDO 的代價是發熱量和功耗的增加。若想在控制功率損耗時確保低雜訊,一種有效的方法是從設計中完全消除 LDO,並使用低雜訊 DC/DC 降壓轉換器或模組,如图 14 中所示。這種無 LDO 設計可降低功率損耗並改善散熱性能,同時實現低雜訊。

图 14. 使用無 LDO 的低雜訊降壓轉換器。

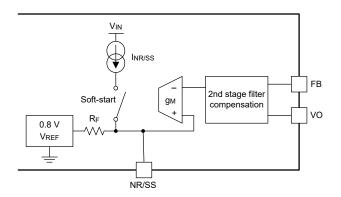

TPS62912 和 TPS62913 系列低雜訊降壓轉換器以及 TPSM82912 和 TPSM82913 模組實現了一個用於連接電容器的降噪/緩啟動針腳,使用整合式 R<sub>f</sub> 和外部連接的 C<sub>NR/SS</sub> 形成低通電阻-電容器濾波器,如图 15 所示。此實作形式本質上模擬了 LDO 中能隙低通濾波器的行為,並可讓輸出電壓漣波低於 10μV<sub>RMS</sub>。TPS62913 還可利用 2.2MHz 切換頻率和可選的第二級鐵氧體磁珠電感電容濾

波器,在高頻區域實現低本底雜訊,而不會出現典型的切 換雜訊。

图 15. 具有能隙雜訊濾波功能的低雜訊降壓轉換器方塊圖。

ADC12DJ5200RF 是一款 RF 取樣 ADC,可在 DC 至 10GHz 範圍內取樣,功耗為 4W。PSRR 可衰減任何電源 漣波和雜訊,但任何殘餘紋波和雜訊都會出現在 ADC 輸出 頻譜上,因而造成誤差。ADC12DJ5200RF 對類比電壓軌 的電源需求更敏感,因此需要低雜訊。將 TPS62912 用於低雜訊和高功率類比電源軌可實現簡化且高效的電源架構,而且與 DC/DC 加 LDO 組合相比,可將功率損耗降至 最低。

# 以 LDO 電源軌實現高電流低雜訊

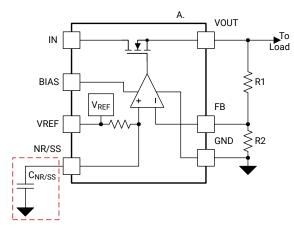

LDO 最大的固有雜訊來源為其內部電壓參考。為了減少雜訊並提升整體系統性能,TI 產品組合中的各種 LDO 都整合了 NR 針腳的降噪功能。將電容器 (C<sub>NR/SS</sub>) 連接到 NR 針腳上可建立在 V<sub>REF</sub> 節點具有內阻的電阻電容濾波器,如图 16 中所示。

图 16. 具有 NR/SS 針腳的 N 通道金屬氧化物半導體 LDO。

A.

$$V_{OUT} = V_{REF} \times \left(1 + \frac{R1}{R2}\right)$$

(2)

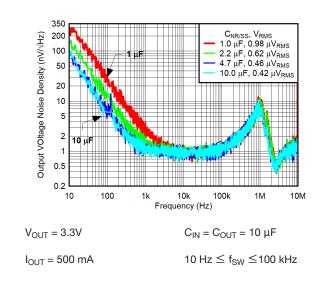

較新的 LDO 採用高準確度、高精密度和低雜訊電流來源, 後接誤差放大器。實作單一增益配置還可確保在整個輸出 範圍中保持低雜訊。TPS7A94 就是此類高準確度低雜訊 LDO 一個很好的例子,它可以在 10Hz 至 100kHz 頻寬範 圍內實現 0.46μV<sub>RMS</sub>。图 17 顯示了輸出雜訊密度以及將 C<sub>NR/SS</sub> 從 1 μF 增加至 10 μF 的影響。

图 17. TPS7A94 的輸出雜訊與 CNR/SS 的關係。

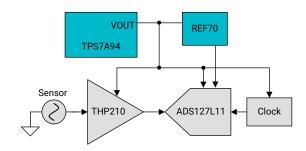

TPS7A94 擁有的功能組合代表了新一代低雜訊 LDO,可實現優異的電壓準確度與超低雜訊,這在 TPS7A94 是高解析度訊號鏈的主要電源時十分重要,因為高解析度 ADC 對雜訊更為敏感。在图 18 所示的典型應用中,TPS7A94 是 ADC、運算放大器、時鐘和外部電壓參考的主電源,這些都是高性能元件。此訊號鏈的目標是透過使用 TPH210 和 REF70 具有低 1/f 雜訊的超低輸入電流雜訊,將 ADS127L11 的總諧波失真、訊號雜訊比和增益誤差降至最低。TPS7A94 的低雜訊及高 PSRR 提供了一條乾淨的電源線,可限制可能耦合到 TPS210、ADC127L11 和 REF70 主動電路並降低性能的任何雜訊。

图 18. 為訊號鏈供電的 TPS7A94。

# 精密電池監控的創新

適用於電動汽車的電池監控器具有 1 mV 的測量電池電壓 準確度。這種更高的準確度和精密度,使汽車原始設備製 造商得以在不增加電動汽車電池組的成本或容量的情況 下,提供更長的續航里程。正如預期一般,許多系統和環 境因素都會導致電壓測量不準確,包括伴隨溫度和壽命的 漂移、電源雜訊以及電路板彎曲引起的晶片應力。

TI 在單一晶粒上採用多種技術,以減少對環境的影響,並 實現更高準確度的電壓量測。例如:

- 埋入式齊納二極體使埋設的連接點遠低於表面,不易受到熱載子的影響。此二極體可在積體電路 (IC) 溫度與使用壽命期間提供非常穩定的電壓參考。

- 將電池監控器焊接至 PCB 時, PCB 的彎曲會使晶粒稍 微彎曲,導致電壓量測不準確。整合的應變片可量測此 彎曲並修正電壓量測。

整合式電池平衡場效應電晶體和電源供應器會造成晶粒 升溫,由於溫度偏差而導致電壓量測誤差。

BQ79718 和 BQ79731-Q1 等專用 IC 有助於在單晶片中解 決系統級問題,使系統設計人員能夠在不犧牲上市時間的 情況下實現最佳性能。

#### 結論

用於低雜訊 ADC 和類比前端的傳統低雜訊電源架構通常面臨功耗和熱性能方面的挑戰。使用低雜訊電壓參考和電源進行設計,可讓設計人員簡化電源架構並滿足嚴格的功率預算要求。REF35 等電壓參考的創新正在協助設計人員將邊緣裝置的低雜訊與低功耗提升至全新層次。在 RF 取樣 ADC 等雜訊敏感型應用中,與傳統切換穩壓器和 LDO 相比,TPS62913 等低雜訊切換穩壓器有著更低的發熱量。

## 其他資源

- · 如需有關低雜訊和精密度的詳細資訊,請造訪**低雜訊和** 精密度。

- 閱讀技術文章*如何以低雜訊和低漣波設計技術強化電源* 與訊號完整性。

- 下載電子書精密 ADC 雜訊分析的基本原理和 LDO 基礎知 證。

- · 參閱應用說明以 TPS62913 低漣波與低雜訊降壓轉換器 為敏感的 ADC 設計供電和以 TPS62913 低漣波與低雜訊 降壓轉換器為 AFE7920 供電。

- 閱讀白皮書 電池管理系統創新如何提升 EV 採用率。

**重要聲明:**本文所述德州儀器及其子公司相關產品與服務經根據 TI 標準銷售條款及條件。建議客戶在開出訂單前先取得 TI 產品及服務的最新完整資訊。 TI 不負責應用協助、客戶的應用或產品設計、軟體效能或侵害專利等問題。其他任何公司產品或服務的相關發佈資訊不構成 TI 認可、保證或同意等表示。

# **IMPORTANT NOTICE AND DISCLAIMER**

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2024, Texas Instruments Incorporated