# 高速轉換器奈奎斯特(Nyquist)孔周圍取樣

#### Luke Allen

Application Engineer High-Speed Converters

#### **Rob Reeder**

Application Engineer High-Speed Converters

#### **Chase Wood**

Application Engineer High-Speed Converters

頻率規劃是任何頻率架構應用中最重要的部分。確保一般 頻率或感興趣的頻率在帶內有效,且不會降低到失去雜散 動態範圍的程度,應成為任何頻率開發策略的一部分。本 文將探討高速類比轉數位轉換器 (ADC) 奈奎斯特(Nyquist) 規則,因為它們適用於超級奈奎斯特(Nyquist) 取樣。我們 也將說明如何使用降取協助您規劃頻率,以及如何在設計 與開發階段防止頻帶落入頻率「洞」。

# 奈奎斯特(Nyquist)規則

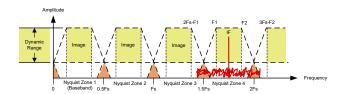

超奈奎斯特取樣,中頻 (IF) 取樣與次取樣在許多採用軟體 定義無線電 (SDR) 或類似雷達的接收器架構的頻率架構應 用中都很受歡迎 (請參閱图 1)。

**图 1.** 超奈奎斯特(Nyquist)取樣與基頻取樣 (第一個奈奎斯特 (Nyquist)) 的範例  $\circ$

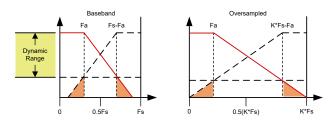

規劃基頻外頻率 (第一個奈奎斯特(Nyquist)) 的主要原因有兩個。第一個原因是獲得抗混疊濾波器設計 (AAF) 上的鬆弛限制 (請參閱图 2)。一開始,在設計基頻濾波器時,一般濾波器滾降必須要更高,而非較高 奈奎斯特(Nyquist)區域的濾波器設計。更陡峭的濾清器滾降會導致濾清器更複雜,被動元件會變得更麻煩。這是簡單的物理學原理;您無法購買 0201 尺寸的 100μH 電感器。因此,若採用較高的奈奎斯特(Nyquist)區域且可能採用較高的取樣率,帶阻區內滾降的取捨和要求就會較為放鬆,進而產生較少元件與較小元件尺寸。

使用高頻次取樣技術的第二個原因,是放鬆 ADC 前的射頻 (RF) 接收器訊號鏈。假設 ADC 可支援超越第一個奈奎斯特(Nyquist)的頻寬需求 (這種情況幾乎總是如此) ,放鬆接收器訊號鏈即可免除射頻(RF)訊號鏈中的一個或甚至兩個混頻階段,進而產生更少的元件,更少的雜訊及更低的複雜性。

图 2. 動態範圍與 AAF 阻帶衰減。

例如,图 3 顯示了德州儀器 (TI) ADC3669 相對於 500 MSPS 取樣頻率 (fs) 以 800MHz 的中頻進行取樣。基本上,訊號位於第四奈奎斯特(Nyquist)區域。感興趣頻率的影像或混疊會反射回以 200MHz 訊號出現的第一個奈奎斯特(Nyquist)區域。最快速的傅立葉轉換 (FFT) 分析器,如

高速資料轉換器 Pro,只會繪製第一個奈奎斯特(Nyquist) 區域的 FFT ,或 0F 至 0.5F。因此,如果感興趣的頻率高 於 0.5Fs ,影像就會向下反射至第一個奈奎斯特(Nyquist) 區域或基頻。如果雜散色調也在感興趣的頻段中,這會使 問題變得混亂。

那麼 ADC 取樣高於 0.5Fs 仍要如何符合奈奎斯特(Nyquist) 區域標準? 奈奎斯特(Nyquist)區域規則規定訊號必須以等於或大於頻寬兩倍的速率進行取樣,以保留訊號的所有資訊 (請參閱**方程式 1**):

$$Fs > 2 > FBW \tag{1}$$

其中 fs 是取樣頻率, FBW 是感興趣的最大頻率。

图 3. ADC3669 範例,其中 Fs = 500MSPS 且中頻 = 800MHz。

要讓奈奎斯特(Nyquist)規則為真,關鍵在於感興趣頻率的 位置。只要訊號不重疊並保持在單一奈奎斯特(Nyquist) 內, 奈奎斯特(Nyquist)準則仍維持不變。唯一變更的是第 一個奈奎斯特(Nyquist)的位置變成更高的區域。因為這些 取捨而使取樣變得非常普及。

# 什麼是流程增益?

早期的高速訊號鏈排列形式包含用於每單一通道消耗功率 瓦特的 ADC ,以及用於擷取、過濾和處理所有轉換器資料 為實用格式的 FPGA (現場可編程邏輯閘陣列)。大多數設 計人員會使用一種稱為*流程增益*的方法。此方法不僅可藉 由消除不必要的雜散與雜訊來幫助頻率規劃,更可限制奈 奎斯特(Nyquist)區域內處理的頻寬,以提升訊號雜訊比 (SNR) 方面的動態範圍。將流程增益校正系數添加到標準 SNR 方程式中會得到方程式 2:

SNR =

$$6.02 \times N + 1.76 dB + 10 \times log_{10} \left( \frac{Fs}{(2 \times BW)} \right)$$

(2)

其中 N 是 ADC 位元數, Fs 是 ADC 取樣頻率, BW 是奈奎斯特(Nyquist)區域內的相關頻寬。

由於 ADC 和數位轉類比轉換器技術中部署了更小的流程節點,因此現在大多數標準 FPGA 數位功能都駐留在 ADC內。部分範例包括數位降頻轉換器 (DDC)、數控振盪器 (NCO) 和跳頻。這些功能可大幅協助分擔 FPGA 處理負荷,讓內部資源可在其他地方使用。

## 為什麼選擇頻率規劃?

適當頻率規劃是使用 ADC 設計系統時的重要步驟。頻率規劃可確保有效利用 ADC 的動態範圍,並將不必要的雜散訊號降到最低,這對 SDR 系統或高密度 RF 訊號鏈等高效能應用而言至關重要。

頻率規劃的其中一個重要層面,是將 ADC 的動態範圍最佳化。類比域中的每個額外訊號,都會消耗部分 ADC 可用輸入訊號功率預算,進而降低總動態範圍能力。適當的頻率規劃可確保 ADC 能以策略性方式配置輸入頻率,以最大化可用的動態範圍,充分發揮其功能。此方法包含考慮在取樣帶中出現不必要的突波與諧波的位置,確保感興趣訊號與雜散元件之間沒有重疊。

另一個重要層面則是管理 ADC 產生的固有雜散訊號,例如 諧波和交錯偽影。若雜散貢獻遠離預期頻帶,頻率計畫即 為成功執行,特別是在資料取樣後未採用數位濾波的系 統。頻率規劃也有助於將時脈相關突波的影響降到最低, 例如來自缺乏通道隔離的時脈裝置的突波,在使用高密度 時脈分配解決方案的大型元件系統中,此類突波的影響尤 為嚴重。

交錯突波管理也是包含交錯式 ADC 的系統中的考量因素, 其中多個 ADC 核心可對共同輸入訊號進行正交取樣,有效 地將取樣率與奎斯特(Nyquist)區域加倍為兩倍。但這種交 錯方式會在 Fs/2-Fin 產生雜散頻調。此外,在使用較高交 錯係數的系統中,相同 Fs/2-Fin 突波會由「新」Fs/2-Fin 再次調變。這導致新的 Fin 由交錯式 Fs/2-Fin 突波組成, 這表示引入的突波計數遠高於單一交錯係數。頻率規劃可 讓您運用類比濾波或 (最好是) 數位降取濾波器來緩解這些 突波,並可大幅衰減,而無需設計複雜的類比訊號鏈。雖 然此方法可將瞬時頻寬降低至選定區域,但可確保更佳的 動態範圍和更清晰的訊號性能。

## 頻率規劃的常見陷阱

儘管有其優點,但頻率方案不當仍可能導致 ADC 性能下降的問題。一個常見的挑戰是奈奎斯特(Nyquist)區域重疊。 規劃不當的輸入訊號可能會落在奈奎斯特(Nyquist)區域邊界,導致混疊效應並降低系統性能。為防止發生這種情況,必須將訊號配置在適當頻帶內,以確保奈奎斯特(Nyquist)區域維持頻譜完整性。

時脈突波汙染是另一個常見問題,特別是在使用低品質時脈裝置或時脈分配不佳的系統中。這些經過調變至 ADC 頻譜的雜散訊號可提供已知偏移突波,對敏感應用造成嚴重影響。仔細設計時脈基礎架構,包括使用高品質時脈解決方案,有助於減輕這些影響。另一種可能的方法是在此偏移頻率下以高階頻帶拒斥濾波器對資料進行數位篩選,但若執行方式不正確,所需的訊號都會隨突波一併移除。

要克服的另一個挑戰是如何修正緊密調變的三階互調失真突波。這些突波幾乎都會落在通帶內,並且通常是限制無雜散動態範圍的突波。當降取係數非常高時,這些頻調可能出現在衰減帶內。然而,大多數多頻系統不太可能發生此情況,因為其固有的瞬時頻寬比單頻系統更高,因此無法採用如此大型的降取濾波器。

最後,您必須在頻寬與動態範圍間進行取捨。降取可抑制 雜散元件與諧波,但其代價是瞬時頻寬減少。在這些取捨 間取得平衡,是為特定應用需求實現最佳性能的關鍵。

## 採用降取進行適當頻率規劃的優點

有效的頻率規劃可提供多項優勢,以強化接收器系統設計。其中一個優點是可改善突波抑制。數位降取濾波器可有效衰減突波,通常可達-85dBFS 左右的抑制等級,因此可提升訊號性能,並更妥善運用 ADC 動態範圍以達預期訊號,而非頻外雜散雜訊。

另一個優點是可減少 ADC 的資料輸送量。透過降取降低 ADC 的輸出資料率,您即可讓 ADC 與速度更低、體積更

小且更具成本效益的 FPGA 介接。減少傳輸資料不僅簡化了硬體需求,也讓系統能以雙頻或四頻運作,因此可同時取樣多個射頻(RF)頻帶。

在軟體中完全重新配置系統的能力,是在 ADC 上使用降取的另一個重要優勢。您可規劃 ADC 和 FPGA 間的硬體介面,以支援系統預期的最大資料速率,進而協助在較低資料速率或較窄頻寬下操作許多其他系統。軟體可重新配置的系統對於需要部署到多個方案中的應用程式尤其重要。

資源節省也是有效頻率規劃的顯著成果。不論是高速序列 資料通道或低電壓差動訊號對,只需較少輸出通道,就能 節省 ADC 和 FPGA 上的寶貴引腳,進而提高利用率。這 在具有印刷電路板面積和功率限制的高通道系統中尤為重 要。

## 理論示例:進行降取頻率規劃與

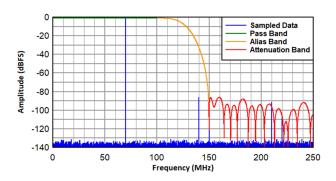

考慮交錯式 ADC 在 Fs 取樣公共射頻(RF)輸入訊號。交錯程序會以 Fs/2-Fin 導入突波,進而擾動所需訊號。採用降取 2 濾波器 (如图 4 所示) 可將此突波衰減至降取濾波器抑制限制內的電平。此外,降取程序可降低 ADC 的輸出資料率,實現符合成本效益的 FPGA 介接並簡化下游處理。此外,由於 SNR 中的 N (即雜訊) 減半,而 S (即訊號) 維持不變,寬頻雜訊降低會導入 3dB 流程增益。

图 4. 採用 70MHz FIN (降取係數為 2) 的 500MSPS 下理論資料降 取濾波器響應。

## 實際示例:進行降取頻率規劃與

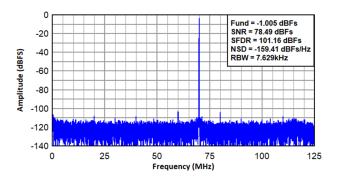

在 ADC 上使用降取可簡化頻率規劃程序,因為降低取樣率可有效縮減所需頻寬。將降取視為有選擇性地聚焦在頻譜較窄的部分。若聚焦於較窄的頻段,更多不必要的諧波或突波最終會落在感興趣的帶通之外,進而被濾除。以下範例使用 ADC3669 來示範進行頻率規劃時降頻的差異。图 5 說明 ADC 未使用 16384 點 FFT 大小執行降取時的傳統

頻譜擷取。您可以看到不必要的諧波位於頻內,並對性能 造成負面影響。

**图 5.** ADC3669 在 500MSPS 下以接近 70MHz FIN (無降取) 擷取 的實際頻譜。

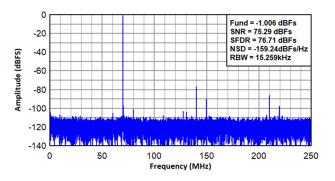

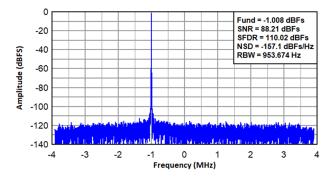

這些諧波可能是由 ADC 或某些外部類比頻率產生的附加雜訊。图 6 顯示 ADC 處於實際降取模式且降取係數為 2 的範例。各位會發現不需要的諧波突波現在已從頻外衰減,並被降取濾波器過濾掉。請注意,由於流程增益,還有額外的 +3dB 改善。

**图 6.** ADC3669 在 500MSPS 及接近 70MHz FIN (降取係數為 2) 下擷取的實際頻譜。

此外,FFT的解析度頻寬實際上也會減少二倍,因為我們在 FFT 計算中維持相同的點數。這有助於將類比頻率解析為更近的間隔。到目前為止,我們只提到了實際降取,此方式只是在沒有任何頻率變化的情況下過濾資料。如果每次降取時您的興趣訊號降到低於 Fs/4 ,則實際降取是很棒的。但如果要對超出此範圍的訊號進行降取呢?所需訊號通常不會集中在零頻率 (基頻) ,而是集中在某個中頻。這時複雜的降取就會發揮作用。具有較新數位功能的 ADC,如 ADC3669,在複雜的 DDC 階段中整合了 NCO 混波器。若混合有興趣訊號與 NCO 頻率,可在降取前將訊號移至基頻,讓您可在裝置頻寬內的任何位置充分利用降取訊號的優勢。

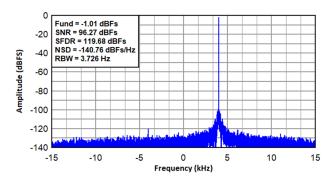

图 7 顯示在複雜降取模式下 ADC3669 的擷取,降取係數為 64 ,在使用 8192 點計算 FFT 時,產生有效取樣頻寬7.8125MHz。輸入頻率為 70MHz , NCO 頻率為71MHz。當訊號與 NCO 頻率混合時,訊號會轉變為基頻,產生約-1MHz 的音調。

图7. ADC3669 在 500MSPS 下擷取複數,降取係數為 64 (FIN=70MHz , Fnco=71MHz)。

ADC3669 可以高達 32768 的降取係數擷取窄頻,對高密度 RF 頻帶或有限通道間距的應用非常有利。如此高的係數進行降取可讓您放大感興趣的訊號,幾乎可濾除其他所有項目。ADC3669 等現代 ADC 提供的降取係數範圍可提供更多頻率規劃彈性,因為更容易濾除不必要的突波。图 8 顯示使用 8192 FFT 點計算出降取係數為 16384 的擷取,得到的解析度頻寬為 3.726Hz。即使突波位於基頻數千赫以內,您仍可輕易以高降取率篩選出突波。

图8. ADC3669 在 500MSPS 下擷取複雜頻譜,降取係數為 16384 (FIN=70MHz , Fnco=69.996MHz)。

由於 NCO 頻率比輸入訊號低 4kHz ,向下轉換的訊號會出現在正頻率偏移。在此降取模式下以 500MSPS 運作時,此 ADC 可圍繞可編程 NCO 頻率在 30.517kHz 範圍內進行訊號取樣。

#### 結論

頻率規劃是 ADC 型系統設計的重要層面,要應對應突波管理、動態範圍最佳化、 AAF 設計及有效率的資料處理等挑戰。透過預先執行深思熟慮的頻率規劃,您可避免奈奎斯特(Nyquist)區域重疊與時脈突波污染等常見陷阱,同時受益於改善雜散抑制與動態範圍,減少 ADC 數位介面或資料速率,以及節省 FPGA 資源等優勢。在這些取捨間仔細取得平衡,並運用 ADC 降取等功能,即可為各種應用實現高性能,軟體可重新配置的接收器系統,同時避免下次的取樣孔。

#### 相關網站

- 查看 SLYT861 ,探索射頻(RF)取樣資料轉換器中快速 跳頻的技術:探索在射頻(RF)取樣資料轉換器中的快速 跳頻,這是 Chase Wood 在 Analog Design Journal 2024 年 10 月發表的焦點。

- 了解 TIPL4701 取樣與資料速率間的關係:高速資料轉換器中的取樣與資料速率,降取 (DDC) 和內插

(DUC),作者: Jim Seton, 2017年8月發表。

- 閱讀 Chase Wood 發表的 Analyzing High-Bandwidth Spectrum Clusters (分析高頻寬頻譜群集),深入了 解高頻寬降取範例 (2024 年 5 月)。

- 使用射頻(RF)取樣頻率規劃工具、類比濾波器和 DDC 計算機,將射頻(RF)取樣頻率規劃最佳化。如需詳細規格,請參者 TI ADC3669 產品規格表。

**重要聲明**:本文所述德州儀器及其子公司相關產品與服務經根據 TI 標準銷售條款及條件。建議客戶在開出訂單前先取得 TI 產品及服務的最新完整資訊。 TI 不負責應用協助、客戶的應用或產品設計、軟體效能或侵害專利等問題。其他任何公司產品或服務的相關發佈資訊不構成 TI 認可、保證或同意等表示。

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2025. Texas Instruments Incorporated