# Application Note

# 모터 드라이브의 옵토 호환 절연 게이트 드라이버 UCC23513용 개별 DESAT

Jerome Shan, Martin Staebler, Roland Bucksch

Systems Engineering Industrial

#### 추상

강화 절연 게이트 드라이버는 산업용 모터 드라이브를 위한 3상 인버터의 주요 부품이며, DESAT는 이러한 애플리케이션에서 OCP(과전류 보호) 또는 SCP(단락 보호)에 대한 일반적인 접근 방식입니다. 이 애플리케이션 노트는 절연 비교기 AMC23C11을 사용한 개별 DESAT 구현으로 6핀 옵토 호환 강화 절연 게이트 드라이버 UCC23513을 기반으로 소형 폼 팩터, 비용 최적화 설계를 보여줍니다. 이 조합은 DESAT 보호 기능이 통합된 16핀 패키지 스마트 게이트 드라이버에 비해 더 작은 PCB 크기와 더 낮은 비용을 달성하며 소형 모터 드라이브 애플리케이션의 유연성을 높이는 데 도움이 됩니다. 또한 이 설계는 DESAT 기능의 애플리케이션 매개 변수를 구성할 수 있는 유연성을 유지합니다.

# 목차

2 DESAT가 통합된 절연 게이트 드라이버의 시스템 과제......4

| 3 UCC23513 및 AMC23C11을 통한 시스템 섭근 방식     | 5               |

|-----------------------------------------|-----------------|

| 3.1 시스템 개요 및 주요 사양                      | 5               |

| 3.2 회로도 설계                              | 6               |

| 3.3 레퍼런스 PCB 레이아웃                       | 10              |

| 4 시뮬레이션 및 테스트 결과                        | 10              |

| 4.1 시뮬레이션 회로 및 결과                       | 10              |

| 4.2 3상 IGBT 인버터를 사용한 테스트 결과             | 13              |

| 5 요약                                    | 16              |

| 6 참고 자료                                 | 17              |

| 7 개정 내역                                 | 17              |

|                                         |                 |

| 그림                                      |                 |

| 그림 1-1. 3상 인버터의 접지 고장으로 인한 단락           | 2               |

| 그림 1-2. 외부 브레이크 저항 단자의 배선 오류로 인한 단락     |                 |

| 그림 1-3. 통합 DESAT 보호 기능을 갖춘 UCC21750     |                 |

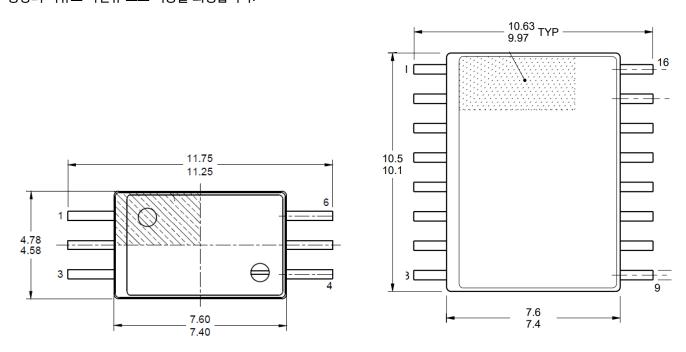

| 그림 2-1. 패키지 크기 비교: SO-6 대 SOIC-16       | 4               |

| 그림 3-1. 간소화된 시스템 블록 다이어그램               |                 |

| 그림 3-2. 제안된 회로도                         |                 |

| 그림 3-3. 예계 레이아웃의 위쪽 및 아래쪽               |                 |

| 그림 3-4. 스마트 게이트 드라이버 ISO5451의 일반적인 레이아웃 | 10              |

| 그림 4-1. 시뮬레이션 회로                        | <mark>11</mark> |

| 그림 4-2. 트리거된 DESAT의 시뮬레이션 결과            | 12              |

| 그림 4-3. 저압측 구동 테스트용 플랫폼                 |                 |

| 그림 4-4. 저압측 구동 테스트 시 단락 보호 지연           | 14              |

| 그림 4-5. 모터 테스트를 실행하기 위한 플랫폼             | 15              |

| 그림 4-6. 모터 테스트 실행 시 단락 보호 지연            | 16              |

| 상표                                      |                 |

모든 상표는 해당 소유권자의 자산입니다.

PSpice<sup>™</sup>, C2000<sup>™</sup>, and 론치패드<sup>™</sup> are trademarks of Texas Instruments.

INSTRUMENTS 머리말 www.ti.com

## 1 머리말

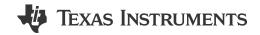

모터 드라이브를 위한 3상 인버터에서 OCP 및 SCP는 비정상적인 작동 조건으로 인한 손상으로부터 시스템을 보호하는 데 중요합니다. 션트 기반 시스템 수준 OCP 또는 SCP는 음극 DC 버스나 3개의 저압측 스위치를 통해 전류를 감지하는 방법으 로 구현되는 경우가 많습니다. 특히 폼 팩터와 시스템 비용이 중요한 많은 저전력 소형 모델에서는 특히 그렇습니다. 이러한 보호 기능은 arm 슛스루 및 위상 간 단락에서 자주 볼 수 있는 고장 패턴에 효과적입니다. 그러나 두 제품 모두 그림 1-1에서 보듯이, 고장 전류가 고압측 스위치를 통해 흐를 때 접지 단락을 감지할 수 없습니다. 게이트 드라이버의 DESAT 기능은 이 고 장으로부터 전원 스위치를 보호하는 데 도움이 됩니다. 사실 장치 수준 DESAT 보호는 3상 인버터의 이러한 모든 고장 모드에 효과적이기 때문에 많은 고전력 고성능 모델에서 널리 사용되고 있습니다.

그림 1-1. 3상 인버터의 접지 고장으로 인한 단락

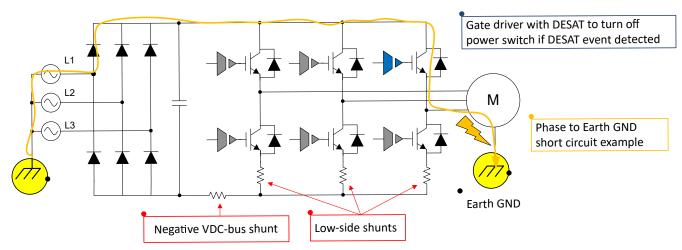

많은 산업용 모터 드라이브에는 전류를 음극 VDC 버스로 전환하고 재생 브레이크 작동 중에 전압이 너무 높아지면 벌크 커패 시터를 방전하는 재생 브레이크 스위치도 있습니다. 종종 이 브레이크 저항을 외부에 설치한 다음 드라이브의 특정 단자에 의 해 시스템에 연결해야 합니다. 사용자가 이 저항을 연결하는 데 오류가 있거나 저항이 매우 낮은 상태에서 실수로 사용한 경 우, 그림 1-2에 나와 있는 것처럼 시스템 컨트롤러에 의해 브레이크 작동이 시작되면 과전류 고장이 발생할 수 있습니다. 이 경 우 게이트 드라이버의 DESAT 기능은 문제를 감지하고 전원 스위치를 적시에 보호할 수 있습니다.

그림 1-2. 외부 브레이크 저항 단자의 배선 오류로 인한 단락

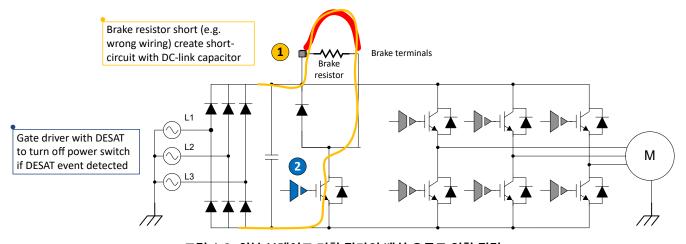

이러한 결함으로부터 시스템을 보호하는 일반적인 접근 방식은 CMOS 입력이 있는 UCC21750 강화 절연 게이트 드라이버 와 같이 DESAT 기능이 있는 절연 스마트 게이트 드라이버를 사용하는 것입니다. 그림 1-3에서 볼 수 있듯이, DESAT 핀은 IGBT가 켜질 때  $V_{CF}$ 의 전압 강하를 모니터링합니다. 이 전압 강하가 위로 올라가 설정된 임계값에 도달하면, 즉 과전류 또는 단락 상태가 발생하는 경우 게이트 드라이버의 출력을 한 번에 로우로 당기고 고장 출력 wii가 활성화되어 시스템 컨트롤러에 오류를 알립니다.

그림 1-3. 통합 DESAT 보호 기능을 갖춘 UCC21750

# 2 DESAT가 통합된 절연 게이트 드라이버의 시스템 과제

그림 2-1에 나와 있듯이 DESAT 기능이 통합된 강화 절연 스마트 게이트 드라이버는 일반적으로 16핀 SOIC 패키지로 제공되며, 이는 스트레칭된 SO-6 패키지에서 DESAT 기능이 없는 소형 게이트 드라이버보다 물리적으로 훨씬 더 큽니다. 이러한 3상 인버터 장치 6개를 전력 인버터 PCB에 배치한다고 가정하면 패키지 길이가 그에 따라 쌓이게 됩니다. 길이가 더 짧은 소형 장치를 사용하는 설계는 PCB 크기에 장점이 있습니다. 재생 브레이크 전원 스위치에서도 더 작은 게이트 드라이버가 애플리케이션 레이아웃 영역을 크게 줄이는 데 도움이 됩니다. 그러나 이러한 게이트 드라이버는 애플리케이션 회로 단순성과 비용상의 이유로 과전류 보호 기능을 희생합니다.

그림 2-1. 패키지 크기 비교: SO-6 대 SOIC-16

대안 접근 방식은 DESAT 없이 더 작은 풋프린트의 초소형 게이트 드라이버를 사용하고 절연 비교기를 사용하여 DESAT 기능을 개별적으로 구현하는 것입니다.

3개의 저압측 스위치 또는 3개의 고압측 스위치에서 DESAT 기능만 필요한 회로 구성의 경우 이 개별 DESAT 설계를 사용하면 6개 스위치가 모두 동일한 6핀 강화 절연 게이트 드라이버를 사용할 수 있으므로 하나의 애플리케이션 시스템에서 스마트 게이트 드라이버와 스마트 게이트 드라이버를 혼합하지 않아도 됩니다. 외부 DESAT 기능은 저압측 또는 고압측 게이트 드라이버에 각각 추가할 수 있습니다. 이 개별 DESAT 구현은 애플리케이션 설계에 DESAT 전압, DESAT 바이어스 전류, DESAT 감지 블랭킹 시간 및 DESAT 출력 디글리치 필터의 매개 변수를 구성하는 유연성을 추가하여 PWM 스위칭 잡음에 대한 내성을 높이는 데 도움이 됩니다.

# 3 UCC23513 및 AMC23C11을 통한 시스템 접근 방식

UCC23513은 4A 소스, 5A 싱크, 5.7kV<sub>RMS</sub> 강화 절연, 옵토 호환 단일 채널 게이트 드라이버입니다. AMC23C11은 조정 가능 임계값 및 래치 기능을 갖춘 빠른 응답, 강화, 절연 비교기입니다. 두 장치를 함께 사용하여 소형 게이트 드라이버에서 외부 DESAT를 달성하고 강화 절연으로 소형 회로 폼 팩터를 유지할 수 있습니다.

## 3.1 시스템 개요 및 주요 사양

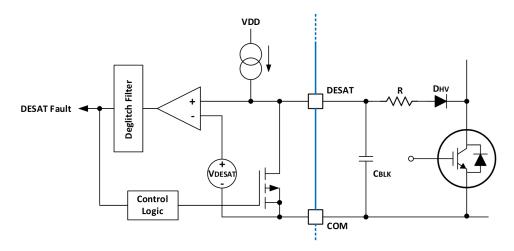

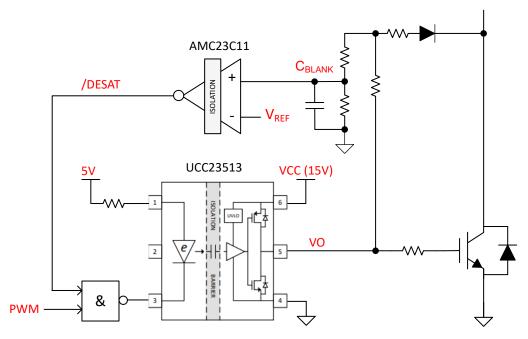

그림 3-1에는 제안된 회로의 간소화된 블록 다이어그램이 나와 있습니다. 여기서는 IGBT를 전원 스위치로 사용하며 이 설계는 약간의 변경 사항이 있는 전력 MOSFET에도 적합합니다.

그림 3-1. 간소화된 시스템 블록 다이어그램

NAND 게이트는 PWM 입력이 높을 때만  $V_{CE}$ 를 모니터링하는 기능을 실현하는 데 사용됩니다. 감지된  $V_{CE}$ 가 DESAT 임계 값 VREF를 초과하면 칩이 게이트 드라이버 입력을 비활성화합니다. 표 3-1에는 애플리케이션 회로의 주요 매개 변수가 나와 있습니다.

| 매개 변수                                                   | 값                                   | 설명                                                                         |

|---------------------------------------------------------|-------------------------------------|----------------------------------------------------------------------------|

| 강화 절연 게이트 드라이버                                          | UCC23513 또는 UCC23511 <sup>(1)</sup> | 6핀 DWY(SO-6) 패키지, 그림 2-1 참조.<br>8V UVLO를 지원하는 B 버전.                        |

| 절연 게이트 드라이버,<br>VDD                                     | +15V(IGBT), +12V(FET)               | 단극 공급                                                                      |

| DESAT V <sub>CE</sub> 임계값 전압,<br>V <sub>CE(DESAT)</sub> | 8.0 V                               | 구성 가능.<br>섹션 3.2.2를 참조하세요.                                                 |

| DESAT 바이어스 전류,<br>i <sub>BIAS(DESAT)</sub>              | 5.5 mA                              | 구성 가능.<br>섹션 3.2.2를 참조하세요.                                                 |

| DESAT 블랭킹 필터 시간 상수, t <sub>BLANK</sub>                  | 0.8µs                               | V <sub>CE(SAT)</sub> =12.5V에 유효. 구성 가능.<br>섹션 3.2.3의 방정식 8 및 표 3-2를 참조하세요. |

| DESAT 디글리치 필터<br>지연, t <sub>DEGLITCH</sub>              | 0.2μs                               | 구성 가능.<br>섹션 3.2.3의 방정식 10을 참조하세요.                                         |

| 리셋 기능이 있는 DESAT 래치                                      | 지원                                  | 비활성화할 수 있습니다.                                                              |

| DESAT 반응 시간 <sup>(2)</sup>                              | 약 1.1µs~1.6µs                       | 기본 구성입니다.<br>테스트 결과를 참조하세요.                                                |

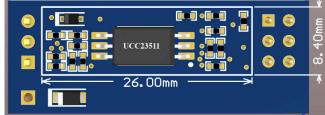

| 커넥터가 없는 PCB 크기                                          | 26 mm x 8.4 mm                      |                                                                            |

표 3-1. 설계의 주요 시스템 매개 변수

주

- (1) UCC23511은 UCC23513과 동일한 패키지의 1.5A 소스, 2A 싱크 장치입니다.

- (2) 보호 프로세스에 대한 명확하고 간단한 설명을 위해 이 애플리케이션 노트에서 감지된 전원 스위치의 전류가 설정된 트리거 레벨까지 DESAT 보호로 인해 전류가 떨어지기 시작하는 지점까지의 기간 동안 'ESAT 반응 시간'을 사용합니다.

UCC2351x 시리즈를 사용하여 IGBT, SiC 또는 MOSFET의 전력 스위치를 구동할 수 있습니다. UCC23511 및 UCC23513 모두 8.5mm 이상의 연면 및 간극으로 7.50mm x 4.68mm 바디 크기의 확장 SO-6 패키지로 제공됩니다. 두 장치는 표준 옵토커플러 기반 게이트 드라이버보다 상당한 성능과 안정성 업그레이드를 제공하는 동시에 핀 대 핀 호환성을 유지합니다. 이러한 성능 이점에는 높은 CMTI, 낮은 전파 지연, 작은 펄스 폭 왜곡이 포함됩니다. 입력 스테이지는 기존의 LED 대비 장기적인 안정성과 탁월한 노화 특성을 제공하는 에뮬레이트된 다이오드(e다이오드)입니다.

AMC23C11 절연 비교기는 바디 크기가 5.85mm × 7.50mm인 8핀 와이드 바디 SOIC 패키지로 제공됩니다. 이 장치는 VIN 핀의 입력 전압을 20mV에서 2V까지 조정 가능한 임계값과 비교하며 내부  $100\mu$ A 레퍼런스 전류 및 외부 저항으로 설정됩니다. 입력 전압 VIN이 레퍼런스 값 VREF보다 높으면 오픈 드레인 출력은 능동적으로 낮은 전압으로 끌어내립니다. VIN 이 트립 임계값 아래로 떨어지면 래치 핀에 의해 장치의 동작이 결정됩니다.

- 래치 핀을 로우로 잡아당기면 장치가 투명 모드로 설정되기 때문에 출력 상태가 변경되고 트립 임계값에 따라 입력 신호를 따릅니다.

- 래치 핀을 하이로 잡아당기면 장치가 래치 모드로 설정됩니다. 범위를 벗어난 상태가 감지되면, 이 래치를 해제하기 위해 래치 핀이 최소 4 µs 이상 낮게 당겨질 때까지 아웃 핀이 로우로 당겨지고 래치됩니다.

AMC23C11의 절연 장벽은 자기 간섭에 대한 저항력이 높고 최대 5kV<sub>RMS</sub>의 강화된 갈바닉 절연을 제공하는 것으로 인증되었습니다.

#### 3.2 회로도 설계

그림 3-2에서는 IGBT를 구동하기 위한 15V 단극 전원을 지원하는 설계 회로도를 보여줍니다. 몇 가지 사소한 변경으로 이 설계는 전원 MOSFET 구동 또는 양극 전원 공급 장치를 위한 12V 전원 공급 장치 설계에 적합할 수 있습니다. 자세한 내용은 레퍼런스 설계 TIDA-00448을 참조하십시오.

저항 R9~R14 및 고전압 다이오드 D1은 턴온 기간 동안 IGBT의 실제 V<sub>CE</sub>를 감지하고 절연 비교기 AMC23C11의 레퍼런스 전압 VREF에 따라 확장하는 데 사용됩니다. R10과 R11은 전력 손실을 분산하기 위해 병렬로 사용됩니다.

R14와 병렬로 연결된 커패시터 C14는 IGBT가 켜지는 동안 잘못된 트리거를 피하기 위해 블랭킹 시간을 설정합니다. IGBT 스위칭으로 인해 가능한 고전압 스파이크를 억제하기 위한 옵션으로 5.1V 제너 다이오드 D2가 추가됩니다. D2의 내부 커패 시턴스는 C14와 병렬로 연결되고 블랭킹 시간에 기여합니다. 이 테스트에서는 D2를 조립하지 않았습니다. 낮은 내부 커패시 턴스가 있는 고속 스위칭 다이오드 D1은 잘못된 DESAT 트리거를 방지하고 필요한 블랭킹 시간을 최소화하는 것이 좋습니다.

저전압 측은 3.3V 전원을 사용하여 C2000™ 및 Sitara MCU와 같이 널리 사용되는 MCU의 I/O 레벨을 직접 인터페이싱합니다. R6 및 C11은 래치가 활성화되지 않은 경우 비교기 출력에 대해 디글리치 지연(기본 0.2μs)을 설정합니다.

## 3.2.1 회로도

그림 3-2. 제안된 회로도

## 3.2.2 V<sub>CE(DESAT)</sub> 임계값과 DESAT 바이어스 전류 구성

저항 R9~R14는 V<sub>CE(DESAT)</sub> 임계값 및 DESAT 바이어스 전류 i<sub>BIAS(DESAT)</sub>를 조정하는 데 사용할 수 있습니다. 다음 방정식 은 다양한 DESAT 임계값 및 DESAT 바이어스 전류 구성에 대한 값을 신속하게 예측하기 위해 간소화됩니다.

절연 비교기 AMC23C11에는 내부 100μA 전류 소스 및 외부 저항 R9로 설정된 레퍼런스 전압 VREF가 있습니다. 이 설계 에서 R9의 값은 방정식 1에 따라 계산되어 VREF를 1.5V로 설정합니다. AMC23C11이 높은 이력 모드에서 작동하도록 1.5V가 선택되었습니다<sup>[1]</sup>.

$$R9 = \frac{VREF}{100 \text{ µA}} = 15 \text{ k}\Omega \tag{1}$$

R10과 R11은 DESAT 바이어스 전류를 결정하고 방정식 2에 따라 계산됩니다.

$$R10 = R11 = 2 \times \frac{VDD - V_{CE(DESAT)} - V_{FW(D1)} - R12 \times i_{BIAS(DESAT)}}{i_{BIAS(DESAT)} + i_{R13R14(DESAT)}}$$

(2)

여기에서

- VDD는 UCC23513의 공급 전압, IGBT 구동의 경우 15V

- V<sub>CE(DESAT)</sub>는 원하는 DESAT 임계값입니다. 이 설계에서는 기본적으로 8V입니다.

- V<sub>FW(D1)</sub>는 고전압 다이오드 D1의 순방향 전압입니다. 0.5V로 가정했습니다.

- R12는 일반적인 관행으로 100 Ω로 설정됩니다<sup>[9]</sup>.

- I<sub>R13R14(DESAT)</sub>는 R13과 R14를 통과하는 전류입니다. 0.5mA로 설정합니다. 낮게 설정하면 잡음 내성을 줄일 수 있습니

- i<sub>BIAS(DESAT)</sub>는 IGBT의 V<sub>CE</sub>가 V<sub>CE(DESAT)</sub>에 도달할 때의 DESAT 바이어스 전류입니다. 이 설계에서는 5.5mA로 설정되 어 있습니다.

따라서 이 설계에서 R10과 R11은 2kΩ로 계산할 수 있습니다.

V<sub>CE(DESAT)</sub>가 훨씬 작은 정상적인 IGBT 작동에서는 R10 및 R11의 전력 정격을 선택해야 합니다 R12 << R10이라고 가정 했을 때 방청식 3에 따라 간소화된 최대 전력 손실은 다음과 같습니다.

$$P_{R10, MAX} = P_{R11, MAX} = \frac{\left(VDD - V_{FW}(D1) - R12 \times i_{BIAS}(DESAT) - V_{CE}(SAT)\right)^{2}}{R10} \times PWM_{DUTY, MAX}$$

(3)

표 3-1의 기본 설정과 일반 V<sub>CE(SAT)</sub> 1.5V의 경우 P<sub>R10(MAX)</sub> 및 P<sub>R11(MAX)</sub>의 최대 전력 손실은 1000% PWM 듀티 사이클에 서도 약 69.8mW입니다.

R13 및 R14는 방정식 4 및 방정식 5에 따라 계산됩니다.

$$R13 = \frac{VREF}{i_{R13R14(DESAT)}} \tag{4}$$

R14 =

$$\frac{VDD - (i_{BIAS(DESAT)} + i_{R13R14(DESAT)}) \times R10 \div 2}{i_{R13R14(DESAT)}} - R13$$

(5)

매개 변수 값을 적용하면 R13은  $3k\Omega$ , R14는  $15k\Omega$ 이 됩니다.

#### 3.2.3 DESAT블랭킹 시간

DESAT 모니터링에 대한 블랭킹 시간인 t<sub>BLANK</sub> 는 IGBT의 턴온 이벤트에서 잘못된 TRIG를 방지하는 데 필요합니다. 커패 시터 C14와 R10~R14의 저항은 V<sub>CF</sub> 감지 신호가 절연 바교기의 입력 VCIN에 도달하도록 지연합니다. 지연은 전압 분할기 R13 및 R14의 등가 저항 R<sub>FO</sub>를 통해 C14의 충전 시간에 의해 제어됩니다.

$$R_{EO} \approx R13 // R14 = 3 \text{ k}\Omega // 15 \text{ k}\Omega = 2.5 \text{ k}\Omega$$

(6)

330pF의 C14를 선택하면 RC 필터의 시간 상수는 다음과 같습니다.

$$T_{au} = R_{EO} \times C14 = 2.5 \text{ k}\Omega \times 330 \text{ pF} = 0.82 \text{ }\mu\text{s}$$

(7)

실제 블랭킹 시간은 과전류 이벤트에서 IGBT의 실제  $V_{CE(SAT)}$  전압에 대한 구성된  $V_{CE(DESAT)}$  정상 상태 임계값의 비율에 따라 달라지며 방정식 8당 대략적으로 계산할 수 있습니다.

$$t_{BLANK} = -\ln\left(1 - \frac{V_{CE(DESAT)}}{V_{CE(SAT)}}\right) \times R_{EQ} \times C14$$

(8)

따라서 시스템에 사용되는 개별 IGBT에 따라 정상 상태  $V_{CE(DESAT)}$  임계값과 블랭킹 시간 상수를 조정하는 것이 중요합니다. 8V에서  $V_{CE(DESAT)}$  정상 상태 임계값의 기본 설정을 가진 일부 값은 아래 표를 참조하십시오.

#### 표 3-2. 기본 V<sub>CE(DESAT)</sub> 설정을 가진 유효 블랭킹 시간

|                               |       | 0=(0=0/11/ |     |     |     |     |

|-------------------------------|-------|------------|-----|-----|-----|-----|

| IGBT V <sub>CE(SAT)</sub> [V] | ≥14.5 | 12.5       | 11  | 10  | 9   | 8.5 |

| t <sub>BLANK</sub> [μS]       | 0.7   | 0.9        | 1.1 | 1.4 | 1.9 | 2.4 |

#### 경고

유효 블랭킹 시간이 구성된 블랭킹 시간 상수보다 훨씬 클 것이기 때문에 과전류 상태에서 IGBT의 실제  $V_{CE(SAT)}$ 에 너무 근접해 정상 상태 임계값  $V_{CE(DESAT)}$ 를 구성하지 마십시오.

#### 3.2.4 DESAT 디글리치 필터

R17과 C11은 시간 상수와 함께 nDESAT 출력 신호를 위한 디글리치 필터를 형성합니다.

$$\tau = 330 \Omega \times 2200 \,\mathrm{pF} = 726 \,\mathrm{ns}$$

(9)

최소 0.8V의 로우 레벨 입력을 가진 TTL 로직 IC에 이어서 디글리치 시간은 0.2  $\mu$ s에 불과합니다.

$$t_{DEGLITCH} = -\ln(1 - \frac{0.8 \, V}{3.3 \, V}) \times \tau = 202 \, \text{ns}$$

(10)

절연 비교기의 OUT 핀 내부 저항이 R17과 직렬로 연결되어 있다고 가정해 보십시오. 테스트된 디글리치 시간은 이 설계에서 약 340ns~380ns입니다. 자세한 내용은 섹션 4의 테스트 결과를 참조하세요.

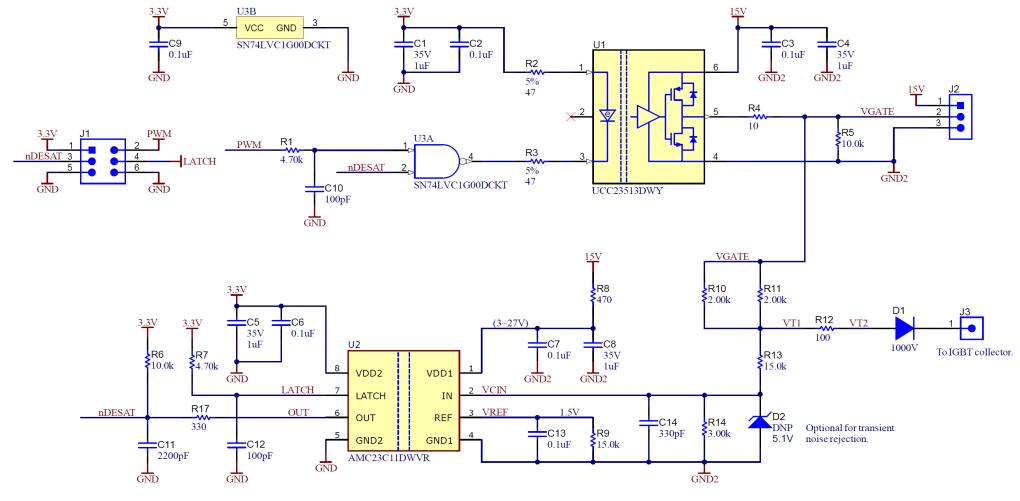

## 3.3 레퍼런스 PCB 레이아웃

4레이어 PCB에서 26mm x 8.4mm 활성 영역의 이 회로를 위한 레퍼런스 레이아웃이 적용되어 있습니다.

그림 3-3. 예제 레이아웃의 위쪽 및 아래쪽

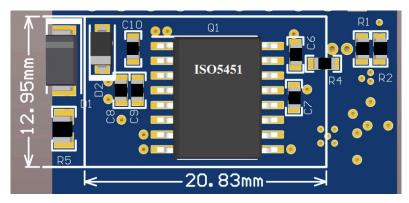

세심한 레이아웃 설계를 통해 게이트 드라이버와 비교기를 PCB의 반대쪽에 배치하면, 16핀 스마트 게이트 드라이버에 비해 더 작은 폼 팩터를 얻을 수 있으며, 더 작은 패키지 길이를 활용할 수 있습니다. 이에 비해 SOIC 16 패키지에 CMOS 입력이 있는 스마트 게이트 드라이버인 ISO5451의 일반적인 레이아웃은 그림 3-4,에 표시된 것처럼 PCB<sup>[10]</sup>의 활성 영역이 20.83mm x 12.95mm로, 그림 3-3의 UCC23513 및 AMC23C11 제안 설계보다 약 23.5% 더 큽니다.

그림 3-4. 스마트 게이트 드라이버 ISO5451의 일반적인 레이아웃

#### 4 시뮬레이션 및 테스트 결과

# 4.1 시뮬레이션 회로 및 결과

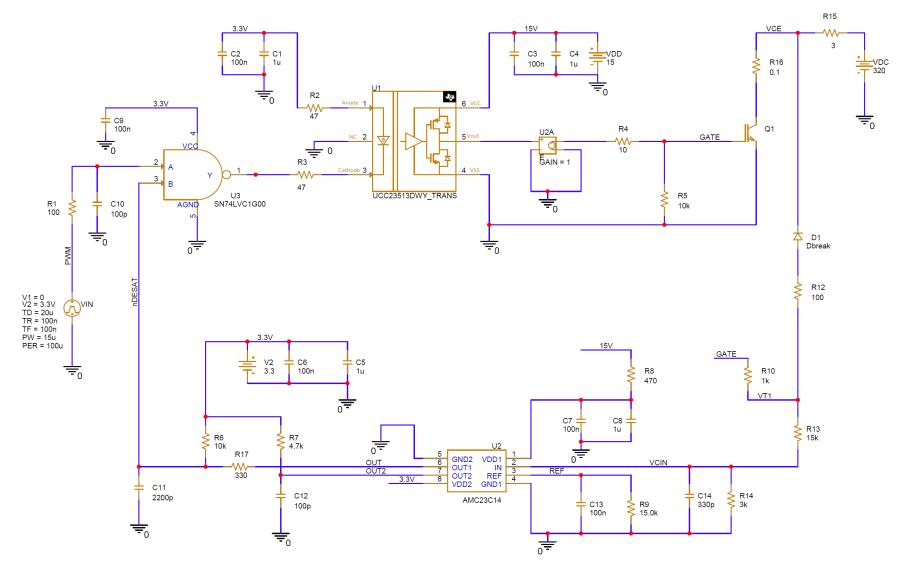

TI용 PSpice<sup>™</sup>에서 능동 브레이크 회로의 저압측 IGBT를 구동하는 회로를 위한 시뮬레이션이 이루어졌습니다. 그림 4-1에 서는 EMI 테스트용 회로도를 보여줍니다.

시뮬레이션은 AMC23C11의 모델이 TI.com에서 아직 사용할 수 없으므로 AMC23C14의 PSpice™ 시뮬레이션 모델을 사용합니다. 이 애플리케이션 노트에서 논의된 DESAT 구현의 경우 회로도의 OUT2(핀7)에 연결된 회로를 무시할 수 있으며 AMC23C14는 래치 입력(핀7)을 낮게 연결한 AMC23C11과 동일한 동작을 보여줍니다.

# 4.1.1 시뮬레이션 회로

그림 4-1. 시뮬레이션 회로

#### 4.1.2 시뮬레이션 결과

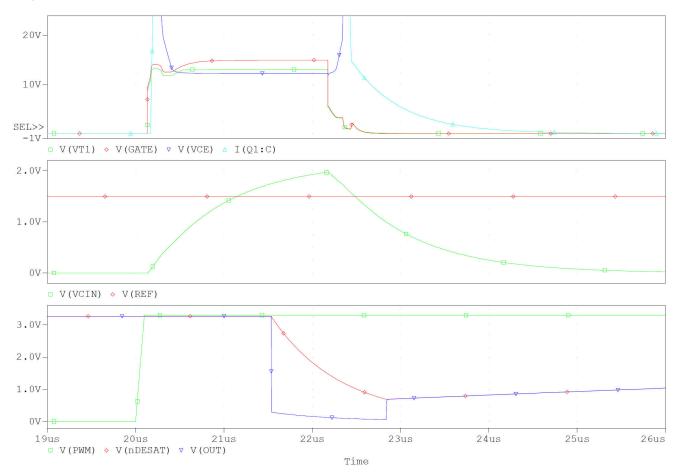

이 시뮬레이션에서 입력 PWM 신호는 10kHz, 15% 듀티 사이클 제곱 파형으로 설정됩니다. 다른 조건은 일반적인 애플리케이션 상황으로 설정됩니다. 그림 4-2은(는) DESAT 보호 케이스에 대한 시뮬레이션 결과입니다.

정적 상태에서는 PWM 입력이 낮기 때문에 NAND 게이트 출력이 높습니다. UCC23513은 입력 전류가 없기 때문에 게이트 의 출력 또한 낮습니다. 따라서 절연 비교기 AMC23C11의 VCIN 입력 전압은 0으로 끌어 옵니다. 출력 OUT 및 nDESAT는 하이로 끌어 옵니다.

입력 PWM 신호가 높아지면 nDESAT가 여전히 높은 경우 NAND 게이트의 출력이 낮게 전환됩니다. UCC23513은 게이트 에서 입력 전류와 높은 출력을 얻습니다. 그런 다음 IGBT U4가 켜지고  $V_{CE}$ 가  $V_{CE(SAT)}$ 로 떨어집니다. 감지 전류가 게이트에서 R10, R12 및 D1을 통해 IGBT U4의 컬렉터로 흐르고, VT1 노드의 전압이 IGBT의 실제  $V_{CE}$ 를 따르며, VCIN 전압은 R13과 R14의 저항 분할기를 통해 VT1 전압을 따릅니다. VCIN이 VREF의 임계값에 도달하지 않는 경우 비교기의 출력 및 필터링된 출력 nDESAT는 높게 유지됩니다.

그림 4-2. 트리거된 DESAT의 시뮬레이션 결과

위 그림과 같이 DESAT 트리거 프로세스의 경우 입력 PWM 신호(아래쪽 플롯의 녹색 트레이스)가 하이가 되면 IGBT의 게이트 전압(상단 플롯의 빨간색 트레이스)이 곧 상승합니다. 그리고 IGBT의  $V_{CE}$  감지 전압 VT1(상단 플롯에서 녹색 트레이스)도 상승합니다. 그런 다음 비교기의 입력 VCIN(중간 플롯의 녹색 트레이스)이 상승하기 시작하여 비례적으로 VT1 전압을 따라갑니다.

그런 다음 IGBT의  $V_{CE}$ (상단 플롯의 파란색 트레이스)가 떨어지기 시작합니다.  $V_{CE}$ 가 게이트 전압 아래로 떨어지면 VT1 전 압이  $V_{CE}$ 를 따르기 시작합니다.

VCINO VREF(중간 플롯의 빨간색 라인)에 의해 설정된 1.5V 트리거 임계값에 도달하기 전에 비교기의 출력(아래쪽 플롯의 파란색 트레이스)은 높게 유지됩니다. VCIN이 트리거 레벨에 도달하면 일반적으로 240ns의 내부 전파 지연으로 비교기 출력이 낮아지게 됩니다. nDESAT의 필터링된 출력(아래쪽 플롯의 빨간색 트레이스)도 떨어지기 시작합니다.

www.ti.com 시뮬레이션 및 테스트 결과

NAND 게이트 U3에 대한 입력으로, nDESAT가 U3의 음의 방향 임계값을 트리거하면 게이트 드라이버 U1의 입력 전류가 차단되고 출력 게이트가 풀다운됩니다. 따라서 IGBT도 꺼지며  $V_{CE}$ 가 곧 상승합니다. 이 프로세스는 회로의 DESAT 보호입니다.

게이트가 풀다운되면 VT1도 풀다운되고 VCIN이 드롭되기 시작합니다. VCIN이 비교기 입력 임계값 아래로 떨어지면 출력이다시 상승합니다. AMC23C14의 경우가 여기에 해당합니다.

AMC23C11은 래치 입력인 핀 7이 로우로 연결되어 있을 때 위의 프로세스와 정확히 동일하게 작동합니다. 래치 핀을 하이로 당기면 비교기의 출력 핀의 출력이 래치됩니다. 래치 핀이 최소 4  $\mu$ s 동안 로우 상태로 당겨져서 래치 상태를 해제합니다.

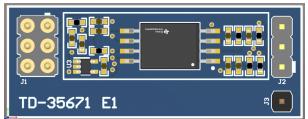

## 4.2 3상 IGBT 인버터를 사용한 테스트 결과

테스트는 DESAT 보호에 대해 제안된 회로의 샘플 보드에서 수행되었습니다. 샘플 보드가 (1) 저압측 브레이크 IGBT의 게이트 드라이버와 (2) 3상 모터 드라이브 인버터에서 고압측 스위치 IGBT의 게이트 드라이버로 사용되는 두 가지 사례를 테스트했습니다.

# 4.2.1 브레이크 IGBT 테스트

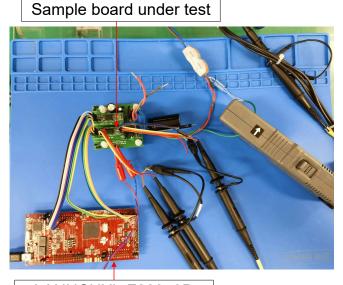

그림 4-3에서는 저압측 브레이크 IGBT 게이트 구동 테스트를 위한 플랫폼을 보여줍니다. LAUNCHXL-F28379D의 C2000 ™ 론치패드™는 저압측 IGBT를 구동하기 위해 10% 듀티 사이클에서 10kHz 또는 각 100μs 기간에 10μs의 타임으로 일련의 PWM 펄스를 생성하는 시스템 컨트롤러로 사용되었습니다. 또한 이 론치패드는 AMC23C11의 래치 입력에 대한 높은 출력을 생성하고 GPIO를 사용하여 nDESAT 신호를 모니터링합니다.

Toktronix

2 SEMES NOTE STOURL COCK OF THE SEMES NOTE STOURL COCK

LAUNCHXL-F28379D

그림 4-3. 저압측 구동 테스트용 플랫폼

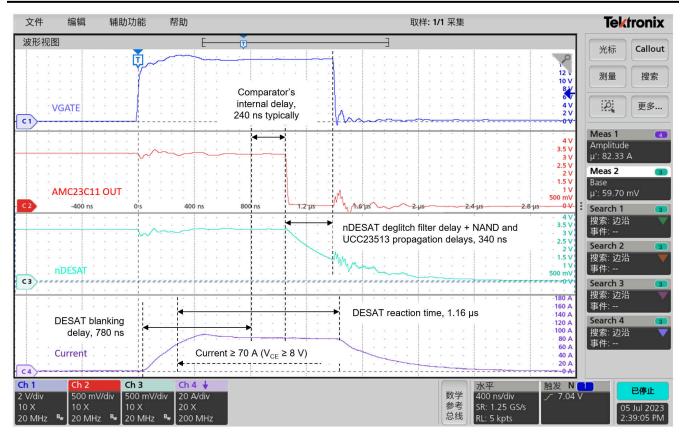

OCP 또는 SCP 상황을 테스트하기 위해 600V 10A 개별 IGBT를 사용하고 1.5Ω 3W 저항 2개를 병렬로 사용하여 브레이크 저항을 에뮬레이션합니다. 저항은 IGBT 컬렉터와 350V DC+ 레일 사이에 삽입됩니다. 검사 결과는 그림 4-4에 표시됩니다.

시뮬레이션 및 테스트 결과 www.ti.com

그림 4-4. 저압측 구동 테스트 시 단락 보호 지연

이 테스트에서 IGBT가 켜지면(t=0 s), 컬렉터 전류가 상승하기 시작했고 곧 약 90A(t=480ns)에서 포화되었습니다. 테스트를 거친 IGBT의 데이터 시트에 따르면 컬렉터 전류가 70A에 도달하면  $V_{CE}$ 가 회로에 대해 설정된 8V 트리거 레벨로 증가합니다. DESAT는 약 780ns의 블랭킹 시간이 지난 후 절연 비교기 AMC23C11에서 감지되었습니다. 그런 다음 일반적으로 240ns의 내부 지연 후 AMC23C11의 출력값이 낮음( $t=1.04\mu s$ )으로 전환되고 래치됩니다(래치가 하이로 설정된 경우). 약 340ns의 nDESAT에 대한 디글리치 필터의 지연 후 NAND 게이트 NTALVC1G00의 출력이 하이로 전환되고 USS23513 의 입력 전류가 차단되어 게이트 드라이버가 NTALVE VICTIGIC V

www.ti.com 시뮬레이션 및 테스트 결과

#### 4.2.2 위상 간 단락이 발생한 3상 인버터에 대한 테스트 결과

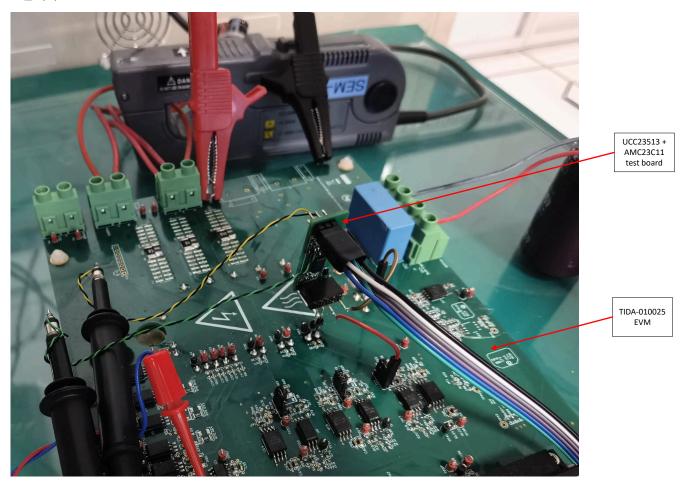

TI 레퍼런스 설계의 3상 인버터 플랫폼인 TIDA-010025에 대한 테스트는 ACIM 모터를 구동할 때 위상 간 단락 상태를 점검하기 위해 수행되었습니다. 이러한 테스트에서 U 위상 고압측 IGBT의 게이트 드라이버는 제안된 회로의 샘플 보드로 대체되었습니다.

그림 4-5. 모터 테스트를 실행하기 위한 플랫폼

TIDA-010025 레퍼런스 설계에는 전원 보드에 1200V, 25A PIM 전원 모듈이 포함되어 있으며, 3상 인버터 스테이지에서 동일한 등급의 IGBT 6개가 통합되어 있습니다. 테스트 준비를 위해, 먼저 U 위상 고압측 IGBT에 대한 원래 게이트 구동 저항을 제거한 다음 VGATE 출력, 15V 전원 공급 장치 및 샘플 보드의 VCE 감지 단자를 전원 보드에 연결했습니다. 레퍼런스 설계 자체 하드웨어 OCP 기능의 영향을 피하기 위해 3상 모두에서 기존  $10m\Omega$ 에 병렬로  $5m\Omega$  션트 저항을 추가하여 OCP 트리거 레벨을 72A로 3배 늘렸습니다. 또한 IGBT의 출력 특성을 확인한 후 샘플 보드에서  $V_{CE(SAT)}$ 가 약 45A 콜렉터 전류에 해당하는 2.5V까지 올라갈 때 DESAT 임계값에 도달하도록 일부 변경을 수행했습니다. 이 테스트 중에 먼저 모터(부하 없음)를 50rps로 작동한 다음 전력 보드의 단자에 연결된 회로 차단기로 인버터의 U 및 W 위상을 단락시킵니다. 그림 4-6은(는) 테스트 결과 파형입니다.

요약 www.ti.com

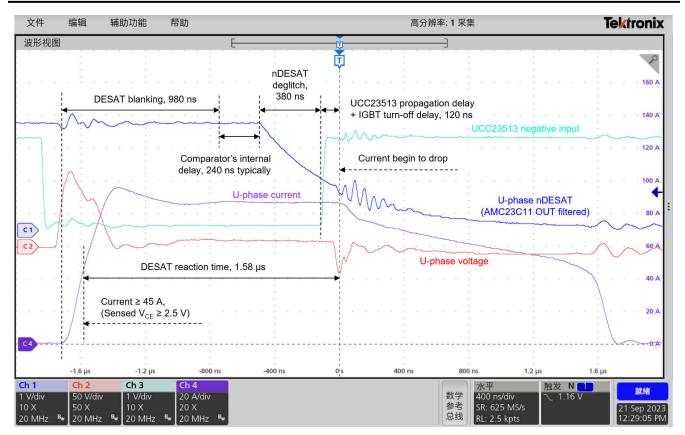

그림 4-6. 모터 테스트 실행 시 단락 보호 지연

회로 차단기가 켜지면 U 및 W 위상이 단락되고 U 위상 전류가 빠르게 상승하기 시작했습니다. 포화 전류는 곧 약 95A의 피크에 도달한 다음 약간 떨어지고 약 86A에서 안정화됩니다. 980ns의 점멸 시간 후 AMC23C11이 DESAT 상태를 감지했습니다. 일반적으로 240ns의 또 다른 내부 전파 지연 후 출력 OUT이 낮음으로 전환됩니다. nDESAT가 NAND 게이트 입력의음극 방향 임계값으로 떨어지고 UCC23513의 입력 전류를 차단하는 데 약 380ns가 걸렸습니다. 그런 다음 게이트 드라이버는 IGBT의 전류가 떨어지기 시작하는 데 약 120ns가 걸렸습니다. DESAT 반응 시간은 총 1.58μs 였습니다.

저압측 구동 테스트의 결과에는 몇 가지 차이점이 있습니다. 테스트한 두 IGBT의 특성과 애플리케이션 회로의 차이와 DESAT 임계값 조정이 이러한 변화의 원인입니다.

## 5 요약

이 애플리케이션 노트에서는 DESAT 보호를 위한 절연 비교기와 소형 절연 단순 게이트 드라이버의 결합은 검증되었습니다. 개별 접근 방식은 DESAT가 통합된 16핀 스마트 게이트 드라이버에 비해 설계 크기를 줄입니다. 이 접근 방식은 또한 임계값, 바이어스 전류, 블랭킹 시간 및 디글리치 필터와 같은 DESAT 기능의 주요 매개 변수를 구성할 수 있는 유연성을 추가합니다. 개별 접근 방식은 MCU에 의해 재설정할 수 있는 DESAT 래치 기능도 제공합니다.

이 개념은 또한 양극 게이트 드라이버 공급 장치로 확장할 수 있으며, 저압측 및 고압측 게이트 드라이버 모두에 동일한 개념을 가지고 있습니다. 이러한 애플리케이션에 대한 자세한 내용은 TIDA-00448을 참조하십시오.

www.ti.com 참고 자료

# 6 참고 자료

- 1. 텍사스 인스트루먼트, AMC23C11: 조정 가능 임계값 및 래치 기능을 가진 빠른 응답, 강화 절연 비교기, 데이터 시트.

- 2. 텍사스 인스트루먼트, UCC23513: 4A 소스, 5A 싱크, 5.7kVRMS Opto 호환 단일 채널 절연 게이트 드라이버 데이터 시트.

- 3. 텍사스 인스트루먼트, UCC23511: 1.5A 소스, 2A 싱크, 5.7kVRMS Opto 호환 단일 채널 절연 게이트 드라이버 데이터 시트.

- 4. 텍사스 인스트루먼트, UCC21750: 능동적 보호, 절연 아날로그 감지 및 높은 CMTI 기능이 있는 SiC/IGBT용 10A 소스/싱크 강화 절연 단일 채널 게이트 드라이버 데이터 시트.

- 5. 텍사스 인스트루먼트, AMC23C14: Dual듀얼, 빠른 응답, 강화 절연, 윈도우 콤퍼레이터, 임계값 조정 가능 데이터 시트.

- 6. 텍사스 인스트루먼트, ISO5451: 능동적 보호 기능을 지원하는 5.7kVrms, 2.5A/5A 단일 채널 절연 게이트 드라이버, 데이터 시트.

- 7. 텍사스 인스트루먼트 TI용 PSpice 설계 및 시뮬레이션 툴.

- 8. 텍사스 인스트루먼트, UCC21750: UCC217xx 및 ISO5x5x에서 DESAT 감지 임계값을 조정하려면 어떻게 합니까? FAO.

- 9. 텍사스 인스트루먼트, TIDA-00448: 강화 디지털 아이솔레이터를 지원하는 유연한 고전류 IGBT 게이트 드라이버 레퍼런스 설계.

- 10. 텍사스 인스트루먼트, TIDA-00638: 태양광 인버터용 능동 밀러 클램프를 지원하는 절연 게이트 드라이버 전력계용 레퍼런스 설계 레퍼런스 설계.

- 11. 텍사스 인스트루먼트, TIDA-010025: 옵토 에뮬레이트 입력 게이트 드라이버를 갖춘 200~480 VAC 드라이브를 위한 3 상 인버터 게이트 레퍼런스 설계 레퍼런스 설계,

## 7 개정 내역

참고: 이전 개정판의 페이지 번호는 현재 버전의 페이지 번호와 다를 수 있습니다

| 날짜           | 개정 | 참고    |

|--------------|----|-------|

| October 2023 | *  | 초기 발매 |

## 중요 알림 및 고지 사항

TI는 기술 및 신뢰성 데이터(데이터시트 포함), 디자인 리소스(레퍼런스 디자인 포함), 애플리케이션 또는 기타 디자인 조언, 웹 도구, 안전 정보 및 기타 리소스를 "있는 그대로" 제공하며 상업성, 특정 목적 적합성 또는 제3자 지적 재산권 비침해에 대한 묵시적 보증을 포함하여(그러나 이에 국한되지 않음) 모든 명시적 또는 묵시적으로 모든 보증을 부인합니다.

이러한 리소스는 TI 제품을 사용하는 숙련된 개발자에게 적합합니다. (1) 애플리케이션에 대해 적절한 TI 제품을 선택하고, (2) 애플리케이션을 설계, 검증, 테스트하고, (3) 애플리케이션이 해당 표준 및 기타 안전, 보안, 규정 또는 기타 요구 사항을 충족하도록 보장하는 것은 전적으로 귀하의 책임입니다.

이러한 리소스는 예고 없이 변경될 수 있습니다. TI는 리소스에 설명된 TI 제품을 사용하는 애플리케이션의 개발에만 이러한 리소스를 사용할 수 있는 권한을 부여합니다. 이러한 리소스의 기타 복제 및 표시는 금지됩니다. 다른 모든 TI 지적 재산권 또는 타사 지적 재산권에 대한 라이선스가 부여되지 않습니다. TI는 이러한 리소스의 사용으로 인해 발생하는 모든 청구, 손해, 비용, 손실 및 책임에 대해 책임을 지지 않으며 귀하는 TI와 그 대리인을 완전히 면책해야 합니다.

TI의 제품은 ti.com에서 확인하거나 이러한 TI 제품과 함께 제공되는 TI의 판매 약관 또는 기타 해당 약관의 적용을 받습니다. TI가 이러한 리소스를 제공한다고 해서 TI 제품에 대한 TI의 해당 보증 또는 보증 부인 정보가 확장 또는 기타의 방법으로 변경되지 않습니다.

TI는 사용자가 제안했을 수 있는 추가 또는 기타 조건을 반대하거나 거부합니다.

주소: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023, Texas Instruments Incorporated

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2024, Texas Instruments Incorporated