*Errata***AM275x プロセッサ シリコン エラッタ、シリコン リビジョン 1.0****概要**

この文書では、機能仕様に対する既知の例外 (アドバイザリ) について説明します。本文書には、使用上の注意事項も記載されています。使用上の注意は、デバイスの動作が推定または文書化された動作と一致しない可能性がある状況を示しています。これには、デバイスの性能や機能の正確さに影響を与える動作が含まれる場合があります。

**目次**

|                                         |           |

|-----------------------------------------|-----------|

| <b>1 使用上の注意およびアドバイザリ マトリックス</b> .....   | <b>2</b>  |

| 1.1 サポート対象デバイス.....                     | 3         |

| <b>2 シリコン リビジョンの使用上の注意とアドバイザリ</b> ..... | <b>4</b>  |

| 2.1 シリコンの使用上の注意.....                    | 4         |

| 2.2 シリコンのアドバイザリ.....                    | 5         |

| <b>3 商標</b> .....                       | <b>16</b> |

| <b>4 改訂履歴</b> .....                     | <b>16</b> |

## 1 使用上の注意およびアドバイザリ マトリックス

使用上の注意マトリックスには、すべての使用上の注意と該当するシリコン リビジョンがリストされます。アドバイザリ マトリックスには、すべてのアドバイザリ、影響を受けるモジュール、および該当するシリコン リビジョンがリストされます。

**表 1-1. 使用上の注意マトリックス**

| ID   | タイトル                                                                | 影響を受けるシリコンの<br>リビジョン |

|------|---------------------------------------------------------------------|----------------------|

|      |                                                                     | AM275x 1.0           |

| R5F  | <a href="#">i2284</a> — Cortex-R5F は、アドバタイズされた NMI をサポートしていません      | あり                   |

| OSPI | <a href="#">i2351</a> — OSPI コントローラは NAND FLASH で連続読み取りモードをサポートしません | あり                   |

| C71x | <a href="#">i2424</a> — PLL プログラミング シーケンスにより、PLL が不安定になる場合があります     | あり                   |

**表 1-2. アドバイザリ マトリックス**

| モジュール    | 説明                                                                                      | 影響を受けるシリコンの<br>リビジョン |

|----------|-----------------------------------------------------------------------------------------|----------------------|

|          |                                                                                         | AM275x 1.0           |

| ECC_AGGR | <a href="#">i2049</a> — 保留中の ECC アグリゲータ割り込みのため、IP クロック ストップ/リセット シーケンスがハングアップする可能性があります | あり                   |

| RAT      | <a href="#">i2062</a> - RAT: エラー ログ ディスエーブルが設定されている場合でも、エラー割り込みが発生します                   | あり                   |

| C71x     | <a href="#">i2120</a> — C71x:LEZR を使用して転置されたストリームで、SE が非パリティ エラー検出でハングアップします            | あり                   |

| PSIL     | <a href="#">i2137</a> - PSIL: クロック停止動作により、未定義の動作が発生する可能性があります」を追加                       | あり                   |

| OSPI     | <a href="#">i2189</a> - OSPI: コントローラ PHY のチューニング アルゴリズムを追加                              | あり                   |

| IA       | <a href="#">i2196</a> - IA:IA でデッドロック シナリオが発生する可能性があります                                 | あり                   |

| C71x     | <a href="#">i2199</a> — C71x: 非アライメントの転置されたストリームが AM1 循環バッファ境界を越えた場合に、SE が誤ったデータを返します   | あり                   |

| OSPI     | <a href="#">i2249</a> - OSPI: DDR タイミングが動作不能の内部 PHY ループバックおよび内部パッド ループバック クロック モード」を追加  | あり                   |

| PRG      | <a href="#">i2253</a> - PRG: CTRL_MMR STAT レジスタは、POK スレッショルド障害の信頼性が低いインジケータです」を追加       | あり                   |

| MCAN     | <a href="#">i2278</a> - MCAN: 同じメッセージ ID で構成された専用 Tx バッファからのメッセージ送信順序が検証されませんを追加        | あり                   |

| MCAN     | <a href="#">i2279</a> - MCAN: 同じメッセージ ID で構成された専用 Tx バッファと Tx キューの仕様の更新                 | あり                   |

| USART    | <a href="#">i2310</a> - USART: 「タイムアウト割り込みの誤ったクリア / トリガ」を追加                             | あり                   |

| USART    | <a href="#">i2311</a> — USART スプリアス DMA 割り込み                                            | あり                   |

| MMCS     | <a href="#">i2312</a> - MMCS: HS200 および SDR104 コマンド タイムアウト ウィンドウが小さすぎます」を追加             | あり                   |

| C71x     | <a href="#">i2377</a> — RAT 入力信号 rbytecnt および wbytecnt 計算が間違っています                       | あり                   |

| OSPI     | <a href="#">i2383</a> - OSPI: 2 バイト アドレスは、PHY DDR モードではサポートされていません                      | あり                   |

| CPSW     | <a href="#">i2401</a> - CPSW: ホストのタイムスタンプにより、CPSW ポートがロックされます」を追加                       | あり                   |

| C71x     | <a href="#">i2427</a> — 安全性: RAM SEC が誤った RAM 書き込みを引き起こす可能性があり、L2&MBOX のメモリ破損が発生します     | あり                   |

| C71x     | <a href="#">i2431</a> - BCDMA: Rx チャネルが特定のシナリオでロックアップする可能性があります                         | あり                   |

| eMMC     | <a href="#">i2435</a> — ブート:eMMC ブートの ROM タイムアウトが長すぎる                                   | あり                   |

| C71x     | <a href="#">i2436</a> — RX CHAN CFG レジスタの BCDMA_RX_IGNORE_LONG 設定が機能しません                | あり                   |

| CPSW     | <a href="#">i2438</a> - CPSW: VLAN 追加/削除によるホストからイーサネットへのチェックサム生成                        | あり                   |

| パルサー     | <a href="#">i2449</a> — Pulsars には RAT MMR パリティがありません。Diagnostic RAT5 との不一致です           | あり                   |

| PWM      | <a href="#">i2455</a> — PWM: 3 つすべての PWM からの EINT 割り込みは、メイン パルサにルーティングされません             | あり                   |

## 1.1 サポート対象デバイス

本文書は、以下のデバイスをサポートしています。

- AM275x

サポート対象デバイスのリファレンス文書:

- 『AM275x プロセッサ テクニカル リファレンス マニュアル』(SPRUJC6)

- AM275x プロセッサ データシート (SPRSPB0)

## 2 シリコン リビジョンの使用上の注意とアドバイザリ

このセクションには、このシリコン リビジョンの使用上の注意およびアドバイザリが記載されています。

### 2.1 シリコンの使用上の注意

**i2284**

**割り込み:Cortex-R5F は、アドバタイズされた NMI をサポートしていません**

#### 詳細

NMI は、ソフトウェアで一定時間の割り込みをディセーブルにすることによって引き起こされる、重要な割り込みに対する不定のレイテンシ応答を防止することを目的としています。このような NMI の定義では、ソフトウェアがそのレベルで割り込みのマスクを開始できないことです。(Cortex R5F 上の FIQ)。

R5F には NMFI オプションがあり、SEC MMR で構成できますが、VIM ではすべての割り込みはマスク可能です。したがって、重要な割り込みは VIM でブロックすることができ、有限な割り込み応答時間を持つことは検証されません。

これは本質的に目的を破っています。

その他の Cortex R5 実装では、割り込みコントローラ定義の一部として 1 つまたは複数の重要なチャネルの割り込みを無効にする機能を備えていないため、NMI がサポートされています。

#### 回避方法

なし

**i2351**

**OSPI:ダイレクト アクセス コントローラ(DAC) は、NAND フラッシュによる連続読み取りモードをサポートしていません**

#### 詳細:

OSPI コントローラは、OSPI コントローラへの内部 DMA バス要求の間に、フラッシュメモリへの CSn 信号を (設計意図によって) デアサートできるため、OSPI ダイレクト アクセス コントローラ (DAC) は、NAND フラッシュによる連続読み取りモードをサポートしていません。

この問題が発生するのは、一部の OSPI/QSPI NAND フラッシュメモリで提供される「連続読み取り」モードでは、バーストトランザクション全体にわたってチップ セレクト入力がアサートされたままにならなければならぬためです。

SOC 内部 DMA コントローラと他のイニシエータは 1023B 以下のトランザクションに制限されており、アービトレイション / キューイングは、さまざまな DMA コントローラの内部、または任意の DMA コントローラと OSPI ペリフェラルの間の相互接続の両方で実行できます。その結果、OSPI コントローラへのバス要求が遅延し、外部 CSn 信号がデアサートされます。

NOR フラッシュメモリは CSn デアサートの影響を受けません。連続読み取りモードは想定通りに動作します。

#### 回避方法:

ソフトウェアは、ページ / バッファ付き読み取りモードを使用して NAND フラッシュにアクセスできます。

**i2424**

**PLL:PLL プログラミング シーケンスにより、PLL が不安定になる場合があります**

#### 詳細:

PLL プログラミング シーケンスが変更され、使用される場合、PLL キャリブレーションをイネーブルにする前にすべてのキャリブレーション フィールドが確実に構成されるようになりました。キャリブレーション ロジックの制御に対する変更に加えて、PLL が有効化されている間に PLL パラメータが変更されないように、他の変更も実装されています。

i2424 (続き)

**PLL:PLL プログラミング シーケンスにより、PLL が不安定になる場合があります**

整数モードの場合、ソフトウェアはキャリブレーション対応 PLL の PLL キャリブレーション機能を有効化します。以前のソフトウェアは、CAL\_LOCK のアサート後にキャリブレーション モードを調整しました。これらの書き込みにより、一部のデバイスでは PLL ロックが失われることが確認されています。また、影響を受けやすいデバイスでも、ロックの喪失は断続的に発生しますが、喪失が発生すると、依存する回路が誤った周波数で動作します。この誤った周波数は、アルゴリズムの実行速度の低下や通信障害として現れことがあります。

**影響の制限:PLL** がフラクショナル モードの場合、キャリブレーション ロジックは使用できません。したがって、フラクショナル モードを使用するようにプログラムされている PLL では、キャリブレーションのプログラミングに関連して障害が発生する可能性が低くなります。しかし、全 PLL シーケンスに変更があるため、新しいソフトウェアはすべてのユーザーに推奨されます。

**回避方法:**

SYSFW で `clk_pll_16fft_cal_option4()` を使用しないでください。PLL 構成を変更するときは、SDK v10.0 以降で更新された PLL プログラミング シーケンスを使用するようにします。

## 2.2 シリコンのアドバイザリ

i2049

**ECC\_AGGR:保留中の ECC アグリゲータ割り込みのため、IP クロック ストップ/リセット シーケンスがハングアップする可能性があります」の詳細を更新**

**詳細:**

ECC アグリゲータ モジュールは、安全エラーの発生 (発生は稀) を集約し、ソフトウェアへの通知用の割り込みを生成するために使用されます。ECC アグリゲータにより、安全エラー割り込みのイネーブル/ディスエーブルおよびクリアをソフトウェア制御できます。

ソフトウェアが IP 上でクロック ストップ/リセット シーケンスを実行している場合、IP に関連付けられている ECC アグリゲータ インスタンスがアイドル ステータスでないため、シーケンスが完了しない可能性があります。ECC アグリゲータのアイドル ステータスは、イネーブルまたはディスエーブルのいずれかの保留中の安全エラー割り込みに依存します。これらは、ソフトウェアでクリアされていないものです。その結果、未処理の安全エラー割り込みが発生していても、IP のクロック ストップ/リセット シーケンスが完了しないこと (ハングアップ) があります。

影響を受ける ECC\_AGGR は、テクニカル リファレンス マニュアル (TRM) に記載されているレジスタ オフセット 0h の REV レジスタ値で決定できます。REV レジスタは、そのフィールド内の ECC\_AGGR バージョンを次のようにエンコードします。

v[REVMAJ].[REVMIN].[REVRTL]

v2.1.1 以前の ECC\_AGGR バージョンが影響を受けます。ECC\_AGGR バージョン 2.1.1 以降は影響を受けません。

影響が発生する例:

REVMAJ = 2

REVMIN = 1

REVRTL = 0

上記の値は ECC\_AGGR バージョン v2.1.0 にデコードされますが、これは影響を受けます。

影響が発生しない例:

REVMAJ = 2

REVMIN = 1

**i2049 (続き)**

**ECC\_AGGR: 保留中の ECC アグリゲータ割り込みのため、IP クロック ストップ / リセット シーケンスがハングアップする可能性があります**」の詳細を更新

REVRTL = 1

上記の値は ECC\_AGGR バージョン v2.1.1 をデコードしますが、これは影響を受けません。

**回避方法:**

一般的な注意事項:

ECC アグリゲータのクロック停止は、機能安全使用事例ではサポートされていません。

ソフトウェアは、機能安全以外の使用事例において、次の回避方法を使用する必要があります。

1. IP のすべての ECC アグリゲータ割り込みを無効化します

2. 保留中の割り込みをすべて処理してクリアします

3. ステップ 3:

a. ECC アグリゲータへのすべての割り込みソースを無効化してから、クロック ストップ / リセット シーケンスを実行します。

b. クロック ストップ / リセット シーケンスを実行しながら、保留中の割り込みの処理 / クリアを続けます。

ソフトウェアでは、割り込みが外部刺激であるため、ステップ 3 で次の 2 つのオプションを利用できます。

1. クロック ストップ / リセット シーケンスを実行する前に、保留中の ECC\_AGGR 割り込みを生成できるすべての割り込みソース (EDC CTRL チェッカー) を無効化します

2. クロック ストップ / リセット シーケンスの実行中に発生する保留中の割り込みの処理 / クリアを続行します。すべての割り込みがクリアされると、シーケンスが続行されます。

一般に、ソフトウェアは、このシーケンス全体の間に連続的に起動する保留中の割り込みを検出し (縮退故障シナリオなど)、関連する EDC CTRL 安全チェックを無効化して、クロック ストップ / リセット シーケンスを完了に向かって進行できるようにする必要があります。

**i2062**

**RAT: エラー ログ ディスエーブルが設定されている場合でも、エラー割り込みが発生します**

**詳細:**

RAT エラー ログがログを無効化して割り込みを有効化するようにプログラムされている場合、エラーによって割り込みが誤ってトリガされますが、エラー ログ レジスタは正しく更新されません。エラー割り込みは生成されてはなりません。

**回避方法:**

RAT エラー ログがディスエーブルの場合、エラー割り込みもソフトウェアで無効化する必要があります。

**i2120**

**C71x: LEZR を使用して転置されたストリームで、SE が非パティエラー検出でハングアップします**

**詳細:**

C71x ストリーミングエンジン (SE) パイプラインでは、フォーマットされたデータを返し、レポートの内部エラー情報を返すために、常にタグを監視して、作業中のデータのタグを監視します。データを CPU にフォーマットするために使用されるデータの行にエラーが検出されると、UMC、uTLB に移動するコマンドをキューイングするためのフェッチ側の実行がすべて停止され、フォーマットパイプラインが CPU に戻されます。

一般的な動作では、エラーが監視されているタグは、現在のコマンドで使用されているタグだけです。転置モードの場合、これは現在の配列列によってタッチされるすべてのタグです。内部タグ監

**i2120 (続き)****C71x:LEZR を使用して転置されたストリームで、SE が非パリティ エラー検出でハングアップします**

視の抑制にギャップがあると、フォーマット パイプラインは **LEZR** 機能のゼロ ベクトルを作成する際に現在作業していないタグを監視します。SE のフェッチ側で将来の列のエラーが発生して記録された場合、フォーマット側はそれを認識してその列のコマンドがフォーマットのためにコミットされる前にフェッチ側を停止することがあります。

エラーは、フォーマットのために内部的にコミットされたコマンドについてのみ CPU に報告されます。したがって、列をコミットする前に内部実行を停止しても、CPU にエラーは報告されません。SE はエラーを報告せずにフェッチ動作を停止するため、関連しない外部イベントまたは割り込みが発生するまで、CPU は SE からのデータまたはエラーを待機してハングアップします。

**回避方法:**

唯一の 100% 回避方法は、**LEZR** モードと転置モードの両方が有効な状態でストリーム テンプレートを使用しないことです。

**i2137****PSIL:クロック停止動作により、未定義の動作が発生する可能性があります」を追加****詳細:**

クロック停止インターフェイスは、モジュールへのメインクロックを適切に停止するハンドシェイクを調整するために使用される要求 / ACK インターフェイスです。最初にチャネル ティアダウンを実行したり、グローバル イネーブル ビットをクリアしたりせずにモジュール上でクロック停止を試みると、モジュール固有の動作が未定義になる可能性があります。

影響を受けるモジュールは、PDMA、SA2UL、Ethernet SW、CSI、UDMAP、ICSS、および CAL です。

**回避方法:**

クロック停止動作を実行する前に、ソフトウェアはすべてのアクティブ チャネルを解除する必要があります (UDMAP の「リアルタイム」レジスタ、または PSIL ベースのモジュールの PSIL レジスタ 0x408 を介して)。これが完了したら、すべてのチャネルのグローバル イネーブル ビットもクリアします (UDMAP および PSIL ベースのモジュールの両方の PSIL レジスタ 0x2 を使用)。

**i2189****OSPI:コントローラ PHY のチューニング アルゴリズムを追加****詳細:**

PHY モジュールがイネーブルのとき、OSPI コントローラは DQS 信号を使用してデータをサンプリングします。しかし、モジュールに問題が存在する必要があります。これは、このサンプルは内部クロックで定義されたウインドウ内で発生する必要があります。読み取り動作は外部遅延の影響を受け、温度によって変化します。任意の温度での有効な読み取りを検証するには、最も堅牢な TX、RX、読み取り遅延の値を選択する特別なチューニング アルゴリズムを実装する必要があります。

**回避方法:**

このバグの回避方法については、[SPRACT2](#) に詳細が記載されています。一部の PVT 条件でデータをサンプリングするには、読み取り遅延フィールドをインクリメントして、内部クロックのサンプリング ウィンドウをシフトします。これにより、データ アイ内の任意の場所でデータのサンプリングが可能になります。しかし、これには次の副作用があります。

- すべての読み取り動作に対して PHY パイプライン モードを有効化する必要があります。書き込みのために PHY パイプライン モードを無効化する必要があるため、読み出しと書き込みは個別に処理する必要があります。

**i2189 (続き)**

**OSPI:コントローラPHYのチューニングアルゴリズムを追加**

2. 回避方法が実行されると、ビジー ビットのハードウェア ポーリングが壊れます。そのため、代わりに **SW** ポーリングを使用する必要があります。ホストとフラッシュ デバイスのどちらからも割り込みが発生しないように、**DMA** アクセスにより、ページ境界内で書き込みを行う必要があります。ソフトウェアは、ページ書き込みの間でビジー ビットをポーリングする必要があります。または、ハードウェア ポーリングを有効化した状態で、**PHY** 以外のモードで書き込みを実行することもできます。

3. **STIG** 読み取りは余分なバイトでパディングされ、受信データは右シフトされなければなりません。

**i2196**

**IA:IA でデッドロック シナリオが発生する可能性があります**

**詳細:**

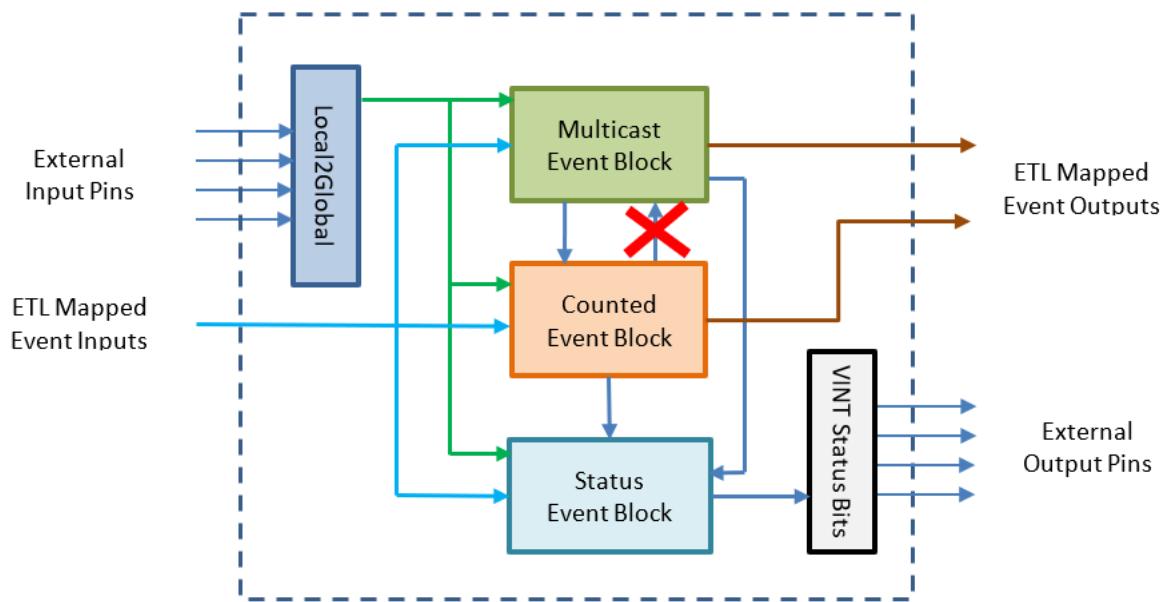

割り込みアグリゲータ (IA) には、イベントトランスポートレーン (ETL) バスに到着したイベントを割り込みステータス ビットに変換するというメイン機能が 1 つあります。これは、レベル割り込みの生成に使用されます。IA バージョン 1.0 でこの関数を実行したブロックはステータス イベント ブロックと呼ばれていました。

ステータス イベント ブロックに加えて、マルチキャスト イベント ブロックとカウント イベント ブロックという 2 つの主要な処理ブロックがあります。マルチキャスト ブロックは、実際にはイベント スプリッタとして機能します。イベントが発生するたびに、2 つの出力イベントを生成できます。カウント イベント ブロックは、高周波イベントを読み取り可能なカウントに変換するために使用されます。入力イベントをカウントし、0 以外のカウント値との間のカウント遷移時に出力イベントを生成します。ステータス イベント ブロックとは異なり、マルチキャストおよびカウント イベント ブロックは出力 ETL イベントを生成し、他の処理ブロックにマッピングします。

設計後に、IA のデッドロックを引き起こす可能性のある問題が発見されました。この問題は、これら 3 つの処理ブロック間でイベント「ループ」が発生した場合に発生します。バスがブロックされているために処理ブロックがイベントを出力できず、イベントを出力できないために、新しい入力イベントを取得できない状況が発生する場合があります。この入力イベントを受信できないため、出力バスがアンワインドできなくなり、両方のバスがブロックされたままになります。

**回避方法:**

図 2-1 に、IA 1.0 の概念ブロック図を示します。潜在的なループは、カウント イベント ブロックがマルチキャスト ブロックにイベントを送信しないようにするポリシーを採用することで回避できます。最初にイベントを分割してから、他の場所に送信する間に 1 を数えるのが一般的であるために、この方法が選択されました。このバスが慣例によってブロックされている場合、1 つのイベントが複数回ブロックにアクセスすることはできず、出力がブロックされない限り、バスがブロックされることはありません。

i2196 (続き)

IA:IA でデッドロック シナリオが発生する可能性があります

図 2-1. 割り込みアグリゲータ バージョン 1.0

ここに概説されているルールに従うと、システムは、デッドロック シナリオを発生させる可能性のあるループ危険性を回避して安全に動作できます。

i2199

**C71x:非アライメントの転置されたストリームが AM1 循環バッファ境界を越えた場合に、SE が誤ったデータを返します**

詳細:

AM1 が AM0 よりも大きい循環バッファ サイズを参照している場合、SE は非アライメントの転置されたストリーム中に間違った 64B 行のデータを再利用することができます。これは、転置されている行の 1 つが AM1 循環バッファ境界を超えて、AM0 境界を超えていないときに発生します。

回避方法:

転置されたストリームを完全にアラインさせます。つまり、開始アドレスとスケーリングされたすべての DIM 値が 64B の倍数になるか、AM1 が AM0 よりも大きな循環アドレッシング バッファ サイズにならないように設定します。

i2249

**OSPI:DDR タイミングが動作不能の内部 PHY ループバックおよび内部パッド ループバック クロック モード**

詳細

OSPI 内部 PHY ループバック モードと内部パッド ループバック モードは、「立ち上げエッジをキャプチャ エッジとして」(同じエッジ キャプチャまたは 0 サイクル タイミング)を使用します。

プログラマブル受信遅延ライン (Rx PDL) は、往復遅延 (Tx クロックからフラッシュ デバイス、フラッシュ クロックから出力、フラッシュ データからコントローラ) を補償するために使用されます。

内部ループバック モードと IO ループバック モードの場合、Rx PDL の合計遅延は往復遅延を補償するのに十分ではないため、これらのモードは使用できません。

**i2249 (続き)**

**OSPI:DDR タイミングが動作不能の内部 PHY ループバックおよび内部パッド ループバック クロック モード**

次の表に、OSPI コントローラで推奨されるクロックトポロジを示します。ここで説明されていない他のモードはすべて、DDR モードのアドバイザリの影響を受け、クロックトポロジは推奨されません。

**表 2-1. OSPI クロッキング トポロジ**

| クロック モードの用語         | CONFIG_REG.PHY_MODE_ENABLE | READ_DATA_CAPTURE.BYPASS | READ_DATA_CAPTURE.DQS_EN | ボードの実装                                   |

|---------------------|----------------------------|--------------------------|--------------------------|------------------------------------------|

| ループバックなし、PHY なし     | 0 (PHY ディスエーブル)            | 1 (適応ループバック クロックを無効化)    | X                        | なし。内部クロックに依存。最大周波数 50MHz。                |

| PHY による外部ボード ループバック | 1 (PHY イネーブル)              | 0 (適応ループバック クロックを有効化)    | 0 (DQS ディスエーブル)          | 外部ボード ループバック (OSPI_LOOPBACK_CLK_SEL = 0) |

| PHY を搭載した DQS       | 1 (PHY イネーブル)              | x (DQS イネーブルが優先)         | 1 (DQS イネーブル)            | メモリストローブは SOC DQS ピンに接続                  |

**回避方法**

なし。説明の表に基づいて、影響を受けないクロック モードのいずれかを使用してください。

**i2253**

**PRG:CTRL\_MMR\_STAT レジスタは、POK スレッショルド障害の信頼性が低いインジケータです**

**詳細**

CTRL\_MMR PRG STAT レジスタの POK 過電圧および低電圧フラグは、POK が障害を認識したかどうかを示す信頼性が低いインジケータです。その結果、デバイス テクニカル リファレンス マニュアル (TRM) では、これらのビットが「予約済み」とマークされています。

**回避方法**

フィルタ処理された POK 出力は ESM フラグを更新します。

POK の初期化 (イネーブル) 時に、ESM フラグをクリアする必要があります (バンドギャップ中または POK のセトリング タイム中に実行される比較のため)。この最初のクリアの後、ESM フラグは、POK からの信頼できる障害 (または障害なし) インジケータとして使用できます。

**i2278**

**MCAN:同じメッセージ ID で構成された専用 Tx バッファからのメッセージ送信順序が検証されませんを追加**

**詳細**

このエラッタは、複数の Tx バッファが同じメッセージ ID (TXBC.NDTB > 1) で構成されている場合に制限されます。

次の状況では、メッセージは順序が正しくない状態で送信されることがあります。

- 同じメッセージ ID で構成された複数の Tx バッファ

- これらの Tx バッファに対する Tx 要求が、それぞれの間に遅延が発生して順次送信される場合

**回避方法**

回避方法 1:

## i2278 (続き)

### **MCAN:同じメッセージ ID で構成された専用 Tx バッファからのメッセージ送信順序が検証されませんを追加**

メッセージ RAM に同じメッセージ ID を持つ Tx メッセージを書き込んだ後、TXBAR への 1 回の書き込みアクセスにより、これらすべてのメッセージの同時送信を要求します。同時要求を実行する前に、これらのメッセージに保留中の Tx 要求がないことを確認してください。

#### 回避方法 2:

特定の順序で同じメッセージ ID を持つ複数のメッセージを送信するには、専用 Tx バッファの代わりに Tx FIFO を使用します (Tx FIFO を使用するには、ビット MCAN\_TXBC[30] TFQM = 0 を設定)。

## i2279

### **MCAN:同じメッセージ ID で構成された専用 Tx バッファと Tx キューの仕様の更新**

#### 詳細

同じメッセージ ID で構成された複数の専用 Tx バッファからのメッセージ送信に関する M\_CAN ユーザー マニュアルのセクション 3.5.2「専用送信バッファ」とセクション 3.5.4「送信キュー」の説明がエラッタで更新されています。

#### 回避方法

##### 回避方法 1:

メッセージ RAM に同じメッセージ ID を持つ Tx メッセージを書き込んだ後、TXBAR への 1 回の書き込みアクセスにより、これらすべてのメッセージの同時送信を要求します。同時要求を実行する前に、これらのメッセージに保留中の Tx 要求がないことを確認してください。

##### 回避方法 2:

特定の順序で同じメッセージ ID を持つ複数のメッセージを送信するには、専用 Tx バッファの代わりに Tx FIFO を使用します (Tx FIFO を使用するには、ビット MCAN\_TXBC[30] TFQM = 0 を設定)。

## i2310

### **USART:「タイムアウト割り込みの誤ったクリア/トリガ」を追加**

#### 詳細:

RHR/MSR/LSR レジスタが読み出されたときに、USART が誤ってクリアしたり、タイムアウト割り込みをトリガしたりすることがあります。

#### 回避方法:

##### CPU の使用事例の場合。

- ・ タイムアウト割り込みが誤ってクリアされた場合:

- FIFO 内の保留データがタイムアウト割り込みを再トリガするため、これは有効です

- ・ タイムアウト割り込みが誤って設定され、FIFO が空である場合は、次の SW 回避方法を使用して割り込みをクリアします。

- TIMEOUTH および TIMEOUTL レジスタでタイムアウト カウンタの High 値を設定します

- EFR2 ビット 6 を 1 に設定して、タイムアウト モードを周期的に変更します

- IIR レジスタを読み出して、割り込みをクリアします

- タイムアウト モードを元のモードに戻すには、EFR2 ビット 6 を 0 に戻します

##### DMA の使用事例の場合。

- ・ タイムアウト割り込みが誤ってクリアされた場合:

- 次の周期的なイベントでタイムアウト割り込みが再トリガされるため、これは有効です

**i2310 (続き)**

**USART:「タイムアウト割り込みの誤ったクリア/トリガ」を追加**

- ユーザーは、EFR2 の bit6 を 1 に設定して、RX タイムアウト動作を周期的モードにする必要があります

- タイムアウト割り込みが誤って設定されている場合:

- これにより、DMA は SW ドライバによって破棄されます

- 次の受信データが有効なので、SW で DMA が再度設定されます

**i2311**

**USART スプリアス DMA 割り込み**

**詳細:**

スプリアス DMA 割り込みは、DMA を使用して TLR レジスタの 2 の非幂乗 (Non power of two) のトリガ レベルで TX/RX FIFO にアクセスする場合に発生することがあります。

**回避方法:**

TX/RX FIFO のトリガ レベル (1, 2, 4, 8, 16, 32) に 2 の幂乗の値を使用します。

**i2312**

**MMCSD:HS200 および SDR104 コマンド タイムアウト ウィンドウが小さすぎます**

**詳細:**

高速 HS200 および SDR104 モードでは、MMC モジュールの機能クロックは最大 192MHz に達します。この周波数では、MMCSD\_SYSCTL[19:16] DTO = 0xE を使用した MMC ホストコントローラからの最大取得可能タイムアウトは、 $(1/192\text{MHz}) \times 2^{27} = 700\text{ms}$  です。700ms を超えるコマンドは、この小さなウィンドウ フレームによって影響される場合があります。

**回避方法:**

このコマンドで 700ms より長いタイムアウトが必要な場合は、MMC ホストコントローラのコマンドのタイムアウトを無効化し (MMCSD\_CON[6] MIT=0x1)、その代わりにソフトウェア実装を使用できます。詳細な手順は次の通りです (Linux の場合)。

1. MMC ホストコントローラのプローブ機 (omap\_hsmmc.c:omap\_hsmmc\_probe()) 中、ホストコントローラが必要なすべてのタイムアウトをサポートできないことをプロセッサに通知します。

2. 基盤となる MMC ホストコントローラが必要なタイムアウトをサポートできない場合、コアが自動的にタイムアウトするように、MMC コアソフトウェア層の機能を変更します。

**i2377**

**ラット入力信号の *rbytecnt* と *wbytecnt* 計算が間違っています**

**詳細:**

R5SS 内部のラットロジックは、*rbytecnt* と *wbytecnt* を使用して、リード アクセスとライト アクセスが SW によって設定された領域境界をまたぐかどうかを判断します。RAT に送られる *rbytecnt* と *wbytecnt* の値は R5SS で計算されるが、使用される方程式は正しくありません。

その結果、RAT は領域境界の交差を検出しないか、誤って検出しません。

**回避方法:**

Cortex-R5 AXI メインインターフェイス ランザクションは 32 バイトの境界を超えないため、32 バイト以上の領域境界で問題はありません。この問題は、リージョン境界が 32 バイト未満の場合にのみ発生します。したがって、ソフトウェアは 32 バイト未満の領域境界を設定できません。

**i2383****OSPI:2 バイト アドレスは、PHY DDR モードではサポートされません****詳細:**

PHY DDR モードで OSPI コントローラが 2 バイトアドレスに構成されていると、内部ストートマシンが送信されたアドレス バイト数を誤って (2 ではなく) 1 と比較します。これにより、ストートマシンがアドレス位相でロックアップし、PHY DDR モードが動作不能になります。

この問題は、タップ モードまたは PHY SDR モードを使用する場合は発生しません。PHY DDR モードで 4 バイトアドレスを使用する場合も、この問題は発生しません。

**回避方法:**

互換性のある OSPI メモリにプログラマブルアドレス バイト設定がある場合は、フラッシュの 2 ~ 4 に必要なアドレス バイト数を設定します。これには、アドレス バイトを変更するための特定のコマンドの送信やフラッシュ上の構成レジスタへの書き込みが含まれる場合があります。完了したら、コントローラ設定で送信されたアドレス バイト数を 2 から 4 に更新します。

2 バイトアドレスのみをサポートし、再プログラムできない互換 OSPI メモリについては、PHY DDR モードはそのメモリと互換性がありません。代替モード:

- PHY SDR モード

- TAP (非 PHY) DDR モード

- TAP (非 PHY) SDR モード

**i2401****CPSW:ホストのタイムスタンプにより、CPSW ポートがロックされます****詳細:**

CPSW は、パケット入力タイムスタンプ情報をホストに通信するための 2 つのメカニズムを提供します。

1 つ目のメカニズムは、特定のイベントによってトリガされたときにタイムスタンプを記録する CPTS イベント FIFO を経由します。そのようなイベントの 1 つは、指定された EtherType フィールドを持つイーサネットパケットの受信です。最も一般的に、これは PTP パケットの入力タイムスタンプをキャプチャするために使用されます。このメカニズムでは、ホストは DMA 経由で配信されるパケットペイロードとは別に、(CPTS FIFO から) タイムスタンプを読み取る必要があります。このモードはサポートされており、このエラッタの影響を受けません。

2 つ目のメカニズムは、PTP パケットだけでなく、すべてのパケットの受信タイムスタンプを有効化することです。このメカニズムでは、タイムスタンプは DMA を介してパケットペイロードと一緒に配信されます。この 2 番目のメカニズムは、このエラッタの主題です。

CPTS ホストタイムスタンプがイネーブルの場合、内部 CPSW ポート FIFO へのすべてのパケットには、CPTS からのタイムスタンプが必要です。EMI やその他の破損メカニズムによってパケットプリアンブルが破損した場合、タイムスタンプ要求が CPTS に送信されない可能性があります。この場合、CPTS は CPSW ポート FIFO でロックアップ状態を引き起こすタイムスタンプを生成しません。CPTS\_CONTROL レジスタの tstamp\_en ビットをクリアして CPTS ホストのタイムスタンプを無効化すると、ロックアップ状態が発生しなくなります。

**回避方法:**

イーサネットからホストへのタイムスタンプを無効化する必要があります。

CPTS ホストのタイムスタンプの代わりに、イベント FIFO のタイムスタンプを使用できます。

**i2427****RAM SEC が誤った RAM 書き込みを引き起こす可能性があり、L2&MBOX のメモリ破損が発生します****詳細:**

RAM の読み取りデータ中に、読み取りまたは部分的な書き込みトランザクションにより 1 ビットのエラーが発生した場合、RAM は、次の「メモリ読み取り」がその後の部分的な書き込みトランザク

**i2427 (続き)**

**RAM SEC が誤った RAM 書き込みを引き起こす可能性があり、L2&MBOX のメモリ破損が発生します**

ションによるものであると、RAM への後続の誤った書き込みにつながる可能性のある状態になります。「メモリ読み取り」が実際のメモリ読み出しトランザクションによるものであるならば、内部状態の残存は消去され、後にスプリアス書き込みが行われる可能性はありません。スプリアス書き込みは、部分的な書き込みトランザクションより前に書き込まれた最後のメモリアドレスに行われ、スプリアス書き込みがトリガされます。この問題は MBOX と L2 にのみ適用されます。

**図 2-2** には、問題が該当するシナリオ(例 1、2、3)と該当しないシナリオ(例 4、5、6)を明確に示します。トランザクション番号は説明のためのものであり、各操作が発生する正確なサイクルを必ずしも表しているわけではありません。[SEC-シングルビットエラー訂正、DED-ダブルビットエラー検出]

| Ex # | Transaction 1                                            | Transaction 2+N<br>N=0,1,2,3..                                                                               | Transaction 2+N+1                          | Transaction 2+N+2                                                                                                                                                     |

|------|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | Read or Partial Write<br>Addr A (SEC) ← read<br>with SEC | Full Write Addr X ← last write prior to partial write<br>Note: N=0                                           | Partial Write ← Triggers<br>spurious write | Spurious write to Addr X<br>with Transaction 1<br>corrected read data of Addr A                                                                                       |

| 2    | Read or Partial Write<br>Addr A (SEC) ← read<br>with SEC | Full Write Addr B<br>Full Write Addr C<br>Full Write Addr D ← last write prior to partial write<br>Note: N=2 | Partial Write ← Triggers<br>spurious write | Spurious write to Addr D<br>with Transaction 1<br>corrected read data of Addr A                                                                                       |

| 3    | Read or Partial Write<br>Addr A (SEC)                    | Partial Write Addr B<br><br>Note: N=0                                                                        |                                            | Spurious write to Addr A with Transaction 1 corrected read<br>data of Addr A (Addr A is overwritten with the RAM content<br>prior to the Transaction 1 Partial write) |

| 4    | Read Addr A (SEC)                                        | Partial Write Addr B<br>Note: N=0                                                                            |                                            | No Spurious write to Addr A with Transaction 1 corrected read<br>data of address A (no data corruption)                                                               |

| 5    | Read or Partial Write<br>Addr A (SEC)                    | Read ← Clears bad internal state<br>Note: N=0                                                                |                                            | No spurious writes with all command combinations in<br>subsequent cycles                                                                                              |

| 6    | Read or Partial Write<br>Addr A (SEC)                    | Full Write Addr B<br>Note: N=0                                                                               | Read ← Clears bad internal<br>state        | No spurious writes will all<br>command combinations in<br>subsequent cycles                                                                                           |

**図 2-2.**

**回避方法:**

以下のオプションのいずれかを回避方法として使用できます。

**オプション 1:**

ECC を無効にします。安全でないアプリケーションにのみ適用されます。

**オプション 2:**

メモリへの部分的な書き込みを禁止します(行全体の書き込みのみを実行)

L2 の場合、L2 スペースがキャッシュ可能な場合、コアは行全体の書き込みのみを実行し、この問題は該当しません。

**オプション 3:**

アプリケーションは、読み取りまたは部分的な書き込みトランザクションで 1 ビットエラーが発生した場合に、アプリケーションがトランザクションを直ちに制御できないと RAM データが破損する可能性があるため、すべての SEC エラーを DED(単一ビットエラーの場合も修正はせず、検出のみ)として処理できます。

**注**

ECC CTRL-SEC カウンタを通常の SEC 問題とスプリアス書き込みのインジケータとして使用するというこれまでの記述は無効です。スプリアス書き込みが行われた後も、ECC CTRL SEC カウンタは 1 のままになる場合があります。

i2431

**BCDMA :RX チャネルが特定のシナリオでロックアップする可能性があります**

詳細:

BCDMA RX チャネル ティアダウンにより、チャネルがロックされる可能性があります。構成固有のフラグ フィールドに EOP フラグが設定されている TR がない場合は、後続の転送に使用できなくなります。その後、チャネルが再度有効になっても、転送は完了せず、TR 応答でさまざまなエラーが発生して終了します。

回避方法:

- PSIL/PDMA ペリフェラルからデータを受信する場合、チャネル ティアダウンが正しく機能し、内部状態メモリをクリーンアップするためには、各 TR の構成固有のフラグ フィールドに EOP フラグを設定し、PDMA の 1 X-Y FIFO モード静的 TR「Z」パラメータを 0 以外の値に設定する必要があります。そうしないと、後続の実行時にチャネルがロックアップする可能性があります。PDMA が各転送を個別のパケットとして区切るように、PDMA Z カウントも TR サイズと一致する必要があります。これは、ストリーミング モードで TR の 1 セットを使用して周期的転送を実行するため TRPD が無限のリロード カウントを設定している場合などに特に問題となります。この場合、各 TR が最後の TR になる可能性があります。

- 事前に PDMA Z カウントを設定できない場合、またはパケット EOP を設定できない場合は、BCDMA ではなくシングル バッファ モードで PKTDMA を使用することが推奨されます。

i2435

**ブート:eMMC ブートの ROM タイムアウトが長すぎる**

詳細:

ROM のバグにより、空または消去された (または工場出荷時の状態) eMMC デバイスから eMMC ブート モード (eMMC ブートパーティションから起動するモード、eMMC 代替モードとも呼ばれる) で起動を試みると、バックアップ ブート モードに切り替わるまでの通常のブート タイム アウトが 10 秒になります。

回避方法:

このタイムアウトがシステム内で長すぎると判断される場合、別のブート モードからブートする必要があります。

i2436

**BCDMA :RX CHAN CFG レジスタの BCDMA\_RX\_IGNORE\_LONG 設定が機能しません」を追加**

詳細:

BCDMA の RXCHAN CFG レジスタの RX\_IGNORE\_LONG フラグは無視され、リモート エンドポイントが TR 境界と一致するように EOP を送信しない場合、BCDMA は TR 応答のエラーを報告します。

回避方法:

RX\_IGNORE\_LONG は使用できないため、PDMA などのリモート エンドポイントは、TR 境界に一致するように EOP を送信してパケットを閉じる必要があります (PDMA X\*Y\*Z は TR ICNT0\*ICNT1\*ICNT2\*ICNT3 と一致する必要があります)。

無限のストリームが必要な場合 (PDMA Z = 0)、PKTDMA に切り替えて、シングル バッファ モードを使用します

**i2438****CPSW:VLAN 追加/削除によるホストからイーサネットへのチェックサム生成****詳細:**

ハードウェアで **CPSW** ホストからイーサネットへのチェックサム生成がイネーブルになっており、イーサネット出力で **VLAN** タグが追加または削除されると、ホストからイーサネットへのパケットが破損し、良好な **CRC** を持つガベージとして送信されます。これは許容されません。

**回避方法:**

チェックサムが生成されたパケットのイーサネット出力で **VLAN** タグを追加または削除しないでください。

**i2449****パルサーには RAT MMR パリティがありません — 不一致 w. 診断 RAT5****詳細:**

Pulsar RAT MMR に格納されている値は、格納中にパリティ保護されません。これは、パリティ保護が検出されない場合でも MMR のビット反転を意味するため、永続的または一時的なエラーからの保護はありません。読み取り時に MMR に格納されている値からパリティが動的に計算される場合、イニシエータ パリティでチェックすると、インターフェクトのみが対象となります。

**回避方法:**

ユーザーは、実行時に MMR 値のソフトウェア リードバックを実行する必要があります。

**i2455****PWM:3 つすべての PWM からの EINT 割り込みは、メインパルサにルーティングされません****詳細:**

ePWM の EINT 割り込みは、2 つの C7x デバイス マネージャ (DM) R5 にのみルーティングされます。ただし、これらの割り込みはメイン Pulsar R5FSS0 と R5FSS1 に配線されていません。

**回避方法:**

EINT 割り込みを受信するプロセッサの中で、次のいずれかの方法を使用します。

- DM R5 (EPWM0-EPWM2 eint を管理)

- PWM eint 割り込みをメイン パルサに渡すための DM R5 割り込みサービス ルーチン。以下に、eint 割り込みを渡す方法の例を 2 つ示します。

1. 専用 GPIO ピンを使用して PWM eint を GPIO 割り込みに変換し、メイン GPIO マルチプレクサをプログラムして、割り込みをメイン パルサにルーティングします

2. PWM eint を Mailbox から Main Pulsar へ IPC メッセージに変換します

**3 商標**

すべての商標は、それぞれの所有者に帰属します。

**4 改訂履歴**

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

**Changes from DECEMBER 2, 2024 to JULY 1, 2025 (from Revision \* (December 2024) to Revision A (July 2025))**

**Page**

- 注意 i2449 を追加: パルサーには RAT MMR パリティがありません。診断 RAT5 との不一致です ..... 2

- 注意 i2377 を追加: ラット入力信号の rbytecnt と wbytecnt 計算が間違っています ..... 2

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適したテキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているテキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、[テキサス・インスツルメンツの販売条件](#)、または [ti.com](http://ti.com) やかかるテキサス・インスツルメンツ製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2025, Texas Instruments Incorporated

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ（データシートを含みます）、設計リソース（リファレンス デザインを含みます）、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適したテキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているテキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、[テキサス・インスツルメンツの販売条件](#)、または [ti.com](http://ti.com) やかかるテキサス・インスツルメンツ製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所 : Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2025, Texas Instruments Incorporated