## Errata

# CC2340R5-Q1 SimpleLink™ ワイヤレス MCU デバイスリビジョン B

## 概要

この文書では、CC2340R5-Q1 および CC2340R53-Q1 SimpleLink™ デバイスの機能仕様に対する既知の例外 (アドバイザリ) を説明します。

## 目次

|                                 |    |

|---------------------------------|----|

| 1 アドバイザリ マトリックス.....            | 2  |

| 2 命名法、パッケージのマーキングとリビジョンの識別..... | 2  |

| 2.1 デバイスおよび開発サポートツール命名規則.....   | 2  |

| 2.2 サポート対象デバイス.....             | 3  |

| 2.3 パッケージの記号表記およびリビジョンの識別.....  | 3  |

| 3 アドバイザリ.....                   | 3  |

| 4 改訂履歴.....                     | 10 |

## 商標

SimpleLink™ and テキサス インストルメンツ™ are trademarks of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

## 1 アドバイザリ マトリックス

表 1-1 はすべてのアドバイザリ、影響を受けるモジュール、および適用可能なシリコン リビジョンを一覧にします。

表 1-1. アドバイザリ マトリックス

| モジュール  | 説明                                                                   | 影響を受けるシリコンのリビジョン |              |

|--------|----------------------------------------------------------------------|------------------|--------------|

|        |                                                                      | CC2340R5-Q1      | CC2340R53-Q1 |

|        |                                                                      | 影響を受けるリビジョン      |              |

| SPI    | アドバイザリ SPI_04 — SPI が CPU の介入を永遠に待機してハングするシナリオ                       | B                | B            |

| ADC    | アドバイザリ ADC_08 — 反復シングル、シーケンス、および反復シーケンス変換モードで ADC BUSY ビットがクリアされません。 | B                | B            |

| ADC    | アドバイザリ ADC_09 — ADC がランダム変換エラーを発生する可能性があります。                         | B                | B            |

| BATMON | アドバイザリ BATMON_01 — 温度測定が不正確です                                        | B                | B            |

| BATMON | アドバイザリ BATMON_02 — スタンバイ状態の BATMON から不要な温度更新割り込みが発生します               | B                | B            |

| CKM    | アドバイザリ CKM_01 — スタンバイ復帰時のトラッキング ループの問題                               | 影響を受けない          |              |

| CKM    | アドバイザリ CLK_01 — LFOSC のみを使用している場合、Bluetooth Low Energy リンクを維持できません   | B                | B            |

| I2C    | アドバイザリ I2C_02 — SDA および SCL オープンドレイン出力バッファの問題                        | B                | B            |

| GPIO   | アドバイザリ GPIO_01 — オープンドレイン構成でも短いハイ パルスを駆動してしまう可能性があります                | B                | B            |

| PMU    | アドバイザリ PMU_01 — ブラウンアウト検出 (BOD) スレッショルドをゆっくりと上回ると、デバイスがハングする可能性があります | B                | B            |

| UART   | アドバイザリ UART_01 — UART がスプリアス μDMA 書き込みバースト要求を発行する可能性があります            | B                | B            |

表 1-2. 部品番号による最新リビジョン

| 部品番号         | 改訂 |

|--------------|----|

| CC2340R5-Q1  | B  |

| CC2340R53-Q1 | B  |

## 2 命名法、パッケージのマーキングとリビジョンの識別

### 2.1 デバイスおよび開発サポート ツール命名規則

製品開発サイクルの各段階を明確にするために、テキサス インスツルメントズ™ はすべてのデバイスおよびサポートツールに対して段階を示す記号を付与しています。デバイスには、次の 2 つの識別子のいずれかが割り当てられます:「X」または「P」は、製品版ではないシリコン ダイのバージョンであることを示すために使用されます (例:CC2340Q/R53/TI X など)。完全認定済みの量産バージョンには記号が付きません。テキサス インスツルメントズでは、サポートツールに対して可能な記号:の 2 つを推奨しています。これらの記号は、製品開発の進展段階を表し、エンジニアリング プロトタイプ (X/TMDX) から完全認定済みの量産デバイス/ツール (TMDS) までをカバーします。

デバイスの開発進展フロー:

- X** 実験的デバイス。最終デバイスの電気的特性を必ずしも表さず、量産アセンブリフローを使用しない可能性があります

- P** プロトタイプ デバイス。最終的なシリコン ダイとは限らず、最終的な電気的特性を満たさない可能性があります

- 記号なし 認定済みのシリコン ダイの量産バージョン

サポートツールの開発進展フロー:

**TMDX** テキサス・インスツルメントズの社内認定試験がまだ完了していない開発サポート製品です。

**TMDS** 完全に認定済みの開発サポート製品

X および P デバイスと TMDX 開発サポートツールは、以下の免責事項の下で出荷されます。

「開発中の製品は、社内での評価用です。」

量産デバイスおよび TMDS 開発サポートツールの特性は完全に明確化されており、デバイスの品質と信頼性が十分に示されています。テキサス・インスツルメンツの標準保証が適用されます。

プロトタイプ デバイス (X または P) は、認定済みの量産デバイスに比べて故障率がより高いと予測されます。テキサス・インスツルメンツは、長期的な信頼性が十分に特性評価されていないため、量産システムでの使用を推奨しません。最終製品では、完全に認定済みの量産デバイスのみを使用する必要があります。

## 2.2 サポート対象デバイス

本文書は、以下のデバイスをサポートしています：

- [CC2340R5-Q1](#)

- [CC2340R53-Q1](#)

## 2.3 パッケージの記号表記およびリビジョンの識別

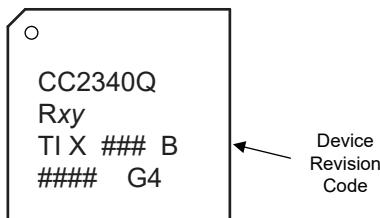

図 2-1 および 表 2-1 はパッケージの記号表記とデバイスのリビジョン コードを説明します。

図 2-1. パッケージの記号表記

**xy** フラッシュと RAM の仕様を示します

表 2-1. リビジョンの識別

| デバイス リビジョン コード | シリコンのリビジョン |

|----------------|------------|

| B              | PG2.0      |

## 3 アドバイザリ

**SPI\_04** *CPU の介入を永遠に待機すると、SPI がハングするシナリオが発生する可能性があります*

### 影響を受けるリビジョン B

#### 詳細

CPU が割り込みを生成するために FIFO レベル トリガを使用して SPI FIFO の読み書きを行っている場合、システムがハングする可能性があります。最初の割り込みが処理された後、FIFO レベルが設定されたスレッショルドを恒常的に下回るか上回る状態になることがあります。その結果、次の CPU 割り込みが発生しなくなる可能性があります。この状態になると、SPI が CPU の介入を永遠に待機することになり、システムがハングする可能性があります。

#### 回避方法

1. SPI 内で FIFO ステータスをポーリングして監視し、FIFO レベルに基づく割り込みには依存しないようにします

2. 空/オーバーフロー割り込みのみを使用し、FIFO レベルで構成された割り込みを使用しないようにします

3. または、ハング状態を回避するためのフェイルセーフとして、FIFO レベルに基づく割り込みと併せて、TXFIFO に対しては空の割り込みを、RXFIFO に対してはオーバーフロー割り込みを使用します。

**ADC\_08**

リピートシングル、シーケンス、および反復シーケンス変換モードでは、**ADC BUSY** ビットがクリアされません。

**影響を受けるリビジョン**

B

**説明**

MEMCTLx レジスタのトリガ ポリシーが「次のトリガ」に設定され、ADC がリピートシングル、シーケンス、または反復シーケンス変換モードで動作している場合、ソフトウェアが ENC ビットをクリアして変換シーケンスを停止しようとしても、STATUS レジスタの **BUSY** ビットはクリアされません。シーケンス変換モードでトリガ ポリシーが「次のトリガ」に設定されている場合、変換シーケンスの終了時に **BUSY** ビットがクリアされます。

**回避方法**

上記の ADC 動作シナリオで変換を停止し、**BUSY** ビットをクリアするには、次のソフトウェアシーケンスを実行してください。

1. CTL0.ENC = 0 を書き込みます

2. CTL1.TRIGSRC をソフトウェアに変更します

3. CTL1.SC = 1 を書き込みます

**ADC\_09**

**ADC** がランダム変換エラーを発生する可能性があります

**影響を受けるリビジョン**

B

**説明**

ADC は、ADC 変換の 4 億回に 1 回程度の割合でエラーを発生する可能性があります。変換エラーが発生すると、ADC のデジタル出力にジャンプが生じ、ADC 入力電圧の対応する変化がない場合、「スパークルコード」と呼ばれます。ADC が 12 ビット分解能設定で使用されている場合、ジャンプの大きさは予想される ADC 出力に対して 64LSB 高くまたは低くなります。ジャンプの大きさは、10 ビット分解能で  $\pm 16$ LSB、8 ビット分解能に設定すると  $\pm 4$ LSB に減少します。

**回避方法**

ADC.DEBUG1:CTRL[10:9] ビットを high に設定すると、ADC 変換で 1000 億回に 1 回のエラー率に低減できます。

3 回の連続サンプリングのうち標準偏差が最も高いものを破棄し、残り 2 つを平均化して ADC 出力を生成する「ベストアウトオブ スリー」などのソフトウェア回避策も検討可能です。

12 ビット分解能に設定した場合、16 個の連続 ADC 出力をソフトウェアで平均化すると、ADC 出力の偏差が  $\pm 4$ LSB に減少します。

これらの回避策は、SimpleLink™ 低消費電力 F3 ソフトウェア開発キット (SDK) の将来のリリースに組み込まれる予定です。

## BATMON\_01

温度測定が不正確です

### 影響を受けるリビジョン

B

#### 説明

ヒステリシスが有効な場合、BATMON が不正確な温度を報告する可能性があります。誤った温度報告の可能性を防ぐため、ユーザーは常に BATMON のヒステリシスを無効にする必要があります。

#### 回避方法

ヒステリシスは PMUD.CLT[2] HYST\_EN ビットによって制御されます。

ヒステリシスはデフォルトで有効 (リセット値 = 1) であり、ブート中に積極的に無効にする必要があります。

ヒステリシスは、次のコマンドを使用して PMUD.CLT[2] HYST\_EN ビットをクリアして無効にできます：

```

HWREG (PMUD_BASE + PMUD_O_CTL) = (PMUD_CTL_CALC_EN |

PMUD_CTL_MEAS_EN)

```

この回避策は、SimpleLink™ 低消費電力 F3 ソフトウェア開発キット (SDK) バージョン 8.10 以降に組み込まれています。

## BATMON\_02

スタンバイ状態の BATMON からスプリアス温度更新割り込みが発生します

### 影響を受けるリビジョン

B

#### 説明

PMUD.EVENT.TEMP\_UPDATE がスタンバイからのウェークアップ ソースとして使用されている場合、BATMON がスプリアス温度更新割り込みを発行する可能性があります。

#### 回避方法

PMUD.EVENT.TEMP\_UPDATE をウェークアップ ソースとして使用する代わりに、PMUD.EVENT.TEMP\_OVER\_UL (現在の温度が設定上限を超過) または PMUD.EVENT.TEMP\_BELOW\_LL (現在の温度が設定下限を下回る) を検討してください。

PMUD.EVENT.TEMP\_OVER\_UL または PMUD.EVENT.TEMP\_BELOW\_LL をウェークアップ 割り込みとして使用する場合、以下の他の設定を有効にする必要があります：

- PMCTL.VDDRCTL.SELECT を 0x0 に設定して、VDDR 調整のソースとして GLDO を選択します。

#### 注

これにより、スタンバイ消費電力がわずかに増加します。詳細については、データシートの「消費電力 — 電力モード」セクションを確認してください。

- SYS0.TMUTE4.RECHCOMPREFLVL を 0x2 に設定します

- SYS0.TMUTE5.GLDOISSET を 0x1E に設定します

この回避策は、SimpleLink™ 低消費電力 F3 ソフトウェア開発キット (SDK) の将来のリリースに組み込まれる予定です。

**CKM\_01****スタンバイ復帰時のループの問題の追跡****影響を受けるリビジョン**

CC2340R53-Q1 Rev B

**詳細**

いくつかのコーナーケースにおいて、スタンバイからの復帰時に HFOSC のトラッキングループが動作を停止し、TRACKREFLOSS が設定されることがあります。これは、トラッキングループで選択されている基準クロックが失われたことを示しています。

**回避方法**

スタンバイへの移行シーケンスには、ソフトウェア オーバーライドの無効化および CKM LDO 制御ビットのクリアが含まれています。これらの書き込みは、まずソフトウェアの上書きをクリアし、その後にすべての LDOCTL ビットをゼロに設定するという順序で実行する必要があります。

これらの設定が並行して発生すると、トラッキング ループがいくつかのケースで停止しているよう見えます。

この回避策はパワー ドライバ内に実装されており、SDK バージョン 9.10 のリリースに含まれています。

**CLK\_01****LFOSC のみを使用する場合、Bluetooth Low Energy リンクを維持することはできません。****影響を受けるリビジョン**

B

**説明**

一部のデバイスでは、スリープ クロックとして LFOSC を使用した場合に、ランダムなタイミング誤差が 500PPM を超えることにより、Bluetooth Low Energy リンクが維持できないことがあります。

**回避方法**

ソフトウェアによる回避策が、SimpleLink F3 SDK バージョン 8.10.xx 以上にて提供されているため、LFOSC のみを使用する場合でも、デバイスがブロードキャスター、オブザーバ、ペリフェラルの各ロールで動作できるようになります。ソフトウェアによる回避策を使用している場合、タイミング誤差が発生すると、短時間ではありますがスループットの低下や電力消費の増加が見られことがあります。このソフトウェア回避策は、中心的な役割をサポートしていません。電力消費の増加やスループット低下の影響を完全に回避し、かつ Central ロールをサポートするために、TI は外部の 32.768kHz 水晶発振子の使用を推奨しています。

## I2C\_01

## SDA および SCL のオープンドレイン出力バッファに関する問題

### 影響を受けるリビジョン B

#### 説明

SDA および SCL 出力は、I<sup>2</sup>C の仕様で求められているオープンドレイン出力バッファではなく、プッシュプルの 3-state 出力バッファで実装されています。プッシュプルの 3-state 出力バッファは、オープンドレイン出力のように動作させることも可能ですが、内部のタイミングスキュームにより、出力が無効になる前に約 1ns ~ 2ns の間、論理 High を出力してしまう現象が発生します。この予期しないハイレベルのパルスは、SCL または SDA の出力が駆動された Low 状態からハイインピーダンス状態へ遷移する際にのみ発生します。

この短いハイレベルのパルスは、I<sup>2</sup>C 信号ラインにエネルギーを注入し、その結果、伝送線路内での複数の反射によって I<sup>2</sup>C 信号が一定期間リングを引き起こす原因となります。このリングは、SDA 信号に対しては問題を引き起こさないと考えられます。なぜなら、リングは SDA が論理レベルを変化させるタイミングでのみ発生し、受信デバイスがデータをラッチするまでに十分に減衰するためです。このリングの振幅が十分に大きい場合、リングの最初の数ナノ秒の間に SCL の入力バッファのスレッショルドを複数回クロスする可能性があり、それによってクロックのグリッチが発生するおそれがあります。このリングは、最初の 50ns 以内に振幅が減衰すれば問題にはなりません。I<sup>2</sup>C デバイスはクロックのグリッチを除去するために SCL 入力をフィルタリングするよう規定されているためです。したがって、PCB 信号パターンを設計して、リングの持続時間を 50ns 未満に制限することが重要です。リングを抑える 1 つの方法として、SCL および SDA 端子の近くに直列終端抵抗を挿入し、伝送線路の反射を減衰させることができます。

この問題は、ターゲット側が ACK サイクルを開始する際に、予期しないハイレベル パルスの継続時間中、SDA 出力がターゲットの SDA 出力と競合状態になる可能性もあります。これは、予期しないハイレベル パルスが発生する前に、ターゲットがすでに SDA を Low に駆動している可能性があるために発生します。この短時間の競合によって SDA 上に発生するグリッチは、I<sup>2</sup>C プロトコル上の問題を引き起こすことはありませんが、ピーク電流が両方の I<sup>2</sup>C デバイスに不要なストレスを与え、電源ノイズの増加につながる可能性があります。したがって、この短時間の競合時に電流を制限するため、SDA 端子付近に直列終端抵抗を配置することが推奨されます。

同様の競合問題は、クロック スレッチ機能をサポートする I<sup>2</sup>C ターゲット デバイスに接続されている場合、SCL ラインでも発生する可能性があります。これは、予期しないハイレベル パルスが発生する前に、ターゲット側が SCL を Low に駆動しているために発生します。この短時間の競合によって SCL 上に発生するグリッチは、I<sup>2</sup>C プロトコル上の問題を引き起こすことはありません。これは、I<sup>2</sup>C デバイスが SCL 入力に対してグリッチ フィルタを適用することが規定されているためです。ただし、ピーク電流は、両方の I<sup>2</sup>C デバイスに望ましくないストレスを印加し、電源ノイズが増加する可能性があります。したがって、この短時間の競合時に電流を制限するため、SCL 端子付近に直列終端抵抗を配置することが推奨されます。

別のコントローラーが接続されている場合、SCL および SDA 出力における予期しないハイレベル パルスが、クロック同期や調停の際に競合を引き起こす可能性があります。上記で説明した直列終端抵抗は、このような使用状況においても競合電流を制限し、I<sup>2</sup>C プロトコル上の問題を引き起こすことなく機能します。

#### 回避方法

SCL および SDA 信号には直列終端抵抗を挿入し、SCL および SDA の端子付近に配置します。あわせて、SCL および SDA のプルアップ抵抗も同じく端子付近に配置します。

リングは、出力のドライブ強度を最小にし、スルーレートを低減することで抑えることもできます。これらのオプションは、高い駆動出力をサポートするピンでのみ構成できます。標準ドライブピンには構成オプションはありません。

**GPIO\_01****オープンドレイン構成による短い High パルスを駆動する可能性****影響を受けるリビジョン B****説明**

各 DIO は、IOCx レジスタを使用してオープンドレイン モードに設定できます。

ただし、内部デバイスのタイミングの問題により、GPIO が高インピーダンス状態への遷移中、または高インピーダンス状態からの遷移中におよそ 1ns~2ns の間、ロジック High を駆動することができます。この望ましくない High レベルにより、他のドライバが同時に低レベルを駆動している場合、GPIO がライン上の別のオープンドレインドライバと競合する可能性があります。この競合は、両方のデバイスにストレスを加え、信号に短時間の中間電圧レベルが生じるため、望ましくありません。レシーバ ロジックにこの短いパルスをフィルタリングするのに十分なロジック フィルタリングがない場合、この中間電圧レベルは誤って高レベルと解釈される可能性があります。

**回避方法**

競合が問題となる場合、GPIO のオープンドレイン機能を使用せず、ソフトウェアでオープンドレイン モードをエミュレートします。オープンドレイン エミュレーションは、GPIO データ (DOUT31\_0.DIOx) を固定で 0 に設定し、GPIO 出力イネーブル (DOE31\_0.DIOx) を制御することで、Low 駆動の有効/無効を切り替えて実現できます。実装例については、以下のコードを参照してください。

```

#include <ti/devices/cc23x0r5/driverlib/gpio.h>

/* Call driver init functions */

GPIO_init();

//Set GPIO data (DOUT31_0.DIOx) to static 0

GPIOClearDio(CONFIG_GPIO_LED_0);

while(1) //loop below toggles the LED on and off every 1 second

{

GPIOSetOutputEnableDio(CONFIG_GPIO_LED_0, 1);

sleep(1);

GPIOSetOutputEnableDio(CONFIG_GPIO_LED_0, 0);

sleep(1);

}

```

## PMU\_01

ブラウンアウト検出 (BOD) スレッショルドをゆっくり超えると、デバイスがハンギングする可能性があります

### 影響を受けるリビジョン

B

#### 詳細

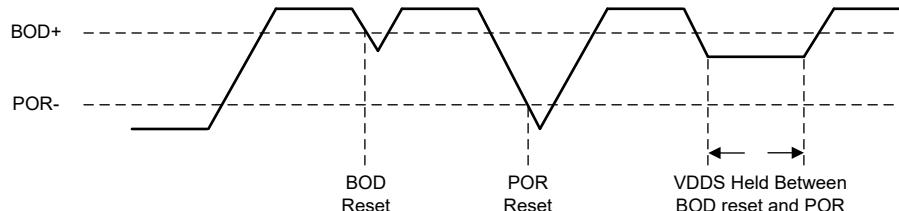

VDDS 電源電圧がブラウンアウト検出 (BOD) のスレッショルド付近 (およそ 1.68V) に留まると、まれにデバイスがロックアップ状態に陥る可能性があります。この状態では、デバイスは約 2.25mA の電流を消費し続け、たとえその後 VDDS 電源電圧が BOD スレッショルドを上回っても、復帰しません。この状態からの復帰には、ピンリセットを行うか、VDDS 電源電圧をパワーオンリセット (POR) のスレッショルド (1.0V) 未満に下げて POR リセットを発生させる必要があります。

ロックアップ状態は、ブートコードの特定の実行段階でブラウンアウト検出 (BOD) イベントが発生した場合に引き起こされます。このロックアップが発生する可能性のある重要なタイミングは、約 10ns の狭い時間ウィンドウが 2 つあり、いずれもブートコードを開始するリセットイベントの後、100μs ~ 1ms の間に発生します。この問題は通常、電源電圧が BOD スレッショルドを超えてゆっくりと上昇するときに発生します。このような場合、電源の抵抗成分とデバイスの起動時電流が組み合わさることで、リセットのたびに VDDS 電圧が BOD スレッショルドを繰り返し下回ることがあり、その結果、ロックアップ状態に入る可能性が高まります。

リチウムイオン電池や NiMH 充電池を使用する場合、チップの VDDS 電源を遮断する一次保護機能があれば、バッテリー放電中に電源電圧が POR スレッショルドを下回るため、デバイスがロックアップ状態に入るのを通常は防ぐことができます。

非充電式 (プライマリ) バッテリを使用している場合でも、特にバッテリが寿命末期に近づき、電圧がゆっくりと低下していく際には、この問題が発生する可能性があります。このような場合、デバイスは最終的にバッテリの交換を必要とし、パワーオンリセットもトリガするため、回避方法が必ずしも必要でない場合があります。ただし、ロックアップのリスクを排除することはできません。

図 3-1. 発生を示す図

#### 回避方法

次の回避方法を実装する必要があります:

デバイスの規定動作電源電圧範囲は 1.72V ~ 3.8V です。再充電可能バッテリを使用する場合、バッテリ保護システムは以下のいずれかを確保する必要があります:

- デバイスが一度起動した後は、電源電圧が最小動作電圧 (1.72V) 以上を維持している場合、

- デバイスの電源電圧が最小動作電圧未満に放電された場合 (1.72V)、電源電圧が再び最小動作電圧 (1.72V) を上回った場合には、デバイスをリセット (ピンリセットまたはパワーオンリセット) する必要があります。

**UART\_01****UART がスプリアス μDMA 書き込みバースト要求を発行する可能性があります****影響を受けるリビジョン****B****詳細**

UART は、FIFO 内のエントリ数が設定されたバースト FIFO スレッショルド以下になると、μDMA バースト書き込み要求を発行します。その後も FIFO の総エントリ数が設定されたスレッショルドを下回っている場合は、μDMA の書き込みバースト要求が引き続き発行されます。UART は、μDMA がバーストアクティブ状態の終了を示すシグナルを出すタイミングと比べて、内部 FIFO レベルの更新に 1 サイクル分の SVT クロックサイクルの遅延が生じます。特定の初期 UART FIFO レベル、バースト要求に対する設定 FIFO スレッショルド、インターフェースの遅延などに依存するコーナーケースでは、UART 内部の追加クロック遅延により、μDMA に対して誤ったスプリアス書き込みバースト要求が発行されることがあります。その結果、μDMA がこの要求に応じて行った最後の書き込みが取りこぼされる可能性があります。この問題は UART の読み取りバースト要求では発生しません。これは、μDMA が読み取り完了を待ってから読み取りバーストの終了を示すためです。

**回避方法**

UART と併用する場合、μDMA の SETBURST はバースト要求に対応するように設定する必要があります。

μDMA 調停サイズは 2 である必要があります。

書き込みバーストトリガを有効にするには、TX FIFO レベルのトリガを 1/4 空き以下に設定する必要があります

**4 改訂履歴**

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

**Changes from SEPTEMBER 30, 2024 to JULY 16, 2025 (from Revision A (September 2024) to Revision B (July 2025))**

**Page**

|                                                       |   |

|-------------------------------------------------------|---|

| • CC2340R53-Q1 を追加.....                               | 1 |

| • アドバイザリ CKM_01、BATMON_02、PMU_01、および UART_01 を追加..... | 2 |

| • 「概要」を更新.....                                        | 4 |

| • アドバイザリ ADC_09 を追加.....                              | 4 |

| • 「概要」を更新.....                                        | 5 |

| • 「概要」を更新.....                                        | 5 |

**Changes from DECEMBER 1, 2023 to SEPTEMBER 30, 2024 (from Revision \* (December 2023) to Revision A (September 2024))**

**Page**

|                           |   |

|---------------------------|---|

| • ドキュメント全体を通して誤字を修正.....  | 1 |

| • アドバイザリ CLK_01 を追加.....  | 2 |

| • アドバイザリ I2C_02 を追加.....  | 2 |

| • アドバイザリ GPIO_01 を追加..... | 2 |

| • アドバイザリ ADC_09 を追加.....  | 2 |

| • 「概要」を更新.....            | 4 |

| • アドバイザリ ADC_09 を追加.....  | 4 |

| • 「概要」を更新.....            | 5 |

| • 「概要」を更新.....            | 5 |

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適したテキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているテキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、[テキサス・インスツルメンツの販売条件](#)、または [ti.com](http://ti.com) やかかるテキサス・インスツルメンツ製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2025, Texas Instruments Incorporated

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月