### Errata

# Errata AM261 Sitara™ マイクロコントローラ シリコン リビジョン 1.0

#### 概要

この文書では、機能仕様に対する既知の例外 (アドバイザリ) について説明します。本文書には、使用上の注意事項も記載されています。使用上の注意は、デバイスの動作が推定または文書化された動作と一致しない可能性がある状況を示しています。これには、デバイスの性能や機能の正確さに影響を与える動作が含まれる場合があります。

# 目次

| 1 使用上の注意およびアドバイザリ マトリックス        | 2  |

|---------------------------------|----|

| 2 シリコン リビジョン 1.0 の使用上の注意とアドバイザリ |    |

| 2.1 シリコン リビジョン 1.0 の使用上の注記      |    |

| 2.2 シリコン リビジョン 1.0 のアドバイザリ      |    |

| 3 商標                            |    |

|                                 |    |

| 4 改訂履歷                          | 16 |

# 1 使用上の注意およびアドバイザリ マトリックス

表 1-1 に、すべての使用上の注意と、該当するシリコンのリビジョンを示します。表 1-2 にすべてのアドバイザリ、影響を受けるモジュール、および適用可能なシリコン リビジョンを一覧表示します。

### 表 1-1. 使用上の注意マトリックス

| P4 P411 |                                           |                               |  |

|---------|-------------------------------------------|-------------------------------|--|

| モジュール   | 説明                                        | 影響を受けるシリコ<br>ンのリビジョン<br>AM261 |  |

|         |                                           | 1.0                           |  |

| クロック    | i2324 — GCM と GCD ステータス信号の間にシンクロナイザがありません | あり                            |  |

### 表 1-2. アドバイザリ マトリックス

|                                                                                       |                                                                                                                                                                 | <b>影響</b> を受けるシリコンの<br>リビジョン |  |

|---------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|--|

| モジュール 説明                                                                              |                                                                                                                                                                 | AM261                        |  |

|                                                                                       |                                                                                                                                                                 | 1.0                          |  |

| CONTROLSS                                                                             | i2352 — CONTROLSS-SDFM:スレッショルド設定 (LLT、HLT)、フィルタ タイプ、COSR 設定を動的に変更すると、スプリアス コンパレータ イベントがトリガされます                                                                  | あり                           |  |

| CONTROLSS                                                                             | i2353 — CONTROLSS-SDFM: データ フィルタ設定 (フィルタ タイプや DOSR など) を動的に変更すると、誤ったデータ確認イベントがトリガされます                                                                           | あり                           |  |

| CONTROLSS                                                                             | i2354 — CONTROLSS-SDFM: SD 変調器の 3 クロック サイクル以内に SDCPARMx レジスタのビットフィールド CEVT1SEL、CEVT2SEL、および HZEN に連続して 2 回書き込みを行うと、SDFM ステートマシンが破損し、誤ったコンパレータ イベントが発生する可能性があります | あり                           |  |

| CONTROLSS                                                                             | i2356 — CONTROLSS-ADC: INTxCONT (割り込み継続モード) が設定されていない場合、割り込みは停止する可能性があります                                                                                       | あり                           |  |

| CONTROLSS                                                                             | i2357 — CONTROLSS-ePWM:ePWM グリッチは、ブランキング ウィンドウの終了時にトリップがアクティブのままの場合、発生する可能性があります                                                                                | あり                           |  |

| CONTROLSS                                                                             | i2358 — CONTROLSS-ePWM:ブランキング開始後の最初の3 サイクルの間、トリップ イベントはブランキング ウィンドウによってフィルタされません                                                                                | あり                           |  |

| CONTROLSS                                                                             | i2359 — CONTROLSS-CMPSS: DACSOURCE を 0 にしたとき、または 1 に再構成したときのプリスケーラ カウンタの動作が仕様と異なります                                                                             | あり                           |  |

| CPSW                                                                                  | i2345 — CPSW: CPDMA がメモリ バンクにまたがるパケットを取得すると、イーサネット パケットの破損が発生します                                                                                                | あり                           |  |

| UART                                                                                  | i2310 — USART:タイムアウト割り込みの誤ったトリガを追加                                                                                                                              | あり                           |  |

| UART                                                                                  | i2311 — USART:スプリアス DMA 割り込み                                                                                                                                    | あり                           |  |

| DTHE                                                                                  | i2428 — DTHE の AES は、GCM 暗号化の最後に data_in に対する追加の DMA 要求を生成します                                                                                                   | あり                           |  |

| SEC                                                                                   | i2427 — RAM SEC が誤った RAM 書き込みを引き起こす可能性があり、L2&MBOX のメモリ破損が発生します                                                                                                  | あり                           |  |

| USB                                                                                   | i2412 — DMA 読み取り/書き込みアクセス エラー時に USB は割り込みを生成できません                                                                                                               | あり                           |  |

| TCM                                                                                   | i2411 — 128 バイトのバースト アクセスは、TCM ではサポートされていません                                                                                                                    | あり                           |  |

| OSPI                                                                                  | i2383 — OSPI:2 バイト アドレスは、PHY DDR モードではサポートされていません                                                                                                               | あり                           |  |

| PBIST                                                                                 | i2374 — R5SS_CORE_CLK のクロック周波数が R5FSS_CLK_SELECTED 周波数と異なると、<br>PBIST は失敗します                                                                                    | あり                           |  |

| OSPI i2351 — OSPI:ダイレクトアクセスコントローラ (DAC) は、NAND フラッシュによる連続読み取りモードをサポートしていませんの使用上の注意を更新 |                                                                                                                                                                 | あり                           |  |

| OSPI                                                                                  | i2189 — OSPI:コントローラ PHY のチューニング アルゴリズムを追加                                                                                                                       | あり                           |  |

| CPSW                                                                                  | i2440 - CPSW:ホストからイーサネットへのタイムスタンプ シーケンス ID の問題                                                                                                                  | あり                           |  |

| CPSW                                                                                  | i2439 - CPSW:ホストからイーサネットへのタイムスタンプの精度の問題                                                                                                                         | あり                           |  |

| ICSS                                                                                  | i2433 - ICSS:LSW が読み取られるとき、64 ビット IEP タイマの読み取りにはロック MSW ロジックがありません                                                                                              | あり                           |  |

# 2 シリコン リビジョン 1.0 の使用上の注意とアドバイザリ

このセクションには、このシリコンリビジョンの使用上の注意およびアドバイザリが記載されています。

#### 2.1 シリコン リビジョン 1.0 の使用上の注記

このセクションでは、シリコン リビジョン 1.0 [およびそれ以前のシリコン リビジョン] に適用されるすべての使用上の注意を一覧表示しています。

i2324 GCM とGCD ステータス信号の間にシンクロナイザがありません

詳細: GCM と GCD の間にシンクロナイザがないため、クロック構成レジスタの読み取りが一時的に正

しくなくなる可能性があります。

重大度: 軽微

回避方法: ステータス レジスタが、プログラムされた SRC SEL および DIV の値に反映されるまで、ステー

タスレジスタの変更をポーリングします。

# 2.2 シリコン リビジョン 1.0 のアドバイザリ

以下のアドバイザリは、機能仕様に対する設計上の既知の例外です。アドバイザリには、この文書に追加された順序で番号が付けられます。設計例外が解消されたという理由で、またはデバイス固有のデータマニュアルまたは技術リファレンスマニュアルに文書化されたという理由で、この文書の将来のリビジョンで一部のアドバイザリ番号を削除することがあります。項目を削除しても、残りのアドバイザリ番号を並べ直すことはありません。

i2189 OSPI:コントローラ PHY のチューニング アルゴリズムを追加

詳細:

PHY モジュールがイネーブルのとき、OSPI コントローラは DQS 信号を使用してデータをサンプリングします。しかし、モジュールに問題が存在する必要があります。これは、このサンプルは内部クロックで定義されたウィンドウ内で発生する必要があります。読み取り動作は外部遅延の影響を受け、温度によって変化します。任意の温度での有効な読み取りを保証するには、最も堅牢なTX、RX、読み取り遅延の値を選択する特別なチューニングアルゴリズムを実装する必要があります。

回避方法:

このバグの回避方法については、アプリケーション ノート spract2 (リンク: https://www.ti.com/lit/spract2) で詳しく説明されています。一部の PVT 条件でデータをサンプリングするには、読み取り遅延フィールドをインクリメントして、内部クロックのサンプリング ウィンドウをシフトする必要があります。これにより、データ アイ内の任意の場所でデータのサンプリングが可能になります。しかし、これには次の副作用があります。

- 1. すべての読み取り動作に対して PHY パイプライン モードを有効化する必要があります。書き込みのために PHY パイプライン モードを無効化する必要があるため、読み出しと書き込みは個別に処理する必要があります。

- 2. 回避方法が実行されると、ビジービットのハードウェアポーリングが壊れます。そのため、代わりに SW ポーリングを使用する必要があります。ホストとフラッシュデバイスのどちらからも割り込みが発生しないように、DMA アクセスにより、ページ境界内で書き込みを行う必要があります。ソフトウェアは、ページ書き込みの間でビジービットをポーリングする必要があります。または、ハードウェアポーリングを有効化した状態で、PHY 以外のモードで書き込みを実行することもできます。

#### i2189 (続き) OSPI:コントローラ PHY のチューニング アルゴリズムを追加

3. STIG 読み取りは余分なバイトでパディングされ、受信データは右シフトされなければなりません。

i2310 USART:「タイムアウト割り込みの誤ったクリア / トリガ /を追加

詳細: RHR/MSR/LSR レジスタが読み出されたときに、USART が誤ってクリアしたり、タイムアウト割り

込みをトリガしたりすることがあります。

回避方法:

CPU の使用事例の場合。

タイムアウト割り込みが誤ってクリアされた場合:

FIFO 内の保留データがタイムアウト割り込みを再トリガするため、これは問題ありません

タイムアウト割り込みが誤って設定され、FIFO が空である場合は、次の SW 回避方法を使用して割り込みをクリアします。

- TIMEOUTH および TIMEOUTL レジスタでタイムアウト カウンタの High 値を設定します

- EFR2 ビット 6 を 1 に設定して、タイムアウト モードを周期的に変更します

- IIR レジスタを読み取って、割り込みをクリアします

- タイムアウト モードを元のモードに戻すには、EFR2 ビット 6 を 0 に戻します

DMA の使用事例の場合。

タイムアウト割り込みが誤ってクリアされた場合:

-次の周期的なイベントでタイムアウト割り込みが再トリガされるため、これは問題ありません

-ユーザーは、EFR2 のビット 6 を 1 に設定して、RX タイムアウト動作を周期的モードにする必要があります

タイムアウト割り込みが誤って設定されている場合:

-これにより、DMA は SW ドライバによって破棄されます

-次の受信データにより SW で DMA が再度設定されるため、問題ありません

i2311 USART スプリアス DMA 割り込み

スプリアス DMA 割り込みは、DMA を使用して TLR レジスタの 2 の非冪乗 (Non power of two)

のトリガレベルで TX/RX FIFO にアクセスする場合に発生することがあります。

回避方法:

詳細:

TX/RX FIFO のトリガレベル (1、2、4、8、16、32) に 2 の冪乗の値を使用します。

i2345

CPSW:CPDMA がメモリバンクにまたがるパケットを取得すると、イーサネット パケットの破損が 発生します

詳細:

SoC の各メモリバンクは、個別のメモリコントローラを備えています。メモリアドレスは連続していても、各バンクは独立したコントローラを持つ独立したエンティティです。

メモリ バンクが 32 バイト、メモリ要求のアドレスが 16 バイトでメモリ バンク終了前のメモリ要求を受信した場合、メモリ コントローラの動作は次のようになります。

メモリコントローラが 16 バイト後にメモリバンクの終了に遭遇すると、そのメモリバンクの先頭から 16 バイトを返します。

これにより、パケットが破損します。

回避方法:

アプリケーション側からのシングル イーサネット パケットが、メモリ バンクにまたがっていないことを確認してください。

i2351

OSPI:ダイレクト アクセス コントローラ (DAC) は、NAND フラッシュによる連続読み取りモードをサポートしていません |の使用上の注意を更新

詳細:

OSPI コントローラは、OSPI コントローラへの内部 DMA バス要求の間に、フラッシュ メモリへの CSn 信号を (設計意図によって) デアサートできるため、OSPI ダイレクト アクセス コントローラ (DAC) は、NAND フラッシュによる連続読み取りモードをサポートしていません。

この問題が発生するのは、一部の OSPI/QSPI NAND フラッシュ メモリで提供される「連続読み取り」モードでは、バーストトランザクション全体にわたってチップ セレクト入力がアサートされたままにならなければならないためです。

SoC 内部 DMA コントローラと他のイニシエータは 1023B 以下のトランザクションに制限されており、アービトレーション / キューイングは、さまざまな DMA コントローラの内部、または任意の DMA コントローラと OSPI ペリフェラルの間の相互接続の両方で実行できます。その結果、OSPI コントローラへのバス要求が遅延し、外部 CSn 信号がデアサートされます。

NOR フラッシュメモリは CSn デアサートの影響を受けません。連続読み取りモードは想定通りに動作します。

回避方法:

ソフトウェアは、ページ / バッファ付き読み取りモードを使用して NAND フラッシュにアクセスできます。

i2352

CONTROLSS-SDFM:スレッショルド設定 (LLT、HLT)、フィルタ タイプ、COSR 設定を動的に変更すると、スプリアス コンパレータ イベントがトリガされます

詳細:

SDFM コンパレータ設定 (フィルタ タイプ、下限/上限スレッショルド、コンパレータ OSR (COSR) 設定など) が実行中に動的に変更されると、誤ったコンパレータ イベントがトリガされてしまいます。 スプリアス コンパレータ イベントは、適切に設定されている場合、対応する CPU 割り込み、CLA タスク、ePWM クロスバー イベント、GPIO 出力クロスバー イベントをトリガします。

回避方法:

コンパレータ設定を動的に変更する必要がある場合は、以下の手順に従って、誤ったコンパレータ イベントによって CPU 割り込み、CLA イベント、または X-BAR イベント (ePWM X-BAR/GPIO 出力 X-BAR イベント) が生成されないようにしてください。

1. コンパレータフィルタを無効にします。

# i2352 (続き) CONTROLSS-SDFM:スレッショルド設定 (LLT、HLT)、フィルタ タイプ、COSR 設定を動的に変更すると、スプリアス コンパレータ イベントがトリガされます

- 2. コンパレータ フィルタの少なくともレイテンシ + 3 SD-Cx クロックサイクルの遅延。

- 3. フィルタ タイプ、COSR、下限/上限スレッショルドなどのコンパレータ フィルタ設定を変更します。

- 4. コンパレータフィルタの少なくともレイテンシ + 5 SD-Cx クロックサイクルの遅延。

- 5. コンパレータフィルタを有効にします。

i2353 CONTROLSS-SDFM: データ フィルタ設定 (フィルタ タイプや DOSR など) を動的に変更する と、誤ったデータ確認イベントがトリガされます

実行時に SDFM データ設定 (フィルタ タイプや DOSR 設定など) が動的に変更されると、誤ったデータ フィルタ準備完了イベントがトリガされます。 スプリアス データ準備完了イベントは、適切に構成されている場合、対応する CPU 割り込み、CLA タスク、DMA トリガをトリガします。

SDFM データフィルタ設定を動的に変更する必要がある場合は、以下の手順に従って、スプリアス データフィルタ準備完了イベントが生成されないようにします。

- 1. データフィルタを無効にします。

- 2. データフィルタの少なくともレイテンシー + 3 SD-Cx クロック サイクルの遅延。

- 3. フィルタ タイプや DOSR などのデータ フィルタ設定を変更します。

- 4. データフィルタの少なくともレイテンシー + 5 SD-Cx クロック サイクルの遅延。

- 5. データフィルタを有効にします。

CONTROLSS-SDFM:SD 変調器の3 クロック サイクル以内に SDCPARMx レジスタのビット フィールド CEVT1SEL、CEVT2SEL、および HZEN に連続して2 回書き込みを行うと、SDFM ステートマシンが破損し、誤ったコンパレータ イベントが発生する可能性があります

3 つの SD モジュレータ クロック サイクル内で SDCPARMx レジスタ ビット フィールド CEVT1SEL、CEVT2SEL、および HZEN に連続書き込みをすると、SDFM ステート マシンが破損する可能性があり、誤ったコンパレータ イベントが発生する可能性があります。これにより、適切に構成されている場合は、CPU 割り込み、CLA タスク、ePWM XBAR イベント、および GPIO 出力 X-BAR イベントがトリガされる可能性があります。

**3** つの SD モジュレータ クロック サイクル内での連続書き込みを避けるか、SDCPARMx レジスタ ビット フィールドを **1** 回のレジスタ書き込みで構成します。

CONTROLSS-ADC:INTxCONT (割り込み継続モード) が設定されていない場合、割り込みは停止する可能性があります

ADCINTSELxNx[INTxCONT] = 0 の場合、ADCINTFLG が設定されると割り込みは停止し、追加の ADC 割り込みは発生しません。ADCINTFLGCLR レジスタのソフトウェア書き込みとともにADC 割り込みが同時に発生すると、ADCINTFLG が予期せず設定されたままになり、将来のADC 割り込みをブロックします。

1. ADCINTFLG が追加の ADC 割り込みをブロックしないように、Continue-to-Interrupt モードを使用します。

i2354

詳細:

回避方法:

詳細:

回避方法:

i2356

詳細:

#### i2356 (続き)

# CONTROLSS-ADC:INTxCONT (割り込み継続モード) が設定されていない場合、割り込みは停止する可能性があります

ADCINTSEL1N2[INT1CONT] = 1;

ADCINTSEL1N2[INT2CONT] = 1;

ADCINTSEL3N4[INT3CONT] = 1;

ADCINTSEL3N4[INT4CONT] = 1;

- 2. この状態を回避するために、次の ADC 割り込みが発生する前に、ADC ISR をサービスし、 ADCINTFLG をクリアするのに十分な時間を常に確保してください。

- 3. ADCINTFLG をクリアするとき、ISR のオーバーフロー状態を確認します。 ADCINTFLGCLR への書き込み直後に ADCINTOVF をチェックし、これが設定されている 場合は、ADCINTFLGCLR をもう一度書き込んで ADCINTFLG がクリアされていることを確認します。 ADCINTOVF レジスタが設定され、ADC 変換割り込みが失われたことを示します。

AdcaRegs.ADCINTFLGCLR.bit.ADCINT1 = 1; //INT1 フラグをクリア

if(1 == AdcaRegs.ADCINTOVF.bit.ADCINT1) //ADCINT オーバーフロー

AdcaRegs.ADCINTFLGCLR.bit.ADCINT1 = 1; //INT1 を再度クリア

// アプリケーションによって ADCINTOVF 条件が無視される場合

// ADCINTOVFCLR に 1 を書き込んでフラグをクリアします。

// ADCINTOVF を処理するルーチンがある場合

// そのコードをここに挿入して ADCINTOVF フラグをクリアするか

// ここで ADCINTOVF をクリアしないようにして

# 外部ルーチンが条件を検出するようにします。

// AdcaRegs.ADCINTOVFCLR.bit.ADCINT1 = 1; // OVF をクリア

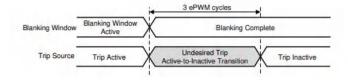

#### i2357

# CONTROLSS-ePWM:ePWM グリッチは、ブランキング ウィンドウの終了時にトリップがアクティブのままの場合、発生する可能性があります

#### 詳細:

ブランキング ウィンドウは通常、システムへの誤ったトリップを引き起こす可能性のある遷移中の PWM トリップ イベントをマスクするために使用されます。 ブランキング ウィンドウ サイクルの終了後、3 未満の ePWM クロックの間 ePWM トリップ イベントがアクティブのまま維持されている場合、ePWM 出力に望ましくないグリッチが発生する可能性があります。

以下の画像に、不要な ePWM 出力が発生する可能性のある時間を示します。

以下の画像に、ブランキング ウィンドウが閉じる前または 3 サイクル後にトリップイベントが 1 サイクル以内に終了した場合に可能性のある 2 つの ePWM 出力を示します。

# i2357 (続き) CONTROLSS-ePWM:ePWM グリッチは、ブランキング ウィンドウの終了時にトリップがアクティ ブのままの場合、発生する可能性があります

ePWM Output Pin (Possibility A)

(Trip interrupt will be issued)

ePWM Output Pin (Possibility B)

(Trip interrupt will not be issued)

Active State

Active State

Trip State

Active State

Active State

回避方法:

トリップ入力がこの範囲(ブランキング ウィンドウの閉じる 1 サイクル前および 3 サイクル後)に入るようなブランキング ウィンドウの構成は避けてください。

i2358

CONTROLSS-ePWM:ブランキング開始後の最初の3 サイクルの間、トリップ イベントはブランキング ウィンドウによってフィルタされません

詳細:

ブランキング ウィンドウは、ブランキング ウィンドウの開始後の最初の 3 サイクルのトリップ イベントをブランクにしません。DCEVTFILT は、DCxEVTy 信号の変更を継続的に反映することができます。DCEVTFILT が有効化されている場合、設定されている後続のサブシステム (たとえば、トリップ ゾーン サブモジュール、TZ 割り込み、ADC SOC、PWM 出力) に影響を及ぼす可能性があります。

回避方法:

ブランキングが必要な前に、ブランキング ウィンドウを 3 サイクル開始します。周期境界でブランキング ウィンドウが必要な場合、次の周期の開始 3 サイクル前にブランキング ウィンドウを開始します。これは、ブランキング ウィンドウが期間の境界を越えて持続するため、機能します。

i2359

CONTROLSS-CMPSS:DACSOURCE を 0 にしたとき、または 1 に再構成したときのプリスケーラ カウンタの動作が仕様と異なります

詳細:

プリスケーラの動作中に DACSOURCE = 0 にした場合、プリスケール カウンタはリセットされません。イネーブル条件が LOW の場合、値は維持され、DACSOURCE が再度 1 として構成された場合、カウンタは以前に保持された値から開始します。このバグは、PRESCALE カウンタの実行中に DACSOURCE が設定されている場合にのみ存在します。

回避方法:

動的構成ではない DACSOURCE 構成間にソフトリセットを発行します。

i2374

R5SS\_CORE\_CLK のクロック周波数が R5FSS\_CLK\_SELECTED 周波数と異なると、PBIST は失敗します

詳細

R5SS メモリは、プログラマブル分周器を使用して R5SS\_CLOCK\_SELECTED ルート クロック から派生する R5SS\_CORE\_CLK (R5SS CPU クロック)を受信します。 PBIST コントローラを使用して R5SS メモリをテストすると、 PBIST コントローラは R5SS\_CLOCK\_SELECTED ルート クロックを受信します。 2 つのクロックに対して異なる周波数を選択すると、 PBIST 動作が失敗します。

回避方法

PBIST を R5SS メモリと組み合わせて使用するには、両方のクロックの周波数を同じにする必要があります。アプリケーションの使用で R5SS\_CORE\_CLK を R5SS\_CLOCK\_SELECTRED の分周周波数にする必要がある場合、R5SS メモリの PBIST 動作中に、アプリケーションによって R5SS\_CORE\_CLK が R5SS\_CLOCK\_SELECTED と同じ周波数に構成されるようにする必要があります。

i2383 OSPI:2 バイト アドレスは、PHY DDR モードではサポートされていません

詳細:

PHY DDR モードで OSPI コントローラが 2 バイト アドレッシングに構成されていると、内部ステート マシンが送信されたアドレス バイト数を誤って (2 ではなく) 1 と比較します。これにより、ステート マシンがアドレス位相でロックアップし、PHY DDR モードが動作不能になります。

この問題は、タップ モードまたは PHY SDR モードを使用する場合は発生しません。 PHY DDR モードで 4 バイト アドレッシングを使用する場合も、この問題は発生しません。

回避方法:

互換性のある OSPI メモリにプログラマブル アドレス バイト設定がある場合は、フラッシュの 2 ~ 4 に必要なアドレス バイト数を設定します。これには、アドレス バイトを変更するための特定のコマンドの送信やフラッシュ上の構成レジスタへの書き込みが含まれる場合があります。 完了したら、コントローラ設定で送信されたアドレス バイト数を 2 から 4 に更新します。

2 バイトアドレッシングのみをサポートし、再プログラムできない互換 OSPI メモリについては、 PHY DDR モードはそのメモリと互換性がありません。 代替モード:

PHY SDR モード

TAP (非 PHY) DDR モード

TAP (非 PHY) SDR モード

i2411

128 バイトのバースト アクセスは、TCM ではサポートされていません

詳細:

インターコネクトの問題により、任意のマスタによる TCM への 128 バイトのバースト アクセスが予想どおりに動作しないため、データが古くなります。

回避方法

128bytes バースト アクセスを使用しないでください。リセット後に、すべてのマスタによってソフトウェアで無効化してください。

i2412

DMA 読み取り書き込みアクセス エラー時に USB は割り込みを生成できません

詳細:

USB には、DMA R/W アクセスにより VBUSM 上で読み取り/書き込みエラー応答が検出された場合に、エラー イベント/割り込みを生成するメカニズムはありません。これは、メモリへのアクセス中にアドレス/MPU エラーが発生し、バスがハングアップした場合に発生する可能性があります。

回避方法:

- 1. SW は TRB とデータに正しいアドレスをプログラムする必要があります。

- 2. USB 転送タイムアウトを使用し、バス エラーを記録する次のレジスタを読み取ります

GSTS. BUSERRADDRVLD(ホスト/デバイス モード) USBSTS.HSE(ホスト モード)

i2427

RAM SEC が誤った RAM 書き込みを引き起こす可能性があり、L2&MBOX のメモリ破損が発生します

詳細:

RAM の読み取りデータ中に、読み取りまたは部分的な書き込みトランザクションにより 1 ビットのエラーが発生した場合、RAM は、次の「メモリ読み取り」がその後の部分的な書き込みトランザクションによるものであると、RAM への後続の誤った書き込みにつながる可能性のある状態になります。「メモリ読み取り」が実際のメモリ読み出しトランザクションによるものであるならば、内部状態

#### i2427 (続き)

# RAM SEC が誤った RAM 書き込みを引き起こす可能性があり、L2&MBOX のメモリ破損が発生します

の残存は消去され、後にスプリアス書き込みが行われる可能性はありません。スプリアス書き込みは、部分的な書き込みトランザクションより前に書き込まれた最後のメモリアドレスに行われ、スプリアス書き込みがトリガされます。この問題は MBOX と L2 にのみ適用されます。

図 2-1 には、問題が該当するシナリオ(例 1、2、3)と該当しないシナリオ(例 4、5、6)を明確に示します。トランザクション番号は説明のためのものであり、各操作が発生する正確なサイクルを必ずしも表しているわけではありません。[SEC-シングル ビット エラー訂正、DED-ダブル ビット エラー検出]

| Ex<br># | Transaction 1                                            | Transaction 2+N<br>N=0,1,2,3                                                                        | Transaction 2+N+1                                                                                                                                               | Transaction 2+N+2                                                                  |  |

|---------|----------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|--|

| 1       | Read or Partial Write<br>Addr A (SEC) ← read<br>with SEC | Full Write Addr $X \leftarrow$ last write prior to partial write Note: N=0                          | Partial Write ← Triggers<br>spurious write                                                                                                                      | Spurious write to Addr X<br>with Transaction 1<br>corrected read data of Addr<br>A |  |

| 2       | Read or Partial Write<br>Addr A (SEC) ← read<br>with SEC | Full Write Addr B Full Write Addr C Full Write Addr D ← last write prior to partial write Note: N=2 | Partial Write ← Triggers spurious write                                                                                                                         | Spurious write to Addr D<br>with Transaction 1<br>corrected read data of Addr<br>A |  |

| 3       | Read or Partial Write<br>Addr A (SEC)                    | Partial Write Addr B Note: N=0                                                                      | Spurious write to Addr A with Transaction 1 corrected read data of Addr A (Addr A is overwritten with the RAM content prior to the Transaction 1 Partial write) |                                                                                    |  |

| 4       | Read Addr A (SEC)                                        | Partial Write Addr B<br>Note: N=0                                                                   | No Spurious write to Addr A with data of address A (no data corrup                                                                                              | write to Addr A with Transaction 1 corrected read is A (no data corruption)        |  |

| 5       | Read or Partial Write<br>Addr A (SEC)                    | Read ← Clears bad internal state<br>Note: N=0                                                       | No spurious writes with all command combinations in subsequent cycles                                                                                           |                                                                                    |  |

| 6       | Read or Partial Write<br>Addr A (SEC)                    | Full Write Addr B<br>Note: N=0                                                                      | Read ← Clears bad internal state                                                                                                                                | No spurious writes will all command combinations in subsequent cycles              |  |

#### 図 2-1.

#### 回避方法:

以下のオプションのいずれかを回避方法として使用できます。

#### オプション 1:

ECC を無効にします。安全でないアプリケーションにのみ適用されます。

#### オプション 2:

メモリへの部分的な書き込みを禁止します(行全体の書き込みのみを実行)

**L2** の場合、L2 スペースがキャッシュ可能な場合、コアは行全体の書き込みのみを実行し、この問題は該当しません。

#### オプション 3:

アプリケーションは、読み取りまたは部分的な書き込みトランザクションで 1 ビットエラーが発生した場合に、アプリケーションがトランザクションを直ちに制御できないと RAM データが破損する可能性があるため、すべての SEC エラーを DED(単一ビット エラーの場合も修正はせず、検出のみ)として処理できます。

#### 注

ECC CTRL-SEC カウンタを通常の SEC 問題とスプリアス書き込みのインジケータとして使用するというこれまでの記述は無効です。スプリアス書き込みが行われた後も、ECC CTRL SEC カウンタは 1 のままになる場合があります。

#### i2428

#### DTHE の AES は、GCM 暗号化の最後に data in に対する追加の DMA 要求を生成します

詳細:

AES エンジンは、暗号化の GCM 暗号化モードの終了時にデータ入力用の追加の DMA 要求を生成します。この問題は、AES-GCM モードを使用した暗号化にのみ適用され、AES-GCM 復号化またはその他のブロック暗号モード(CBC など)には適用されません。

余分な DMA 要求は、数サイクル後に、データが書き込まれることなく、自動的に消失(デアサート)されます。

システム内の DMA が AES-GCM モード用にどのように設定されているかによっては、パケット転送の最後に追加の DMA 要求があると、次のパケットで意図しないデータ転送が発生する可能性があります。

回避方法:

なし

i2433

ICSS:LSW が読み取られるとき、64 ビットIEP タイマの読み取りにはロック MSW ロジックがありません

詳細:

下位 32 ビットデータが 0xFFFFFFC 以上の場合、IEPx 64 ビットのタイムスタンプが不正確になる可能性があります(250MHz の場合)。この場合、上位 32 ビットの値は更新されますが、下位の値は古い値です。この問題は、ICSS PRU コアから IEP カウンタ(IEP\_COUNT\_REG1: IEP COUNT\_REG0)を連続的に読み取ったときに見られます。

#### 事例 1:

1st 読み取り値: 0x000000D0 (上位): 0xFFFFFC (下位)

2nd 読み取り値:0x000000D0(上位):0x00000028(下位)

#### 事例 2:

1st 読み取り値:0x000000D7(上位):0xFFFFFFC(下位)

2nd 読み取り値: 0x000000D7(上位): 0x0000002C(下位)

#### 事例 3:

1st 読み取り値: 0x000000D6(上位): 0xFFFFFF0(下位)

2nd 読み取り値: 0x000000D7(上位): 0xFFFFFFC(下位)

上に示したように、これにより、例 3 のように非単調またはタイマの差であるタイマ インクリメント動作が異常に大きくなります。これは、IEPx カウンタから 64 ビット値をロードするときの 1 サイクル競合状態によるものです。

#### 回避方法:

注:これらの回避方法は SDK9.2 以降で存在します

PRU の C での回避方法:

uint64\_t timestamp = (uint64\_t) (0x2E0010);

/\*回避方法ここから開始\*/

if ((timestamp & 0xffffffff) >= 0xfffffffc)

timestamp = \*(uint64\_t\*) (0x2E0010); }

#### i2433 (続き)

# ICSS:LSW が読み取られるとき、64 ビットIEP タイマの読み取りにはロック MSW ロジックがありません

/\*回避方法ここで終了\*/

PRU のアセンブリでの回避方法:

```

ldi32 r4, 0xFFFFFFFC; 0-4 for 250MHz clock

;load 64-bit timestamp to r2:r3

lbco &r2, c26, 0x10, 8

qbgt skip_iep_read_errata. r2, r4

;re-read IEP if IEP_COUNTER_LOW >= 0xFFFF_FFFC

lbco &r2, c26, 0x10, 8

skip_iep_read_errata:

```

#### R5F、A53 の C での回避方法:

```

uint64_t getIepTimeStamp64 (void)

uint64_t u64Timestamp1 = (volatile uint64_t)(0x300AE010);

uint64_t u64Timestamp2 = (volatile uint64_t)(0x300AE010);

if (u64Timestamp2 > u64Timestamp1)

#ifdef ___DEBUG

if (((u64Timestamp2 >> 32)-(u64Timestamp1 >> 32)) == 1)

/* HW errata fixed due to picking u64Timestamp1*/

if ((u64Timestamp2 & 0xFFFFFFFF) >= (u64Timestamp1 & 0xFFFFFFFF))

DebugP_log ("Errata fixed (1): %llx : %llx \n',

{

u64Timestamp1, u64Timestamp2);

#endif

return u64Timestamp1;

else

#ifdef

_DEBUG

if ((u64Timestamp2 & 0xFFFFFFFF) < (u64Timestamp1 & 0xFFFFFFFF))</pre>

/* Adjust the IEP MSW in the case running into HW errata

DebugP_log ("Errata fixed (2): %llx : %llx\r\n", u64Timestamp1,

u64Timestamp2);

#endif

/* HW errata fixed due to picking u64Timestamp2*/

return u64Timestamp2;

}

}

```

#### i2439 CPSW:ホストからイーサネットへのタイムスタンプの精度の問題

詳細:

イーサネット出力で生成されるタイムスタンプを使用してホストからイーサネットにパケットが送信されると、下位8ビットの0xD5のパケット長はタイムスタンプエラーになります。

PTP メッセージのタイムスタンプの使用は、通常 0xD5 パケット長よりもはるかに短いため、影響を受けません。

#### 回避方法:

イーサネット タイムスタンプを Host Tx 上の PTP メッセージに対してのみ有効にします。

i2440 CPSW:ホストからイーサネットへのタイムスタンプ シーケンス ID の問題

詳細:

タイムスタンプが有効なホストからイーサネットへのパケットでは、特定のシナリオでタイムスタンプに関連付けられたシーケンス ID が正しくない場合があります。タイムスタンプは正しいですが、シーケンス ID が正しくありません。ホストはシーケンス ID を使用して、パケットをタイムスタンプと相関させます。この問題は PTP メッセージには影響しません。

回避方法:

ホストからイーサネットへの接続の場合、タイムスタンプのあるパケットは無効にする必要があります。

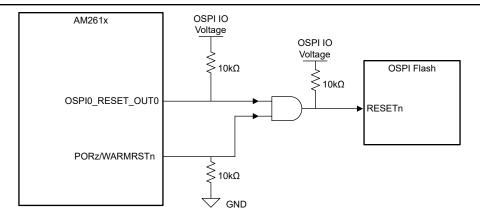

i2479

GPIO61 のリセットピン構成での OSPI ブートの問題

詳細:

OSPI ブートモードのときに、その結果となるフォールバック モードを含む、OSPI ブートモードでは、ROM はピン GPIO61 を OSPIO\_RESET\_OUTO に構成します。このピンが OSPI フラッシュメモリのリセットピンに接続されている場合、OSPI コントローラのリセット信号管理の問題により、ブート障害が発生する可能性があります。

OSPI ブートモード中、ROM コードは次の動作を行います。

- 1. GPIO61 を OSPIO RESET OUTO 多重化モードに構成します

- 2. リセット 信号を正しくアサートします(Low 駆動)

- 3. OSPI コントローラの構成が正しくないため、RESET 信号をデアサートしません(GPIO61 ピンは Low 駆動のまま)

GPIO61 がフラッシュ メモリのリセット ピンに接続されている場合、フラッシュ デバイスは RESET 状態を維持します。これにより、適切なブート シーケンスが完了しません。この問題は、OSPI フラッシュのリセット制御に GPIO61 が使用されているすべてのパッケージ タイプに影響します。

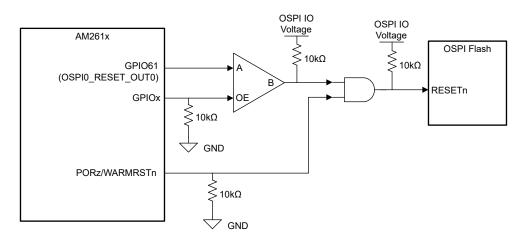

回避方法:

オプション 1:フラッシュをリセットする目的で GPIO61 ピンを使用しないでください。PORz/WARMRSTn を使ってパワー サイクル時にフラッシュ デバイスをリセットし、別の GPIO を OSPI0\_REST\_OUT0 に使用して、その信号を PORz/WARMRSTn で AND ゲートを通過させます。例については、OSPI0\_RESET\_OUT0 ピンと PORz/WARMRSTn を使用した AM261x OSPI リセットを参照してください。

オプション 2:ブート中にリセット ロジックへの伝搬を防止するために GPIO61 をゲートし、フラッシュ デバイスのパワー サイクル中に PORz/WARMRSTn をリセットとして使用してその信号をゲートします。 ゲート制御された GPIO61 ピンと PORz/WARMRSTn を使用した AM261x OSPIのリセットにおける一つの実装例を示します。

# i2479 (続き) GPIO61 のリセット ピン構成での OSPI ブートの問題

図 2-2. OSPI0\_RESET\_OUT0 ピンと PORz/WARMRSTn を使用した AM261x OSPI リセット

図 2-3. ゲートされた GPIO61 ピンと PORz/WARMRSTn を使用した AM261x OSPI リセット

# i2480 OSPI ブート中の GPIO61/OPSI0\_RESET\_OUT0 の 1μs グリッチ

詳細:

OSPI ブートモードのときに、その結果となるフォールバック モードを含む、OSPI ブートモードでは、ROM はピン GPIO61を OSPIO\_RESET\_OUTO に構成します。このピンが OSPI フラッシュメモリのリセットピンに接続されている場合、OSPI コントローラのリセット信号管理の問題により、ブート障害が発生する可能性があります。

OSPI ブートモード中、ROM コードは次の動作を行います。

- 1. GPIO61 を OSPIO\_RESET\_OUTO 多重化モードに構成します

- 2. リセット 信号を正しくアサートします(Low 駆動)

- 3. OSPI コントローラの構成が正しくないため、RESET 信号をデアサートしません(GPIO61 ピンは Low 駆動のまま)

GPIO61 がフラッシュメモリのリセットピンに接続されている場合、フラッシュデバイスは RESET 状態を維持します。これにより、適切なブートシーケンスが完了しません。この問題は、OSPI フラッシュのリセット制御に GPIO61 が使用されているすべてのパッケージ タイプに影響します。また、ユーザーアプリケーションが再構成するまで、GPIO61 は Low のままです。

回避方法:

オプション 1:なし。GPIO61 ピンを使用しないでください。

# i2480 (続き) OSPI ブート中の GPIO61/OPSI0\_RESET\_OUTO の 1µs グリッチ

オプション 2:このピンを使用する必要がある場合は、ユーザー アプリケーション コードでこのピンを再構成できます。しかし、アプリケーションでグリッチの影響を受けやすい場合は、外部回路に適切なフィルタリングを組み込むことで、接続されているペリフェラルにグリッチが影響を与えないようにします。

# 3 商標

すべての商標は、それぞれの所有者に帰属します。

# 4 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| C | Changes from NOVEMBER 7, 2024 to APRIL 30, 2025 (from Revision * (November 2024) to |      |  |  |  |

|---|-------------------------------------------------------------------------------------|------|--|--|--|

| R | evision A (April 2025))                                                             | Page |  |  |  |

| • | アドバイザリ i2479:GPIO61 のリセット ピン構成での OSPI ブートの問題                                        | 14   |  |  |  |

| • | アドバイザリ i2480:OSPI ブート中の GPIO61/OPSIO RESET OUTOの 1µs グリッチ                           | 15   |  |  |  |

|   |                                                                                     |      |  |  |  |

# 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した テキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているテキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、テキサス・インスツルメンツの販売条件、または ti.com やかかる テキサス・インスツルメンツ製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2025, Texas Instruments Incorporated

### 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、 テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した テキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている テキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、 テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。 テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、 テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、 テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、 テキサス・インスツルメンツの販売条件、または ti.com やかかる テキサス・インスツルメンツ 製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。 テキサス・インスツルメンツがこれらのリソ 一スを提供することは、適用される テキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、 テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所:Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2025, Texas Instruments Incorporated