## ホワイト・ペーパー

Tom Catalino 副社長

Critical Link. LLC

Asheesh Bhardwaj

DSP シニア・アプリケーション・エンジニア テキサス・インスツルメンツ

#### はじめに

マシン・ビジョン技術の採用は増加傾向にあ り、様々なアプリケーション領域に展開されて います。たとえば、シート製品、医薬品、半導 体、自動車からかみそりの刃までといった、 様々な製品を製造する際に使用される計装 機器や検査機器の領域にも広がっていま す。マシン・ビジョンを採用するアプリケーショ ンには、デバイスの事前設定だけでは満た すことができないような固有のビジョン・シス テム要件があります。このホワイト・ペーパー では、計算量の多い様々なマシン・ビジョン・ システムを対象として追加リソースを含めた アーキテクチャに関する詳細説明を提供して おり、読者は本アーキテクチャまたは類似の アーキテクチャに基づいて独自のビジョン・シ ステムを設計できます。

# 計算量の多い様々なシステムに柔軟な マシン・ビジョン用アーキテクチャ

### 課題

マシン・ビジョン・システムのアルゴリズムは、計算量が非常に多いため専用のハードウェアを必要とすることがあります。また、各アプリケーションには固有の要件があり、それらはコーデックや ASIC によるビジョン分析および動画圧縮などの専用機能に特化したデバイスやコアよりも、むしろ DSP や FPGA のようなプログラマブル・アーキテクチャが役立ちます。

現在、標準準拠のビジョン・システムを構成する要素として最適かつ導入も 簡単なビジョン製品が数多く市販されています。このような製品として、たとえば OpenCV を使用したオープン・ソースのビジョン・アルゴリズムがあります。そし て、多くのビジョン・システムの標準システムは、様々な標準ビデオ・フォーマット (MPEG-4、H.264 など) を対応したビデオ・エンコードやトランスコード、また標 準的なデジタル・インターフェイス (USB、GigE、Camera Link、HDMI など) に対応する必要があります。

しかし、特殊なカメラを開発する場合はどうでしょう。たとえば、カメラを開発する場合、必ずしも毎秒 30、60 フレーム (fps) のフル解像度・高精細度動画を必要としないこともあり、この場合特定のある小さな領域で解像度 50×50 ピクセルに対して、高フレーム・レートの数千 fps でフル・カスタマイズのアルゴリズム処理が必要となることがあります。またその一方で、これとは逆に非常に高い解像度の画像に対して、低総消費電力かつ低フレーム・レートでカスタム・アルゴリズムを実行する場合もあります。このような特殊なカメラの生産量はおそらく中小規模であり、特殊 ASIC を開発するのに必要となるスケジュールやコスト、リスクを十分に正当化することができません。

本書では、これらのような固有要件に対処するアーキテクチャについて説明 し、概略的なコンセプトに基づいてユーザが独自の設計を推進するために必要 なリソースを提供します。

#### アーキテクチャ

これらの要件を持つ数々の設計において、テキサス・インスツルメンツのデザイン・ネットワークのメンバーである Critical Link 社が使用するアーキテクチャでは、uPP インターフェイスの使用によって優れた能力と柔軟性を備えた TI 社製品 OMAP-L138 DSP+ARM9™ プロセッサと、Xilinx 社の FPGA 製品 Spartan-6 ファミリーを活用しています。本書内で図示しているように、これらの2 つのデバイスを Critical Link 社の MityDSP-L138F System on Module (SoM) と組合せることにより、固有要件に対して対処可能でかつ効率的な低消費電力システムを実現します。

## Xilinx Spartan-6 による プログラマブル・ロジック

ハードウェア設計にプログラマブル・ロジックを組み込むことにより、システム全体の柔軟性を向上させることができます。このとき、TI 社製品 OMAP-L138 プロセッサや本書内で示すシステムに適合するものとして Xilinx 社の製品 Spartan-6 が適しています。Spartan-6 は SelectIO を備えており、LVDS や LVTTL、LVCMOS、その他様々なシグナリング標準に対応するように設定することができます。また、設計中のシステムに対して最も適したデジタル画像センサに直接インターフェイスするようにカスタマイズすることができます。さらに、CCD カメラなどのアナログ・ベース・センサと FPGA 間の ADC を設計することによって、これらセンサとのインターフェイスに使用することもできます。

FPGA で画像データを収集すると、プログラマブル・ロジックを使用してデータに関する様々な操作を迅速かつ効率的に実行できます。FPGA は、エッジやコーナーの検出、抽出、および低レベル分析などの操作に最適です。また、FPGA では、基本的なフレーム毎の操作を効率的に実行することもできます。

さらに、生データから DSPまたはアプリケーション・プロセッサで処理する必要があるデータのみを選別できるという利点もあります。このことは、高フレーム・レートにおけるフル解像度動画ストリームの全フレーム分析など処理要件が DSP またはアプリケーション・プロセッサで処理可能なレベルを超えた場合や、またはデータ量がプロセッサのデジタル・インターフェイスで取り込むことができるレベルを超えるほど膨大な場合に特に有効です。この生データからのデータ選別は、FPGA を使用してアプリケーション・プロセッサが処理する画像の特定の領域(ライセンス・プレートや顔など)を静的・動的に識別したり、画像のヒストグラムなどの主要統計データやバックグラウンド推定値を計算してその情報をOMAP-L138 プロセッサに提供したりする際に実行されます。

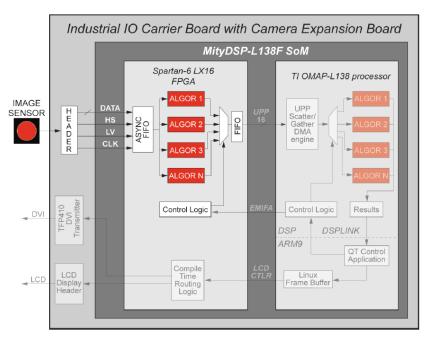

図 1. Xilinx FPGA での画像処理

Xilinx Spartan-6 FPGA は、非常に高いフレーム・レートでデータをキャプチャし、無関係のフレームのすべてまたは一部を削除することができます。したがって、DSP で処理する対象となるデータのみを渡すことができ、FPGA と DSP またはアプリケーション・プロセッサ間の通信量を低減します。

Xilinx Spartan-6 デバイスは、パラレル・ハードウェア・アーキテクチャを使用した高性 能動画加速ブロックを実装するために活用できる DSP48A1 スライスを最大 180 個装 備しています。また、Xilinx では、開発時間を短縮する動画および画像処理 IP コアも提 供しています。

さらに、Xilinx FPGA は非標準インターフェイスを実装するためにも使用されます。これには、例えばマルチ・ディスプレイ・システムやマルチ・カメラ・システム、カスタム同期シリアル・インターフェイス、カスタム・パラレル・インターフェイス、およびシステム内のアプリケーション・プロセッサは対応していない追加標準インターフェイス用に追加された機能などがあります。これらのインターフェイスは、FPGA (LVDS など) によって提供された様々な物理レイヤを再び利用することができます。

## FPGA から uPP を介して DSP に画像データを搬送

Critical Link では、TI OMAP-L138 プロセッサ上の uPP インターフェイスを使用して、Xilinx Spartan-6 から OMAP-L138 プロセッサの DSP へ画像データを 搬送しています。このインターフェイスは、プロセッサのメモリとの連続的な大量データ移行用に特別に設計されています。

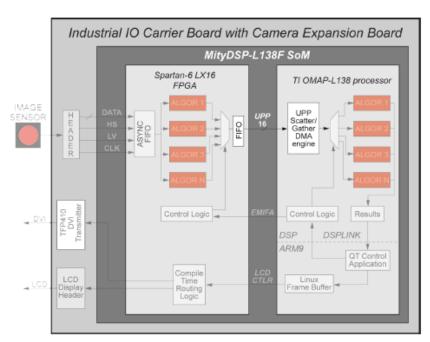

uPP は、クロック・サイクルあたり 1 データ・ワード (8 ビットまたは 16 ビット) をクロック制御することができます。(ダブル・データ・レートでは、クロックあたり 2 データ・ワードを処理することができますが、クロック速度は 1/2 になります。) uPP のクロック・レートは最大でプロセッサ・クロック・レートの 1/2 であり、最大 uPP クロック 75 MHz において最大毎秒150 メガバイトのスループットを実現します。 uPPインターフェイスは FPGA にも簡単に組込むことができます。 (次ページの図 2 を参照。)

TI OMAP-L138 プロセッサは uPP インターフェイスを 2 本有し、それぞれ独立して設定できます。uPP インターフェイスは、ハードウェアの観点から非常にシンプルな同期データ・インターフェイスです。クロック・ピン、データ・ピン、および複数の制御ピンが持ち、これらによって有効データや開始または待機状態を示します。uPP インターフェイスはパラレル AD コンバータや DA コンバータに接続して使用することができます。

図 2 に示した uPP のデータ通信を例として考えた場合に Xilinx Spartan-6 FPGA から OMAP-L138 プロセッサ・システム・メモリに転送できる理論上の最大 fps を表 1 に示します。ただし、センサが必要とするフレーム間またはライン間ギャップは、計算上はないものとします。OMAP-L138 プロセッサの 456 MHz ARM9™ および 456 MHz 浮動小数点 DSP が、データに対して意図したアルゴリズムを実行する能力は、全体的な処理済みフレーム・レートに影響を及ぼします。したがって、システムの規模を拡張する場合はこの点を考慮する必要があります。

図2. TI OMAP-L138 DSP+ARM9™ プロセッサと FPGA との間の uPP インターフェイス

意図したアルゴリズムの実行試験は、可能であればプロトタイプのシステムや評価モジュールを用いてください。DSP または ARM® 上でのアプリケーション処理がシステム設計の制限要因として特定されている場合、OMAP-L138 プロセッサから FPGA に移行することができる反復操作を正確に識別することによって、FPGA を最も活用することができます。このとき、DSP と ARM は、非反復操作、よりグローバルな操作、または一度に複数のフレームを必要とする操作を行う状態になります。キャプチャ・レートが非常に高く、uPP 周辺機器がロウ・データの全量を処理できない場合、FPGA を使用して全体的なデータレートを下げることができます。

| W×H         | バイト / ピクセル | fps    |

|-------------|------------|--------|

| 1024 × 1    | 2          | 73,242 |

| 64 × 64     | 2          | 18,311 |

| 256 × 256   | 2          | 1,144  |

| 1024 × 256  | 2          | 286    |

| 640 × 480   | 2          | 244    |

| 752 × 480   | 2          | 208    |

| 640 × 480   | 3          | 163    |

| 1024 × 768  | 2          | 95     |

| 1280 × 720  | 2          | 81     |

| 1280 × 720  | 3          | 54     |

| 1920 × 1080 | 2          | 36     |

| 1920 × 1080 | 3          | 24     |

表 1. uPP を介した理論的フレーム (@150 MB/s)

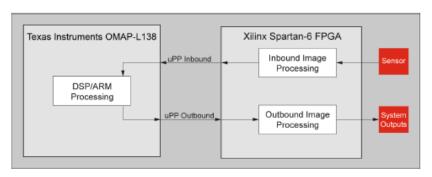

uPP の 2 本の独立チャネルを使用して、図 3 に示すようなアーキテクチャを実装することができます。インバウンド・データを FPGA で前処理し、uPP を介して OMAP- L138 プロセッサ内の DSP に送信できます。ここでさらにインテリジェントな画像・動画解析操作を実行するように動作します。最後に、FPGA を介して任意の出力インターフェイスにデータを返送することができます。このデータが再び FPGA を通過する際、OMAP-L138 の ARM コアが提供するグラフィカル・ユーザ・インターフェイス上で動画をオーバーレイしたり、または OMAP-L138 プロセッサ内の DSP によって指示されたテキストや他のグラフィカル・オーバーレイを提供したりするなどの低レベル出力処理を実行することができます。

図 3. TI OMAP-L138 DSP+ARM9 プロセッサとの uPP データ入出力

## OMAP-L138 プロセッサを用いた 統合 ARM と DSP 処理

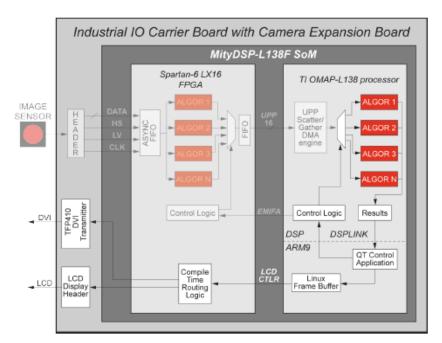

ここまで、FPGA へのデータ収集、FPGA によるデータの処理、および OMAP-L138 プロセッサへのデータ転送について説明してきました。また、OMAP-L138 プロセッサは、入出力画像データを処理するために 456 MHz ARM9 アプリケーション処理コアおよび 456 MHz TMS320C674x DSP コアを組み込んだ独自のアーキテクチャを提供していることも説明してきました。

Critical Link で一般的に活用されている OMAP-L138 プロセッサ と Xilinx Spartan-6 FPGA を組み合わせたアーキテクチャでは、FPGA から前処理された画像データを受信すると、この画像データに対して OMAP-L138 プロセッサの DSP が残りのアルゴリズムを実行します。この作業は、C または C++ でハンド・コーディングされ、DSP 用に最適化したカスタム・アルゴリズムによって実行されます。このカスタム・アルゴリズムの最適化は、Code Composer Studio™ 統合開発環境 (IDE) にある TI 提供のコンパイラか、または画像処理・動画処理用に TI が提供している最適化済みライブラリ、IMGLIB とVLIB を使用することによって実行できます。 OpenCV は、DSP に移植しやすい、ビジョンに関連する多くのアルゴリズムを採用しているオープン・ソースのライブラリです。

DSP は、オブジェクト検出、オブジェクト識別、エッジ検出、色変換、画像フィルタ処理、オブジェクト追跡およびサイズ変更など、計算集約的な画像分析および処理演算を実行することができます。

オブジェクトの形状、クラック、ほこり、その他の異常を検出するために、マシン・ビジョン・アルゴリズムには多くのフィルタリング操作が必要です。Dilation、erosion、Sobel、Canny フィルタ、Harris、Hough および Haar 分類子は、オブジェクトの検出と特長の抽出に役立ちます。オブジェクト検出および追跡アルゴリズムは、主に Lucas Kanade、オプ

ティカル・フロー、Kalman フィルタ、Bhattacharya 距離およびガウス・モデルでサポートされます。

画像処理操作のほとんどは、グレースケールまたは RGB カラーモードで行われます。 YCbCr フォーマットの画像データをキャプチャした場合は、ルミナンス Y データを使用したグレースケール処理が可能です。RGB フォーマットのデータをキャプチャした場合は、必要となる処理のタイプに応じて YCbCr フォーマットに変換することも RGB フォーマットのままにすることもできます。様々な信号処理アルゴリズムを実行する機能は、IMGLIBと VLIB のいずれか、または、OpenCV で利用可能な要素です。また、開発されたアプリケーションは、外部のメモリへの DMA アクセスを利用するので、データをより高速で処理するために内部メモリに転送することができます。

図 4. TI OMAP-L138 DSP+ARM9 プロセッサの画像処理

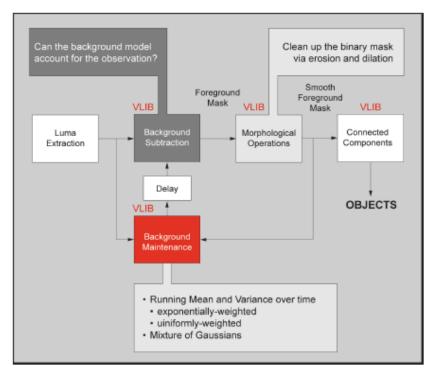

移動オブジェクト・セグメンテーションは、動画処理をグレースケール・モードで実行 (バックグラウンド・データを削除してフォアグラウンド・データを処理) するマシン・ビジョン処理 のひとつです。1 この作業は、フォアグラウンド・マスク上での拡大・縮小のような形態操作で行われます。オブジェクト境界は、連結成分モデルを使用して形成されます。(次ページの図5を参照。)

16 ビット精度の移動オブジェクト・セグメンテーションは、単一のガウス・モデルの 16 ビット精度よりもパフォーマンスが低くなります。必要となる操作のタイプに応じて、DSP に供給する近似解像度を選択できます。データが外部のメモリにあるときは、VLIB 処理のために 50% のオーバーヘッドが加わります。

図 5. 移動オブジェクト・セグメンテーション

外部のシステム・インターフェイスは、ARM コアに接続し、ARM コアで管理されるので、データ処理とドライバの処理負荷をそこで処理することができます。計算処理を 3 つのコアに分割することによって、アーキテクチャから最大の処理能力が得られます。

| VLIB 関数        | サイクル / ピクセル |

|----------------|-------------|

| YUV を Luma に変換 | 0.38        |

| バックグラウンドの減算    | 1.38        |

| 縮小             | 0.2         |

| 拡大             | 0.2         |

| EWRMean        | 1.16        |

| EWRVariance    | 1.37        |

| CreateCCList   | 1.8         |

表 2. VLIB パフォーマンス・ベンチマーク

DSP アルゴリズム作業の実行中、DSP は OMAP-L138 プロセッサの ARM と通信することができ、また ARM を介して外部の世界と通信することができます。これは、ローカルまたはリモート・ユーザ・インターフェイスでも、より大きなシステム内の別の処理サブシステムでもかまいません。DSP は、TI の DSPLink ライブラリが提供する共用メモリ、メールボックス、その他様々な他のメカニズムを介して ARM と通信することができます。RingIO、MessageQ、および Notify は、DSPLink 内にこの通信用のインターフェイスを提供します。ARM と DSP とでデータ・ポインタを共有するために、これらのプロセッサ間

の共用メモリ領域が使用されます。DSPLink ライブラリによってデータ交換効率が向上されます。

設定データは ARM から DSP に渡されます。測定値、統計値、および処理された画像・動画データまたはこれらの生データは、 ARM に渡され、外部の世界と共有することができます。ARM は、埋込みの Linux™、Windows® CE、QNX® または ThreadX などフル機能のオペレーティング・システムを実行することができるので、通信とディスプレイ機能に最適です。

## サマリー

本書では、マシン・ビジョン市場における様々な要件のうち、そのいくつかに対応するアーキテクチャについて説明しています。本アーキテクチャでは、Xilinx Spartan-6 FPGA (設計段階では任意のファミリーの FPGA を使用可能) の能力、TI OMAP-L138 プロセッサの浮動小数点 DSP、固定小数点 DSP、ARM9™、および uPP インターフェイス周辺機器を活用します。

各トピックに関する追加情報については、以下の参考ドキュメントを参照してください。特に、MityDSP-L138F SoM と Critical Link が提供するビジョン開発キットは、技術者が自らの設計において本アーキテクチャをさらに研究するための便利なプラットフォームを提供します。

- Critical Link MityDSP

- Critical Link ビジョン開発キット

- TI OMAP-L138 DSP+ARM9 プロセッサ

- Xilinx Spartan-6

- Xilinx 画像処理ライブラリ

- TI IMGLIB

- TI VLIB

- TI Code Composer Studio IDE

- Open-Source OpenCV

- OpenCV on TI

### 参考ドキュメント

"An Optimized Vision Library Approach for Embedded Systems (埋込みシステム用に最適化されたビジョン・ライブラリ・アプローチ)"、G. Dedeoglu、B. Kisacanin、D. Moore、V. Sharma、A. Miller、IEEE Workshop on Embedded Computer Vision (埋込みコンピュータ・ビジョンに関する IEEE ワークショップ) 議事録、pp. 8 ~ 13、2011 年

"Moving Object Segmentation for Security and Surveillance Applications (セキュリティ および監視アプリケーションのための移動オブジェクト・セグメンテーション)"、G. Dedeoglu、D. Moore、Texas Instruments, Inc.、Embedded Vision Summit (埋込みビ ジョン・サミット) 議事録、2012 年 9 月

ご注意 Texas Instruments Incorporated および本書に記載するその子会社の製品およびサービスは、TI の標準販売契約約款に従って販売されます。お客様は、発注される前に、TI の製品およびサービスに関する最新の完全な情報を取得してください。TI は、アプリケーション支援、カスタマ・アプリケーションまたはプロダクト・デザイン、ソフトウェア・パフォーマンス、または特許権侵害について、一切の責任を負わないものとします。他社の製品またはサービスに関する情報の公開は、それらに関する TI の承認、保証またはその支持を表すものではありません。

Code Composer Studio は、Texas Instruments Incorporated の商標です。その他のすべての商標は、それぞれの所有者に帰属します。

# ご注意

Texas Instruments Incorporated 及びその関連会社(以下総称してTIといいます)は、最新のJESD46に従いその半導体製品及びサービスを修正し、改善、改良、その他の変更をし、又は最新のJESD48に従い製品の製造中止またはサービスの提供を中止する権利を留保します。お客様は、発注される前に、関連する最新の情報を取得して頂き、その情報が現在有効かつ完全なものであるかどうかご確認下さい。全ての半導体製品は、ご注文の受諾の際に提示されるTIの標準販売契約約款に従って販売されます。

TIは、その製品が、半導体製品に関するTIの標準販売契約約款に記載された保証条件に従い、販売時の仕様に対応した性能を有していることを保証します。検査及びその他の品質管理技法は、TIが当該保証を支援するのに必要とみなす範囲で行なわれております。各デバイスの全てのパラメーターに関する固有の検査は、適用される法令によってそれ等の実行が義務づけられている場合を除き、必ずしも行なわれておりません。

TIは、製品のアプリケーションに関する支援又はお客様の製品の設計について責任を負うことはありません。TI 製部品を使用しているお客様の製品及びそのアプリケーションについての責任はお客様にあります。TI 製部品を使用したお客様の製品及びアプリケーションに関連する危険を最小のものとするため、適切な設計上及び操作上の安全対策は、お客様にてお取り下さい。

TIは、TIの製品又はサービスが使用されている組み合せ、機械装置、又は方法に関連しているTIの特許権、著作権、回路配置利用権、その他のTIの知的財産権に基づいて何らかのライセンスを許諾するということは明示的にも黙示的にも保証も表明もしておりません。TIが第三者の製品もしくはサービスについて情報を提供することは、TIが当該製品又はサービスを使用することについてライセンスを与えるとか、保証又は是認するということを意味しません。そのような情報を使用するには第三者の特許その他の知的財産権に基づき当該第三者からライセンスを得なければならない、又はTIの特許その他の知的財産権に基づきTIからライセンスを得て頂かなければならない場合もあります。

TIのデータ・ブック又はデータ・シートの中にある情報の重要な部分の複製は、その情報に一切の変更を加えること無く、且つその情報と関連する全ての保証、条件、制限及び通知と共になされる限りにおいてのみ許されるものとします。TIは、変更が加えられて文書化されたものについては一切責任を負いません。第三者の情報については、追加的な制約に服する可能性があります。

TIの製品又はサービスについて TI が提示したパラメーターと異なる、又は、それを超えてなされた説明で当該 TI 製品又はサービスを再販売することは、関連する TI 製品又はサービスに対する全ての明示的保証、及び何らかの黙示的保証を無効にし、且つ不公正で誤認を生じさせる行為です。TI は、そのような説明については何の義務も責任も負いません。

TI からのアプリケーションに関する情報提供又は支援の一切に拘わらず、お客様は、ご自身の製品及びご自身のアプリケーションにおける TI 製品の使用に関する法的責任、規制、及び安全に関する要求事項の全てにつき、これをご自身で遵守する責任があることを認め、且つそのことに同意します。お客様は、想定される不具合がもたらす危険な結果に対する安全対策を立案し実行し、不具合及びその帰結を監視し、害を及ぼす可能性のある不具合の可能性を低減し、及び、適切な治癒措置を講じるために必要な専門的知識の一切を自ら有することを表明し、保証します。お客様は、TI 製品を安全でないことが致命的となるアプリケーションに使用したことから生じる損害の一切につき、TI 及びその代表者にその全額の補償をするものとします。

TI 製品につき、安全に関連するアプリケーションを促進するために特に宣伝される場合があります。そのような製品については、TIが目的とするところは、適用される機能上の安全標準及び要求事項を満たしたお客様の最終製品につき、お客様が設計及び製造ができるようお手伝いをすることにあります。それにも拘わらず、当該TI 製品については、前のパラグラフ記載の条件の適用を受けるものとします。

FDA クラスIII(又は同様に安全でないことが致命的となるような医療機器)へのTI 製品の使用は、TIとお客様双方の権限ある役員の間で、そのような使用を行う際について規定した特殊な契約書を締結した場合を除き、一切認められていません。

TIが軍需対応グレード品又は「強化プラスティック」製品として特に指定した製品のみが軍事用又は宇宙航空用アプリケーション、若しくは、軍事的環境又は航空宇宙環境にて使用されるように設計され、かつ使用されることを意図しています。お客様は、TIがそのように指定していない製品を軍事用又は航空宇宙用に使う場合は全てご自身の危険負担において行うこと、及び、そのような使用に関して必要とされるすべての法的要求事項及び規制上の要求事項につきご自身のみの責任により満足させることを認め、且つ同意します。

TIには、主に自動車用に使われることを目的として、ISO/TS 16949の要求事項を満たしていると特別に指定した製品があります。当該指定を受けていない製品については、自動車用に使われるようには設計されてもいませんし、使用されることを意図しておりません。従いまして、前記指定品以外のTI製品が当該要求事項を満たしていなかったことについては、TIはいかなる責任も負いません。

Copyright © 2013, Texas Instruments Incorporated 日本語版 日本テキサス・インスツルメンツ株式会社

## 弊社半導体製品の取り扱い・保管について

半導体製品は、取り扱い、保管・輸送環境、基板実装条件によっては、お客様での実装前後に破壊/劣化、または故障を起こすことがあります。

弊社半導体製品のお取り扱い、ご使用にあたっては下記の点を遵守して下さい。

- 1. 静電気

- 素手で半導体製品単体を触らないこと。どうしても触る必要がある場合は、リストストラップ等で人体からアースをとり、導電性手袋等をして取り扱うこと。

- 弊社出荷梱包単位(外装から取り出された内装及び個装)又は製品 単品で取り扱いを行う場合は、接地された導電性のテーブル上で(導 電性マットにアースをとったもの等)、アースをした作業者が行う こと。また、コンテナ等も、導電性のものを使うこと。

- マウンタやはんだ付け設備等、半導体の実装に関わる全ての装置類は、静電気の帯電を防止する措置を施すこと。

- 前記のリストストラップ・導電性手袋・テーブル表面及び実装装置類の接地等の静電気帯電防止措置は、常に管理されその機能が確認されていること。

- 2. 温·湿度環境

- 温度:0~40°C、相対湿度:40~85%で保管・輸送及び取り扱いを行うこと。(但し、結露しないこと。)

- 直射日光があたる状態で保管・輸送しないこと。

- 3. 防湿梱包

- 防湿梱包品は、開封後は個別推奨保管環境及び期間に従い基板実装すること。

- 4. 機械的衝撃

- 梱包品(外装、内装、個装)及び製品単品を落下させたり、衝撃を 与えないこと。

- 5. 熱衝撃

- しました付け時は、最低限 260℃以上の高温状態に、10秒以上さらさないこと。(個別推奨条件がある時はそれに従うこと。)

- 6. 汚染

- はんだ付け性を損なう、又はアルミ配線腐食の原因となるような汚染物質(硫黄、塩素等ハロゲン)のある環境で保管・輸送しないこと。

- はんだ付け後は十分にフラックスの洗浄を行うこと。(不純物含有率が一定以下に保証された無洗浄タイプのフラックスは除く。)

以上