# ADC3660x/ ADC364x 評価基板

## 説明

ADC3660/ADC364x 評価基板 (EVM) は、ADC36xx ファミリの高速 A/D コンバータ (ADC) を評価するために設計されています。このファミリには、ADC3660、ADC3644、ADC3643 があります。これらのデバイスはすべて、シリアル低電圧 CMOS (LVCMOS) インターフェイスを備えています。

## 設計を開始

1. [ADC3660EVM](#)、[ADC3644EVM](#)、または [ADC3643EVM](#) をご注文ください

2. データシートの最新版をダウンロードしてください

3. 最新のソフトウェアのダウンロードしてください

4. EVM のツールページから、総合的なリファレンスデザイナーファイルをダウンロードしてください

## 特長

- オンボード バランを使用した AC 結合アナログ入力に対して、シングルエンドおよび差動入力の両方のオプションを提供

- サンプリング クロック入力に対して、シングルエンドおよび差動入力の両方のオプションを提供

- 外部 12V 接続による給電と、オンボード電源レギュレーションを備えています

- USB-C 接続または FMC コネクタを介して、スイッチ制御による柔軟な ADC 設定が可能

- FMC コネクタは、TI データキャプチャカードまたは他社製 FPGA 開発キットとのインターフェイスとして機能

## アプリケーション

- ソフトウェア無線

- 通信インフラ

- スペクトル アナライザ

- 医療 / ヘルスケア

- 制御システム

ADC3660/ADC364xEVM

## 1 評価基板の概要

### 1.1 はじめに

ADC3660/ADC364xEVM は、テキサス インスツルメンツ製の A/D コンバータ (ADC) ファミリである ADC36xx の評価に使用される評価ボードです。ADC36xx は、シリアル LVC MOS インターフェイスを使用してデジタル データを出力します。ADC36xx は、内部デシメーション フィルタを用いた「オーバーサンプリング + デシメーション」モードで動作させることで、ダイナミックレンジを向上させることができます。

評価基板はデフォルトで、AC 結合トランス (バラン) 入力を用いてサンプリング クロックおよびアナログ入力の外部信号を受け取るように構成されています。このトランスはシングルエンドから差動への変換を行い、低ノイズかつ低歪のパッシブ 入力を提供します。

このユーザー ガイドでは、ADC3660/ADC364x 評価基板 (EVM) の特性、動作、および使用方法について説明します。さらに、ソフトウェアおよびハードウェアのセットアップと構成方法についても解説します。

### 1.2 キットの内容

EVM 評価キットには、以下の機器が同梱されています。

**表 1-1. 同梱機器**

| 項目                          | 説明          | 数量 |

|-----------------------------|-------------|----|

| ADC3660/<br>ADC364xEVM      | PCB         | 1  |

| DC ジャック電源ケーブル               | ケーブル        | 1  |

| USB-C ケーブル                  | ケーブル        | 1  |

| JTAG ドングルおよび Micro USB ケーブル | PCB およびケーブル | 1  |

### 1.3 製品情報

ADC3660/ADC364xEVM には、LVDS 出力インターフェイスを備えたこのファミリのデバイスをカバーする 3 種類のバリエントがあります。それぞれは ADC3660EVM、ADC3644EVM、および ADC3643EVM です。

以下は、これらの各 EVM バリエントで評価可能なデバイスの一覧です。

**表 1-2. ADC3660EVM を使用して評価するデバイス**

| ADC3660EVM |       |     |           |

|------------|-------|-----|-----------|

| デバイス       | チャネル数 | 分解能 | 最大サンプルレート |

| ADC3660    | 2     | 16  | 65MHz     |

**表 1-3. ADC3644EVM を使用して評価するデバイス**

| ADC3644EVM |       |     |           |

|------------|-------|-----|-----------|

| デバイス       | チャネル数 | 分解能 | 最大サンプルレート |

| ADC3644    | 2     | 14  | 125MHz    |

**表 1-4. ADC3643EVM を使用して評価するデバイス**

| ADC3643EVM |       |     |           |

|------------|-------|-----|-----------|

| デバイス       | チャネル数 | 分解能 | 最大サンプルレート |

| ADC3643    | 2     | 14  | 65MHz     |

| ADC3642    | 2     | 14  | 25MHz     |

| ADC3641    | 2     | 14  | 10MHz     |

## 2 ハードウェア

本セクションでは、ADC3660、ADC3644、および ADC3643 各バリエント評価基板を含む ADC3660 および ADC364x EVM を効果的に使用するために必要なハードウェア ツールおよび接続について詳述します

### 2.1 必要なハードウェア

以下の機器は EVM 評価キットには含まれていませんが、この EVM を評価するために必要です。

- TSWDC155EVM データキャプチャ ボードおよび関連機器

- アナログ入力、サンプル クロック、および **DCLKIN** 信号用の低ノイズ信号発生器 3 台(これらの信号発生器は同一のリファレンス周波数を共有する必要があります)

- 希望するサンプル クロック周波数およびアナログ入力周波数に対応したバンドパス フィルタ 2 個。

- 12V、1A を供給可能な電源装置 1 台。

- Microsoft® Windows® 10 または 11 が動作する PC。

TI は、アナログ入力およびクロック入力用として、以下の低位相ノイズ信号発生器を推奨しています。

- Rohde & Schwarz SMA100A

- Rohde & Schwarz SMA100B

- Keysight E8257D

- Hewlett Packard HP8644B

- Rohde & Schwarz SMHU

- またはこれらと同等の機器

すべての信号発生器には、スプリアス成分やノイズを除去するためにバンドパス フィルタが必要です。ただし、**DCLKIN** 入力にはバンドパス フィルタは不要です。バンドパス フィルタを使用しない場合、ADC の真の性能を必ずしも十分に確認できず、使用している信号発生器の性能によって結果が制限されます。

使用するバンドパス フィルタは、以下の特性を備えていることが推奨されます。

- 高調波減衰量: 60dB 以上

- 帯域幅: 10% 以下

- 許容電力: 18dBm 超

- 挿入損失: 5dB 未満

## 2.2 ハードウェア設定

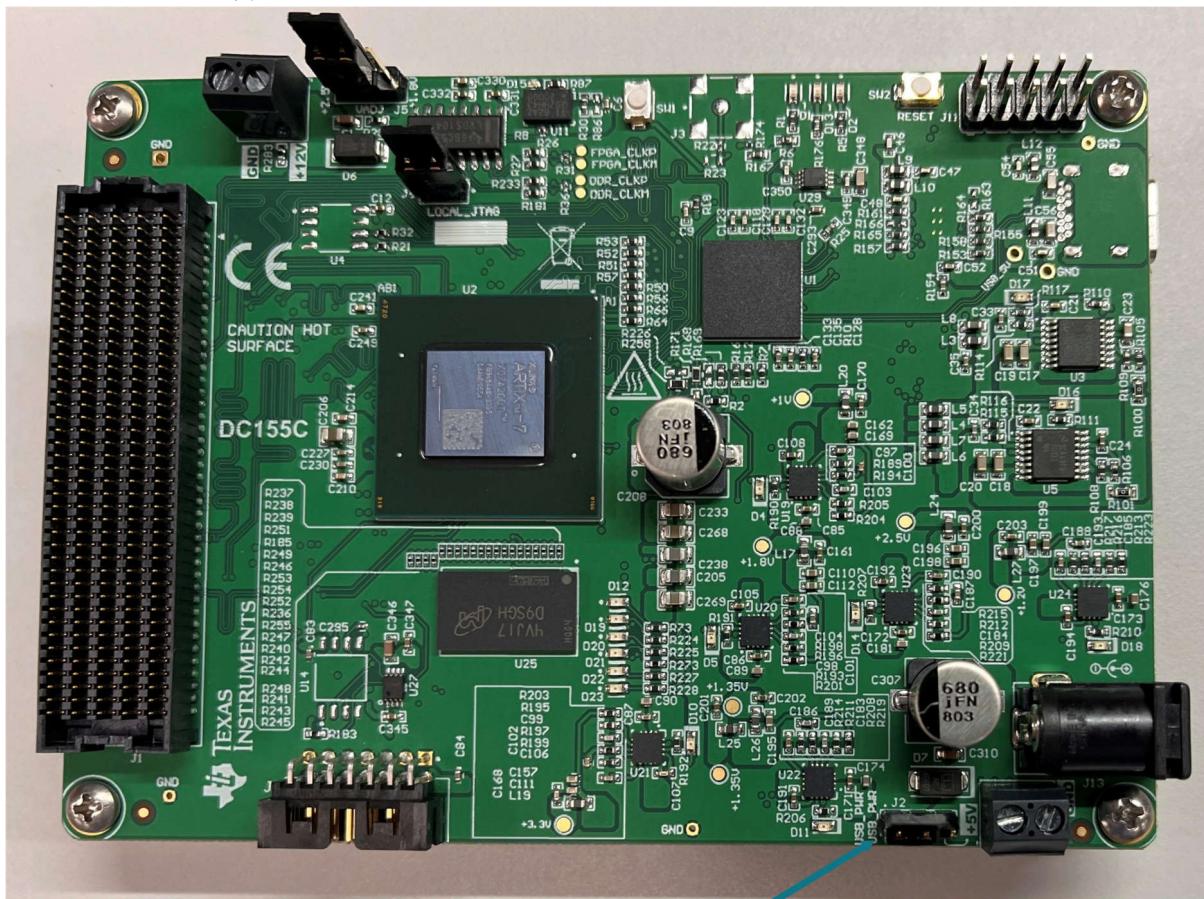

1. ADC3660/ADC364xEVM を FMC コネクタ経由で TSWDC155EVM に接続します。

2. 付属の USB-C ケーブルを使用して、PC と ADC3660/ADC364xEVM 上の J3 USB-C コネクタを接続します。

3. 付属の USB-C ケーブルを使用して、PC と TSWDC155EVM 上の J8 USB-C コネクタを接続します。

4. Micro USB ケーブルを JTAG ドングルに接続し、その JTAG ドングルを TSWDC155EVM 上の JTAG ヘッダ J7 に接続します。その後、Micro USB ケーブルを PC に接続します。

5. TSWDC155EVM 上のジャンパ J2 がピン 1-2 間に装着され、USB-C コネクタ経由でボードに電源が供給される状態になっていることを確認してください

**Jumper J2

Connected across

Pins 1-2**

図 2-1. TSWDC155EVM ジャンパ J2

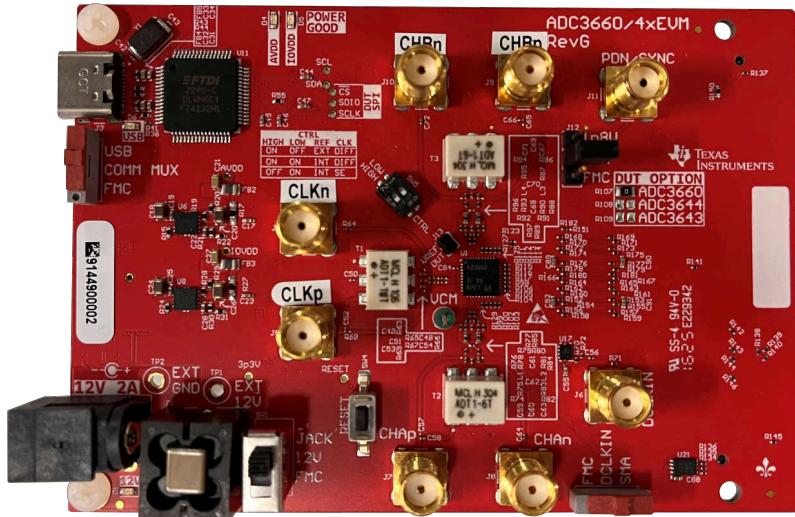

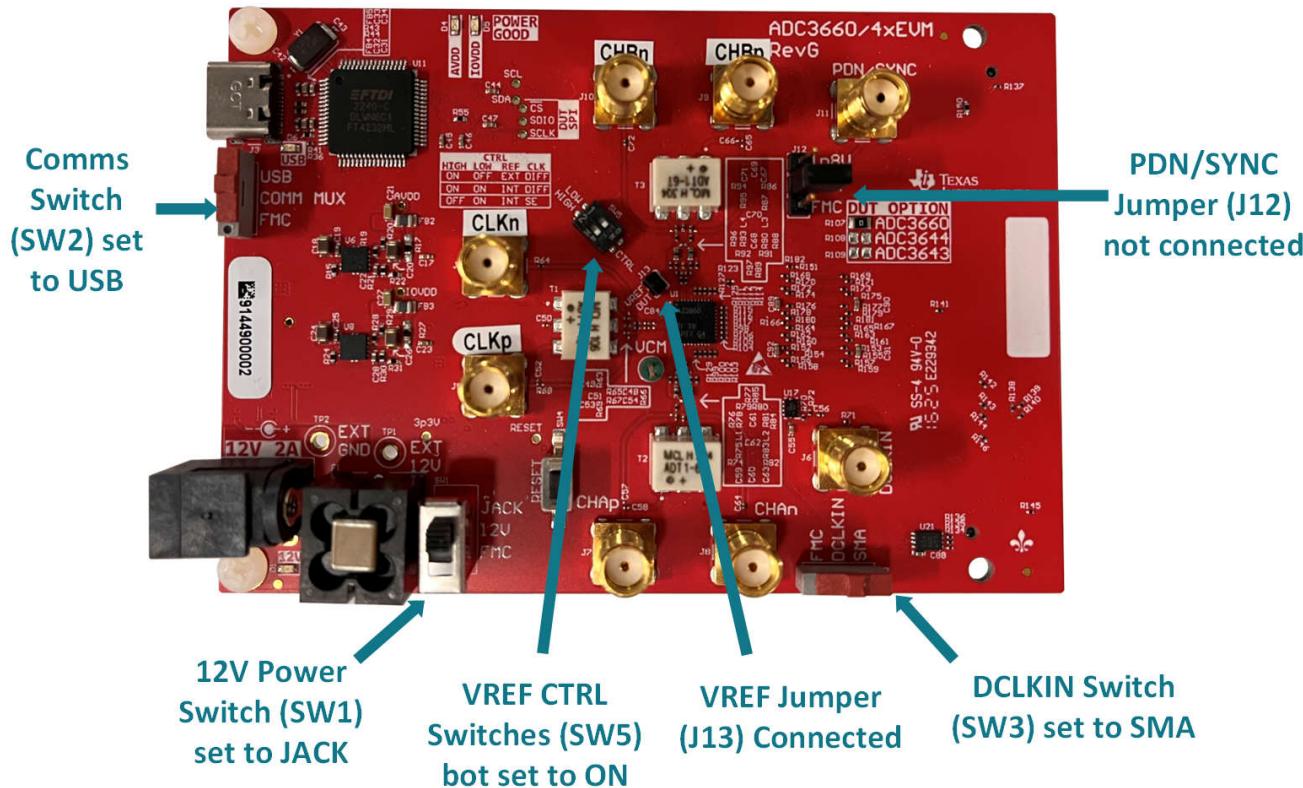

6. ADC3660/ADC364xEVM 上のスイッチおよびジャンパが、以下の設定になっていることを確認してください。

- 12V 電源スイッチ (SW1) がジャック側に切り替えられていること。

- 通信 Mux スイッチ (SW2) が USB 側に切り替えられていること。

- DCLKIN スイッチ (SW3) が SMA 側に切り替えられていること。

- VREF CTRL スイッチバンク (SW5) 上の両方のスイッチが「ON」に設定されていること。

- VREF ジャンパ (J13) が装着されていること。

- PDN/SYNC ジャンパ (J12) が接続されていないこと。

図 2-2. ADC3660/ADC364xEVM のスイッチおよびジャンパ設定

### 3 ソフトウェア

本セクションでは、ADC3660、ADC3644、および ADC3643 各バリアント評価基板を含む ADC3660/ADC364xEVM を効率的に使用するために必要なソフトウェア ツールおよびアプリケーションについて詳述します。

#### 3.1 必要なソフトウェア

ADC3660/ADC364xEVM を評価するために必要なソフトウェアは以下のとおりです。

- [ADC36xxEVM GUI](#)

- テキサス・インスツルメンツ [HSDC Pro](#) ソフトウェア

- [Vivado Lab](#) ソリューション

#### 3.2 ソフトウェアの設定

1. ADC36xxEVM GUI をダウンロードしてインストールします。

- a. ADC36xxEVM GUI をインストール中に、FX3 USB ドライバも併せてインストールされていることを確認してください。

2. HSDC Pro をダウンロードしてインストールします。キャプチャしたデータを表示するのに使用されます。

3. また、AMD のウェブサイトから Vivado Lab ソリューションをダウンロードしてインストールしてください。これは、FPGA からデータをキャプチャするために必要になります。

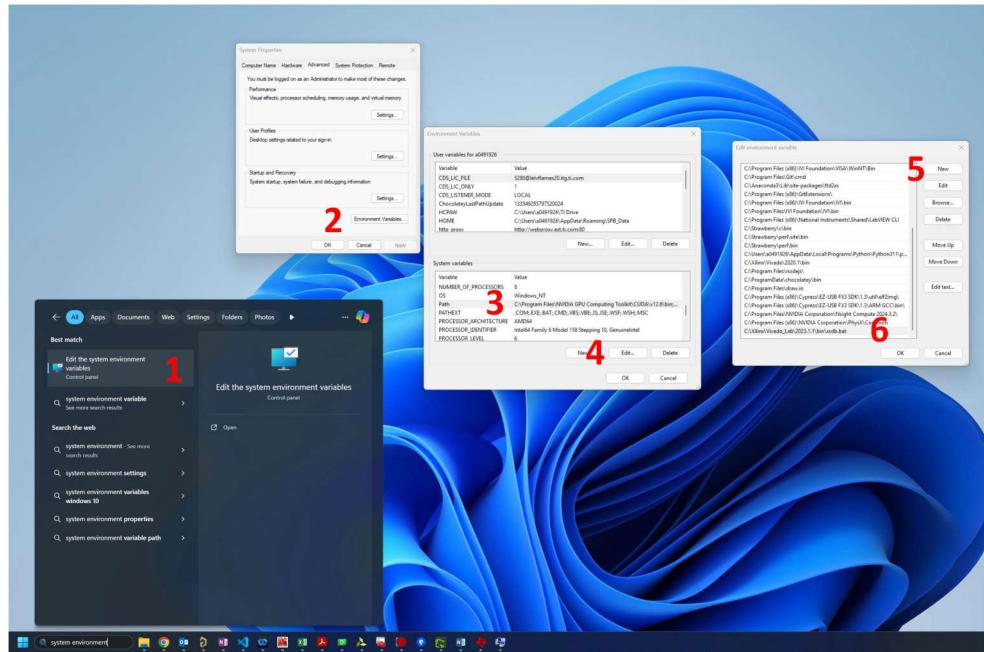

4. Vivado Lab の bin フォルダがシステム環境変数 PATH に追加されていることを確認してください。

- a. スタートメニューで「システム環境変数の編集」を検索します

- b. 「Environment Variables...」(環境変数...) を選択します

- c. 「System variables」(システム環境変数)の一覧から「Path」(パス) 変数を探して選択します

- d. 「Edit...」(編集...) を選択します

- e. 「New」(新規) をクリックして、新しいパスを追加します

- f. インストール先およびバージョンに応じて、Vivado Lab のインストール ディレクトリのパスを追加します。bin フォルダへのパスは通常、次のようにになります。C:\Xilinx\Vivado\_Lab\2023.1\bin

図 3-1. 環境変数の設定

## 4 セットアップ手順

以下のセットアップ手順では、ADC3660/ADC364xEVM の 3 種類すべてのバリエントを評価するために必要なハードウェアおよびソフトウェアのセットアップ方法と使用手順について詳しく説明します。

### 4.1 ADC3660EVM のセットアップ

1. ソフトウェアが「ソフトウェア セットアップ」セクションに従って正しく設定されていることを確認してください。

2. ハードウェアが「ハードウェア セットアップ」セクションに従って正しく構成されていることを確認してください。

3. CLK 信号を供給するには、以下の手順を実施します。

- a. SMA ケーブルおよびインライン 65MHz バンドパス フィルタを使用して、信号発生器を ADC3660EVM 上の CLKp SMA コネクタ (J5) に接続します。

- b. 信号ジェネレータの出力信号周波数を 65MHz に、信号振幅を +10dBm に設定します

4. EVM はデフォルトでシングルエンド入力に対応しているため、アナログ入力はチャンネル A 用の CHAp コネクタ (J7) またはチャンネル B 用の CHBp コネクタ (J9) に入力してください。アナログ入力を供給するには、以下の手順を実施します。

- a. SMA ケーブルおよびインライン 5MHz バンドパス フィルタを使用して、信号発生器をアナログ入力チャンネル A に接続します。

- b. 信号発生器の出力信号周波数を 5.135MHz (素数) に、出力レベルを 0dBm に設定します。

5. DCLK 信号を供給するには、次の手順を実施します。

- a. SMA ケーブルを使用して、信号発生器を DCLKIN SMA コネクタ (J6) に接続します。

- b. 信号発生器の出力周波数を 260MHz (16 ビット、2 ワイヤ、DDC バイパス) に設定し、信号振幅を +2dBm に設定します。

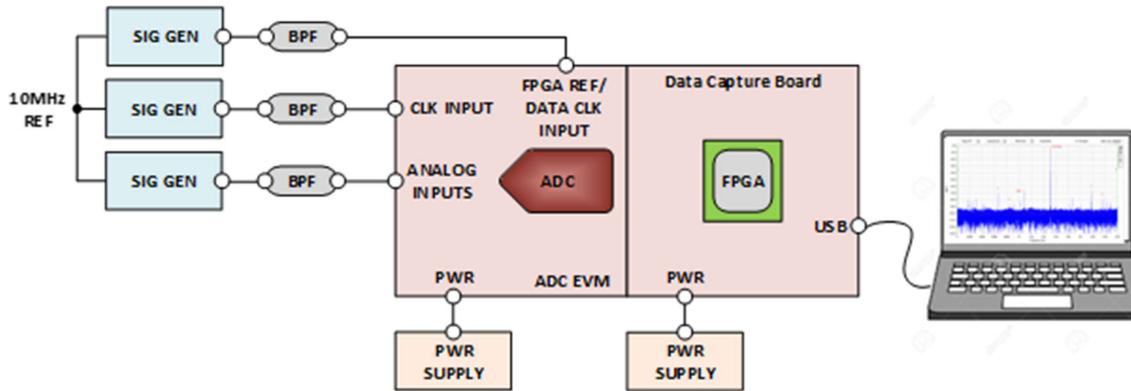

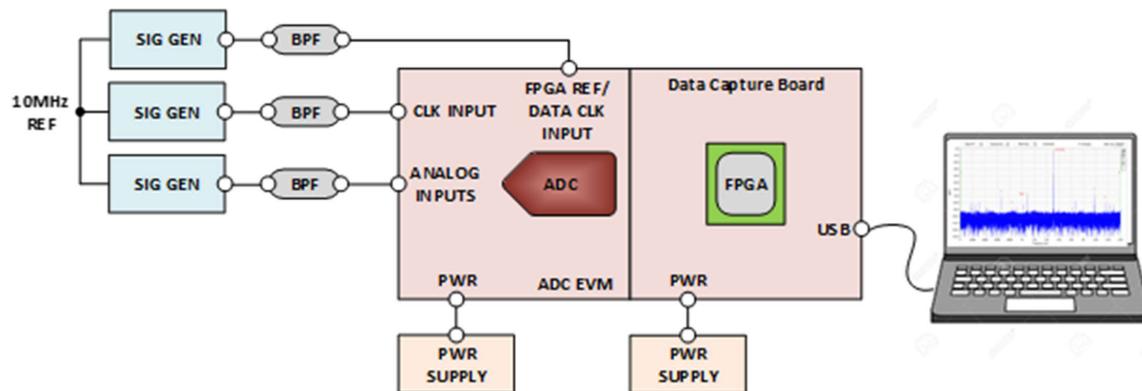

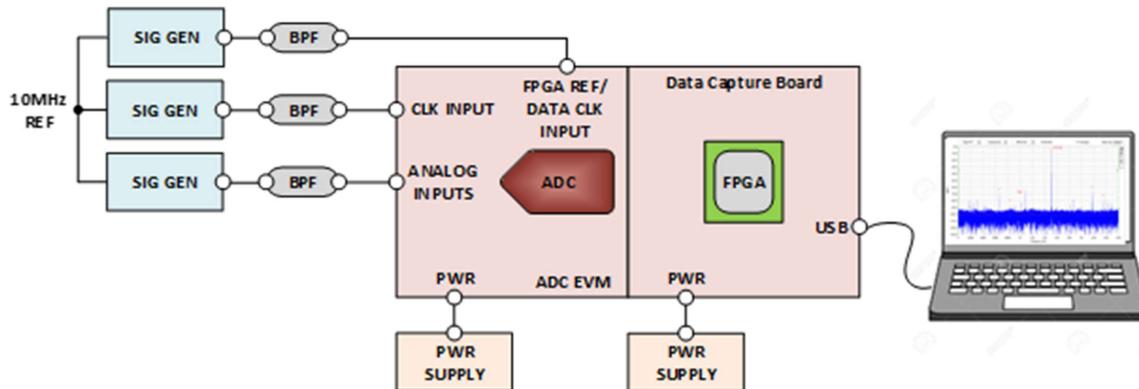

6. クロック、アナログ入力、および DCLK 用のすべての信号発生器が、背面の 10MHz リファレンス出力を使用してリファレンス ロックされていることを確認してください。この例については、下図を参照してください。

図 4-1. 基本テスト測定セットアップ

セットアップ手順

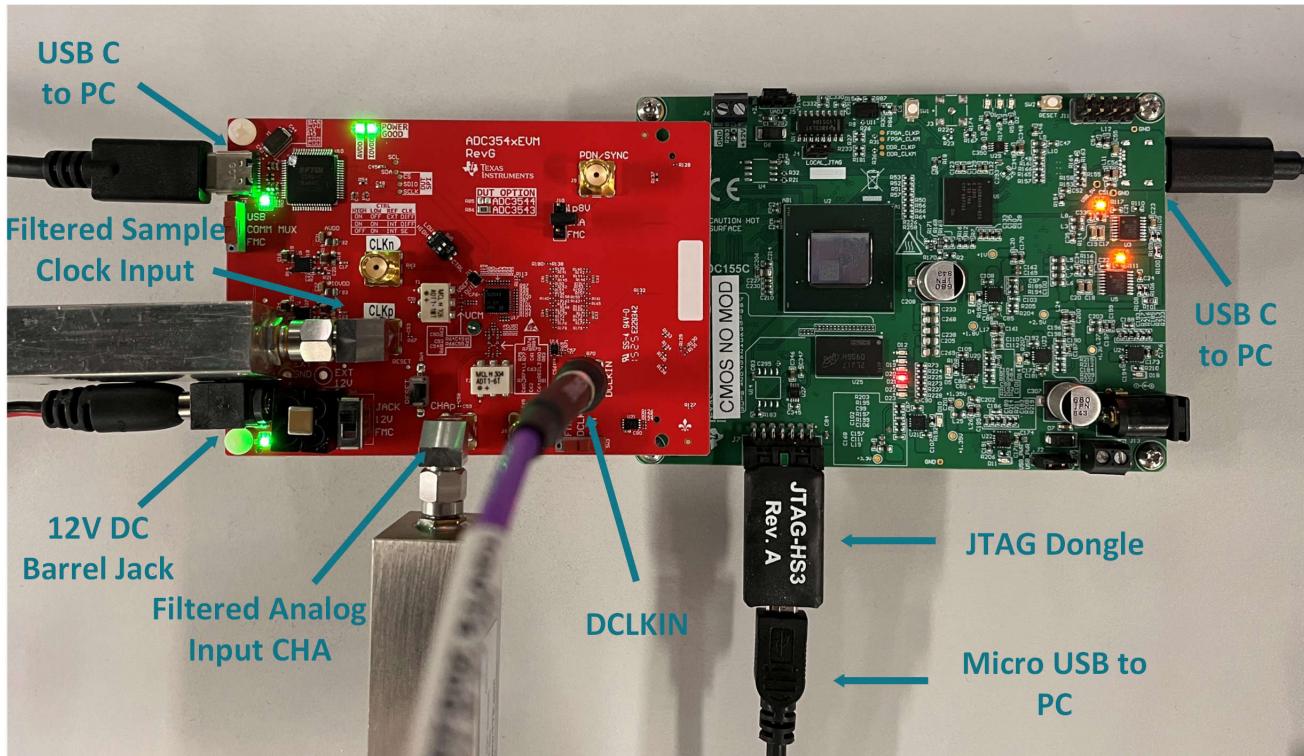

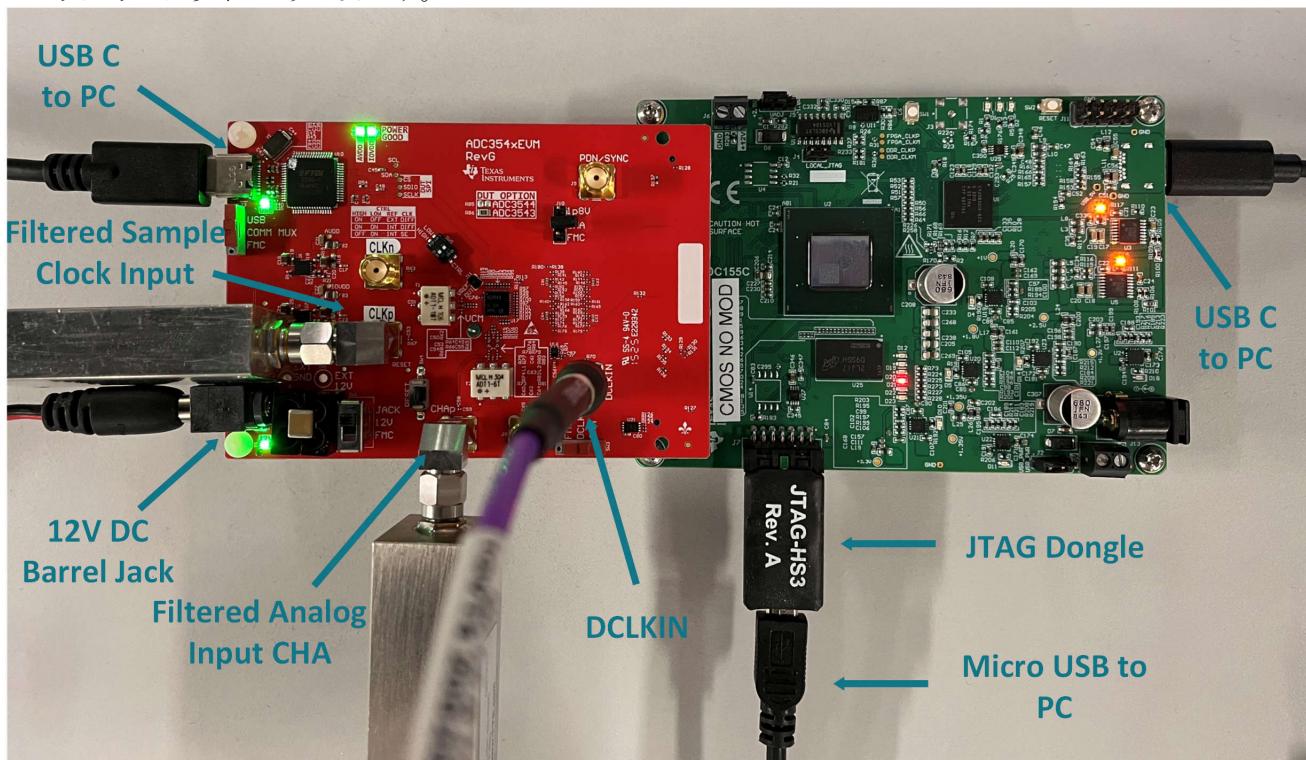

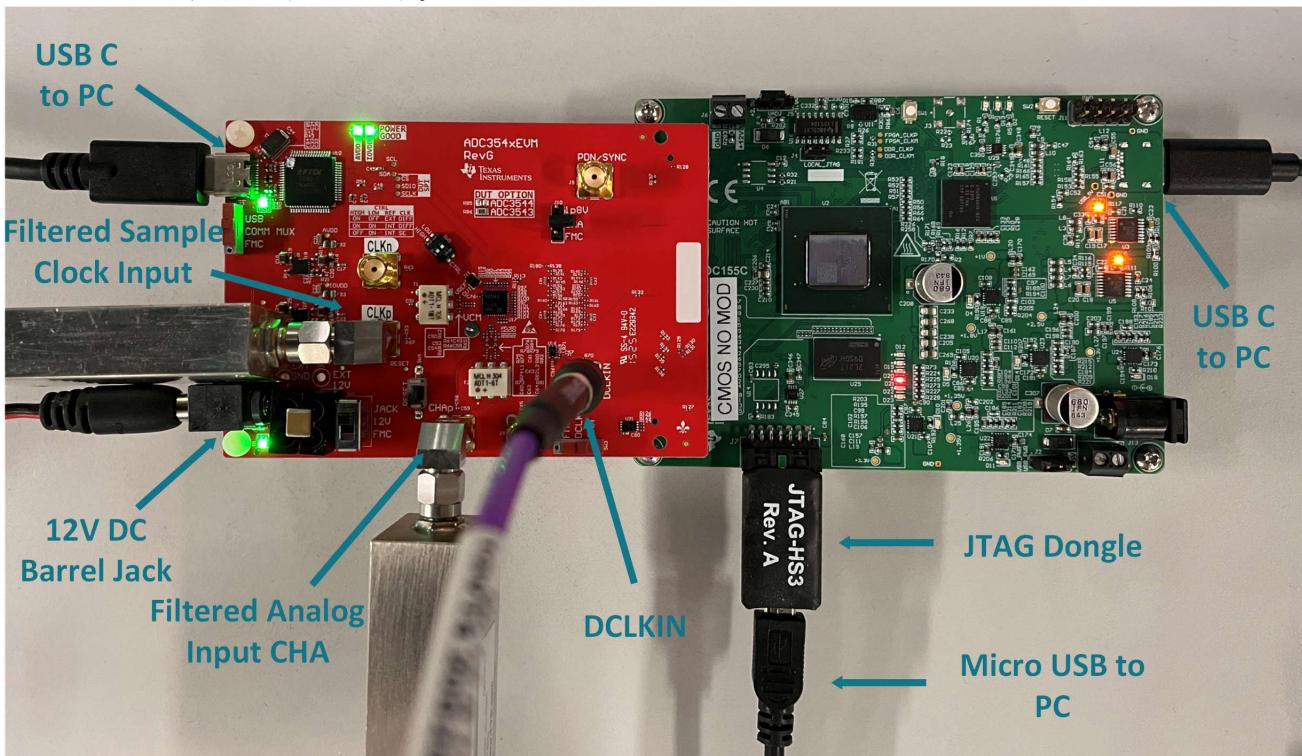

7. セットアップは以下のようになります。

図 4-2. ADC3660EVM のハードウェア設定

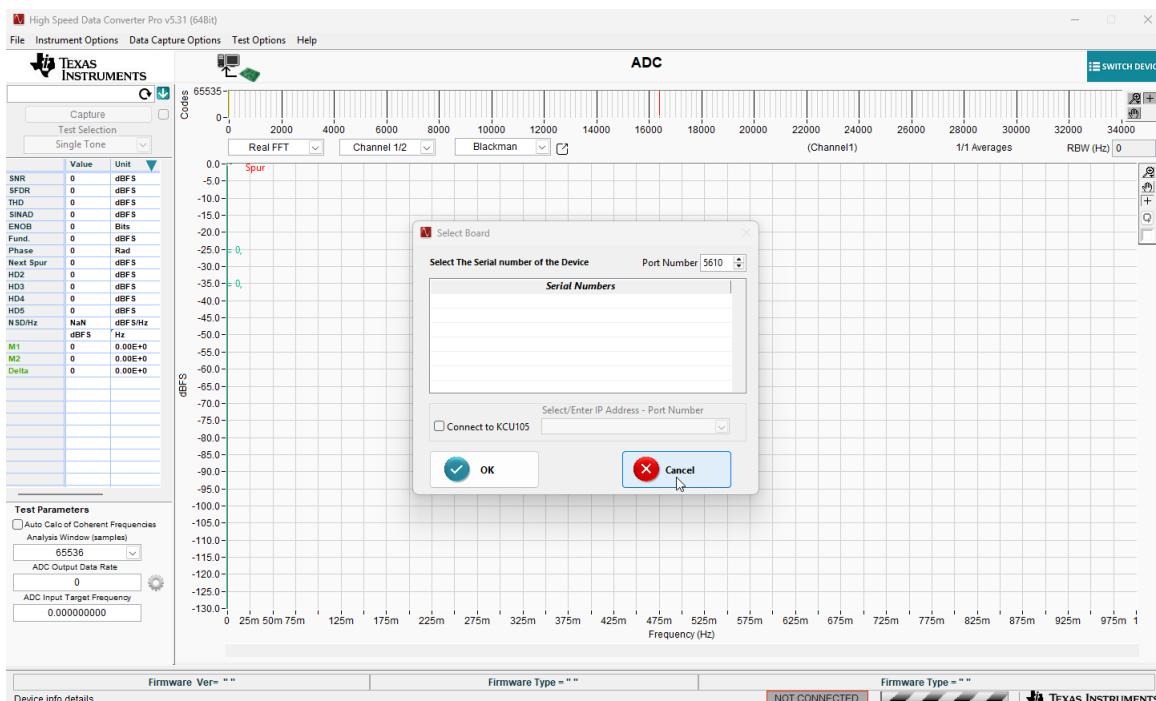

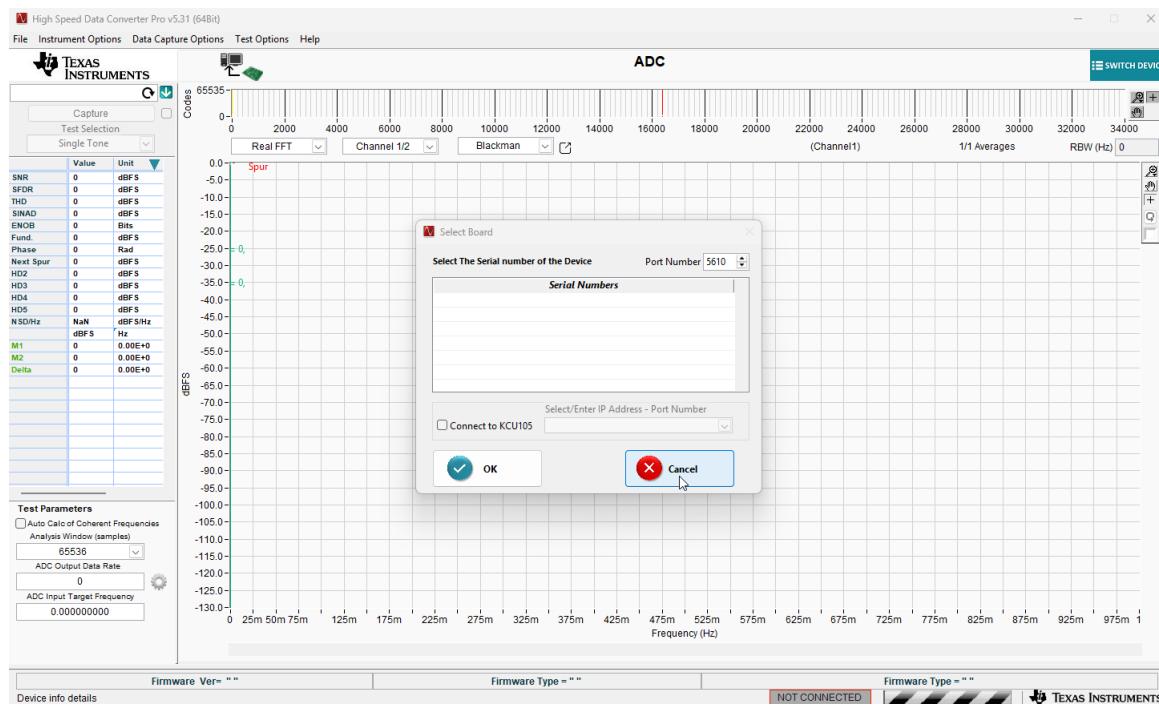

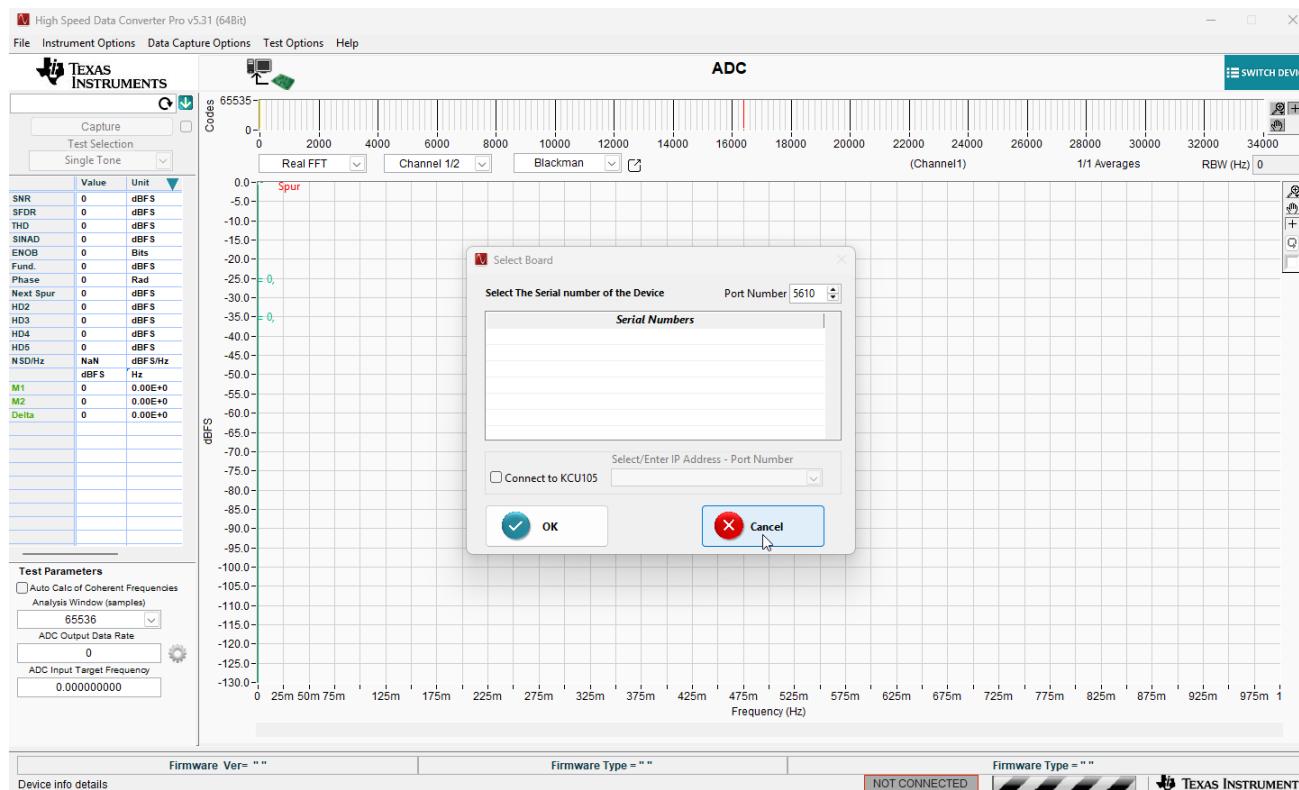

8. HSDC Pro を起動します。ADC36xxEVM GUI を開く前に、必ず HSDC Pro が起動していることを確認してください。

9. ボードへの接続を求めるメッセージが表示された場合は、「cancel」(キャンセル) を選択します。GUI は、その他の HSDC Pro に関するキャプチャおよび設定操作をすべて自動で処理します。

図 4-3. HSDC Pro

10. ADC36xxEVM GUI を起動します。GUI が TSWDC155EVM FPGA キャプチャボードに接続するまで、数秒待機してください。接続が確立されると TSWDC155EVM の電源が入り、下図のように複数の LED が点灯するようになります。

図 4-4. TSWDC155EVM の電源がオンになった状態

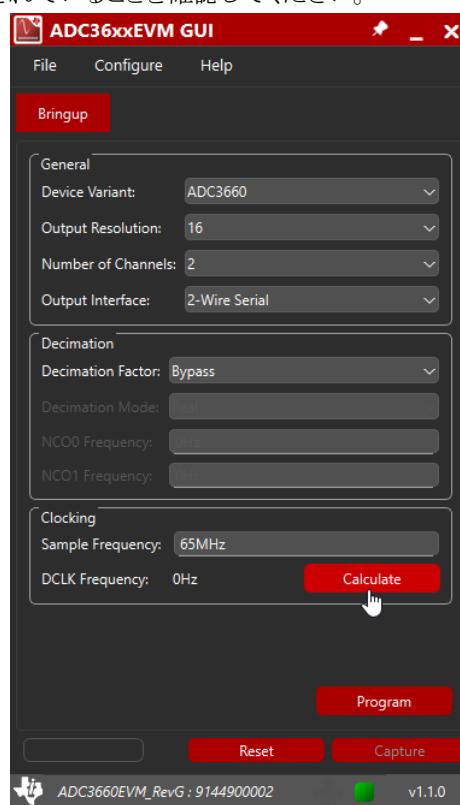

11. GUI を開いたら、ADC モード オプションが正しいことを確認し、「Calculate」(計算) ボタンをクリックして必要な DCLK を計算します。このモードでは、DCLK は 260MHz である必要があります。この信号がハードウェア セットアップ上の DCLK 入力 に正しく供給されていることを確認してください。

図 4-5. ADC3660 用 DCLK 周波数の計算

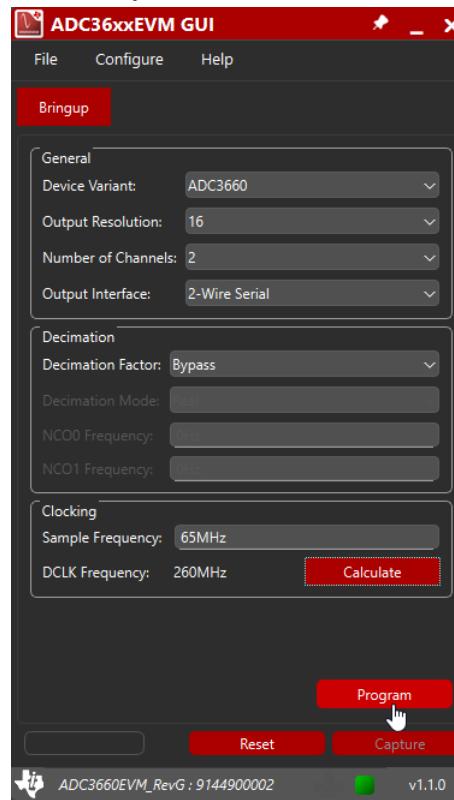

12. 「Program」(プログラム) ボタンを選択します。ADC のプログラム、FPGA のプログラム、および FPGA フームウェアの構成が完了するまで、数秒待機してください。

図 4-6. ADC3660EVM のプログラミング

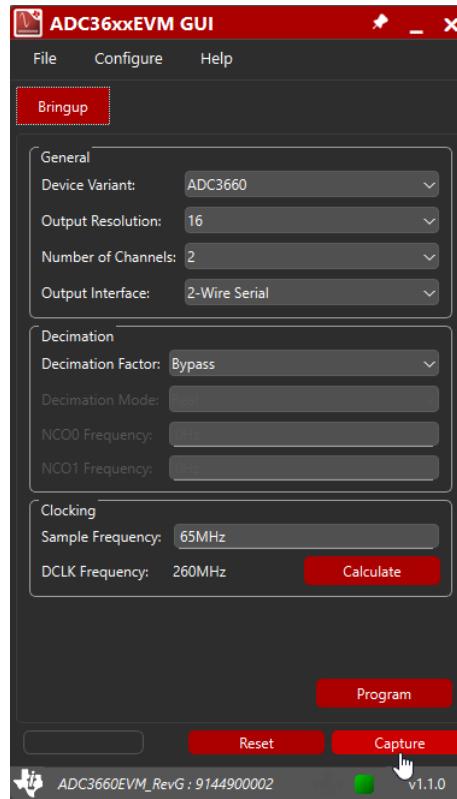

13. プログラミングが完了したら、「Capture」(キャプチャ) ボタンを選択して FFT データキャプチャを実行します。

図 4-7. FFT のキャプチャ

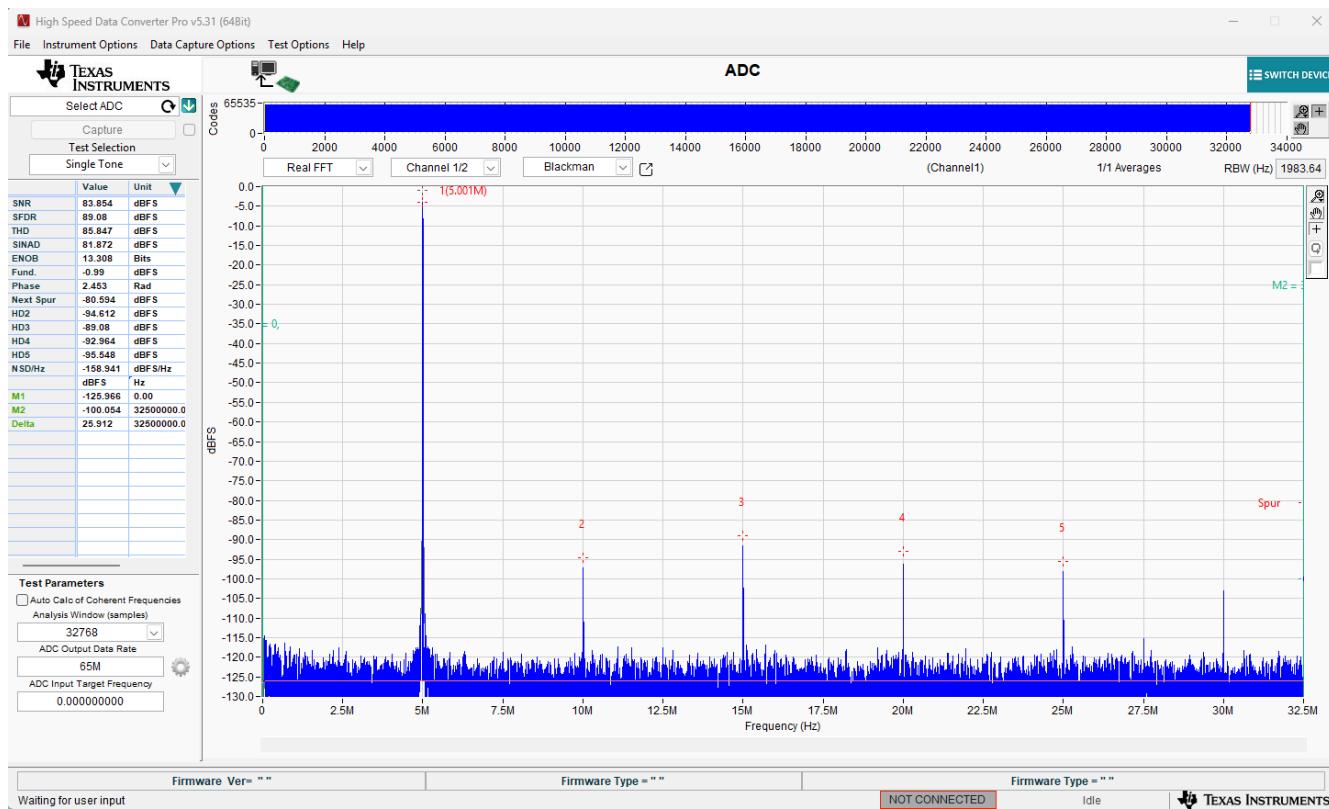

14. 数秒後、キャプチャされたデータが HSDC Pro ウィンドウに表示され、デバイスの性能を確認できます。HSDC Pro のその他の機能や詳細については、HSDC Pro ユーザー ガイドを参照してください。

図 4-8. HSDC Pro における ADC3660EVM の FFT データキャプチャ

15. キャプチャ機能の実行中にエラーが発生した場合は、GUI を再起動し、手順 5~8 を再度実施してください。

## 4.2 ADC3644EVM のセットアップ

1. ソフトウェアが「ソフトウェア セットアップ」セクションに従って正しく設定されていることを確認してください。

2. ハードウェアが「ハードウェア セットアップ」セクションに従って正しく構成されていることを確認してください。

3. CLK 信号を供給するには、以下の手順を実施します。

- a. SMA ケーブルおよびインライン 125MHz バンドパス フィルタを使用して、信号発生器を ADC3644EVM 上の CLKp SMA コネクタ (J5) に接続します。

- b. 信号ジェネレータの出力信号周波数を 125MHz に、信号振幅を +10dBm に設定します

4. EVM はデフォルトでシングルエンド入力に対応するよう構成されているため、アナログ入力はチャンネル A 用の CHAp コネクタ (J7) またはチャンネル B 用の CHBp コネクタ (J9) に入力してください。アナログ入力を供給するには、以下の手順を実施します。

- a. SMA ケーブルおよびインライン 5MHz バンドパス フィルタを使用して、信号発生器をアナログ入力チャンネル A に接続します。

- b. 信号発生器の出力信号周波数を 5.135MHz (素数) に、出力レベルを 0dBm に設定します。

5. DCLK 信号を供給するには、次の手順を実施します。

- a. SMA ケーブルを使用して、信号発生器を DCLKIN SMA コネクタ (J6) に接続します。

- b. 信号発生器の出力周波数を 227.5MHz (14 ビット、2 ワイヤ、DDC バイパス) に設定し、信号振幅を +2dBm に設定します。

6. クロック、アナログ入力、および DCLK 用のすべての信号発生器が、背面の 10MHz リファレンス出力を使用してリフアレンス ロックされていることを確認してください。この例については、下図を参照してください。

図 4-9. 基本テスト測定セットアップ

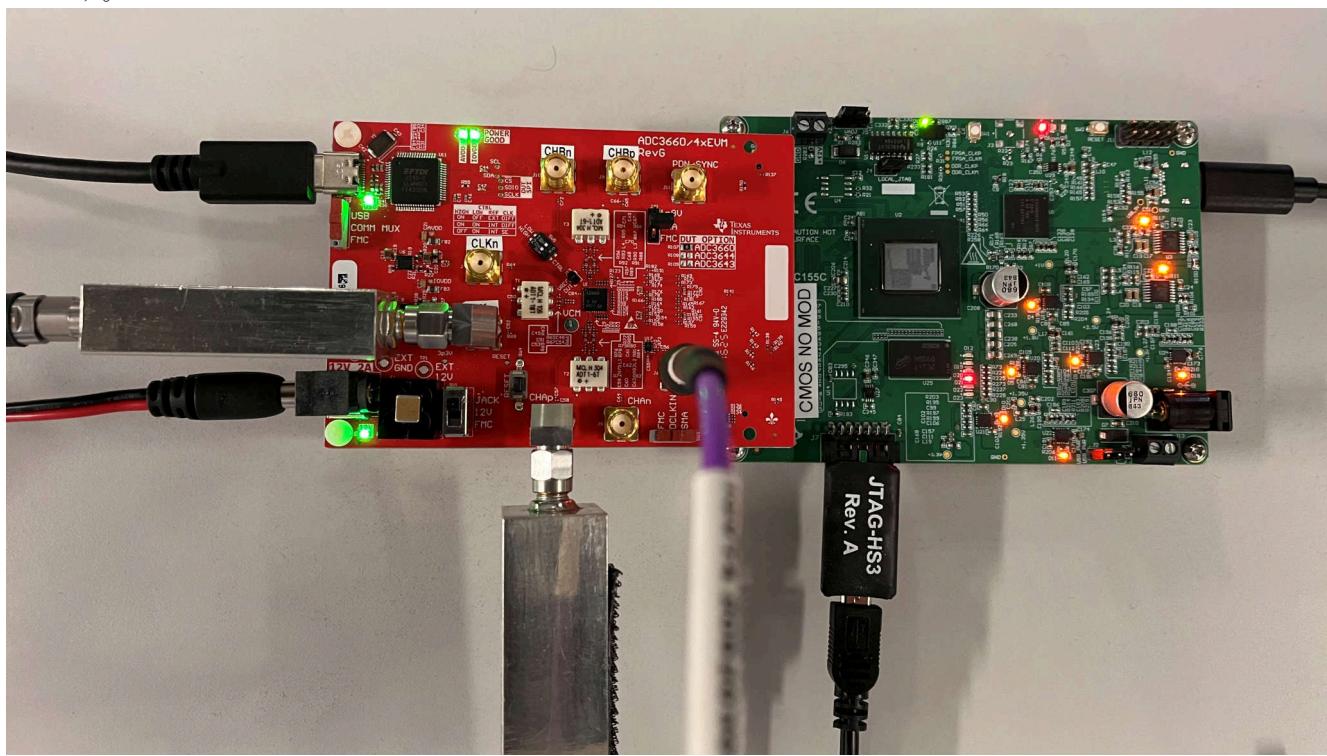

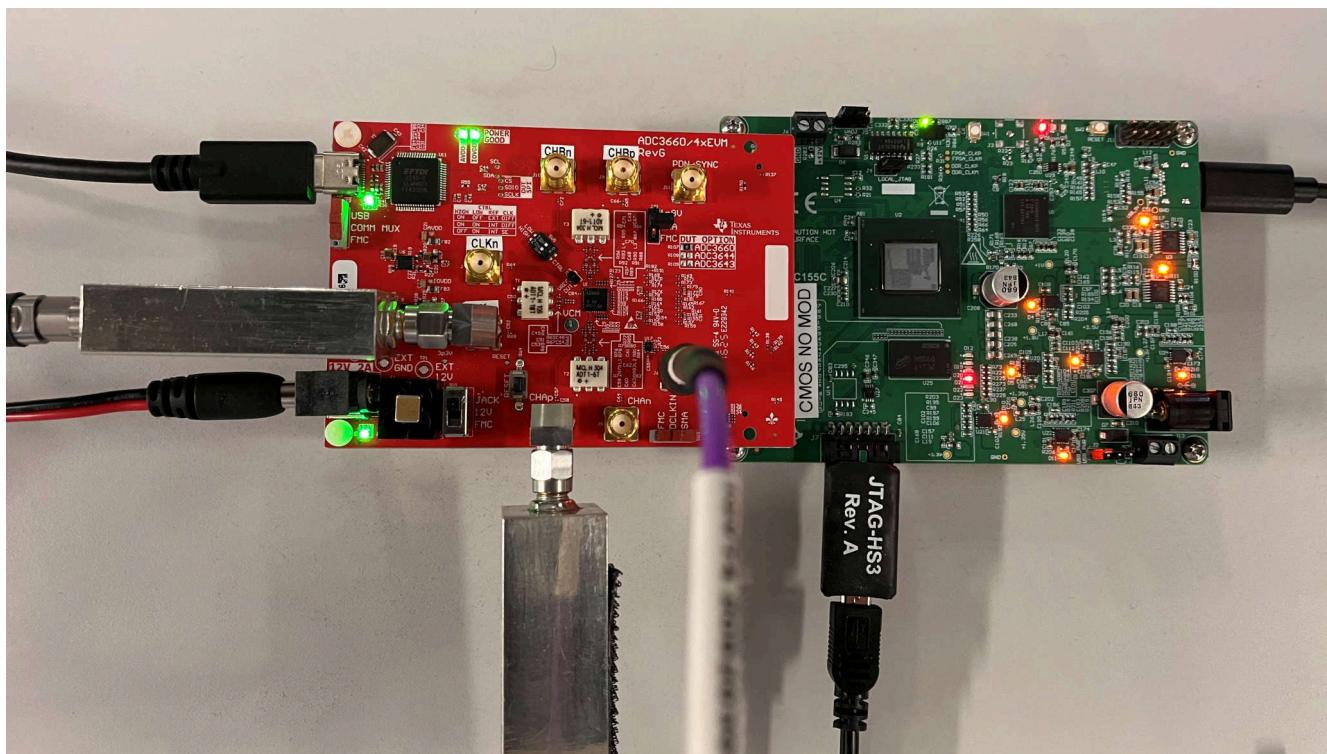

7. セットアップは以下のようになります。

図 4-10. ADC3644EVM のハードウェア設定

8. HSDC Pro を起動します。ADC36xxEVM GUI を開く前に、必ず HSDC Pro が起動していることを確認してください。

9. ボードへの接続を求めるメッセージが表示された場合は、「cancel」(キャンセル)を選択します。GUI は、その他の HSDC Pro に関するキャプチャおよび設定操作をすべて自動で処理します。

図 4-11. HSDC Pro

10. ADC36xxEVM GUI を起動します。GUI が TSWDC155EVM FPGA キャプチャボードに接続するまで、数秒待機してください。接続が確立されると TSWDC155EVM の電源が入り、下図のように複数の LED が点灯します。

図 4-12. TSWDC155EVM の電源がオンになった状態

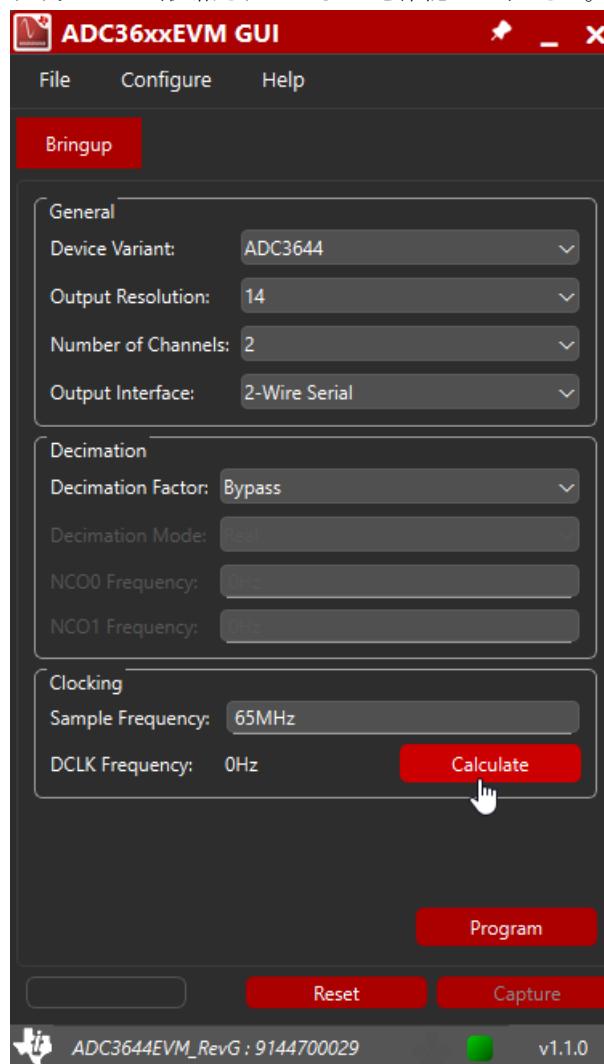

11. GUI を開いたら、正しい ADC モード パラメータが選択されていることを確認し、「Calculate」(計算) ボタンをクリックして必要な DCLK を計算します。このモードでは、DCLK は 437.5MHz である必要があります。この信号がハードウェア セットアップ上の DCLK 入力に正しく供給されていることを確認してください。

図 4-13. ADC3644 用 DCLK 周波数の計算

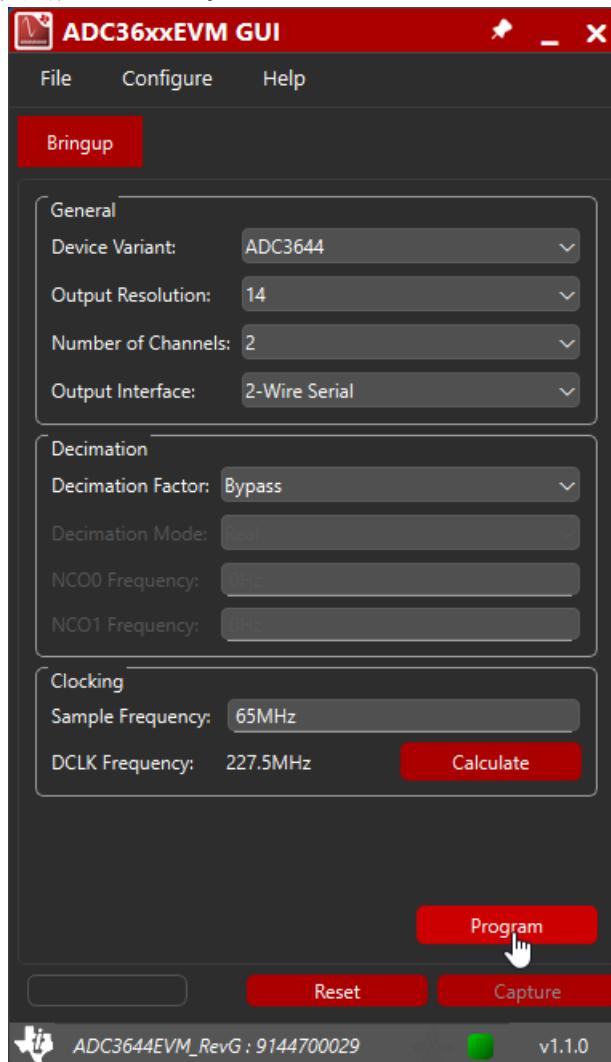

12. 「Program」(プログラム) ボタンを選択します。ADC のプログラム、FPGA のプログラム、および FPGA フームウェアの構成が完了するまで、数秒待機してください。

図 4-14. ADC3644EVM のプログラミング

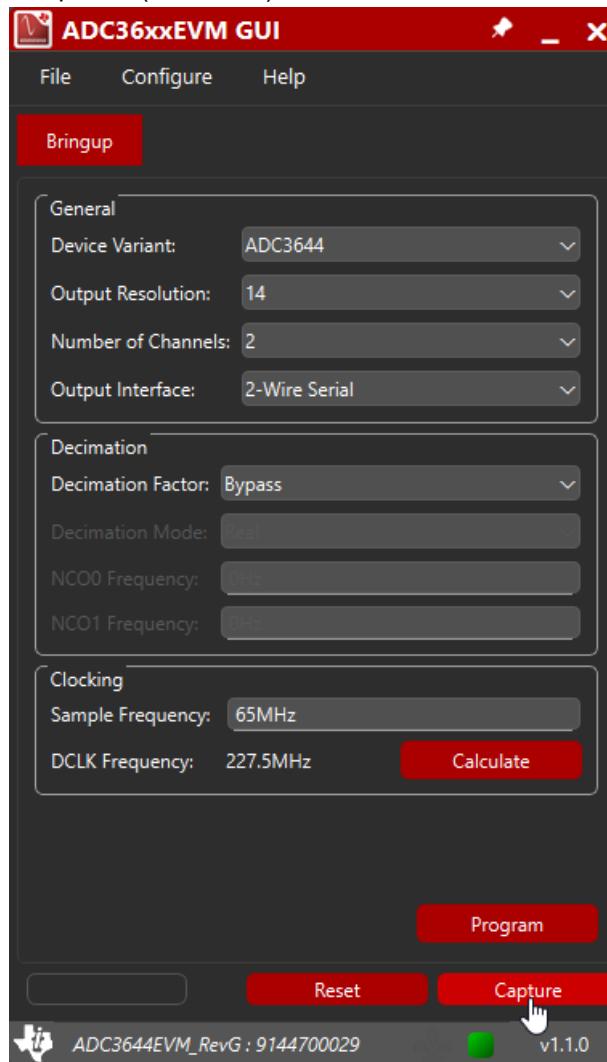

13. プログラミングが完了したら、「Capture」(キャプチャ) ボタンを選択して FFT データキャプチャを実行します。

図 4-15. FFT のキャプチャ

**セットアップ手順**

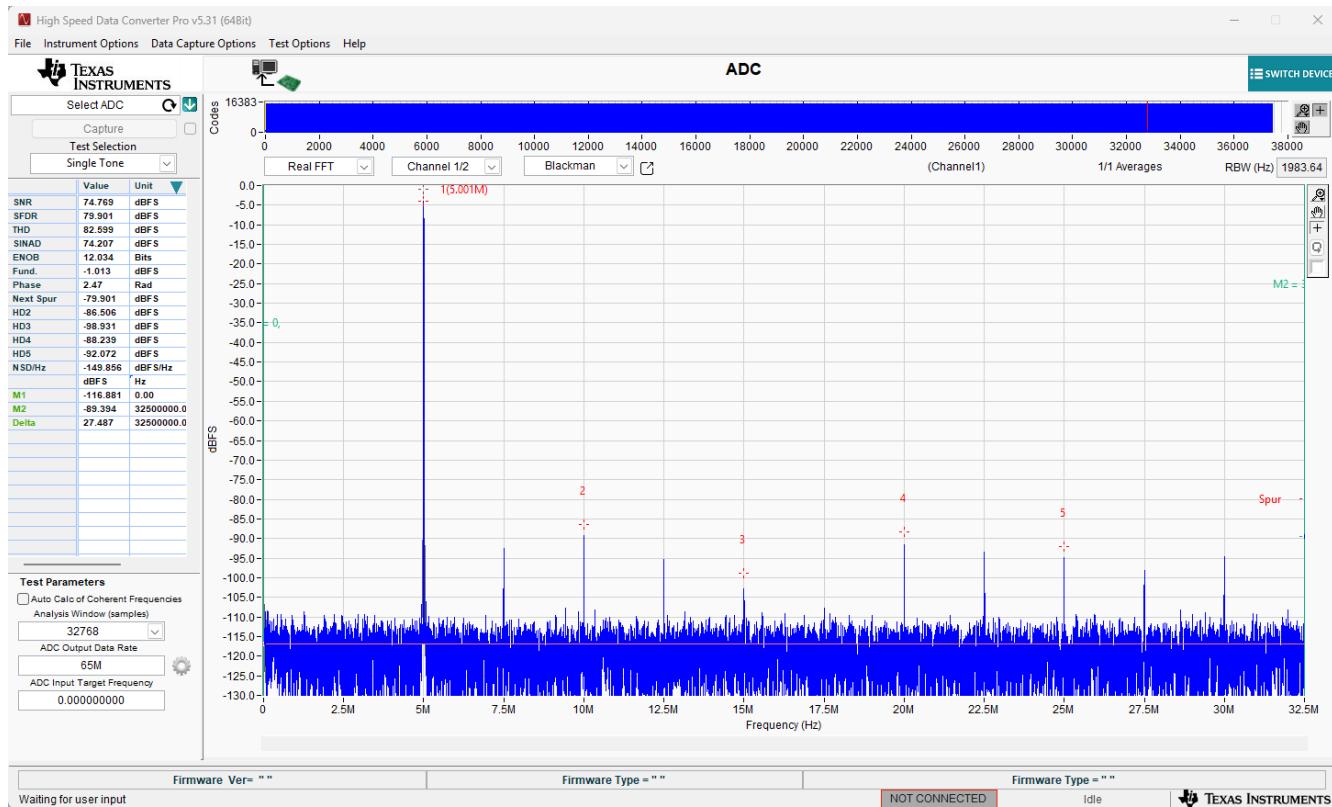

14. 数秒後、キャプチャされたデータが HSDC Pro ウィンドウに表示され、デバイスの性能を確認できます。HSDC Pro のその他の機能や詳細については、HSDC Pro ユーザー ガイドを参照してください。

**図 4-16. HSDC Pro における ADC3644EVM の FFT データキャプチャ**

15. キャプチャ機能の実行中にエラーが発生した場合は、GUI を再起動し、手順 5~8 を再度実施してください。

### 4.3 ADC3643EVM のセットアップ

1. ソフトウェアが「ソフトウェア セットアップ」セクションに従って正しく設定されていることを確認してください。

2. ハードウェアが「ハードウェア セットアップ」セクションに従って正しく構成されていることを確認してください。

3. CLK 信号を供給するには、以下の手順を実施します。

- a. SMA ケーブルおよびインライン 65MHz バンドパス フィルタを使用して、信号発生器を ADC3643EVM 上の CLKp SMA コネクタ (J5) に接続します。

- b. 信号ジェネレータの出力信号周波数を 65MHz に、信号振幅を +10dBm に設定します。

4. EVM はデフォルトでシングルエンド入力に対応するよう構成されているため、アナログ入力はチャンネル A 用の CHAp コネクタ (J7) またはチャンネル B 用の CHBp コネクタ (J9) に入力してください。アナログ入力を供給するには、以下の手順を実施します。

- a. SMA ケーブルおよびインライン 5MHz バンドパス フィルタを使用して、信号発生器をアナログ入力チャンネル A に接続します。

- b. 信号発生器の出力信号周波数を 5.135MHz (素数) に、出力レベルを 0dBm に設定します。

5. DCLK 信号を供給するには、次の手順を実施します。

- a. SMA ケーブルを使用して、信号発生器を DCLKIN SMA コネクタ (J6) に接続します。

- b. 信号発生器の出力周波数を 227.5MHz (14 ビット、2 ワイヤ、DDC バイパス) に設定し、信号振幅を +2dBm に設定します。

6. クロック、アナログ入力、および DCLK 用のすべての信号発生器が、背面の 10MHz リファレンス出力を使用してリファレンス ロックされていることを確認してください。この例については、下図を参照してください。

図 4-17. 基本テスト測定セットアップ

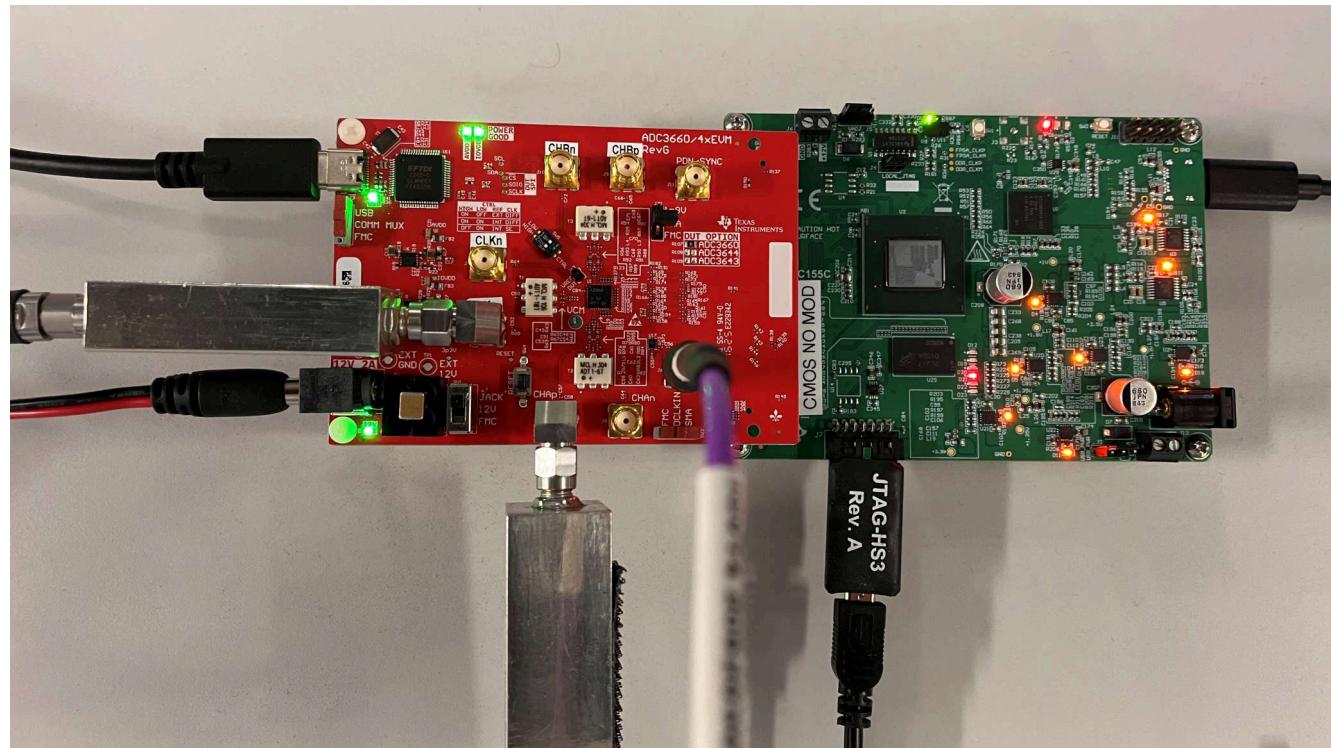

7. セットアップは以下のようになります。

図 4-18. ADC3643EVM のハードウェア設定

8. HSDC Pro を起動します。ADC36xxEVM GUI を開く前に、必ず HSDC Pro が起動していることを確認してください。

**セットアップ手順**

9. ボードへの接続を求めるメッセージが表示された場合は、「cancel」(キャンセル)を選択します。GUI は、その他の HSDC Pro に関するキャプチャおよび設定操作をすべて自動で処理します。

図 4-19. HSDC Pro

10. ADC36xxEVM GUI を起動します。GUI が TSWDC155EVM FPGA キャプチャボードに接続するまで、数秒待機してください。接続が確立されると TSWDC155EVM の電源が入り、下図のように複数の LED が点灯するようになります。

図 4-20. TSWDC155EVM の電源がオンになった状態

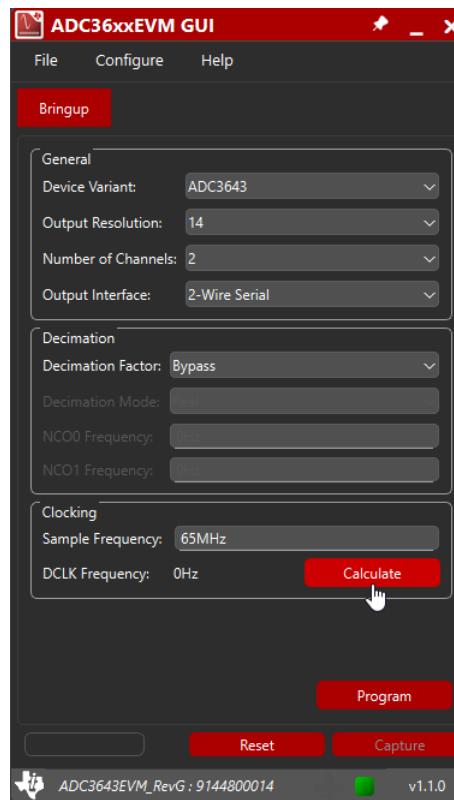

11. GUI を開いたら、正しい ADC モード パラメータが選択されていることを確認し、「Calculate」(計算) ボタンをクリックして必要な DCLK を計算します。このモードでは、DCLK は 227.5MHz である必要があります。この信号がハードウェア セットアップ上の DCLK 入力に正しく供給されていることを確認してください。

図 4-21. ADC3643 用 DCLK 周波数の計算

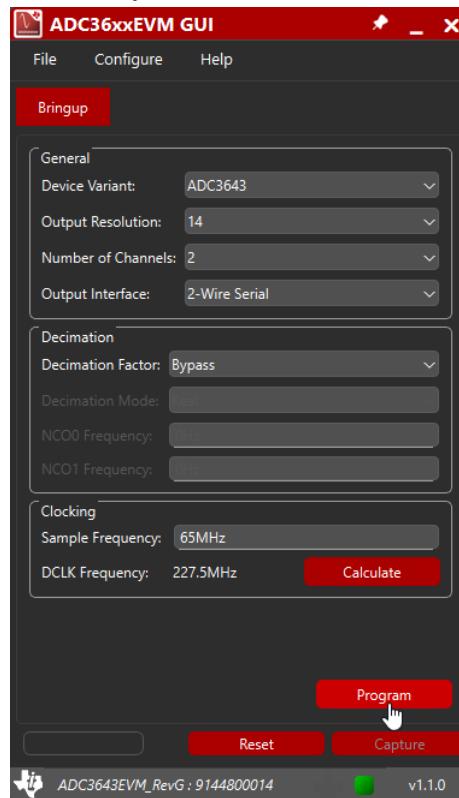

12. 「Program」(プログラム) ボタンを選択します。ADC のプログラム、FPGA のプログラム、および FPGA フームウェアの構成が完了するまで、数秒待機してください。

図 4-22. ADC3643EVM のプログラミング

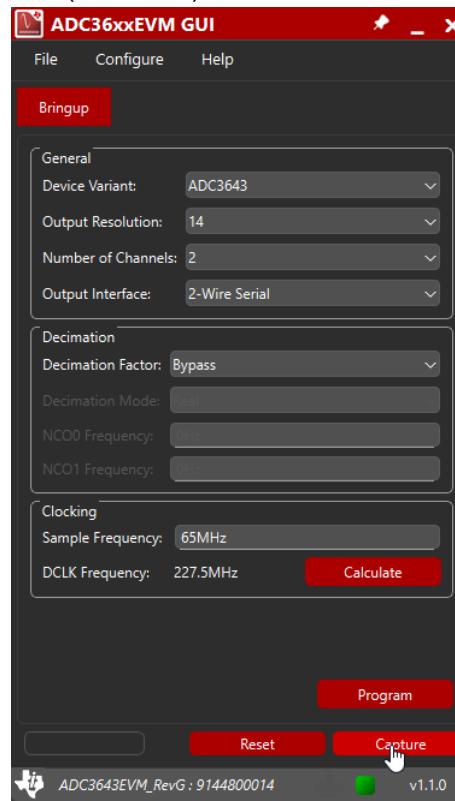

13. プログラミングが完了したら、「Capture」(キャプチャ) ボタンを選択して FFT データキャプチャを実行します。

図 4-23. FFT のキャプチャ

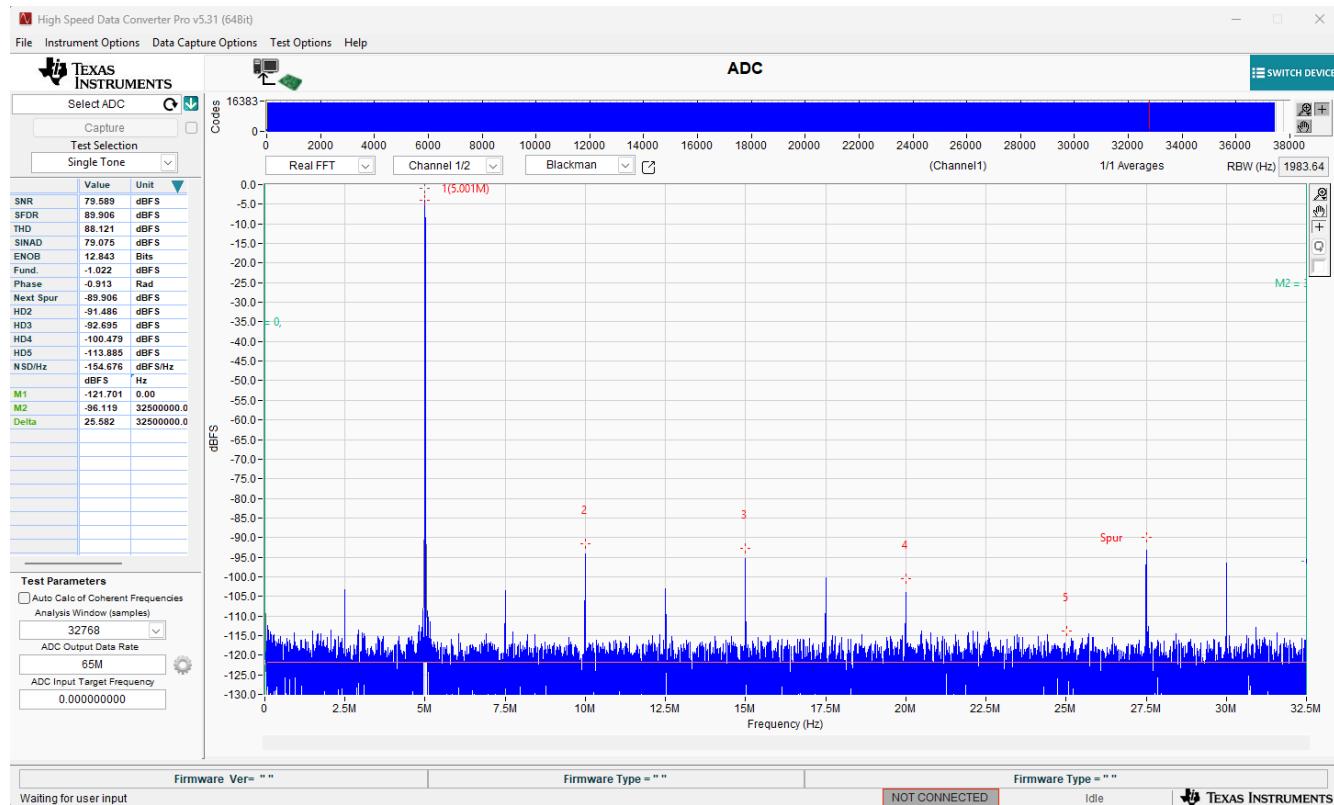

14. 数秒後、キャプチャされたデータが HSDC Pro ウィンドウに表示され、デバイスの性能を確認できます。HSDC Pro のその他の機能や詳細については、HSDC Pro ユーザー ガイドを参照してください。

図 4-24. HSDC Pro における ADC3643EVM の FFT データキャプチャ

15. キャプチャ機能の実行中にエラーが発生した場合は、GUI を再起動し、手順 5~8 を再度実施してください。

## 5 ハードウェア設計ファイル

以下の設計ファイル (回路図、PCB レイアウト、および部品表 (BOM)) は、製品ページで入手可能です。

[ADC3660EVM](#)、[ADC3644EVM](#)、および [ADC3643EVM](#)。

## 6 追加情報

### 6.1 商標

Microsoft® and Windows® are registered trademarks of Microsoft Corporation.

すべての商標は、それぞれの所有者に帰属します。

## 7 参考資料

- テキサス・インスツルメンツ、[ADC3660EVM](#) 製品ページ

- テキサス・インスツルメンツ、[ADC3644EVM](#) 製品ページ

- テキサス・インスツルメンツ、[ADC3643EVM](#) 製品ページ

- テキサス・インスツルメンツ、[TSWDC155](#) 評価基板、ユーザーズ ガイド

- テキサス・インスツルメンツ、[High-Speed Data Converter Pro GUI](#)、ユーザーガイド

- テキサス・インスツルメンツ、[ADC3660](#) 16 ビット、0.5MSPS ~ 65MSPS、低ノイズ、低消費電力、デュアル チャネル ADC、データシート

- テキサス・インスツルメンツ、[ADC3644](#) 14 ビット、125MSPS、低ノイズ、低消費電力、デュアル チャネル ADC、データシート

- テキサス・インスツルメンツ、[ADC364x](#) 14 ビット、10MSPS ~ 65MSPS、低ノイズ、低消費電力、デュアル チャネル ADC、データシート

## 8 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| Changes from Revision * (October 2020) to Revision A (November 2025) | Page |

|----------------------------------------------------------------------|------|

| • 最新の評価基板ユーザー ガイド テンプレートに合わせてドキュメントのフォーマットを更新。.....                  | 1    |

| • ドキュメント全体にわたって表、図、相互参照の採番方法を更新。.....                                | 1    |

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月