## Design Guide: TIDA-010970

# 低ノイズ、非常に線形性の高いアナログ フロントエンド リファレンス デザイン

## 説明

このリファレンス デザインのターゲット アプリケーションには、DC 信号の測定に超高精度を必要とするデジタル マルチメータ (DMM) が含まれます。このリファレンス デザインは、有効直線性を備えた高性能 24 ビット A/D コンバータ (ADC) である ADS127L21B を使用して、効果的な DC 精度を実現します。超低ドリフトの埋め込みツェナーリファレンスである REF81 は、シグナル チェーンのキャリブレーションを実施し、ゲイン誤差とオフセット誤差を除去します。

## リソース

|                     |            |

|---------------------|------------|

| TIDA-010970         | デザイン フォルダ  |

| ADS127L21B、REF81    | プロダクト フォルダ |

| REF54、RES21A、RES11A | プロダクト フォルダ |

| THP210、OPA828       | プロダクト フォルダ |

| MUX36S08、TMUX6104   | プロダクト フォルダ |

## 特長

- シグナル チェーン全体のキャリブレーションに適した超低ドリフト、低ノイズのリファレンスで、キャリブレーション後に高い DC 精度を実現

- 3 つの入力範囲:  $\pm 100\text{mV}$ 、 $\pm 1\text{V}$ 、 $\pm 10\text{V}$

- 直線性: 最大 1.1ppm ( $\pm 10\text{V}$  の範囲)

- ノイズ: 60SPS で  $335\text{nV}_{\text{RMS}}$  ( $\pm 10\text{V}$  の範囲)

## アプリケーション

- デジタル マルチメータ (DMM)

- 高精度マルチファンクション入出力 DAQ

- 電力アナライザ

- ソース メジャー ユニット (SMU)

## 1 システムの説明

このリファレンス デザインは、デジタル マルチメータ (DMM)、データ アクイジション (DAQ)、ソース メジャー ユニット (SMU)、その他の高精度試験および測定アプリケーションなど、高精度電圧測定を行うシステムに適した、リニア、低ノイズのシグナル チェーンです。このドキュメントでは、DMM アプリケーションに焦点を当てます。

DMM は、信号を正確に測定するために、高い直線性と低ノイズを必要とします。一貫した分解能で信号レベルを一致させるには、複数の入力範囲が必要です。キャリブレーションにより、初期ゲイン誤差とオフセット誤差を補正します。

この設計は、高精度の抵抗ネットワークである RES21A と高性能のデータ コンバータである ADS127L21B を使用し、実効直線性とノイズ性能を実現しています。OPA828 と TMUX6104 は、プログラマブル ゲイン入力アンプを作成しており、複数の入力範囲に対応できます。この設計には、オンボードの較正用線源である REF81 も実装されており、シグナル チェーン全体のゲイン誤差とオフセット誤差をキャリブレーションできます。

### 1.1 主なシステム仕様

このリファレンス デザインの主要なシステム仕様を、表 1-1 に示します。

表 1-1. 主なシステム仕様

| RANGE     | ノイズ                                    | 直線性 (最大値) |

|-----------|----------------------------------------|-----------|

| ±10V 範囲   | 60SPS で $335\text{nV}_{\text{RMS}}$    | 1.1ppm    |

| ±1V 範囲    | 60SPS で $547\text{nV}_{\text{RMS}}$    | 0.6ppm    |

| ±100mV 範囲 | 60SPS で $3.23\mu\text{V}_{\text{RMS}}$ | 3.0ppm    |

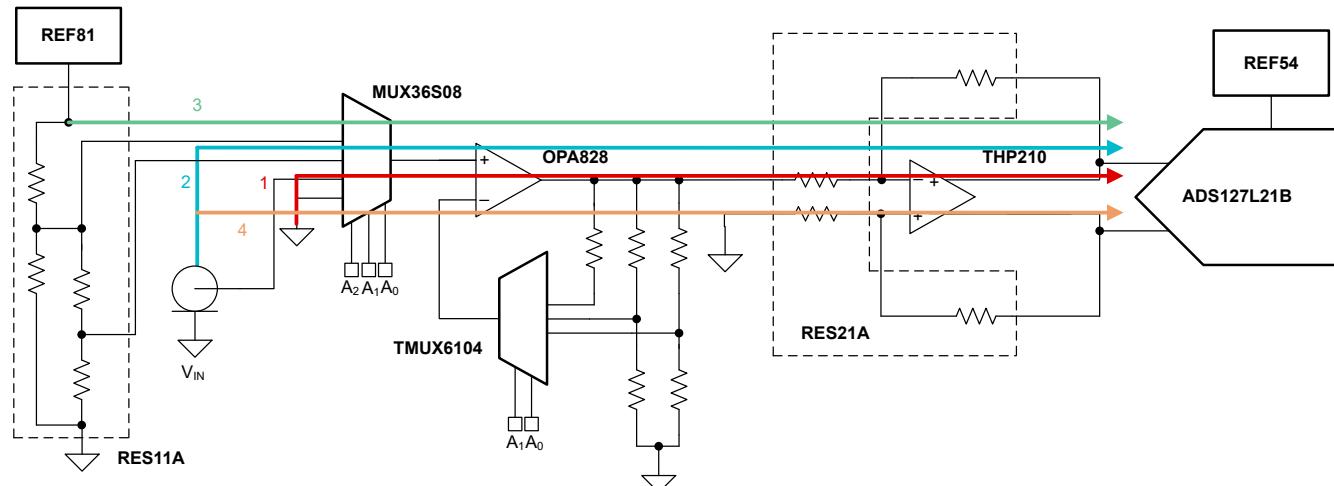

## 2 システム概要

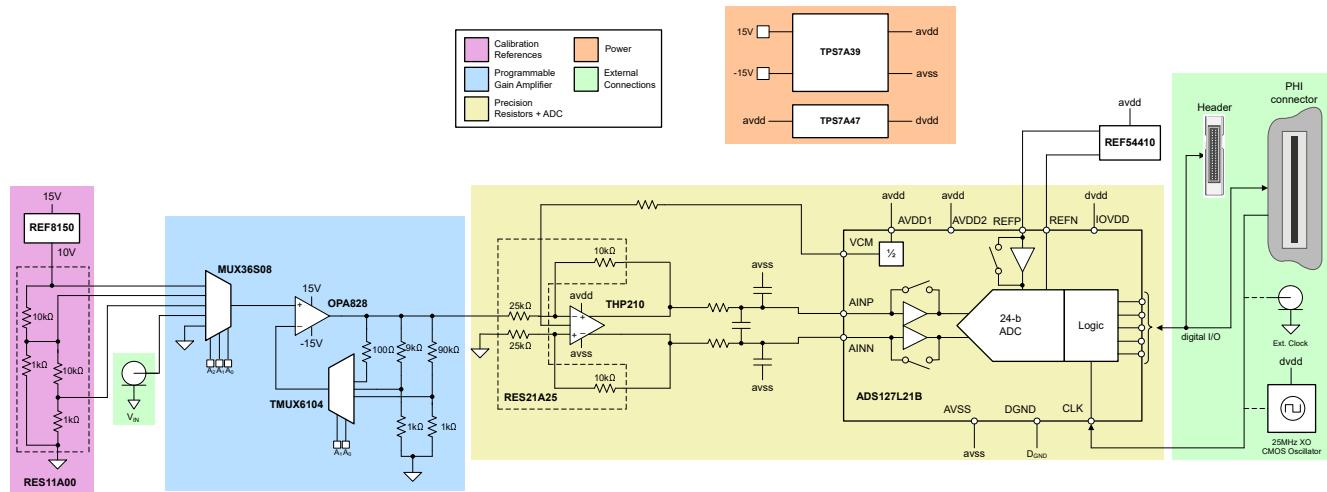

### 2.1 ブロック図

図 2-1. TIDA-010970 のブロック図

### 2.2 設計上の考慮事項

DMM は、DMM が画面に表示できる桁数によって分類されます。たとえば、6.5 桁の DMM では、6 桁の整数 (0~9 の範囲の数字) と、0 または 1 を表示できる先頭の数字を表示できます。先頭の数字は 2 つの値しか表示できないため、半角です。したがって、6.5 桁の DMM の測定範囲は  $\pm 1999999$  (2,000,000 カウント) です。DMM 桁ごとに分解能の桁数が 1 桁増えます。たとえば、6.5 桁の DMM のカウント数は 5.5 桁の DMM の 10 倍、7.5 桁の DMM のカウント数は 6.5 桁の DMM の 10 倍です。6.5 桁以上の高分解能 DMM は、高分解能を持つ高感度 DC 信号の測定に使用されます。

DMM は、数十ボルトまたは数百ボルトから、ミリボルトまたはマイクロボルトの範囲のさまざまな信号レベルに対応できるように異なる入力範囲を使用します。複数の範囲に対応できるため、DMM はより大きな信号と同じ分解能でより小さな信号を測定できます。たとえば、0V ~ 10V の単一範囲のみを有する 6.5 DMM メーターでは、 $10 \pm 0.00005V$  として 10V 信号を測定します。この同じ DMM は 100mV の信号を  $0.1 \pm 0.00005V$  として測定し、これは 4.5 桁の分解能に相当します。10V、1V、100mV など複数の範囲を持つ DMM は、100mV の信号を  $100 \pm 0.00005mV$  として測定し、これは 6.5 桁の分解能に相当します。

DMM シグナル チェーンは、入力範囲全体にわたって信号を正確に測定するために、できるだけ誤差を小さくする必要があります。キャリブレーションを行うとシグナル チェーンから初期ゲイン誤差とオフセット誤差を除去でき、連続キャリブレーションを行うと温度ドリフトと長期ドリフトを除去できます。ただし、キャリブレーションは、較正用線源の精度と同等の精度にとどまります。

DMM シグナル チェーンがゲイン誤差とオフセット誤差に対して較正されていても、ノイズや非線形性の誤差は依然として存在します。積分非直線性 (INL) は、オフセットおよびゲイン誤差を補正した後の、システム出力の線形理論出力に対する偏差の測定値です。ノイズは、シグナル チェーンに干渉する不要な信号です。ノイズは電子部品に固有のものであるため、どのシグナル チェーンからもノイズを完全に除去することはできません。非線形性やノイズはキャリブレーションが困難なので、シグナル チェーン内のノイズと非線形性を最小化するには、低ノイズのリニア デバイスを選択するのが最善の方法です。

## 2.3 主な使用製品

この設計は、目的の性能を実現するため、多くの高精度部品を使用しています。

### 2.3.1 ADS127L21B

ADS127L21B は、プログラマブル デジタル フィルタを特徴とする、24 ビットのデルタシグマ ( $\Delta\Sigma$ ) A/D コンバータ (ADC) です。このデジタル フィルタのデータレートは、広帯域フィルタ使用時に最大 512kSPS、低レイテンシ sinc フィルタ使用時に最大 1365kSPS です。本デバイスは、低消費電力で優れた AC 性能と DC 精度を備えています。

この低ドリフトの変調器は、優れた DC 精度、業界トップクラスの 0.8ppm の INL 仕様 ( $0^{\circ}\text{C} \sim 70^{\circ}\text{C}$ )、低広帯域ノイズによる優れた AC 性能を実現しています。アーキテクチャは、消費電力に関する拡張性が高く、データレート、分解能、消費電力を最適化するために、4 つの速度モードがあります。信号およびリファレンス入力バッファは、ドライバの負荷を低減して精度を向上させます。

### 2.3.2 REF81

REF81 は、7.6V 埋め込みツェナー出力を有する高精度の抵抗デバイスを内蔵しており、高性能データコンバータで使用できる高精度電圧リファレンスを実現します。内蔵の抵抗ペアは、クラス最高レベルの温度ドリフトと長期安定性を実現するためにマッチングされています。内蔵ヒーターには温度制御機能が内蔵されており、周囲温度が変化しても一定のリファレンス電圧を維持できます。この内蔵ヒーターにより、REF81 は 0.05ppm/ $^{\circ}\text{C}$  という非常に小さい温度ドリフトを実現できます。このデバイスは、温度制御と高精度の分圧器を内蔵しているので、設計の複雑さを解消できます。これにより、設計サイクルが短縮され、簡単に起動でき、温度制御および電圧生成における高コストの外付け高精度部品に依存する必要はありません。

REF81 ファミリは、20 ピン LCCC パッケージで供給されます。LCCC パッケージは、キャリブレーションなしで長期間安定して動作することが必要とされるアプリケーションのために、1ppm という非常に低い長期ドリフト安定性仕様を実現できる気密封止セラミック パッケージです。このパッケージは、湿度の変化に対する耐性も非常に優れています。

### 2.3.3 REF54

REF54 は、高精度、低ドリフト、低消費電流の電圧リファレンス デバイスです。REF54 は、380 $\mu\text{A}$  の消費電流で、低温度ドリフト係数 (0.8ppm/ $^{\circ}\text{C}$ )、低ノイズ (0.11ppm<sub>p-p</sub>)、高精度 ( $\pm 0.02\%$ ) を実現します。REF54 により、長期ドリフトが小さい (3ppm LCCC、25ppm SOIC)、高精度アプリケーションの厳しい性能要件をシステムが満たせるようになります。このデバイスは、ADS127L21B などの高分解能データコンバータのコンパニオン デバイスとして設計されています。

### 2.3.4 RES21A

RES21A は、マッチングされた抵抗デバイスのペアで、テキサス インスツルメンツの最新の高性能アナログ CMOS プロセスで薄膜 SiCr に実装されています。このデバイスは、熱および電流ノイズを低減するための公称入力抵抗が 10k $\Omega$  であり、幅広いシステムの要求を満たすため、いくつかの公称比率で供給されます。RES21A は、デバイスの配置を 180° 回転させるだけで、ゲインを反転した構成で使用できます。この機能により、レイアウトの再利用がサポートされ、ディスクリート計測機器や差動アンプの実装などのアプリケーションで柔軟性が向上します。RES21A シリーズは、公称値から  $\pm 500\text{ppm}$  以内の高い比率マッチング精度を有しており、最大比率ドリフトはわずか  $\pm 2\text{ppm}/^{\circ}\text{C}$  です。

### 2.3.5 THP210

THP210 は、完全差動信号チェーンを簡単にフィルタおよび駆動できる超低オフセット、低ノイズ、高電圧、高精度の完全差動アンプです。また THP210 は、シングルエンドの信号源を、高分解能 ADC が必要とする差動出力に変換するためにも使用されます。非常に優れたオフセット、低ノイズ、全高調波歪み (THD) を実現するように設計されたバイポーラースーパー ベータ入力は、非常に小さい静止電流と入力バイアス電流において超低ノイズ指数を実現します。このデバイスは、低消費電力と優れた信号対雑音比 (SNR) が必要とされる信号コンディショニング回路用に設計されています。THP210 は、最大  $\pm 18\text{V}$  の高電圧電源に対応しています。この機能により、差動信号の各極性のために個別のアンプを追加しなくても、高電圧差動シグナル チェーンがダイナミックレンジの恩恵を受けられます。THP210 は電圧および電流ノイズが非常に低いため、信号忠実度への影響を最小限に抑えながら高ゲイン構成で使用できます。

### 2.3.6 OPA828

OPA828 および OPA2828 (OPAx828) 接合部電界効果トランジスタ (JFET) 入力オペアンプは、高速性と高い DC 精度および AC 性能を兼ね備えています。これらのオペアンプは、低オフセット電圧、過熱に対する低ドリフト、低バイアス

電流、低ノイズを実現しており、0.1Hz ~ 10Hz のノイズはわずか 60nV<sub>RMS</sub> です。OPAx828 は  $\pm 4V$  ~  $\pm 18V$  の広い電源電圧範囲で動作し、典型的な消費電流はチャネルあたり 5.5mA です。

45MHz のゲイン帯域幅積 (GBW) や 150V/μs のスルーレートなどの AC 特性により、OPAx828 ファミリはさまざまなシステムに最適です。これには、高速かつ高分解能のデータ アクイジション システム、トランシスインピーダンス (I/V 変換) アンプ、フィルタ、高精度の  $\pm 10V$  フロント エンド、およびハイインピーダンスのセンサ インターフェイス アプリケーションなどが含まれます。

### 3 システム設計理論

線形性が高く、低ノイズのシグナル チェーンであるこのリファレンス デザインは、次の 3 つの主な目標を達成しています。

- 複数の入力範囲への対応

- システムレベルのオンボード キャリブレーションの実現

- 低ノイズと線形性の高い性能の提示

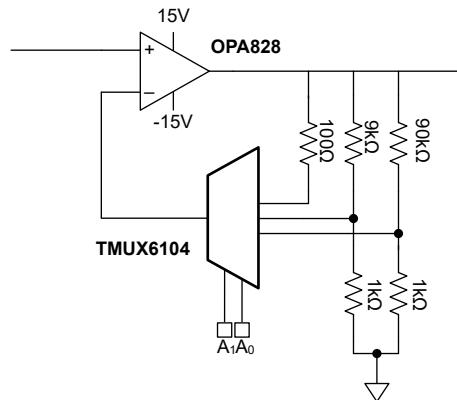

#### 3.1 レンジ選択

この設計では、次の 3 つの測定範囲を持つ電圧測定シグナル チェーンを備えています： $\pm 100mV$ 、 $\pm 1V$ 、 $\pm 10V$ 。[図 3-1](#) に示すように、OPA828 は入力アンプで、高入力インピーダンスを実現するために非反転構成です。低リークのマルチプレクサ (TMUX6104) は、3 つの異なるゲイン設定の間で切り替えを行います。

図 3-1. TIDA-010970 プログラマブル ゲイン アンプのブロック図

OPA828 は JFET アンプで、バイポーラ入力アンプに比べて入力インピーダンスが高く、CMOS 入力アンプよりも 1/f ノイズが低くなります。広帯域ノイズよりも 1/f ノイズが低いことは、DC 測定ではより重要です。バイポーラ アンプは JFET よりも 1/f ノイズが低いにもかかわらず、JFET アンプの入力インピーダンスが高いため、実用的なトレードオフとなっています。入力インピーダンスが高いため、測定シグナル チェーンが測定信号を中断することを防止できます。電圧測定のために、DMM は負荷に並列に接続します。テスト対象の回路からの大電流がメーターを流れるとき、負荷で電圧降下が発生し、測定値が不正確になる恐れがあります。

入力アンプのゲインはプログラマブルで、シグナル チェーンは 1V/V、10V/V、99.8V/V の 3 つの入力範囲に対応して入力信号を 10V の範囲にスケーリングできます。各ゲイン設定の帯域幅は異なり、最大ゲインでの最小帯域幅は 15kHz となります。この設計は DC 信号の測定を目的としているため、ゲイン全体での帯域幅の違いは問題になりません。必要に応じて帯域幅を調整するために、コンデンサ C17、C18、および C19 を取り付けます。

ADS127L21B の推奨最大電源電圧は 5.5V なので、各範囲で入力信号を 5.5V 以下にスケーリングする必要があります。この設計では、ADC のリファレンス電圧が 4.096V であるため、入力信号を 4V にスケーリングします。ADS127L21B 電源は  $\pm 2.75V$  です。この電源範囲は THP210 と共有され、THP210 同相入力制限のマージンを確保します。

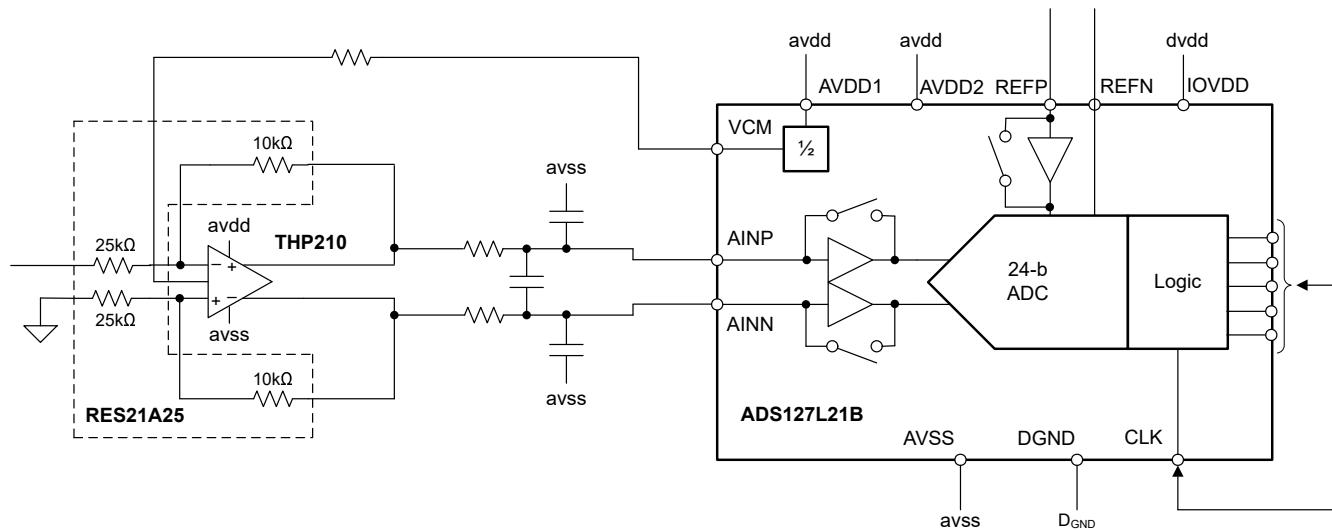

### 3.2 直線性と低ノイズのシグナル チェーン

この設計では、DC 電圧の測定のための、線形性が高く低ノイズのシグナル チェーンを採用しています。オフセットとゲイン誤差は、単純な 2 点または 3 点のキャリブレーションで簡単に補正できますが、ノイズと直線性は簡単にキャリブレーションできません。低ノイズで線形性の高い部品を選択することが不可欠です。1/f ノイズ、つまりフリッカー ノイズは、広帯域ノイズよりもはるかに大きな懸念事項になります。このシグナル チェーンは、低周波信号の測定を目的としているためです。

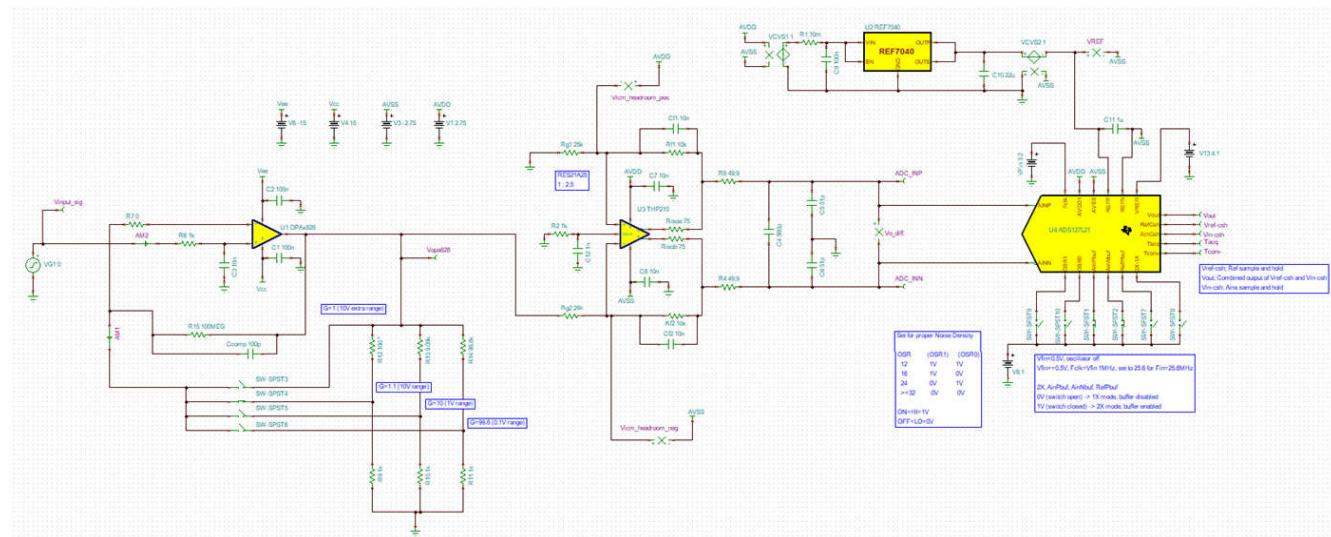

図 3-2 に示す完全差動アンプ THP210 デバイスは、ADS127L21B を使用して測定するために、シングルエンド入力信号を差動信号に変換します。

図 3-2. TIDA-010970 ADC のブロック図

シングルエンド入力の測定により、DMM は共通のグランドを基準とした負荷を測定できます。信号を差動信号に変換することで、残りのシグナル チェーンについて、シグナル インテグリティとノイズ耐性が向上します。THP210 は、外付けの高精度薄膜抵抗 RES21A を使用し、1:2.5 比で 0.4V/V のゲインを実現します。この段は、OPA828 の出力を 10V 範囲から 4V の範囲まで減衰します。ADC リファレンス電圧は 4.096V なので、最大 ADC 入力信号は ADC フルスケール レンジの 98% を使用します。これにより、ADC の分解能が最大化されます。

RES21A 抵抗デバイスは 10kΩ ベースです。RES21A は、抵抗が大きく自己発熱が低減されるため、非直線性が小さくなっています。これらのより大きい抵抗により、このシステムに広帯域ノイズが追加されます。ただし、ほとんどの DMM の測定はより低速で行われるため、RES21A による直線性の向上は、追加のノイズよりも影響力があります。

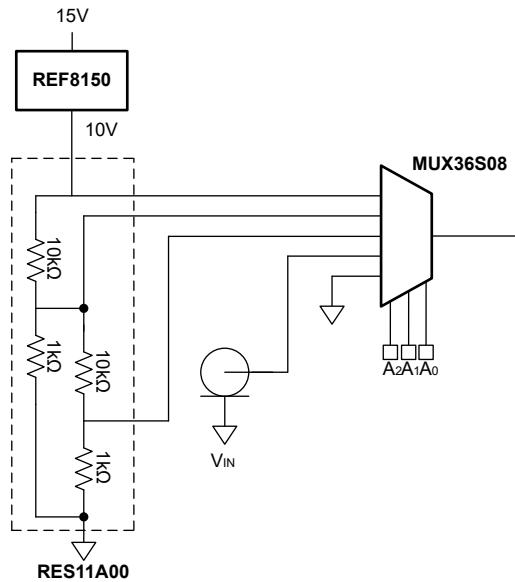

### 3.3 較正

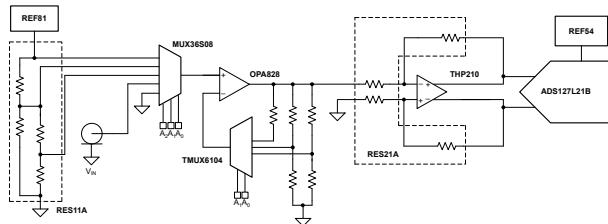

この設計では、シグナル チェーンのキャリブレーション用に非常に安定性の高い埋め込みツェナー リファレンスである REF81 を使用しています。高精度の抵抗デバイス ネットワーク (RES11A) は、1V および 100mV の入力範囲用に追加の較正用線源信号を生成します (図 3-3 を参照)。入力マルチプレクサ (MUX36) は入力信号、各入力範囲の較正用線源信号、グランドのいずれかを選択します。

図 3-3. TIDA-010970 キャリブレーション リファレンス ブロック図

10V 範囲の較正用線源は REF81 から直接派生しているため、この範囲は最も正確なキャリブレーション範囲となります。1V および 100mV の範囲の較正用線源は 10V 信号から生成されるため、精度はわずかに低くなります。1V および 100mV のソースを生成するために使用する高精度の抵抗デバイダに起因する誤差が存在します。このリファレンス デザインでは、ほぼフルスケールの信号を使用して、入力範囲全体にわたって較正された誤差を最大化します。

較正用線源は、シグナル チェーン全体をキャリブレーションします。測定間でキャリブレーションを繰り返すと、すべての測定から初期ゲイン誤差とオフセット誤差が連続的に除去されます。この連続キャリブレーションにより、オフセット誤差とゲイン誤差のドリフトも除去されます。したがって、システムに残る誤差は、シグナル チェーンのノイズと直線性、および較正用線源のドリフトだけです。長期ドリフトおよび温度ドリフトによる誤差を低減するために、較正用線源は時間と温度の変化に対して安定している必要があります。これは、シグナル チェーン全体の精度が較正用線源に依存するためです。安定した較正用線源により、主要な誤差発生源は非線形性とノイズとなります。[セクション 3.2](#) で説明しているように、部品を慎重に選択することで、これらの誤差発生源を低減します。

以下の手順に従って、連続キャリブレーション手順を実行します：ソフトウェアはこの手順を自動的に実装でき、正確な測定を行うにはキャリブレーション手順のフルサイクルが必要です。図 3-4 にこのプロセスを示します。

1. 入力をグランドに設定して、システムのオフセットを測定します。オフセット誤差を計算します。

2. マルチプレクサを再び入力に切り替えます。入力を測定し、オフセットを減算してゲインを乗算します。この手順の最初の繰り返しにおける最初の測定では、ゲイン係数はありません。

3. マルチプレクサを較正用線源に切り替えます。較正用線源を測定し、ゲイン誤差を計算します。各範囲に較正用線源があり、目的の範囲に応じて適切なソースを選択します。

4. マルチプレクサを再び入力に切り替えます。入力を測定し、オフセットを減算して、ゲインを乗算して、最終的な較正結果を求めます。

5. 手順 1 ~ 4 を繰り返します。

図 3-4. TIDA-010970 の較正手順

ADS127L21B のゲインおよびオフセットレジスタにゲイン値とオフセット値を適用するため、ADS127L21B は変換データにゲインおよびオフセット補正を自動的に適用します。オフセットレジスタの値が、変換結果から最初に減算されます。次に、ゲインレジスタの値が、変換結果を 400000h で除算した値で乗算されます。詳細については、[『ADS127L21B: 512kSPS、高精度、24 ビット、広帯域デルタシグマ ADC』](#)データシートの「キャリブレーション」セクションを参照してください。

このキャリブレーション手順は、1 サイクル中の入力を 2 回測定します。入力を 2 回測定すると、DMM は 1 回の測定ごとに入力を測定するため、サンプリングレートの 1/3 ではなく、半分のサンプリングレートで入力を測定できます。たとえば、60SPS でキャリブレーション手順を実行する DMM の実効測定レートは 30SPS です。または、DMM を 120SPS で動作させて 60SPS の測定を行います。さらに、連続的なルーチン キャリブレーションでは、正確な測定を行うために、セトリングタイムが短いマルチプレクサが必要です。

### 3.4 システム設計の追加検討事項

TPS7A39 はデュアル出力 LDO で、THP210 と ADS127L21B 用の正と負の電源レールを生成します。TPS7A39 の出力は  $\pm 2.75V$  に設定され、THP210 の同相入力電圧範囲を維持します。

この設計は、起動時に 335mA を消費し、通常動作時に約 75mA を消費します。消費電力の影響を受けやすいアプリケーションでは、いくつかの方法によって消費電力を最小限に抑えることができます。REF81 は消費電力の 80% を供給します。REF81 ヒーターは、通常動作時に約 60mA を消費します。この設計では、+15V レールを使用して REF81 ヒーターに電力を供給しますが、HEATP ピンと HEATM ピンの間のヒーター電源を増やすと、REF81 の消費電流が削減されます。詳細については、[『REF81: 温度ドリフト 0.05ppm/°C、変動 1ppm 未満の安定性を示す温度制御型の高精度電圧リファレンス』](#)データシートを参照してください。さらに、PCB には外部筐体に対応するために、REF81 の周囲に取り付け穴があります。筐体を追加すると、ヒーターのレギュレーションが改善され、全体的な出力電圧ドリフトが低減されます。

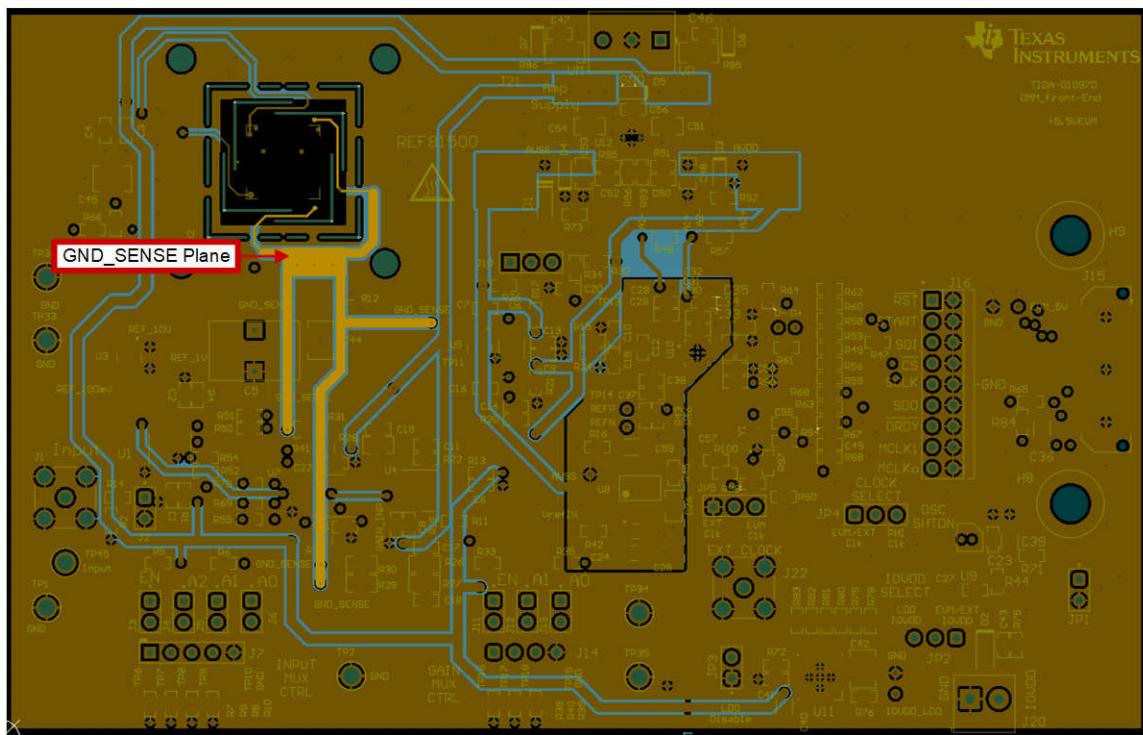

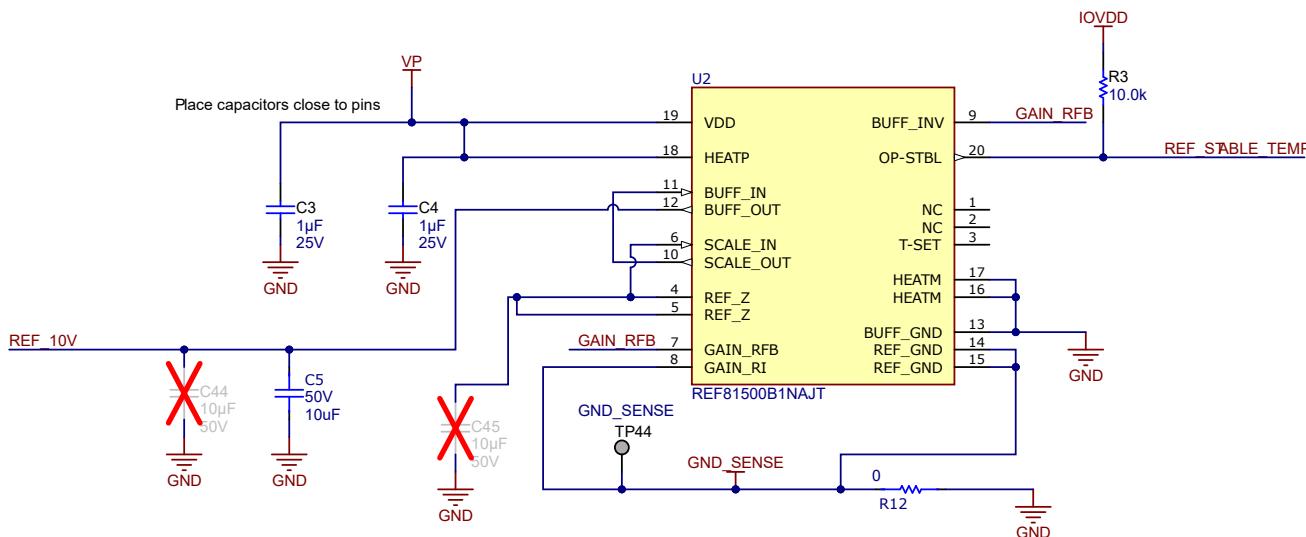

グランドプレーンの抵抗が小さいと、REF81 電流消費量が非常に大きいため、測定パスに予測不能な電圧降下が発生します。この電流降下による誤差を防止するため、信号測定パスのすべての部品はスターグランドプレーン (GND\_SENSE) を基準としています。このスターグランドプレーンを基準とする部品は、より低い電流を示します。スターグランドプレーンの抵抗は、REF81 グランドプレーンの等価抵抗よりも電圧降下が小さくなり、誤差を最小限に抑えます。スターグランドプレーンと REF81 のグランドプレーンは、R12 の 1 点で接続されています。[『GND\\_SENSE プレーンを持つ回路図と PCB』](#)を参照してください。

図 3-5. GND\_SENSE プレーンを持つ回路図と PCB

1/f ノイズと温度ドリフトが小さいことから、ADC リファレンスとして REF54 を選択します。REF54 にはバッファ付き出力があるため、高精度で安定した ADC リファレンスを提供するために追加のリファレンス回路は必要ありません。REF81 を ADC リファレンスとして使用できますが、REF54 は REF81 よりも小さく、電流も少なくなります。さらに、REF54 は発熱を心配することなく、ADC の近くに配置できます。

## 4 ハードウェア、ソフトウェア、テスト要件、テスト結果

### 4.1 ハードウェアの説明

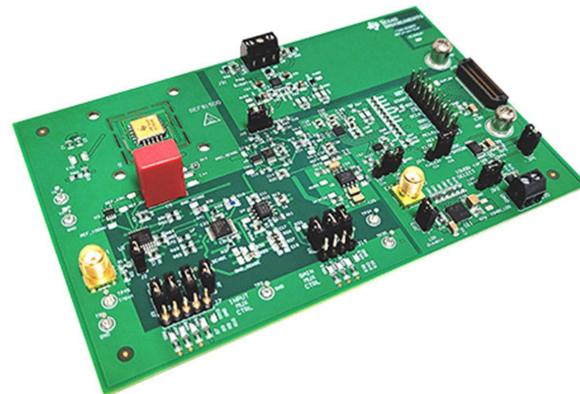

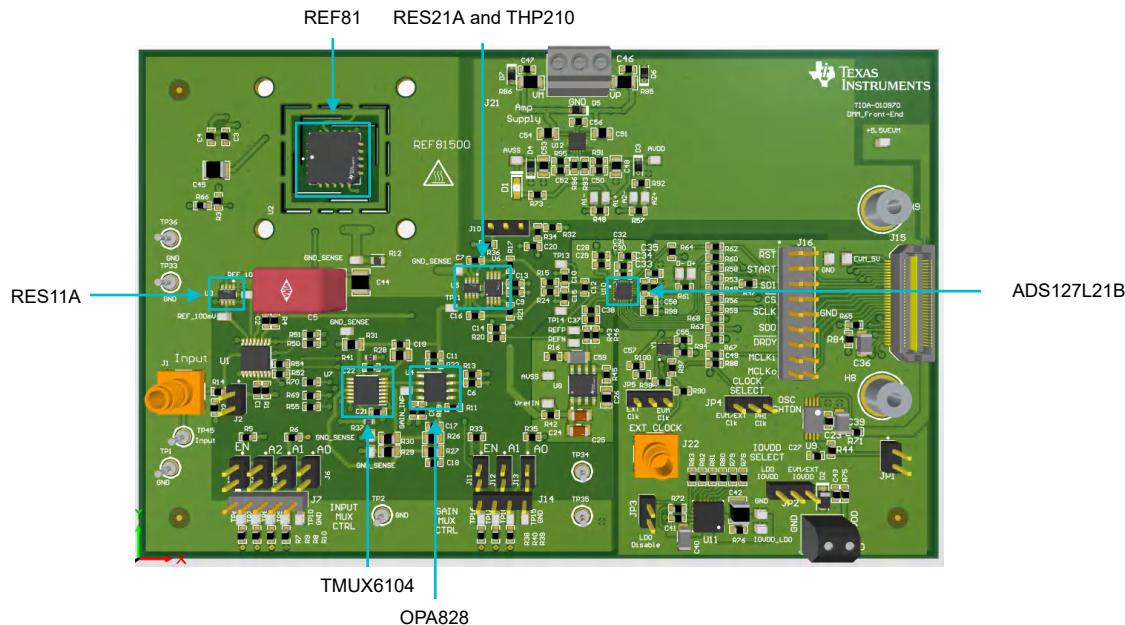

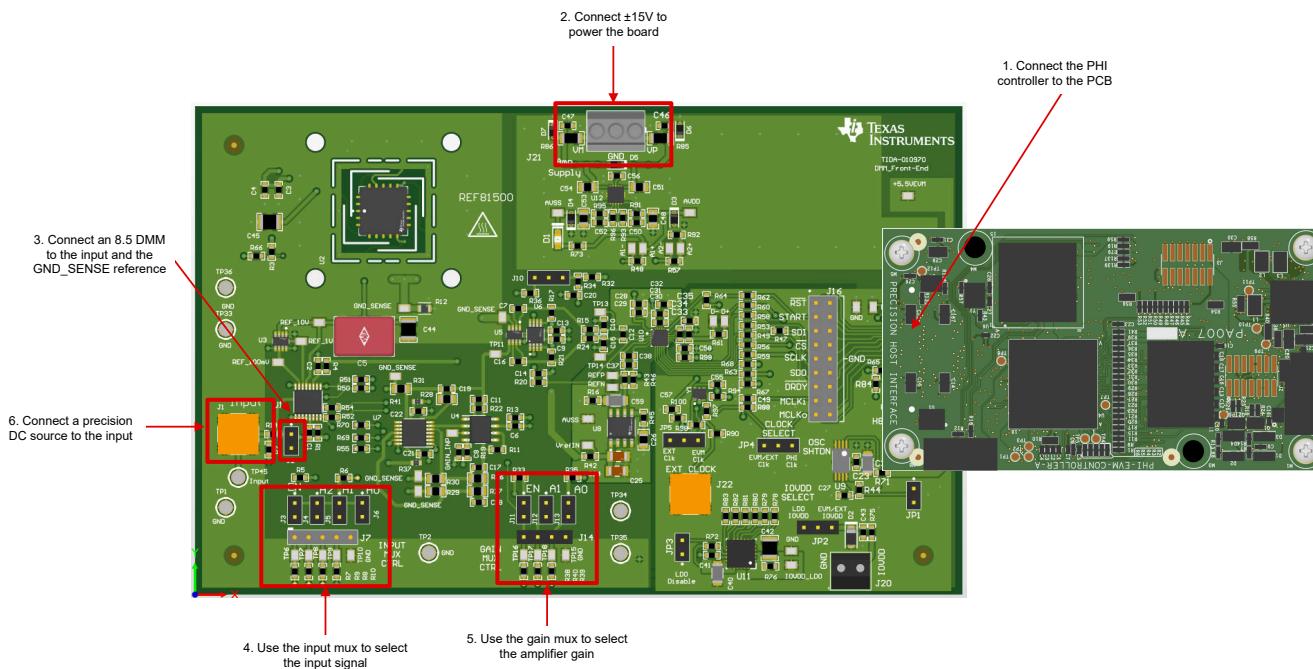

図 4-1 に、PCB 設計を示します。左上の REF81 と RES11 (U2 と U3) は、キャリブレーションのリファレンス電圧を供給します。右下にある TMUX6104 と OPA828 (U7 と U4) は、プログラマブル ゲイン アンプを作成します。基板の中央にある THP210 と ADS127L21B (U6 と U10) は、リニアで低ノイズの信号路を備えています。性能を向上させるためのレイアウトの選択肢がいくつかあります。セクション 3.4 で説明したスターグランド プレーンは、REF81 の大きな消費電流による誤差を低減します。さらに、差動信号路のパターンはできるだけ対称であり、差動信号間のミスマッチによる誤差を低減します。

図 4-1. TIDA-010970 PCB

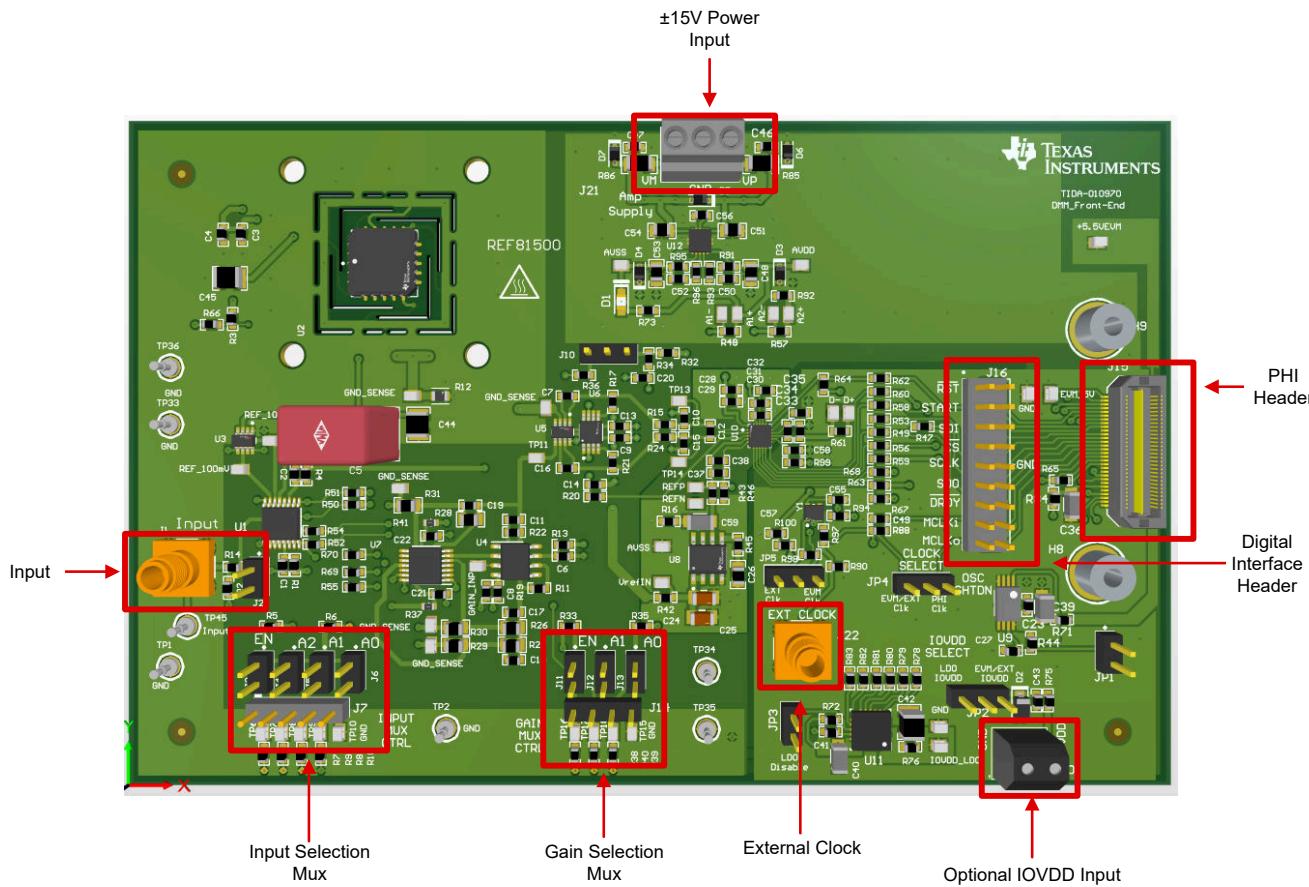

#### 4.1.1 PCB インターフェイス

図 4-2 に PCB コネクタを示します。PHI コントローラに接続する J15、またはピン ヘッダの J16 を介してデジタル インターフェイスにアクセスします。J16 は、オシロスコープやロジック アナライザと簡単に接続できるように、グランドへの一列の接続端子を備えています。このリファレンス デザインは、動作用に外部電源を必要とします。この電源は、J21 で供給されます。ピン ヘッダを使用して、プログラマブル ゲイン アンプの入力を選択し、ゲインを設定します。

図 4-2. PCB のコネクタ

表 4-1. TIDA-010970 の外部接続

| コネクタ               | 説明                                                              |

|--------------------|-----------------------------------------------------------------|

| J1                 | 入力信号用の SMA コネクタ                                                 |

| J2                 | 入力信号用のヘッダ コネクタ                                                  |

| J3, J4, J5, J6, J7 | 入力マルチプレクサ (U7) のイネーブルおよび入力選択ヘッダ。詳細については、表 4-2 を参照してください。        |

| J10                | THP210 シャットダウン対応ヘッダ                                             |

| J11, J12, J13, J14 | ゲイン マルチプレクサのイネーブルと入力選択の各ヘッダ。詳細については、表 4-3 を参照してください。            |

| J15                | PHI に接続するための QSH コネクタ。接続前に PCB に電力を供給するのがベスト プラクティスです。          |

| J16                | SPI 信号ヘッダで、デバッグやプローブ、または別の基板への接続 (QSH がない場合) に使用されます            |

| JP1                | EEPROM イネーブル                                                    |

| JP2                | 1-2: 外部 IOVDD 信号<br>2-3: TPS7A47 によって生成される IOVDD 信号             |

| JP3                | LDO イネーブル                                                       |

| JP4                | 1-2: ADC CLK ピンのオンボード クロックを選択<br>2-3: ADC CLK ピンの PHI クロックを選択   |

| JP5                | 1-2: オンボード クロックとして外部クロックを選択<br>2-3: 局部発振器 (Y1) をオンボード クロックとして選択 |

このリファレンス デザインは、高精度のホスト インターフェイス (PHI) 基板と組み合わせて動作することを想定しており、ADS127L21 グラフィカル ユーザー インターフェイス (GUI) と簡単に接続できます。さらに、PCB にはヘッダが搭載されており、外部コントローラを使用して ADC からのデジタル信号にアクセスできます。すべての PCB 接続については、図 4-2 を参照してください。

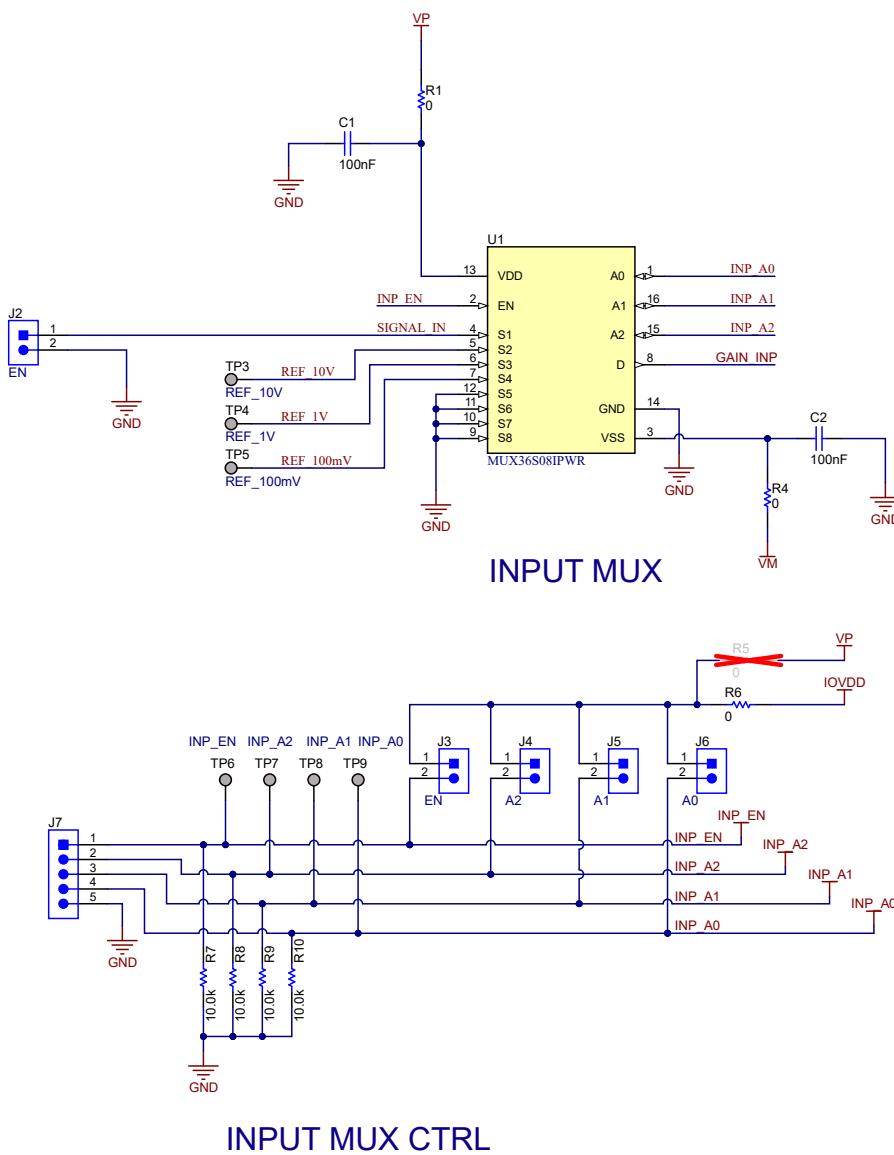

#### 4.1.2 入力マルチプレクサ

このリファレンス デザインには、較正可能な  $\pm 100\text{mV}$ 、 $\pm 1\text{V}$ 、 $\pm 10\text{V}$  の 3 つの入力範囲があります。8 チャネル入力マルチプレクサ (U1) を使用して、入力信号と較正用線源との間で選択します。ジャンパ J3、J4、J5、J6 は、入力マルチプレクサを有効にし、目的の入力チャネルを選択します。詳しくは、表 4-2 を参照してください。

表 4-2. 入力マルチプレクサのジャンパ設定

| J3 (EN) | J4 (A2)          | J5 (A1)          | J6 (A0)          | 入力チャネル       |

|---------|------------------|------------------|------------------|--------------|

| 0       | X <sup>(1)</sup> | X <sup>(1)</sup> | X <sup>(1)</sup> | なし、U1 は無効    |

| 1       | 0                | 0                | 0                | 入力信号         |

| 1       | 0                | 0                | 1                | 10V 範囲較正信号   |

| 1       | 0                | 1                | 0                | 1V 範囲較正信号    |

| 1       | 0                | 1                | 1                | 100mV 範囲較正信号 |

| 1       | 1                | X <sup>(1)</sup> | X <sup>(1)</sup> | グランド         |

(1) 「X」は「未使用」を意味します。

図 4-3. 入力マルチプレクサの回路図

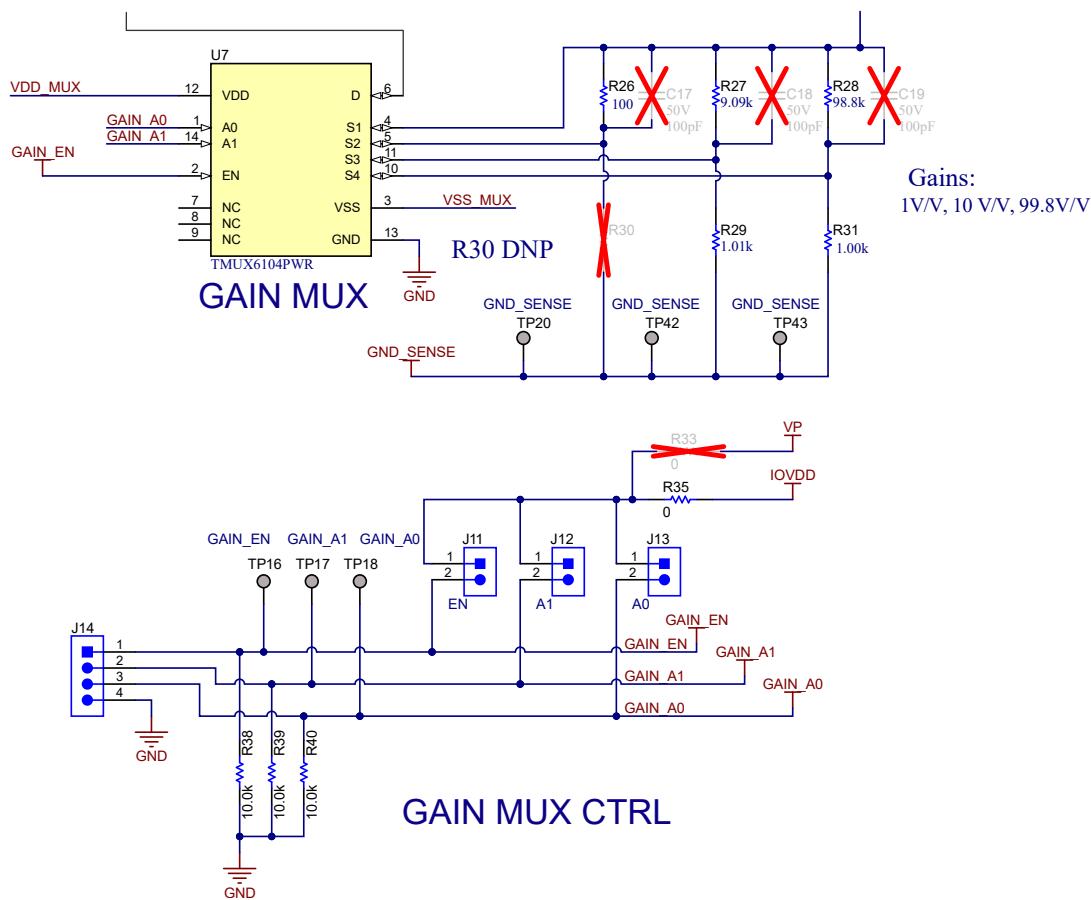

#### 4.1.3 ゲイン マルチプレクサ

4 チャネルのゲイン マルチプレクサ (U7) を使用して、目的の入力範囲を選択します。ゲイン マルチプレクサは、入力アンプ (U4) のゲインを変化させます。測定分解能を最大化するために、入力信号は ADS127L21B のフルスケールレンジでスケーリングする必要があります。入力アンプは、入力信号を 10V のスケールにスケーリングします。ジャンパ J11、J12、J13 は、ゲイン マルチプレクサを有効にし、目的の入力チャネルを選択します。詳細については、表 4-3 を参照してください。

表 4-3. ゲイン マルチプレクサのジャンパ設定

| J11 (En) | J12 (A1)         | J13 (A0)         | 入力チャネル         | 電圧レンジ  |

|----------|------------------|------------------|----------------|--------|

| 0        | X <sup>(1)</sup> | X <sup>(1)</sup> | U7 無効          | -      |

| 1        | 0                | X <sup>(1)</sup> | ゲイン = 1.00 V/V | ±10V   |

| 1        | 1                | 0                | ゲイン = 10.0 V/V | ±1V    |

| 1        | 1                | 1                | ゲイン = 99.8 V/V | ±100mV |

(1) 「X」は「未使用」を意味します。

図 4-4. ゲイン マルチプレクサの回路図

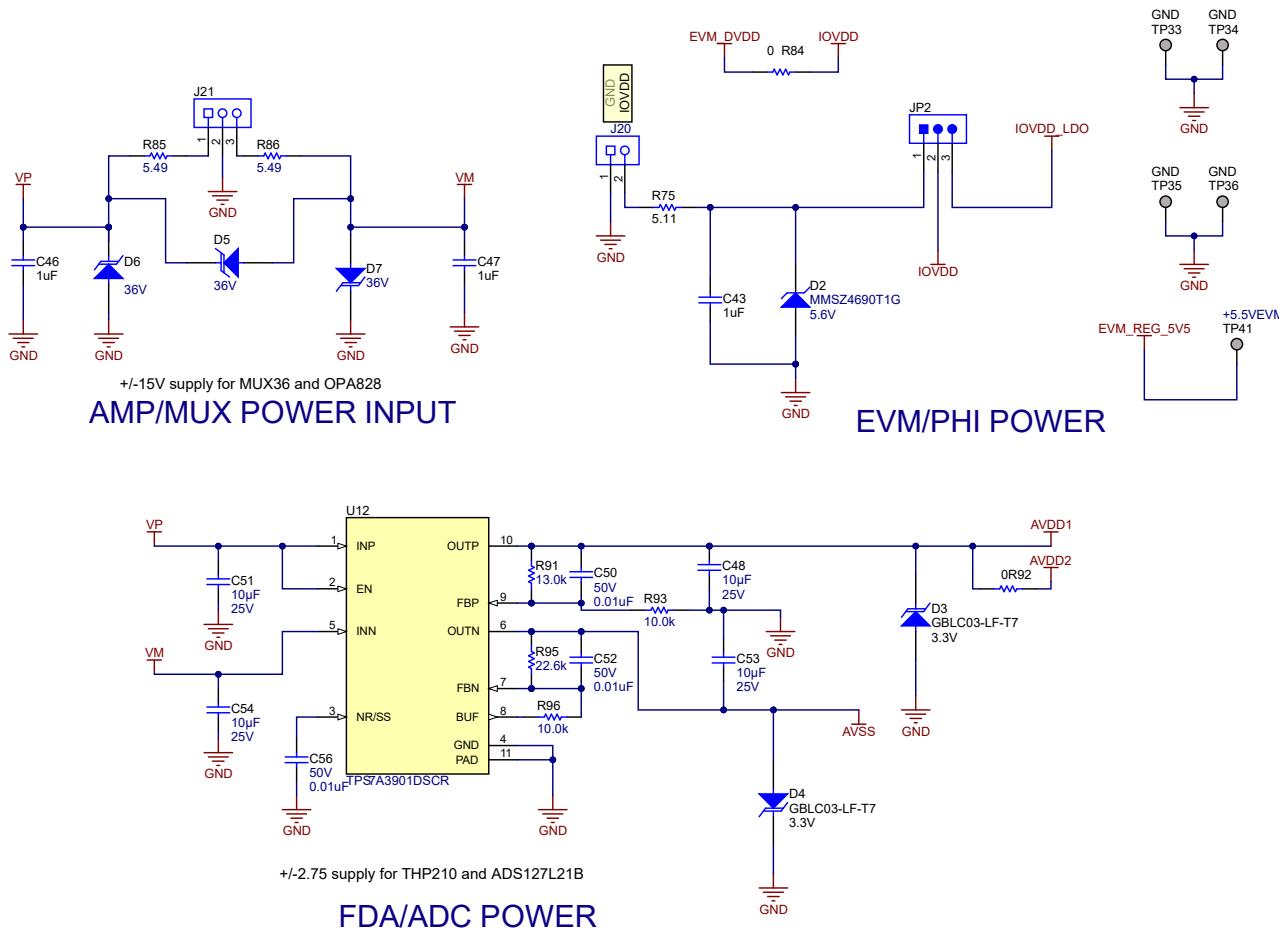

#### 4.1.4 電源

PCB には外部 ±15V 電源が電力を供給します。電源ツリーを、図 4-5 に示します。±15V 電源は、REF81、OPA828、TPS7A39、TPS7A47、MUX36S08、TMUX6104 に直接電力を供給します。このリファレンス デザインには、36V のダイオード D5、D6、D7 が搭載されています。これらのダイオードを使用して、TMUX6104 の推奨最大動作電圧である ±16.5V バイポーラ電源を供給できます。

TPS7A39 は、THP210、ADS127L21B、REF54 に電力を供給する  $\pm 2.75V$  (AVDD および AVSS) 電源レールを生成します。TPS7A47 は、IOVDD を ADS127L21B に供給する 2.5V 電源レールを生成します。JP2 を 1-2 の位置に取り付け、J20 を使用して外部 IOVDD レールに電力を供給します。

図 4-5. 電源ツリーの回路図

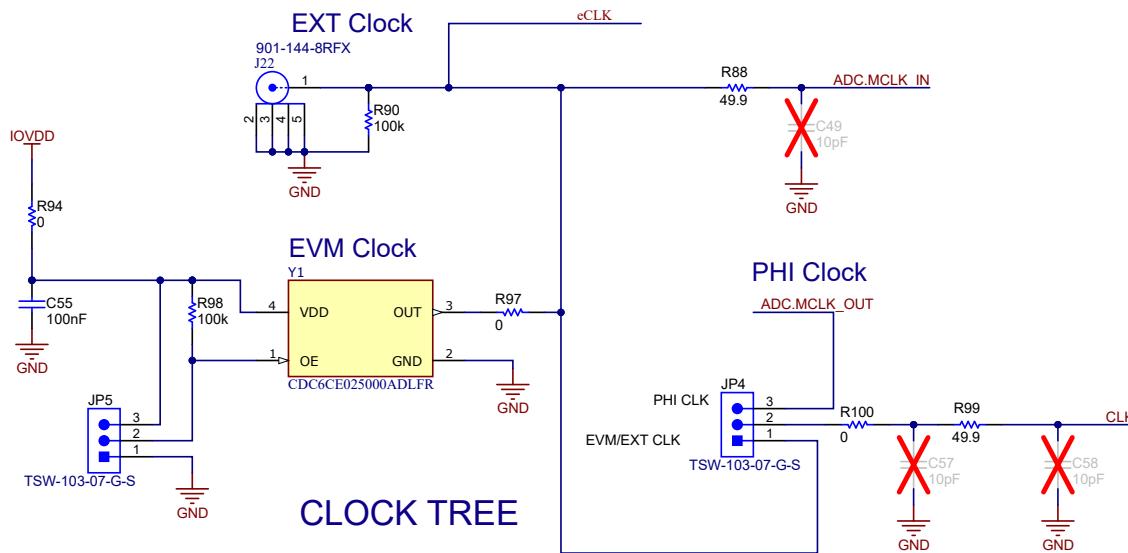

#### 4.1.5 クロックツリー

このリファレンス デザインは、3 種類のクロック オプションをサポートしています。

1. PHI クロック (外部接続なし)

2. ローカル クロック (外部接続なし)

3. 外部クロック

ジャンパ JP4 のデフォルト位置は 2-3 で、PHI デジタルコントローラ基板のクロックを ADS127L21 (U10) の CLK ピンに配線します。PHI コントローラなしで PCB を使用する場合は、ジャンパ位置を 1-2 に移動して、ローカル クロックを ADS127L21 に直接配線します。ジャンパ JP5 の位置を 2-3 にすると、PCB 上でローカル 32.768MHz 発振器 (Y1) が有効になります。これは、ADS127L21EVM-PDK-GUI ソフトウェアを使用するための必要なデフォルトの位置です (ADS127L21EVM-PDK ツール ページを参照)。位置 1-2 にジャンパ J5 を使用して、外部クロックを供給します。振幅が IOVDD (PHI 基板使用時に 2.5V) に等しく、周波数が ADS127L21B の指定範囲内にある CMOS 方形波信号を使用してください。

図 4-6. クロックツリーの回路図

## 4.2 ソフトウェア要件

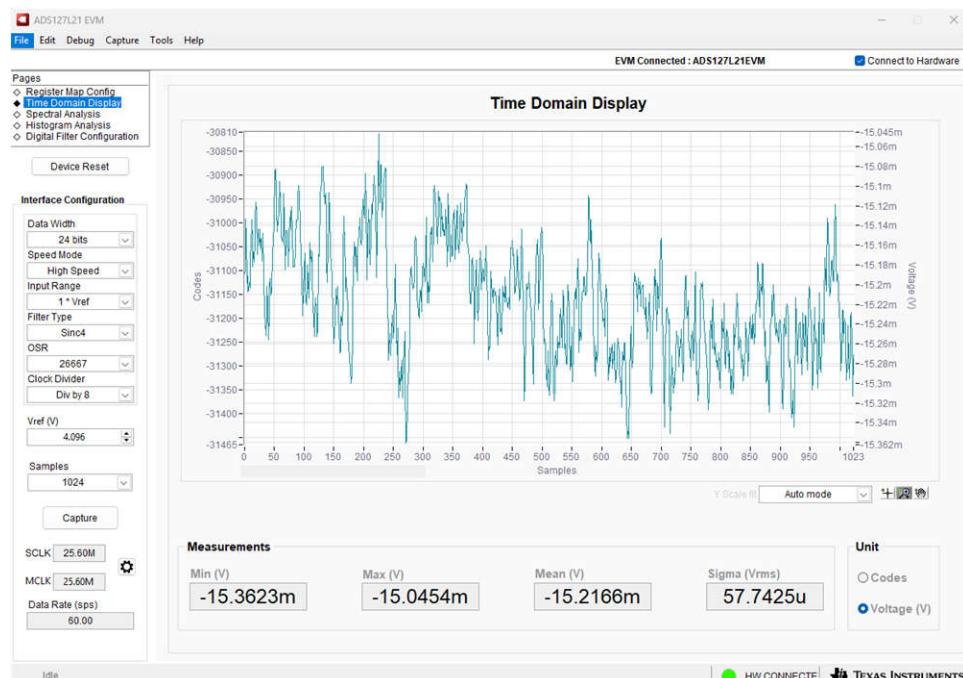

このリファレンス デザインは、図 4-7 に示す専用の [ADS127L21EVM-PDK-GUI](#) ソフトウェアと組み合わせて使用することを意図しています。ADS127L21GUI は、ADS127L21 と ADS127L21B の両方にに対応しています。詳細については、[『ADS127L21EVM-PDK 評価基板』ユーザー ガイド](#)も参照してください。

GUI を使用して ADS127L21B を構成し、ADC のサンプル レートを選択します。クロック周波数を調整して、データ レートを変更します。

また、GUI は時間ドメイン データを収集し、RMS ノイズを自動的に計算します。GUI が収集したデータをダウンロードして、追加の後処理を行うことができます。

図 4-7. ADS127L21 EVM GUI

## 4.3 テスト設定

この PCB は、ADS127L21EVM-PDK-GUI ソフトウェアを実行するコンピュータに接続された PHI 基板を経由して評価されます。

ノイズと直線性テストには、次の部品が必要です。

- リファレンス デザイン PCB

- PHI コントローラ カード

- ADS127L21B ソフトウェアを実行している PC

- ±15V 電源

- 低ノイズ DC 電源

- 8.5 枝の DMM

図 4-8 に示す手順に従って、DC 電圧を測定します。

- PHI コントローラを PCB に接続します

- J21 を使用して、±15V 電源を PCB に接続します

- J2 の入力と GND\_SENSE (TP19) の間に 8.5 枝の DMM を接続します。

- J4、J5、J6 を使用して、入力信号を選択します

- J12 と J13 を使用して、プログラマブル ゲインアンプのゲインを選択します

- 高精度 DC 電源を SMA 入力コネクタ J1 に接続します

図 4-8. TIDA-010970 を使用した DC 電圧測定のテスト設定

SMA コネクタを使用して、できるだけ短い接続で、高精度 DC 電源をシグナル チェーンの入力に接続します。SMA コネクタは、ピン ヘッダと比較して、シグナル チェーンに結合するノイズを低減し、より高精度の測定を実現できます。このリファレンス デザインは 7.5 枝の精度で測定することを意図しているため、8.5 枝の DMM を使用してください。シグナル チェーンのターゲット分解能よりも高い分解能のメーターを使用することが重要です。メーターに誤差があるため、メーターの分解能が同じである場合、シグナル チェーンがターゲットの分解能を満たしているかどうかを評価することはできません。

GND\_SENSE テスト ポイント (TP19, TP20, TP42, TP43, TP44) に対するキャリブレーションと測定の実施が重要です。REF81 は GND プレーンを基準とされています。GND プレーンの抵抗が小さいと、REF81 は大電流を消費し、測定可能な電圧降下が発生することで、測定精度に影響を及ぼす場合があります。

測定されたテスト結果はすべて、GND\_SENSE テスト ポイントを基準にして取得されています。

## 4.4 テスト結果

ノイズと直線性のテストには、以下の ADC 設定を使用します。

**表 4-4. GUI の設定**

| 設定        | 選択             | GUI の配置              |

|-----------|----------------|----------------------|

| REF_RNG   | High のリファレンス範囲 | レジスタ マップ構成 - CONFIG1 |

| CLK_SEL   | 内部クロック動作       | レジスタ マップ構成 - CONFIG3 |

| VREF      | 4.096V         | インターフェイスの構成          |

| 速度モード     | 高速             | インターフェイスの構成          |

| フィルタ タイプ  | Sinc4+Sinc1    | インターフェイスの構成          |

| OSR       | 26667          | インターフェイスの構成          |

| CLK ディバイダ | 8 分周           | インターフェイスの構成          |

| CLK ソース   | 外部             | クロック設定               |

| CLK 周波数   | 25.6MHz        | クロック設定               |

| SCLK ソース  | 内部 (PHI)       | クロック設定               |

| SCLK 周波数  | 25.6MHz        | クロック設定               |

| サンプル      | 1024           | インターフェイスの構成          |

図 4-7 に示すように、SCLK 周波数と MCLK 周波数の横にある歯車アイコンを押して、クロック設定を検索します。表 4-4 に示されていない設定は、GUI のデフォルト設定に残されています。これらの変更を行うと、計算データレートは 60SPS に設定されます。外部クロックソースを使用して、10PLC (電力線サイクル) や 0.1PLC などの他のデータレートをテストします。コネクタ J22 を使用し、JP5 を 1-2 の位置に移動して、外部クロックソースを接続します。詳細については、[セクション 4.1.5](#) を参照してください。

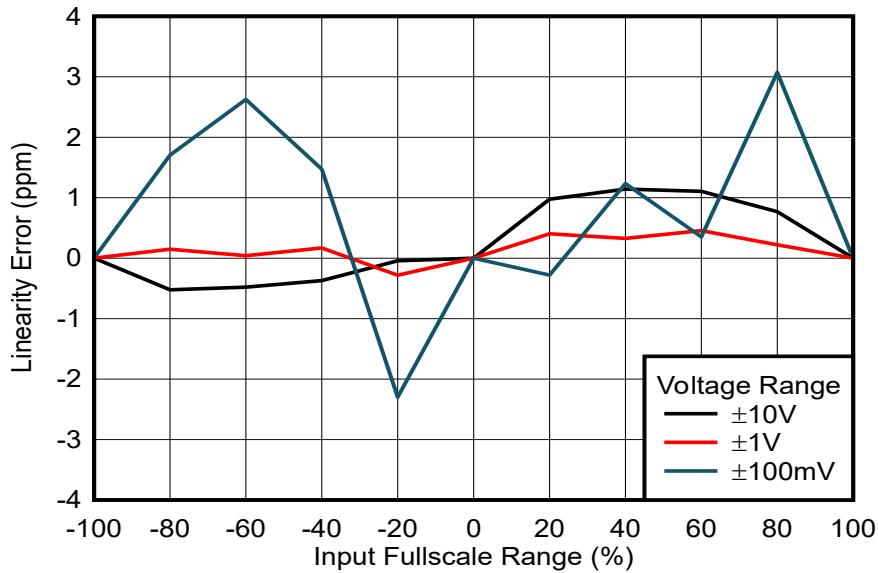

### 4.4.1 積分非直線性測定

INL テストでは、測定誤差が発生しないように、超低ノイズなソースを必要とします。INL は線形性の高いシグナル チェーンであるため、正確に測定するには 8.5 術の DMM が必要です。DMM はシグナル チェーン入力を測定し、GUI は ADC 出力を測定します。出力とスケーリングされた入力が比較されます。入力範囲全体にわたって測定を実施します。

INL はノイズフロアよりも低くなることがあります。測定シグナル チェーンは非直線性が低くなるように設計されているためです。N サンプルの平均化により、熱ノイズが  $\sqrt{N}$  分の 1 に減少します。十分な平均化を行えば、INL を検出および測定できます。測定される各ポイントは、平均 1024 回の測定値です。

図 4-9 は、このリファレンス デザインで測定された INL が、10V 範囲に対して約 1.1ppm であることを示しています。TIDA-010970 は完全な DMM 設計ではありません。完全な DMM 設計には、入力保護など非線形性を加える他の部品がシグナル チェーン内に含まれています。ただし、TIDA-010970 は、信号測定パスの最も重要な部品を搭載しています。

図 4-9. TIDA-010970 の直線性誤差と入力フルスケール レンジとの関係

3 エンドポイントキャリブレーションを使用して INL を計算します。この方法では、ゼロ、正のフルスケール、負のフルスケールの 3 つの測定が必要です。これら 3 つの測定値から 2 組の係数を計算します。1 つ目で負の範囲を線形補正し、2 つ目では正の範囲について線形補正します。これらの線形補正是、個別の線形フィットを作成します。次に、実際に測定された出力と、較正された個々のリニア出力を比較して、INL を計算します。理論的には、3 つ以上の点を測定して、2 つ以上の係数セットを持つ個別の関数を作成することができます。ただし、このシステムは低直線性を意図して設計されているため、2 組の係数で十分です。

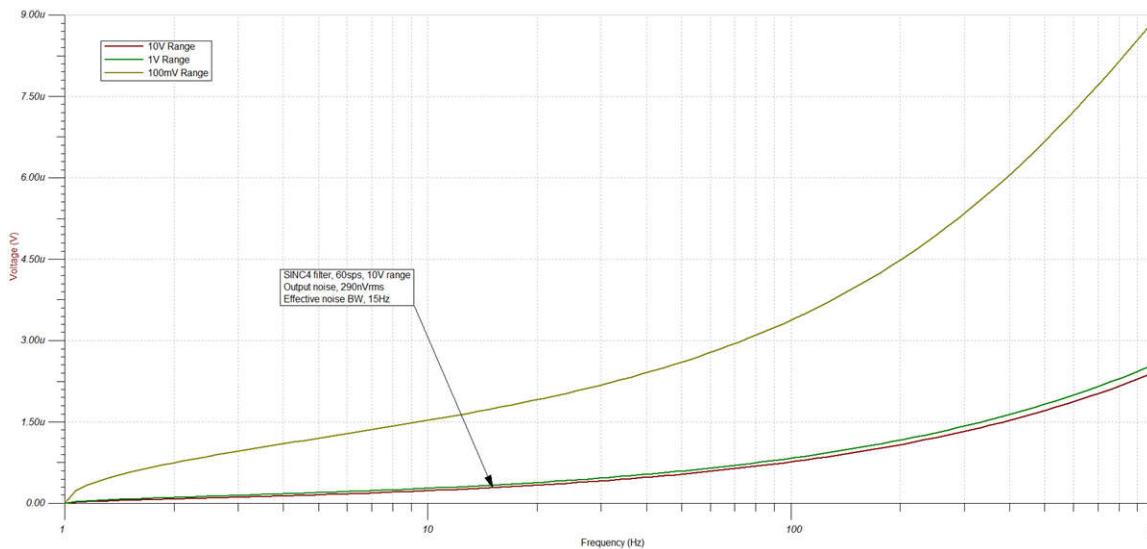

#### 4.4.2 ノイズ シミュレーション

図 4-10 に、シグナル チェーン全体のノイズをシミュレーションするために使用した TINA-TI の回路図を示します。図 4-11 にシミュレーション結果を示します。DMM ノイズは多くの場合、パワーラインサイクル (PLC) 数で規定されます。これは、電源ラインの周波数の 1 サイクルを表します。PLC が高いほど、測定の積分時間が長いことを示します。たとえば、5 PLC は、5 回のパワーラインサイクルで測定された DMM を示します。PLC が高いほど、測定時間が長くなり、より正確な測定が可能になります。60Hz、または 1 PLC でのノイズのシミュレーション結果は  $1\mu\text{V}_{\text{RMS}}$  未満です。

図 4-10. TIDA-010970 TINA-TI のシミュレーション回路図

図 4-11. 全入力範囲の TIDA-010970 の合計ノイズ

#### 4.4.3 ノイズ測定

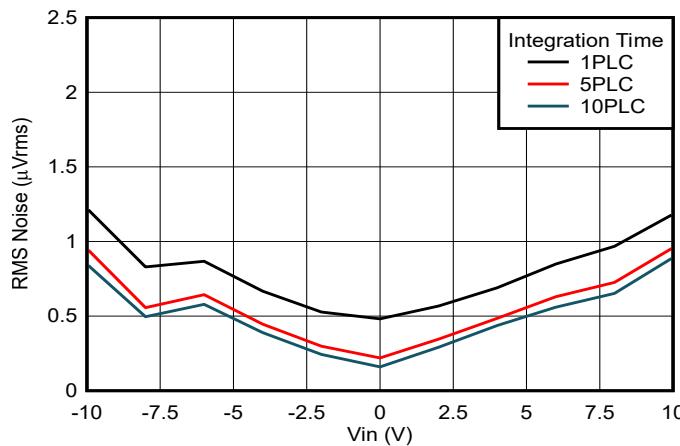

サンプリングされたデータからノイズも計算できます。1 PLC の RMS ノイズは、データが 60SPS で収集されているため、すべてのサンプルの標準偏差を取ることで計算できます。 $\pm 10V$  範囲の測定結果を図 4-12 に示します。

図 4-12.  $\pm 10V$  範囲の 1, 5, 10 PLC での RMS ノイズ

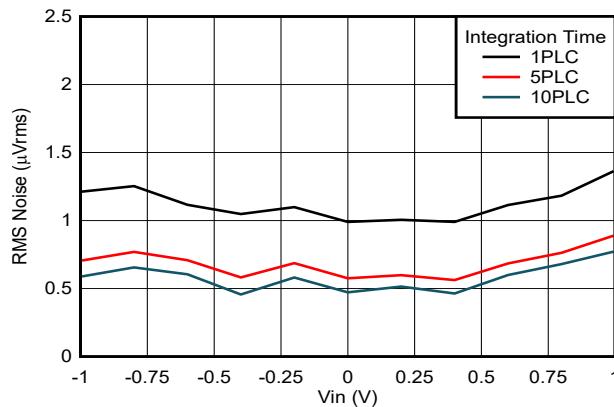

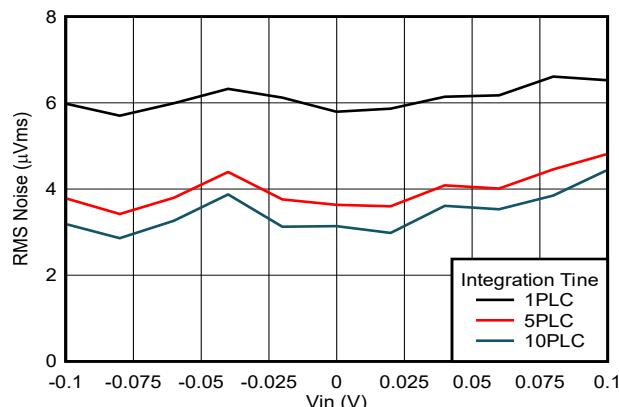

移動平均を取って、5 PLC または 10 PLC (それぞれ 5 ポイントと 10 ポイント) などより高いデータレートのノイズ測定値を取得します。移動平均は、データに Sinc1 フィルタを効果的に適用します。 $\pm 1V$  と  $\pm 100mV$  の結果については、図 4-12 も参照してください。

図 4-13.  $\pm 1V$  範囲の 1、5、10 PLC での RMS ノイズ

図 4-14.  $\pm 100mV$  範囲の 1、5、10 PLC での RMS ノイズ

表 4-5. TIDA-010970 ノイズの測定結果とシミュレーションとの関係

| 1 PLC でのノイズ      | $\pm 10V$ RANGE | $\pm 1V$ RANGE | $\pm 100mV$ RANGE |

|------------------|-----------------|----------------|-------------------|

| 測定ノイズ (短絡入力)     | $335nV_{RMS}$   | $547nV_{RMS}$  | $3.23\mu V_{RMS}$ |

| TINA-TI シミュレーション | $290nV_{RMS}$   | $337nV_{RMS}$  | $1.74\mu V_{RMS}$ |

#### 4.4.4まとめ

このリファレンス デザインには、以下の 3 つの設計目標があります。

- 複数の入力範囲への対応

- システムレベルのオンボード キャリブレーションの実現

- 低ノイズと線形性の高い性能の提示

この設計にはプログラマブル ゲイン アンプが搭載されており、ユーザーは  $\pm 10V$ 、 $\pm 1V$ 、 $\pm 100mV$  の範囲から選択できます。また、このリファレンス デザインにはオンボードの較正用線源である REF81 も採用されており、シグナル チェーン全体のキャリブレーションのための安定したリファレンス電圧を供給します。また、このデザインは低ノイズ、低 INL であり、 $\pm 10V$  範囲で  $335nV_{RMS}$  ノイズ、 $1.1ppm$  INL を測定できます。このような低ノイズおよび INL 測定と、安定した較正用線源および複数の入力範囲から、このリファレンス デザインは、DMM 電圧測定パスの設計において最適な選択肢です。

## 5 設計とドキュメントのサポート

### 5.1 デザイン ファイル

#### 5.1.1 回路図

回路図をダウンロードするには、[TIDA-010970](#) のデザイン ファイルを参照してください。

#### 5.1.2 BOM

部品表 (BOM) をダウンロードするには、[TIDA-010970](#) のデザイン ファイルを参照してください。

### 5.2 ツール

[ADS127L21 EVM ソフトウェア ユーザー イン](#) このリファレンス デザインは、ADS127L21 EVM 専用の GUI と組み合わせて使用することを意図しています。

### 5.3 ドキュメントのサポート

1. テキサス インスツルメンツ、[『REF81: 温度ドリフト 0.05ppm/°C、変動 1ppm 未満の安定性を示す温度制御型の高精度電圧リファレンス』データシート](#)

2. テキサス インスツルメンツ、[『ADS127L21B:512kSPS、高精度、24 ビット、広帯域幅デルタシグマ ADC』データシート](#)

3. テキサス インスツルメンツ、[『RES11A: マッチング済み、薄膜抵抗デバイダ、1kΩ 入力』データシート](#)

4. テキサス インスツルメンツ、[『RES21A-Q1: 車載用、マッチング済み、薄膜抵抗デバイダ、10kΩ 入力』データシート](#)

5. テキサス インスツルメンツ、[『ADS127L21EVM-PDK 評価基板ユーザー ガイド』](#)

### 5.4 サポート・リソース

テキサス・インスツルメンツ E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツルメンツの[使用条件](#)を参照してください。

### 5.5 商標

テキサス インスツルメンツの E2E™ and テキサス・インスツルメンツ E2E™ are trademarks of Texas Instruments. すべての商標は、それぞれの所有者に帰属します。

### 6 著者について

**MAGGIE LEE** は、テキサス インスツルメンツのシステム エンジニアであり、テストおよび測定アプリケーションのリファレンス デザイン開発を担当しています。Maggie は、カリフォルニア工科大学で電気工学の学士号 (B.S.) を取得しています。このリファレンス デザインをサポートしてくれた、KEITH NICHOLAS, LUIS CHIOYE, CARRIE STOLL, CARL SCHARRER に感謝します。

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月