# EVM User's Guide: PGA848EVM

## PGA848 評価基板

### 説明

PGA848 評価基板 (PGA848EVM) は、高精度、低ノイズ、広帯域幅プログラマブルゲイン計測アンプ (PGIA) である [PGA848](#) を評価するための開発プラットフォームです。PGA848 には、3 本のデジタル ゲイン選択ピンを使用して、減衰ゲインが 0.5V/V から最大 100V/V までの 8 つのディケイド (スコープ) ゲイン設定が備わっています。

### 設計を開始

1. PGA848EVM をご注文ください。

2. 製品仕様については、[PGA848 データシート](#)を参照してください。

3. ゲイン (V/V) を 8 つのオプション (0.5, 1, 2, 5, 10, 20, 50, 100) の間で構成します。

4. 電源、入力信号、出力機器を接続します。

### 特長

- シングルエンド出力への差動またはシングルエンド入力計測機器シグナルコンディショニング

- 入力段と出力段の電源を一緒に、または別個に使用するオプション

- デフォルトでオペアンプ バッファ経由で REF ピンを外部または中間出力段の電源に駆動するオプション

- PGA848 の入力と出力にノイズフィルタリングを柔軟に実装できるフットプリント

### アプリケーション

- 産業用オートメーション

- アナログ入力モジュール

- 高精度マルチファンクション入出力 (DAQ)

- 試験および測定機器

- パラメトリック測定ユニット (PMU)

## 1 評価基板の概要

### 1.1 はじめに

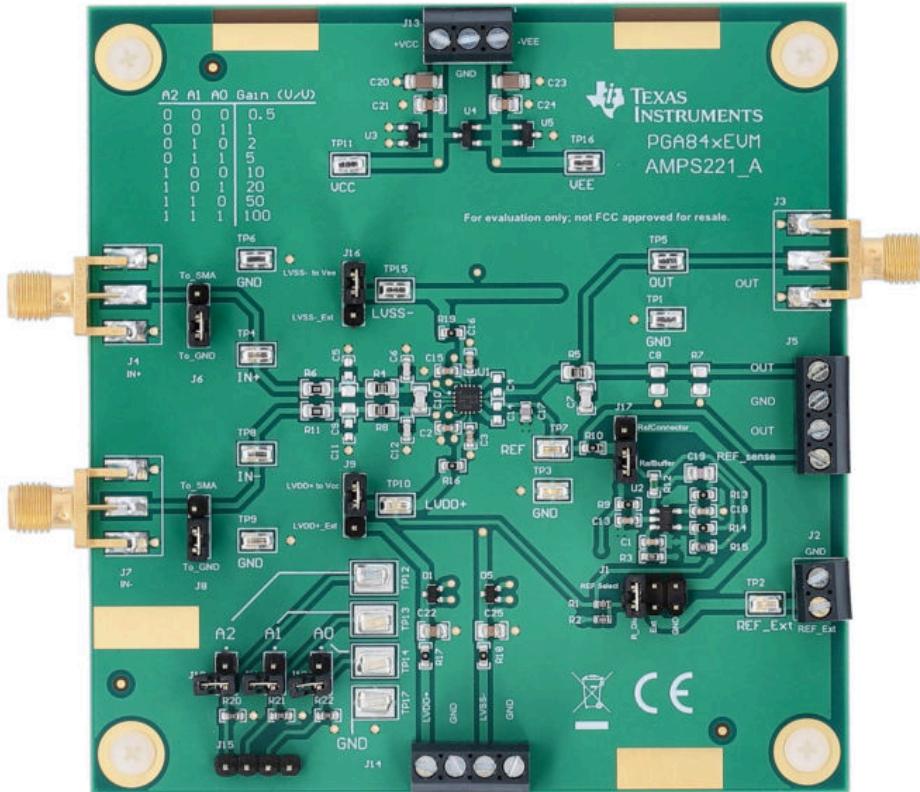

このユーザー ガイドには、PGA848EVM に関する情報とサポート資料が含まれてされています。PGA848EVM の回路の説明、ジャンパ設定、必要な接続、プリント基板 (PCB) のレイアウト、回路図、部品表が含まれます。このドキュメント全体を通して、評価ボード、評価基板、EVM という用語は PGA848EVM と同じものです。

### 1.2 静電放電に関する注意事項

#### 注意

PGA848EVM 上の部品の多くは、静電気放電 (ESD) による損傷を受けやすくなっています。評価基板の開梱および取り扱いの際は、認定された ESD ワークステーションで接地されたリストラップを使用するなど、ESD に関する適切な取り扱い上の注意に従っていただくことをお勧めします。

### 1.3 キットの内容

PGA848EVM は PGA848 を実装しているほか、電源、入力、出力に対応するコネクタも搭載しています。

**表 1-1. PGA848EVM キットの内容**

| 項目        | 説明  | 数量 |

|-----------|-----|----|

| PGA848EVM | PCB | 1  |

### 1.4 仕様

PGA848EVM は、PGA848RGTR デバイスの内外で信号を接続するメカニズムを実現しています。プリント基板 (PCB) のサイズは FR4 材料を使用した場合、3.75 インチ x 4.5 インチです。入出力段の電源、出力、REF ピンは、ねじ込み端子コネクタまたはテストポイント経由で利用できます。入出力信号は、SMA コネクタまたはテストポイント経由で利用できます。ゲインは、ジャンパ実装、または J15 ヘッダピン (MCU GPIO) により選択できます。

## 1.5 製品情報

PGA848 は、シングルエンド出力を備えた広帯域、高電圧、低ノイズのプログラム可能なゲイン計測アンプです。スーパーベータ入力トランジスタを使用することで、入力バイアス電流が小さくなり、その結果入力電流ノイズ密度が  $0.3\text{pA}/\sqrt{\text{Hz}}$  と小さくなるため、PGA848a は事実上あらゆる種類のセンサにとって汎用性の高い選択肢となります。入力には、電源電圧を  $\pm 40\text{V}$  上回る過電圧保護機能が内蔵されています。低ノイズの電流フィードバック フロントエンド アーキテクチャにより、高周波数でのゲイン平坦性が実現するため、PGA848 は、優れた高インピーダンスのセンサ読み出しデバイスとなります。

PGA849 は PGA848 と類似していますが、異なるゲインオプションが用意されています。PGA848 と PGA849 はピン互換であり、この評価基板はそのどちらでも使用できます。下表に、ジャンパとゲインの構成の概要を示します。

**表 1-2. PGA848 および PGA849 のゲインオプション (V/V)**

| A2 (J10) | A1 (J11) | A0 (J12) | PGA848 | PGA849 |

|----------|----------|----------|--------|--------|

| 0        | 0        | 0        | 0.5    | 0.125  |

| 0        | 0        | 1        | 1      | 0.25   |

| 0        | 1        | 0        | 2      | 0.5    |

| 0        | 1        | 1        | 5      | 1      |

| 1        | 0        | 0        | 10     | 2      |

| 1        | 0        | 1        | 20     | 4      |

| 1        | 1        | 0        | 50     | 8      |

| 1        | 1        | 1        | 100    | 16     |

## 1.6 高温表面警告

**警告**

大電流状況ではデバイスが高温になる可能性があります。評価基板を取り扱う際にはご注意ください。

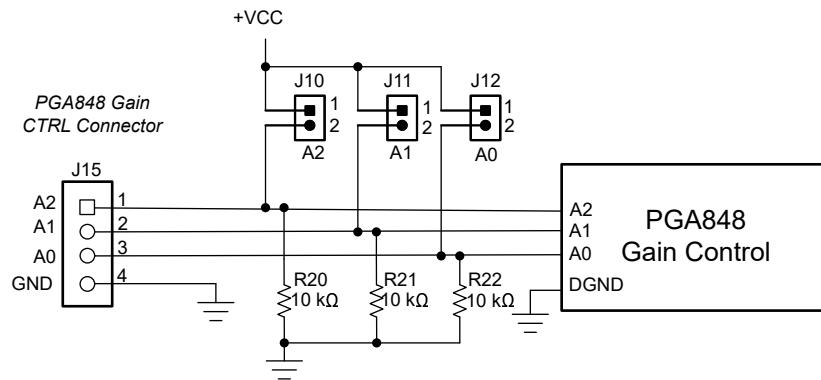

## 2 ハードウェア

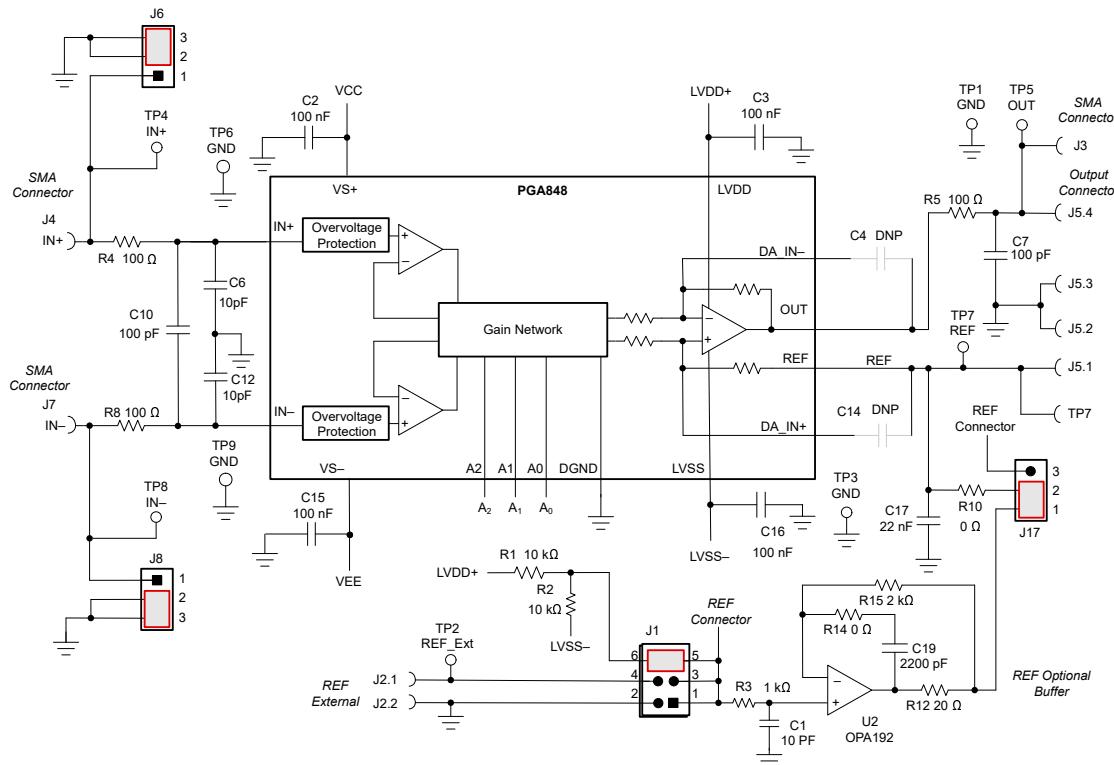

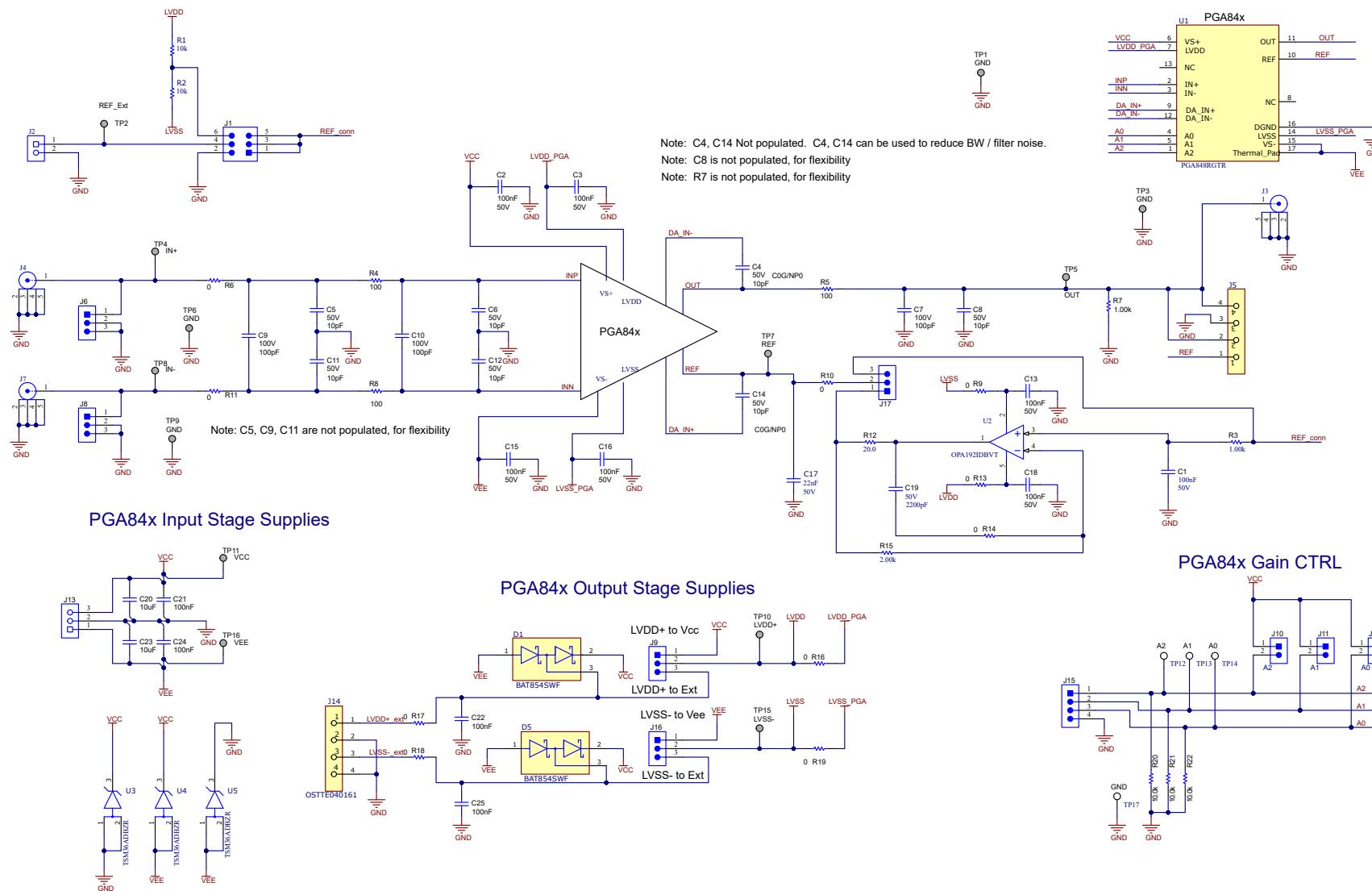

評価基板により、PGA848 デバイスの各種機能にアクセスし、このデバイスの性能を測定します。デフォルトでは、PGA848EVM のプログラマブルゲイン計測アンプは 0.5V/V のゲインに構成されています。この評価基板は、ジャンパ J10 (A2)、J11 (A1)、J12 (A0) を搭載し、PGA848 のゲインを設定できます。

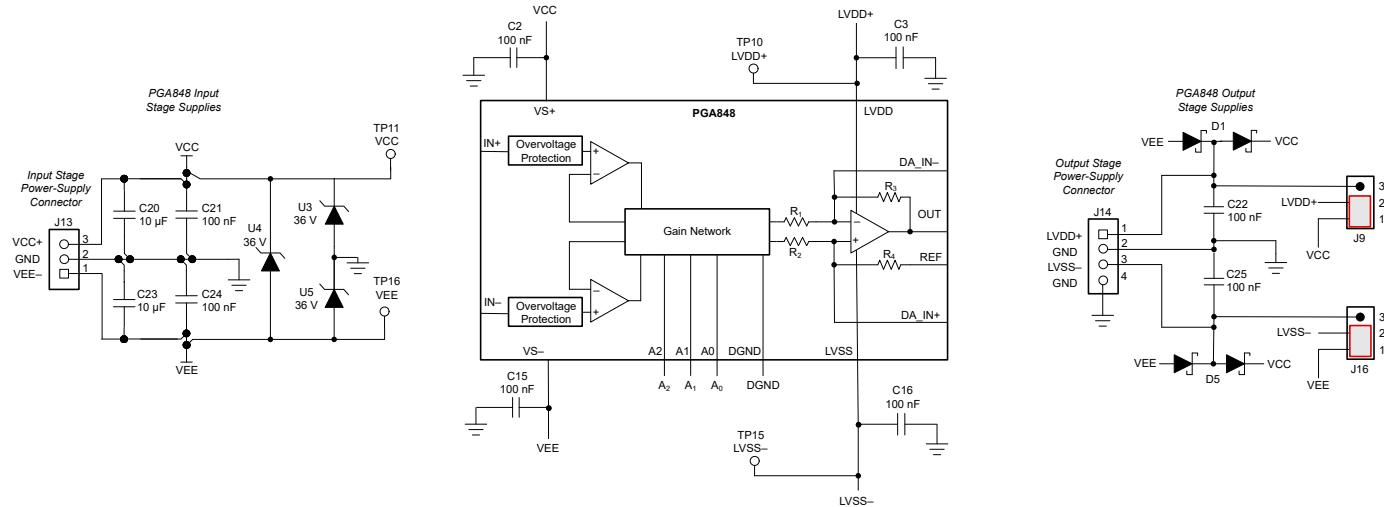

このデバイスでは、入力段と出力段という 2 組の電圧電源が使用されます。出力段の電源は入力段から分離されて PGA848 の出力振幅電圧レベルを制限し、ADC または下流側のデバイスをオーバードライブの損傷から保護します。入力段電源 VS+ と VS- には、コネクタ J13 を使用してアクセスできます。出力段電源 LVDD+ と LVSS- には、コネクタ J14 を使用してアクセスできます。選択可能なジャンパ J9 および J16 は、出力段の電源電圧レベルを、入力段電源 (デフォルト) と同じ値、またはコネクタ J14 を使用して外部電圧と同じ値に設定します。

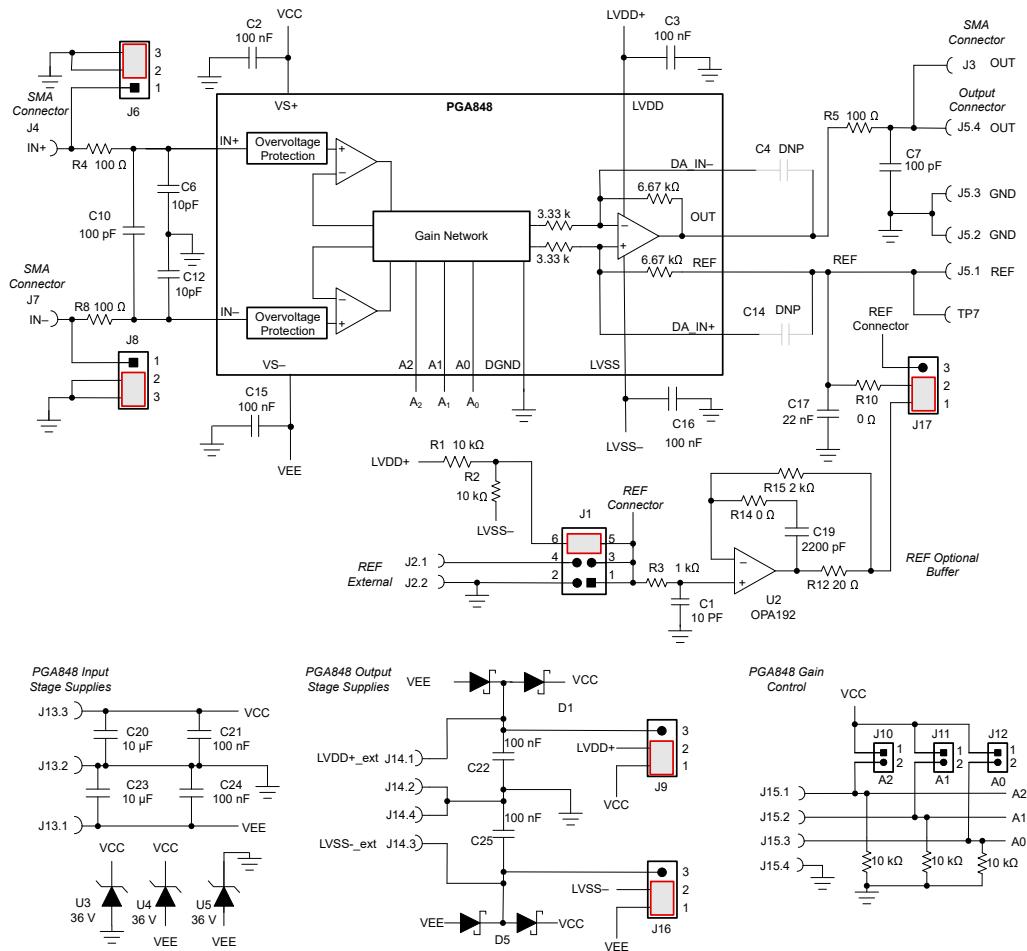

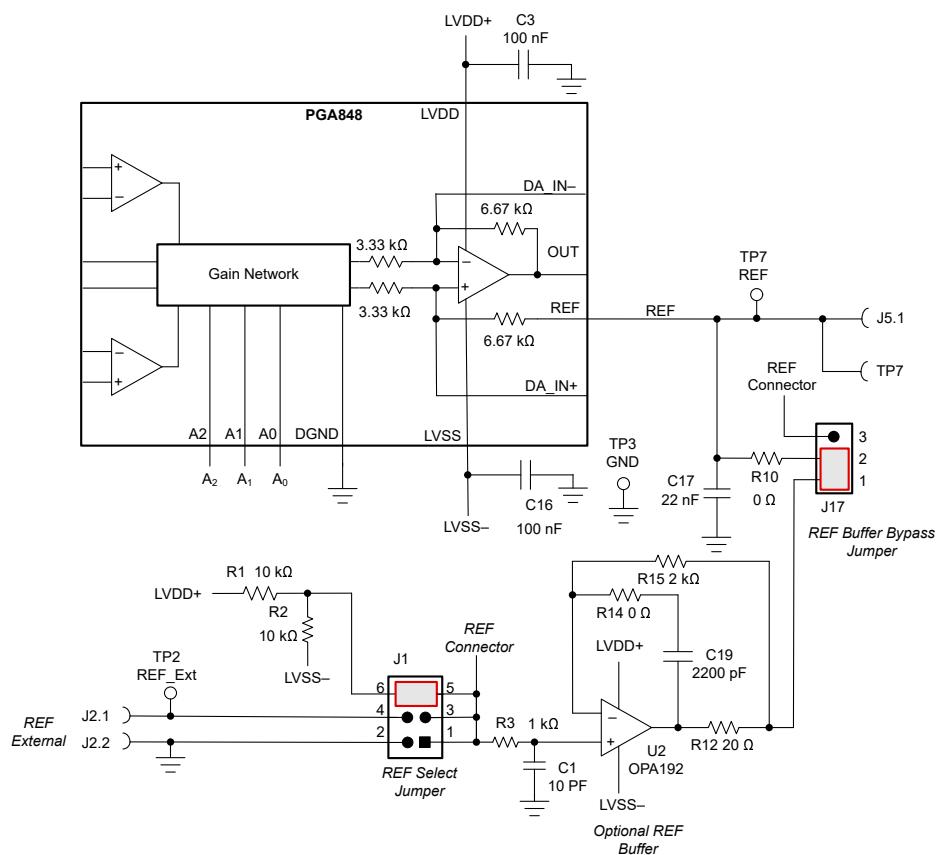

PGA848 には、シングルエンドまたは疑似差動入力 ADC とのインターフェイスを簡素化する機能が組み込まれています。REF ピンは、PGA848 の出力電圧の基準点を設定します。REF ピンは、低インピーダンス電源で駆動する必要があり、評価ボードには REF ピンを駆動するためのオプションのバッファ (U2) があります。選択可能なジャンパ J1 には、コネクタ J2 経由で REF ピンの電圧を外部から設定するオプション、または REF を GND に接続するオプション、または REF を PGA848 出力段電源 (LVDD+ および LVSS-) の中電圧値に設定するオプションがあります。PGA848EVM を使用すると、オプションのコンデンサ C4 と C14 を使用して、DA\_IN- と DA\_IN+ の各ピンにアクセスできます。これらのコンデンサは、PGA848 出力段差動アンプの内部抵抗と並列に配置されて、ノイズフィルタリングが実装されています。図 2-1 に、PGA848EVM 回路の概略ブロック図を示します。PGA848EVM の完全な回路図については、図 3-6 を参照してください。

図 2-1. PGA848EVM の概略回路図

## 2.1 セットアップおよび接続

## PGA848EVM の設定方法:

1. セクション 2.2 でのリファレンスジャンパ構成。

2. セクション 2.3 で説明するとおり、電源を接続します。

3. セクション 2.4 で説明するとおり、入力と出力を接続します。

4. セクション 2.5 に記載されているバイアス基準ピン。

5. ご希望に応じて、セクション 2.6 で説明するとおり、ゲインを動的に変更します。

6. 必要に応じて、セクション 2.7 を参照して基板に変更を適用します。

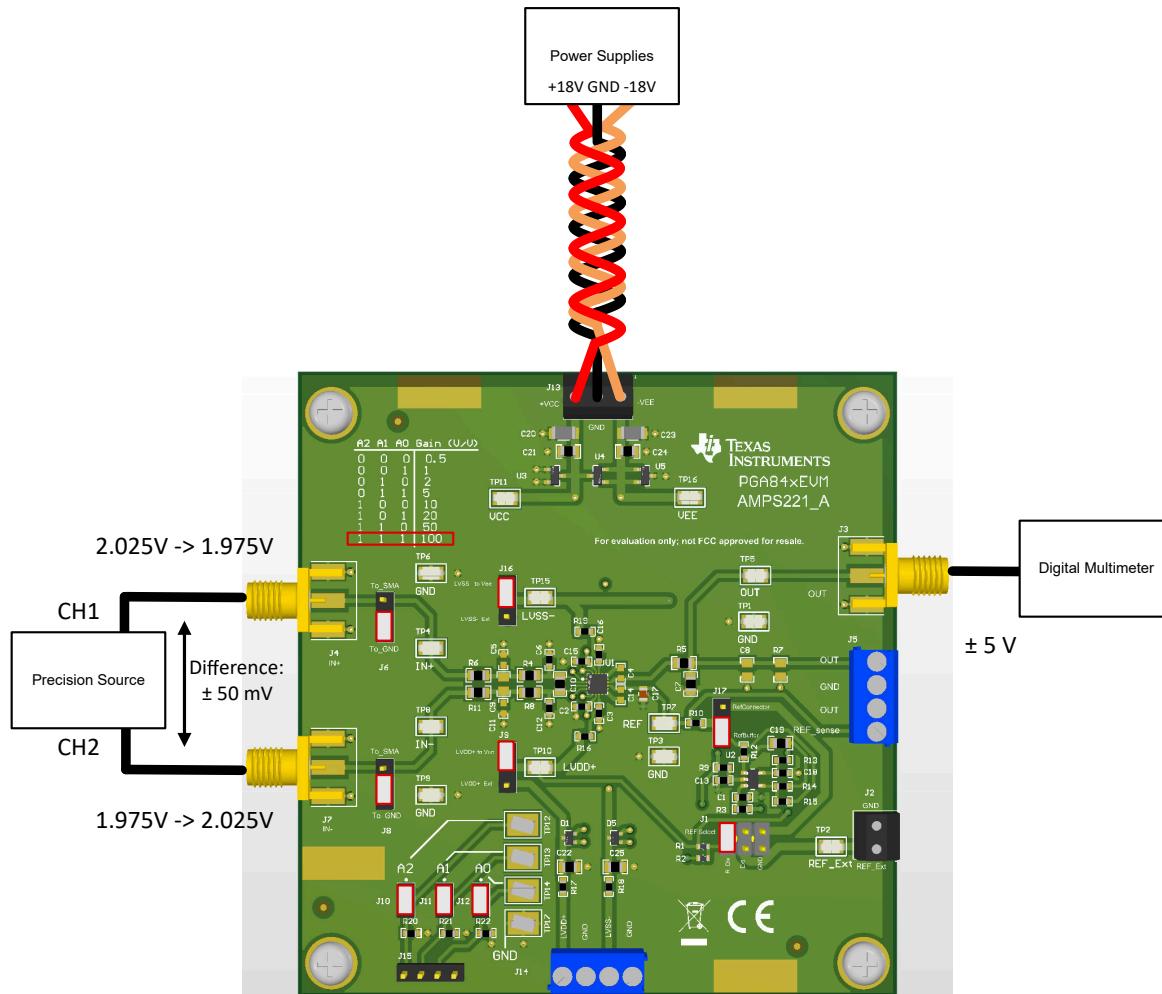

ハードウェアに変更を加えずに実行可能な基本機能テストを、図 2-2 に示します。すべてのゲインジャンパ (J10、J11、J12) を実装する必要があり、ゲインは 100 (A2:A0:111) になります。±18V 電源 (入力段および出力段) により、±15V の同相入力範囲と±17.6V の出力範囲に対応できます。以下の式に示す PGA848 の伝達関数を考慮に入れます。

$$OUT = G \times [(IN+) - (IN-)] + VREF \quad (1)$$

この例での入力の同相電圧は 2V、差動電圧は  $\pm 50\text{mV}$  です。REF は、出力電源の中電圧 (0V) に設定されます。ゲインが 100 の入力により、出力信号範囲が  $\pm 5\text{V}$  に設定されます。このテストで優れた精度を達成するには、低ノイズで高精度の入力ソースを使用する必要があります。

図 2-2. PGA848EVM の例

## 2.2 ジャンパ設定

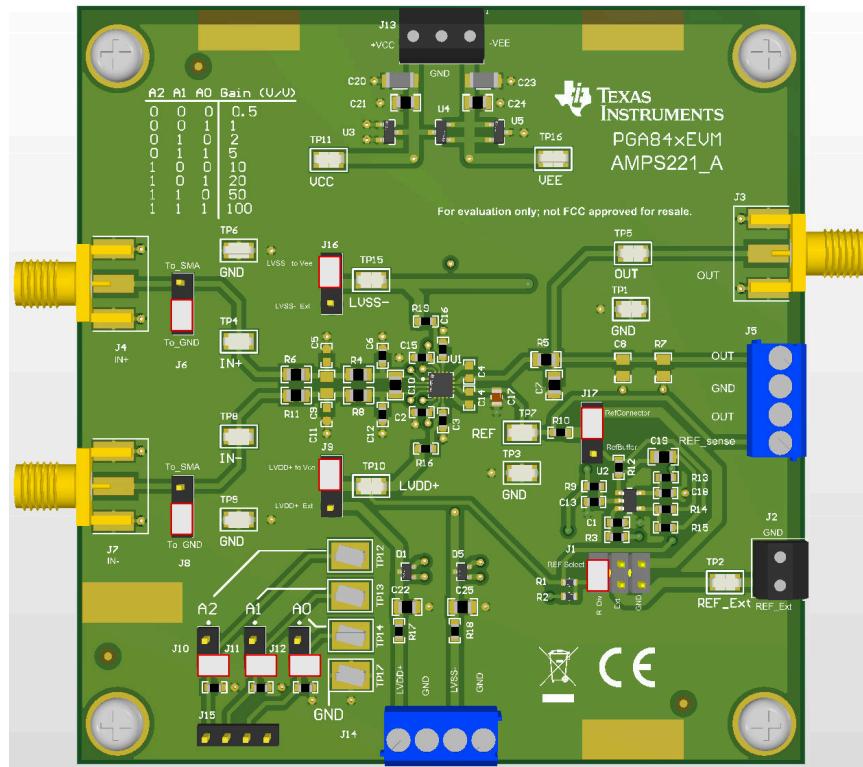

図 2-3 に、PGA848EVM でのデフォルトのジャンパ設定の詳細を示します。表 2-1 に、これらのジャンパの構成を明らかにしています。

図 2-3. PGA848EVM のデフォルトのジャンパ設定

表 2-1. デフォルトのジャンパ構成

| ジャンパ | 機能               | デフォルトの位置 | 説明                                                                                                      |

|------|------------------|----------|---------------------------------------------------------------------------------------------------------|

| J1   | REF 選択           | シャント 5-6 | シャント 5-6:REF を中間出力段電源 (R_DIV) に設定します<br>シャント 3-4:REF を外部に設定します。REF コネクタ J2<br>シャント 1-2:REF を GND に設定します |

| J17  | REF バッファ/コネクタ    | シャント 1-2 | シャント 1-2:REF ピンから REF バッファ (U2) 出力<br>シャント 2-3:REF コネクタ J2 への REF ピン                                    |

| J6   | 正 (非反転) 入力、IN+   | シャント 2-3 | シャント 2-3:SMA コネクタ J4 への入力信号<br>シャント 1-2:IN+ を GND に接続します                                                |

| J8   | 負 (反転) 入力、IN-    | シャント 2-3 | シャント 2-3:SMA コネクタ J7 への入力信号<br>シャント 1-2:IN- を GND に接続します                                                |

| J9   | LVDD+ 接続         | シャント 1-2 | シャント 1-2:出力段電源 LVDD+ を +VCC 電源に設定します<br>シャント 2-3:LVDD+ を外部コネクタ J14 のピン 1 に接続します                         |

| J16  | LVSS-接続          | シャント 1-2 | シャント 1-2:出力段電源を LVDD- から VEE 電源に設定します<br>シャント 2-3:LVDD- を外部コネクタ J14 ピン 3 に接続します                         |

| J10  | PGIA ゲイン CTRL A2 | オープン     | オープン:A2 を GND または 0 に設定します<br>シャント 1-2:A2 を VCC または 1 に設定します                                            |

| J11  | PGIA ゲイン CTRL A1 | オープン     | オープン:A1 を GND または 0 に設定します<br>シャント 1-2:A1 を VCC または 1 に設定します                                            |

| J12  | PGIA ゲイン CTRL A0 | オープン     | オープン:A0 を GND または 0 に設定します<br>シャント 1-2:A0 を VCC または 1 に設定します                                            |

## 2.3 電源接続

PGA848EVM では、入力段と出力段という 2 組の電圧電源を使用します。このデバイスは、 $\pm 4V$  (8V) ~  $\pm 18V$  (36V) の入力段電源と、 $\pm 2.25V$  (4.5V) ~  $\pm 18V$  (36V) の出力段電源を使用して動作します。出力段の電源電圧は、入力段の電源電圧を超えないようにする必要があります。

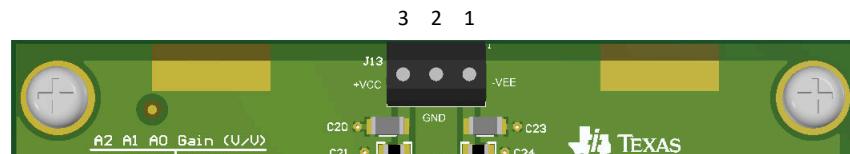

PGA848EVM の入力段の電源接続は、評価基板の上部にあるコネクタ J13 経由で実現しています。入力段の正の電源接続は +VCC とラベル付けされ、負の電源接続は -VEE とラベル付けされ、接地接続は GND とラベル付けされています。電源を PGA848EVM に接続するには、J13 の各端子に配線を挿入した後、ネジを締めて接続します。

図 2-4. 入力段電源コネクタ (J13)

表 2-2 に、電源コネクタ J13 のピン定義と、各電源接続で許容される電圧範囲の概要を示します。

表 2-2. PGA848EVM の電源電圧範囲仕様

| コネクタピン番号 | 電源接続           | 電圧レンジ                                                                         |

|----------|----------------|-------------------------------------------------------------------------------|

| J13.3    | 入力段の正電源 (+VCC) | 単一電源、 $V_S = +VCC$ : 8V ~ 36V<br>デュアル電源、 $V_S = (+VCC) - (-VEE)$ : 4V ~ 18V   |

| J13.2    | グランド           | 0V                                                                            |

| J13.1    | 負電源 (- VEE)    | 単一電源、 $V_S = +VCC$ : 0V (GND)<br>デュアル電源、 $V_S = (+VCC) - (-VEE)$ : -4V ~ -18V |

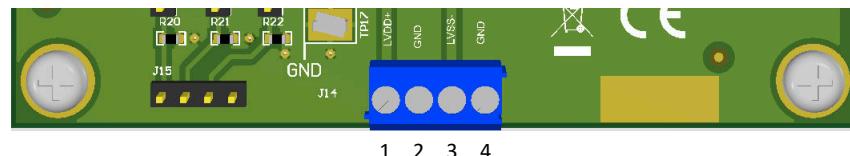

| J14.1    | LVDD+_ext      | 単一電源、LVDD+_ext: 4.5V ~ 36V<br>デュアル電源、出力段電源 (LVSS+) - (LVSS-): 2.25V ~ 18V     |

| J14.2    | グランド           | 0V                                                                            |

| J14.3    | LVSS-_ext      | 単一電源、LVSS-_ext: 0V (GND)<br>デュアル電源、出力段電源 (LVSS+) - (LVSS-): -2.25V ~ -18V     |

| J14.4    | グランド           | 0V                                                                            |

デフォルトでは、出力段電源電圧レベル (+LVDD および -LVSS) はそれぞれ PGA848 の正 (+VCC) 電源と負 (-VEE) 電源に設定されます。+LVDD ピンはジャンパ J9 1-2 経由で +VCC に接続され、-LVSS ピンは J16 1-2 経由で -VEE に接続されます。ねじ込み端子コネクタ J14 により、出力段の電源ピンにアクセスできます。外部電源を使用して LVDD と LVSS の電圧レベルを設定するには、ジャンパ J9 2-3 をシャントし、コネクタ J14.1 を使用して +LVDD にアクセスします。同様に、ジャンパ J16 2-3 をシャントして、コネクタ J14.3 を使用して -LVSS ピンにアクセスします。

図 2-5. 出力段電源コネクタ (J14)

図 2-6 に、PGA848EVM の電圧電源接続を示します。

図 2-6. PGA848EVM 電圧電源接続

## 2.4 アナログ入力接続と出力接続

PGA848EVM に対するプログラマブルアンプ入力信号接続は、評価基板の左側に配置している SMA コネクタ J4 (IN+)、J7 (IN-)、複数のテストポイント TP4 (IN+)、TP8 (IN-) を使用して実現します。REF 外部入力は、基板の右側にあるねじ込み端子コネクタ J2 によって供給されます。また、PGA848EVM は、基板の右側にあるねじ込み端子コネクタ J2.1 やテストポイント TP2 経由で REF ピンに直接アクセスすることもできます。

PGA848 の出力接続は、評価基板の右側にあるねじ込み端子コネクタ J5.4、SMA コネクタ J3、テストポイント TP5 を使用して実現します。図 2-7 に、PGA848EVM の入出力接続の概略図を示します。

図 2-7. PGA848EVM のアナログ入出力接続

表 2-3 に、入力および出力コネクタ、および対応するテストポイントの概要を示します。

表 2-3. PGA848EVM のアナログ入出力接続

| コネクタ指定子 | 信号                 | コメント | テスト ポイント |

|---------|--------------------|------|----------|

| J4      | IN+                | SMA  | TP4      |

| J7      | IN-                | SMA  | TP8      |

| J3      | OUT                | SMA  | TP3      |

| J5.4    | OUT                | ねじ端子 | TP3      |

| J5.3    | GND                | ねじ端子 | TP2      |

| J5.2    | GND                | ねじ端子 | TP9      |

| J5.1    | REF ピン / REF_sense | ねじ端子 | TP7      |

| J2.1    | REF_Ext            | ねじ端子 | TP2      |

| J2.2    | GND                | ねじ端子 | 該当なし     |

## 2.5 リファレンス入力

PGA848 の出力電圧は、基準ピン REF の電圧を基準にして開発されています。REF ピンを使用して、出力信号を精密に中点電源電圧レベルにオフセットします。通常、このオフセットは、出力段電源の中電圧レベルに設定されます。このレベルシフトを達成するには、PGA848 が単一電源の ADC を駆動するように、電圧源を REF ピンに接続して出力をレベルシフトする必要があります。デュアル電源動作では、通常、REF ピンを低インピーダンスのシステム接地に接続します。

基準ピンに印加される電圧源により、出力インピーダンスを低くする必要があります。基準ピンでの抵抗は、内部の  $6.67\text{k}\Omega$  抵抗と直列で、内部差動アンプの 4 つの抵抗に不均衡が生じます。PGA848EVM は、OPA192 オペアンプ (U2) 経由で、オプションの基準電圧バッファを実現します。外部基準電圧源で REF ピンを駆動する際、このバッファは低インピーダンスのパスを実現します。

評価基板のコネクタ J2.1 を使用して、外部基準電圧源にアクセスできます。最高の性能を得るために、外部ソースで REF ピンを駆動する場合は、低ノイズ、低ドリフトの高精度基準電圧を使用してください。バッファを外部基準電圧源に接続するには、J2 の各端子に配線を挿入した後、ネジを締めて接続します。バッファをバイパスし、REF ピンに直接アクセスするには、ジャンパ J17 2-3 をシャントします。

デフォルトでは、バッファは REF ピンを駆動し、基準電圧は出力段電源の中電圧レベルに設定されています。ジャンパ J17 はシャントピン 1-2 に、ジャンパ J1 はシャントピン 5-6 に設定されます。図 2-8 に、REF 入力接続とオプションの REF バッファを示します。

図 2-8. PGA848EVM リファレンス入力およびオプションのバッファ

### 注

オプションの REF バッファ (U2) を使用する場合、REF 入力信号によりオペアンプ電源電圧の上下にヘッドルームが許容される必要があります。良好な OPA192 出力スイングの線形範囲内に維持するには、(LVSS-)  $+ 300\text{mV} < \text{REF}_{\text{ext}} < (\text{LVDD}+) - 300\text{mV}$  の範囲内の基準入力電圧を使用します。オペアンプの線形範囲を超えると、PGA848 回路の直線性性能が低下します。

## 2.6 デジタル入力ピンとゲイン制御

PGA848 には、減衰ゲイン 0.5V/V から最大 100V/V までの 8 つのディケイド (スコープ) ゲイン設定が備わっています。ゲインは、次の 3 本のデジタル選択ピンで制御されます。A2、A1 および A0。デフォルトでは、PGA848 は約 0.5V/V のゲインに構成されています。

この評価ボードは、シャントジャンパ J10、J11、J12 を搭載しており、PGA848 のゲイン制御選択ピンを設定できます。[表 2-4](#) に、ゲイン制御オプションの一覧を示します。ゲイン制御ピンを High に設定するには、シャントを対応するジャンパに取り付けます。ゲイン制御ピンを Low に設定するには、シャントジャンパを取り外します。

**表 2-4. PGA848EVM ゲイン制御**

| A2<br>ジャンパ J10<br>コネクタ J15.1 | A1<br>ジャンパ J11<br>コネクタ J15.2 | A0<br>ジャンパ J12<br>コネクタ J15.3 | PGA848 ゲイン (V/V) |

|------------------------------|------------------------------|------------------------------|------------------|

| 0 (オープン)                     | 0 (オープン)                     | 0 (オープン)                     | 0.5              |

| 0 (オープン)                     | 0 (オープン)                     | 1 (シャント)                     | 1                |

| 0 (オープン)                     | 1 (シャント)                     | 0 (オープン)                     | 2                |

| 0 (オープン)                     | 1 (シャント)                     | 1 (シャント)                     | 5                |

| 1 (シャント)                     | 0 (オープン)                     | 0 (オープン)                     | 10               |

| 1 (シャント)                     | 0 (オープン)                     | 1 (シャント)                     | 20               |

| 1 (シャント)                     | 1 (シャント)                     | 0 (オープン)                     | 50               |

| 1 (シャント)                     | 1 (シャント)                     | 1 (シャント)                     | 100              |

あるいは、A2、A1、A0 のデジタルピンをコネクタ J15 を介して外部から駆動することもできます。外部ソースで駆動されていないピン、またはオープンのままにしているシャントは、プルダウン抵抗を使用して DGND でバイアスされます。[図 2-9](#) はゲイン設定ブロック図を示しています。

**図 2-9. PGA848EVM ゲイン制御**

## 2.7 変更点

フレキシビリティを高めるために、この評価基板はオプションのコンデンサ C4 と C14 を搭載しています。これらのコンデンサには PGA848 出力段差動アンプ内部抵抗 (6.67kΩ) と並列に配置され、ノイズフィルタリングが実装されています。ノイズフィルタリングを実装するには、アプリケーションで目的の周波数 ( $f_{oi}$ ) を設定し、帰還コンデンサを計算します。 $f_{oi}$  が 1kHz の場合の例では、C4 と C14 に実装されたコンデンサは 2.2nF (C0G NP0) コンデンサです。

$$C_4 \text{ and } C_{14} = \frac{1}{2\pi \times 6.67\text{k}\Omega \times 10 \times f_{oi}} = \frac{1}{2\pi \times 6.67 \text{ k}\Omega \times 10 \times 1 \text{ kHz}} = 2.39\text{nF} \approx 2.2\text{nF} \quad (2)$$

また、この評価ボードは、オプションの入力ローパスフィルタに対応できるフットプリント R6、R11、C9、C5、C11 と、負荷抵抗 R7 のフットプリントを実現しています。

同相コンデンサ (C5 と C11) は、別のコンデンサと等しく、入力直列抵抗 (R6 と R11) は互いに等しくする必要があります。差動コンデンサ (C9) は、同相コンデンサの 10 倍大きくする必要があります。

$$f_{CM} = \frac{1}{2\pi \times R_{IN} \times C_{CM}} = \frac{1}{2\pi \times R6 \times C5} \quad (3)$$

$$f_{Diff} = \frac{1}{2\pi \times 2R_{IN} \times (C_{DIFF} + C_{CM}/2)} = \frac{1}{4\pi \times R6 \times (C9 + C5/2)} \quad (4)$$

レイアウトでのこれらの追加部品フットプリントにより、ユーザーは評価回路をカスタマイズできます。PGA848EVM の完全な回路図については、[図 3-6](#) を参照してください。

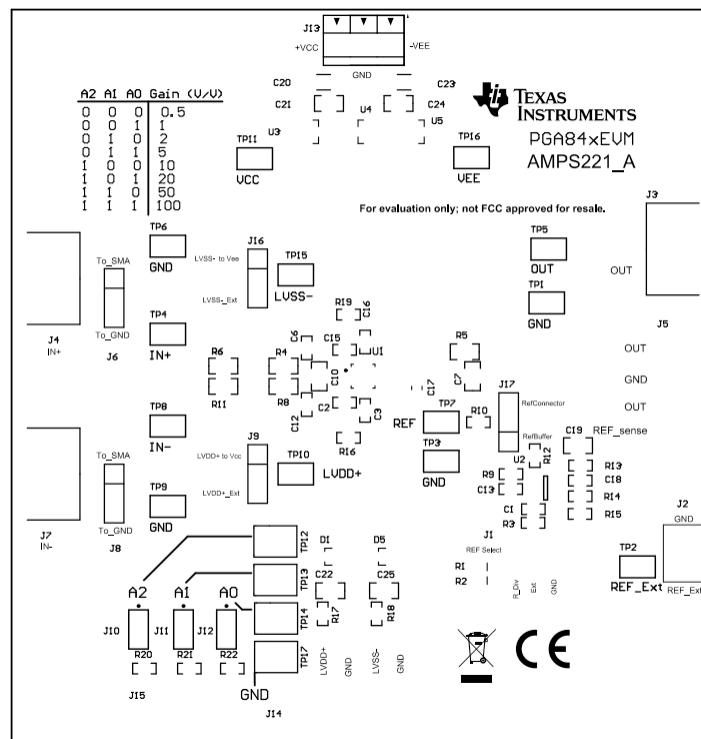

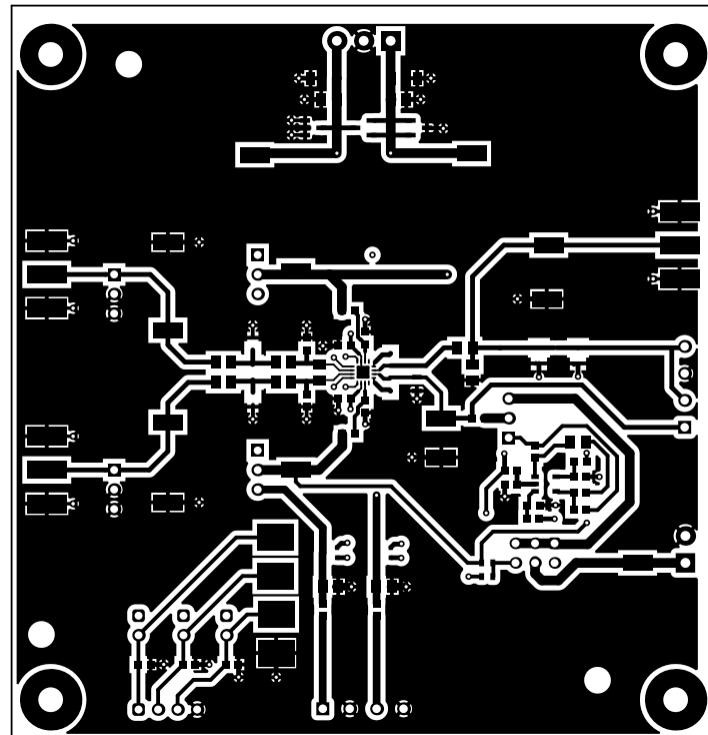

### 3 ハードウェア設計ファイル

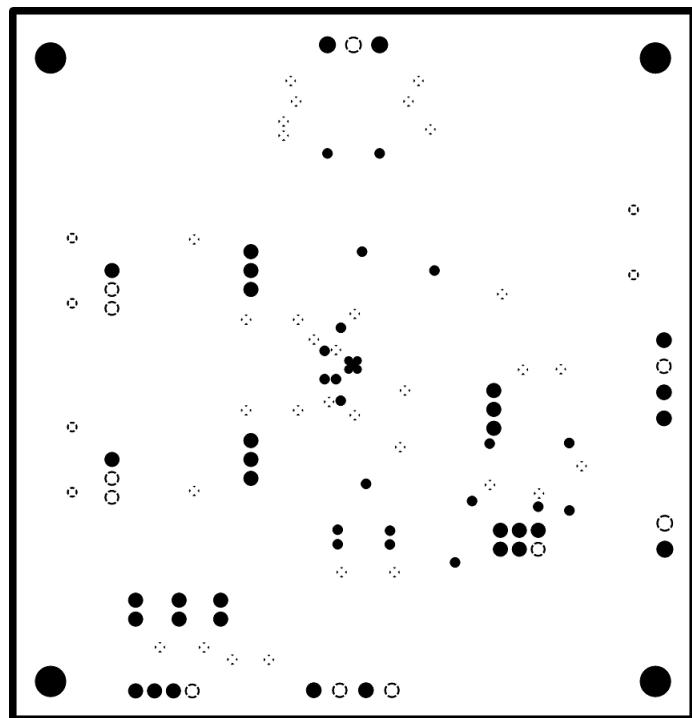

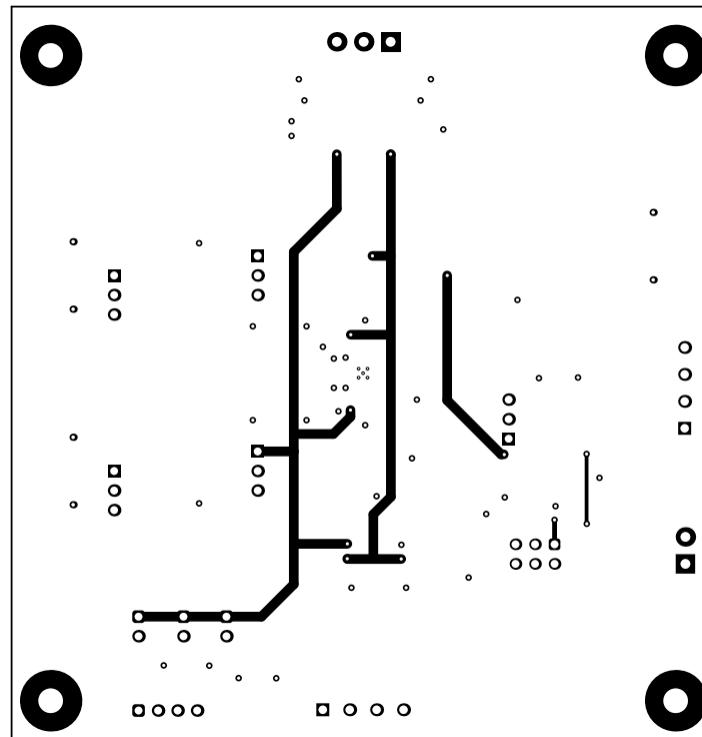

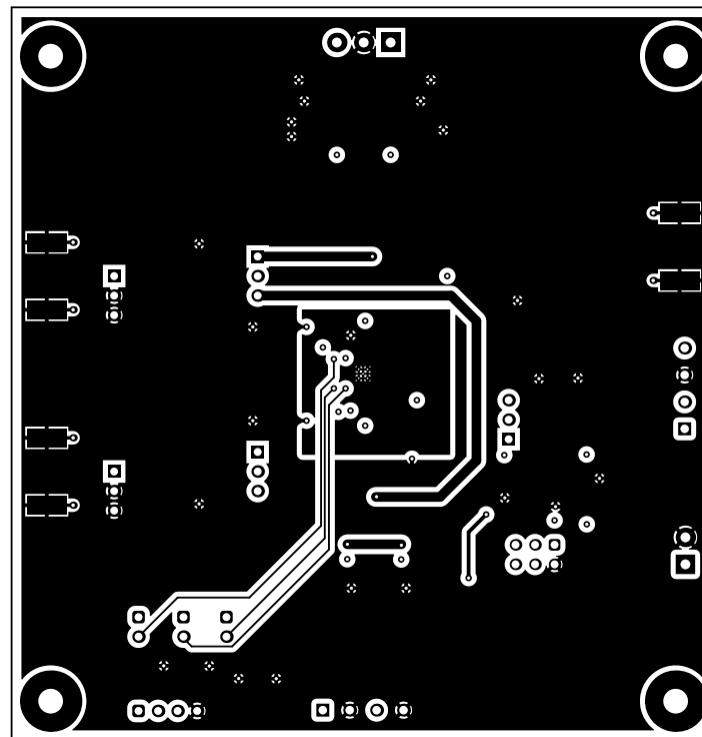

#### 3.1 PCB レイアウト

PGA848EVM は 4 層 PCB 設計仕様です。図 3-1～図 3-5 に、PCB 層の図を示します。最上層はすべての信号パスのトレースで構成されており、ソリッド グランド プレーンで注入されています。対称的な基板レイアウトを差動入力で使用して、優れた性能マッチングを維持し、同相ノイズ除去を改善します。正と負の両方の経路については、可能な限り対称にトレースを配線します。オプションの差動入力ローパス フィルタ コンデンサは、外部ノイズを低減するため、PGIA 入力のすぐ近くに配置しています。コンデンサ C17 は、ノイズの注入を回避するため、REF ピンに近接して配置しています。デカップリング コンデンサ C2、C15、C3、C16 は、このデバイスの電源ピンにできるだけ近い上層に配置しています。2 つ目の内部層は、専用のソリッド GND プレーンです。リファレンスピンに印加される電圧ソースは、出力インピーダンスを低くする必要があります。REF ピンの抵抗は、内部の  $6.67\text{k}\Omega$  抵抗と直列で、内部差動アンプの 4 つの抵抗に不均衡が生じます。オプションの OPA192 バッファ (U2) は、REF ピンの近くに配置して、REF ピンの直列抵抗を最小限に抑えます。すべての部品の接地接続に独立したビアを配置して、接地への低インピーダンスパスを実現します。3 番目の内部層と下層により、入力段の電源接続と出力段の電源接続を配線します。

図 3-1. 上面オーバーレイ PCB レイアウト

図 3-2. 最上層 PCB レイアウト

図 3-3. 接地層 PCB レイアウト

図 3-4. 電源層 PCB レイアウト

図 3-5. 最下層 PCB レイアウト

### 3.2 回路図

図 3-6 に、評価基板回路図を示します。

注:DNP コンポーネントは実装されていません。

図 3-6. PGA848EVM の回路図

### 3.3 部品表

表 3-1 に、PGA848EVM の部品表 (BOM) を示します。

**表 3-1. PGA848EVM 部品表**

| 記号                    | 数量 | 値      | 説明                                                       | パッケージ記号           | 部品番号                | メーカー                        |

|-----------------------|----|--------|----------------------------------------------------------|-------------------|---------------------|-----------------------------|

| !PCB1                 | 1  |        | プリント基板                                                   |                   | AMPS221             | 任意                          |

| C6、C12                | 2  | 10pF   | コンデンサ、セラミック、10pF、50V、± 1%、C0G/NP0、0603                   | 0603              | C0603C100F5GAC7867  | Kemet                       |

| C1                    | 1  | 0.1uF  | コンデンサ、セラミック、0.1uF、50V、±10%、C0G/Np0、0603                  | 0603              | C0603C104K5RACTU    | Kemet                       |

| C2、C3、C13、C15、C16、C18 | 6  | 0.1uF  | コンデンサ、セラミック、0.1μF、50V、± 5%、X7R、0603                      | 0603              | C0603C104J5RACTU    | Kemet                       |

| C7、C10                | 2  | 100pF  | コンデンサ、セラミック、100pF、100V、± 5%、C0G/NP0、0805                 | 0805              | C0805C101J1GACTU    | Kemet                       |

| C17                   | 1  | 22nF   | キヤップセラミック 22nF 50V C0G ±5% SMD 0805 +125°C エンボス T/R      | 0805              | GRT21B5C1H223JA02L  | Murata (村田製作所)              |

| C19                   | 1  | 2200pF | コンデンサ、セラミック、2200pF、50V、± 5%、C0G/NP0、0805                 | 0805              | 08055A222JAT2A      | AVX                         |

| C20、C23               | 2  | 10uF   | CAP、CERM、10uF、35V、+/- 10%、X7R、1206                       | 1206              | C3216X7R1V106K160AC | TDK                         |

| C21、C22、C24、C25       | 4  | 0.1uF  | コンデンサ、セラミック、0.1μF、50V、± 10%、X7R、0805                     | 0805              | 08055C104KAT2A      | AVX                         |

| D1、D5                 | 2  |        | ダイオードアレイ 1 対直列接続ショットキー 40V 200mA (DC) 表面実装 SC-70、SOT-323 | SOT-323           | BAT854SWF           | Nexperia                    |

| H1、H2、H3、H4           | 4  |        | 小ねじ、丸、#4-40x 1/4、ナイロン、十字穴付きなべ                            | ねじ                | NY PMS 440 0025 PH  | B&F Fastener Supply         |

| H5、H6、H7、H8           | 4  |        | スタンドオフ、六角、0.5 インチ L#4-40 ナイロン                            | スタンドオフ            | 1902C               | Keystone                    |

| J1                    | 1  |        | ヘッダ、2.54mm、3x2、金、TH                                      | ヘッダ、2.54mm、3x2、TH | TSW-103-08G-D       | Samtec                      |

| J2                    | 1  |        | 端子台、3.5mm ピッチ、2x1、TH                                     | 7.0x8.2x6.5mm     | ED555/2DS           | On-Shore Technology         |

| J3、J4、J7              | 3  |        | コネクタ、エンド ローンチ SMA、50Ω、SMT                                | エンド ローンチ SMA      | 142-0701-801        | Cinch の接続                   |

| J5、J14                | 2  |        | 端子台 3.5mm VERT 4POS PCB                                  | HDR4              | OSTTE040161         | On-Shore Technology         |

| J6、J8、J9、J16、J17      | 5  |        | ヘッダ、100mil、3x1、金、TH                                      | PBC03SAAN         | PBC03SAAN           | Sullins Connector Solutions |

| J10、J11、J12           | 3  |        | ヘッダ、100mil、2x1、金、TH                                      | 2x1 ヘッダ           | TSW-102-07G-S       | Samtec                      |

| J13                   | 1  |        | 端子台、3.5mm ピッチ、3x1、TH                                     | 10.5x8.2x6.5mm    | ED555/3DS           | On-Shore Technology         |

表 3-1. PGA848EVM 部品表 (続き)

| 記号                                                                  | 数量 | 値     | 説明                                                                                                                           | パッケージ記号               | 部品番号               | メーカー                        |

|---------------------------------------------------------------------|----|-------|------------------------------------------------------------------------------------------------------------------------------|-----------------------|--------------------|-----------------------------|

| J15                                                                 | 1  |       | ヘッダ、100mil、4x1、金、TH                                                                                                          | 10.5x8.2x6.5mm        | TSW-104-07G-S      | Samtec                      |

| R1、R2                                                               | 2  | 10k   | Res 厚膜 0603 10K 0.1% 1/10W±10ppm/°C 成形 SMD パンチ キャリア T/R                                                                      | 0603                  | ERA-3ARB103V       | Panasonic                   |

| R3                                                                  | 1  | 1.00k | RES、1.00k、0.1%、0.1W、0603                                                                                                     | 0603                  | RT0603BRD071KL     | Yageo America               |

| R4、R5、R8                                                            | 3  | 100   | RES、100、0.1%、0.125W、0805                                                                                                     | 0805                  | RT0805BRD07100RL   | Yageo America               |

| R6、R11                                                              | 2  | 0     | RES、0、5%、0.125W、AEC-Q200 グレード 0、0805                                                                                         | 0805                  | ERJ-6GEY0R00V      | Panasonic                   |

| R9、R10、R13、R14、<br>R16、R17、R18、R19                                  | 8  | 0     | RES、0、5%、0.1 W、0603                                                                                                          | 0603                  | RC0603JR-070RL     | Yageo                       |

| R12                                                                 | 1  | 20    | RES、20.0、0.1%、0.1W、0603                                                                                                      | 0603                  | RT0603BRD0720RL    | Yageo America               |

| R15                                                                 | 1  | 2.00k | RES、2.00k、0.1%、0.1W、0603                                                                                                     | 0603                  | RT0603BRD072KL     | Yageo America               |

| R20、R21、R22                                                         | 3  | 10.0k | RES、10.0k、1%、0.1W、0603                                                                                                       | 0603                  | RCG060310K0FKEA    | ヴィシエイ・ドラロック                 |

| SH-J0、SH-J1、SH-J2、<br>SH-J3、SH-J4、SH-J5、<br>SH-J6、SH-J7、SH-J8       | 9  | 1x2   | シャント、100mil、フラッシュ ゴールド、黒                                                                                                     | クローズド トップ 100mil シャント | SPC02SYAN          | Sullins Connector Solutions |

| TP1、TP2、TP3、TP4、<br>TP5、TP6、TP7、TP8、<br>TP9、TP10、TP11、<br>TP15、TP16 | 13 |       | テスト ポイント、ミニチュア、SMT                                                                                                           | テスト ポイント、ミニチュア、SMT    | 5019               | Keystone                    |

| U1                                                                  | 1  |       | 低ノイズ、広帯域、高精度プログラマブル ゲイン計測アンプ                                                                                                 | VQFN16                | PGA848RGTR         | テキサス・インスツルメンツ               |

| U2                                                                  | 1  |       | 高精度、レールツーレール入出力、低オフセット電圧、E-trim 搭載低入力バイアス電流オペアンプ、4.5V～36V、-40°C～125°C、8 ピン SOT-23 (DBV)、グリーン (RoHS 準拠、Sb/Br 非含有)、テープ アンド リール | DBV0005A              | OPA192IDBV7        | テキサス・インスツルメンツ               |

| U3、U4、U5                                                            | 3  |       | SOT-23 パッケージのサージ保護デバイス                                                                                                       | SOT23-3               | TSM36ADBZR         | テキサス・インスツルメンツ               |

| C4、C5、C11、C14                                                       | 0  | 10pF  | コンデンサ、セラミック、10pF、50V、±1%、C0G/NPO、0603                                                                                        | 0603                  | C0603C100F5GAC7867 | Kemet                       |

| C8                                                                  | 0  | 10pF  | コンデンサ、セラミック、10pF、50V、± 5%、C0G/NPO、0805                                                                                       | 0805                  | 08055A100JAT2A     | AVX                         |

| C9                                                                  | 0  | 100pF | コンデンサ、セラミック、100pF、100V、±5%、C0G/NPO、0805                                                                                      | 0805                  | C0805C101J1GACTU   | Kemet                       |

表 3-1. PGA848EVM 部品表 (続き)

| 記号 | 数量 | 値  | 説明                                               | パッケージ記号 | 部品番号          | メーカー      |

|----|----|----|--------------------------------------------------|---------|---------------|-----------|

| R7 | 0  | 1k | RES, 1.00k, 1%, 0.125W, AEC-Q200 グレード 0,<br>0805 | 0805    | ERJ-6ENF1001V | Panasonic |

## 4 追加情報

### 4.1 商標

すべての商標は、それぞれの所有者に帰属します。

### 5 関連資料

本文書には、PGA848EVM のアセンブリに使用されているテキサス インスツルメンツの IC に関する情報が記載されています。このユーザー ガイドは、TI の Web サイト (資料番号 SLVUDF7) から入手できます。資料番号に付記されている文字は、本文書の作成時点における当該文書の改訂版を示しています。

**表 5-1. 関連資料**

| デバイス      | 資料番号    |

|-----------|---------|

| PGA848    | SBOSAN4 |

| PGA849    | SBOSAG3 |

| PGA849EVM | SBOU315 |

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月