## Design Guide: TIDA-060031

## Hi-Fi アプリケーション向けプレミアムオーディオ高精度 DAC のリファレンス デザイン

## 説明

DAC11001 オーディオ リファレンス デザインは、DAC11001A と DAC11001B を搭載した比類のない包括的なオーディオ デザインです。DAC11001 は、20 ビットの低ノイズで超高性能な精密 R-2R D/A コンバータ (DAC) です。オーディオ アプリケーションで最も一般的に使用される DAC はデルタシグマ変調器です。精密 R-2R 型 DAC は特定のオーディオ要件に応じた追加の設計考慮が必要なため、一般的にはオーディオ アプリケーションにはあまり用いられません。このリファレンス デザインでは、Hi-Fi オーディオを対象とした動的信号生成における、精密 R-2R DAC の強みと制約を示しています。

## リソース

|             |            |

|-------------|------------|

| TIDA-060031 | デザイン フォルダ  |

| DAC11001A   | プロダクト フォルダ |

| DAC11001B   | プロダクト フォルダ |

| OPA1656     | プロダクト フォルダ |

| OPA1622     | プロダクト フォルダ |

## 特長

- オーディオ生成向けの 20 ビット精密 R-2R DAC

- 2.1V<sub>RMS</sub> ラインレベル出力、108dB の全高調波歪みおよびノイズ (THD+N)

- 低ノイズ出力バッファ

- 高帯域幅のリファレンス バッファ

- USB および TOSLINK® 光入力

- I2S からシリアル ペリフェラル インターフェイス (SPI) への変換

## アプリケーション

- AV レシーバ

- ストリーミング メディア プレーヤ

- サウンドバー

- 車載用 ヘッド ユニット

テキサス・インスツルメンツの™ E2E サポート エキスパートにお問い合わせください。

## 1 システムの説明

### 1.1 主なシステム仕様

表 1-1. 主なシステム仕様

| パラメータ      | DAC11001A                     | DAC11001B                     | 詳細                          |

|------------|-------------------------------|-------------------------------|-----------------------------|

| THD+N      | 108dB                         | 111dB                         | <a href="#">セクション 3.3.2</a> |

| ダイナミックレンジ  | 119dB                         | 119dB                         | <a href="#">セクション 3.3.4</a> |

| SNR        | 121dB                         | 121dB                         | <a href="#">セクション 3.3.6</a> |

| アイドル時のノイズ  | $1.9\mu\text{V}_{\text{RMS}}$ | $1.9\mu\text{V}_{\text{RMS}}$ | <a href="#">セクション 3.3.6</a> |

| ライン出力振幅    | $2.1\text{V}_{\text{RMS}}$    | $2.1\text{V}_{\text{RMS}}$    | <a href="#">セクション 3.3.6</a> |

| ヘッドフォン出力振幅 | 480mV <sub>RMS</sub>          | 480mV <sub>RMS</sub>          | <a href="#">セクション 3.3.2</a> |

## 2 システム概要

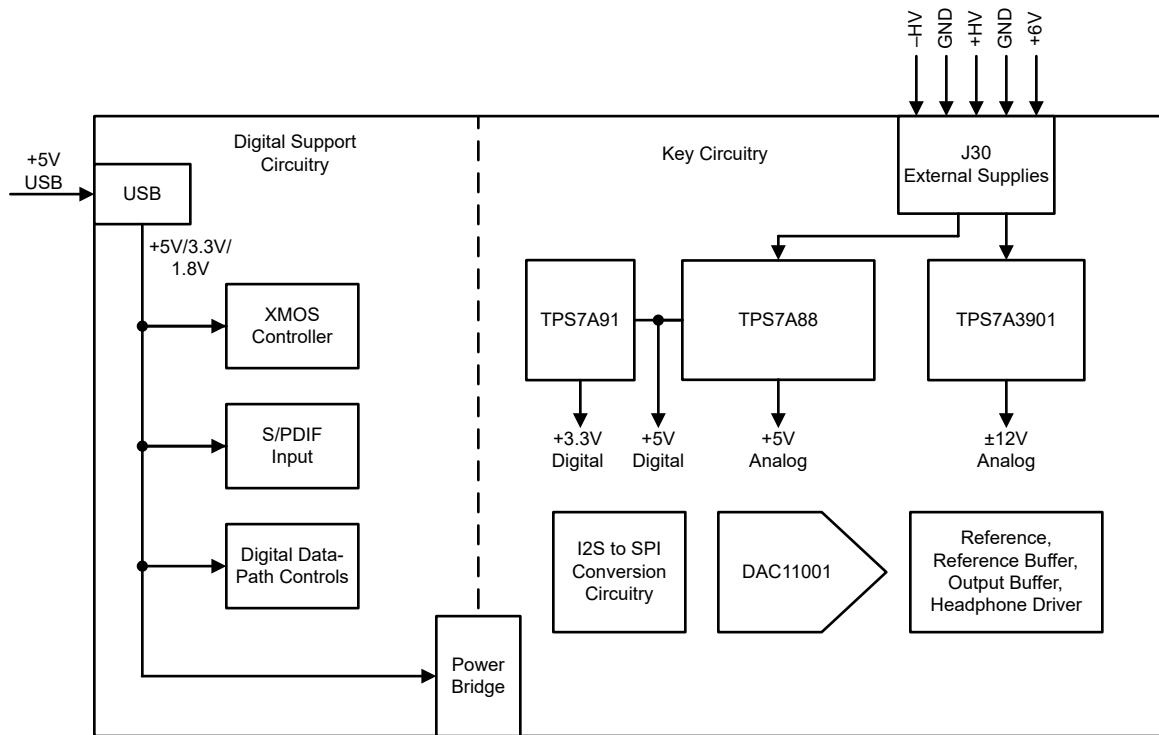

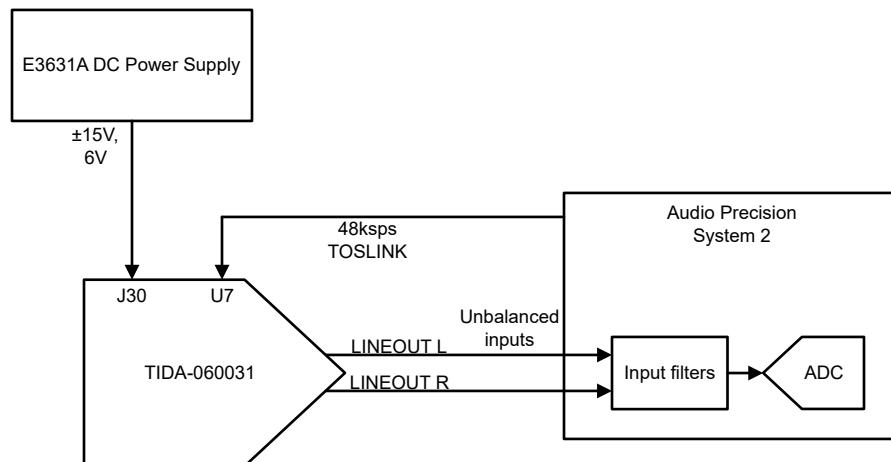

### 2.1 ブロック図

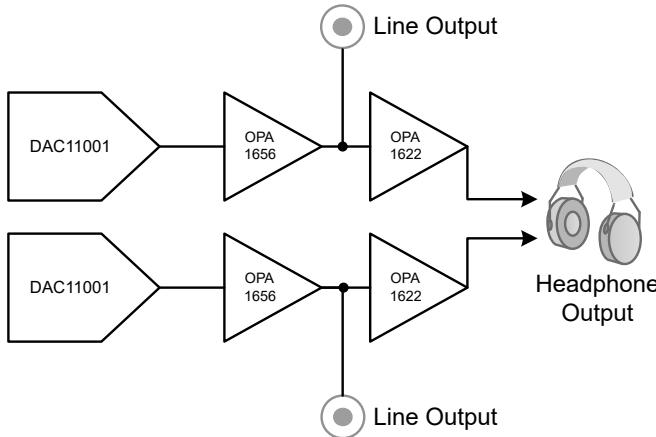

図 2-1. TIDA-060031 のブロック図

### 2.2 設計上の考慮事項

#### 2.2.1 オーディオ DAC と高精度 DAC の違い

市場には多くの種類の D/A コンバータ (DAC) が存在します。これには、汎用の電圧出力 DAC、高度に特化したオーディオ DAC、そして DAC11001A のような高精度 DAC が含まれます。これらの DAC にはさまざまなアーキテクチャがあります。ほとんどの DAC は、ストリング分圧器や R-2R ラダーのような精密抵抗アーキテクチャを使用しています。より特殊な DAC では、パルス幅変調 (PWM) やデルタシグマ変調器のような高周波スイッチングアーキテクチャを採用しています。

初期のオーディオ DAC は主に R-2R ラダーを特徴としていましたが、デジタルプロセスの改善に伴い、ほとんどの製品でマルチセグメント型デルタシグマアーキテクチャが R-2R 設計に代わるようになりました。

これらのアーキテクチャには、それぞれ利点と欠点があります。例えば、R-2R 抵抗ラダーは非常に精密な抵抗を設計に組み込む必要があります、コストが増加する可能性があります。さらに、ほとんどの抵抗ラダー型設計では、グリッチなどのコード間依存誤差が発生し、AC 性能に影響を与えることがあります。

デルタシグマ設計では、誤差を平均化する仕組みが組み込まれており、誤差の影響を低減し、精密なアナログ部品の必要性を減らすことができます。ただし、これらの DAC ではオーバーサンプリング回路を駆動するために、高周波のメインクロックが必要となります。このクロックにより高周波ノイズが発生しますが、R-2R アーキテクチャはフラットなノイズ特性を持っています。

実際には、高精度 DAC をオーディオ DAC アプリケーションに使用することにはいくつかの課題があります。まず、高精度 DAC は低ノイズかつ精密なリファレンス電圧を必要とします。さらに、ゼロクロス検出付きボリューム減衰のようなデジタル機能を持たず、標準的な I2S 入力にも対応していません。そのため、I2S を SPI に変換するためのデジタルロジックを設計に追加する必要があります。

このリファレンスデザインでは DAC11001A と DAC11001B の性能を比較しています。DAC11001B は、より高度なトランクアンドホールド回路を採用することで、DAC11001A よりも高周波領域での THD+N 性能が優れています。この回路の詳細や利点・制約については、[セクション 2.4.1『出力グリッチ』](#)で説明しています。

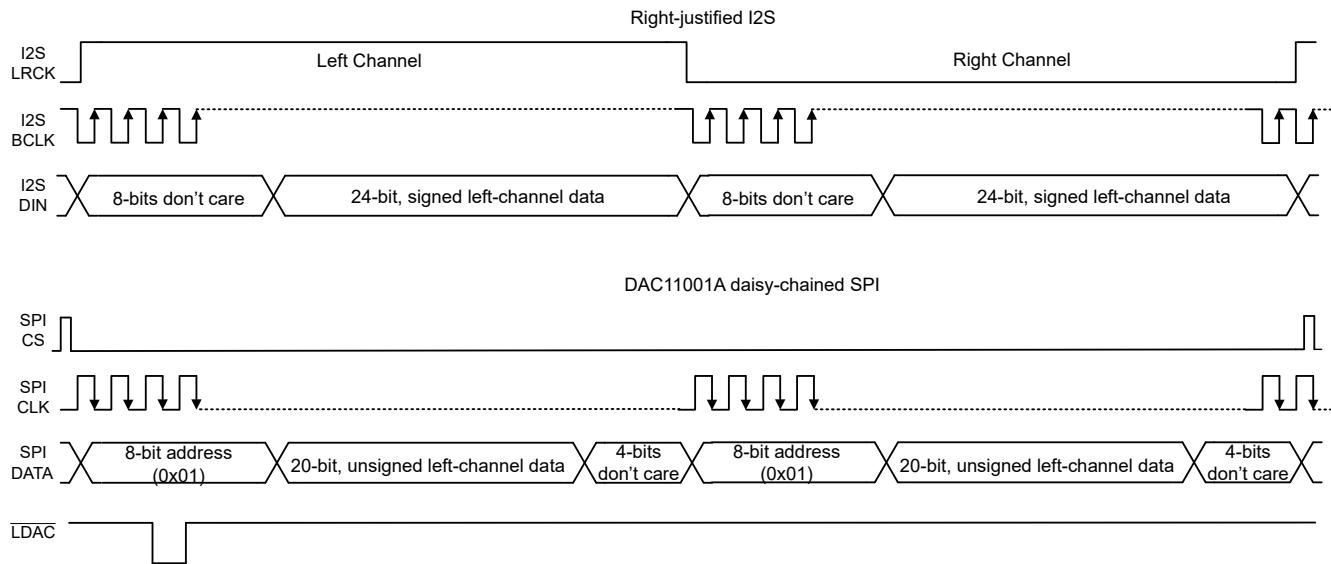

### 2.2.2 右詰め I2S からデイジーチェーン SPI への変換

オーディオデバイスでは、は主に、I2S (Inter-Integrated Circuit Sound) プロトコルを使用して通信を行います。I2S は、ビットクロック (BCLK)、左右クロック (LRCLK)、データラインを備えています。使いやすさを向上させるため、TIDA-060031 はオンボードのデジタルロジックを搭載しており、24 ビットの右詰め I2S 入力を、2 フレームのデイジーチェーン SPI 出力に変換します。DAC は、デイジーチェーン構成で設定されています。この出力は、2 つの DAC11001 デバイスによってラッピングされます。図 2-2 は、I2S 入力と目的の SPI 出力を重ねて示しています。

図 2-2. I2S からデイジーチェーン SPI への変換

I2S から SPI への変換デジタルロジックを設計する際には、いくつかの設計上の課題を考慮する必要があります。

- SPI クロックは I2S クロックと反転します。

- I2S フレームの最上位 8 ビットは *don't care* ビットですが、DAC11001 ではこのビットを DAC アドレス (0x01) として使用する必要があります。これは、SN74LV165APW (8 ビットパラレルロードシフトレジスタ) を用いることで実現しています。

- DAC11001 の最下位 4 ビット (LSB) も *don't care* ですが、I2S では一般的に 24 ビットデータが使用されるため、追加のビットシフトは不要です。

- LRCK は 50% デューティサイクルの信号ですが、DAC11001 ではアクティブ *low* のチップセレクト信号が必要です。このため、LRCLK 信号を遅延および反転し、元の LRCLK 信号と処理を行うことで、DAC11001 が必要とする CS 信号の *High* パルスを生成します。

- DAC が同時にデータをラッピングできるようにするために、LDAC 信号を生成する必要があります。

- I2S ではデータ値が符号付き 24 ビット整数として表現されますが、DAC11001A では符号なし整数形式を要求します。これは、データ値の最上位ビットを反転する必要があることを意味します。

TIDA-060031 は、図 2-3 に示されているロジックを用いて I2S から SPI への変換を実装しています。

図 2-3. I2S から SPI への変換に適したデジタルロジック

## 2.3 主な使用製品

### 2.3.1 DAC11001

DAC11001 は、高精度、低ノイズ、電圧出力の 20 ビットシングル チャネル D/A コンバータです。DAC11001 は、単調性が設計で仕様規定されており、出力範囲全体にわたって非常に優れた直線性を示します。

バッファなしの電圧出力により、低ノイズ性能 ( $7\text{nV}/\sqrt{\text{Hz}}$ ) と高速セトリング時間 ( $1\mu\text{s}$ ) を両立させているため、このデバイスは低ノイズ、高速制御ループ、波形生成アプリケーションに最適です。DAC11001 には拡張グリッチ除去回路が内蔵されており、コードに依存しない超低グリッチ ( $1\text{nV}\cdot\text{s}$ ) を実現しているため、全高調波歪み (THD) が非常に小さいクリーンな波形ランプを生成できます。

DAC11001 には、DAC の電源オン時にレジスタが既知の値になるようにパワー オン リセット回路が組み込まれています。外部基準電圧を使用すると、 $V_{\text{REFPF}} \sim V_{\text{REFNF}}$  までの DAC 出力範囲 (非対称な出力範囲も含む) を実現できます。

DAC11001 は、最高 50MHz のクロック速度で動作する多用途の 4 線式シリアル インターフェイスを備えています。

DAC11001 は、工業用温度範囲の  $-40^{\circ}\text{C} \sim +125^{\circ}\text{C}$  で動作が規定されています。

### 2.3.2 OPA1656

OPA1656 は、信号の忠実度の維持が重要なオーディオおよび産業用アプリケーション向けに特に設計された Burr-Brown™ オペアンプです。FET 入力アーキテクチャにより、低い電圧ノイズ密度  $2.9\text{nV}/\sqrt{\text{Hz}}$  と電流ノイズ密度  $6\text{fA}/\sqrt{\text{Hz}}$  を達成し、広範な回路で超低ノイズの性能を実現できます。帯域幅が広く、オープンループゲインが大きい OPA1656 は、20kHz で  $0.000035\% (-129\text{dB})$  という低歪みを実現し、全オーディオ帯域幅にわたってオーディオ信号の忠実性を高めることができます。また、出力電流の駆動能力が非常に高く、 $2\text{k}\Omega$  の負荷で電源から  $250\text{mV}$  以内のレールツーレール出力スイングが可能であり、 $100\text{mA}$  の出力電流を供給できます。

OPA1656 は  $\pm 2.25\text{V} \sim \pm 18\text{V}$ 、または  $4.5\text{V} \sim 36\text{V}$  の非常に広い電源電圧範囲で動作し、消費電流がわずか  $3.9\text{mA}$  であるため、各種オーディオ製品の電源制約にも対応できます。温度範囲は  $-40^\circ\text{C}$  から  $+125^\circ\text{C}$  と規定されています。本デバイスは 8 ピン SOIC パッケージで提供されます。

### 2.3.3 OPA1622

OPA1622 は、デュアル構成のバイポーラ入力 SoundPlus™ オーディオ オペアンプで、 $32\Omega$  負荷において  $100\text{mW}$  出力を駆動しながら、極めて低い  $2.8\text{nV}/\sqrt{\text{Hz}}$  のノイズ密度と、 $1\text{kHz}$  で  $-119.2\text{dB}$  という超低 THD+N を実現します。OPA1622 は非常に高い交流 PSRR および CMRR の特性を持ち、電源由来のノイズを除去できるため、ポータブル オーディオのアプリケーションに最適です。これらのデバイスは、 $+145\text{mA}$  から  $-130\text{mA}$  まで対応する高い出力駆動能力も持っています。

OPA1622 は、電源電圧範囲は  $\pm 2\text{V} \sim \pm 18\text{V}$  と非常に広く、チャンネルあたりわずか  $2.6\text{mA}$  の消費電流で動作します。OPA1622 オペアンプは、ユニティゲインにおいて安定であり、幅広い負荷条件にわたって優れた動的挙動を示します。さらに、OPA1622 にはシャットダウンモードが搭載されており、通常動作からスタンバイ電流 (通常  $5\mu\text{A}$  以下) へ切り替えることができます。このシャットダウン機能は、シャットダウン モードへの移行、または通常動作への復帰時に、クリックやポップのノイズ音が発生しないよう設計されています。

OPA1622 の内部レイアウトはクロストークを最小化する独自設計で、過負荷やオーバードライブ時でもチャンネル間の干渉を防ぎます。このデバイスは、 $-40^\circ\text{C} \sim +125^\circ\text{C}$  で規定されています。

### 2.3.4 OPA2828

OPA828 および OPA2828 (OPAx828) JFET 入力オペアンプは、OPA627 および OPA827 の次世代モデルであり、高速性と高い dc 精度および ac 性能が特徴です。これらのオペアンプは、低オフセット電圧、温度変化に対する低ドリフト、低バイアス電流、低ノイズを実現しており、 $0.1\text{Hz} \sim 10\text{Hz}$  のノイズはわずか  $60\text{nV}_{\text{RMS}}$  です。OPAx828 は  $\pm 4\text{V} \sim \pm 18\text{V}$  の広い電源電圧範囲で動作し、典型的な消費電流はチャンネルあたり  $5.5\text{mA}$  です。

45MHz のゲイン帯域幅積 (GBW) や  $150\text{V}/\mu\text{s}$  のスルーレートなどの AC 特性と、高精度の dc 特性により、OPA x 828 ファミリはさまざまなシステムに最適です。これには、16 ビット  $\sim$  18 ビット混合信号システム、トランスインピーダンス (I/V 変換) アンプ、フィルタ、精密  $\pm 10\text{V}$  フロントエンド、ハイインピーダンス センサー インターフェイスといった高速・高分解能データ アクイジション システムが含まれます。

OPAx828 は、8 ピン SOIC パッケージと、熱設計強化型の 8 ピン HVSSOP PowerPAD™ IC パッケージで供給されます。

## 2.4 システム設計理論

### 2.4.1 出力グリッチ

グリッチは THD 性能に大きく影響する要因です。そのため、高忠実度オーディオ性能を実現するには、グリッチを最小限に抑える必要があります。R-2R DAC におけるグリッチの主な原因是、R-2R スイッチ ネットワークにあります。

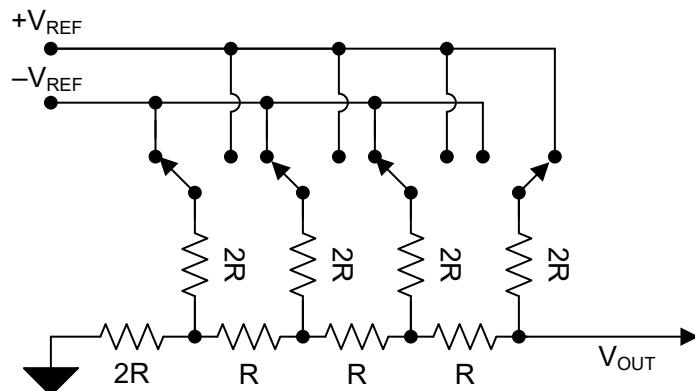

通常、R-2R DAC アーキテクチャでは、各ビットは 2 つの抵抗 ( $R$  および  $2R$ ) と、抵抗ペアを DAC の正または負の基準電圧に接続するスイッチで構成されます。図 2-4 に、簡略化した例を示します。このアーキテクチャは、バイナリ加重の分圧器として動作します。対応するビットが *high* の場合、スイッチは R-2R ペアを正の基準電圧に接続します。ビットが *low* の場合、ペアは負の基準電圧に接続されます。

図 2-4. R-2R スイッチのアーキテクチャ

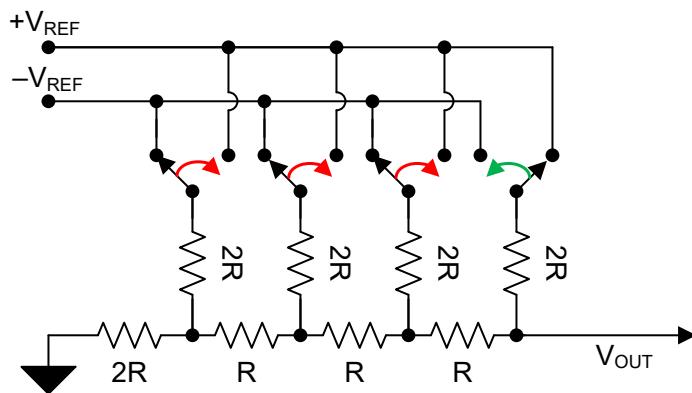

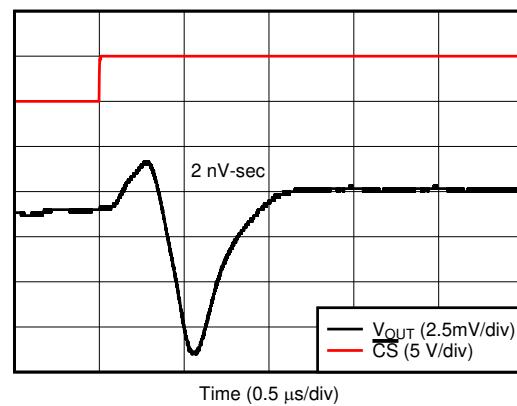

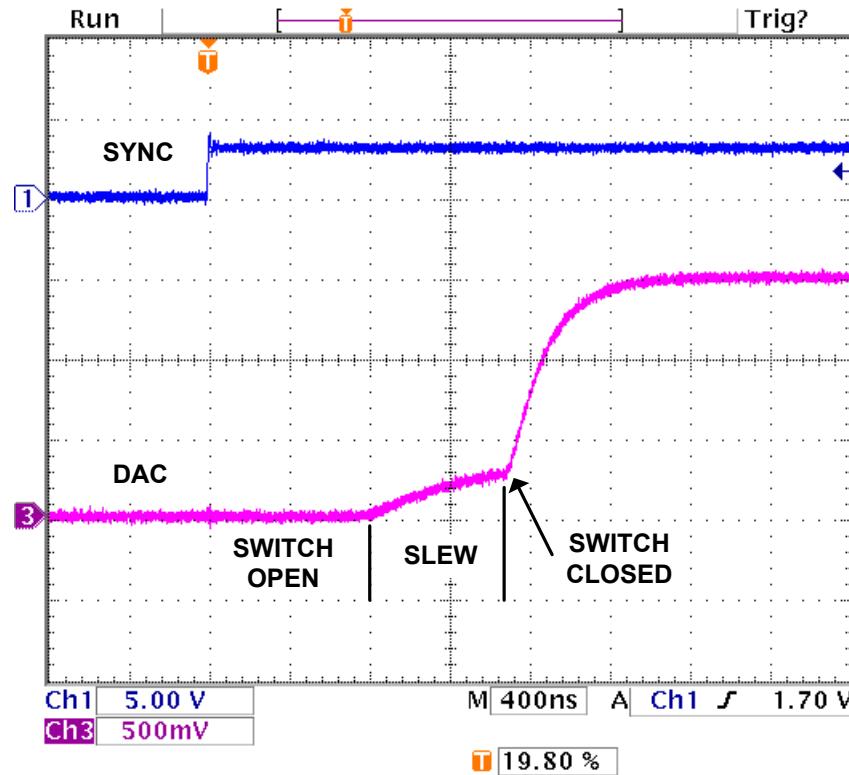

DAC のグリッチとは、DAC のコードトランジションによって生じるオーバーシュートやアンダーシュートに伴うエネルギーを指します。このグリッチは、たった 1 つのコードが変化した場合でも発生することがあります。グリッチ エネルギーは、R-2R スイッチからのチャージ インジェクションによって生じます。R-2R DAC では、各スイッチがビットに対応しているため、コード更新時のグリッチが大きくなります。コード間のグリッチは、コードトランジション時に抵抗ラダー内で切り替わるスイッチの数に依存します。より多くのビットが切り替わるほど、グリッチは大きくなります。最悪のコード間グリッチは、20 ビットデバイスにおいてミッドスケールのコードトランジション (0x7FFFFF から 0x80000) で発生します。さらに、R-2R ラダーでは、一般的に大きなスイッチを使用する必要があり、これらは大きな静電容量を持っていています。静電容量が大きいほど、各スイッチからのチャージ インジェクションが増加します。多くの R-2R DAC では、出力に 2 つのピークが現れるグリッチが特徴です。DAC 出力が増加すると、出力には小さなオーバーシュートの後に大きなアンダーシュートが生じます。このオーバーシュートとアンダーシュートは、R-2R スイッチが開閉する特性によるものです。図 2-6 に、2 つのピークが現れるグリッチの例を示します。コード依存のグリッチ エネルギーは、出力スペクトルにおいて、高次高調波の増加や非高調波での追加スプリアスとして検出可能です。

図 2-5. R-2R スイッチのミッドスケールコードトランジション

図 2-6. R-2R 出力グリッチ

D035

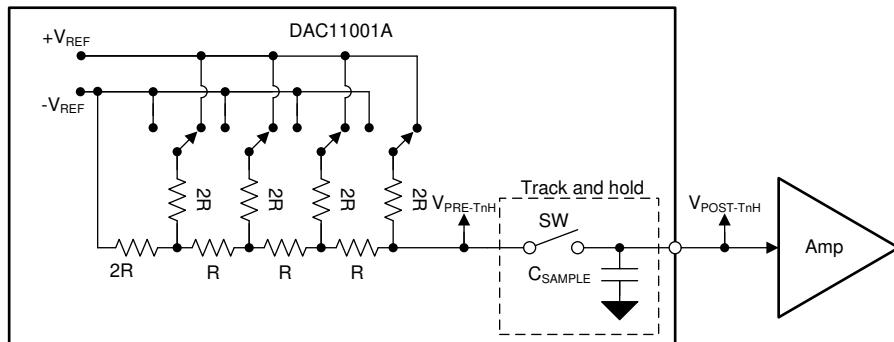

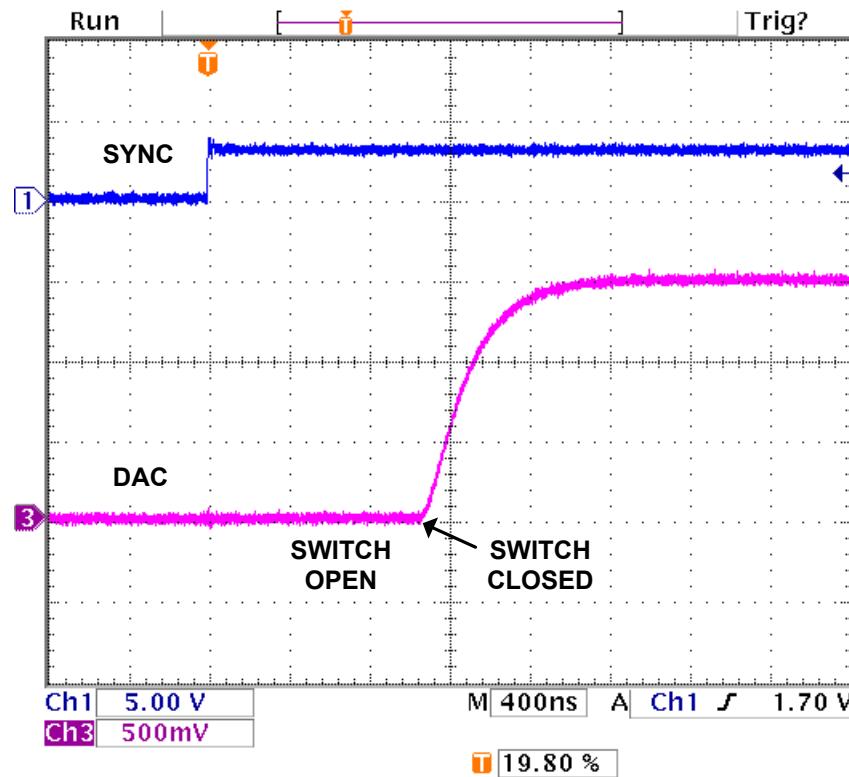

DAC11001 デバイスは、20 ビットの R-2R 抵抗ラダーによるコード間グリッチの影響を低減するため、複雑で高性能なトラック・アンド・ホールド (TnH) 回路を備えています。この回路を [図 2-7](#) に示します。この回路は、R-2R ラダーの出力にスイッチとサンプル用コンデンサを備えています。DAC コードが更新されると、R-2R ラダーが変化する前にトラックアンドホールドスイッチが開きます。サンプル用コンデンサは、初期電圧 ( $V_{POST-TnH}$ ) で電圧を安定させます。R-2R ラダーの更新が完了すると、トラックアンドホールドスイッチが閉じ、出力電圧が更新されます。トラックアンドホールド回路は、DAC のコードトランジション時のグリッチを大幅に低減しますが、その代償として DAC の更新速度に影響します。[図 2-8](#) に、トラックアンドホールド回路の有効および無効時の出力グリッチの比較を示します。

図 2-7. DAC11001 トラックアンドホールド回路図

図 2-8. DAC11001 トラックアンドホールド回路の有効および無効の比較

TnH 回路の有効性は、1kHz のトーンを 192kSPS のサンプルレートで入力し、回路オン / オフ時の THD+N を測定することで評価されます。TnH 回路オン時の THD+N は  $-107\text{dB}$  であり、回路オフ時の THD+N は  $-73\text{dB}$  です。これは  $34\text{dB}$  の差に相当し、およそ 50 倍性能が低下することを意味します。

さらに、R-2R スイッチが位置を変えるたびに、リファレンス入力のインピーダンスも変化します。図 2-9 に、コードトランジションによるリファレンスへの影響を示します。この突然のインピーダンス変化により、リファレンスにわずかな電圧降下としての小さなグリッチが生じます。トラック・アンド・ホールド回路はこのグリッチを軽減しますが、トラック・アンド・ホールド・スイッチが開く前にリファレンスが安定していることが重要です。リファレンスからのグリッチを最小限に抑えるには、高速セトリングのリファレンスバッファが必要です。

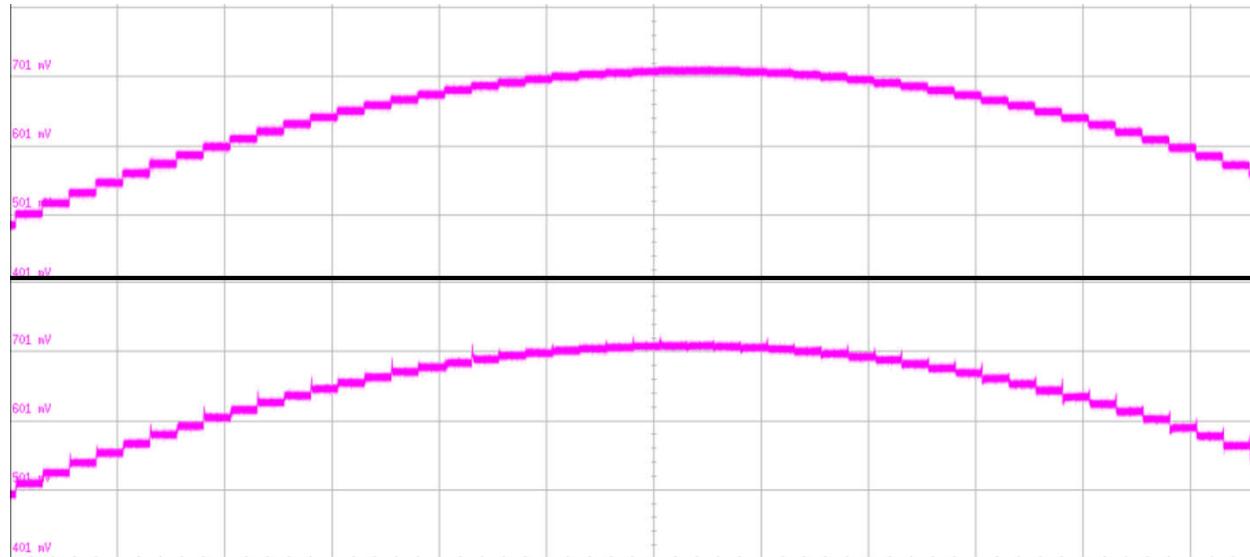

図 2-9. リファレンス電流と DAC コードとの関係

#### 2.4.2 高精度 DAC におけるサンプルレート依存性

サンプルレートを上げることで、量子化ノイズが低減され、DAC 出力の歪みも低下します。高精度 DAC は、高速 DAC やオーディオ DAC とは異なり、通常 1MSPS 未満の低サンプルレートで動作します。高精度 DAC には、サンプルレートが出力のセトリングタイムに制限される閾値があります。出力バッファは、各 DAC コードの更新ごとに安定して信号を生成できる必要があり、これを満たさないと出力信号に歪みが生じます。

トラック・アンド・ホールド回路を備えたデバイスでは、高サンプルレートに対して追加の制約があります。トラック・アンド・ホールド回路では、各 DAC の更新後にスイッチが開いたままの時間が決まっており、サンプルレートがトラック・アンド・ホールドのサンプル期間を超えると出力に歪みが生じます。

デルタシグマ方式の DAC では、別の形の誤差平均化が行われるため、トラック・アンド・ホールド回路によるサンプルレートの制約はありません。

#### 2.4.3 システムノイズ

ノイズに敏感なアプリケーションでは、DAC ノイズを可能な限り低減することが、最高の性能を引き出すための目標となります。バッファなしの R-2R 高精度 DAC を用いたシステムを設計する際には、複数のノイズ源を考慮する必要があります。主なノイズ源には、電源、DAC リファレンス、リファレンスバッファ、DAC 出力アンプ、DAC R-2R 抵抗ネットワークが含まれます。意図的な部品選択により、ノイズを低減することができます。

電源ノイズは、システムのノイズ性能に悪影響を与えることがあります。入力フィルタやデカッピングコンデンサおよびバイパスコンデンサによって、電源ノイズを抑制できます。デカッピングコンデンサは、電圧低下の影響を低減します。バイパスコンデンサは、ローパスフィルタとして働き、電源からの高周波ノイズの影響を低減します。高い電源抑制比(PSRR)を持つデバイスを選定することも、ノイズの影響を減らすのに有効です。AC PSRR は、デバイスが電源からのノイズや振動を除去する能力を示します。表 2-1 には、リファレンスデザインで選定されたデバイスおよびデータシートに示されている PSRR 値を示しています。

表 2-1. リファレンスデザインデバイスの PSRR

| デバイス     | PSRR (1kHz) |

|----------|-------------|

| DAC11001 | 95dB        |

| REF5030  | 130dB       |

| TPS7A39  | 69dB        |

| TPS7A88  | 70dB        |

| TPS7A90  | 60dB        |

リファレンスノイズは、DACのTHD+N性能に直接影響します。リファレンスから発生するノイズはDAC出力にそのまま伝搬するためです。リファレンスノイズは、ノイズ性能の優れたリファレンスを選定することで低減可能です。REF5030のような一部のリファレンスデバイスには、ノイズ性能を改善するためのトリムピンやノイズピンが用意されています。ノイズ低減の方法としては、ローパスフィルタの追加や低ノイズ出力バッファの選定が有効です。リファレンス用バッファでは、出力グリッチのセクションで述べたように、高速セトリングとの両立が必要です。高速セトリングと低ノイズの両立を図ることが最適なアプローチとなります。

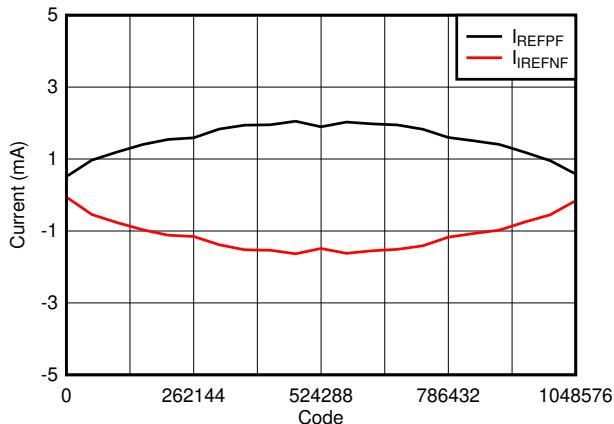

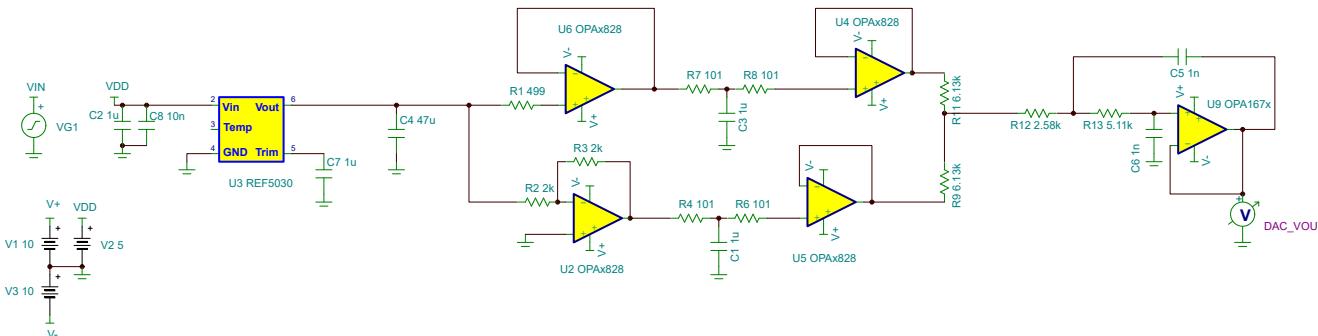

DAC11001のようなバッファなしR-2R DACは、R-2R抵抗ネットワークにより出力インピーダンスが比較的高い特性を持ちます。出力バッファを選定する際、DACの出力インピーダンスが高いため、電圧ノイズよりも電流ノイズに注意する必要があります。表2-2は、異なるオペアンプ入力アーキテクチャのノイズ性能を示しています。バイポーラ入力オペアンプは非常に低い電圧ノイズを特徴としますが、電流ノイズは高めです。OPA1656などのCMOSオペアンプは、わずかに電圧ノイズが高い代わりに電流ノイズが低い特性を持ちます。図2-10は、TINA-TI™で作成したシミュレーションで、高インピーダンス出力に接続した異なるオペアンプを比較した結果を示しています。図2-11は、そのノイズシミュレーションの結果です。2つのCMOSオペアンプは、バイポーラOPA1612よりも優れた性能を示します。R-2R DACを使用した場合、CMOSオペアンプは電流ノイズの低減により、総合的に優れたノイズ性能を示します。

表2-2. オペアンプノイズ比較

| オペアンプ   | 入力段   | 1kHz時の電圧ノイズ               | 1kHz時の電流ノイズ                |

|---------|-------|---------------------------|----------------------------|

| OPA1612 | バイポーラ | 1.1nV/ $\sqrt{\text{Hz}}$ | 1700fA/ $\sqrt{\text{Hz}}$ |

| OPA1656 | CMOS  | 4.3nV/ $\sqrt{\text{Hz}}$ | 6fA/ $\sqrt{\text{Hz}}$    |

| OPA1678 | CMOS  | 4.5nV/ $\sqrt{\text{Hz}}$ | 3fA/ $\sqrt{\text{Hz}}$    |

図2-10. TINA-TI™のノイズシミュレーション

図2-11. オペアンプのノイズシミュレーションの比較

#### 2.4.4 DAC11001A と DAC11001B の比較

DAC11001B は DAC11001A の機能拡張版です。これらの機能強化には、より低い積分非直線性 (INL) および改良されたトラック アンド ホールド回路 (TnH) が含まれます。

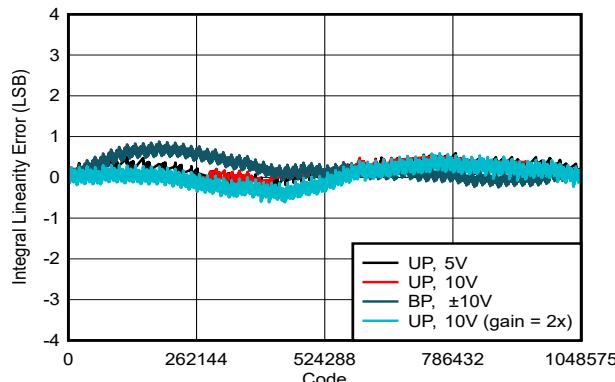

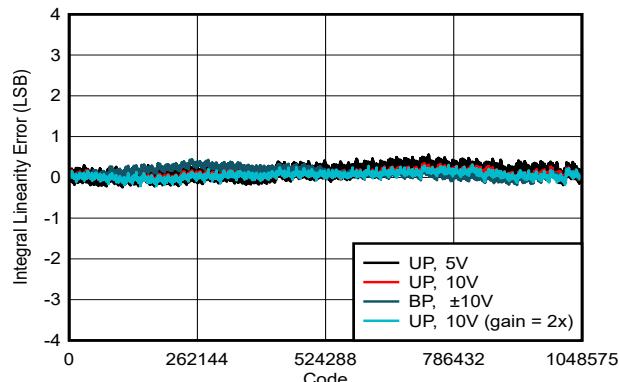

INL は相対精度とも呼ばれ、各コードについて実際の DAC 出力と理論的に期待される出力との差を測定します。このパラメータは一般的に、最下位ビット (LSB) で示されます。数学的には、INL は、すべての前段コードにおけるコード間誤差の総和として表されます。DAC11001A の最大誤差は 4LSB であり、オフセット誤差およびゲイン誤差を除けば、各コードの出力が理想出力から最大 4LSB までずれる可能性があること意味します。DAC11001B の最大誤差は 1LSB であり、出力が著しく高精度となっています。図 2-12 および 図 2-13 に、2 つのデータシートからの INL の比較を示します。

図 2-12. DAC11001A INL

図 2-13. DAC11001B INL

DAC11001A および DAC11001B はどちらもコード間グリッチの影響を低減するためのトラック アンド ホールド サブ回路を実装しています。『[出力グリッチ](#)』で説明したように、スイッチによる DAC 更新中、TnH 回路は DAC 更新時にスイッチを用いて出力を R-2R ラダーから切り離します。このスイッチは相補型 PMOS または NMOS 構造です。これらの MOSFET は、スイッチ両端の電圧がある閾値を超えると、寄生ダイオードとして動作する場合があります。DAC11001A では、図 2-14 に示すように、差動電圧が約 1V を超える場合、TnH 回路により出力がスルーすることがあります。この制限は DAC11001B で改善されており、図 2-15 に示されています。

図 2-14. DAC11001A トラック アンド ホールド電圧フィードスルー

図 2-15. DAC11001B トラック アンド ホールド電圧フィードスルーなし

この TnH の問題は、出力歪みによって THD+N に直接影響を及ぼします。DAC11001A の TnH 回路には、サンプルレート、出力振幅、トーン周波数の 3 つのパラメータが影響します。サンプルレートが低いと、出力更新の間隔が長くなり、

DAC 更新間の電圧ステップが大きくなる可能性があります。DAC 出力範囲が大きいと、電圧変化の振幅も直接的に大きくなります。サンプルレートを一定にした場合、トーン周波数を上げると、出力でより大きな電圧変化が必要になることがあります。これらの影響を受けるパラメータは、他のパラメータに十分なヘッドルームを持たせることで対処可能です。たとえば、出力レンジが大きくても、サンプルレートが十分に高ければ問題は生じにくくなります。

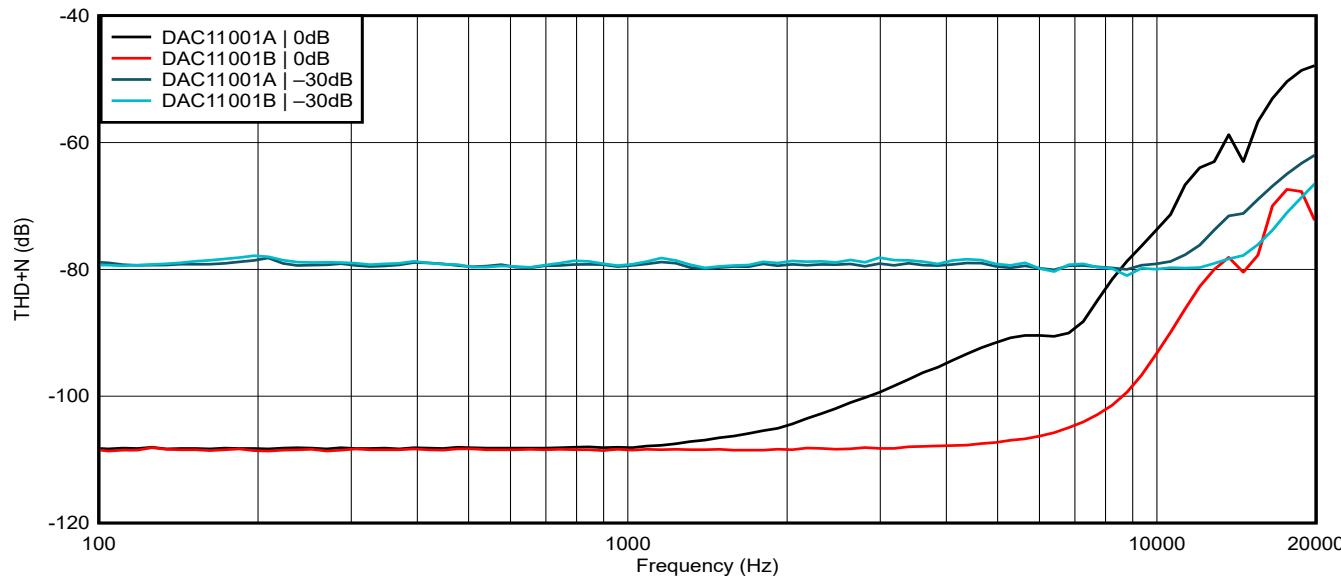

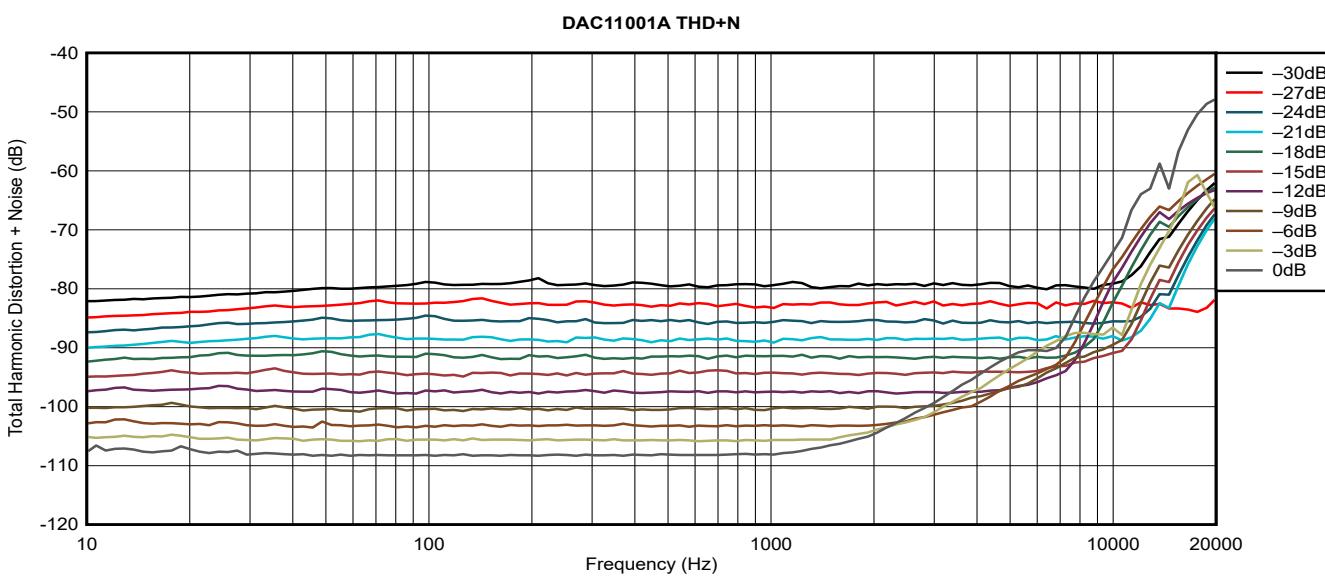

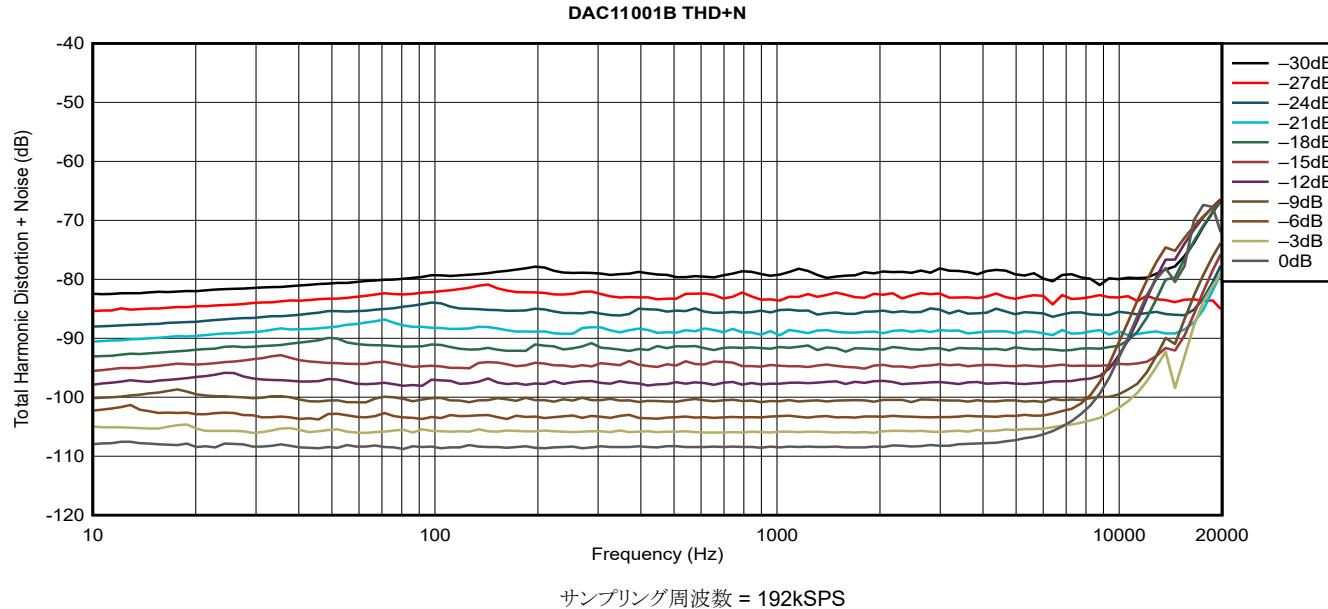

図 2-16 に、これらの異なるパラメータが DAC11001A および DAC11001B の THD+N に周波数スペクトル全体でどのように影響するかを示しています。図では、2 つの DAC の 0dB および -30dB の振幅を比較しています。参考設計の 0dB 出力範囲は  $\pm 3V$  です。4 つのデータセットはすべて、192kSPS の一定のサンプルレートで測定されています。0dB 出力範囲において、DAC11001A は 1kHz から THD+N が悪化し始めます。周波数が上がると、各更新ごとの電圧変化振幅が大きくなり、これによりトラック アンド ホールド回路による歪みが増加します。DAC11001B は、改善された TnH 回路により、5kHz まで始まりません。-30dB DAC では、THD+N は 10kHz まで悪化しません。振幅の低下により、電圧更新時の最大変化振幅が小さくなり、その結果、さらなる TnH 歪みを防ぐことができます。TnH 回路自体は歪みを発生させませんが、-30dB 振幅では DAC 出力がノイズフロアに近くなるため、全体の THD+N 測定値はより悪くなります。

図 2-16. トラック アンド ホールド回路の比較

### 3 ハードウェア、ソフトウェア、テスト要件、テスト結果

#### 3.1 ハードウェア要件

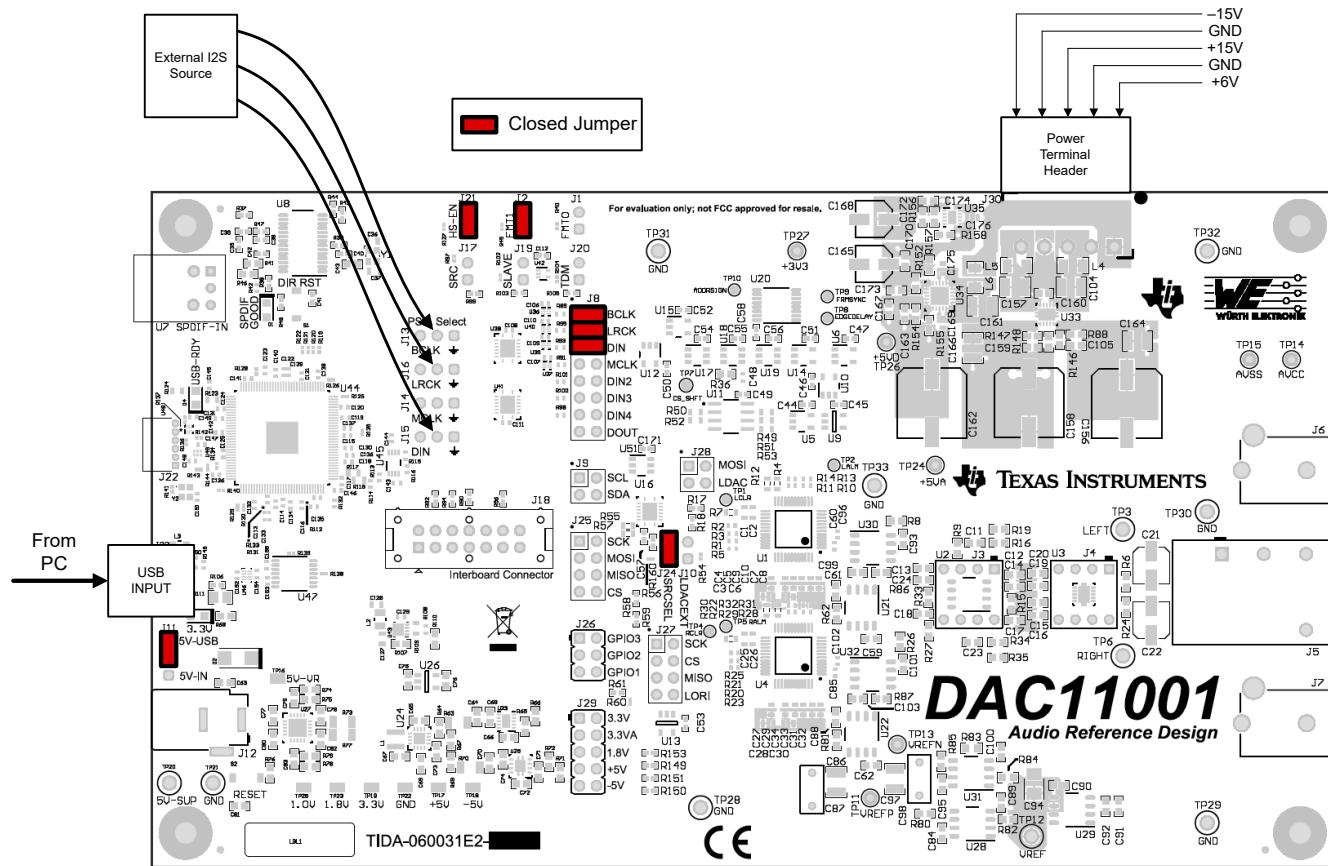

##### 3.1.1 必要な外部電源

TIDA-060031 では、2 系統の電源供給が必要です。基板の左側には、主にデジタル入力と USB インターフェイスのサポート回路があります。図 3-1 は、回路に USB 入力または外部電源から、電源ブリッジを経由して電力を供給できることを示しています。

基板の右側には重要なアナログ回路である DAC、DAC リファレンスおよびリファレンス バッファ、DAC 出力バッファが配置されています。また、この側には SPI データバスの管理や、入力される RJ I2S データをデイジーチェーン形式の SPI に変換するためのデジタル制御回路も含まれています。基板のこの側は外部電源を必要とします。

図 3-1. 電源構成

図 3-1 は、TIDA-060031 の電源入力を示しています。端子ブロック J30 は、主要回路用の外部電源に使用されます。表 3-1 は J30 の定義を示します。

表 3-1. 電源入力

| J30 ピン | 説明                                                        | 値および制限                 |

|--------|-----------------------------------------------------------|------------------------|

| J30.1  | 低電圧電源 +6V。この電源は、主要回路の 5V アナログ、5V デジタル、3.3V デジタル電源に使用されます。 | +6V 入力、300mA 制限        |

| J30.2  | グラウンド                                                     | グラウンド                  |

| J30.3  | 高電圧正電源入力。主要回路の +12V 電源に使用されます。                            | +12.5 ~ +15V、200mA 制限  |

| J30.4  | グラウンド                                                     | グラウンド                  |

| J30.5  | 高電圧負電源入力。主要回路の -12V 電源に使用されます。                            | -12.5V ~ -15V、200mA 制限 |

USB 入力を使用しない場合 (I2S が S/PDIF 入力から供給される場合や、直接リファレンス デザインに接続される場合)、USB 電源は不要です。主要回路側の +3.3V 電源を使用して、ボード左側の最小限のサポート回路に給電することができます。これは、電源ブリッジ (J29、1-2 番位置) で 3.3V 電源を接続することで実現できます。

### 3.1.2 ジャンパ定義

表 3-2 に、ジャンパ定義の詳細を示します。

**表 3-2. ジャンパ定義**

| ジャンパ  | 名称                    | 説明                                                                                                                                                                                                                                   |

|-------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| J1、J2 | S/PDIF フォーマット選択       | FMT1 ショート、FMT0 ショート: 16 ビット、MSB ファースト、右詰め<br>FMT1 ショート、FMT0 オープン: 24 ビット、MSB ファースト、右詰め <b>デフォルト</b> 、<br>TIDA-060031 で唯一サポートされているフォーマットです。<br>FMT1 オープン、FMT0 ショート: 24 ビット、MSB ファースト、左詰め<br>FMT1 オープン、FMT0 オープン: 24 ビット、MSB ファースト、I2S |

| J10   | 外部 LDAC 選択            | ショート: LDAC をグランドにショート。<br>オープン: LDAC は 3.3V にプルアップ。                                                                                                                                                                                  |

| J11   | USB 電源選択              | ショート 1 ~ 2 (5V-IN): J12 を左側ボードの +5V 入力として使用。<br>ショート 2 ~ 3 (5V-USB): 推奨設定で、USB 入力を使用してボード左側に給電。                                                                                                                                      |

| J13   | BCLK の選択              | ショート 2 ~ 3: USB または S/PDIF の BCLK を I2S ソースとして選択。<br><b>1 ~ 2 に外部接続</b> : ピン 1 は接地。これにより、外部 I2S BCLK ソース (例: PSIA) を評価基板に接続できます。                                                                                                     |

| J14   | MCLK の選択              | ショート 2 ~ 3: USB または S/PDIF の MCLK を I2S ソースとして選択。 (MCLK 信号を使用していないため、TIDA-060031 ではこの設定は不要です。<br><b>1 ~ 2 に外部接続</b> : ピン 1 は接地。これにより、外部 I2S ソース (例: PSIA) を評価基板に接続できます。                                                              |

| J15   | DIN の選択               | ショート 2 ~ 3: USB または S/PDIF の DIN を I2S ソースとして選択。<br><b>1 ~ 2 に外部接続</b> : ピン 1 は接地。これにより、外部 I2S DIN ソース (例: PSIA) を評価基板に接続できます。                                                                                                       |

| J16   | LRCK の選択              | ショート 2 ~ 3: USB または S/PDIF の LRCK を I2S ソースとして選択。<br><b>1 ~ 2 に外部接続</b> : ピン 1 は接地。これにより、外部 I2S LRCK ソース (例: PSIA) を評価基板に接続できます。                                                                                                     |

| J17   | DIR9001 (S/PDIF) 入力選択 | ショート: DIR9001 入力を I2S データバスに接続。<br>オープン: USB I2S ソースを I2S データバスに接続。                                                                                                                                                                  |

| J19   | I2S ターゲット選択           | TIDA-060031 はサポートされていないため、オープンのままにします。                                                                                                                                                                                               |

| J20   | I2S TDM モード選択         | TIDA-060031 はサポートされていないため、オープンのままにします。                                                                                                                                                                                               |

| J21   | Xmos 高速 USB           | ショート: TIDA-060031 を USB2.0 デバイスとして認識させ、192kHz サンプルレートに対応させます。                                                                                                                                                                        |

| J22   | JTAG 入力               | このヘッダーを使用すると、JTAG 入力が可能になります。                                                                                                                                                                                                        |

| J24   | SPI ソース選択             | ショート: I2S から SPI への変換回路の SPI 出力を DAC11001A デバイスに接続。<br>オープン: SPI 入力ブリッジ (J25) から DAC11001A デバイスへ接続。                                                                                                                                  |

**表 3-3. 入力・出力コネクタ**

| ジャンパ | 名称            | 説明                       |

|------|---------------|--------------------------|

| J5   | ヘッドフォン出力      | ヘッドフォン出力。左右の DAC 出力を結合。  |

| J6   | 左側のフォノグラフジャック | 左側のライン出力。                |

| J7   | 右側のフォノグラフジャック | 右側ライン出力。                 |

| J12  | 5V デジタル入力     | デジタル回路用 5V DC 電源ジャック     |

| J23  | USB 入力        | USB 入力。不要な場合は未接続のままにします。 |

表 3-4. I2S、SPI、GPO、電源ブリッジ

| ジャンパ | 名称                | 説明                                                                                                                                                                      |

|------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| J8   | I2S 接続ブリッジ        | この接続により、I2S 入力を DAC およびサポート回路に接続できます。TIDA-060031 リファレンス デザインでは、LRCK、BCLK、および DIN のみが必要です。                                                                               |

| J9   | I2C 接続ブリッジ        | TIDA-060031 リファレンス デザインは I2C を使用しません。                                                                                                                                   |

| J18  | I2S を接地。          | このヘッダは、I2S 信号を接地します。未実装のままにすることも可能です。                                                                                                                                   |

| J25  | SPI 接続ブリッジ        | この接続により、XMOS コントローラが DAC11001A デバイスの設定用 SPI を生成できます。デフォルトでは、リファレンス デザインで設定は不要です。SPI を操作するには、専用のソフトウェアが必要です。デフォルトでは、これらの接続は未実装のままにすることも可能です。                             |

| J26  | GPO 接続ブリッジ        | この接続により、XMOS コントローラは SPI で使用するいくつかの制御ラインを設定できます。デフォルトでは、これらは未実装のままにすることも可能です。                                                                                           |

| J27  | SPI 入力            | 代わりに SPI を使用する場合、この接続を使って I2S 回路をバイパスできます。                                                                                                                              |

| J28  | PICO および LDAC の接地 | この接続により、SPI PICO と LDAC がグランドにショートされます。                                                                                                                                 |

| J29  | 電源接続ブリッジ          | この接続により、リファレンス デザインと USB コントローラ間で電源を共有できます。デフォルトでは、この接続は未実装のままにすることも可能です。基板左側の 3.3V 回路に給電する場合は、J29.1-2 (3.3V) にジャンパを配置できます。これは、USB 入力を使用せず、外部または S/PDIF 入力を使用する場合に便利です。 |

### 3.1.3 I2S ソースの選択

このセクションでは、TIDA-060031 リファレンス デザインで使用できるさまざまな入力構成について説明します。

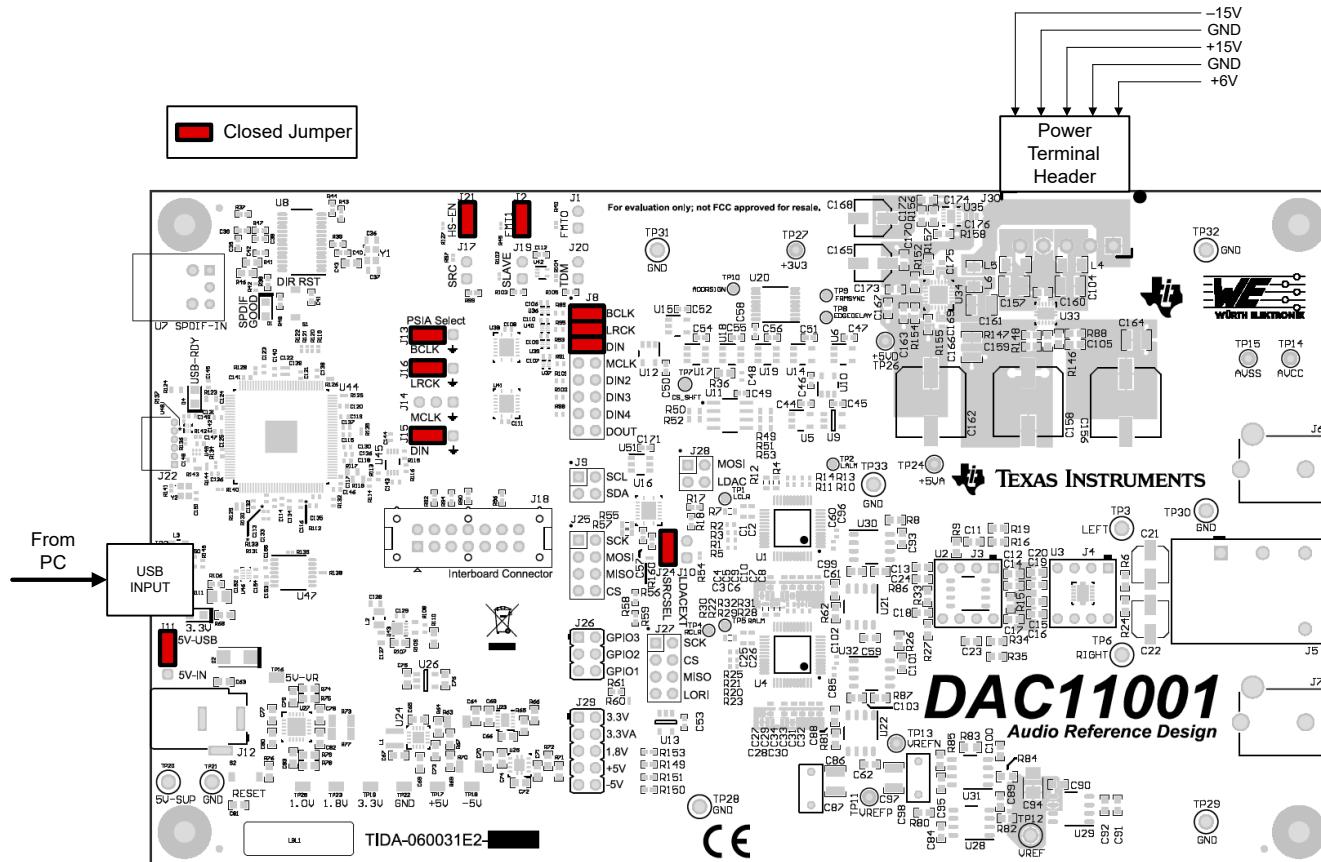

#### 3.1.3.1 USB I2S ソース

DAC11001A のオーディオ性能を評価する最も簡単な方法は、USB 入力を使用することです。図 3-2 には、USB 入力を選択する際のジャンパ設定が示されています。

図 3-2. USB I2S 入力設定

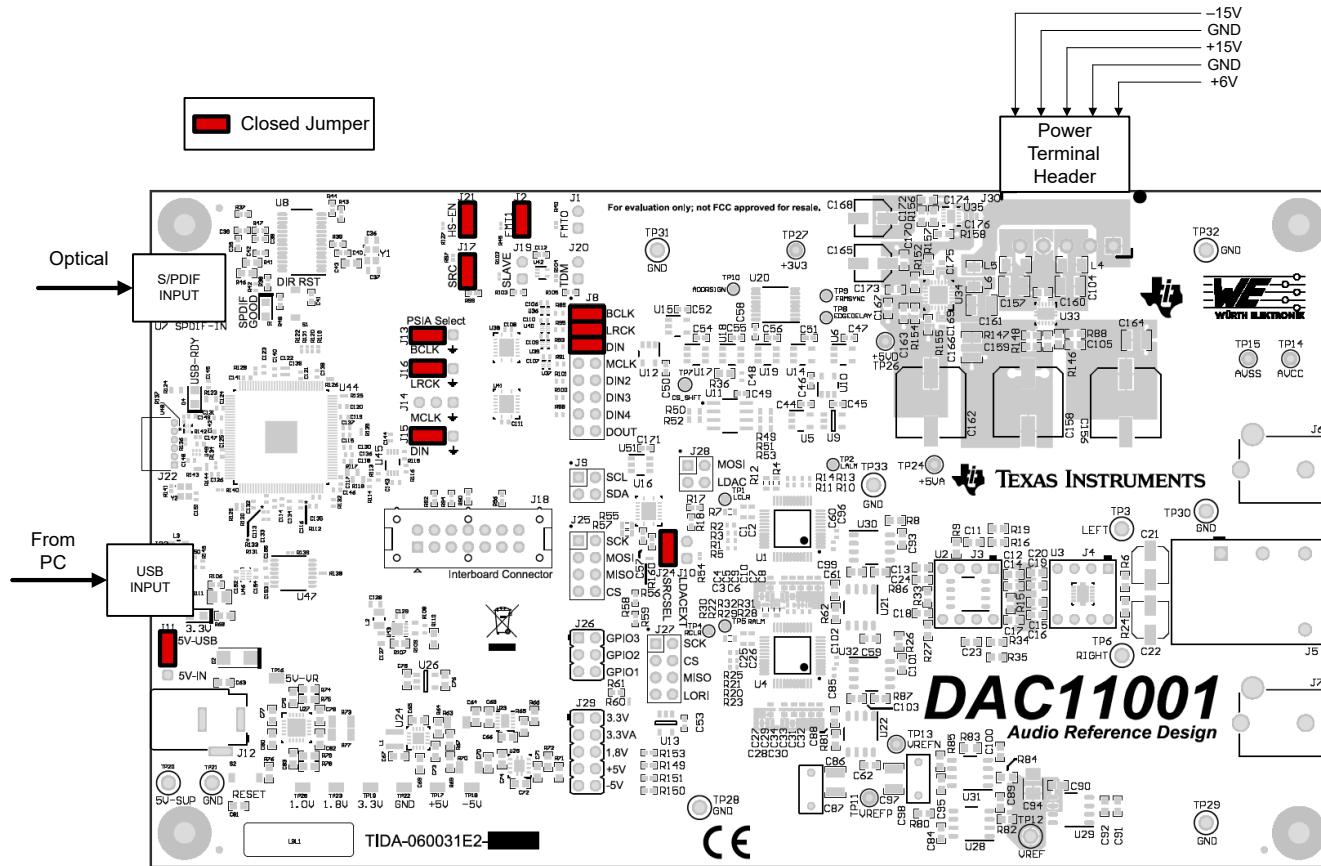

### 3.1.3.2 SPDIF I2S ソース

図 3-3 は、TIDA-060031 リファレンス デザインで光学 SPDIF 入力をオーディオ ソースとして使用する際のジャンパ設定を示しています。これは 48kSPS の入力のみに対応しています。

図 3-3. S/PDIF I2S 入力設定

### 3.1.3.3 外部 PSIA I2S ソース

外部 I2S 入力は、PSIA 入力ヘッダ J13～J16 を使用して TIDA-060031 に接続できます。これを行うには、J13～J16 のジャンパを取り外し、I2S 入力をヘッダのピン 1 とピン 2 の位置に接続します。ヘッダのピン 1 は、よりノイズの少ないデジタル接続を実現するために接地されています。I2S 入力は 24 ビット右詰めモードに構成する必要があります。

図 3-4. 外部 I2S 入力設定

### 3.2 ソフトウェア要件

TIDA-060031 リファレンス デザインでは、制御用ソフトウェアは不要です。USB インターフェイスにはドライバが必要となります。このドライバをインストールする最も簡単な方法は、PurePath™ Console ソフトウェアをインストールすることです。

#### 3.2.1 XMOS USB 2.0 ドライバのインストール

PurePath Console ソフトウェアは、次のランディング ページからアクセスを申請することで利用できます: [PurePath Console](#)。アクセス権が付与されたら、[ti.com/secureresources](http://ti.com/secureresources) からソフトウェアをダウンロードします。

ドライバが正常にインストールされると、PC は TIDA-060031 を *TUSBAudio Eval UAC2.0 (BB04)* として認識します。

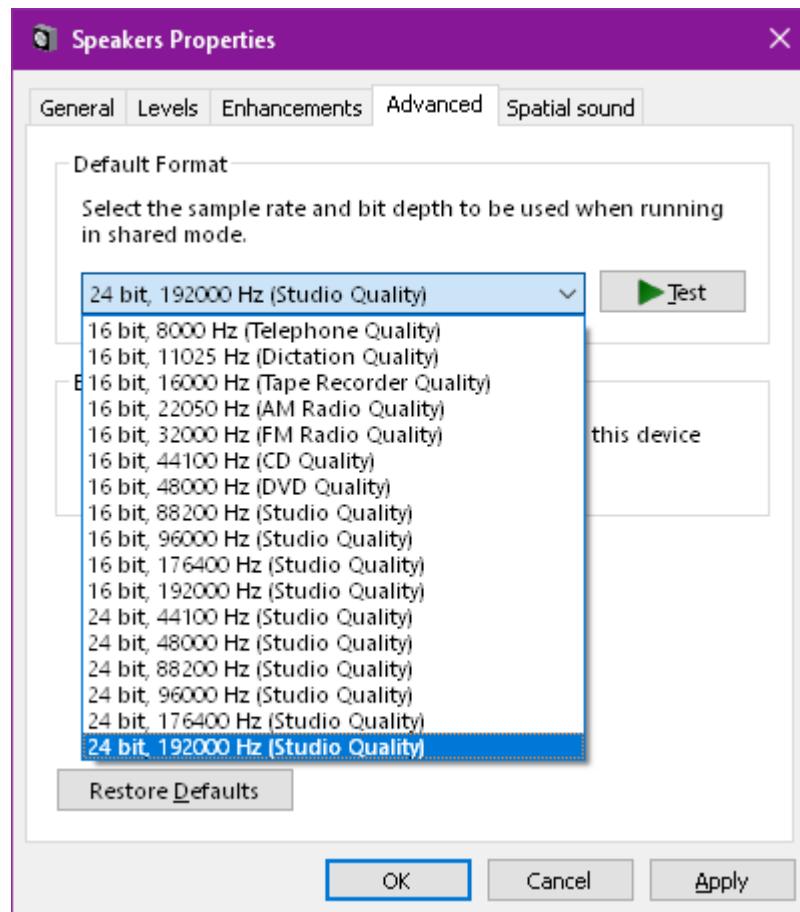

#### 3.2.2 USB サンプル レートの設定

USB 入力のサンプル レートは、PC の設定内にあるオーディオ デバイスのサンプル レート設定によって決まります。サンプル レートを設定するには、デバイスのプロパティにアクセスします。図 3-5 では、テストに 24 ビット / 190000Hz を使用しています。Microsoft® Windows® では、サンプル レートを変更した後、オーディオソースを再生するソフトウェアを再起動する必要があります。

図 3-5. サンプル レートを選択するためのスピーカーのプロパティメニュー

### 3.3 テストと結果

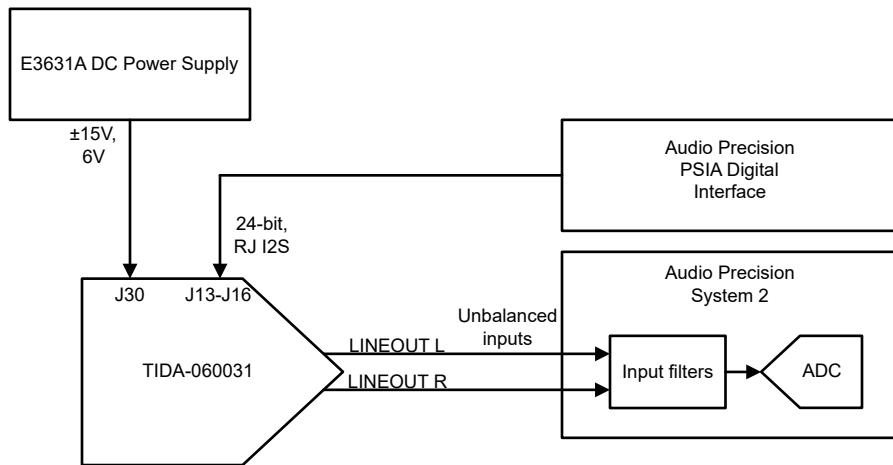

#### 3.3.1 全高調波歪およびノイズの測定

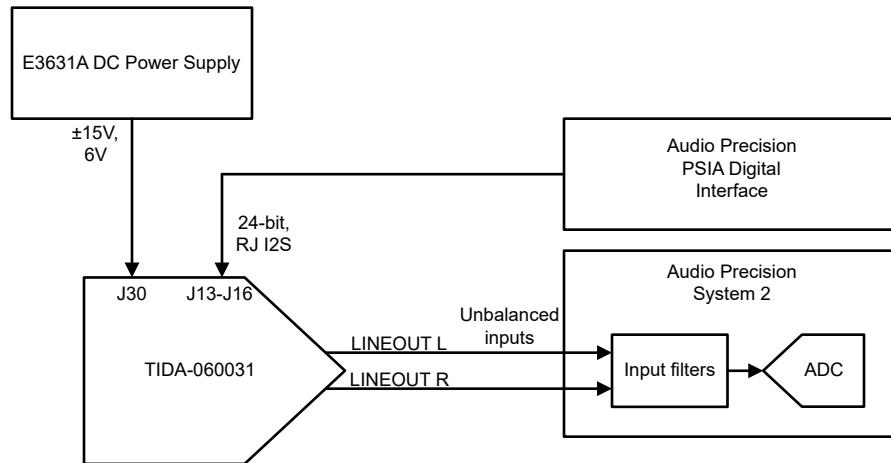

THD+N は、Audio Precision System 2 (AP2) を用いて測定します。AP2 には外部 I2S 信号源が接続され、24 ビットデータの右詰め出力パターンに設定されています。I2S 信号は、TIDA-060031 リファレンス デザインの I2S 入力コネクタ J13 ~ J16 に接続されます。

図 3-6. THD+N 測定時の構成

表 3-5. THD+N 入力フィルタ

| サンプルレート | フィルタ                                 |

|---------|--------------------------------------|

| 48kSPS  | 22Hz ハイパス フィルタ、20kHz AES17 ローパス フィルタ |

| 96kSPS  | 22Hz ハイパス フィルタ、40kHz AES17 ローパス フィルタ |

| 192kSPS | 22Hz ハイパス フィルタ、40kHz AES17 ローパス フィルタ |

#### 3.3.2 THD および THD+N の結果

表 3-6 および 表 3-7 は、さまざまな振幅、音程、サンプルレートにおける THD+N 測定結果を示しています。

表 3-6. DAC11001A THD+N の測定結果

| 入力振幅    | トーン周波数 | サンプルレート |        |         |

|---------|--------|---------|--------|---------|

|         |        | 48kSPS  | 96kSPS | 192kSPS |

| 0dBFS   | 1kHz   | -107dB  | -107dB | -108dB  |

|         | 2kHz   | -94dB   | -101dB | -106dB  |

|         | 5kHz   | -56dB   | -74dB  | -92dB   |

|         | 10kHz  | -49dB   | -45dB  | -73dB   |

| -60dBFS | 1kHz   | -55dB   | -51dB  | -50dB   |

|         | 2kHz   | -54dB   | -50dB  | -49dB   |

|         | 5kHz   | -56dB   | -50dB  | -49dB   |

|         | 10kHz  | -57dB   | -50dB  | -50dB   |

表 3-7. DAC11001B THD+N の測定結果

| 入力振幅  | トーン周波数 | サンプルレート |        |         |

|-------|--------|---------|--------|---------|

|       |        | 48kSPS  | 96kSPS | 192kSPS |

| 0dBFS | 1kHz   | -111dB  | -108dB | -108dB  |

|       | 2kHz   | -110dB  | -108dB | -108dB  |

|       | 5kHz   | -75dB   | -97dB  | -106dB  |

|       | 10kHz  | -47dB   | -69dB  | -92dB   |

**表 3-7. DAC11001B THD+N の測定結果 (続き)**

| 入力振幅    | トーン周波数 | サンプルレート |        |         |

|---------|--------|---------|--------|---------|

|         |        | 48kSPS  | 96kSPS | 192kSPS |

| -60dBFS | 1kHz   | -55dB   | -51dB  | -50dB   |

|         | 2kHz   | -53dB   | -50dB  | -49dB   |

|         | 5kHz   | -55dB   | -50dB  | -40dB   |

|         | 10kHz  | -57dB   | -50dB  | -50dB   |

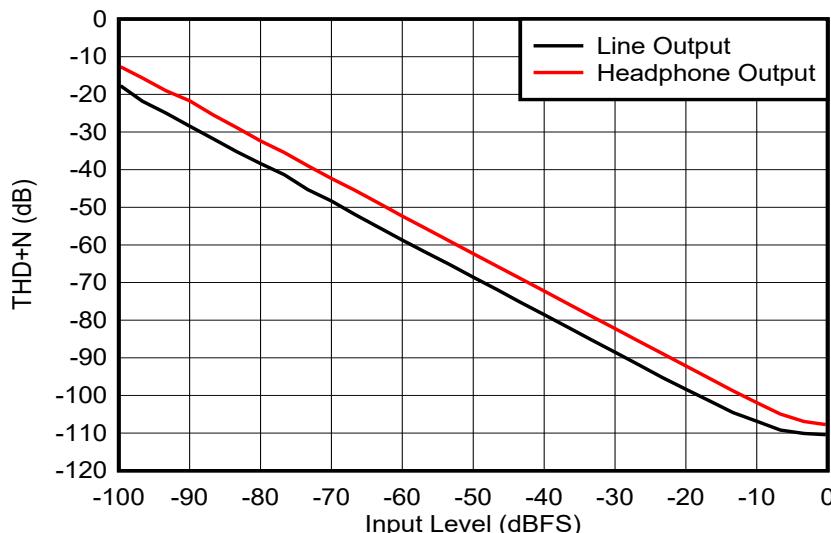

図 3-7 は、入力レベルの大きさが増加するについて THD+N が改善する様子を示しています。これは、DAC 出力の大きさが増加する一方で、ノイズレベルが変わらないためです。THD+N 値の線形に低下していることから、THD+N はノイズによって支配されていることがわかります。ヘッドフォン出力の振幅はライン出力に比べて約 12dB 低く、そのため THD+N の結果もわずかに悪化しています。

500Hz の正弦波入力、サンプリング周波数 = 192kSPS

**図 3-7. ライン出力およびヘッドホン出力の THD+N と入力レベルの関係**

図 3-8 に示されている動作は、DAC11001B のトラック アンド ホールド回路が DAC11001A と比較して性能向上していることを示しています。DAC11001B は、高周波領域でも THD+N プロファイルがよりフラットに維持されます。

図 3-8. ライン出力 THD+N と周波数および振幅の関係

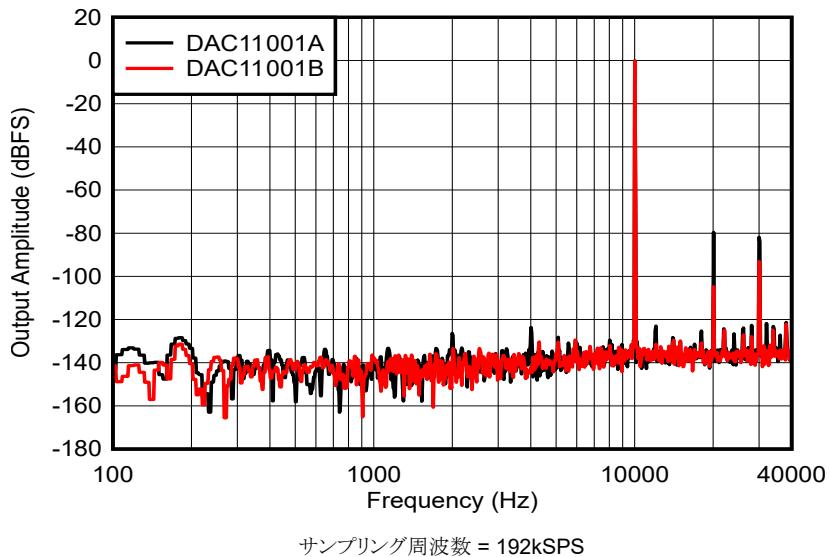

図 3-9 は、10k の信号を用いた DAC11001 のノイズおよび高調波性能を示しています。

図 3-9. 可聴帯域における 10kHz 正弦波の FFT

### 3.3.3 ダイナミックレンジの測定

図 3-10. ダイナミックレンジ測定のセットアップ

表 3-8. ダイナミックレンジ入力のフィルタ

| サンプルレート | フィルタ                                      |

|---------|-------------------------------------------|

| 48kSPS  | 22Hz ハイパスフィルタ、20kHz AES17 ローパスフィルタ、A 特性補正 |

| 96kSPS  | 22Hz ハイパスフィルタ、40kHz AES17 ローパスフィルタ、A 特性補正 |

| 192kSPS | 22Hz ハイパスフィルタ、40kHz AES17 ローパスフィルタ、A 特性補正 |

### 3.3.4 ダイナミックレンジの結果

表 3-9 に、DAC11001 のダイナミックレンジを示します。

表 3-9. ダイナミックレンジの測定結果

| 入力振幅    | トーン周波数 | サンプルレート               |                       |                       |

|---------|--------|-----------------------|-----------------------|-----------------------|

|         |        | 48kSPS                | 96kSPS                | 192kSPS               |

| -60dBFS | 1kHz   | -117dB (THD+N: -57dB) | -117dB (THD+N: -57dB) | -115dB (THD+N: -55dB) |

|         | 2kHz   | -118dB (THD+N: -58dB) | -117dB (THD+N: -57dB) | -115dB (THD+N: -55dB) |

|         | 10kHz  | -113dB (THD+N: -53dB) | -118dB (THD+N: -58dB) | -119dB (THD+N: -59dB) |

### 3.3.5 評価基板の信号対雑音比

図 3-11 に、SNR 測定のセットアップを示します。

図 3-11. SNR 測定のセットアップ

**表 3-10. SNR 入力フィルタ**

| サンプルレート | フィルタ                                        |

|---------|---------------------------------------------|

| 48kSPS  | 22Hz ハイパス フィルタ、20kHz AES17 ローパス フィルタ、A 特性補正 |

| 96kSPS  | 22Hz ハイパス フィルタ、40kHz AES17 ローパス フィルタ、A 特性補正 |

| 192kSPS | 22Hz ハイパス フィルタ、40kHz AES17 ローパス フィルタ、A 特性補正 |

**3.3.6 SNR の結果**

表 3-11 と表 3-12 は、DAC11001A と DAC11001B の SNR 結果を示します。デジタルトランスマッタからノイズが発生するため、SNR がわずかに低下しています。デジタルトランスマッタをオフにした場合の SNR は 表 3-13 に示されています。

**表 3-11. DAC11001A 信号対雑音比測定**

| 入力振幅            | トーン周波数 | サンプルレート                |                        |                       |

|-----------------|--------|------------------------|------------------------|-----------------------|

|                 |        | 48kSPS                 | 96kSPS                 | 192kSPS               |

| 100% フルスケール     | 1kHz   | 2.115V <sub>RMS</sub>  | 2.112V <sub>RMS</sub>  | 2.112V <sub>RMS</sub> |

| 0% フルスケール、ディザなし | 該当なし   | 1.893μV <sub>RMS</sub> | 2.038μV <sub>RMS</sub> | 2.29μV <sub>RMS</sub> |

| SNR の計算値        |        | 120.9dB                | 120.3dB                | 119.3dB               |

**表 3-12. DAC11001B 信号対雑音比測定**

| 入力振幅            | トーン周波数 | サンプルレート                |                        |                        |

|-----------------|--------|------------------------|------------------------|------------------------|

|                 |        | 48kSPS                 | 96kSPS                 | 192kSPS                |

| 100% フルスケール     | 1kHz   | 2.115V <sub>RMS</sub>  | 2.112V <sub>RMS</sub>  | 2.112V <sub>RMS</sub>  |

| 0% フルスケール、TX なし | 該当なし   | 1.858μV <sub>RMS</sub> | 2.039μV <sub>RMS</sub> | 2.325μV <sub>RMS</sub> |

| SNR の計算値        |        | 121.1dB                | 120.3dB                | 119.2dB                |

**表 3-13. DAC11001 デジタルなしの信号対雑音比測定**

| 入力振幅            | トーン周波数 | 結果                     |

|-----------------|--------|------------------------|

| 100% フルスケール     | 1kHz   | 2.115V <sub>RMS</sub>  |

| 0% フルスケール、TX なし | 該当なし   | 1.732μV <sub>RMS</sub> |

| SNR の計算値        |        | 121.7dB                |

## 4 デザイン ファイル

### 4.1 回路図

回路図をダウンロードするには、[TIDA-060031](#) のデザイン ファイルを参照してください。

### 4.2 部品表

部品表 (BOM) をダウンロードするには、[TIDA-060031](#) のデザイン ファイルを参照してください。

### 4.3 PCB レイアウトに関する推奨事項

#### 4.3.1 レイアウト プリント

レイヤ プロットをダウンロードするには、[TIDA-060031](#) のデザイン ファイルを参照してください。

### 4.4 Altium プロジェクト

Altium Designer® のプロジェクト ファイルをダウンロードするには、[TIDA-060031](#) のデザイン ファイルを参照してください。

### 4.5 ガーバー ファイル

ガーバー ファイルをダウンロードするには、[TIDA-060031](#) のデザイン ファイルを参照してください。

### 4.6 アセンブリの図面

アセンブリの図面をダウンロードするには、[TIDA-060031](#) のデザイン ファイルを参照してください。

## 5 関連資料

1. テキサス インスツルメンツ、[DACx1001 20 ビット、18 ビット、16 ビット、低ノイズ、超低高調波歪み、高速セトリング、高電圧出力のデジタル/アナログ コンバータ \(DAC\) データシート](#)

2. テキサス インスツルメンツ、[DAC11001B 20 ビット、低ノイズ、超低高調波歪み、高速セトリング、高電圧出力、D/A コンバータ \(DAC\) データシート](#)

3. テキサス・インスツルメンツ、オーディオ回路におけるオペアンプのノイズの理解 アプリケーション レポート

4. テキサス・インスツルメンツ、[電圧リファレンスを使用した設計のヒントとコツ e-Book](#)

### 5.1 サポート・リソース

テキサス・インスツルメンツ E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツルメンツの[使用条件](#)を参照してください。

### 5.2 商標

テキサス・インスツルメンツの™, Burr-Brown™, SoundPlus™, PowerPAD™, TINA-TI™, PurePath™, and テキサス・インスツルメンツ E2E™ are trademarks of Texas Instruments.

TOSLINK® is a registered trademark of Toshiba Electronics Devices and Storage Corporation.

Microsoft® and Windows® are registered trademarks of Microsoft Corporation.

Altium Designer® is a registered trademark of Altium LLC or its affiliated companies.

すべての商標は、それぞれの所有者に帰属します。

## 6 著者について

**PAUL FROST** (メンバー、グループ技術スタッフ) は、高精度 D/A コンバータ チームのアプリケーションおよび検証マネージャです。アリゾナ大学でコンピュータ工学の学士号を取得しています。

**ERIN BOWRIE** は、高精度 D/A コンバータ チームのアプリケーション エンジニアです。サンタクララ大学で電気工学の理学士号を取得しました。

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月