## User's Guide

# Jacinto7 評価基板インフォティメント拡張

### 概要

この資料では、Jacinto7 評価基板 – インフォティメント拡張 (INFO) 基板のハードウェアアーキテクチャについて説明します。INFO は、Jacinto7 共通プロセッサ基板と接続する拡張基板の 1 つです。

このリファレンスデザインは HDMI® 技術を採用しています。

---

| 目次                                      |    |

|-----------------------------------------|----|

| 1 はじめに.....                             | 3  |

| 1.1 主な特長.....                           | 3  |

| 2 インフォティメント拡張基板の概要.....                 | 4  |

| 2.1 インフォティメント拡張基板の識別.....               | 4  |

| 2.2 インフォティメント拡張基板部品の識別.....             | 5  |

| 3 インフォティメント拡張基板 - ユーザー設定/構成.....        | 7  |

| 3.1 インフォティメント拡張基板と CP ボードの接続.....       | 7  |

| 3.2 電源要件.....                           | 8  |

| 3.3 評価基板のリセット/割り込みプッシュボタン.....          | 9  |

| 3.4 評価基板構成の DIP スイッチ.....               | 9  |

| 4 インフォティメント拡張基板のハードウェアーアーキテクチャ.....     | 10 |

| 4.1 インフォティメント拡張基板のハードウェアの最上図.....       | 10 |

| 4.2 拡張コネクタ.....                         | 11 |

| 4.3 基板 ID EEPROM.....                   | 13 |

| 4.4 オーディオ コーデック インターフェイス.....           | 14 |

| 4.5 FPD Link デシリアルインターフェイス (オーディオ)..... | 15 |

| 4.6 DIR インターフェイス.....                   | 16 |

| 4.7 DIT インターフェイス.....                   | 16 |

| 4.8 レガシーオーディオ/JAMR3 コネクタ.....           | 17 |

| 4.9 VIN/VOUT マルチプレクサの選択.....            | 20 |

| 4.10 HDMI インターフェイスブリッジ.....             | 21 |

| 4.11 FPD Link ディスプレイシリアルインターフェイス.....   | 22 |

| 4.12 並列カメラインターフェイス.....                 | 23 |

| 5 Jacinto7 評価基板のインターフェイス/IO マッピング.....  | 26 |

| 5.1 インターフェイス マッピング.....                 | 26 |

| 5.2 インフォティメント基板の GPIO マッピング.....        | 27 |

| 5.3 I2C アドレス マッピング.....                 | 28 |

| 6 改訂履歴.....                             | 29 |

## 商標

すべての商標は、それぞれの所有者に帰属します。

HDMI、HDMI High-Definition Multimedia Interface、HDMI トレードドレス、および HDMI ロゴは、HDMI Licensing Administrator Inc. の商標または登録商標です。

## 1 はじめに

Jacinto7 評価基板は、開発および評価用のシステムであり、Jacinto7 プロセッサファミリを利用したソフトウェア書き込みとハードウェア開発を可能にします。システムの主な要素は、評価基板のベース基板上で利用可能です。これにより、Jacinto7 プロセッサを含むほとんどの汎用型プロジェクトに必要な基本リソースを利用できます。

Jacinto7 評価基板は、以下の 2 枚の基板で構成されています：

- Jacinto7 システムオンモジュール (SOM) - Jacinto7 プロセッサ、その電源ソリューション、不揮発性メモリが含まれています。

- Jacinto7 共通プロセッサ基板 (CPB) - Jacinto7 プロセッサがサポートする、多様なメモリ、ペリフェラル、デバッグツールが含まれています。

提供された基本リソース以外に、拡張カードを使用して機能を追加できます。

### 1.1 主な特長

インフォティメント拡張基板の主な特長を以下に示します：

- オーディオ インターフェイス：

- 2 つのオーディオコーデックそれぞれに 3 つのステレオ入力と 4 つのステレオ出力を搭載

- FPD Link III 経由のオーディオ入力

- デジタルオーディオインターフェイス転送

- デジタルオーディオインターフェイスレシーバ

- ビデオインターフェイス：

- HDMI/FPD LINK III ディスプレイ出力

- LI/OV カメラ入力

- JAMR3 インターフェイス

- 基板 ID EEPROM

## 2 インフォテインメント拡張基板の概要

Jacinto7 EVM は、さまざまな種類の拡張基板をサポートでき、その 1 つはインフォテインメントです。すべての拡張基板がすべての Jacinto7 拡張基板で利用できるとは限りません。

フォティメント拡張基板をサポートしている Jacinto7 拡張基板のバージョンを確認するには、[セクション 5](#) を参照してください。

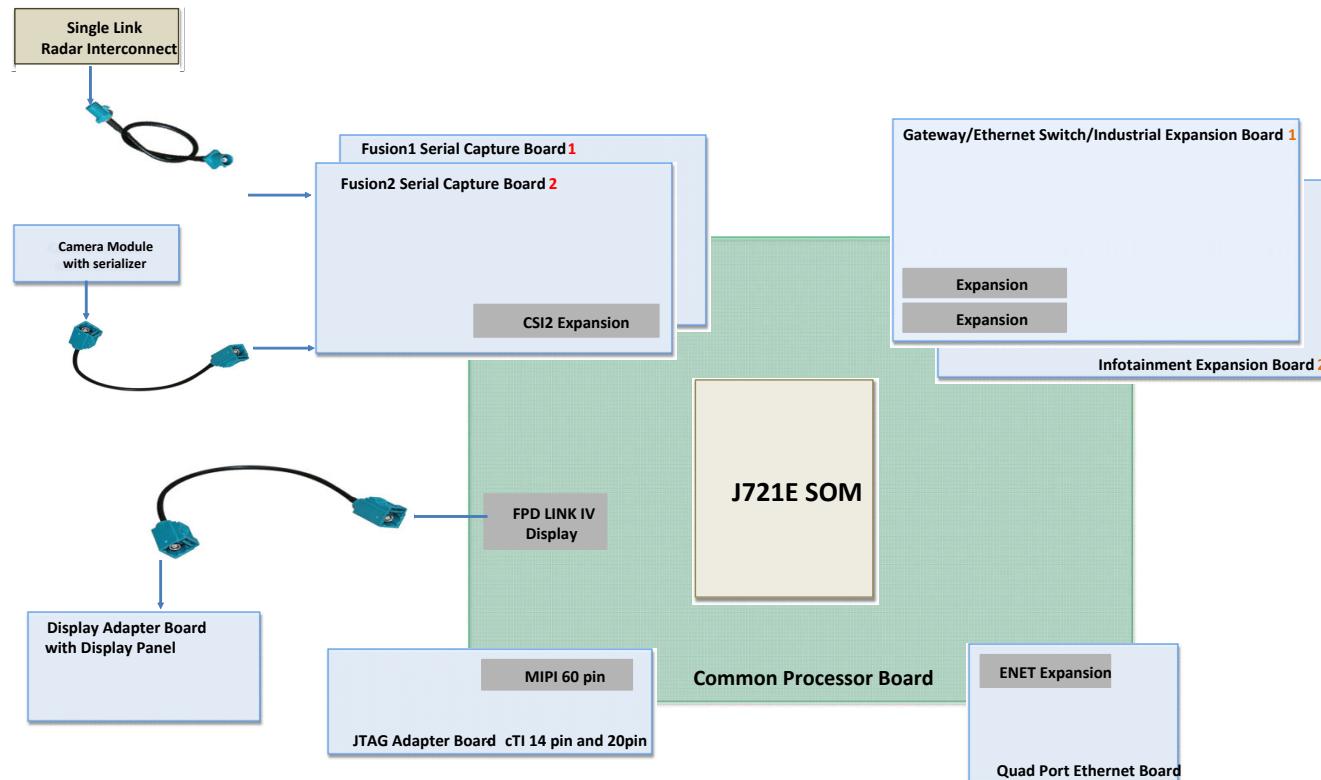

**図 2-1** に、Jacinto7 評価基板の全体的なアーキテクチャを示します。

- A. 拡張コネクタに一度に接続できる基板は 1 つのみです。

- B. CSI2 拡張コネクタに一度に接続できる基板は 1 つのみです。

**図 2-1. システムアーキテクチャインターフェイス**

### 2.1 インフォテインメント拡張基板の識別

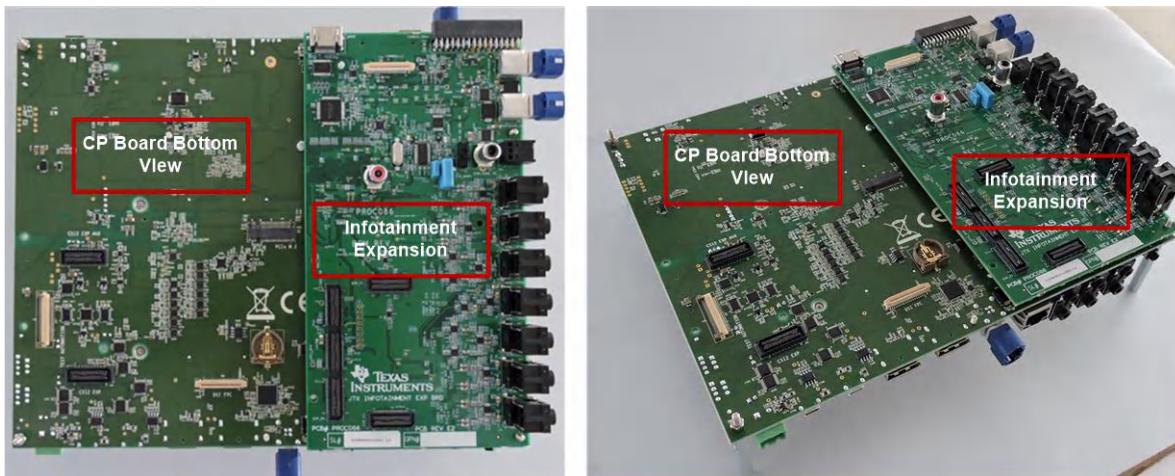

図 2-2. システムアセンブリ画像

## 2.2 インフォテインメント拡張基板部品の識別

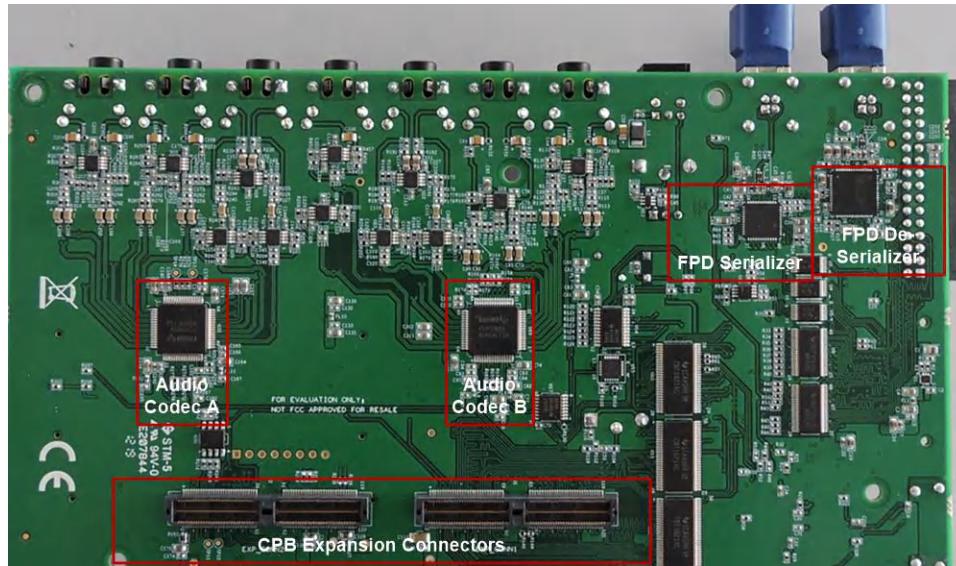

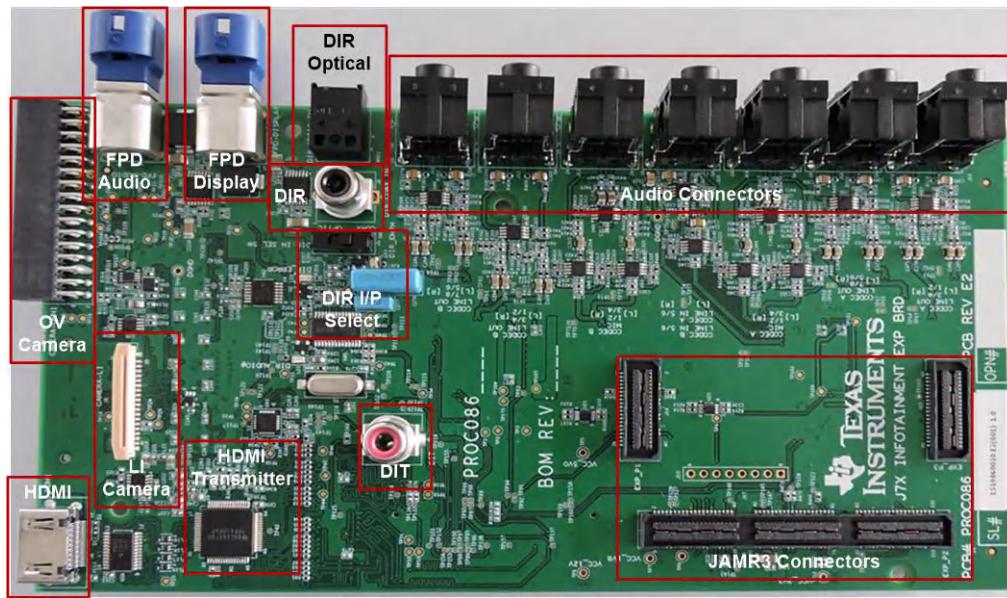

図 2-3. インフォテインメント拡張基板部品の識別

### 3 インフォティメント拡張基板 - ユーザー設定/構成

#### 3.1 インフォティメント拡張基板と CP ボードの接続

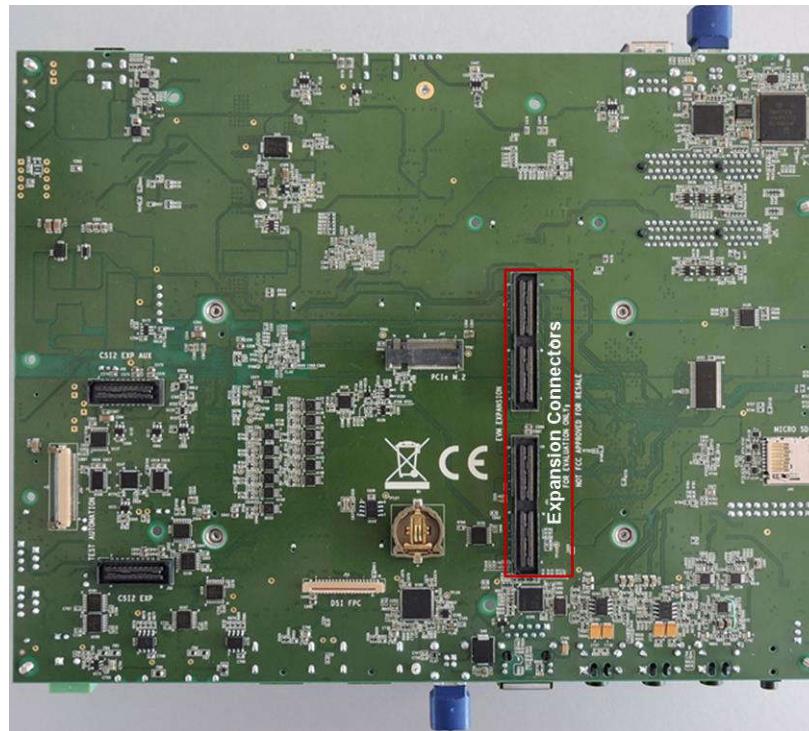

インフォティメント拡張基板は、Jacinto7 評価基板共通プロセッサ基板 (CPB) と接続します。インフォティメント上の拡張コネクタ J1 と J2 は、評価基板 CPB の拡張コネクタ J46 と J51 に接続されます。

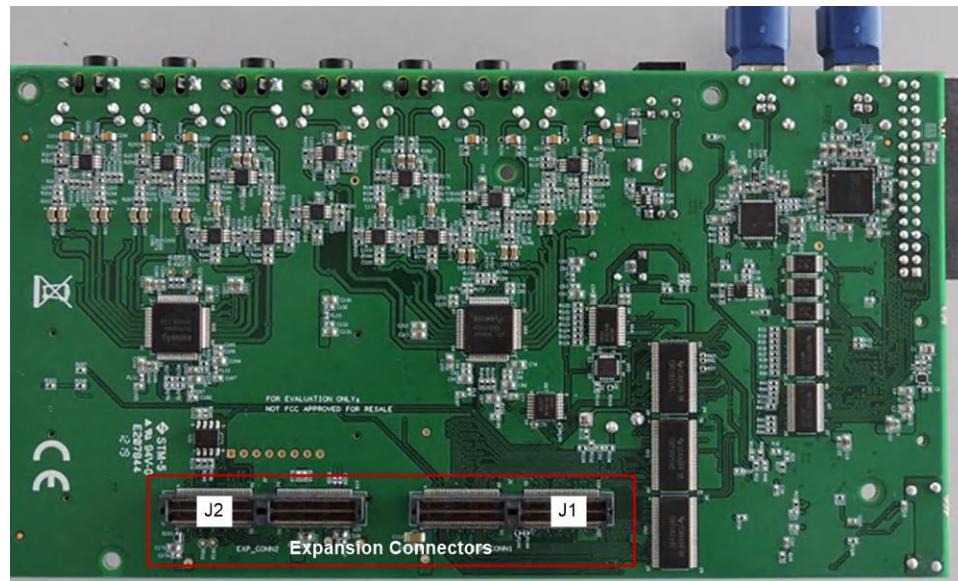

図 3-1. INFO Exp 基板上面の拡張コネクタ

図 3-2. Jacinto7 CP 基板底面の拡張コネクタ

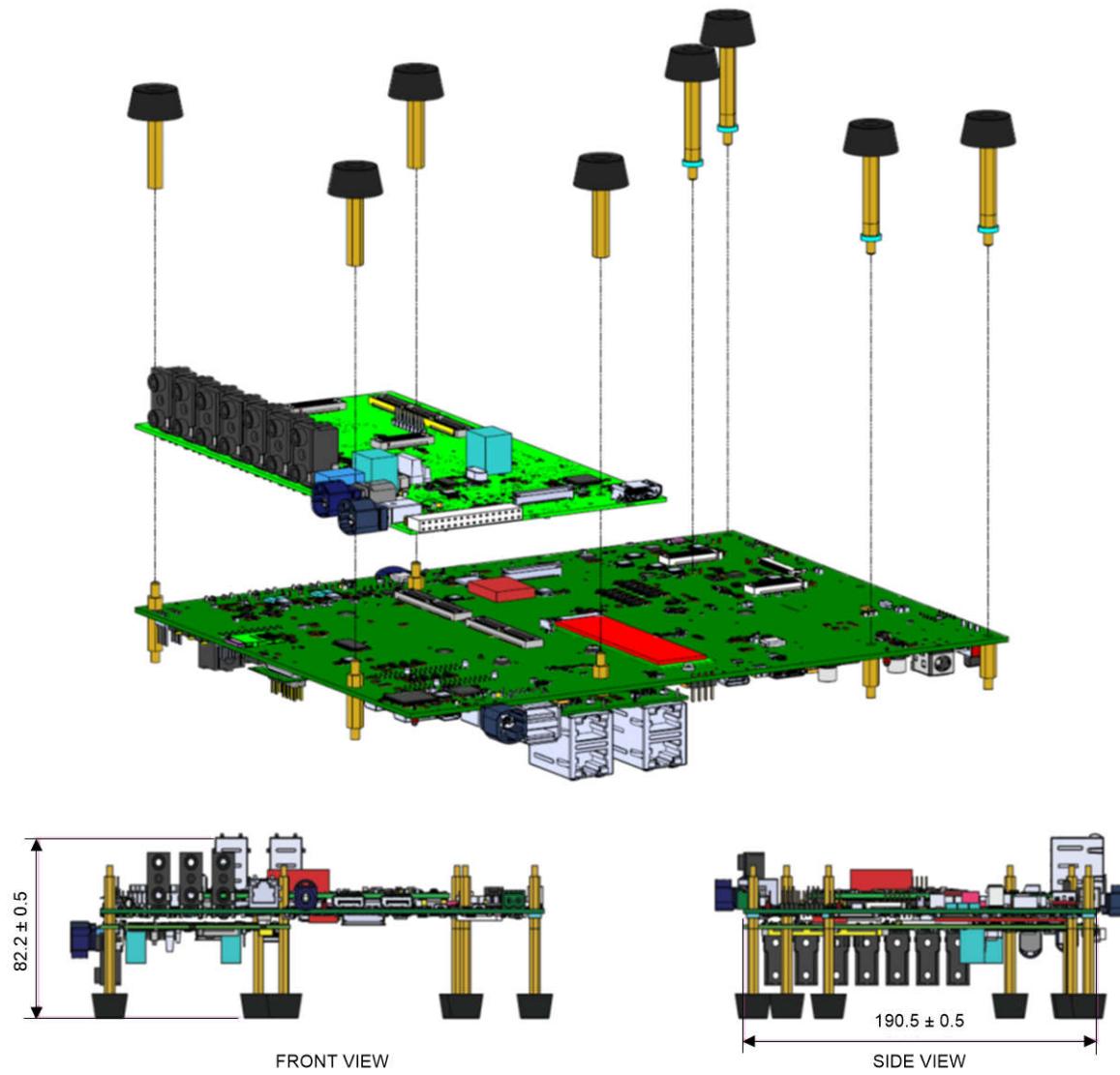

### 3.1.1 基板の組み立て手順

- 組み立て済み CP 基板キットを取り出します。

- CP 基板からスペーサーを取り外し、CP 基板の左側の B-B コネクタにインフォテインメント基板を接続します。

- 2mm の厚さのワッシャー (部品番号: RWM100A) を 4 つのスタンドオフに追加します (CSI 拡張基板を接続しない場合)。

- 8 つのスタンドオフをすべて固定します。

図 3-3. 基板の組み立ての手順

### 3.2 電源要件

インフォテインメントボードは Jacinto7 評価基板共通プロセッサ基板から電力を供給されるため、外部電源は不要です。12V、5V、3.3V、3.3V\_IO は CPB から利用されます。

カメラコネクタへの電力 (3.3V/1.8V) は、LDO を使用してインフォテインメント拡張基板上でローカルに生成され、LDO のイネーブルは CPB のスイッチにより制御されます。

No Power ON 表示 LED はインフォテインメント拡張基板にあります。

### 3.3 評価基板のリセット/割り込みプッシュボタン

Jacinto7 評価基板は、プロセッサにリセット入力とユーザー割り込みを提供する、複数のユーザープッシュボタンが用意されています。その場所と機能については、デバイス固有のユーザーズマニュアルを参照してください。

インフォティメント拡張基板では、規定のリセット/割り込みプッシュボタンを使用できません。

### 3.4 評価基板構成の DIP スイッチ

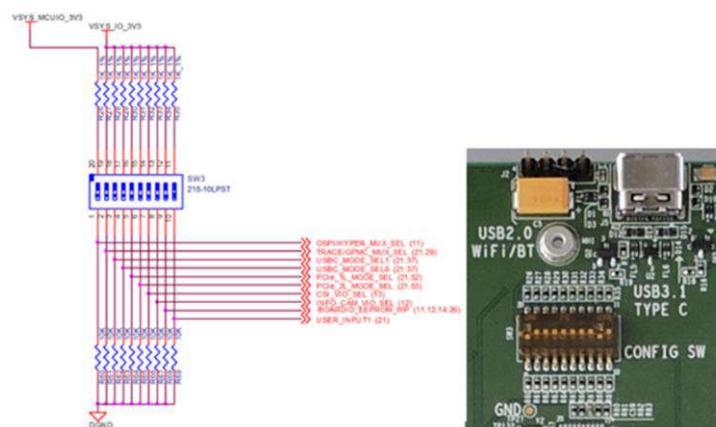

共通プロセッサ基板には、評価基板ペリフェラルの各種機能を設定するための専用評価基板構成スイッチ (SW3) が搭載されています (図 3-4 を参照)。構成 DIP スイッチ (SW3) は、CPB の上面、USB Type-C ポートのすぐ下に配置されています。

図 3-4. 評価基板構成の DIP スイッチ

表 3-1. 拡張基板で使用される Jacinto7 評価基板共通プロセッサ DIP スイッチ

| スイッチ名 | デフォルト条件 | 信号                | 動作                                                                                        |

|-------|---------|-------------------|-------------------------------------------------------------------------------------------|

| SW3.8 | オン      | INFO_CAM_VIO_SEL  | カメラ IO 電圧の '1' (ON) = 3.3V は LDO から選択されます<br>カメラ IO 電圧の '0' (OFF) = 1.8V LDO から選択されます     |

| SW3.9 | オン      | BOARDID_EEPROM_WP | 評価基板の構成 EEPROM 書き込み保護を設定<br>'0' (OFF) = 構成 EEPROM は更新可能<br>'1' (ON) = 構成 EEPROM は更新/保護不可能 |

## 4 インフォテインメント拡張基板のハードウェアアーキテクチャ

このセクションでは、インフォテインメント拡張基板のハードウェアアーキテクチャについて詳しく説明します。

### 4.1 インフォテインメント拡張基板のハードウェアの最上図

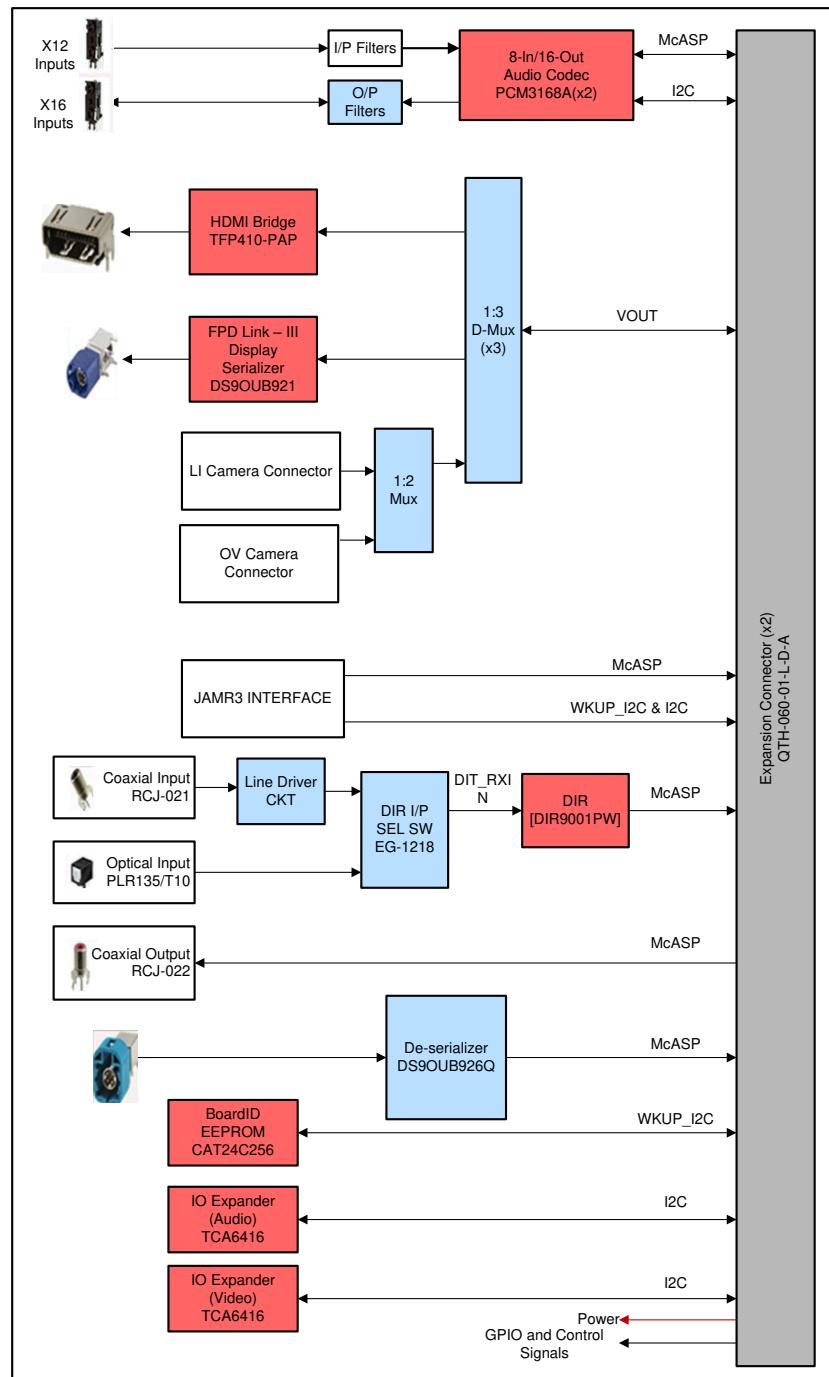

図 4-1 に、インフォテインメント拡張基板の機能ブロック図を示します

図 4-1. インフォテインメント拡張基板の機能ブロック図

上図のインターフェイスの一部は、特定の評価基板の依存関係です。すべてが Jacinto7 評価基板でサポートされているとは限りません。

特定の評価基板のプラットフォームでサポートされているインターフェイスについては、[セクション 5.1](#) を参照してください。

## 4.2 拡張コネクタ

インフォティメント基板には、Jacinto7 評価基板共通プロセッサ基板に接続するための 2 つの拡張コネクタ J1 と J2 (120 ピン Samtec コネクタ) があります。すべてのインフォティメントインターフェイス、電源、制御信号が、これらのコネクタに提供されます。

表 4-1 および 表 4-2 には、ピン配置/信号マッピング INFO 拡張コネクタが含まれています。表には、主要機能/ネット名のみが表示されています。

**表 4-1. J1 拡張コネクタのピン配置**

| ピン | ネット名              | ピン | ネット名             | ピン | ネット名             | ピン  | ネット名            |

|----|-------------------|----|------------------|----|------------------|-----|-----------------|

| 1  | DGND              | 31 | VOUT0_DATA10     | 61 | McASP0_AXR3      | 91  | CAM_SEL_OV#     |

| 2  | VCC_12V0          | 32 | VOUT0_DATA23     | 62 | NC               | 92  | McASP6_ACLKR    |

| 3  | DGND              | 33 | VOUT0_VSYNC      | 63 | WKUP_I2C0_SDA    | 93  | McASP2_AXR0     |

| 4  | VCC_12V0          | 34 | VOUT0_DE         | 64 | SOC_PORZ_OUT     | 94  | MUX_McASP6_AXR0 |

| 5  | DGND              | 35 | NC               | 65 | WKUP_I2C0_SCL    | 95  | DGND            |

| 6  | VCC_12V0          | 36 | VOUT0_PCLK       | 66 | NC               | 96  | DGND            |

| 7  | McASP1_AXR3       | 37 | DGND             | 67 | DGND             | 97  | NC              |

| 8  | VOUT0_DATA15      | 38 | DGND             | 68 | DGND             | 98  | NC              |

| 9  | JAMR3_GPIO1       | 39 | VOUT0_DATA0      | 69 | McASP0_AXR0      | 99  | NC              |

| 10 | VOUT0_DATA14      | 40 | VOUT0_DATA19     | 70 | McASP0_AXR8      | 100 | JAMR3_I2S_DB    |

| 11 | McASP1_AXR2       | 41 | VOUT0_DATA2      | 71 | McASP0_AXR2      | 101 | SPI3_D0         |

| 12 | VOUT0_HSYNC       | 42 | VOUT0_DATA16     | 72 | McASP0_AXR7      | 102 | McASP0_AXR13    |

| 13 | McASP1_AXR0       | 43 | VOUT0_DATA1      | 73 | McASP0_AXR4      | 103 | SPI3_D1         |

| 14 | VOUT0_DATA11      | 44 | VOUT0_DATA20     | 74 | McASP0_AXR11     | 104 | NC              |

| 15 | McASP1_AXR1       | 45 | VOUT0_DATA3      | 75 | UB926_GPIO2      | 105 | SPI3_CLK        |

| 16 | VOUT0_DATA13      | 46 | VOUT0_DATA18     | 76 | McASP0_AXR10     | 106 | NC              |

| 17 | JAMR3_GPIO0       | 47 | VOUT0_DATA4      | 77 | McASP0_AXR1      | 107 | DGND            |

| 18 | VOUT0_DATA12      | 48 | VOUT0_DATA21     | 78 | McASP0_AXR9      | 108 | DGND            |

| 19 | DGND              | 49 | VOUT0_DATA6      | 79 | UB926_GPIO3      | 109 | I2C0_SCL        |

| 20 | DGND              | 50 | VOUT0_DATA17     | 80 | McASP0_AXR12     | 110 | McASP1_ACLKX    |

| 21 | VOUT0_EXTPCLKIN   | 51 | DGND             | 81 | DGND             | 111 | I2C0_SDA        |

| 22 | CON_VPFE0_DATA6   | 52 | DGND             | 82 | DGND             | 112 | SOC_I2C2_SCL    |

| 23 | VOUT0_DATA5       | 53 | McASP0_AXR5      | 83 | McASP1_AXR8      | 113 | I2C1_SCL        |

| 24 | CON_VPFE0_DATA7   | 54 | CON_VPFE0_DATA12 | 84 | MUX_McASP6_ACLKX | 114 | SOC_I2C2_SDA    |

| 25 | VOUT0_DATA7       | 55 | McASP0_AXR6      | 85 | McASP1_AXR7      | 115 | I2C1_SDA        |

| 26 | AUDIO_EXT_REFCLK1 | 56 | CON_VPFE0_DATA11 | 86 | McASP6_AFSR      | 116 | NC              |

| 27 | VOUT0_DATA8       | 57 | McASP0_ACLKX     | 87 | CON_UB921_INTB   | 117 | NC              |

| 28 | VOUT0_DATA22      | 58 | SPI3_CS0         | 88 | MUX_McASP6_AFSX  | 118 | EXP_RSTz        |

| 29 | VOUT0_DATA9       | 59 | McASP0_AFSX      | 89 | JAMR3_GPIO2      | 119 | DGND            |

| 30 | UB926_GPIO1       | 60 | McASP1_AFSX      | 90 | MUX_McASP6_AXR1  | 120 | DGND            |

表 4-2. J2 拡張コネクタのピン配置

| ピン | ネット名              | ピン | ネット名             | ピン | ネット名             | ピン  | ネット名            |

|----|-------------------|----|------------------|----|------------------|-----|-----------------|

| 1  | DGND              | 31 | VOUT0_DATA10     | 61 | McASP0_AXR3      | 91  | CAM_SEL_OV#     |

| 2  | VCC_12V0          | 32 | VOUT0_DATA23     | 62 | NC               | 92  | McASP6_ACLKR    |

| 3  | DGND              | 33 | VOUT0_VSYNC      | 63 | WKUP_I2C0_SDA    | 93  | McASP2_AXR0     |

| 4  | VCC_12V0          | 34 | VOUT0_DE         | 64 | SOC_PORZ_OUT     | 94  | MUX_McASP6_AXR0 |

| 5  | DGND              | 35 | NC               | 65 | WKUP_I2C0_SCL    | 95  | DGND            |

| 6  | VCC_12V0          | 36 | VOUT0_PCLK       | 66 | NC               | 96  | DGND            |

| 7  | McASP1_AXR3       | 37 | DGND             | 67 | DGND             | 97  | NC              |

| 8  | VOUT0_DATA15      | 38 | DGND             | 68 | DGND             | 98  | NC              |

| 9  | JAMR3_GPIO1       | 39 | VOUT0_DATA0      | 69 | McASP0_AXR0      | 99  | NC              |

| 10 | VOUT0_DATA14      | 40 | VOUT0_DATA19     | 70 | McASP0_AXR8      | 100 | JAMR3_I2S_DB    |

| 11 | McASP1_AXR2       | 41 | VOUT0_DATA2      | 71 | McASP0_AXR2      | 101 | SPI3_D0         |

| 12 | VOUT0_HSYNC       | 42 | VOUT0_DATA16     | 72 | McASP0_AXR7      | 102 | McASP0_AXR13    |

| 13 | McASP1_AXR0       | 43 | VOUT0_DATA1      | 73 | McASP0_AXR4      | 103 | SPI3_D1         |

| 14 | VOUT0_DATA11      | 44 | VOUT0_DATA20     | 74 | McASP0_AXR11     | 104 | NC              |

| 15 | McASP1_AXR1       | 45 | VOUT0_DATA3      | 75 | UB926_GPIO2      | 105 | SPI3_CLK        |

| 16 | VOUT0_DATA13      | 46 | VOUT0_DATA18     | 76 | McASP0_AXR10     | 106 | NC              |

| 17 | JAMR3_GPIO0       | 47 | VOUT0_DATA4      | 77 | McASP0_AXR1      | 107 | DGND            |

| 18 | VOUT0_DATA12      | 48 | VOUT0_DATA21     | 78 | McASP0_AXR9      | 108 | DGND            |

| 19 | DGND              | 49 | VOUT0_DATA6      | 79 | UB926_GPIO3      | 109 | I2C0_SCL        |

| 20 | DGND              | 50 | VOUT0_DATA17     | 80 | McASP0_AXR12     | 110 | McASP1_ACLKX    |

| 21 | VOUT0_EXTPCLKIN   | 51 | DGND             | 81 | DGND             | 111 | I2C0_SDA        |

| 22 | CON_VPFE0_DATA6   | 52 | DGND             | 82 | DGND             | 112 | SOC_I2C2_SCL    |

| 23 | VOUT0_DATA5       | 53 | McASP0_AXR5      | 83 | McASP1_AXR8      | 113 | I2C1_SCL        |

| 24 | CON_VPFE0_DATA7   | 54 | CON_VPFE0_DATA12 | 84 | MUX_McASP6_ACLKX | 114 | SOC_I2C2_SDA    |

| 25 | VOUT0_DATA7       | 55 | McASP0_AXR6      | 85 | McASP1_AXR7      | 115 | I2C1_SDA        |

| 26 | AUDIO_EXT_REFCLK1 | 56 | CON_VPFE0_DATA11 | 86 | McASP6_AFSR      | 116 | NC              |

| 27 | VOUT0_DATA8       | 57 | McASP0_ACLKX     | 87 | CON_UB921_INTB   | 117 | NC              |

| 28 | VOUT0_DATA22      | 58 | SPI3_CS0         | 88 | MUX_McASP6_AFSX  | 118 | EXP_RSTz        |

| 29 | VOUT0_DATA9       | 59 | McASP0_AFSX      | 89 | JAMR3_GPIO2      | 119 | DGND            |

| 30 | UB926_GPIO1       | 60 | McASP1_AFSX      | 90 | MUX_McASP6_AXR1  | 120 | DGND            |

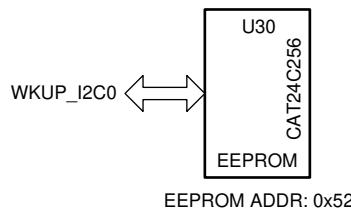

## 4.3 基板 ID EEPROM

インフォティメント拡張基板は、オンボード EEPROM に保存されているバージョンおよびシリアル番号で識別されます。EEPROM CAT24C256WI-GT3 には、アドレス 0x52 WKUP\_I2C0 I2C バスからアクセスできます。

図 4-2. 基板 ID EEPROM

表 4-3. 基板 ID メモリヘッダー情報

| ヘッダー     | フィールド名     | サイズ(バイト) | 説明                   | EEPROM に書き込まれる値 |

|----------|------------|----------|----------------------|-----------------|

|          | MAGIC      | 4        | マジックナンバー             | 0xEE3355AA      |

|          | タイプ        | 1        | 固定長および可変位置基板 ID ヘッダー | 0x1             |

|          |            | 2        | ペイロードのサイズ            | 0xF7            |

| BRD_INFO | タイプ        | 1        | ペイロードタイプ             | 0x10            |

|          | 長さ         | 2        | 次のヘッダーへのオフセット        | 0x002E          |

|          | Board_Name | 16       | 基板の名前                | “J7X-INFO-EXP”  |

|          | Design_Rev | 2        | 設計のリビジョン番号           | 変数              |

|          | PROC_Nbr   | 4        | PROC 番号              | “0086”          |

|          | バリアント      | 2        | 設計バリアント番号            | 変数              |

|          | PCB_Rev    | 2        | PCB のリビジョン番号         | 変数              |

|          | SCHBOM_Rev | 2        | 回路図のリビジョン番号          | 変数              |

|          | SWR_Rev    | 2        | 最初のソフトウェアリリース番号      | 変数              |

|          | VendorID   | 2        | ベンダ ID               | 変数              |

|          | Build_Week | 2        | 製造年の週                | 変数              |

|          | Build_Year | 2        | 製造年                  | 変数              |

|          | BoardID    | 6        | 予約済み。値は入力されていません     | 該当なし            |

|          | Serial_Nbr | 4        | 基板番号の増分              | 変数              |

上記の基板 ID の詳細は、アドレス 0x0h から EEPROM にプログラムされます。

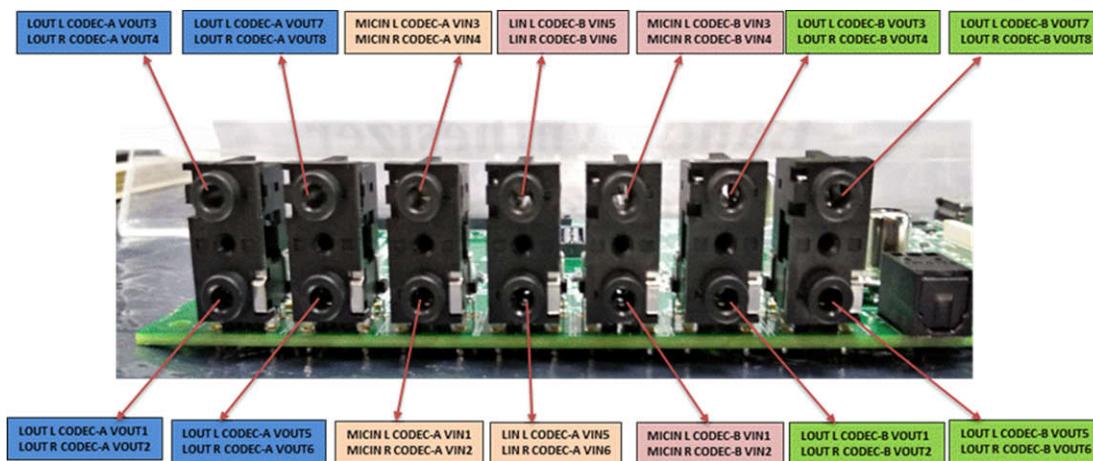

## 4.4 オーディオ コーデック インターフェイス

インフォテインメント拡張基板には、TI の車載オーディオコーデック IC メーカー部品番号 PCM3168A-Q1 が 2 つ搭載され、それぞれ 3 つのステレオ入力と 4 つのステレオ出力をサポートしています。外部オーディオの入力および出力信号は、3.5mm スタックオーディオジャック (ステレオモード) メーカー部品番号 STX-4235-3/3-N に適切なフィルタ回路を使用して終端接続されます。

TI のオーディオ OPAMP メーカー部品番号 OPA2322AI は、シングルエンドを差動に変換、および差動からシングルエンド信号に変換するために使用します。MODE ピンを Low に保持して、I2C を制御インターフェイスとして選択し、コーデックを I2C インターフェイス経由で構成します。コーデック B とコーデック A のデフォルトの I2C アドレスは、それぞれ 0x46 と 0x47 に設定されます。デバイスのリセットは、I2C GPIO エクスパンダで制御されます。

マイクロフォン入力ポートはアクティブマイクとパッシブマイク用に構成でき、ライン入力用に構成することもできます。こ**表 4-4** に示すように、の入力ポート構成は抵抗オプションで設定できます。

**表 4-4. CODEC-A および CODEC-B 用 MIC I/P ポート構成**

|                        |                | インストール         | 削除             |

|------------------------|----------------|----------------|----------------|

| PASSIVE-MIC<br>(デフォルト) | BIAS + PREAMP  | R2, R3, R5, R6 | R1, R4         |

| ACTIVE-MIC             | BIAS のみ        | R1, R2, R4, R5 | R3, R6         |

| LINE-INPUT             | BIAS/PREAMP なし | R1, R4         | R2, R3, R5, R6 |

### 4.4.1 ポートマッピング

7 x 標準、3.5mm スタック 2by1 ステレオオーディオジャックメーカー部品番号 STX-4235-3/3-N は以下に提供:

- 4x – MIC IN

- 2x – Line IN

- 8x – Line OUT

インフォテインメント拡張基板のオーディオポートは、**図 4-3** に示すように、オーディオコーデックにマッピングされます。

**図 4-3. オーディオ入力と出力**

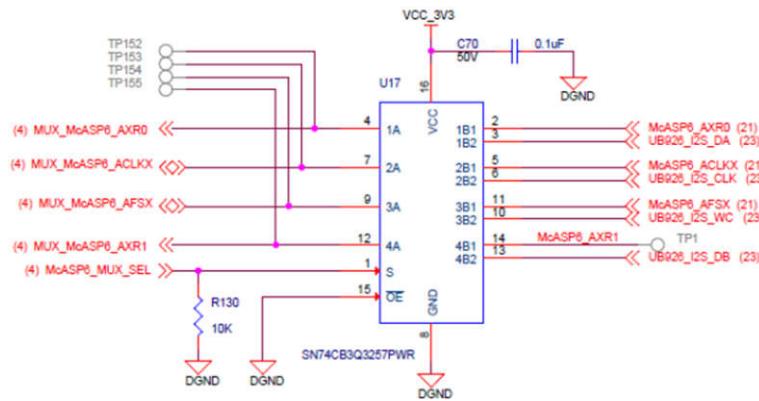

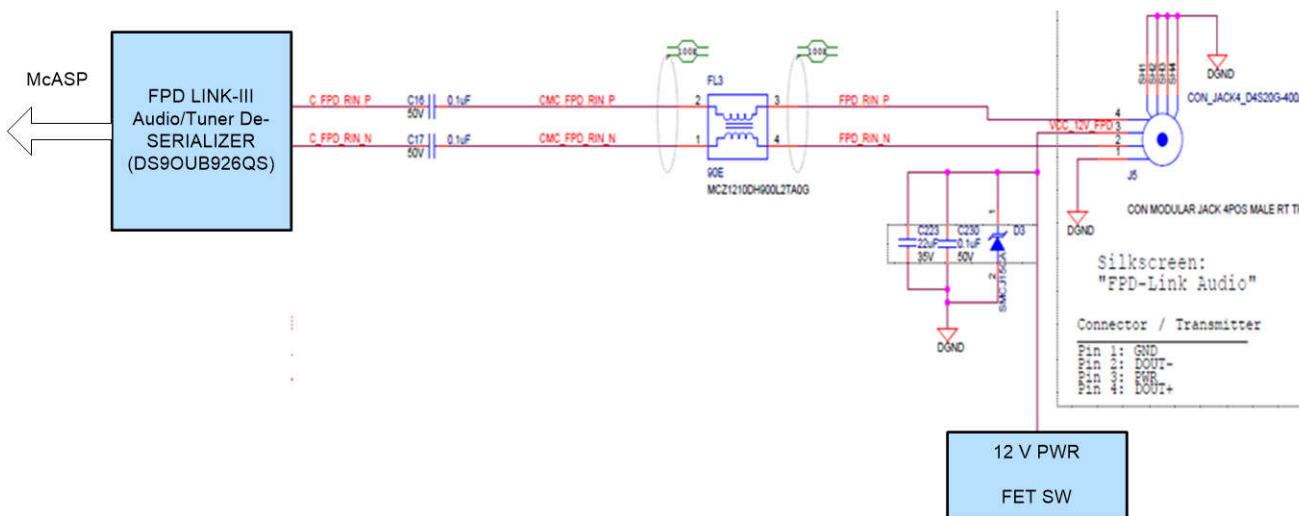

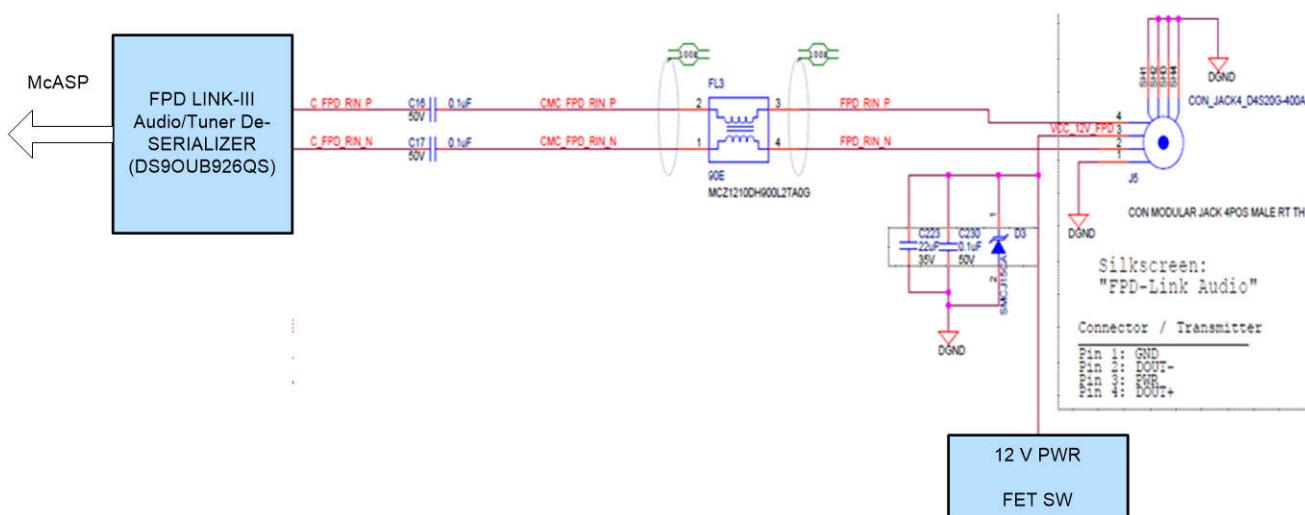

## 4.5 FPD Link デシリアルライザインターフェイス (オーディオ)

インフォティメント拡張基板は FPD Link III デシリアルライザ IC のメーカー部品番号 DS90UB926QSQE を使用して FPD-Link インターフェイスからのオーディオ信号を回復します。デシリアルライザは、デジタルリンク全体で、最大 8 つのデジタルオーディオチャネル、フレーム同期、I2S チャネルを回復します。HSD コネクタメーカー部品番号 D4S20G-400A5-C は入力信号を受信するために使用します。

回復された 8 つのオーディオデータ信号と AFSX は、CP 基板の B-B コネクタ経由で J7 SoC の McASP ポートに直接接続されます。デシリアルライザからの I2S 信号は、インフォティメント基板上の DIR/FPDLink マルチプレクサ選択 IC (U17) を経由して、J7 SoC の McASP ポートに接続されます。GPIO エクスパンダを介したマルチプレクサチャネル選択については、[セクション 5.2](#) を参照してください。

図 4-4. DIR/FPDLink マルチプレクサ選択

デシリアルライザとリモートデバイスの制御/構成に使用する SOC からの I2C 信号。7'b I2C アドレスを 0x3B に設定する ID[X] ピンには 57.6K Ω プルアップと 121K Ω プルダウンが装備されています。

デシリアルライザのデフォルトモード設定は mode0 です。各種モードを設定するための抵抗実装オプションについては、[図 4-5](#) を参照してください。

外部基板に電源を供給するため、パワースイッチ TPS1H100AQPWPRQ1 を使用して HSD コネクタに +12V の電力を供給します。デフォルトではパワースイッチはオフで、GPIO エクスパンダ信号 (PWR\_SW\_UB926) で有効にできます。

図 4-5. FPD Link デシリアルライザインターフェイス

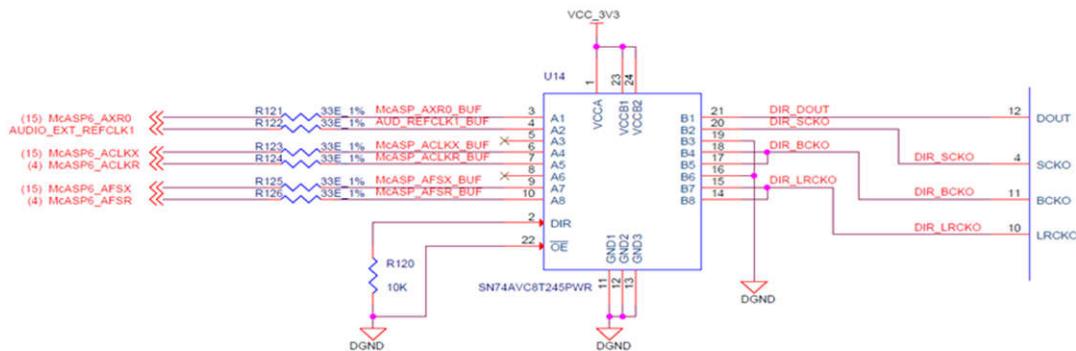

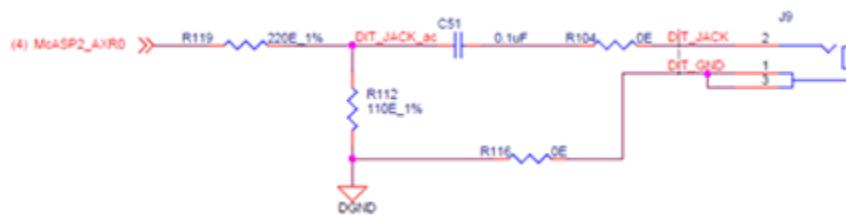

## 4.6 DIR インターフェイス

インフォティメント拡張基板には、TI のデジタルオーディオインターフェイスレシーバ (DIR) IC のメーカー部品番号 DIR9001-Q1 が搭載され、外部デジタルオーディオ入力信号を処理します。DIR IC の DOUT、SCKO、BCKO、LRCKO 出力を CP 基板の McASP 信号に接続するには、INFO 基板上の MUX/DMUX IC U14 のメーカー部品番号 SN74AVC8T245PWR および U17 IC メーカー部品番号 SN74CB3Q3257PWR を使用します。

図 4-8. DIT インターフェイス

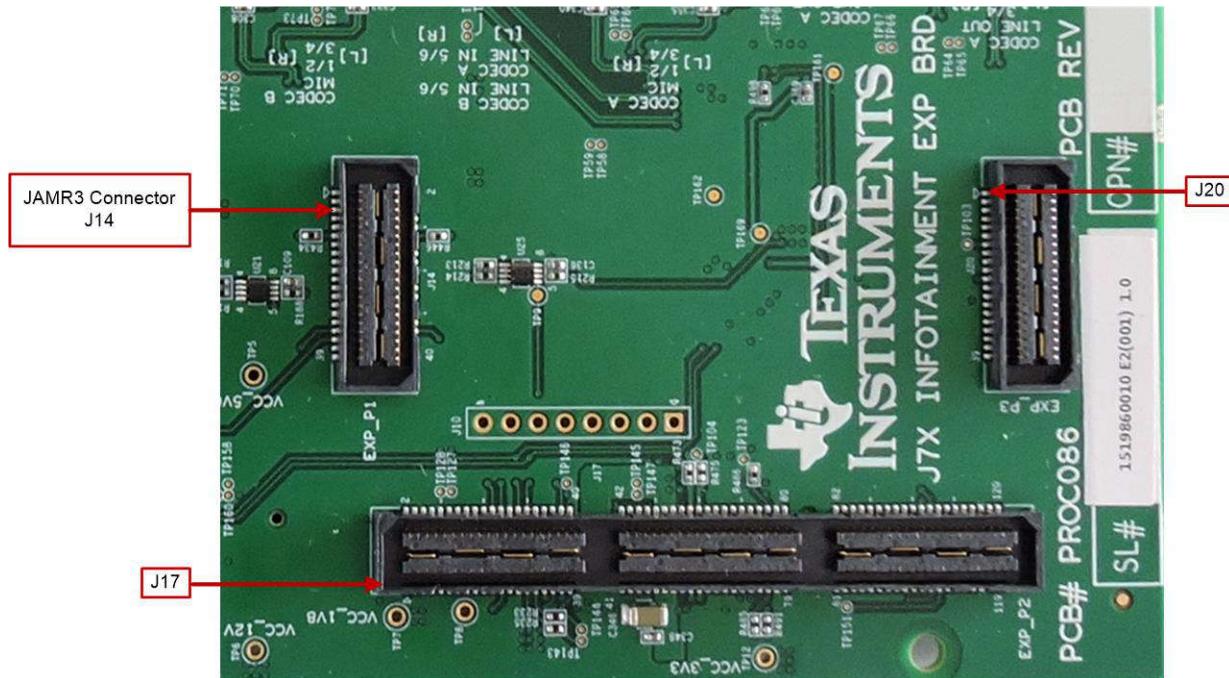

#### 4.8 レガシーオーディオ/JAMR3 コネクタ

インフォテインメント基板上では、レガシーオーディオ/JAMR3 拡張基板と接続するための 3 つの B-B 拡張コネクタが用意されています。

コネクタからの 8 つの McASP データ信号、フレーム同期、クロック信号は、INFO-CP B-B 拡張コネクタに直接接続します。WKUP\_I2C0 および I2C3 は、基板の ID 情報および構成にアクセスするためのコネクタに接続するインフォテインメント基板から信号を送信します。デバイスのリセットは、インフォテインメント基板の I2C GPIO エクスパンダで制御されます。

12V 電源は、拡張基板に電力を供給するインフォテインメント基板から利用できます。VCC\_3V3 電源は、拡張基板のレギュレータを有効にするため、拡張コネクタに接続されます。

表 4-6. J14 レガシーオーディオインターフェイスコネクタのピン配置

| J14 コネクタのピン配置 |              |      |             |

|---------------|--------------|------|-------------|

| ピン番号          | ネット名         | ピン番号 | ネット名        |

| 1             | NC           | 21   | NC          |

| 2             | DGND         | 22   | NC          |

| 3             | NC           | 23   | NC          |

| 4             | DGND         | 24   | NC          |

| 5             | NC           | 25   | NC          |

| 6             | NC           | 26   | NC          |

| 7             | NC           | 27   | NC          |

| 8             | NC           | 28   | NC          |

| 9             | NC           | 29   | DGND        |

| 10            | DGND         | 30   | DGND        |

| 11            | EXP_I2C4_SCL | 31   | NC          |

| 12            | EXP_I2C4_SDA | 32   | NC          |

| 13            | NC           | 33   | JAMR3_GPIO0 |

| 14            | NC           | 34   | JAMR3_GPIO1 |

| 15            | NC           | 35   | JAMR3_GPIO2 |

| 16            | NC           | 36   | NC          |

| 17            | NC           | 37   | NC          |

| 18            | NC           | 38   | NC          |

| 19            | DGND         | 39   | DGND        |

| 20            | DGND         | 40   | DGND        |

表 4-7. J20-JAMR3 インターフェイスコネクタのピン配置

| J20 コネクタのピン配置 |      |      |              |

|---------------|------|------|--------------|

| ピン番号          | ネット名 | ピン番号 | ネット名         |

| 1             | NC   | 21   | EXP_I2C2_SDA |

| 2             | NC   | 22   | EXP_I2C2_SCL |

| 3             | NC   | 23   | NC           |

**表 4-7. J20-JAMR3 インターフェイスコネクタのピン配置 (続き)**

| J20 コネクタのピン配置 |              |      |      |

|---------------|--------------|------|------|

| ピン番号          | ネット名         | ピン番号 | ネット名 |

| 4             | NC           | 24   | NC   |

| 5             | NC           | 25   | NC   |

| 6             | NC           | 26   | NC   |

| 7             | NC           | 27   | NC   |

| 8             | NC           | 28   | NC   |

| 9             | NC           | 29   | NC   |

| 10            | NC           | 30   | NC   |

| 11            | NC           | 31   | NC   |

| 12            | NC           | 32   | NC   |

| 13            | JAMR3_RESETn | 33   | NC   |

| 14            | NC           | 34   | NC   |

| 15            | NC           | 35   | NC   |

| 16            | NC           | 36   | NC   |

| 17            | NC           | 37   | NC   |

| 18            | NC           | 38   | NC   |

| 19            | DGND         | 39   | NC   |

| 20            | DGND         | 40   | NC   |

**表 4-8. J17-JAMR3 インターフェイスコネクタのピン配置**

| J17 コネクタのピン配置 |              |      |             |

|---------------|--------------|------|-------------|

| ピン番号          | ネット名         | ピン番号 | ネット名        |

| 1             | NC           | 61   | NC          |

| 2             | NC           | 62   | NC          |

| 3             | NC           | 63   | NC          |

| 4             | NC           | 64   | NC          |

| 5             | NC           | 65   | NC          |

| 6             | NC           | 66   | NC          |

| 7             | NC           | 67   | NC          |

| 8             | NC           | 68   | NC          |

| 9             | NC           | 69   | NC          |

| 10            | NC           | 70   | NC          |

| 11            | NC           | 71   | NC          |

| 12            | NC           | 72   | NC          |

| 13            | NC           | 73   | NC          |

| 14            | NC           | 74   | NC          |

| 15            | NC           | 75   | NC          |

| 16            | NC           | 76   | APP_BD_PORz |

| 17            | NC           | 77   | DGND        |

| 18            | NC           | 78   | DGND        |

| 19            | NC           | 79   | NC          |

| 20            | NC           | 80   | NC          |

| 21            | NC           | 81   | NC          |

| 22            | McASP11_AXR6 | 82   | NC          |

| 23            | McASP11_AXR4 | 83   | NC          |

| 24            | McASP11_AXR5 | 84   | NC          |

| 25            | NC           | 85   | NC          |

**表 4-8. J17-JAMR3 インターフェイスコネクタのピン配置 (続き)**

| J17 コネクタのピン配置 |               |      |               |

|---------------|---------------|------|---------------|

| ピン番号          | ネット名          | ピン番号 | ネット名          |

| 26            | DGND          | 86   | NC            |

| 27            | DGND          | 87   | NC            |

| 28            | EXP_I2C1_SDA  | 88   | NC            |

| 29            | McASP11_ACLKX | 89   | NC            |

| 30            | EXP_I2C1_SCL  | 90   | NC            |

| 31            | McASP11_AFSX  | 91   | NC            |

| 32            | NC            | 92   | NC            |

| 33            | McASP11_AXR1  | 93   | NC            |

| 34            | NC            | 94   | NC            |

| 35            | McASP11_AXR3  | 95   | NC            |

| 36            | NC            | 96   | NC            |

| 37            | McASP11_AXR0  | 97   | NC            |

| 38            | McASP11_AXR7  | 98   | NC            |

| 39            | McASP11_AXR2  | 99   | NC            |

| 40            | NC            | 100  | NC            |

| 41            | NC            | 101  | NC            |

| 42            | NC            | 102  | JAMR3_I2S_WC  |

| 43            | NC            | 103  | JAMR3_I2S_DA  |

| 44            | NC            | 104  | JAMR3_I2S_CLK |

| 45            | NC            | 105  | JAMR3_I2S_DB  |

| 46            | NC            | 106  | NC            |

| 47            | NC            | 107  | NC            |

| 48            | NC            | 108  | NC            |

| 49            | VCC_12V       | 109  | NC            |

| 50            | VCC_12V       | 110  | NC            |

| 51            | VCC_12V       | 111  | NC            |

| 52            | VCC_12V       | 112  | NC            |

| 53            | VCC_12V       | 113  | NC            |

| 54            | VCC_12V       | 114  | NC            |

| 55            | NC            | 115  | DGND          |

| 56            | NC            | 116  | DGND          |

| 57            | EXP_DC_3V3    | 117  | NC            |

| 58            | EXP_DC_3V3    | 118  | NC            |

| 59            | EXP_DC_3V3    | 119  | NC            |

| 60            | EXP_DC_3V3    | 120  | NC            |

図 4-9. JAMR3 インターフェイスコネクタ

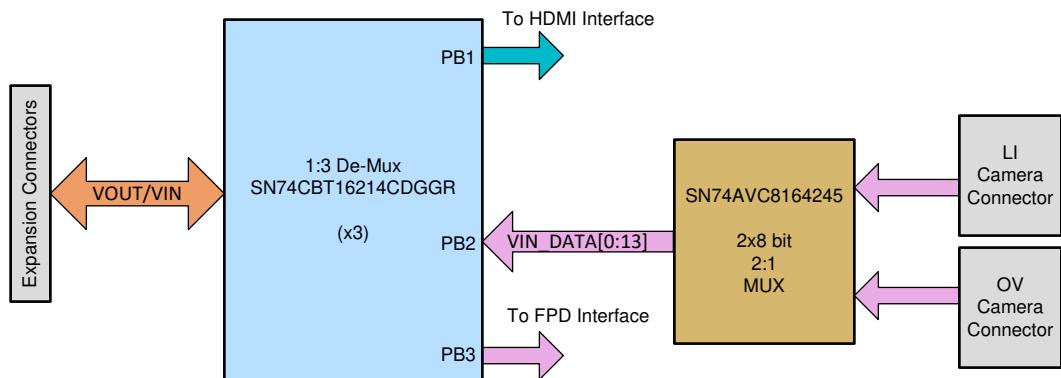

#### 4.9 VIN/VOUT マルチプレクサの選択

多重化ビデオ入力/出力は、3つの12ビット1:3デマルチプレクサ U10、U11、U12 ICのメーカー部品番号 SN74CBT16214CDGGR に接続された拡張コネクタから信号を送信します。デマルチプレクサの1つのチャネル(ポートB1)はHDMIトランスミッタと接続され、2つ目のチャネル(ポートB2)は並列カメラインターフェイスと接続され、3つ目のチャネル(ポートB3)はインフォディainment拡張基板のFPDディスプレイポートと接続されます。マルチプレクサ選択GPIOの詳細については、[セクション5.2](#)を参照してください。

図 4-10. VIN/VOUT マルチプレクサの選択

表 4-9. VIN/VOUT マルチプレクサ選択表

| 選択入力     | 入力 / 出力 | 機能                             |

|----------|---------|--------------------------------|

| S2 S1 S0 | A1      |                                |

| H H L    | VOUT    | A1 ポート = B1 ポート (HDMI) - デフォルト |

| H H H    | VIN     | A1 ポート = B2 ポート (カメラ)          |

| H L H    | VOUT    | A1 ポート = B3 ポート (FPD Link)     |

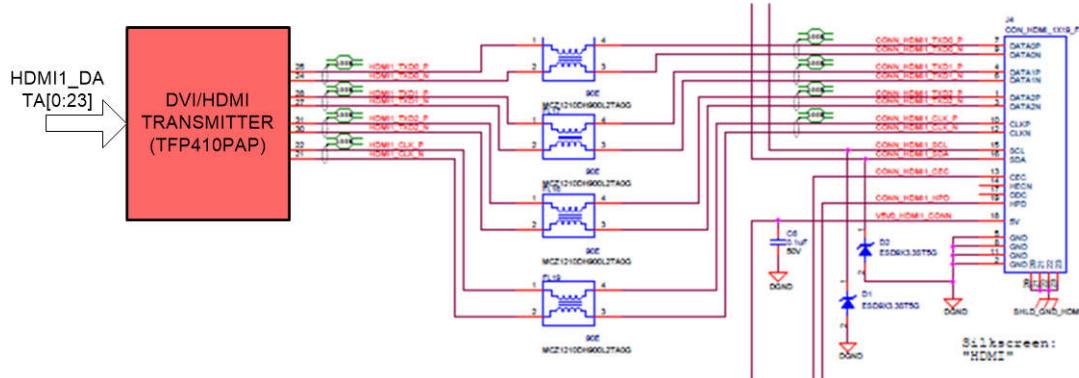

#### 4.10 HDMI インターフェイスブリッジ

TI の HDMI トランシミッタ IC のメーカー部品番号 TFP410-PAP は、24 ビット RGB ビデオ信号を SOC の VOUT ポートから HDMI 出力信号に変換するために使用されます。HDMI トランシミッタチップの出力は、HDMI コネクタのメーカー部品番号 10029449-001RLF に終端接続するために、適切なフィルタと ESD 回路を使用します。

電流を制限するための電流制限負荷スイッチ TPD12S016PWR、および HDMI コントローラのための全体的な ESD 保護を使用して、HDMI コネクタに +5V の電力を供給します。電流制限負荷スイッチは、GPIO エクスパンダ信号 (HDMI\_DDC\_OE) で制御します。ドライブ強度を向上させるため、DDC 信号は TPD12S016 より標準的な I2C レベルトランスレータ PCA9306DCT を使用してレベル変換されます。

図 4-11. HDMI インターフェイスブリッジ

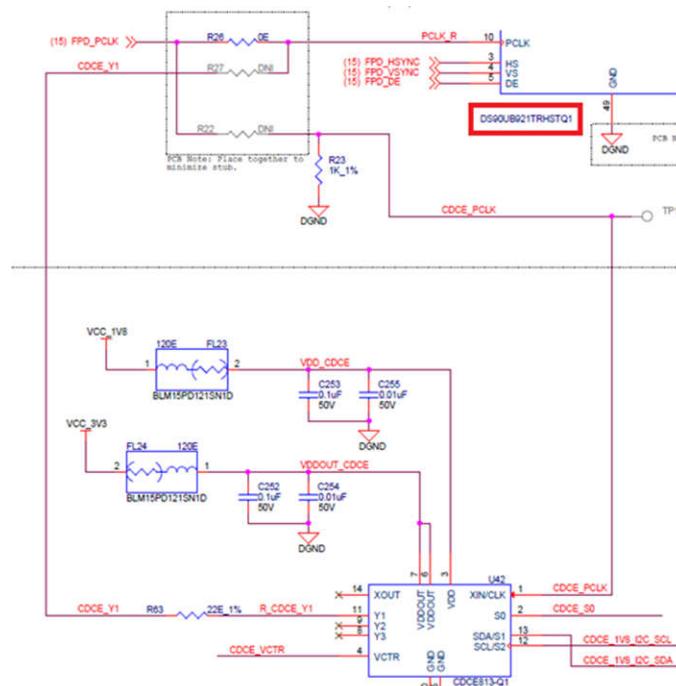

## 4.11 FPD Link ディスプレイシリアルインターフェイス

FPD Link III シリアライザ IC DS90UB921 は、24 ビットの RGB 信号のビデオ信号を、SOC から FPD Link III 信号に変換するために使用します。シリアル化された FPD Link III 出力は、HSD コネクタ (Mfr 部品番号 D4S20G-400A5-C) に終端されます。SOC からの VOUT 信号をデフォルトの HDMI トランシッタからの FPD Link シリアライザに配線するには、表 4-9 と セクション 5.2 を参照してください。

ディスプレイシリアルインターフェイスの制御と構成に使用される J7 SOC の I2C 信号。7'b I2C アドレスを 0x1A に設定する ID[X] ピンには 30.9KΩ プルアップと 95.3KΩ プルダウンが装備されています。

FPD Link-III ディスプレイ基板に電源を供給するため、パワースイッチ TPS1H100AQPWPRQ1 を使用して HSD コネクタに +12V の電力を供給します。パワースイッチは、GPIO エクスパンダ信号 (PWR\_SW\_UB921) で制御されます。オプションのクロッククリーナ回路 Mfr 部品番号:CDCE813-Q1 は、インフォテインメント基板で利用でき、CP 基板から送られる入力クロック信号をクリーンにして、FPD Link III シリアライザに渡します。

図 4-12. FPD Link シリアライザに接続するオプションのクロッククリーナ

図 4-13. FPD Link ディスプレイシリアルインターフェイス

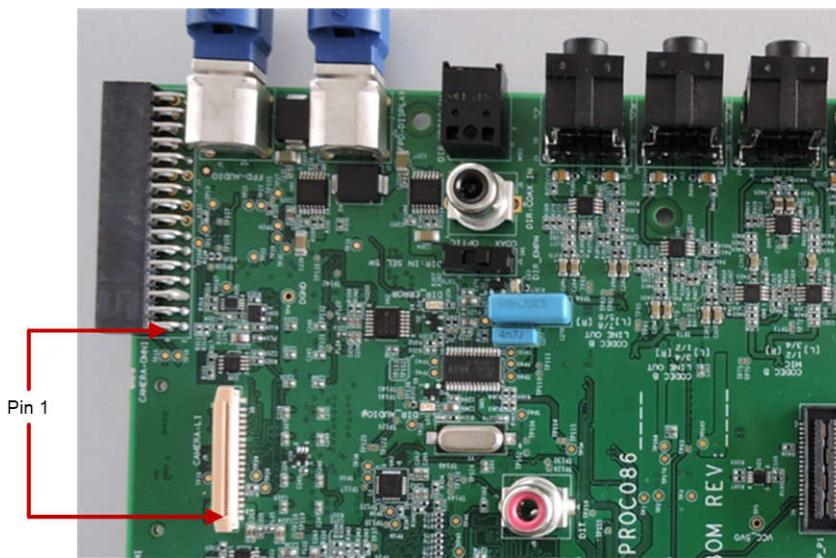

#### 4.12 並列カメラインターフェイス

インフォティメント拡張基板には、並列カメラインターフェイスをサポートする 2 つのカメラモジュールコネクタが搭載されています。

- 32 ピン Omni Vision カメラモジュールコネクタ

- 36 ピン Leopard イメージングカメラモジュールコネクタ

両方のコネクタから入力される並列カメラのデータと **SYNC** 信号は、以下の部品番号の  $2 \times 2:1$  カメラ選択マルチプレクサ IC に接続されます: **SN74AVCB164245VR** の詳細を示します。GPIO 信号 **CAM\_SEL\_OV#** は、OV カメラモジュールと LI カメラモジュールのいずれかの選択に使用されます。デフォルトで、OV カメラの信号パスは有効になっています。GPIO マッピングについては、[セクション 5.2](#) を参照してください。

カメラ選択マルチプレクサの出力は、VIN/VOUT 選択マルチプレクサに接続されます。並列カメラ信号を SoC の VPFE ポートに配線するには、[表 4-9](#) と [セクション 5.2](#) を参照してください。

SPI、リセット、PCLK、パワーダウン信号は、3x レベル変換回路 IC 部品番号 SN74AVC4T245DGVR (U3、U4、U5) を介してカメラコネクタに接続されます。カメラの I2C 信号は、IC 部品番号 PCA9306DCT を使用してレベル変換されます。

注

カメラモジュールは配送キットに含まれていません。

#### 4.12.1 カメラクロック

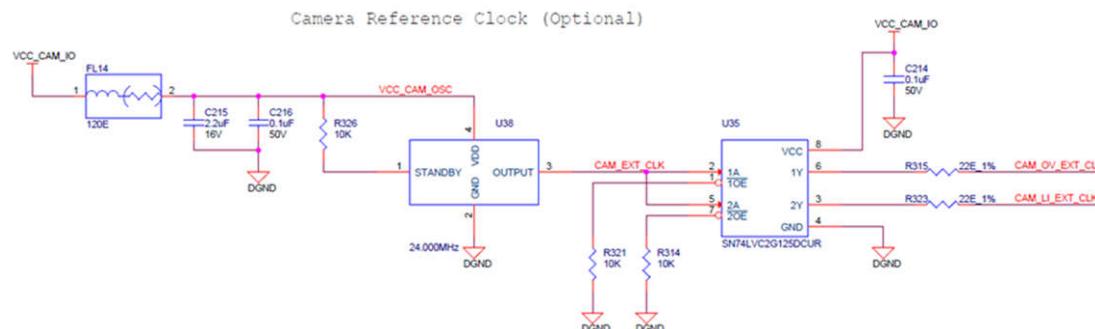

オプションの 24MHz 発振器 IC U38 出力は、バッファ IC U35 メーカー部品番号 SN74LVC2G125DCUR を経由してカメラモジュールに接続します。

図 4-14. カメラクロック

#### 4.12.2 LI カメラモジュールコネクタ

基板には Camera-LI モジュールコネクタ J6 (部品番号 52559-3652) が 1 つ搭載されています。

表 4-10 には LI カメラモジュールコネクタのピン配置が含まれています。

**表 4-10. LI - カメラモジュールコネクタのピン配列**

| J6 コネクタのピン配置 |                |

|--------------|----------------|

| ピン番号         | ネット名           |

| 1            | VCC_CAM_3V3    |

| 2            | VCC_CAM_3V3    |

| 3            | VCC_CAM_3V3    |

| 4            | VCC_CAM_5V0    |

| 5            | VCC_CAM_5V0    |

| 6            | DGND           |

| 7            | CAM_LI_EXT_CLK |

| 8            | DGND           |

| 9            | R_LI_VIN_PCLK  |

| 10           | DGND           |

| 11           | LI_VIN_VD      |

| 12           | LI_VIN_HD      |

| 13           | LI_VIN_DATA13  |

| 14           | LI_VIN_DATA12  |

| 15           | LI_VIN_DATA11  |

| 16           | LI_VIN_DATA10  |

| 17           | LI_VIN_DATA9   |

| 18           | LI_VIN_DATA8   |

| 19           | LI_VIN_DATA7   |

| 20           | LI_VIN_DATA6   |

| 21           | LI_VIN_DATA5   |

| 22           | LI_VIN_DATA4   |

| 23           | LI_VIN_DATA3   |

| 24           | LI_VIN_DATA2   |

| 25           | DGND           |

| 26           | DGND           |

| 27           | LI_VIN_DATA1   |

| 28           | LI_VIN_DATA0   |

| 29           | CAM_I2C_SCL    |

| 30           | CAM_I2C_SDA    |

| 31           | LI_SPI3_MISO   |

| 32           | LI_SPI3_CLK    |

| 33           | LI_CAM_RST#    |

| 34           | LI_SPI3_CS0    |

| 35           | LI_CAM_TRIGGER |

| 36           | LI_SPI3_MOSI   |

#### 4.12.3 OV カメラモジュールコネクタ

基板には Camera-OV モジュールコネクタ J3 (部品番号 SSQ-116-02-L-D-RA) が 1 つ搭載されています。

表 4-11 には OV カメラモジュールコネクタのピン配置が含まれています。

表 4-11. OV - カメラモジュールコネクタのピン配列

| J3 コネクタのピン配置 |               |      |                |

|--------------|---------------|------|----------------|

| ピン番号         | ネット名          | ピン番号 | ネット名           |

| 1            | OV_VIN_DATA5  | 17   | OV_VIN_PCLK_R  |

| 2            | OV_VIN_DATA4  | 18   | DGND           |

| 3            | OV_VIN_DATA7  | 19   | VCC_CAM_5V0    |

| 4            | OV_VIN_DATA6  | 20   | CAM_OV_EXT_CLK |

| 5            | OV_VIN_DATA9  | 21   | VCC_CAM_5V0    |

| 6            | OV_VIN_DATA8  | 22   | DGND           |

| 7            | OV_VIN_DATA11 | 23   | OV_VIN_DATA3   |

| 8            | OV_VIN_DATA10 | 24   | OV_VIN_DATA2   |

| 9            | NC            | 25   | OV_VIN_DATA1   |

| 10           | R_OV_CAM_PWDN | 26   | OV_VIN_DATA0   |

| 11           | NC            | 27   | NC             |

| 12           | CAM_I2C_SDA   | 28   | NC             |

| 13           | OV_VIN_HD     | 29   | NC             |

| 14           | CAM_I2C_SCL   | 30   | NC             |

| 15           | OV_VIN_VD     | 31   | DGND           |

| 16           | DGND          | 32   | DGND           |

図 4-15. OV および LI カメラモジュールのコネクタの Pin1 マーキング

## 5 Jacinto7 評価基板のインターフェイス/IO マッピング

### 5.1 インターフェイス マッピング

インフォテインメント拡張の J721E 評価基板インターフェイスマッピングを [表 5-1](#) に示します。

**表 5-1. インターフェイス マッピング**

| INFO ペリフェラル                            | INFO インターフェイス                             | J721E 接続性                                             |

|----------------------------------------|-------------------------------------------|-------------------------------------------------------|

| オーディオコーデック - A (U32)                   | McASP0 ポート<br>(ネット名 MCASP0_AXR[6:0]*)     | McASP0                                                |

| オーディオコーデック - B (U19)                   | McASP0 ポート<br>(ネット名 MCASP0_AXR[13:7]*)    | McASP0                                                |

| FPD Link III シリアライザ (ディスプレイ) (U8)      | VOUT0 ポート<br>(ネット名 VOUT0_DATA_*)          | VOUT0                                                 |

| FPD Link III デシリアルライザ (オーディオ) (U2)     | McASP1<br>(ネット名 MCASP1_AXR_*、UB926_I2S_*) | McASP1<br>McASP6                                      |

| デジタルオーディオインターフェイスレシーバ (U45、J8、MOD1)    | McASP6<br>(ネット名 MCASP6_AXR_*)             | McASP6                                                |

| デジタルオーディオインターフェイス転送 (J9)               | McASP2<br>(ネット名 MCASP2_AXR0)              | McASP2                                                |

| 並列カメラ (OV/LI) (J3 および J6)              | VPFE0<br>(ネット名 VPFE0_DATA_*)              | (マルチプレクサの選択を参照)<br>VPFE0 または UB921_DIN または HDMI1_DATA |

| HDMI トランスマッタ (U41)                     | VOUT0<br>(ネット名 HDMI1_DATA_*)              | (マルチプレクサの選択を参照)<br>VPFE0 または UB921_DIN または HDMI1_DATA |

| 構成 EEPROM (U30)                        | I2C0 (ネット名 WKUP_I2C0_*)                   | WKUP_I2C0                                             |

| レガシーオーディオ/JAMR3 インターフェイス (J14、J17、J20) | McASP11<br>(ネット名 MCASP11_AXR_*)           | McASP11                                               |

## 5.2 インフォティメント基板の GPIO マッピング

表 5-2 に、GPIO エクスパンダの信号マッピングを示します。

**表 5-2. GPIO エクスパンダの信号マッピング**

| Jacinto7 評価基板 -INFO GPIO エクスパンダ                             |          |                   |             |         |            |                                                         |

|-------------------------------------------------------------|----------|-------------------|-------------|---------|------------|---------------------------------------------------------|

| I2C バス/アドレス                                                 | GPIO ポート | INFO 基板のネット名      | 方向 WRT CTRL | デフォルト状態 | アクティブ状態    | 注記                                                      |

| INFO GPIO エクスパンダ - 1 部品番号 TCA6416ARTWR (オーディオ IO 拡張)        |          |                   |             |         |            |                                                         |

| I2C3/0x21                                                   | P00      | CODEC_RESETn      | 出力          | PD      | アクティブ LOW  | オーディオコーデック A と B のリセット信号として使用                           |

|                                                             | P01      | JAMR3_RESETn      | 出力          | PD      | アクティブ LOW  | JAMR3 インターフェイスのリセット信号として使用                              |

|                                                             | P02      | JAMR3_PWR_CTRL    | 出力          | 該当なし    | アクティブ HIGH | JAMR3 インターフェイスのパワー EN                                   |

|                                                             | P03      | UB926_RESETn      | 出力          | PD      | アクティブ LOW  | FPD オーディオ/FPD コネクタのリセット信号として使用                          |

|                                                             | P04      | PWR_SW_UB926      | 出力          | PD      | アクティブ HIGH | オーディオ/FPD コネクタのパワーイネーブル信号として使用                          |

|                                                             | P05      | UB926_TUNER_RESET | 出力          | PD      | アクティブ LOW  | FPD のリセット信号として使用                                        |

|                                                             | P06      | UB926_GPIO_SPARE  | 出力          | 該当なし    | 該当なし       | FPDLink の SPARE GPIO                                    |

|                                                             | P07      | UB926_LOCK        | 入力          | 該当なし    | 該当なし       | FPDLink からの入力をロック                                       |

|                                                             | P10      | DIR_RESETn        | 出力          | PD      | アクティブ LOW  | DIR インターフェイスのリセット信号として使用                                |

|                                                             | P11      | DIR_CKSEL         | 出力          | PU      | 該当なし       | DIR システムクロックソースの選択に使用 Low: PLL(VCO) クロック、High: XTI クロック |

|                                                             | P12      | DIR_FMT0          | 出力          | PU      | 該当なし       | DOUT オーディオデータ出力フォーマット - 24 ビット、MSB ファースト、I2S (デフォルト)    |

|                                                             | P13      | DIR_FMT1          | 出力          | PU      | 該当なし       |                                                         |

|                                                             | P14      | DIR_PSCK0         | 出力          | PD      | 該当なし       | PLL 選択のシステムクロック                                         |

|                                                             | P15      | DIR_PSCK1         | 出力          | PD      | 該当なし       |                                                         |

|                                                             | P16      | AUDEXP_P16        | 該当なし        | 該当なし    | 該当なし       | 予約済み GPIO                                               |

|                                                             | P17      | McASP6_MUX_SEL    | 出力          | PD      | 該当なし       | マルチプレクサ選択 b/w DIR または FPDLink に使用                       |

| INFO GPIO エクスパンダ - 2 つの部品番号 TCA6416ARTWR (ビデオ IN/OUT IO 拡張) |          |                   |             |         |            |                                                         |

| I2C1/0x21                                                   | P00      | NC                | 該当なし        | 該当なし    | 該当なし       | 未使用                                                     |

|                                                             | P01      | NC                | 該当なし        | 該当なし    | 該当なし       | 未使用                                                     |

|                                                             | P02      | NC                | 該当なし        | 該当なし    | 該当なし       | 未使用                                                     |

|                                                             | P03      | NC                | 該当なし        | 該当なし    | 該当なし       | 未使用                                                     |

|                                                             | P04      | NC                | 該当なし        | 該当なし    | 該当なし       | 未使用                                                     |

|                                                             | P05      | VOUTEXP_P04       | 該当なし        | 該当なし    | 該当なし       | テストポイントで終端                                              |

|                                                             | P06      | VOUTEXP_P05       | 該当なし        | 該当なし    | 該当なし       | テストポイントで終端                                              |

|                                                             | P07      | NC                | 該当なし        | 該当なし    | 該当なし       | 未使用                                                     |

|                                                             | P10      | HDMI_PDn          | 出力          | PD      | アクティブ LOW  | HDMI トランシミッタのパワーダウン信号として使用                              |

|                                                             | P11      | HDMI_DDC_OE       | 出力          | PD      | アクティブ HIGH | HDMI I2C トランスレータイネーブルロジックで使用                            |

|                                                             | P12      | HDMI_HPD          | 入力          | 該当なし    | 該当なし       | HDMI ケーブルホットプラグの検出に使用                                   |

|                                                             | P13      | UB921_RESETn      | 出力          | PD      | アクティブ LOW  | FPD III ディスプレイシリアルライザのリセット信号として使用                       |

|                                                             | P14      | PWR_SW_UB921      | 出力          | PD      | アクティブ HIGH | オーディオ/FPD コネクタのパワーイネーブル信号として使用                          |

|                                                             | P15      | UB921_INTB        | 入力          | 該当なし    | アクティブ HIGH | FPD III ディスプレイシリアルライザ INTB = H、通常 INTB = L、割り込みリクエスト    |

|                                                             | P16      | VOUTEXP_P16       | 該当なし        | 該当なし    | 該当なし       | テストポイントで終端                                              |

|                                                             | P17      | VOUTEXP_P17       | 該当なし        | 該当なし    | 該当なし       | テストポイントで終端                                              |

表 5-3. SoC GPIO マッピング

| 情報ペリフェラル              | ペリフェラル IO   | 方向 (SoC 用) | デフォルト | アクティブ状態                                        | J721E 接続性       |

|-----------------------|-------------|------------|-------|------------------------------------------------|-----------------|

| FPD Link III ディスプレイ   | 割り込み        | 入力         | PU    | アクティブ LOW                                      | GPIO0_79        |

| カメラマルチプレクサの選択         | イネーブル       | 出力         | 該当なし  | '0'-OV<br>'1'-LI                               | GPIO0_78        |

| LI/OV カメラ             | トリガ         | I/O        | PD    | アクティブ HIGH                                     | GPIO0_31        |

|                       | リセット        | 出力         | PU    | アクティブ LOW                                      | GPIO0_32        |

| JAMR3 インターフェイス        | JAMR3_GPIO0 | I/O        | 該当なし  | 該当なし                                           | GPIO0_65        |

|                       | JAMR3_GPIO1 | I/O        | 該当なし  | 該当なし                                           | GPIO0_66        |

|                       | JAMR3_GPIO2 | I/O        | 該当なし  | 該当なし                                           | GPIO0_67        |

| FPD Link III デシリアルライザ | UB926_GPIO1 | I/O        | 該当なし  | 該当なし                                           | GPIO0_11        |

|                       | UB926_GPIO2 | I/O        | 該当なし  | 該当なし                                           | GPIO0_45        |

|                       | UB926_GPIO3 | I/O        | 該当なし  | 該当なし                                           | GPIO0_46        |

| オーディオ IO エクスパンダ       | 割り込み        | 入力         | PU    | アクティブ LOW                                      | GPIO1_23        |

| ビデオ IO エクスパンダ         | 割り込み        | 入力         | PU    | アクティブ LOW                                      | GPIO1_24        |

| VIN/VOUT マルチプレクサの選択   | Select0     | 出力         | PD    | SEL [1:0]<br>'10'-HDMI<br>'11'-CAM<br>'01'-FPD | I2C0 (0x20)、P14 |

|                       | Select1     | 出力         | PU    |                                                | I2C0 (0x20)、P15 |

### 5.3 I2C アドレス マッピング

表 5-4 に、インフォテインメント拡張の完全な I2C アドレスマッピング詳細を示します。

表 5-4. INFO 拡張 I2C 表

| J7ES 評価基板 - インフォテインメント拡張 I2C 表 |                                      |                 |                             |

|--------------------------------|--------------------------------------|-----------------|-----------------------------|

| I2C ポート                        | デバイス / 機能                            | 部品番号            | I2C アドレス                    |

| WKUP_I2C0                      | 基板 ID EEPROM                         | CAT24C256W      | 0x52                        |

| WKUP_I2C0                      | JAMR3 EEPROM                         | CAT24C256WI     | 0x51                        |

| Soc_I2C0                       | 予約済み                                 | TP55、TP56       | 該当なし                        |

| Soc_I2C1                       | VOUT DDC リンク                         | <コネクタ インターフェイス> | 未定                          |

| Soc_I2C1                       | I2C GPIO エクスパンダ (ビデオ)                | TCA6416ARTWR    | 0x21                        |

| Soc_I2C1                       | FPD Link-III シリアライザ (VOUT から FPD)    | DS90UB921-Q1    | 0x1A                        |

| Soc_I2C1                       | CDCI (クロックジェネレータ)                    | CDCE813-Q1      | 0x65                        |

| Soc_I2C2                       | 予約済み                                 | TP52、TP53       | 該当なし                        |

| Soc_I2C3                       | オーディオコーデック - A                       | PCM3168A-Q1     | 0x47                        |

| Soc_I2C3                       | オーディオコーデック - B                       | PCM3168A-Q1     | 0x46                        |

| Soc_I2C3                       | JAMR3 GPIO エクスパンダ                    | PCF8575         | 0x22<br>JAMR3 の修正が必要        |

| Soc_I2C3                       | レガシーオーディオ/JAMR3 インターフェイス             | AFE8310         | 0x048、0x049、0x04A、<br>0x04B |

| Soc_I2C3                       | FPD Link-III デシリアルライザ (FPD から McASP) | DS90UB926Q-Q1   | 0x3B                        |

| Soc_I2C3                       | I2C GPIO エクスパンダ (オーディオ)              | TCA6416ARTWR    | 0x21                        |

| Soc_I2C6                       | カメラセンサ、並列                            | <コネクタ インターフェイス> | 未定                          |

## 6 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| Changes from Revision A (May 2020) to Revision B (October 2025) | Page |

|-----------------------------------------------------------------|------|

| • HDMI 商標情報を追加しました.....                                         | 3    |

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月