## Design Guide: TIDA-050096

# スケーラブル、大電流、パラレル車載リファレンス デザイン

## 説明

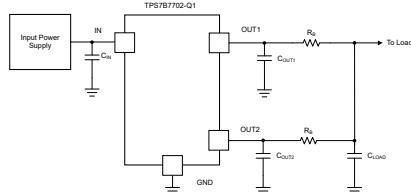

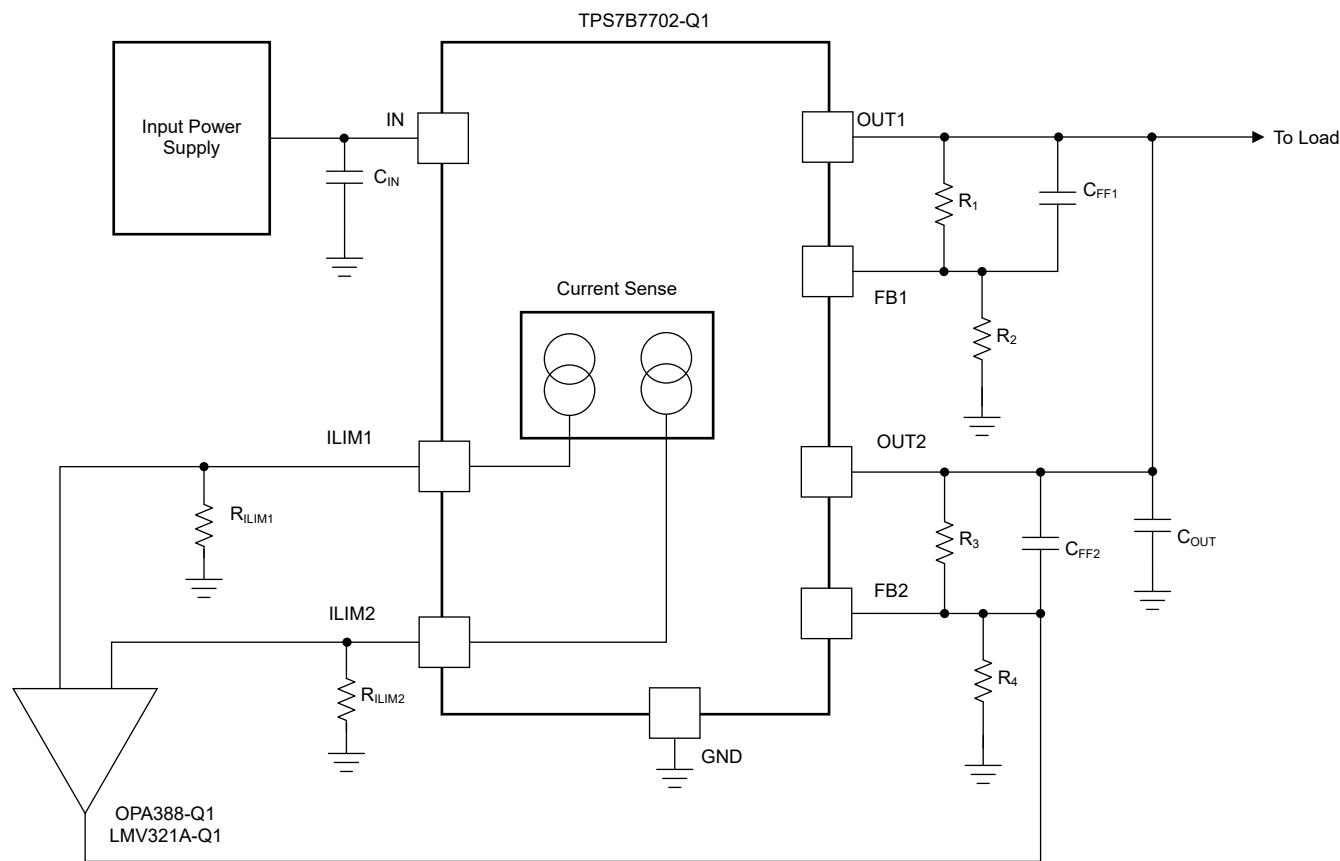

このリファレンス デザインでは、ファンタム電源などの一般的なアプリケーションで必要になる場合がある、より大きな負荷電流を得るために、TPS7B7702-Q1 リニアレギュレータを並列接続する 2 つの方法を示しています。最初の方法では、外付けオペアンプを使用して 4 つの TPS7B7702-Q1 チャネルを並列接続し、最大 1.2A を負荷に供給します。この方式はスケーラブルであり、より多くのリニアレギュレータチャネルを並列接続し、より大きな電流を供給できます。2 つ目の方法では、バラスト抵抗を使用して 2 つの TPS7B7702-Q1 チャネルを並列接続し、最大 500mA の出力電流を供給します。

## リソース

TIDA-050096

デザイン フォルダ

TPS7B7702-Q1

プロダクト フォルダ

OPA388-Q1

プロダクト フォルダ

LMV321A-Q1

プロダクト フォルダ

## 特長

- 出力電流: 最大 500mA

- バラスト抵抗と 2 つの TPS7B7702-Q1 リニアレギュレータチャネルを使用

- 出力電流: スケーラブル

- オペアンプを活用し、4 つの TPS7B7702-Q1 リニアレギュレータチャネルを使用することにより、1.2A の供給能力を実証

- 内蔵の保護機能と診断機能

- 4.5 ~ 40V の広い入力電圧範囲と、45V のロードダングルに対応

- 外付け抵抗で電流制限を調整可能

## アプリケーション

- デジタル コックピット処理装置

- テレマティクス制御ユニット

- サラウンド ビュー システムの ECU

- 車載用ヘッド ユニット

- ANC (アクティブ ノイズ キャンセレーション) 機能搭載、昇圧なしオーディオ アンプ

## 1 システムの説明

低ノイズの低ドロップアウトレギュレータ(LDO)は、電源ノイズが信号チェーンに結合しないようにするために、多くのアプリケーションで必要とされます。新しいセンサがより多くの電流を必要としたり、さまざまな負荷を組み合わせてスペースを節約したりするため、LDO出力電流に対する要求は高まり続けています。消費電力の制限や出力電流能力により、1つのLDOだけで電源を供給することが常に可能とは限りません。TIDA-050096リファレンスデザインは、複数のLDOを並列に構成して電流を共有することにより、この問題を解決します。このリファレンスデザインでは、TPS7B7702-Q1を並列接続する方法が2つあります。

- オペアンプ:**最初の方法では、オペアンプを使用して複数のTPS7B7702-Q1チャネルを並列接続します。TPS7B7702-Q1の並列接続には、OPA388-Q1やLMV321A-Q1など、幅広いタイプのオペアンプを使用できます。このリファレンスデザインでは、オペアンプを使用して最大4つのTPS7B7702-Q1チャネルを並列接続し、1つのTPS7B7702-Q1チャネルの主要機能すべてを維持しながら、最大1.2Aを負荷に供給できます。この方法は4つのLDOチャネルを超えてスケーリングできますが、この方式を使用した場合、並列に接続できるチャネル数に制限はありません。

- バラスト抵抗:**2つ目の方法ではバラスト抵抗を使用します。この抵抗は、ディスクリート抵抗として設計することも、プリント基板(PCB)上の銅のパターンとして設計することもできます。一部のアプリケーションでは、システムに固有のハーネス抵抗を、バラスト抵抗の一部または全体として使用することもできます。この方式を使用する場合、並列に接続できるTPS7B7702-Q1LDOチャネルの数に理論上の制限はありませんが、テキサスインスツルメンツでは2チャネルまでに制限することを推奨しています。これが推奨されるのは、帰還抵抗によって設定されるゲインにより、各LDO<sup>[1]</sup>の出力間に生じる誤差電圧または差異が出力電圧とともに大きくなるためです。電圧が高いと、このゲインの増加によって誤差電圧が増幅され、バラスト抵抗の値が大きくなり、TPS7B7702-Q1では1Ωを超える可能性もあります。バラスト抵抗を大きくすると、ロードレギュレーションに悪影響を及ぼすため、実用的でない方法となる可能性があります。

### 1.1 主なシステム仕様

表 1-1. 主なシステム仕様(オペアンプを使用したパラレル LDO)

| パラメータ                                                                      | 仕様                                                                                                                                     |

|----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| 入力電圧範囲                                                                     | 4.5V ~ 40V                                                                                                                             |

| 出力電圧範囲                                                                     | 1.5V ~ 35V                                                                                                                             |

| 入力電圧 $V_{IN}$ に最適化                                                         | 12V                                                                                                                                    |

| 出力電圧 $V_{OUT}$ に最適化                                                        | 10V                                                                                                                                    |

| 最大出力電流                                                                     | スケーラブル<br>オペアンプを使用して2つのTPS7B7702-Q1チャネルで600mAを供給可<br>オペアンプを使用して3つのTPS7B7702-Q1チャネルで900mAを供給可<br>オペアンプを使用して4つのTPS7B7702-Q1チャネルで1.2Aを供給可 |

| $V_{OUT}$ 過渡偏差、600mA → 1.2A → 600mA、4つの並列チャネル、1A/μs (代表値) <sup>(1)</sup>   | +135mV <sub>PK</sub> /−113mV <sub>PK</sub>                                                                                             |

| $V_{OUT}$ 過渡偏差、600mA → 1.2A → 600mA、4つの並列チャネル、0.1A/μs (代表値) <sup>(1)</sup> | +132mV <sub>PK</sub> /−109mV <sub>PK</sub>                                                                                             |

| $V_{OUT}$ 過渡偏差、450mA → 900mA → 450mA、1A/μs (代表値) <sup>(1)</sup>            | +114mV <sub>PK</sub> /−96mV <sub>PK</sub>                                                                                              |

| $V_{OUT}$ 過渡偏差、450mA → 900mA → 450mA、0.1A/μs (代表値) <sup>(1)</sup>          | +113mV <sub>PK</sub> /−94mV <sub>PK</sub>                                                                                              |

| $V_{OUT}$ 過渡偏差、300mA → 600mA → 300mA、1A/μs (代表値) <sup>(1)</sup>            | +85mV <sub>PK</sub> /−78mV <sub>PK</sub>                                                                                               |

| $V_{OUT}$ 過渡偏差、300mA → 600mA → 300mA、0.1A/μs (代表値) <sup>(1)</sup>          | +82mV <sub>PK</sub> /−79mV <sub>PK</sub>                                                                                               |

| ロードレギュレーション                                                                | +16.7mV/A                                                                                                                              |

(1) 各TPS7B7702-Q1LDOのOUTピンとGNDの間に10μFセラミックコンデンサが1個接続されています。

**表 1-2. 主なシステム仕様 (バラスト抵抗を使用したパラレル LDO)**

| パラメータ                                                                                           | 仕様                                                        |

|-------------------------------------------------------------------------------------------------|-----------------------------------------------------------|

| 入力電圧範囲                                                                                          | 4.5V ~ 40V                                                |

| 出力電圧範囲                                                                                          | 1.5V ~ 35V                                                |

| 入力電圧 $V_{IN}$ に最適化                                                                              | 12V                                                       |

| 出力電圧 $V_{OUT}$ に最適化                                                                             | 10V                                                       |

| 最大出力電流 <sup>(1)</sup>                                                                           | 500mA (バラスト抵抗を使用した 2 つの TPS7B7702-Q1 <sup>(2)</sup> チャネル) |

| $V_{OUT}$ 過渡偏差、300mA → 600mA → 300mA、 $C_{FF} = \text{未実装}$ 、 $1A/\mu s$ (代表値) <sup>(1)</sup>   | +135mV <sub>PK</sub> /-326mV <sub>PK</sub>                |

| $V_{OUT}$ 過渡偏差、300mA → 600mA → 300mA、 $C_{FF} = 22nF$ 、 $1A/\mu s$ (代表値) <sup>(1)</sup>         | +28mV <sub>PK</sub> /-226mV <sub>PK</sub>                 |

| $V_{OUT}$ 過渡偏差、300mA → 600mA → 300mA、 $C_{FF} = \text{未実装}$ 、 $0.1A/\mu s$ (代表値) <sup>(1)</sup> | +139mV <sub>PK</sub> /-323mV <sub>PK</sub>                |

| $V_{OUT}$ 過渡偏差、300mA → 600mA → 300mA、 $C_{FF} = 22nF$ 、 $0.1A/\mu s$ (代表値) <sup>(1)</sup>       | +29mV <sub>PK</sub> /-223mV <sub>PK</sub>                 |

| バラスト抵抗                                                                                          | 1.33Ω                                                     |

| ロードレギュレーション                                                                                     | -662mV/A                                                  |

- (1) 理論的には、バラスト抵抗を使用して並列接続できる LDO チャネルの数に制限はありません。このリファレンス電圧は、パラレル LDO で大きな誤差項を示し、内部リファレンスは TPS7B7702-Q1 パッケージ内の 2 つの LDO チャネルで共有されますが、個別の TPS7B7702-Q1 パッケージでは共有されません。このため、バラスト抵抗方式を使用する場合は、TPS7B7702-Q1 のパラレル LDO チャネルの数を 2 つに制限することを推奨します。

- (2) 各 TPS7B7702-Q1 LDO の OUT ピンと GND の間には、バラスト抵抗の前段に  $10\mu F$  セラミックコンデンサが 1 個接続されています。バラスト抵抗の後段には、追加の  $10\mu F$  セラミックコンデンサが 1 個接続されています。

## 2 システム概要

### 2.1 ブロック図

図 2-1. ブロック図: オペアンプ方式 (上) およびパラスト抵抗方式 (下)

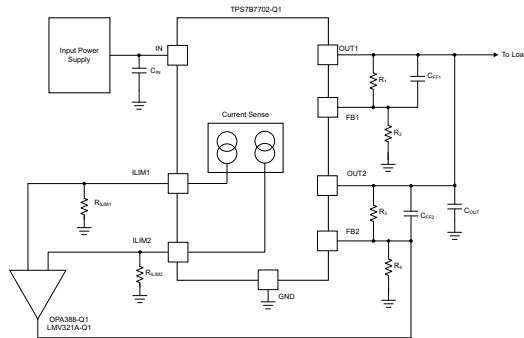

## 2.2 設計上の考慮事項

このリファレンス デザインでは、TPS7B7702-Q1 チャネルを並列接続する 2 つの異なる方式を紹介します。1 つの方は、オペアンプを使用して複数の LDO チャネルを並列接続し、2 つ目の方は、バラスト抵抗を使用して複数の LDO チャネルを並列接続します。これらの各方式の詳細および設計上の考慮事項については、[セクション 2.2.2](#) および [セクション 2.2.3](#) で説明します。

### 2.2.1 フォルト検出および保護

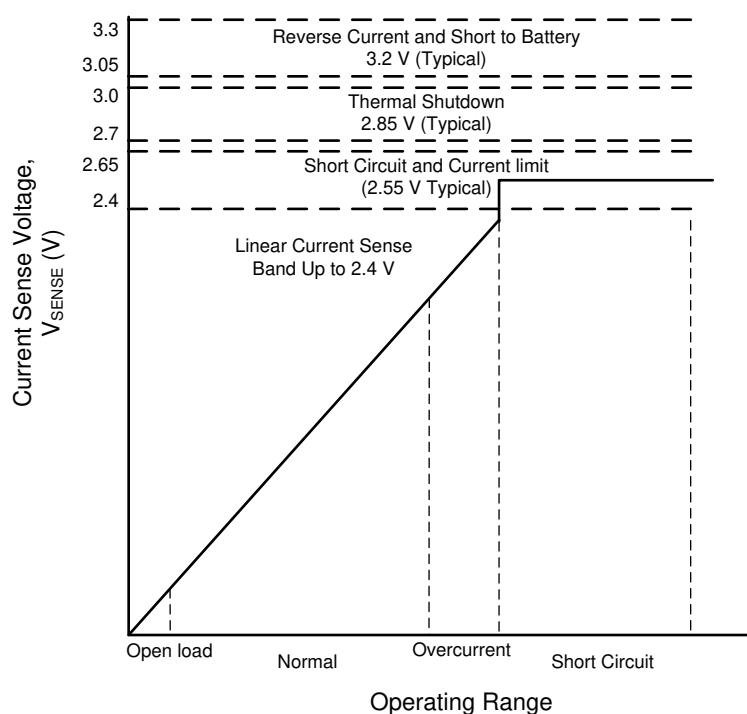

TPS7B7702-Q1 にはアナログ電流センスとデジタルのフォルトピンの両方が搭載されており、各種のフォルト状況を完全に診断します。

電流センス電圧スケールは、関心のある出力電流範囲に基づいて選択されます。[図 2-2](#) は、各フォルトを完全に診断できる推奨設定を示しています。本デバイスが電流制限モードに入る前は、出力電流センス電圧は実際の負荷電流に対して線形に比例します。サーマルシャットダウン (TSD) およびバッテリ短絡 (STB) 状態では、電流センス電圧は、

『[TPS7B770x-Q1 電流センス搭載、車載、シングルチャネルアンテナ/デュアルチャネルアンテナLDO](#)』

(TPS7B7702-Q1) データシートの電気的特性表で規定されたフォルト電圧レベルに設定されます。

図 2-2. 電流センス出力の機能

### 2.2.2 動作原理 - オペアンプを使用したパラレル LDO

このトポロジでは、各 LDO チャネルから引き込まれた負荷電流を検出し、その情報を使用して複数の LDO チャネルを並列接続します。この方式は可変出力 LDO にのみ適用できます。オペアンプを使用して LDO を並列接続する場合、1 次側 LDO と呼ばれる 1 つの LDO が全体の出力を制御します。並列接続された追加の各 LDO チャネルは、2 次側 LDO と呼ばれます。この構成では、アンプの出力が各 2 次側 LDO の帰還ピンに接続され、1 次側 LDO が出力全体を制御できます。この方法を使用すれば、任意の数の 2 次側 LDO を並列接続することができ、電流検出の精度が維持されている限り、利用可能な総電流は各 LDO の電流の総和となります。TPS7B770x-Q1 の電流検出には  $\pm 8\%$  の最悪条件下での許容誤差があり、この誤差により、最悪条件下で確実に引き出すことができる総電流の実用上の上限が設定されます。

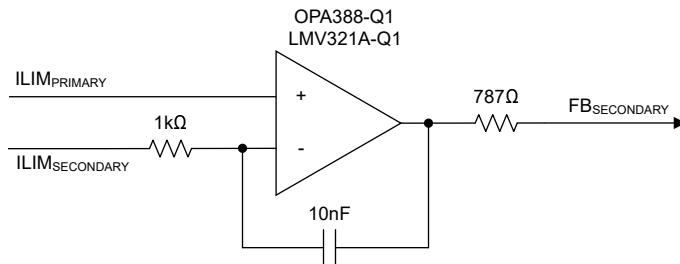

オペアンプ回路の補償は、システムの安定性を維持する上できわめて重要です。このリファレンス デザインでは、オペアンプを単純な積分器として構成しています。オペアンプと FB ピンの間には絶縁抵抗 ( $R_{ISO}$ ) が直列に配置されており、オペアンプが容量性負荷によって不安定になるのを防止しています (リファレンス [8] を参照)。図 2-3 に、最終的なオペアンプ回路を示します。

図 2-3. 最終的なオペアンプ回路

負荷過渡応答の測定値が示されており(セクション 3.3 を参照)、回路の安定性が実証されています。さらに、電源除去比(PSRR)やその他の測定値も含まれており、設計の堅牢性をさらに検証しています(セクション 3.3 を参照)。

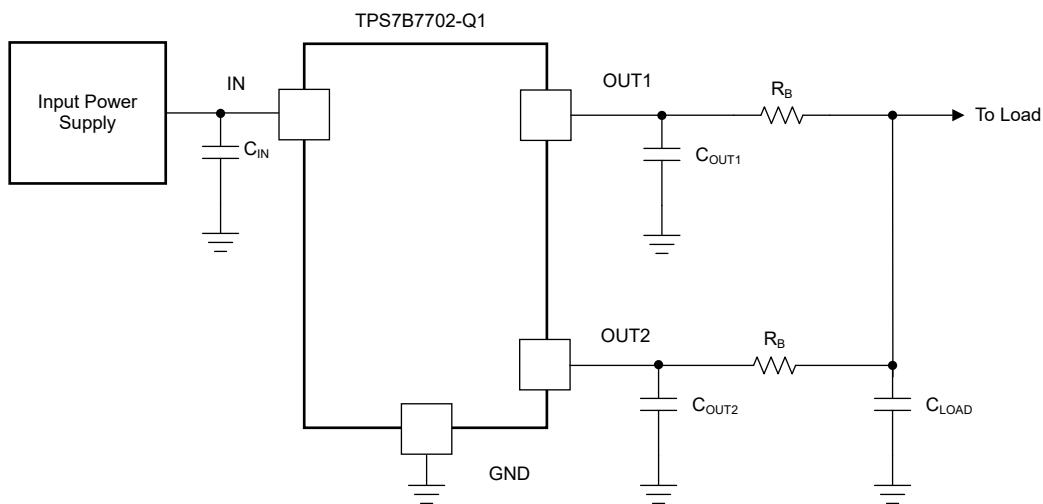

### 2.2.3 動作原理 - バラスト抵抗を使用したパラレル LDO

バラスト抵抗は、複数の電圧源を相互に接続し、共通の負荷に電力を供給する簡単な方法を提供します。各 LDO の出力における誤差電圧  $V_E$  と呼ばれる電圧差を最小化することが重要です。LDO の精度が高いほど、バラスト抵抗のサイズを小さくすることができます。

各 TPS7B7702-Q1 には、内部リファレンスを共有する 2 つの内部 LDO チャネルがあります。これにより、バラスト抵抗を使用して並列接続された LDO の主要な誤差要因であるリファレンス電圧の差が解消されます。残りの誤差要因は、バラスト抵抗、内部出力電界効果トランジスタ(FET)、アンプに由来します。これらの誤差はオフセット電圧として現れ、ライン電圧や負荷電流にも依存します。このオフセット電圧と、設定用帰還抵抗の許容差の組み合わせが、各 LDO の合計誤差  $V_E$  を構成します。複数の LDO 間での電流分担誤差を最小化するには、0.1% (またはそれを上回る精度) の許容差の帰還抵抗を使用します。オフセット電圧は内部誤差アンプゲインによって増幅され、このゲインは  $V_{OUT}$  を決定するために必要な出力電圧に応じて設定されます。このリファレンスデザインでは、簡略化のため、すべてのバラスト抵抗が同じ値に設定されています。

従来、バラスト抵抗は、パラレル LDO 間の電流不均衡  $I_{MAX}$  を設定するために、式 1 を使用して選定されていました。

$$R_B = \frac{\max_{1 < x < n} V_{En} - \min_{1 < x < n} V_{En}}{\Delta I_{MAX}} \quad (1)$$

この式では、負荷電圧  $V_{LOAD}$  が考慮されておらず、これはほとんどの最新のパラレル LDO 設計電源では必要です。テキサス インスツルメンツでは、バラスト抵抗を使用したパラレル LDO の設計と解析を最新化しており(リファレンス [4] および [6] を参照)、システム要件に基づいて LDO 用の  $R_B$  を設計できるダウンロード可能なソフトウェアツールも開発しています(リファレンス [5] を参照)。バラスト抵抗を使用するパラレル TPS7B7702-Q1 デバイスは、ダウンロード可能なこのソフトウェアツールを使用してシステム要件を評価し、必要なバラスト抵抗を設計することにより構成されています。

| TPS7B7702                                  |           |        |                     |        |

|--------------------------------------------|-----------|--------|---------------------|--------|

| LDO Specifications                         |           |        |                     |        |

| Parameter                                  | Value     | Units  | Optional User Entry | Units  |

| V <sub>E</sub> , high                      | 63.503278 | mVdc   | 63.50327828         | mVdc   |

| V <sub>E</sub> , low                       | -63.44464 | mVdc   | -63.44464286        | mVdc   |

| Thermal Impedance T <sub>JA</sub>          | 40.3      | °C / W |                     | °C / W |

| V <sub>REF</sub>                           | 1.233     | Vdc    |                     |        |

| Parallel LDO System Requirements           |           |        |                     |        |

| Parameter                                  | Value     | Units  |                     |        |

| T <sub>A</sub>                             | 25        | °C     |                     | °C     |

| Maximum T <sub>j</sub> per LDO             | 125       | °C     |                     | °C     |

| V <sub>IN</sub>                            | 12        | Vdc    | 12                  | Vdc    |

| V <sub>OUT</sub>                           | 10.048    | Vdc    | 10.048              | Vdc    |

| Allowable load regulation                  | 0.5       | Vdc    | 0.5                 | Vdc    |

| System Noise Requirement (10 Hz - 100 kHz) | 167       | µVRMS  |                     | µVRMS  |

| Total System Load:                         | 0.5       | A      | 0.5                 | A      |

| Minimum Ballast Resistance needed          | 423.15974 | mΩ     |                     |        |

| Optimum Ballast Resistance                 | 1655.1184 | mΩ     |                     |        |

| Ballast Resistance Selected                | 1330      | mΩ     | 1330                | mΩ     |

| N =                                        | 2         |        |                     |        |

| Minimum number of parallel LDO's required: | 2         |        |                     |        |

図 2-4. バラスト抵抗カリキュレータを使用したパラレル LDO を示すスクリーンショット

I<sub>OUTn</sub> や V<sub>LOAD</sub> に加えて、他のシステム要件として、ノイズ、PSRR、ドロップアウト、サーマル制限などのパラレル LDO トポジを使用する必要が生じる場合があります。つまり、バラスト抵抗を使用したパラレル LDO には、以下のような利点があります。

- 並列接続した LDO の数の平方根に反比例して、システムノイズが低減される

- 1つの LDO を使用する場合と比べて、システムの PSRR が向上する

- 負荷電流が複数の LDO に分散され、ドロップアウト要件が緩和される

- 消費電力が複数の LDO に分散され、リニアレギュレータの接合部温度が低減される

これらのシステム要件の詳細、バラスト抵抗を使用したパラレル LDO 性能を向上させる方法、およびシステム要件で必要なパラレル LDO の数については、リファレンス [4], [5]、および [6] を参照してください。

バラスト抵抗は通常、PCB トレースまたはディスクリート抵抗として使用されます。一般に、PCB トレース抵抗は低コストのアプリケーションが適しています。PCB トレース抵抗は、狭い温度範囲で動作するアプリケーションや、高温環境で動作するアプリケーションにも適しています。トレース抵抗は、複数の低電流デバイスを並列接続する場合に(通常、出力電流に制限がある高電圧 LDO など)、優れた選択肢です。

ディスクリート抵抗は、高性能アプリケーション(出力電圧の許容差や過渡応答が重要な場合)に適しています。ディスクリート抵抗による方法は、大電流デバイスが並列接続されるアプリケーション(大電流デバイスがすぐに利用できる低電圧 LDO など)にも適しています。周囲温度が 125°Cを超えると、ディスクリートバラスト抵抗の設計が難しくなり、150°Cを超えるとディスクリートバラスト抵抗の使用が困難になります。バラスト抵抗の解析と設計の詳細については、リファレンス [4] を参照してください。

表 2-1. PCB トレース抵抗とディスクリート抵抗との関係の概要

| バラスト抵抗オプション | 関連コスト                     | 許容誤差                           | 寄生インダクタンス       | 高温動作                                        |

|-------------|---------------------------|--------------------------------|-----------------|---------------------------------------------|

| PCB トレース抵抗  | PCB トレース抵抗の設計が完了した後は、なし   | より広範: 抵抗値は動作温度範囲全体でほぼ 2 倍      | PCB パターン長とともに増加 | FR4 の T <sub>g</sub> によってのみ制限               |

| ディスクリート抵抗   | 各 PCB 上で調達、購入、実装する必要があります | 高精度: ディスクリート抵抗は 100ppm 以下の許容誤差 | 低               | 高温では大きな抵抗パッケージサイズ(0805 または 1206)が必要になる可能性あり |

## 2.3 主な使用製品

### 2.3.1 TPS7B7702-Q1 電流センス搭載、車載、デュアルチャネル アンテナ低ドロップアウト(LDO) レギュレータ

TPS7B770x-Q1 ファミリのデバイスには、シングルおよびデュアルの高電圧で、電流検出機能付きの低ドロップアウトレギュレータ (LDO) が搭載されており、4.5V ~ 40V の広い入力電圧範囲で動作するよう設計されています (負荷ダンプ保護 45V)。これらのデバイスは、同軸ケーブル経由でアクティブアンテナの低ノイズアンプを駆動し、チャネルごとに 300mA の電流を供給します。また、各チャネルの出力電圧は 1.5V ~ 20V の範囲で調整可能です。

これらのデバイスは、電流センスおよびエラー ピンにより診断を行えます。負荷電流を監視するために、ハイサイド電流センサ回路は、検出した負荷電流に比例したアナログ信号を出力します。正確な電流センスにより、追加のキャリブレーションなしで、オープン、通常、短絡の状態を検出できます。アナログ/デジタル コンバータ(ADC)のリソースを節約するため、チャネル間およびデバイス間で電流センスを多重化できます。各チャネルの電流制限は、外付けの抵抗を使用して調整することもできます。

逆極性保護ダイオードが内蔵されているため、外付けのダイオードは不要です。これらのデバイスには、標準のサーマルシャットダウン、出力からバッテリへの短絡保護、および逆電流保護機能が搭載されています。各チャネルの出力には、誘導性クランプ保護が内蔵されており、誘導性スイッチのオフ時に動作します。

これらのデバイスは、-40°C ~ +125°C の周囲温度範囲で動作します。

### 2.3.2 OPAx388 車載対応、高精度、ゼロドリフト、ゼロクロスオーバー、真のレール ツー レール入出力のオペアンプ

OPA388-Q1 と OPA2388-Q1 (OPAx388-Q1) は、レール ツー レール入力および出力動作に対応した車載対応、低ノイズ、高速セトリング、ゼロドリフトの高精度オペアンプです。OPAx388-Q1 は非常に優れた AC 性能を備え、全温度範囲でわずか  $0.25\mu\text{V}$  のオフセットと  $0.005\mu\text{V}/^\circ\text{C}$  の温度ドリフトを達成しているため、高分解能 A/D コンバータ (ADC) を高精度で駆動するのに最適です。ゼロクロスオーバー テクノロジーは、すべてのオフセットの変化を同相範囲全体で最小限に抑えます。OPAx388-Q1 は低ドリフトと超低  $1/\text{f}$  ノイズを兼ね備えているため、信号の整合性を損なうことなく障害条件を監視および検出できます。

これらのデバイスは、-40°C ~ +125°C の産業用温度範囲について仕様が規定されています。

### 2.3.3 LMV321A-Q1 車載対応低電圧レール ツー レール出力オペアンプ

LMV3xxA-Q1 ファミリには、出力をレール ツー レールでスイングできる、シングル (LMV321A-Q1)、デュアル (LMV358A-Q1)、クワッド チャネル (LMV324A-Q1) の低電圧 (2.5V ~ 5.5V) 車載用オペアンプがあります。これらのオペアンプは、インフォテインメントや照明など、低電圧での動作と大きな容量性負荷の駆動が必要で、スペースの制約が厳しいアプリケーション向けにコスト効率の優れた方法を提供します。LMV3xxA-Q1 ファミリの容量性負荷の駆動能力は 500pF であり、オープン ループ出力インピーダンスが抵抗性なので、はるかに大きな容量性負荷についても容易に安定化できます。これらのオペアンプは低電圧 (2.5V ~ 5.5V) で動作し、LMV3xx-Q1 デバイスと同様の性能仕様を満たすよう、特別に設計されています。

LMV3xxA-Q1 ファミリは堅牢に設計されているため、回路設計を簡素化できます。これらのオペアンプは、ユニティゲイン安定性、RFI および EMI 除去フィルタ内蔵、およびオーバードライブ状態で位相反転がない、といった特長があります。

LMV3xxA-Q1 ファミリは、SOIC、MSOP、SOT-23、TSSOP などの業界標準パッケージで供給されます。

## 3 ハードウェア、テスト要件、およびテスト結果

### 3.1 ハードウェア要件

### 3.2 テスト設定

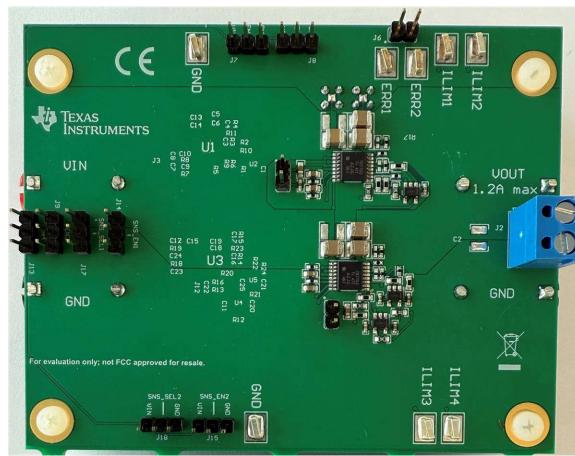

TIDA-050096 リファレンス デザインでは、TPS7B7702-Q1 LDO を並列接続する 2 つの方法を紹介します。評価に必要なすべての部品が実装されており、入力、出力、V<sub>CC</sub>、センス、およびフィードフォワードの各コンデンサに加えて、誤差、電流制限、帰還、センス抵抗も実装されています。これらの部品の選択に関するガイダンスについては、『[TPS7B770x-Q1 電流センス搭載、車載、シングルチャネルアンテナ/デュアルチャネルアンテナ LDO](#)』データシートも参照してください。TIDA-050096 リファレンス デザインは、入力 12V、出力 10V に構成されており、さまざまな負荷電流オプションを取り揃えています。

TPS7B7702-Q1 LDO を並列接続する最初の方法では、オペアンプを使用して複数の LDO の電流を共有します。リファレンス デザイン (OPA388-Q1 および LMV321A-Q1) の性能を評価するために、2 つの異なるオペアンプが使用されています。新しい帰還ループを追加しても安定性を維持できるように、補償用のコンデンサと抵抗も実装されています。TIDA-050096 リファレンス デザインは、最大 4 つの LDO チャネルを並列接続でき、1 つの TPS7B7701-Q1 LDO にすでに搭載されているすべての機能を維持したまま、最大 1.2A の出力電流を供給できます。

図 3-1. オペアンプと電流検出を使用した 2 ~ 4 つのパラレル LDO チャネル

この方式では、4 つの LDO チャネルに制限されるわけではありません。最終的なアプリケーションでより多くの電流が必要な場合は、オペアンプ方式を使用して追加の LDO チャネルを並列接続できます。

TPS7B7702-Q1 LDO を並列接続する 2 つ目の方法では、バラスト抵抗を使用します。推奨されるバラスト抵抗と追加の負荷コンデンサが実装されています。バラスト抵抗で並列接続できる LDO の数には基本的な制限はありませんが、異なるパッケージの TPS7B7702-Q1 デバイス間で単一のリファレンスを共有できないため、パッケージ間で並列接続された LDO では誤差電圧が増加します。この誤差電圧の増加は、バラスト抵抗の増加に直接関係します。テキサス・インスツルメンツでは、TPS7B7702-Q1 パッケージ内のパラレル チャネルの数を 2 つの LDO に制限し、それ以上の LDO が必要な場合は、オペアンプの並列方式を使用することを推奨しています。

図 3-2. パラスト抵抗を使用した 2 つのパラレル LDO チャネル

TPS7B7702-Q1 の LDO チャネルは、3 ピン ヘッダを使用して有効または無効にできます (オペアンプ方式の場合は J7、J8、J9、J13、パラスト抵抗方式の場合は J23 と J26)。

- デバイスを有効にする場合は 3 ピン ヘッダのセンター ピンを  $V_{IN}$  に接続する

- デバイスを無効にする場合は 3 ピン ヘッダのセンター ピンを  $GND$  に接続する

各チャネルが負荷電流を均等に共有していることを確認するために、各 LDO チャネルの  $ILIM$  電圧を測定するテスト ポイントが用意されています。2 ピン ヘッダにより、TPS7B7702-Q1 の  $V_{CC}$  をオペアンプの正電源レールに接続し、オペアンプの引き込まれた電流を測定できます。 $V_{CC}$  ピンは、外部回路から最大 15mA の電流を供給できます。J2 (オペアンプを使用したパラレル LDO) または J25 (パラスト抵抗を使用したパラレル LDO) を使用して、評価用に外部負荷を接続できます。

オペアンプを使用したパラレル LDO には、評価用の追加コネクタも搭載されています。MMCX コネクタは、 $V_{IN}$  と  $V_{OUT}$  の測定に使用できます。各パッケージの  $V_{ERR}$  を測定するためのテスト ポイントも用意されています (上側の IC 用に  $V_{ERR1}$ 、下側の IC 用に  $V_{ERR2}$ )。2 ピン ヘッダを使用して  $V_{ERR1}$  と  $V_{ERR2}$  を短絡させることができ、この設計ガイドの測定値はこの方法で取得しています。

### 3.3 テスト結果 - オペアンプを使用したパラレル LDO

このセクションのテスト結果は、以下の条件で測定されています。

$V_{IN} = 12V$ 、 $V_{OUT} = 10V$ 、 $C_{INn} = 10\mu F$ 、 $C_{OUTn} = 10\mu F$ 、 $C_{FFn} = 22nF$ 、 $V_{ERR} = V_{ERR1} = V_{ERR2}$ 、オペアンプ = OPA388-Q1 (特に記載がない限り)。

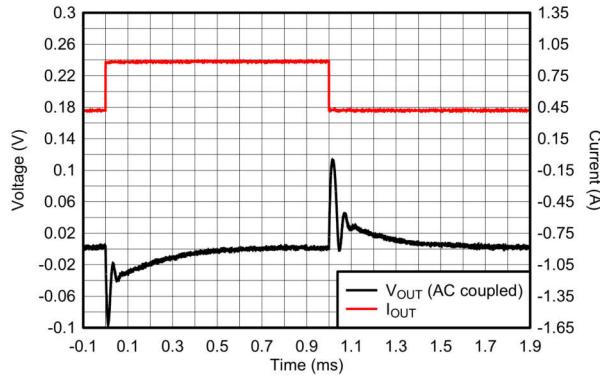

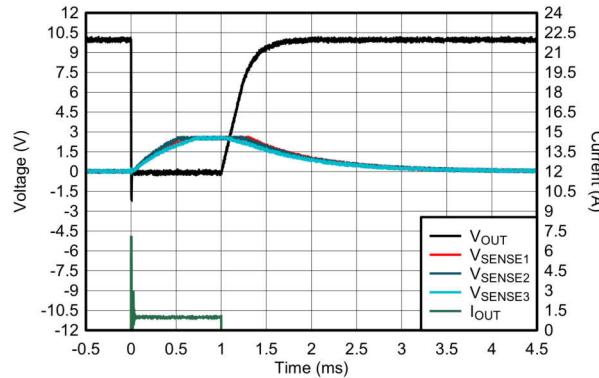

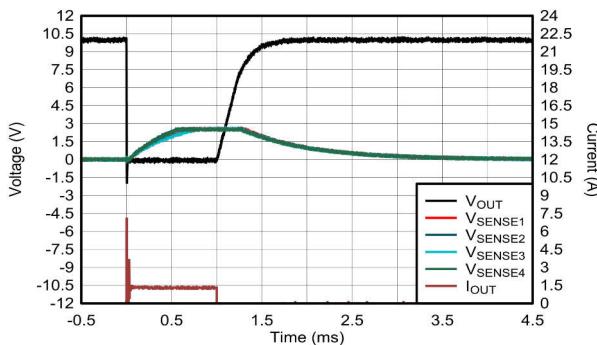

#### 3.3.1 ノバティリ短絡

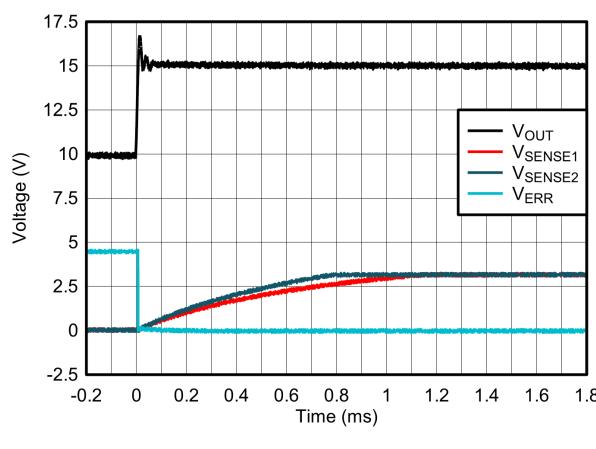

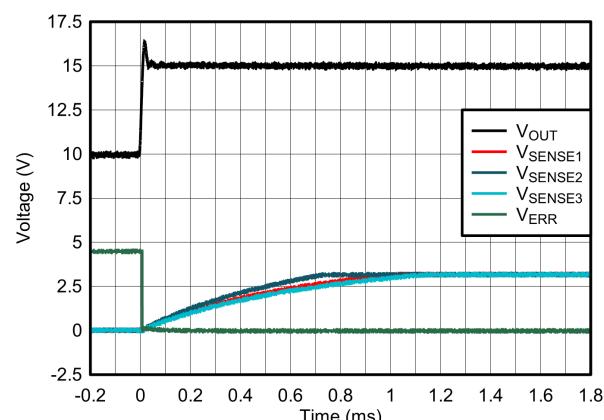

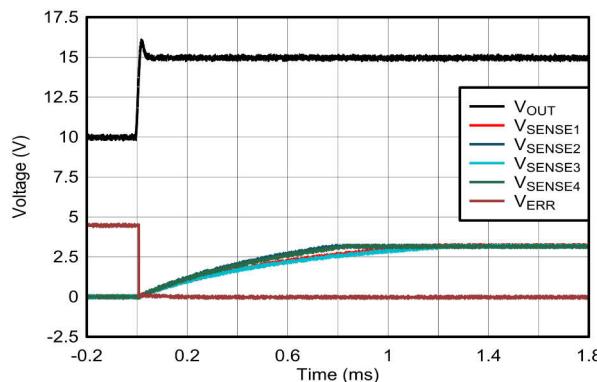

図 3-3. 2 つの LDO チャネル

図 3-4. 3 つの LDO チャネル

図 3-5. 4 つの LDO チャネル

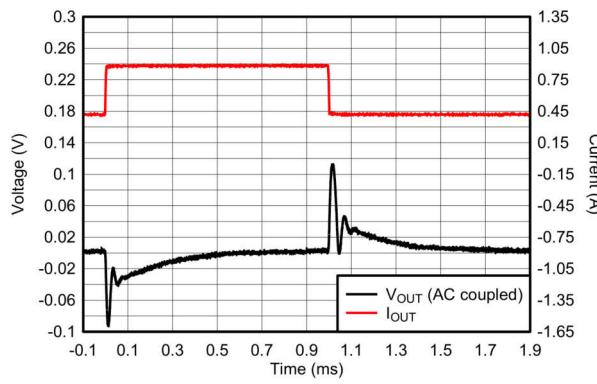

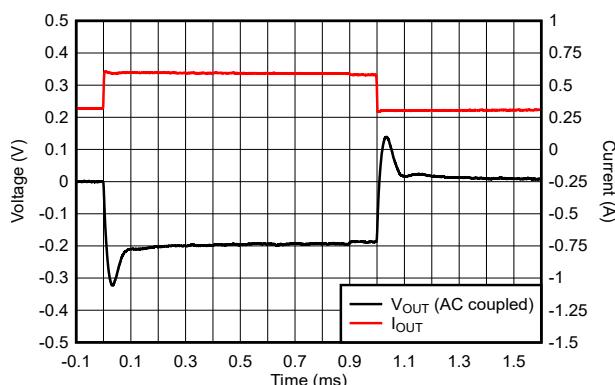

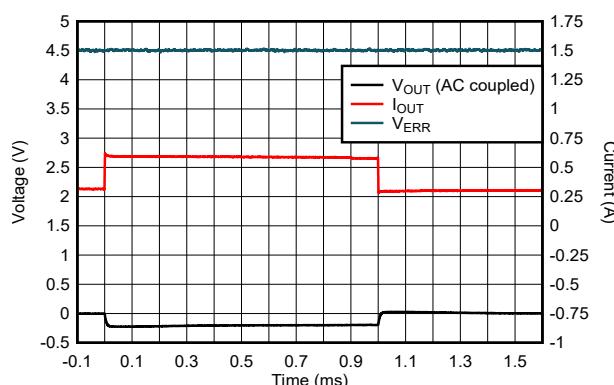

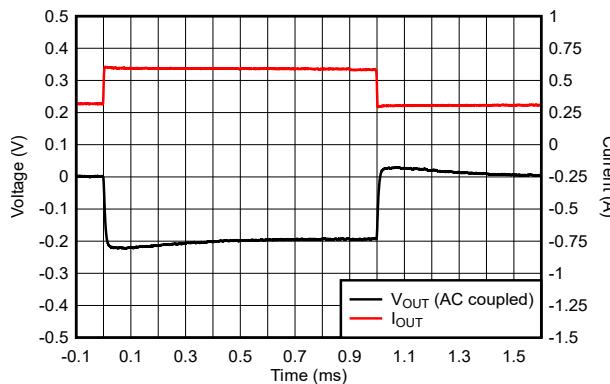

### 3.3.2 負荷過渡応答

$I_{OUT} = 600\text{mA} \rightarrow 1.2\text{A} \rightarrow 600\text{mA}$ , SR =  $1\text{A}/\mu\text{s}$

図 3-6. 4つのLDOチャネルの負荷過渡

$I_{OUT} = 600\text{mA} \rightarrow 1.2\text{A} \rightarrow 600\text{mA}$ , SR =  $1\text{A}/\mu\text{s}$

図 3-7. 4つのLDOチャネルの負荷過渡(拡大)

$I_{OUT} = 600\text{mA} \rightarrow 1.2\text{A} \rightarrow 600\text{mA}$ , SR =  $0.1\text{A}/\mu\text{s}$

図 3-8. 4つのLDOチャネルの負荷過渡

$I_{OUT} = 600\text{mA} \rightarrow 1.2\text{A} \rightarrow 600\text{mA}$ , SR =  $0.1\text{A}/\mu\text{s}$

図 3-9. 4つのLDOチャネルの負荷過渡(拡大)

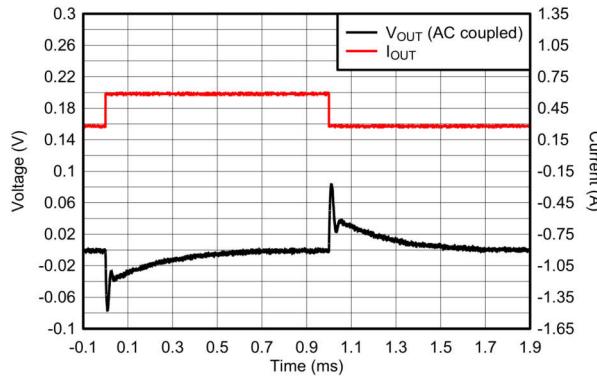

$I_{OUT} = 450\text{mA} \rightarrow 900\text{mA} \rightarrow 450\text{mA}$ , SR =  $1\text{A}/\mu\text{s}$

図 3-10. 3つのLDOチャネルの負荷過渡

$I_{OUT} = 450\text{mA} \rightarrow 900\text{mA} \rightarrow 450\text{mA}$ , SR =  $1\text{A}/\mu\text{s}$

図 3-11. 3つのLDOチャネルの負荷過渡(拡大)

$I_{OUT} = 450\text{mA} \rightarrow 900\text{mA} \rightarrow 450\text{mA}$ , SR =  $0.1\text{A}/\mu\text{s}$

図 3-12. 3 つの LDO チャネルの負荷過渡

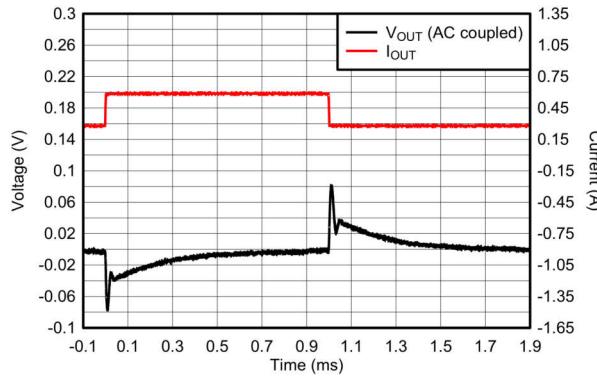

$I_{OUT} = 300\text{mA} \rightarrow 600\text{mA} \rightarrow 300\text{mA}$ , SR =  $1\text{A}/\mu\text{s}$ ,

$V_{ERR} = V_{ERR1}$

図 3-14. 2 つの LDO チャネルの負荷過渡

$I_{OUT} = 300\text{mA} \rightarrow 600\text{mA} \rightarrow 300\text{mA}$ , SR =  $0.1\text{A}/\mu\text{s}$ ,  $V_{ERR} = V_{ERR1}$

図 3-16. 2 つの LDO チャネルの負荷過渡

$I_{OUT} = 450\text{mA} \rightarrow 900\text{mA} \rightarrow 450\text{mA}$ , SR =  $0.1\text{A}/\mu\text{s}$

図 3-13. 3 つの LDO チャネルの負荷過渡 (拡大)

$I_{OUT} = 300\text{mA} \rightarrow 600\text{mA} \rightarrow 300\text{mA}$ , SR =  $1\text{A}/\mu\text{s}$

図 3-15. 2 つの LDO チャネルの負荷過渡 (拡大)

$I_{OUT} = 300\text{mA} \rightarrow 600\text{mA} \rightarrow 300\text{mA}$ , SR =  $0.1\text{A}/\mu\text{s}$

図 3-17. 2 つの LDO チャネルの負荷過渡 (拡大)

### 3.3.3 電流制限

図 3-18. 2 つの LDO チャネル

図 3-19. 3 つの LDO チャネル

図 3-20. 4 つの LDO チャネル

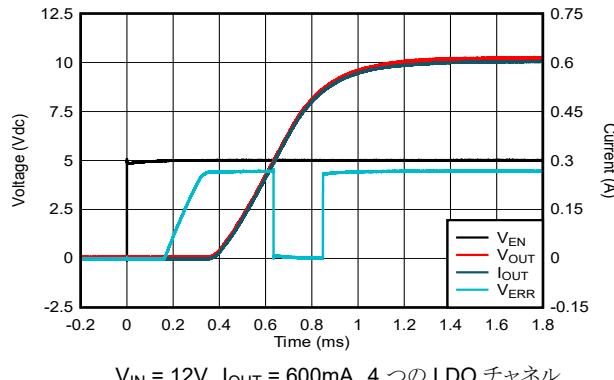

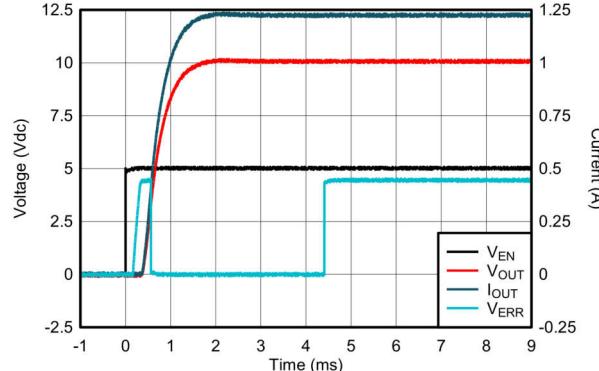

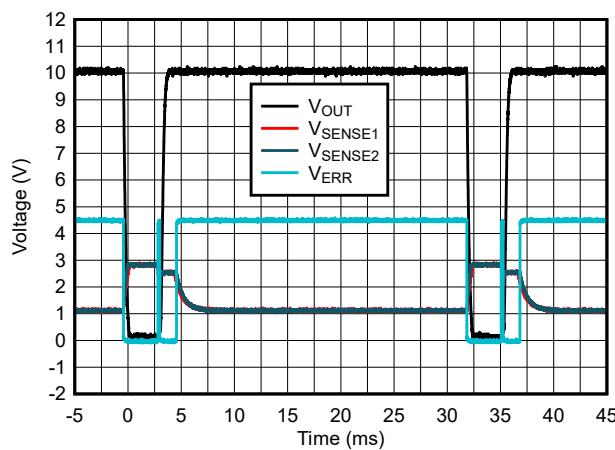

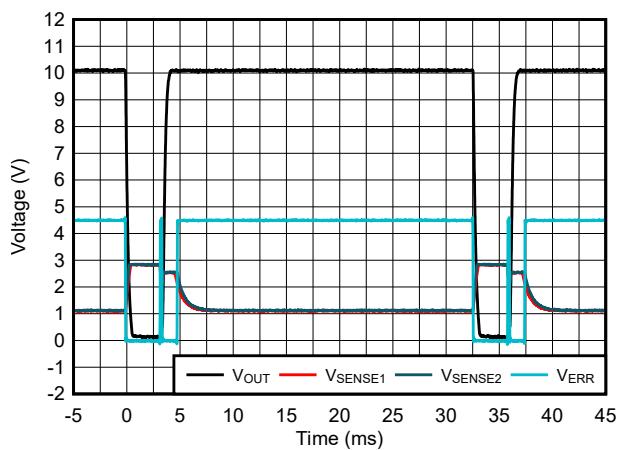

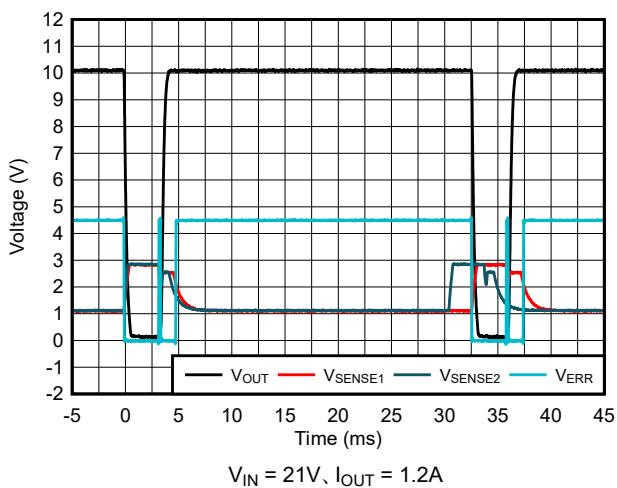

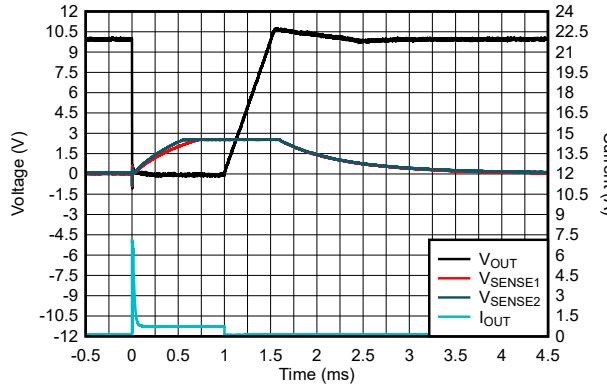

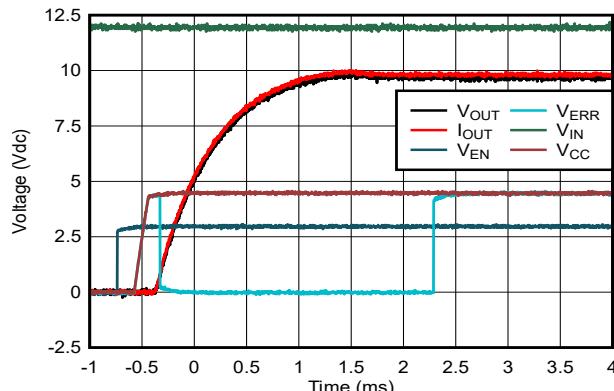

### 3.3.4 スタートアップ

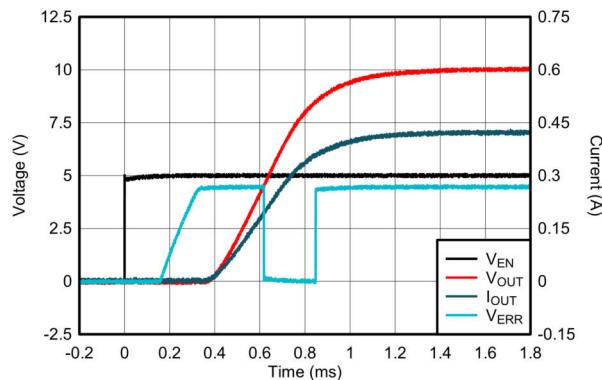

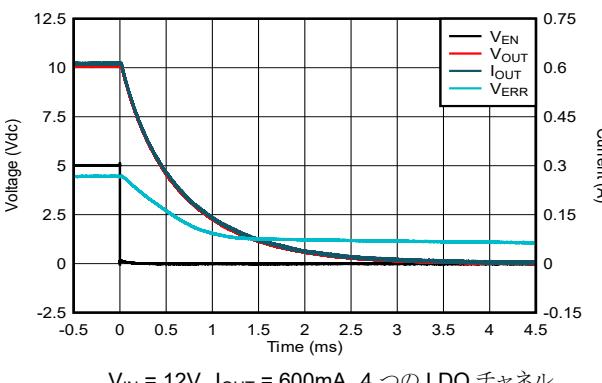

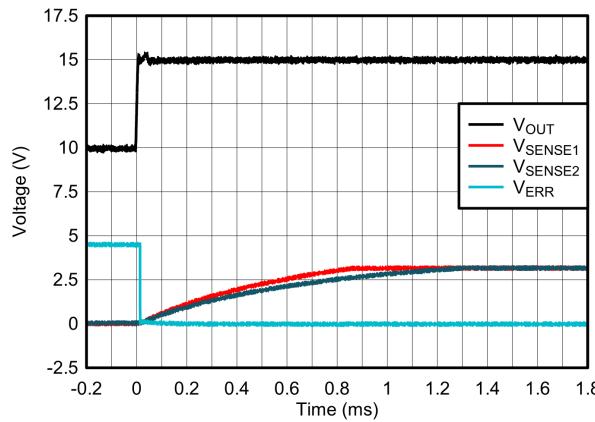

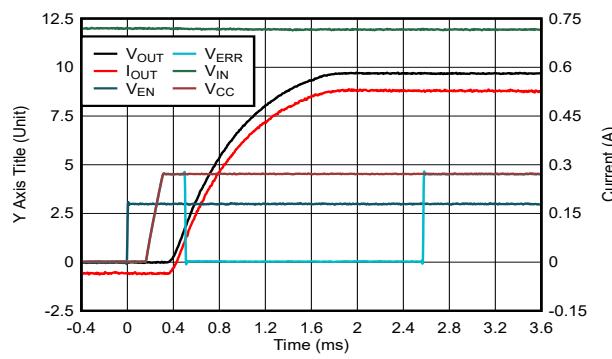

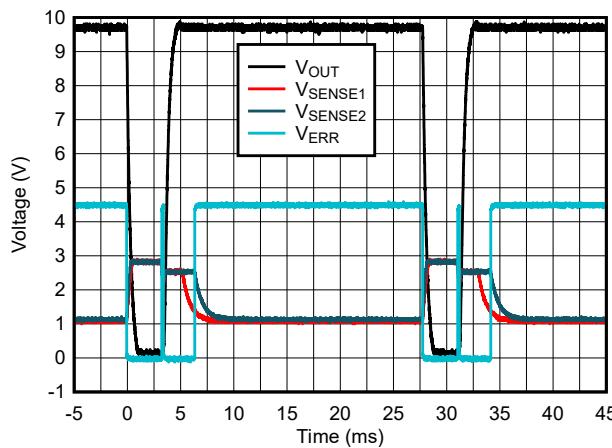

$V_{IN} = 12V$ ,  $I_{OUT} = 600mA$ 、4 つの LDO チャネル

図 3-21. 600mA 負荷に対するスタートアップ

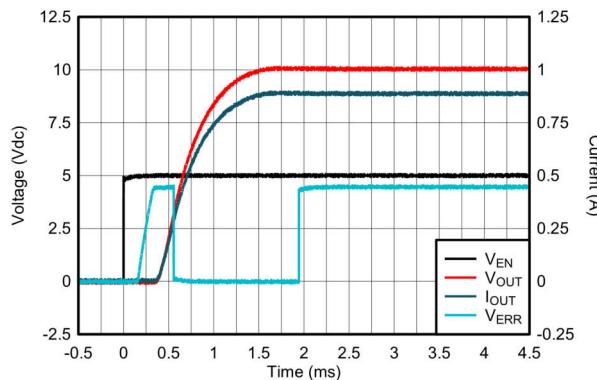

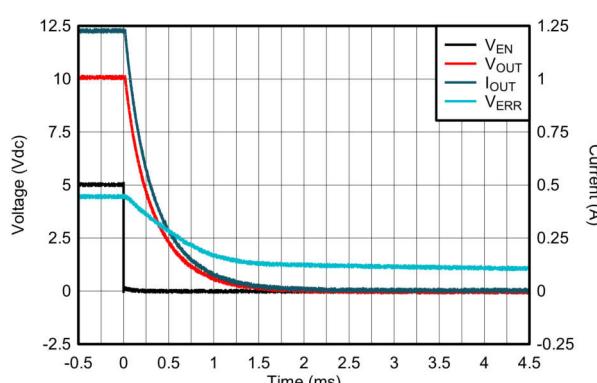

$V_{IN} = 12V$ ,  $I_{OUT} = 1.2A$ 、4 つの LDO チャネル

図 3-22. 1.2A 負荷に対するスタートアップ

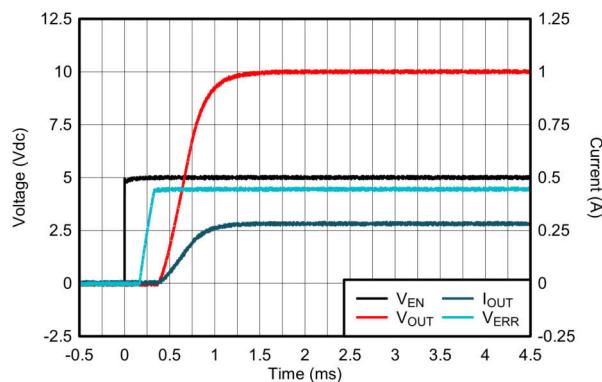

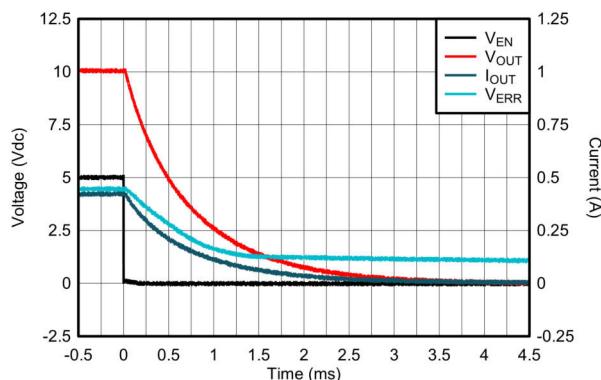

図 3-23. 415mA 負荷に対するスタートアップ

図 3-24. 870mA 負荷に対するスタートアップ

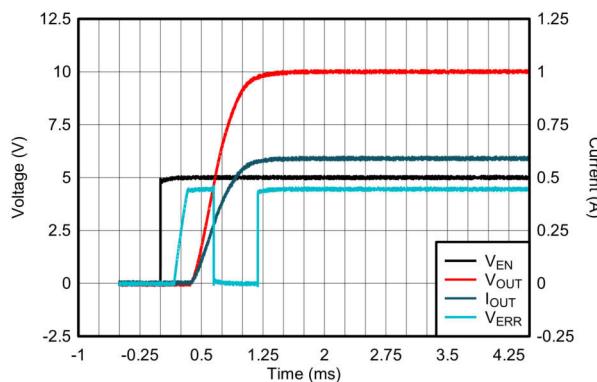

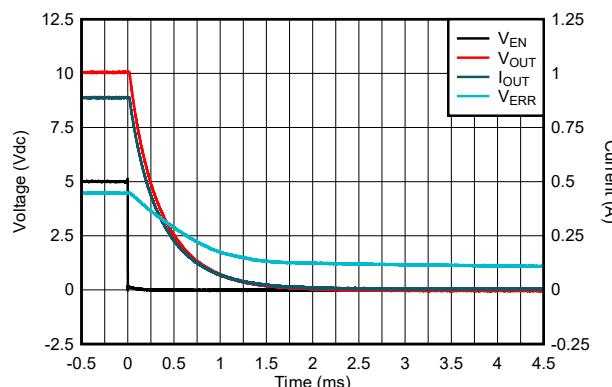

図 3-25. 275mA 負荷に対するスタートアップ

図 3-26. 580mA 負荷に対するスタートアップ

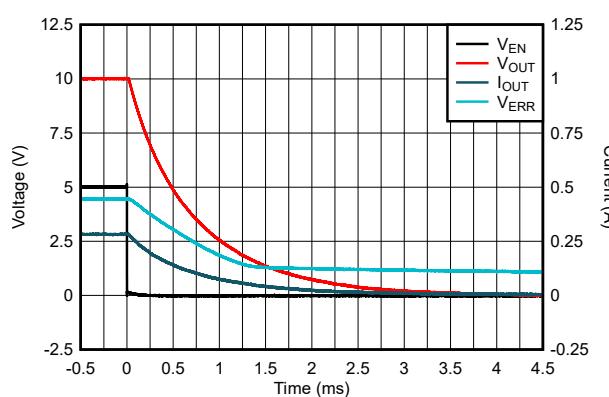

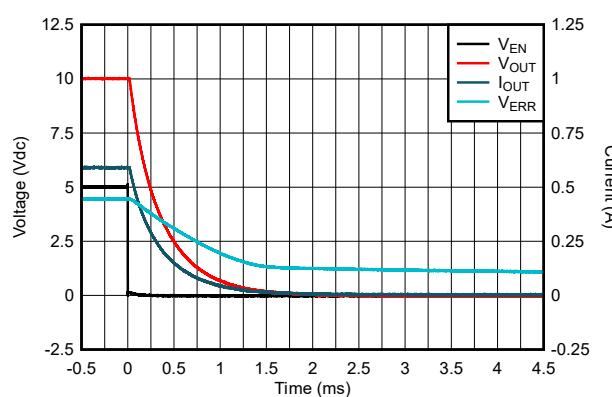

### 3.3.5 シャットダウン

図 3-27. 600mA 負荷に対するシャットダウン

図 3-28. 1.2A 負荷に対するシャットダウン

$V_{IN} = 12V, I_{OUT} = 415mA, 3 \text{ つの LDO チャネル}$

**図 3-29. 415mA 負荷に対するシャットダウン**

$V_{IN} = 12V, I_{OUT} = 870mA, 3 \text{ つの LDO チャネル}$

**図 3-30. 870mA 負荷に対するシャットダウン**

$V_{IN} = 12V, I_{OUT} = 275mA, V_{ERR} = V_{ERR1}, 2 \text{ つの LDO チャネル}$

**図 3-31. 275mA 負荷に対するシャットダウン**

$V_{IN} = 12V, I_{OUT} = 580mA, V_{ERR} = V_{ERR1}, 2 \text{ つの LDO チャネル}$

**図 3-32. 580mA 負荷に対するシャットダウン**

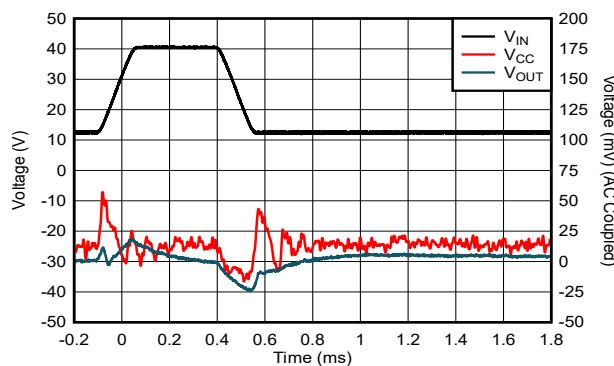

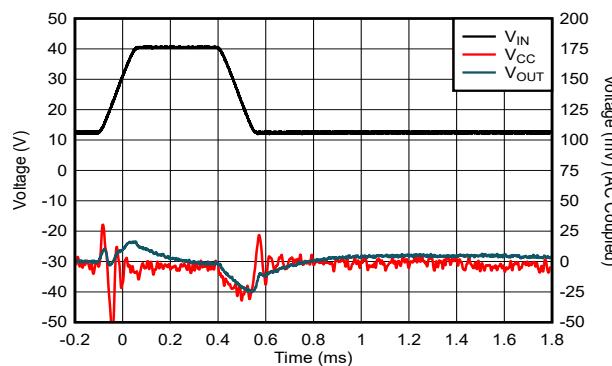

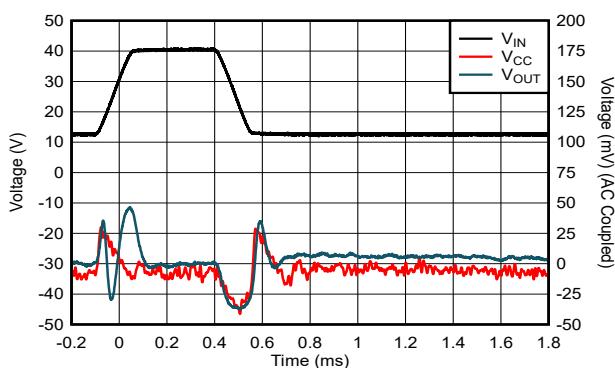

### 3.3.6 ライントランジエント

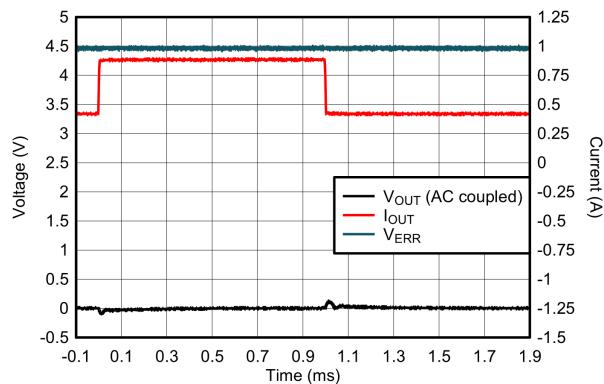

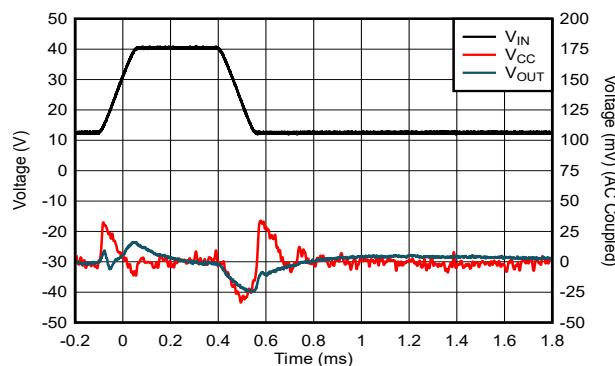

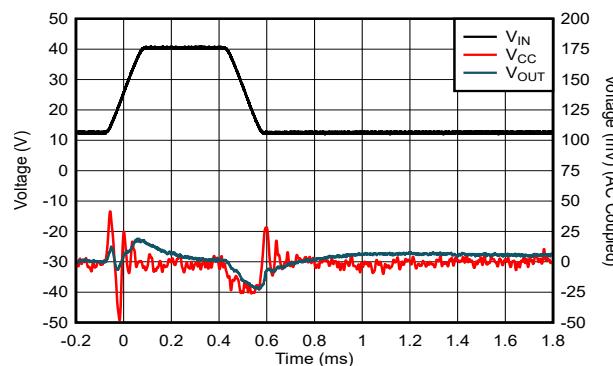

$\text{オペアンプ} = \text{LMV321A}, 0.25V/\mu\text{s}, 2 \text{ つの LDO チャネル}, 625mA \text{ 負荷}$

$\text{オペアンプ} = \text{OPA388}, 0.25V/\mu\text{s}, 2 \text{ つの LDO チャネル}, 625mA \text{ 負荷}$

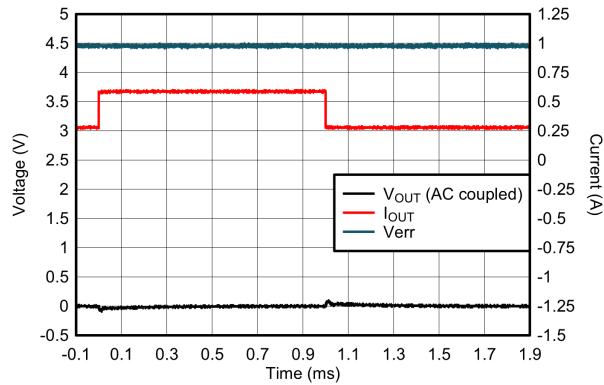

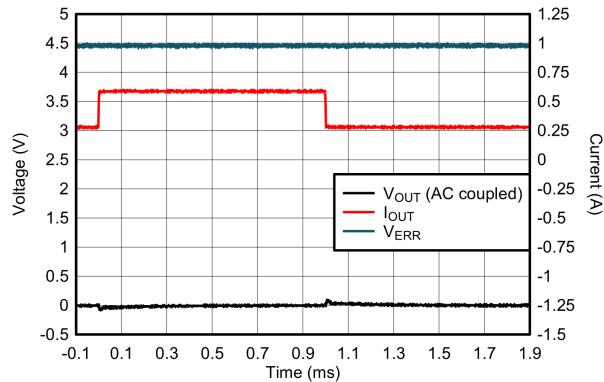

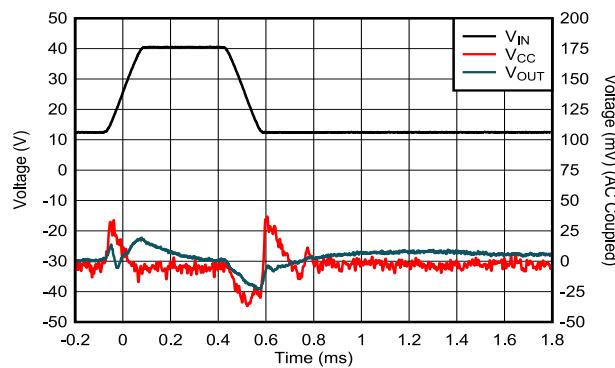

図 3-35. オペアンプ = LMV321A、 $0.25\text{V}/\mu\text{s}$ 、3 つの LDO チャネル、900mA 負荷

図 3-36. オペアンプ = OPA388、 $0.25\text{V}/\mu\text{s}$ 、3 つの LDO チャネル、900mA 負荷

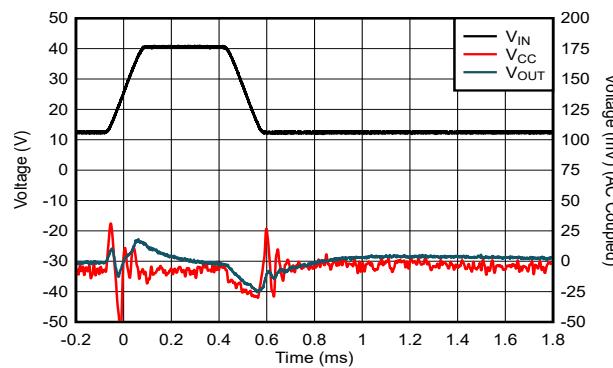

図 3-37. オペアンプ = LMV321A、 $0.25\text{V}/\mu\text{s}$ 、4 つの LDO チャネル、1.2A 負荷

図 3-38. オペアンプ = OPA388、 $0.25\text{V}/\mu\text{s}$ 、4 つの LDO チャネル、1.2A 負荷

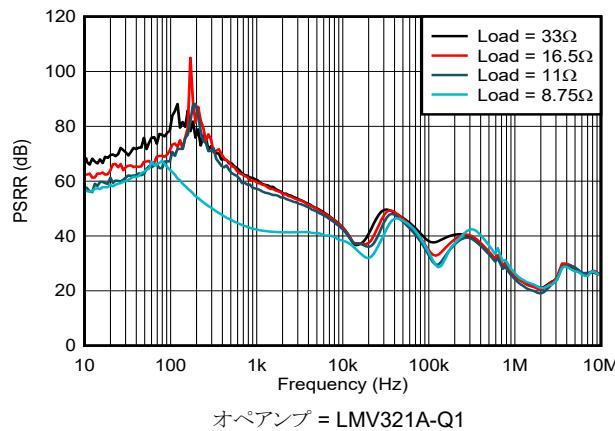

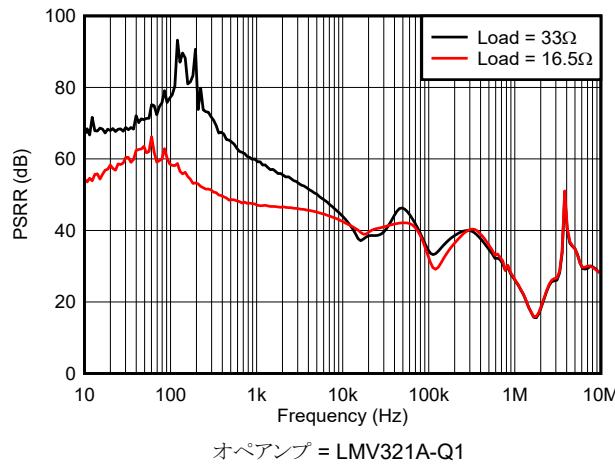

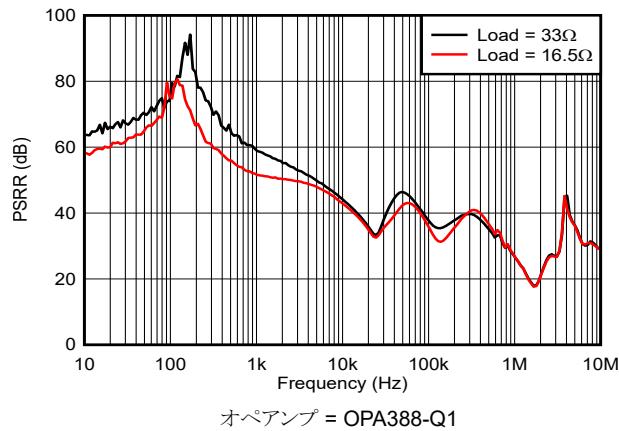

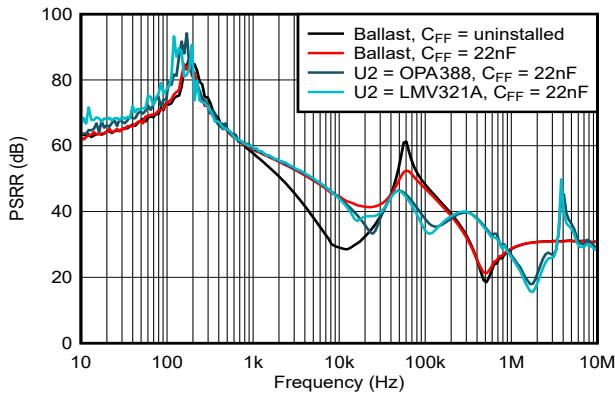

### 3.3.7 PSRR

図 3-39. 4 つの LDO チャネル: PSRR と周波数および  $I_{OUT}$  との関係

図 3-40. 4 つの LDO チャネル: PSRR と周波数および  $I_{OUT}$  との関係

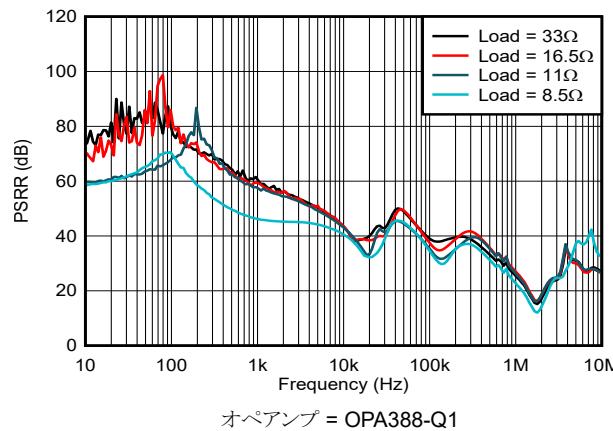

図 3-41. 3 つの LDO チャネル:PSRR と周波数および

$I_{OUT}$  との関係

図 3-42. 3 つの LDO チャネル:PSRR と周波数および

$I_{OUT}$  との関係

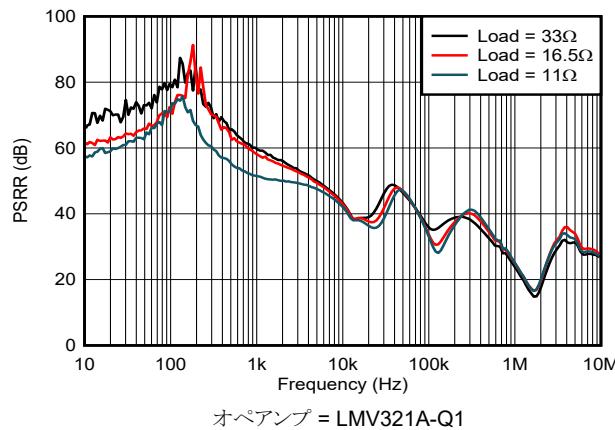

図 3-43. 2 つの LDO チャネル:PSRR と周波数および

$I_{OUT}$  との関係

図 3-44. 2 つの LDO チャネル:PSRR と周波数および

$I_{OUT}$  との関係

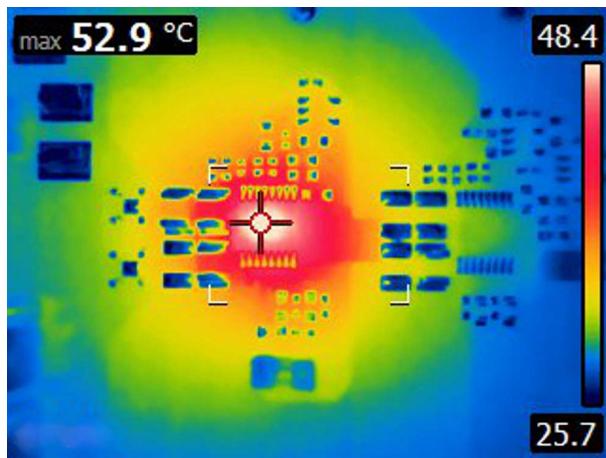

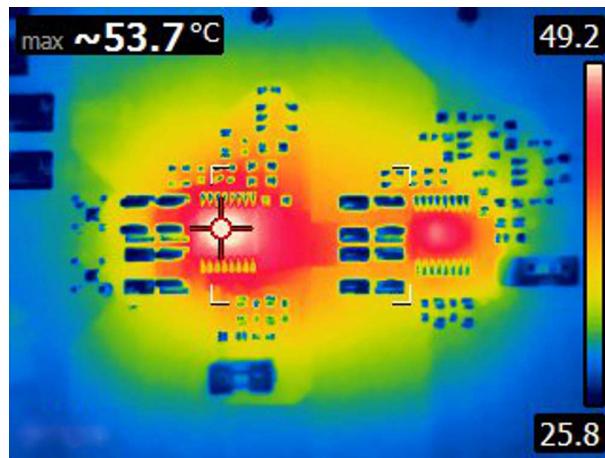

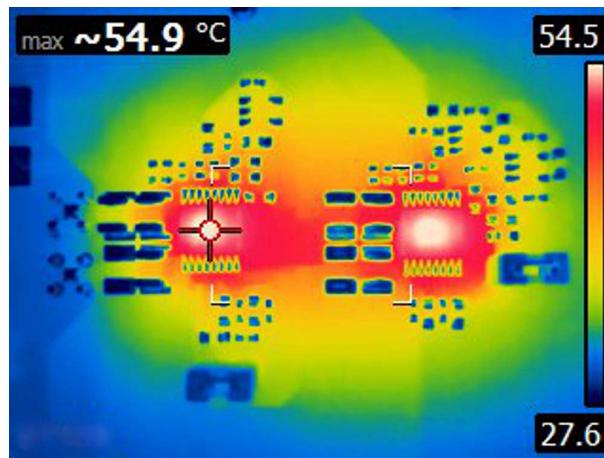

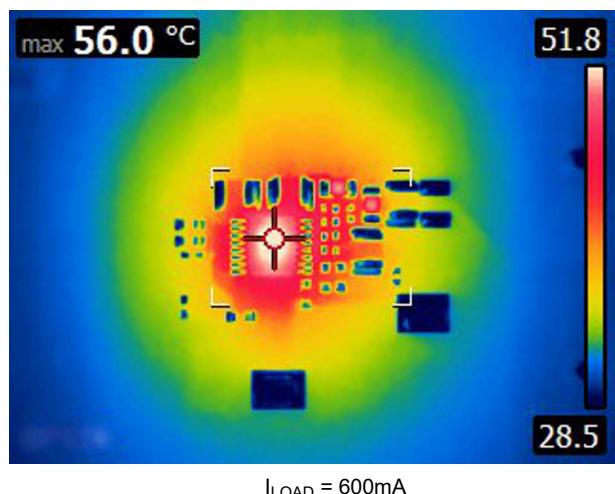

### 3.3.8 熱性能

測定ごとに、負荷は 30 分印可されます。測定は、約 26°C の周囲温度でキャプチャされます。

$I_{LOAD} = 600\text{mA}$ 、オペアンプ = OPA388-Q1

図 3-45. 2 つの LDO チャネル

$I_{LOAD} = 900\text{mA}$ 、オペアンプ = OPA388-Q1

図 3-46. 3 つの LDO チャネル

$I_{LOAD} = 1.2\text{A}$ 、オペアンプ = OPA388-Q1

図 3-47. 4 つの LDO チャネル

### 3.3.9 サーマル制限保護

パラレル LDO チャネルのサーマル保護性能は、各 LDO がサーマル シャットダウンを開始して終了する際（オフ／オン時）に、 $V_{LOAD}$  に階段状の変化を示します。パラレル LDO チャネルの消費電力が解消されるまで、サーマル保護は繰り返し動作します。図 3-48 は、LDO 全体で大きな消費電力が発生している場合でも、サーマル保護回路が意図したとおりに機能していることを示しています。

図 3-48. 2 つの LDO チャネル

図 3-49. 3 つの LDO チャネル

図 3-50. 4 つの LDO チャネル

### 3.4 テスト結果 - バラスト抵抗を使用したパラレル LDO

このセクションのテスト結果は、以下の条件で測定されています。

$V_{IN} = 12V$ 、 $V_{OUT} = 10V$ 、 $C_{INn} = 10\mu F$ 、 $C_{OUTn} = 10\mu F$ 、 $C_{FFn} = 22nF$ 、 $R_B = 1.33\Omega$ 、 $C_{LOAD} = 10\mu F$  (特に記載がない限り)。

#### 3.4.1 バッテリ短絡

$$V_{ERR} = V_{ERR1}$$

図 3-51. 2 つの LDO チャネル

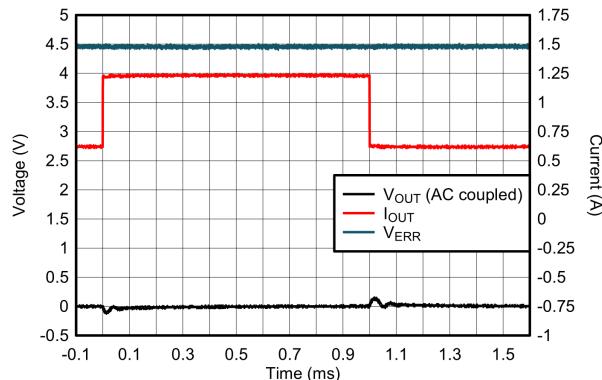

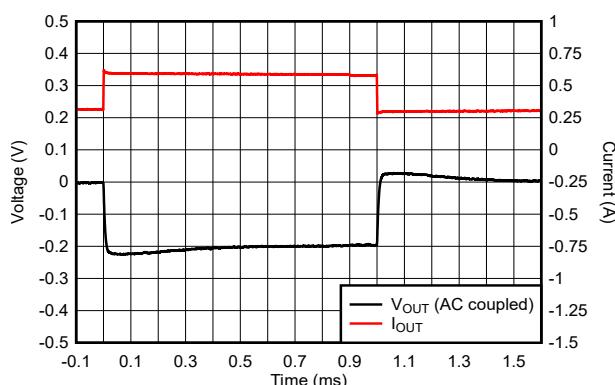

### 3.4.2 負荷過渡応答

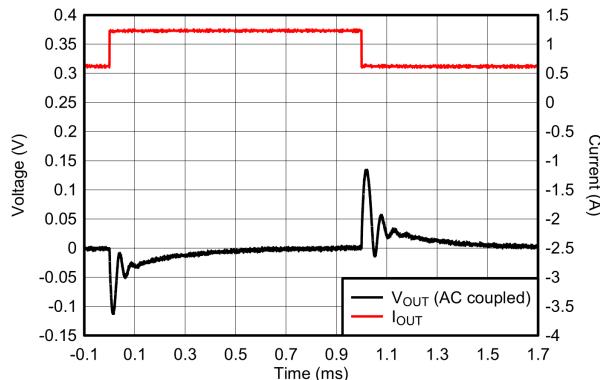

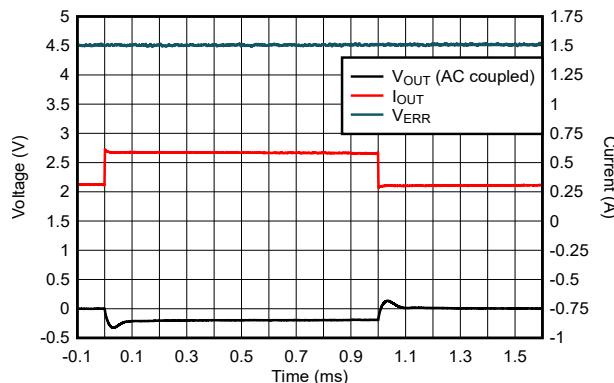

$I_{OUT} = 300mA \rightarrow 600mA \rightarrow 300mA, SR = 1A/\mu s,$

$C_{FF} = \text{未実装}$

図 3-52. 2 つの LDO チャネル

$I_{OUT} = 300mA \rightarrow 600mA \rightarrow 300mA, SR = 1A/\mu s,$

$C_{FF} = \text{未実装}$

図 3-53. 2 つの LDO チャネル (拡大)

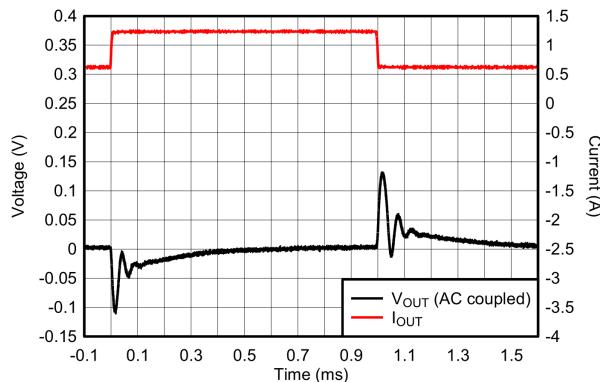

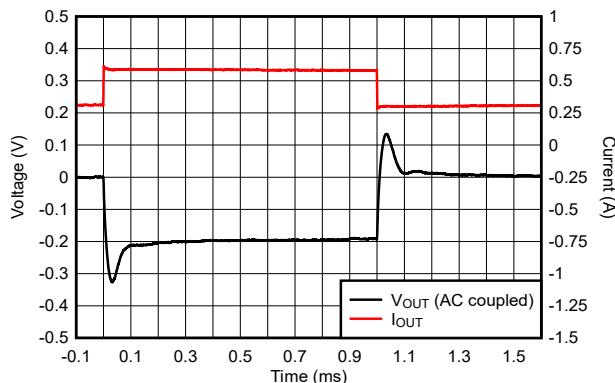

$I_{OUT} = 300mA \rightarrow 600mA \rightarrow 300mA, SR = 0.1A/\mu s,$

$C_{FF} = \text{未実装}$

図 3-54. 2 つの LDO チャネル

$I_{OUT} = 300mA \rightarrow 600mA \rightarrow 300mA, SR = 0.1A/\mu s,$

$C_{FF} = \text{未実装}$

図 3-55. 2 つの LDO チャネル (拡大)

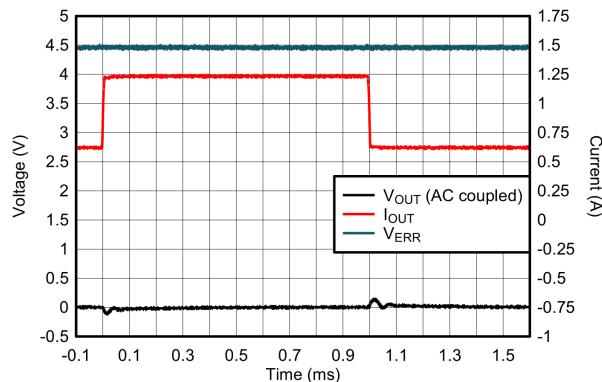

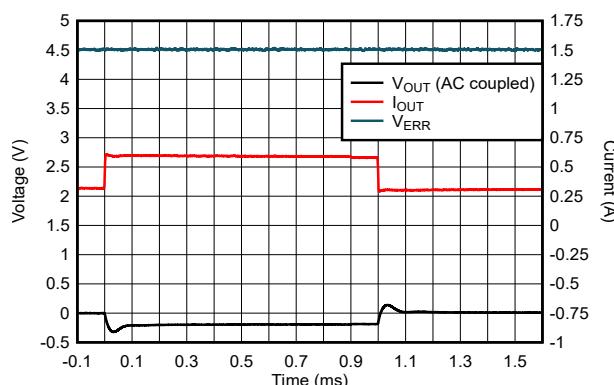

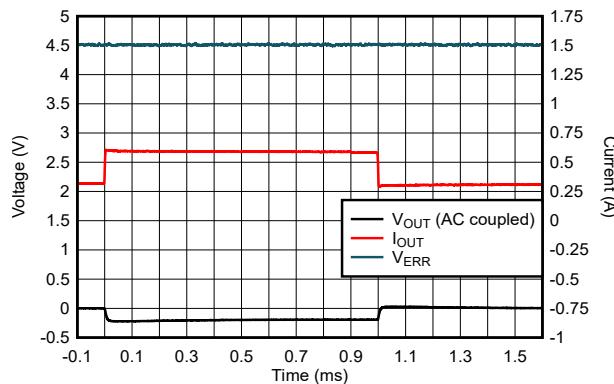

$I_{OUT} = 300mA \rightarrow 600mA \rightarrow 300mA, SR = 1A/\mu s, C_{FF} = 22nF$

図 3-56. 2 つの LDO チャネル

$I_{OUT} = 300mA \rightarrow 600mA \rightarrow 300mA, SR = 1A/\mu s,$

$C_{FF} = 22nF$

図 3-57. 2 つの LDO チャネル (拡大)

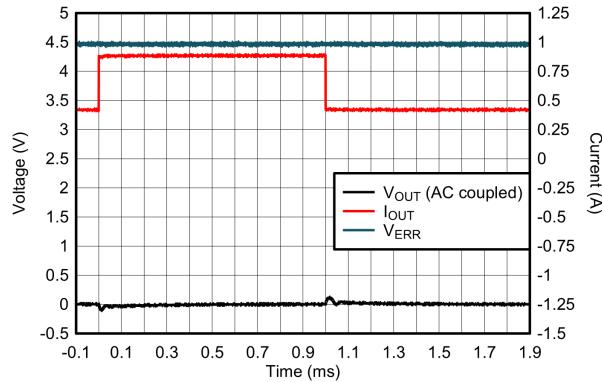

$I_{OUT} = 300\text{mA} \rightarrow 600\text{mA} \rightarrow 300\text{mA}$ , SR =  $0.1\text{A}/\mu\text{s}$ ,  $C_{FF} = 22\text{nF}$

図 3-58. 2 つの LDO チャネル

$I_{OUT} = 300\text{mA} \rightarrow 600\text{mA} \rightarrow 300\text{mA}$ , SR =  $0.1\text{A}/\mu\text{s}$ ,  $C_{FF} = 22\text{nF}$

図 3-59. 2 つの LDO チャネル (拡大)

### 3.4.3 電流制限

図 3-60. 2 つの LDO チャネル

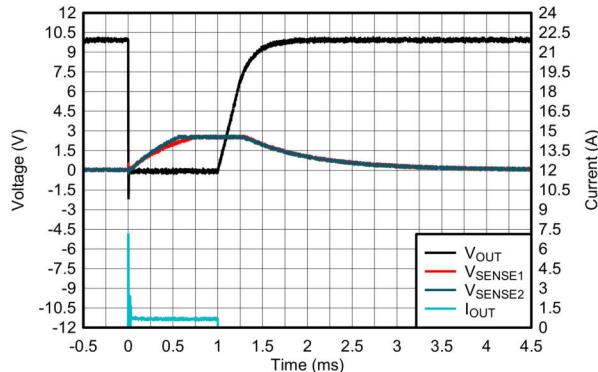

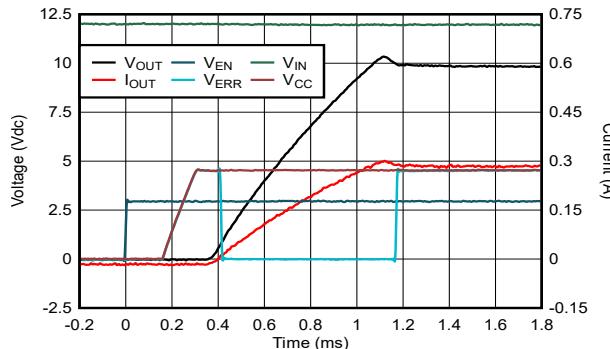

### 3.4.4 スタートアップ

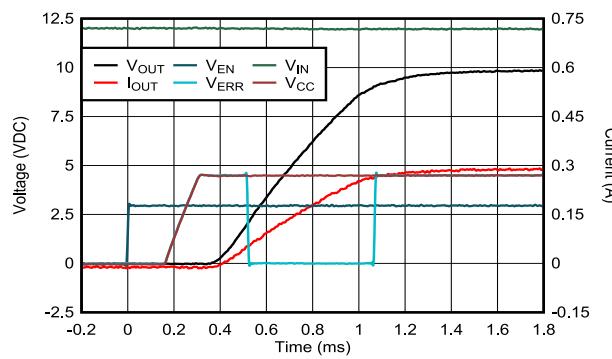

$V_{IN} = 12\text{V}$ ,  $I_{OUT} = 600\text{mA}$ ,  $C_{FF}$  = 未実装

図 3-61. 600mA 負荷に対するスタートアップ

$V_{IN} = 12\text{V}$ ,  $I_{OUT} = 300\text{mA}$ ,  $C_{FF}$  = 未実装

図 3-62. 300mA 負荷に対するスタートアップ

図 3-63. 565mA 負荷に対するスタートアップ

図 3-64. 300mA 負荷に対するスタートアップ

### 3.4.5 ライントランジエント

図 3-65. 0.25V/ $\mu$ s、2 つの LDO チャネル、598mA 負荷

### 3.4.6 熱性能

測定ごとに、負荷は 30 分印可されます。測定は、約 26°C の周囲温度でキャプチャされます。

図 3-66. 2 つの LDO チャネル

### 3.4.7 サーマル制限保護

パラレル LDO チャネルのサーマル保護性能は、各 LDO がサーマル シャットダウンを開始して終了する際 (オフ／オン時) に、 $V_{LOAD}$  に階段状の変化を示します。パラレル LDO の消費電力が解消されるまで、サーマル保護は繰り返し動作します。図 3-48 は、LDO 全体で大きな消費電力が発生している場合でも、サーマル保護回路が意図したとおりに機能していることを示しています。

図 3-67. 2 つの LDO チャネル (パラスト)

### 3.5 パラレル LDO 方式間の結果の比較

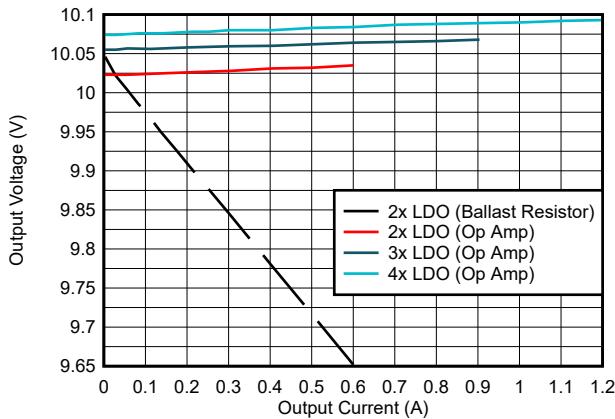

このセクションのテスト結果は、以下の条件で測定されています。

$V_{IN} = 12V$ 、 $V_{OUT} = 10V$ 、 $C_{INn} = 10\mu F$ 、 $C_{OUTn} = 10\mu F$ 、 $C_{FFn} = 22nF$ 、 $R_B = 1.33\Omega$ 、 $C_{LOAD} = 10\mu F$ 、オペアンプ = OPA388-Q1 (特に記載がない限り)。

#### 3.5.1 $V_{LOAD}$ と $I_{LOAD}$ との関係

図 3-68. 負荷電圧と総負荷電流との関係

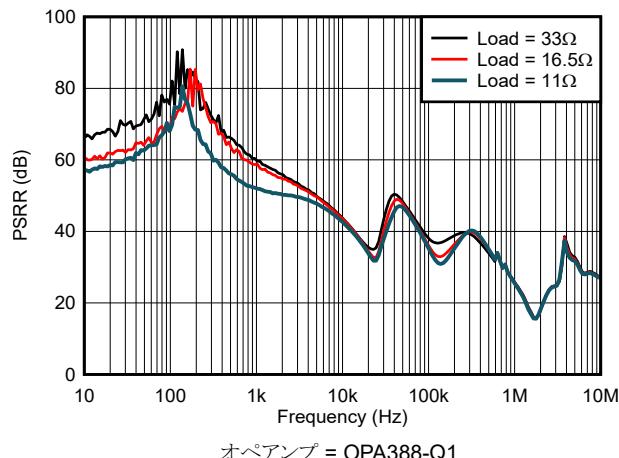

#### 3.5.2 PSRR

図 3-69. 2 つの LDO:PSRR と周波数との関係

## 4 設計とドキュメントのサポート

### 4.1 デザイン ファイル

#### 4.1.1 回路図

回路図をダウンロードするには、[TIDA-050096](#) のデザイン ファイルを参照してください。

#### 4.1.2 BOM

部品表 (BOM) をダウンロードするには、[TIDA-050096](#) のデザイン ファイルを参照してください。

#### 4.1.3 レイアウト プリント

レイヤ プロットをダウンロードするには、[TIDA-050096](#) のデザイン ファイルを参照してください。

### 4.2 ツール

バラスト抵抗カリキュレータを使用し 一連のシステム要件 (温度、 $V_{IN}$ 、 $V_{OUT}$ 、 $I_{LOAD}$ 、ロード レギュレーション、ノイズ) を満たすために必要なパラレル LDO の最小数を簡単に計算できます。

### 4.3 ドキュメントのサポート

1. IPC-2221B『プリント基板設計に関する共通基準』

2. テキサス インスツルメンツ、[『TPS7B770x-Q1 電流センス搭載、車載、シングルチャネル アンテナ/デュアルチャネル アンテナ LDO』データシート](#)

3. テキサス インスツルメンツ、[『LMV321A-Q1, LMV358A-Q1, LMV324A-Q1 車載用低電圧レール ツー レール出力 オペアンプ』データシート](#)

4. テキサス インスツルメンツ、[『バラスト抵抗を使ったパラレル LDO の包括的解析と一般方程式』技術白書](#)

5. テキサス インスツルメンツ、[『パラレル LDO \(低ドロップアウト\) のカリキュレータ』](#)

6. テキサス インスツルメンツ、[『バラスト抵抗を使用したパラレル LDO アーキテクチャ設計』技術白書](#)

7. テキサス インスツルメンツ、[『新しい熱評価基準の解説』アプリケーションノート](#)

8. テキサス インスツルメンツ、[『DIY: オペアンプの容量性負荷を安定化する 3 つの方法』技術記事](#)

9. テキサス インスツルメンツ、[『OPAx388 高精度、ゼロドリフト、ゼロクロスオーバー、真のレール ツー レール入出力の オペアンプ』データシート](#)

### 4.4 サポート・リソース

テキサス・インスツルメンツ E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツルメンツの[使用条件](#)を参照してください。

### 4.5 商標

テキサス・インスツルメンツの E2E™ and テキサス・インスツルメンツ E2E™ are trademarks of Texas Instruments. すべての商標は、それぞれの所有者に帰属します。

## 5 著者について

**STEPHEN ZIEL** は、低電圧 LDO 担当のアプリケーションおよび検証マネージャであり、2023 年に Member, Group Technical Staff (MGTS) に選出され、就任しました。TI に入社する前は大手の航空宇宙・防衛企業の主任エンジニアとして、1mW ~ 1.5kW にわたるあらゆる電力エレクトロニクス分野の業務に携わっていました。Stephen は、電源システム要件の策定とアーキテクチャ設計、電源回路設計、電源エンジニアの大規模なチームを指揮するエンジニアリング マネジメントにおいて 18 年以上の経験を有しています。また、ミシガン州立大学で電気工学の学士号 (BSEE) と修士号 (MSEE) を取得しています。

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Webツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適したTI製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているTI製品を使用するアプリケーションの開発の目的でのみ、TIはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TIや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TIおよびその代理人を完全に補償するものとし、TIは一切の責任を拒否します。

TIの製品は、[TIの販売条件](#)、[TIの総合的な品質ガイドライン](#)、[ti.com](#)またはTI製品などに関連して提供される他の適用条件に従い提供されます。TIがこれらのリソースを提供することは、適用されるTIの保証または他の保証の放棄の拡大や変更を意味するものではありません。TIがカスタム、またはカスタマー仕様として明示的に指定していない限り、TIの製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TIはそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025年10月