## EVM User's Guide: TMDS62LEVM

# AM62L 評価基板

## 説明

TMDS62LEVM 評価基板 (EVM) は、低コストかつ性能が最適化された AM62L アプリケーション プロセッサ ファミリ用に設計されています。AM62L は、スケーラブルな Arm® Cortex®-A53 コアの性能と、以下のような組込み機能を搭載しています。すなわち、マルチメディア DSI サポート、チップ内蔵 ADC、高度な低消費電力管理モード、および IP 保護とセキュア ブート用の広範なセキュリティオプションです。AM62L デバイス ファミリは、Linux® と FreeRTOS™ を用いた開発をサポートしています。

TMDS62LEVM には、広範な産業用アプリケーションに適した幅広いペリフェラル セットが含まれており、また、インテリジェントな機能や最適化された電源アーキテクチャも提供します。さらに、AM62L に搭載されている幅広いペリフェラル セットにより、以下のようなシステム レベルのコネクティビティを実現できます。すなわち、USB、MMC/SD、OSPI、CAN-FD、ADC、およびプロトタイプの製作を容易にするその他のインターフェイスです。また、SoC と LPDDR4 それぞれの温度条件を監視するために 2 つのオンボード温度センサを採用しています。

## 設計を開始

1. [TMDS62LEVM](#) で EVM を注文します。

2. 評価基板の[設計ファイル](#)をダウンロードします。

3. [TMDS62LEVM](#) からソフトウェアをダウンロードします。

4. 『EVM ユーザー ガイド』を読みます。

## 特長

- ギガビットイーサネット RJ45 拡張コネクタ x 2

- 2GB LPDDR4 メモリ

- 512MB OSPI フラッシュ メモリ

- 1GB QSPI フラッシュ メモリ

- 32GB eMMC フラッシュ メモリ

- microSD カード スロット

- USB 2.0 Type-C® x 1

- USB Type-A 2.0 x 1

- MCAN ヘッダ x 3

- 3.5mm TRRS オーディオ ジャック x 1

- Wi-Fi/BT モジュール用 M.2 コネクタ

- 外部ディスプレイ用 HDMI®コネクタ

- GPIO 拡張コネクタ x 2

- ADC ヘッダー

- DSI ディスプレイ コネクタ

## アプリケーション

- [ビル オートメーション](#):スマート ハウス デバイス、HVAC コントローラ、IoT デバイス

- [エネルギー インフラ](#):EV 充電および給電機器、スマートメーター

- [産業用オートメーション](#):ファクトリ オートメーション、ロボット、産業用 HMI

- [医療](#):医療用機器、患者モニタリング システム

TMDS62LEVM のハードウェア ボード

このリファレンスデザインは HDMI®技術を採用しています。

|                               |    |

|-------------------------------|----|

| <b>説明</b>                     | 1  |

| <b>設計を開始</b>                  | 1  |

| <b>特長</b>                     | 1  |

| <b>アプリケーション</b>               | 1  |

| <b>1 評価基板の概要</b>              | 4  |

| 1.1 はじめに                      | 4  |

| 1.2 キットの内容                    | 4  |

| 1.3 仕様                        | 5  |

| 1.4 製品情報                      | 5  |

| 1.5 EVM のリビジョンおよびアセンブリバリエーション | 6  |

| <b>2 ハードウェア</b>               | 6  |

| 2.1 補足画像                      | 6  |

| 2.2 主な特長                      | 7  |

| 2.3 電源要件                      | 8  |

| 2.4 設定および構成                   | 9  |

| 2.5 電源オン / オフの手順              | 16 |

| 2.6 インターフェイス                  | 19 |

| 2.7 電源                        | 42 |

| 2.8 クロック処理                    | 48 |

| 2.9 リセット                      | 49 |

| 2.10 拡張ヘッダ                    | 50 |

| 2.11 割り込み                     | 52 |

| 2.12 I2C アドレスマッピング            | 52 |

| <b>3 ハードウェア設計ファイル</b>         | 54 |

| 3.1 回路図                       | 54 |

| 3.2 PCB のレイアウト                | 54 |

| 3.3 部品表 (BOM)                 | 54 |

| <b>4 準拠に関する情報</b>             | 54 |

| 4.1 準拠および認証                   | 54 |

| <b>5 追加情報</b>                 | 54 |

| 5.1 ハードウェアまたはソフトウェアに関する既知の問題  | 54 |

| 5.2 商標                        | 55 |

| <b>6 関連資料</b>                 | 55 |

| <b>7 改訂履歴</b>                 | 55 |

## 図の一覧

|                                                       |    |

|-------------------------------------------------------|----|

| 図 1-1. AM62L EVM の機能ブロック図                             | 5  |

| 図 2-1. AM62L EVM の上面                                  | 6  |

| 図 2-2. AM62L EVM の底面                                  | 7  |

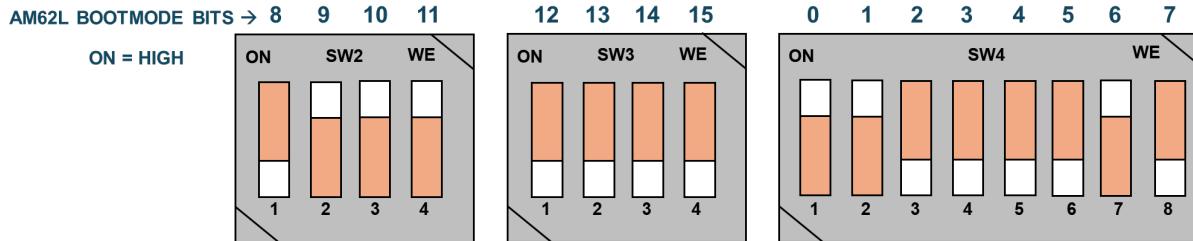

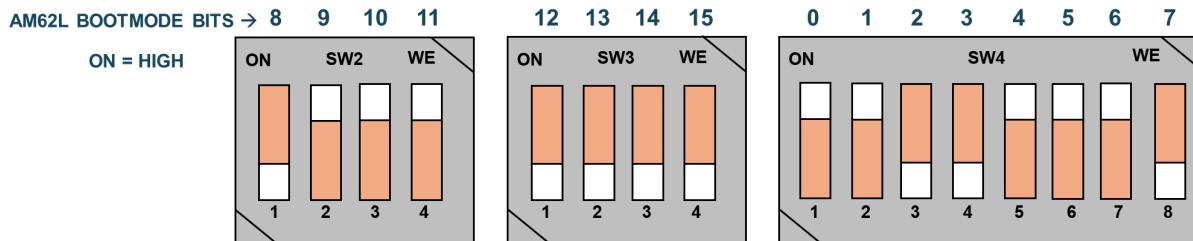

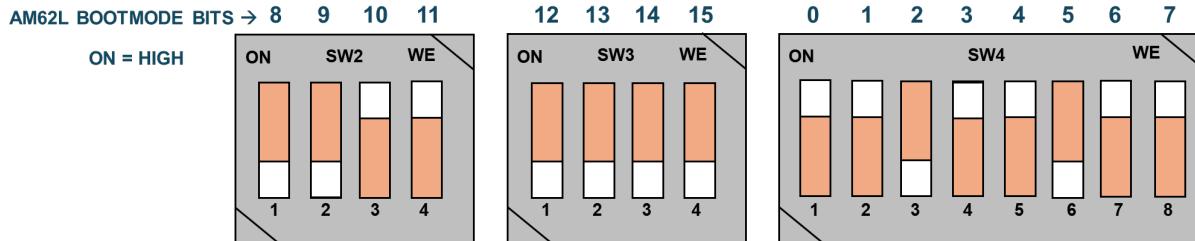

| 図 2-3. ブートモードスイッチの例 (フルピン数構成 - SD カードブート)             | 9  |

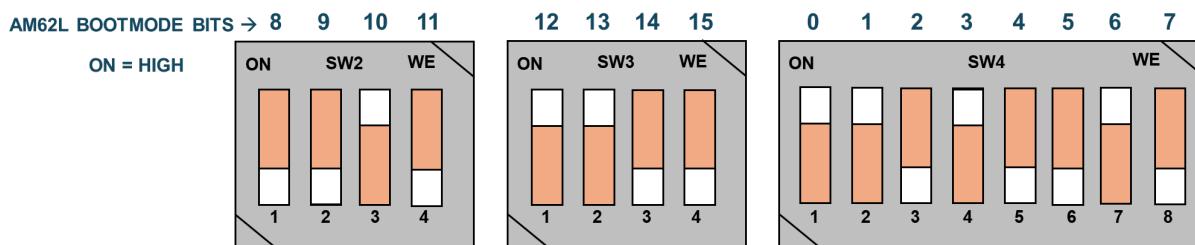

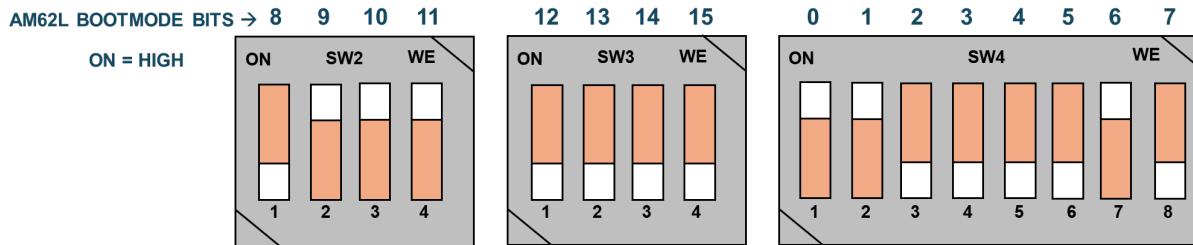

| 図 2-4. MMCSD/UART バックアップ用のブートモードスイッチの構成               | 15 |

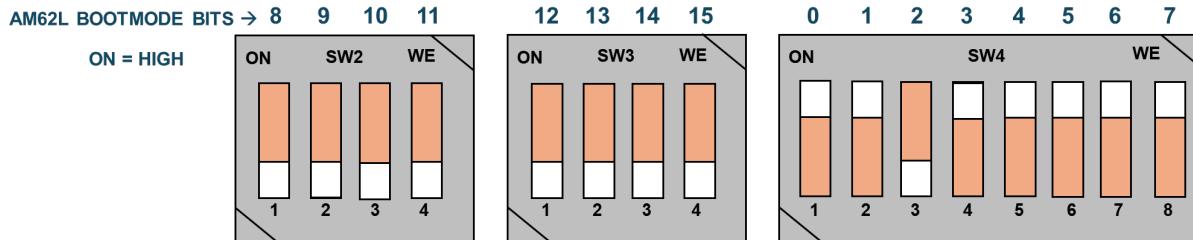

| 図 2-5. xSPI/UART バックアップ用のブートモードスイッチの構成                | 15 |

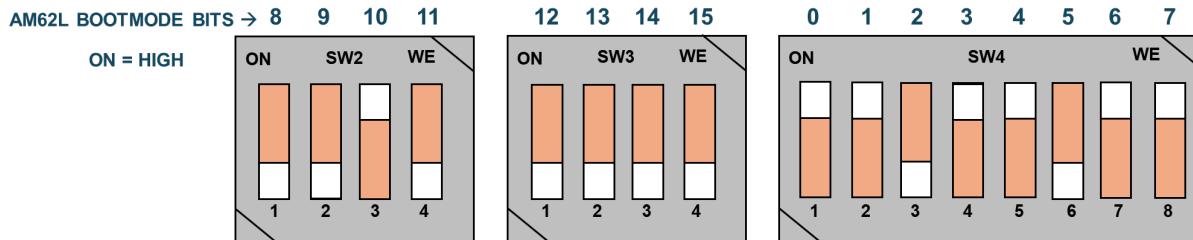

| 図 2-6. NOBOOT (DEVBOOT = 0) / バックアップなし用のブートモードスイッチの構成 | 15 |

| 図 2-7. GPMC NAND/USB バックアップ用のブートモードスイッチの構成            | 15 |

| 図 2-8. GPMC NAND/UART バックアップ用のブートモードスイッチの構成           | 16 |

| 図 2-9. eMMC/MMCSD バックアップ用のブートモードスイッチの構成               | 16 |

| 図 2-10. フルピン数構成のブートモード (SD カードブート) の例                 | 17 |

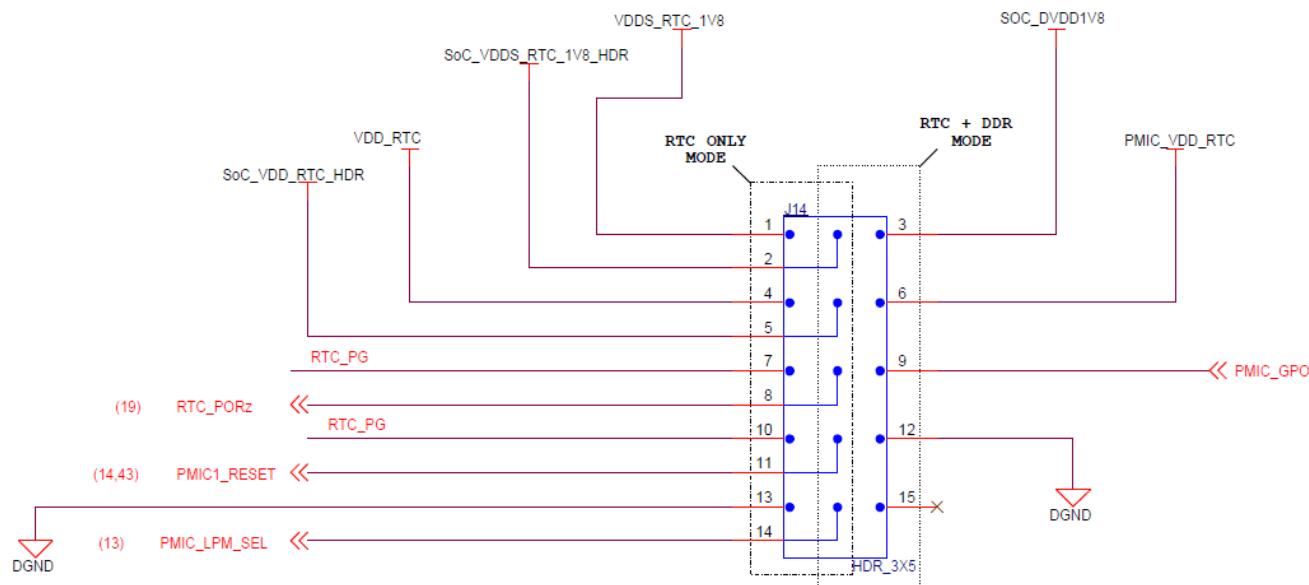

| 図 2-11. RTC 電源選択ヘッダ                                   | 17 |

| 図 2-12. DSI インターフェイスのブロック図                            | 20 |

| 図 2-13. オーディオコーデック インターフェイスのブロック図                     | 22 |

| 図 2-14. HDMI インターフェイスのブロック図                           | 23 |

| 図 2-15. JTAG インターフェイスのブロック図                           | 24 |

| 図 2-16. テストオートメーション インターフェイスのブロック図                    | 25 |

| 図 2-17. UART インターフェイスのブロック図                           | 27 |

| 図 2-18. USB 2.0 Type-A インターフェイスのブロック図                 | 28 |

| 図 2-19. USB 2.0 Type-C インターフェイスのブロック図                 | 29 |

|                                          |    |

|------------------------------------------|----|

| 図 2-20. MCAN インターフェイスのブロック図.....         | 30 |

| 図 2-21. ADC インターフェイスのブロック図.....          | 31 |

| 図 2-22. LPDDR4 インターフェイスの ブロック図.....      | 32 |

| 図 2-23. OSPI のブロック図.....                 | 33 |

| 図 2-24. eMMC インターフェイスのブロック図.....         | 35 |

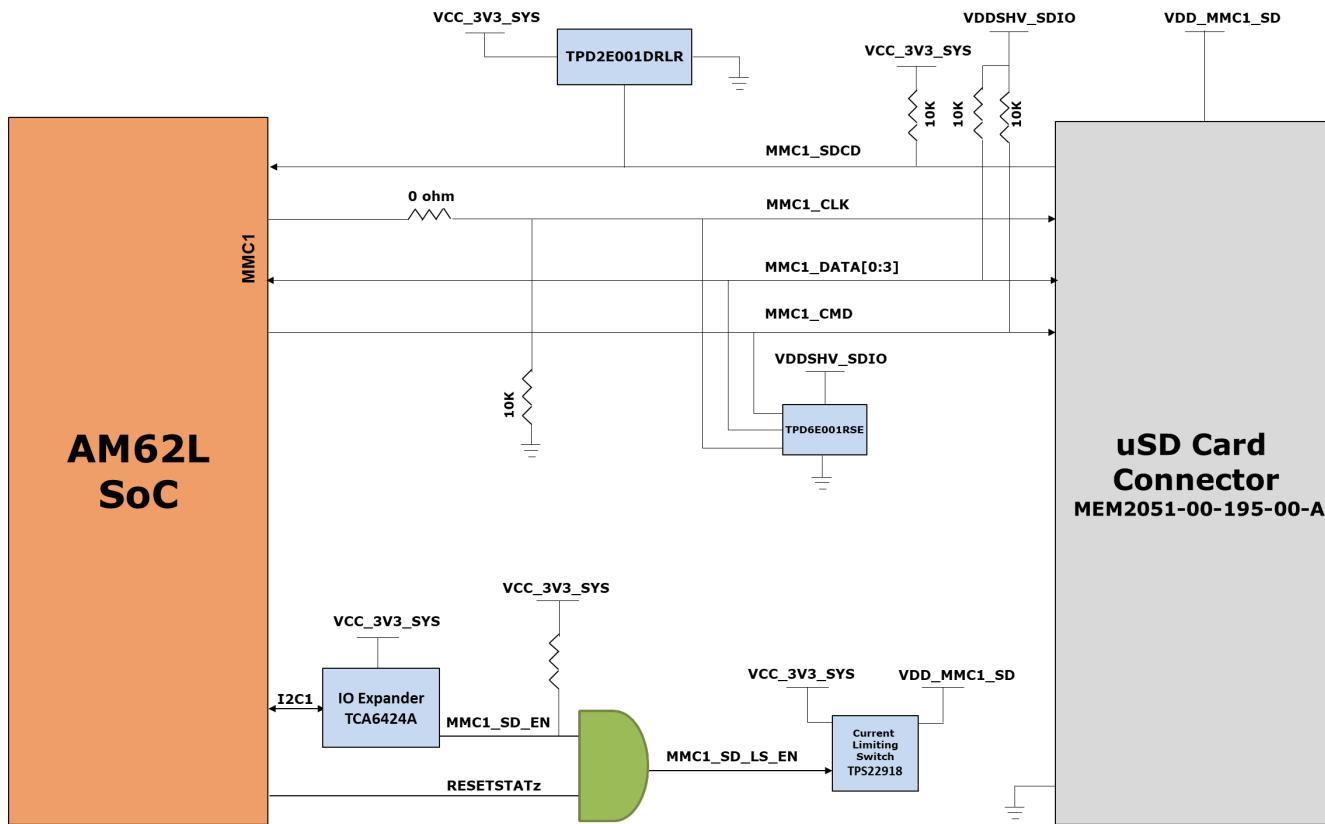

| 図 2-25. microSD インターフェイスのブロック図.....      | 36 |

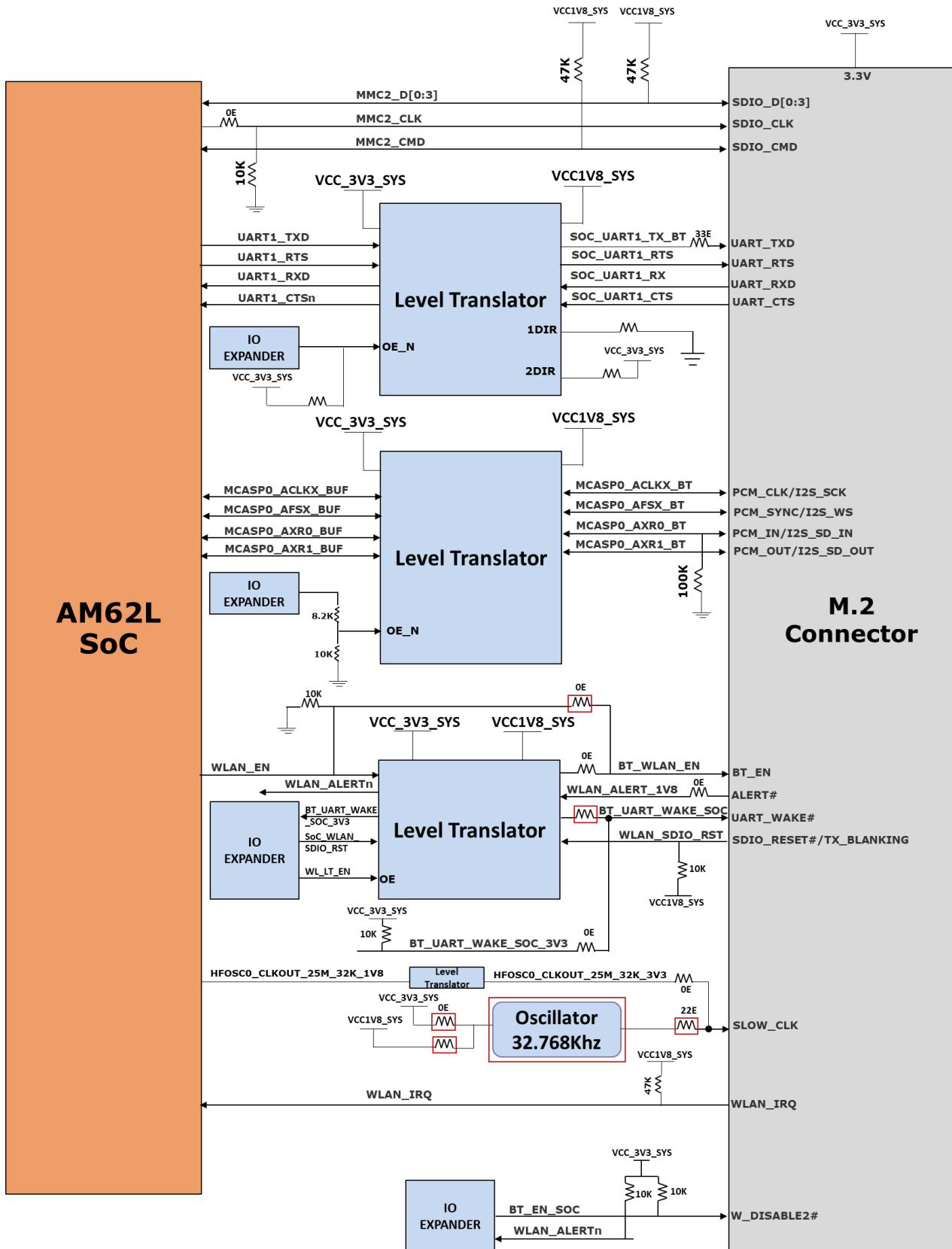

| 図 2-26. M.2 インターフェイスの ブロック図.....         | 37 |

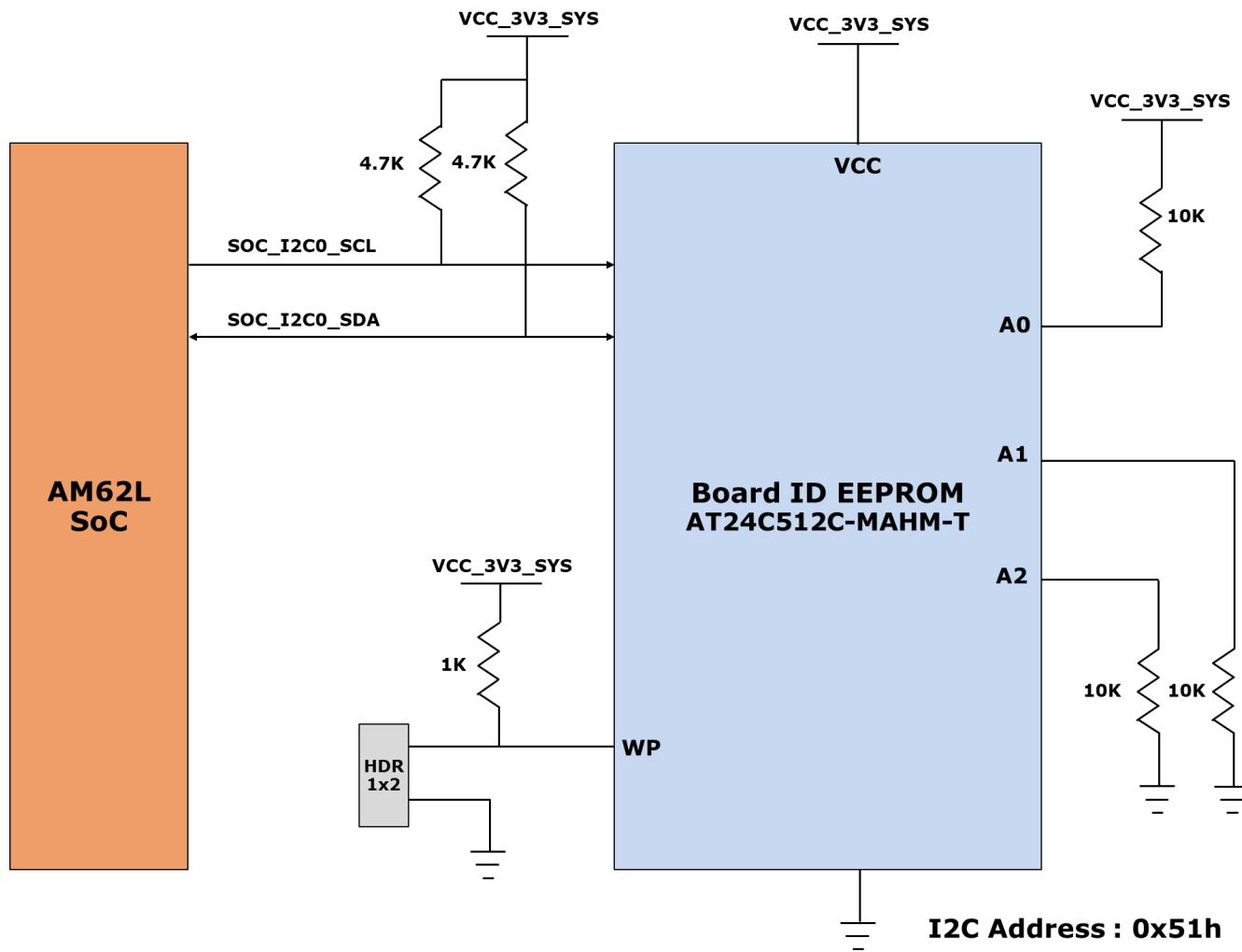

| 図 2-27. 基板 ID EEPROM インターフェイスのブロック図..... | 38 |

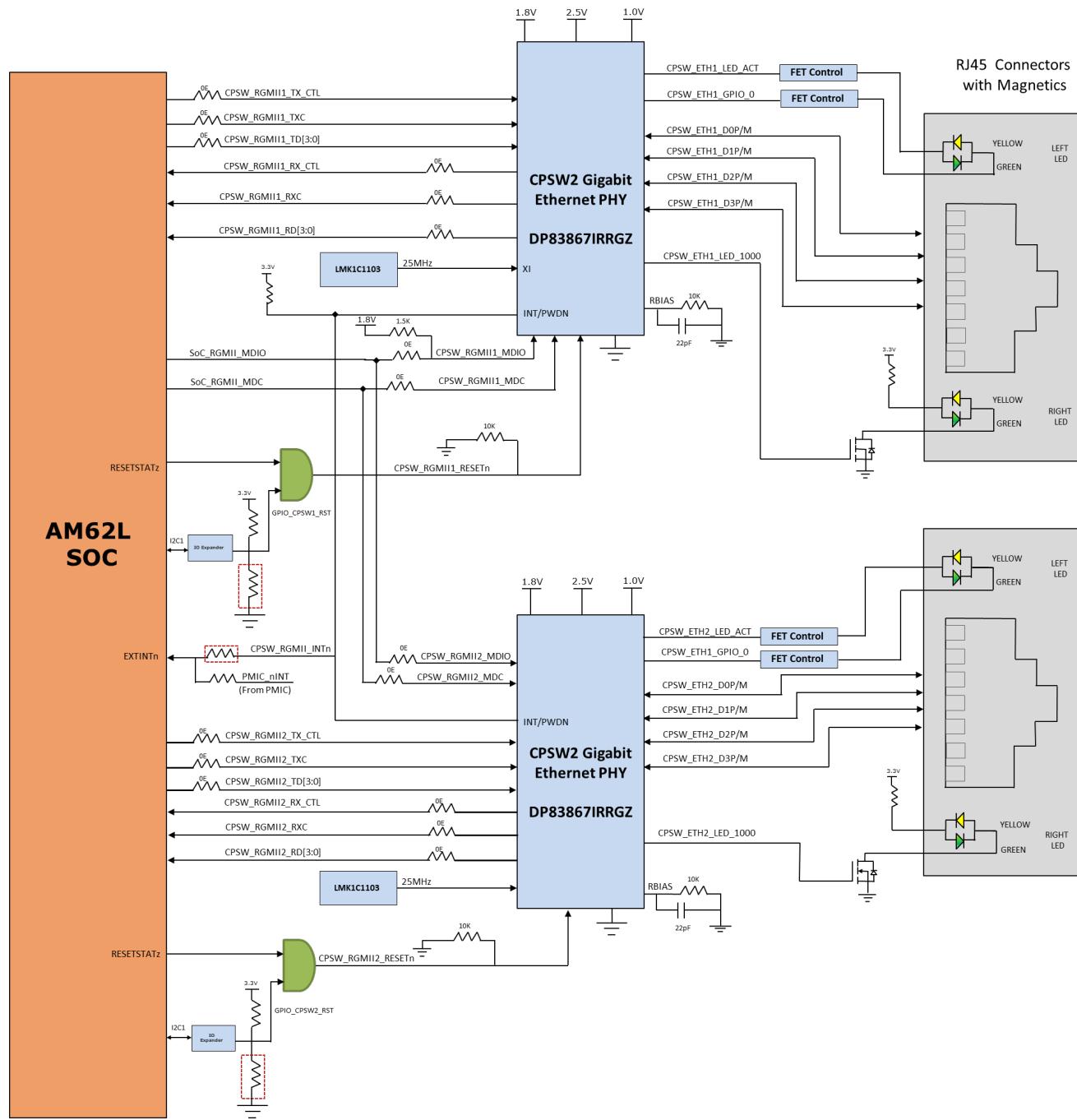

| 図 2-28. イーサネット インターフェイスのブロック図.....       | 39 |

| 図 2-29. 電源入力のブロック図.....                  | 43 |

| 図 2-30. 電力アーキテクチャ.....                   | 44 |

| 図 2-31. 5V および 3.3V 電源の生成を可能にするロジック..... | 45 |

| 図 2-32. 電源シーケンス.....                     | 46 |

| 図 2-33. クロックアーキテクチャ.....                 | 48 |

| 図 2-34. SOC RTC ドメイン クロック.....           | 49 |

| 図 2-35. リセットの ブロック図.....                 | 50 |

| 図 2-36. I2C インターフェイス ツリー.....            | 53 |

## 表の一覧

|                                                                     |    |

|---------------------------------------------------------------------|----|

| 表 1-1. EVM の PCB 設計リビジョンおよびアセンブリ バリエーション.....                       | 6  |

| 表 2-1. Type-C ポートの電源ロール .....                                       | 8  |

| 表 2-2. 推奨外部電源.....                                                  | 9  |

| 表 2-3. フル構成と削減構成のブートモード ピンのマッピング .....                              | 10 |

| 表 2-4. ブートモード ピンのマッピング (ピン数削減構成).....                               | 10 |

| 表 2-5. ブートモード ピンのマッピング (フル ピン数構成).....                              | 11 |

| 表 2-6. PLL リファレンス クロックの選択 BOOTMODE[2:0].....                        | 11 |

| 表 2-7. ブート デバイス選択 BOOTMODE[6:3].....                                | 11 |

| 表 2-8. プライマリ ブート メディアの構成 BOOTMODE[9:7].....                         | 12 |

| 表 2-9. バックアップ ブート モードの選択 BOOTMODE[13:10].....                       | 12 |

| 表 2-10. シリアル NAND 構成フィールド.....                                      | 12 |

| 表 2-11. OSPI ブート構成フィールド.....                                        | 13 |

| 表 2-12. QSPI ブート構成フィールド.....                                        | 13 |

| 表 2-13. SPI ブート構成フィールド.....                                         | 13 |

| 表 2-14. SD カード ブート構成フィールド.....                                      | 13 |

| 表 2-15. eMMC ブート構成フィールド.....                                        | 13 |

| 表 2-16. USB ブート構成フィールド.....                                         | 13 |

| 表 2-17. xSPI ブート構成フィールド.....                                        | 14 |

| 表 2-18. ユーザー テスト LED.....                                           | 16 |

| 表 2-19. 15 ピン RTC 電源選択ヘッダ (J14).....                                | 18 |

| 表 2-20. 電力テスト ポイント.....                                             | 18 |

| 表 2-21. インターフェイス マッピング .....                                        | 19 |

| 表 2-22. DSI ディスプレイ コネクタのピン配置 (J23).....                             | 20 |

| 表 2-23. JTAG コネクタ (J10) のピン配置 .....                                 | 24 |

| 表 2-24. UART ポート インターフェイス.....                                      | 26 |

| 表 2-25. CPSW イーサネット PHY1 のデフォルト構成 .....                             | 40 |

| 表 2-26. CPSW イーサネット PHY2 のデフォルト構成 .....                             | 40 |

| 表 2-27. I/O エクスパンダの信号詳細 .....                                       | 40 |

| 表 2-28. AM62L ローパワー SK EVM ペリフェラルを搭載した AM62D ローパワー SoC のマッピング ..... | 41 |

| 表 2-29. SoC 電源.....                                                 | 46 |

| 表 2-30. INA I2C デバイスアドレス .....                                      | 47 |

| 表 2-31. クロック表.....                                                  | 49 |

| 表 2-32. 10 ピン GPIO 拡張コネクタ (J3).....                                 | 51 |

| 表 2-33. 30 ピン GPIO 拡張コネクタ (J2).....                                 | 51 |

| 表 2-34. EVM のプッシュ ボタン .....                                         | 52 |

| 表 2-35. I2C マッピング表 .....                                            | 54 |

## 1 評価基板の概要

### 1.1 はじめに

本テクニカル ユーザー ガイドでは、テキサス インスツルメンツ (TI™) の AM62L システム オン チップ (SoC) を実装した低コストの評価基板である、AM62L EVM のハードウェア アーキテクチャについて説明します。AM62L プロセッサは、組込み Linux および RTOS オペレーティング システムを実行できるデュアルコア 64 ビット Arm Cortex A53 マイクロプロセッサで構成されています。AM62L は、スケーラブルな性能、高度なセキュリティ、電力効率の優れたコンピューティング能力を低コストで実現します。その結果、開発期間の短縮や、汎用性が高く低消費電力でコスト重視の汎用ソリューションへの導入を進めることができます。

AM62L EVM を使用すると、HDMI (DPI 経由) や MIPI DSI を使用した高解像度ディスプレイ機能と、シリアル、イーサネット、USB、その他のインターフェイスを使用した産業用通信ソリューションを実現できます。AM62L EVM は他のプロセッサまたはシステムと通信でき、通信ゲートウェイとして動作することも可能です。さらに、AM62L EVM は標準リモート I/O システムとして直接動作すること、または産業用通信ネットワークに接続したシンプルなセンサとして動作できます。テキサス インスツルメンツ (TI™) の Code Composer Studio™ IDE などの標準的な開発ツールを使用し、組込み済みエミュレーション ロジックを通じてエミュレーションやデバッグを実施できます。

### 1.2 キットの内容

パッケージには以下が含まれます。

- ・『TMDS62LEVM』EVM (評価基板)

- ・『EVM ユーザー ガイド』冊子

- ・EVM の免責事項と標準約款

### 1.3 仕様

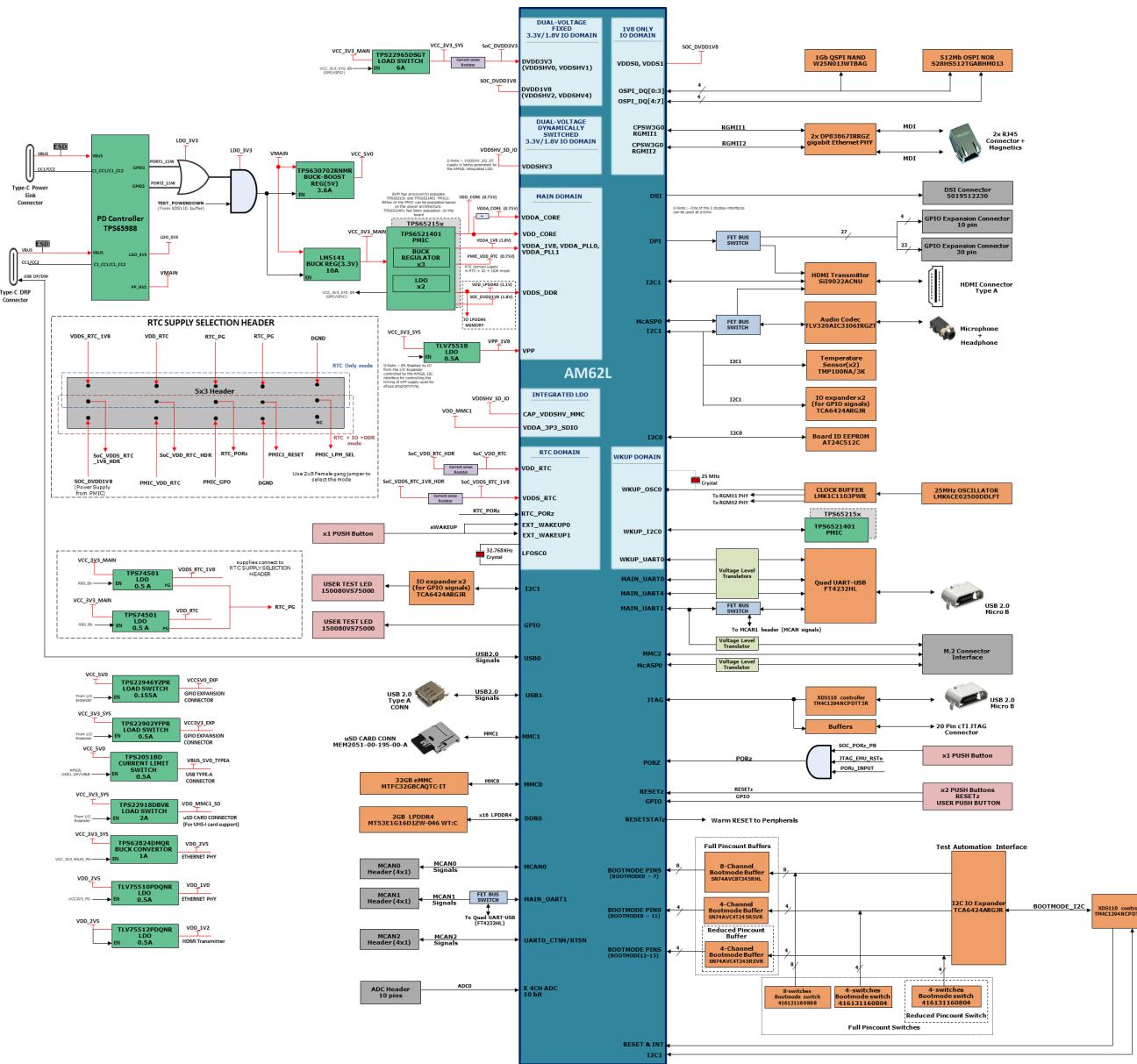

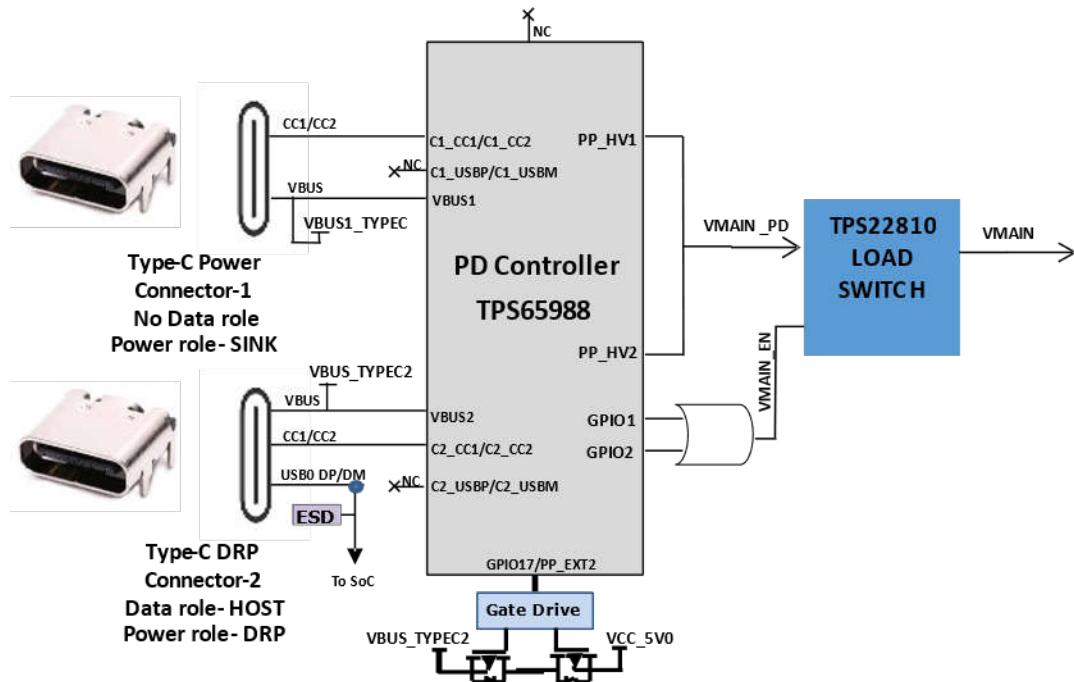

図 1-1 に、AM62L EVM の機能ブロック図を示します。

図 1-1. AM62L EVM の機能ブロック図

## 1.4 製品情報

AM62L EVM は、機能の豊富な SDK (ソフトウェア開発キット) を使用する Linux および FreeRTOS の開発をサポートしています。オンチップ エミュレーション ロジックを搭載しているため、TI™ の Code Composer Studio™ IDE などの標準的な開発ツールを使用したエミュレーションやデバッグが可能です。また、すぐに使用できる直観的なユーザー ガイドにより迅速に設計評価を開始できます。

## 1.5 EVM のリビジョンおよびアセンブリ バリエーション

AM62L EVM のさまざまな PCB 設計リビジョンとアセンブリ バリエーションを、表 1-1 に示します。特定の PCB リビジョンは PCB 上にシルクスクリーンで示され、特定のアセンブリ バリエーションは追加のステッカー ラベルで示されています。

表 1-1. EVM の PCB 設計リビジョンおよびアセンブリ バリエーション

| OPN        | PCB リビジョン    | アセンブリ バリエーション         | リビジョンとアセンブリ バリエーションの説明                                                                    |

|------------|--------------|-----------------------|-------------------------------------------------------------------------------------------|

| TMDS62LEVM | PROC181E1    | 該当なし<br>(単一バリエーションのみ) | AM62L EVM の最初のプロトタイプ、初期リリース リビジョン。TPS65215x (PMIC-1) に実装済み。                               |

| TMDS62LEVM | PROC181E1-1  | 該当なし                  | AM62L EVM の 2 番目のプロトタイプ、初期リリース リビジョン。多数の変更とバグ修正が実施されています。TPS65214x (PMIC-2) に実装済み。        |

| TMDS62LEVM | PROC181E1-1a | 該当なし                  | SoC の型番を更新した量産バージョン (AM62L32BOGHAANB)。PROC181E1-1 と機能的に同等で、SoC リビジョンのみの変更。PCB 設計の変更はありません |

## 2 ハードウェア

### 2.1 補足画像

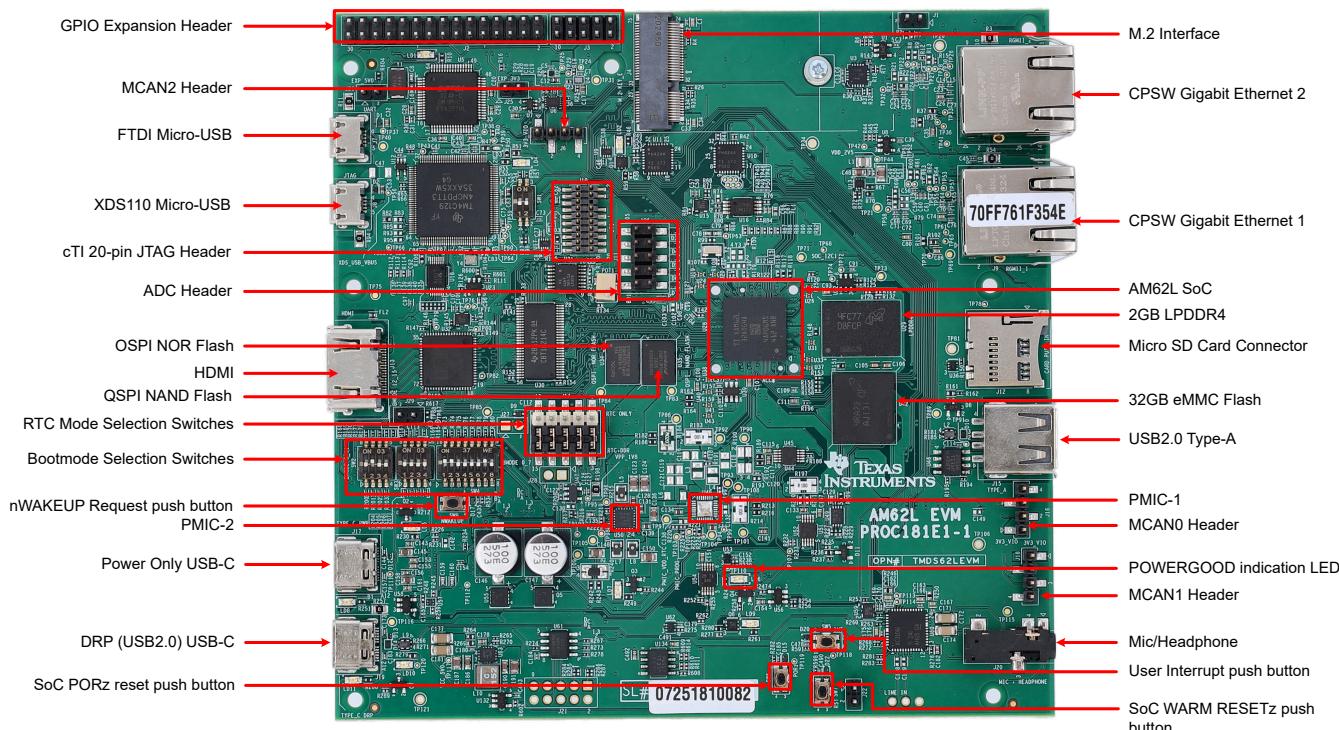

図 2-1 および図 2-2 に、AM62L EVM の上面と底面の画像、および基板上のさまざまなブロックの位置を示します。

図 2-1. AM62L EVM の上面

図 2-2. AM62L EVM の底面

## 2.2 主な特長

AM62L EVM は、高性能のスタンドアロン開発プラットフォームです。これを用いることによって、テキサス インstrument の AM62L システム オン チップ (SoC) 用の産業用アプリケーションの評価と開発を行うことができます。

以下のセクションでは、AM62L EVM の主な特長について説明します。

### 2.2.1 プロセッサ

- AM62L SoC, 11.9mm x 11.9mm, 373 ピン BGA。

### 2.2.2 電源

- USB Type-C ポート (入力範囲 5V ~ 12V) x 2

- PMIC、ディスクリート レギュレータ、LDO を使用してプロセッサおよびペリフェラル用に最適化された電源ソリューション

- RTC 専用モードと RTC+xDDR モードのいずれかを選択できる、RTC 電源選択ヘッダ (5x3 ヘッダ) およびジャンパ (5x2)

### 2.2.3 メモリ

- 最大 1600Mbps のデータ レートをサポートする 2GB (16Gb) LPDDR4 x 1

- UHS-1 対応の microSD® カード スロット

- 512Mbit オクタル SPI NOR フラッシュメモリ x 1

- 1Gbit クワッド SPI NAND フラッシュメモリ x 1

- 512Kbit I2C (Inter-Integrated Circuit) 基板 ID EEPROM

- HS200 モードをサポートする 32GB eMMC フラッシュ

#### 2.2.4 JTAG / エミュレータ

- XDS110 オンボード エミュレータ

- 外付けエミュレータからの 20 ピン JTAG 接続に対応

#### 2.2.5 サポートされるインターフェイスおよびペリフェラル

- USB 2.0 Type-C インターフェイス x 1、DFP および UFP モード (データ) および DRP モード (電源) をサポート

- USB 2.0 ホストインターフェイス x 1、Type-A

- 1x HDMI インターフェイス

- オーディオ ライン入力および MIC + ヘッドフォン出力

- M.2 Key E インターフェイスは、Wi-Fi と Bluetooth の両方のモジュールをサポート

- RJ45 コネクタで 10/100/1000Mbps のデータをサポートするギガビットイーサネットポート x 2

- micro-B USB コネクタ経由のクワッド ポート UART-to-USB 回路

- ユーザー テスト LED

- SoC 電源監視用の INA デバイス x 8

- SoC と LPDDR4 付近に温度監視用温度センサ x 2

#### 2.2.6 アプリケーション固有のアドオン基板をサポートするための拡張コネクタ / ヘッダー

- DSI ディスプレイコネクタ x 1

- GPIO 拡張コネクタ x 2

- MCAN ヘッダー x 3

- ADC ヘッダー x 1

### 2.3 電源要件

AM62L EVM は、2 つの USB Type-C コネクタのいずれかを通じて電力を供給できます。

- コネクタ 1 (J17) - 電源ロール - SINK、データロールなし

- コネクタ 2 (J19) - 電源ロール - DRP、データロール - USB 2.0 DFP または UFP

AM62L EVM は、5V~15V の電圧入力範囲と、3A の電流に対応しています。USB PD コントローラ (メーカー型番 TPS65988DHRSHR) は、ケーブル検出時の PD ネゴシエーションに使用され、基板に必要な電力を取得します。コネクタ 1 は UFP ポートとして構成され、データロールはありません。コネクタ 2 は DRP ポートとして構成されています。コネクタ 2 は、コネクタ 1 によって基板に電力が供給されている場合にのみ DFP として動作できます。両方のコネクタが外部電源に接続されている場合、PD の電力供給能力が最も高いポートが基板の電源として選択されます。

PD コントローラは、外部電源を検出し、ソースが 5V で 15W を上回る電力を供給できるかどうかを検出するように構成されています。外部電源が供給できる電力が 5V で 15W 以下の場合、AM62L EVM は電源オフ状態に移行します。

AM62L EVM は、外部電源が 5V で 15W を上回る電力を供給できる場合に電源投入されます。

表 2-1. Type-C ポートの電源ロール

| J24 (UFP) | J25 (DRP) | 基板電源             | 注記                                                             |

|-----------|-----------|------------------|----------------------------------------------------------------|

| 接続済み      | NC        | ON - J17         | J17 は UFP で、電力のシンクのみを行います。ペリフェラルが接続されている場合に J19 は DRP として動作します |

| NC        | 接続済み      | ON - J19         | J19 は UFP で、電力のシンクのみを行います                                      |

| 接続済み      | 接続済み      | ON - J17 または J19 | 基板は、PD の電力供給能力が最も高いポートから電力を供給されます                              |

PD IC は、パワーアップ時に SPI EEPROM を使用して必要な構成をロードし、それによって PD は互換性のある電源と電力供給能力をネゴシエートできます。

構成ファイルは、ヘッダー J21 を使用して EEPROM にロードされます。EEPROM がプログラミングされると、PD は SPI 通信を介して構成ファイルを取得します。構成ファイルがロードされると、PD は必要な電源要件を満たすために電源とネゴシエートします。

### 注

EEPROM には、PD コントローラの動作に必要な構成ファイルがあらかじめプログラムされています。

EVM 基板に電力を供給しているコネクタを識別するために、両方の Type-C コネクタには電源表示 LED が搭載されています。外部電源 (Type-C 出力) は EVM の電源として使用可能ですが、EVM キットには含まれていません。

外部電源の要件 (Type-C) は次のとおりです。

**表 2-2. 推奨外部電源**

| DigiKey 型番   | メーカー          | メーカー型番               |

|--------------|---------------|----------------------|

| 1939-1794-ND | GlobTek, Inc. | TR9CZ3000USBCG2R6BF2 |

| Q1251-ND     | Qualtek       | QADC-65-20-08CB      |

### 注

最小電圧: 5VDC、推奨最小電流: 3000mA

最大電圧: 12VDC、最大電流: 5000mA

AM62L EVM は電源用に USB PD を実装しているため、デバイスと電源アダプタの両方がサポートする最大電圧 / 電流の組み合わせにネゴシエートできます。そのため、電源アダプタが USB-C PD 仕様に準拠している限り、電源が上記の最大電圧と電流の要件を超えて許容されます。

## 2.4 設定および構成

### 2.4.1 EVM DIP スイッチ

AM62L EVM には、目的の SoC ブートモードを設定するための 8 ポジション DIP スイッチが 1 つ、4 ポジション DIP スイッチが 2 つ、搭載されています。

### 2.4.2 ブートモード

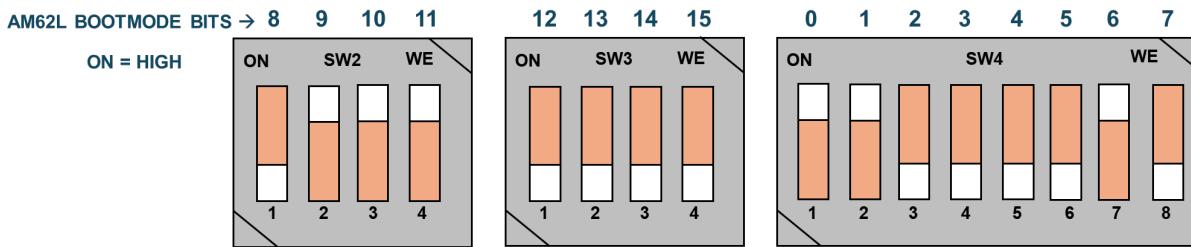

ブートモードピンは、デバイスに電源投入する前にブートモードおよびオプションを選択する手段を提供します。各 POR の後、ブートモードピンがブートパラメータテーブルに入力するためのメインソースになります。評価基板のブートモードは、図 2-3 に示すように、SW2、SW3、SW4 のスイッチからなる 3 つのバンクによって定義されます。あるいは、テストオートメーション (XDS110) に接続された I2C バッファによって定義されます。これにより、AM62L SoC のブートモードは、ユーザー (DIP スイッチ制御) またはテストオートメーション (XDS110) によって制御できます。

スイッチ (SW2、SW3、SW4) のすべてのビットには、弱いプルダウン抵抗と強いプルアップ抵抗があります。オフ設定のときは Low ロジックレベル ('0') が、オン設定のときは High ロジックレベル ('1') が提供されます。

**図 2-3. ブートモード スイッチの例 (フル ピン数構成 - SD カード ブート)**

SoC のブートモードピンは、通常動作時には代替機能が関連付けられています。このため、代替えピン機能に対応するために、バッファ IC を使用して分離が可能です。バッファの出力は AM62L SoC のブートモードピンに接続され、リセットサイクル中にブートモードが必要な場合にのみ出力が有効になります。

バッファへの入力は、DIPスイッチ回路と、テストオートメーション回路によって設定されたI2C I/Oエクスパンダの出力に接続されています。テストオートメーション回路がブートモードを制御する場合は、すべてのスイッチを手動でオフ位置に設定できます。ブートモードバッファは、SoCにパワー サイクルが施されてもブートモードが維持されるように、常時オンの電源から電源供給されます。

SoCのブートモードを設定するには、SW4 (BOOTMODE[7:0])、SW2 (BOOTMODE[11:8])、SW3 (BOOTMODE[15:12])の各スイッチが用いられます。

- BOOTMODE[2:0] - PLL構成用にROMコードへのシステムクロック周波数 (WKUP\_OSC0\_XI/XO) を示します。

- BOOTMODE[6:3] - POR後に要求されるブートモードを選択するためのプライマリブートモードの構成が提供されます。つまり、プライマリブートデバイスからブートするペリフェラル/メモリの選択に関する詳細です。

- BOOTMODE[9:7] - これらのピンはプライマリブートのためのオプション構成を提供し、選択されたブートモードと組み合わせて使用されます。

- BOOTMODE[12:10] - プライマリブートデバイスに障害が発生した場合に、バックアップブートモード、つまりブート元となるペリフェラル/メモリを選択します。

- BOOTMODE[13] - このピンは、バックアップブートデバイス用のオプション構成を提供します。スイッチ SW3.7 をオンにすると1が設定され、オフにすると0が設定されます。各デバイスのTRMを参照してください。

- BOOTMODE[15:14] - フルピン数構成またはピン数削減構成のブートモードマッピングを選択します。

#### 2.4.2.1 ブートモードピンのマッピング オプション

このデバイスは、次の2種類のBOOTMODEピンマッピングオプションをサポートしています。

1. ピン数削減構成 - ブートストラップピンBOOTMODE[15:12]のうち4本のみを使用

2. フルピン数構成 - ブートストラップピンBOOTMODE[15:0]の16本すべてを使用

フルピン数構成のブートモードオプションを選択した場合、BOOTMODE[15:0]のすべてのピンをプルアップまたはプルダウンする必要があります。これらのピンをフローティング状態のままにしてはいけません。ピン数削減構成のオプションを選択した場合、これはBOOTMODE[15:12]ピンにのみ適用されます。

表 2-3. フル構成と削減構成のブートモードピンのマッピング

| BOOTMODE[15]<br>SW3.4 | BOOTMODE[14]<br>SW3.3 | ブートモードのマッピング |

|-----------------------|-----------------------|--------------|

| OFF                   | OFF                   | フルピン数構成      |

| OFF                   | オン                    |              |

| オン                    | OFF                   |              |

| オン                    | オン                    |              |

#### 2.4.2.2 ブートモードピンのマッピング (ピン数削減構成)

削減構成のマップには、必要なブートストラップピンが少なくて済むという利点があり、その結果、必要なプルアップ部品やプルダウン部品を減らすことができます。これには、ピンを選択できるブートモードオプションが少なくなるという代償が伴います。

必要なプルアップ/プルダウン部品の必要な低減を実現するため、BOOTMODE[15:14]が「00」でない限り、BOOTMODE[11:0]ピンの入力バッファはPORの間ディスエーブルになります。ピン数削減構成のオプションを使用すると、これらのピンにフローティング入力があるため、消費電力を低減できます。

表 2-4. ブートモードピンのマッピング (ピン数削減構成)

| BOOTMODE[15]<br>SW3.4 | BOOTMODE[14]<br>SW3.3 | BOOTMODE[13]<br>SW3.2 | BOOTMODE[12]<br>SW3.1 | プライマリ                                            | 予備   | PLL構成 |

|-----------------------|-----------------------|-----------------------|-----------------------|--------------------------------------------------|------|-------|

| OFF                   | OFF                   | X                     | X                     | フルピン数構成オプションを選択します。BOOTMODE[15:0]の入力バッファはイネーブルです |      |       |

| OFF                   | オン                    | OFF                   | OFF                   |                                                  | 予約済み |       |

| OFF                   | オン                    | OFF                   | オン                    |                                                  | 予約済み |       |

| OFF                   | オン                    | オン                    | OFF                   | ブートなし/デバイスブート                                    | なし   | 25MHz |

**表 2-4. ブートモードピンのマッピング (ピン数削減構成) (続き)**

| BOOTMODE[15]<br>SW3.4 | BOOTMODE[14]<br>SW3.3 | BOOTMODE[13]<br>SW3.2 | BOOTMODE[12]<br>SW3.1 | プライマリ        | 予備          | PLL 構成 |

|-----------------------|-----------------------|-----------------------|-----------------------|--------------|-------------|--------|

| OFF                   | オン                    | オン                    | オン                    | USB0         | UART        | 25MHz  |

| オン                    | OFF                   | OFF                   | OFF                   | eMMC         | USB DFU     | 25MHz  |

| オン                    | OFF                   | OFF                   | オン                    | QSPI         | UART        | 25MHz  |

| オン                    | OFF                   | オン                    | OFF                   | MMC / SD カード | UART        | 25MHz  |

| オン                    | OFF                   | オン                    | オン                    | eMMC         | MMC1/SD カード | 25MHz  |

| オン                    | オン                    | OFF                   | OFF                   | OSPI         | UART        | 25MHz  |

| オン                    | オン                    | OFF                   | オン                    | SPI          | UART        | 25MHz  |

| オン                    | オン                    | オン                    | OFF                   | UART         | MMC1/SD カード | 25MHz  |

| オン                    | オン                    | オン                    | オン                    | USB DFU      | MMC1/SD カード | 25MHz  |

#### 2.4.2.3 ブートモードピンのマッピング (フルピン数構成)

これにより、フレキシビリティが向上し、ブート元のペリフェラルが増加します。

ブートモード機能 (フルピン数構成)へのスイッチマッピングを、次の表に示します。

**表 2-5. ブートモードピンのマッピング (フルピン数構成)**

| Bit15 | Bit14 | Bit13          | Bit12        | Bit11         | Bit10       | Bit9 | Bit8 | Bit7 | Bit6    | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|-------|-------|----------------|--------------|---------------|-------------|------|------|------|---------|------|------|------|------|------|------|

| 0     | 0     | バックアップブートモード構成 | バックアップブートモード | プライマリブートモード構成 | プライマリブートモード |      |      |      | PLL の構成 |      |      |      |      |      |      |

表 2-6 に、PLL リファレンスクロック選択の詳細を示します。

**表 2-6. PLL リファレンスクロックの選択 BOOTMODE[2:0]**

| BOOTMODE[2]<br>SW4.3 | BOOTMODE[1]<br>SW4.2 | BOOTMODE[0]<br>SW4.1 | PLL REF CLK (MHz) |

|----------------------|----------------------|----------------------|-------------------|

| OFF                  | OFF                  | OFF                  | 予約済み              |

| OFF                  | OFF                  | オン                   | 予約済み              |

| OFF                  | オン                   | OFF                  | 24                |

| OFF                  | オン                   | オン                   | 25                |

| オン                   | OFF                  | OFF                  | 26                |

| オン                   | OFF                  | オン                   | 予約済み              |

| オン                   | オン                   | OFF                  | 予約済み              |

| オン                   | オン                   | オン                   | 予約済み              |

表 2-7 に、プライマリブートメディアの構成の詳細を示します。

**表 2-7. ブートデバイス選択 BOOTMODE[6:3]**

| BOOTMODE[6]<br>SW4.7 | BOOTMODE[5]<br>SW4.6 | BOOTMODE[4]<br>SW4.5 | BOOTMODE[3]<br>SW4.4 | プライマリブートデバイスの選択                                       |

|----------------------|----------------------|----------------------|----------------------|-------------------------------------------------------|

| OFF                  | OFF                  | OFF                  | OFF                  | シリアル NAND                                             |

| OFF                  | OFF                  | OFF                  | オン                   | OSPI                                                  |

| OFF                  | OFF                  | オン                   | OFF                  | QSPI                                                  |

| OFF                  | OFF                  | オン                   | オン                   | SPI                                                   |

| OFF                  | オン                   | オン                   | オン                   | UART                                                  |

| オン                   | OFF                  | OFF                  | OFF                  | MMCSD ブート<br>(UDA を使用する SD カード<br>ブートまたは<br>eMMC ブート) |

表 2-7. ブートデバイス選択 BOOTMODE[6:3] (続き)

| BOOTMODE[6]<br>SW4.7 | BOOTMODE[5]<br>SW4.6 | BOOTMODE[4]<br>SW4.5 | BOOTMODE[3]<br>SW4.4 | プライマリ ブート デバイスの選択 |

|----------------------|----------------------|----------------------|----------------------|-------------------|

| オン                   | OFF                  | OFF                  | オン                   | eMMC ブート          |

| オン                   | OFF                  | オン                   | OFF                  | USB               |

| オン                   | OFF                  | オン                   | オン                   | GPMC NAND         |

| オン                   | オン                   | OFF                  | オン                   | Fast-xSPI         |

| オン                   | オン                   | オン                   | OFF                  | xSPI              |

| オン                   | オン                   | オン                   | オン                   | ブートなし / デバイスブート   |

表 2-8 に、プライマリ ブート メディアの構成の詳細を示します。

表 2-8. プライマリ ブート メディアの構成 BOOTMODE[9:7]

| BOOTMODE[9]<br>SW2.2 | BOOTMODE[8]<br>SW2.1 | BOOTMODE[7]<br>SW4.8 | ブートデバイス                                                |

|----------------------|----------------------|----------------------|--------------------------------------------------------|

| 予約済み                 | 読み取りモード 2            | 読み取りモード 1            | シリアル NAND                                              |

| 予約済み                 | 予約済み                 | チップ選択                | OSPI                                                   |

| 予約済み                 | 予約済み                 | チップ選択                | QSPI                                                   |

| 予約済み                 | モード                  | チップ選択                | SPI                                                    |

| 予約済み                 | 予約済み                 | 予約済み                 | UART                                                   |

| ポート                  | 予約済み                 | サンプリング周波数 / 生データ     | MMCSD ブート<br>(UDA を使用する SD カード ブート<br>または<br>eMMC ブート) |

| 予約済み                 | 予約済み                 | 予約済み                 | eMMC ブート                                               |

| 予約済み                 | モード                  | レーン スワップ             | USB                                                    |

| 予約済み                 | 予約済み                 | 予約済み                 | GPMC NAND                                              |

| 予約済み                 | 予約済み                 | 予約済み                 | Fast-xSPI                                              |

| SFDP                 | 読み取りコマンド             | モード                  | xSPI                                                   |

| 予約済み                 | 予約済み                 | なし / デバイス            | ブートなし / デバイスブート                                        |

表 2-9 に、バックアップ ブート モードの選択の詳細を示します。

表 2-9. バックアップ ブート モードの選択 BOOTMODE[13:10]

| BOOTMODE[13]<br>SW3.2 | BOOTMODE[12]<br>SW3.1 | BOOTMODE[11]<br>SW2.4 | BOOTMODE[10]<br>SW2.3 | バックアップ ブート デバイスの選択 |

|-----------------------|-----------------------|-----------------------|-----------------------|--------------------|

| 予約済み                  | OFF                   | OFF                   | OFF                   | なし (バックアップ モードなし)  |

| モード                   | OFF                   | OFF                   | オン                    | USB                |

| 予約済み                  | OFF                   | オン                    | OFF                   | 予約済み               |

| 予約済み                  | OFF                   | オン                    | オン                    | UART               |

| ポート                   | オン                    | OFF                   | オン                    | MMC/SD             |

| 予約済み                  | オン                    | オン                    | OFF                   | SPI                |

表 2-10. シリアル NAND 構成フィールド

| ブートモード ピン | フィールド     | 値 | 説明                                                          |

|-----------|-----------|---|-------------------------------------------------------------|

| 8 [SW2.1] | 読み取りモード 2 | 0 | 予約済み (読み取りモードは読み取りモード 1 から取得)                               |

|           |           | 1 | SPI/1-1-1 モード (読み取りモードは、読み取りモード 2 から取得され読み取りモード 1 は無視されます。) |

**表 2-10. シリアル NAND 構成フィールド (続き)**

| ブートモードピン  | フィールド     | 値 | 説明                                      |

|-----------|-----------|---|-----------------------------------------|

| 7 [SW4.8] | 読み取りモード 1 | 0 | OSPI/ 1-1-8 モード (読み取りモード 2 が 0 の場合のみ有効) |

|           |           | 1 | OSPI/ 1-1-4 モード (読み取りモード 2 が 0 の場合のみ有効) |

**表 2-11. OSPI ブート構成フィールド**

| ブートモードピン  | フィールド | 値 | 説明                  |

|-----------|-------|---|---------------------|

| 7 [SW4.8] | チップ選択 | 0 | ブート フラッシュは CS 0 に搭載 |

|           |       | 1 | ブート フラッシュは CS 1 に搭載 |

**表 2-12. QSPI ブート構成フィールド**

| ブートモードピン  | フィールド | 値 | 説明                  |

|-----------|-------|---|---------------------|

| 7 [SW4.8] | チップ選択 | 0 | ブート フラッシュは CS 0 に搭載 |

|           |       | 1 | ブート フラッシュは CS 1 に搭載 |

**表 2-13. SPI ブート構成フィールド**

| ブートモードピン  | フィールド | 値 | 説明                  |

|-----------|-------|---|---------------------|

| 8 [SW2.1] | モード   | 0 | SPI モード 0           |

|           |       | 1 | SPI モード 3           |

| 7 [SW4.8] | チップ選択 | 0 | ブート フラッシュは CS 0 に搭載 |

|           |       | 1 | ブート フラッシュは CS 1 に搭載 |

**表 2-14. SD カード ブート構成フィールド**

| ブートモードピン                               | フィールド  | 値 | 説明                                       |

|----------------------------------------|--------|---|------------------------------------------|

| 9 [SW2.2]<br>13 <sup>(1)</sup> [SW3.2] | ポート    | 0 | 予約済み                                     |

|                                        |        | 1 | MMC ポート 1 (4 ビット幅)。このビットは 1 に設定する必要があります |

| 7 [SW4.8]                              | FS/Raw | 0 | ファイルシステム モード                             |

|                                        |        | 1 | Raw モード                                  |

(1) MMCSD がバックアップ モードの場合

**表 2-15. eMMC ブート構成フィールド**

| ブートモードピン             | フィールド  | 値 | 説明                                         |

|----------------------|--------|---|--------------------------------------------|

| 9 [SW2.2] 13 [SW3.2] | ポート    | 0 | MMCSD ポート 0 (8 ビット幅)。このビットは 0 に設定する必要があります |

|                      |        | 1 | 予約済み                                       |

| 7 [SW4.8]            | FS/Raw | 0 | ファイルシステム モード                               |

|                      |        | 1 | Raw モード                                    |

**表 2-16. USB ブート構成フィールド**

| ブートモードピン                               | フィールド    | 値 | 説明                            |

|----------------------------------------|----------|---|-------------------------------|

| 9 [SW2.2]                              | コア電圧     | 0 | 予約済み                          |

|                                        |          | 1 |                               |

| 8 [SW2.1]<br>13 <sup>(1)</sup> [SW3.2] | モード      | 0 | DFU (USB デバイス フームウェア アップグレード) |

|                                        |          | 1 | ホスト (MSC ブート)                 |

| 7 [SW4.8]                              | レーン スワップ | 0 | D+/D- ラインはスワップされていません         |

|                                        |          | 1 | D+/D- ラインがスワップされています          |

(1) USB がバックアップ モードの場合。

表 2-17. xSPI ブート構成フィールド

| ブートモード ピン | フィールド    | 値 | 説明                   |

|-----------|----------|---|----------------------|

| 9 [SW2.2] | SFDP     | 0 | SFDP はディセーブル         |

|           |          | 1 | SFDP はイネーブル          |

| 8 [SW2.1] | 読み取りコマンド | 0 | 0x0B 読み取りコマンド        |

|           |          | 1 | 0xEE 読み取りコマンド        |

| 7 [SW4.8] | モード      | 0 | 1S-1S-1S モード (50MHz) |

|           |          | 1 | 8D-8D-8D モード (25MHz) |

#### 2.4.2.4 ブートモード DIP スイッチ構成 (フルピン数)

##### 2.4.2.4.1 次側:SD カード、バックアップ:UART\_0xE43

図 2-4. MMCSD/UART バックアップ用のブートモード スイッチの構成

##### 2.4.2.4.2 プライマリ:xSPI SFPD 1、バックアップ:UART\_0xE73

図 2-5. xSPI/UART バックアップ用のブートモード スイッチの構成

##### 2.4.2.4.3 1 次側:NOBOOT、バックアップ:None\_0x00FB

図 2-6. NOBOOT (DEVBOOT = 0) / バックアップなし用のブートモード スイッチの構成

##### 2.4.2.4.4 1 次側:GPMC NAND の元のタイミング、バックアップ:USB\_DFU\_0x04DB

図 2-7. GPMC NAND/USB バックアップ用のブートモード スイッチの構成

#### 2.4.2.4.5 1 次側:GPMC NAND の元のタイミング、バックアップ:UART\_0x0CDB

図 2-8. GPMC NAND/UART バックアップ用のブートモード スイッチの構成

#### 2.4.2.4.6 プライマリ:eMMC、バックアップ:SD\_card\_0x344B

図 2-9. eMMC/MMCSD バックアップ用のブートモード スイッチの構成

#### 2.4.3 ユーザー テスト LED

AM62L EVM 基板には、ユーザー定義による機能用に 2 つの LED が搭載されています。

表 2-18 に、ユーザー テスト LED と、その制御に使用される関連 GPIO を示します。

表 2-18. ユーザー テスト LED

| シリアル番号 | LED | 使用した GPIO   | SCH ネット名        |

|--------|-----|-------------|-----------------|

| 1      | LD8 | GPIO0_123   | SOC_GPIO0_123   |

| 2      | LD2 | U11.24(P27) | IO_EXP_TEST_LED |

#### 2.5 電源オン / オフの手順

評価基板への電力供給は、2 つの USB Type-C® ポートのいずれかによって、PD 機能を備えた外部電源から行われます。

注

テキサス・インスツルメンツでは、I/O ケーブルの最大長が 3m を超えないことを推奨します。

##### 2.5.1 電源オンの手順

1. 評価基板ブートスイッチ セレクタ (SW4, SW3, SW2) を選択したブートモードに設定します。図 2-10 に、SD カードのフル ピン数構成のブートモードの例を示します。

2. ブートメディアを接続します (該当する場合)。

3. PD 対応の USB Type-C ケーブルを、評価基板の Type-C (J17 または J19) コネクタに取り付けます。

4. Type-C ケーブルのもう一方の端を AC 電源アダプタまたは Type-C ソース デバイス (ノートコンピュータなど) に接続します。

5. LD6 LED が点灯していること、および LD8 または LD11 の LED も点灯していることを目視で確認します。

6. XDS110 JTAG と UART のデバッグ コンソール出力は、それぞれ micro-USB ポート J8 と J7 に接続されています。

図 2-10. フル ピン数構成のブートモード (SD カード ブート) の例

### 2.5.2 電源オフの手順

1. AC/DC コンバータから AC 電源を切り離します。

2. EVM から USB Type-C ケーブルを取り外します。

### 2.5.3 RTC 電源選択ヘッダ

RTC 電源選択ヘッダは 5x3 ヘッダであり、図 2-11 に示すように、5x2 のメス ギャング ジャンパを使用して、RTC 専用モードまたは RTC + DDR モードのいずれかを選択するために使用できます。

注

低消費電力モードをサポートするために必要な接続の詳細については、『AM62L の電源実装』アプリケーション ノート (AM62L の電源実装) を参照してください。

## RTC SUPPLY SELECTION

図 2-11. RTC 電源選択ヘッダ

表 2-19 に、RTC 電源選択ヘッダのピン配置の詳細を示します。

**表 2-19. 15 ピン RTC 電源選択ヘッダ (J14)**

| ピン番号 | ネット名                         |

|------|------------------------------|

| 1    | VDDS_RTC_1V8                 |

| 4    | VDD_RTC                      |

| 7    | RTC_PG                       |

| 10   | RTC_PG                       |

| 13   | DGND                         |

| 2    | SoC_VDDS_RTC_1V8_HDR         |

| 5    | SoC_VDD_RTC_HDR              |

| 8    | RTC_PORz                     |

| 11   | PMIC1_RESET<br>(PMIC 1 に対して) |

| 14   | PMIC_LPM_SEL                 |

| 3    | SOC_DVDD1V8                  |

| 6    | PMIC_VDD_RTC                 |

| 9    | PMIC_GPO                     |

| 12   | DGND                         |

| 15   | NC                           |

#### 2.5.4 RTC 専用モード

RTC 専用モードは、デバイスの RTC ドメインのみがアクティブで MAIN ドメインは非アクティブの、低消費電力モードです。

RTC 専用モードでは、SoC の RTC 電源および RTC\_PORz は外部のディスクリート LDO から供給されるとともに、PMIC の電源オフ用の PMIC\_EN を制御するために使用される SoC からの PMIC\_LPM\_EN0 信号出力から供給されます。

RTC 専用モードでは、時刻とカレンダー情報を維持できます。

#### 2.5.5 RTC + DDR モード

RTC+DDR モードでは、MAIN I/O ドメインおよび RTC 電源ドメインの両方がアクティブのままで。SoC からの PMIC\_LPM\_EN0 信号出力は、PMIC のスタンバイモードのイネーブル / ディスエーブルに使用されます。スタンバイモードがイネーブルの場合、PMIC は VDD\_CORE および VDDA\_1V8 からの出力をディスエーブルします。PMIC からの RTC、DDR、I/O 電源はアクティブのままで。スタンバイモードがディスエーブルの場合、すべての PMIC 出力がアクティブになります。

#### 2.5.6 電力テスト ポイント

基板上の各電力出力のテスト ポイントを、表 2-20 に示します。

**表 2-20. 電力テスト ポイント**

| シリアル番号 | 電源           | テスト ポイント | 電圧   |

|--------|--------------|----------|------|

| 1      | VCC5V0_EXP   | TP24     | 5    |

| 2      | VCC3V3_EXP   | TP25     | 3.3  |

| 3      | VDD_1V0      | TP132    | 1    |

| 4      | VDD_1V2      | TP41     | 1.2  |

| 5      | VDDS_RTC_1V8 | TP200    | 1.8  |

| 6      | VDD_RTC      | TP85     | 0.75 |

| 7      | VPP_1V8      | TP95     | 1.8  |

| 8      | VDD_2V5      | TP44     | 2.5  |

| 9      | VDD_CORE     | TP86     | 0.75 |

**表 2-20. 電力テスト ポイント (続き)**

| シリアル番号 | 電源               | テスト ポイント | 電圧   |

|--------|------------------|----------|------|

| 10     | PMIC_VDD_RTC     | TP97     | 0.75 |

| 11     | VCC1V8_SYS       | TP92     | 1.8  |

| 12     | VDDA_1V8         | TP101    | 1.8  |

| 13     | VDD_LPDDR4       | TP90     | 1.1  |

| 14     | VCC_3V3_SYS      | TP202    | 3.3  |

| 15     | VCC_3V3_MAIN     | TP102    | 3.3  |

| 16     | VMAIN            | TP112    | 12   |

| 17     | VCC_5V0          | TP117    | 5    |

| 18     | VCC3V3_XDS       | TP66     | 3.3  |

| 19     | XDS_USB_VBUS     | TP56     | 5    |

| 20     | VCC3V3_TA        | TP201    | 3.3  |

| 21     | VBUS_5V0_TYPEA   | TP91     | 5    |

| 22     | VBUS_TYPEC1      | TP111    | 12   |

| 23     | VBUS_TYPEC2      | TP120    | 12   |

| 24     | FT4232_USB_VBUS  | TP37     | 5    |

| 25     | LDO_3V3          | U61.8    | 3.3  |

| 26     | VCC_3V3_FT4232   | C20.2    | 3.3  |

| 27     | VDD_MMC1_SD      | TP174    | 3.3  |

| 28     | VCC_5V0_HDMICONN | TP161    | 5    |

## 2.6 インターフェイス

以下のセクションでは、AM62L EVM のさまざまなインターフェイスと回路の概要について説明します。表 2-21 に、AM62L EVM のインターフェイス マッピングを示します。

### 2.6.1 AM62L EVM のインターフェイス マッピング

**表 2-21. インターフェイス マッピング**

| インターフェイス名              | SoC 上のポート                     | デバイス部品番号                                     |

|------------------------|-------------------------------|----------------------------------------------|

| メモリ - LPDDR4           | DDR0                          | MT53E1G16D1ZW-046 WT:C                       |

| メモリ - OSPI NOR         | OSPI0                         | S28HS512TGABHM013                            |

| メモリ - QSPI NAND        | OSPI0                         | W25N01JWBTAG                                 |

| メモリ - Micro SD ソケット    | MMC1                          | MEM2051-00-195-00-A                          |

| メモリ - eMMC             | MMC0                          | MTFC32GBCAQTC-IT                             |

| メモリ - 基板 ID EEPROM     | SoC_I2C0                      | AT24C512C-MAHM-T                             |

| イーサネット 1 - RGMII       | SoC_RGMII1                    | DP83867IRRGZ                                 |

| イーサネット 2 - RGMII       | SoC_RGMII2                    | DP83867IRRGZ                                 |

| GPIO ポート エクスパンダ 1      | SoC_I2C1                      | TCA6424ARGJR                                 |

| GPIO 拡張コネクタ - 2x5 HDR  | UART2, VCC3V3, VCC5V0, GPIO   | 67997-410HLF                                 |

| GPIO 拡張コネクタ - 2x15 HDR | SPI1, SPI3, UART4, I2C3, GPIO | PREC015DAAN-RC                               |

| USB -2.0 Type C        | USB0                          | 2012670005                                   |

| USB -2.0 Type A        | USB1                          | 629104151021                                 |

| DSI インターフェイス           | DSI0-TX                       | 5019512230                                   |

| 3 個の MCAN インターフェイス     | MCAN0, MCAN1 および MCAN2        | TSM-104-02-L-SV                              |

| HDMI                   | VOUT0, McASP0and, SoC_I2C1    | Sil9022ACNU + TPD12S016PWR + DC04S019JA1R600 |

| オーディオ コーデック            | McASP0 および SoC_I2C1           | TLV320AIC3106IRGZT+ SJ-43514-SM              |

表 2-21. インターフェイス マッピング (続き)

| インターフェイス名             | SoC 上のポート                                      | デバイス部品番号                |

|-----------------------|------------------------------------------------|-------------------------|

| GPIO ポート エクスパンダ 2     | SoC_I2C1                                       | TCA6424ARGJR            |

| UART 端子 (UART-to-USB) | SoC_UAR SoC_UART[1:0]、WKUP_UART0、<br>SoC_UART4 | FT4232HL + 629105150521 |

| 温度センサ                 | SoC_I2C1                                       | TMP100NA/3K             |

| 電流モニタ                 | SoC_I2C1                                       | INA228AIDGSR            |

| コネクティビティ - M.2 Key E  | MMC2、McASP0、SoC_UART1                          | 2199119-4               |

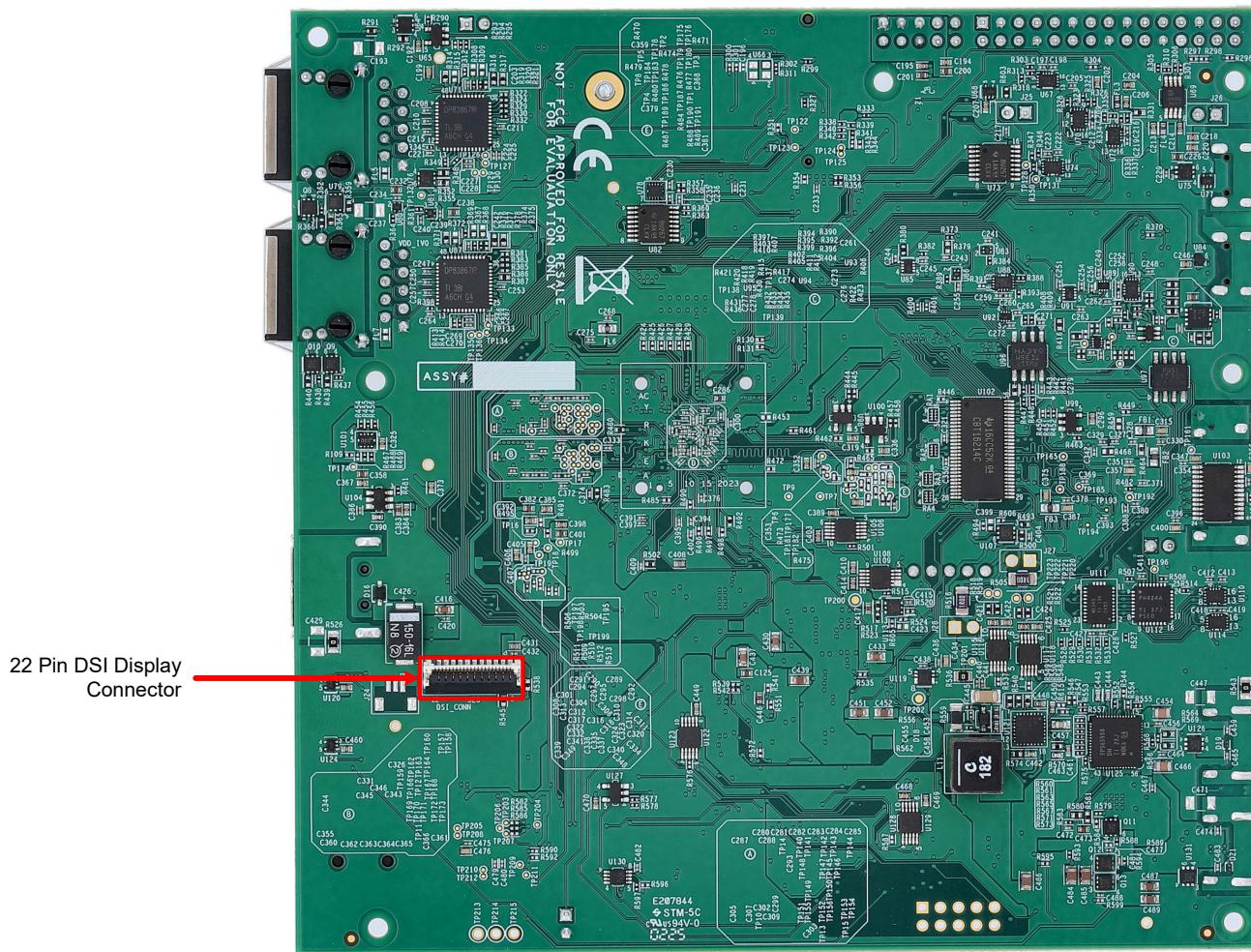

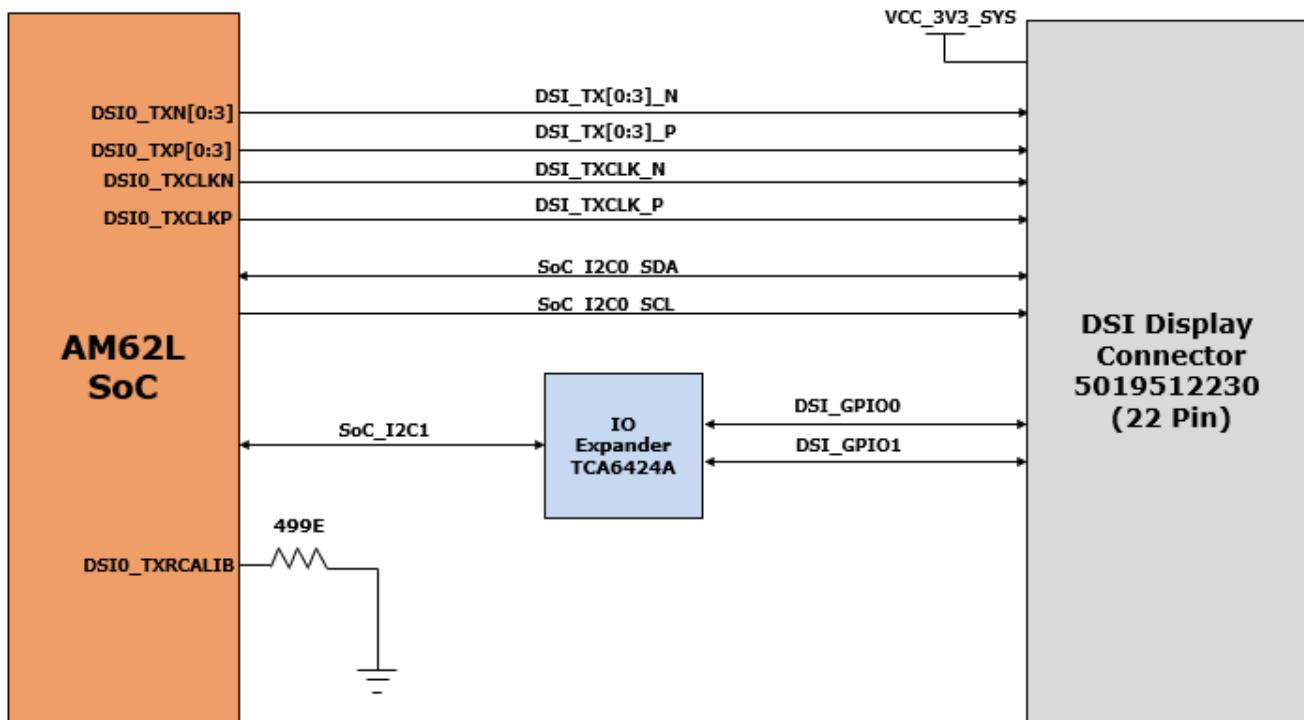

## 2.6.2 DSI インターフェイス

AM62L SoC の DSI ディスプレイインターフェイスは、Molex の 22 ピン ディスプレイコネクタ (J23) (メーカー型番 5019512230) に接続されています。AM62L EVM は、最大 1920x1080p (60fps) の解像度の高速ビデオリンクおよび低消費電力コマンドリンク向けに 4 つの DSI-TX レーンをサポートしています。これら 4 つのレーンを除き、22 ピンコネクタには 3.3V 電源が供給され、500mA までのソース機能、すべての事前初期化用の I2C0、インターフェイスディスプレイへの割り込みおよびリセットを処理するための 2 つの GPIO があります。

図 2-12. DSI インターフェイスのブロック図

表 2-22 に、ディスプレイコネクタのピン配置の詳細を示します。

表 2-22. DSI ディスプレイ コネクタのピン配置 (J23)

| ピン番号 | 信号           |

|------|--------------|

| 1    | VCC_3V3_SYS  |

| 2    | SOC_I2C0_SDA |

| 3    | SOC_I2C0_SCL |

| 4    | DGND         |

| 5    | DSI_GPIO1    |

| 6    | DSI_GPIO0    |

**表 2-22. DSI ディスプレイ コネクタのピン配置 (J23) (続

き)**

| ピン番号 | 信号          |

|------|-------------|

| 7    | DGND        |

| 8    | DSI_TX3_P   |

| 9    | DSI_TX3_N   |

| 10   | DGND        |

| 11   | DSI_TX2_P   |

| 12   | DSI_TX2_N   |

| 13   | DGND        |

| 14   | DSI_TXCLK_P |

| 15   | DSI_TXCLK_N |

| 16   | DGND        |

| 17   | DSI_TX1_P   |

| 18   | DSI_TX1_N   |

| 19   | DGND        |

| 20   | DSI_TX0_P   |

| 21   | DSI_TX0_N   |

| 22   | DGND        |

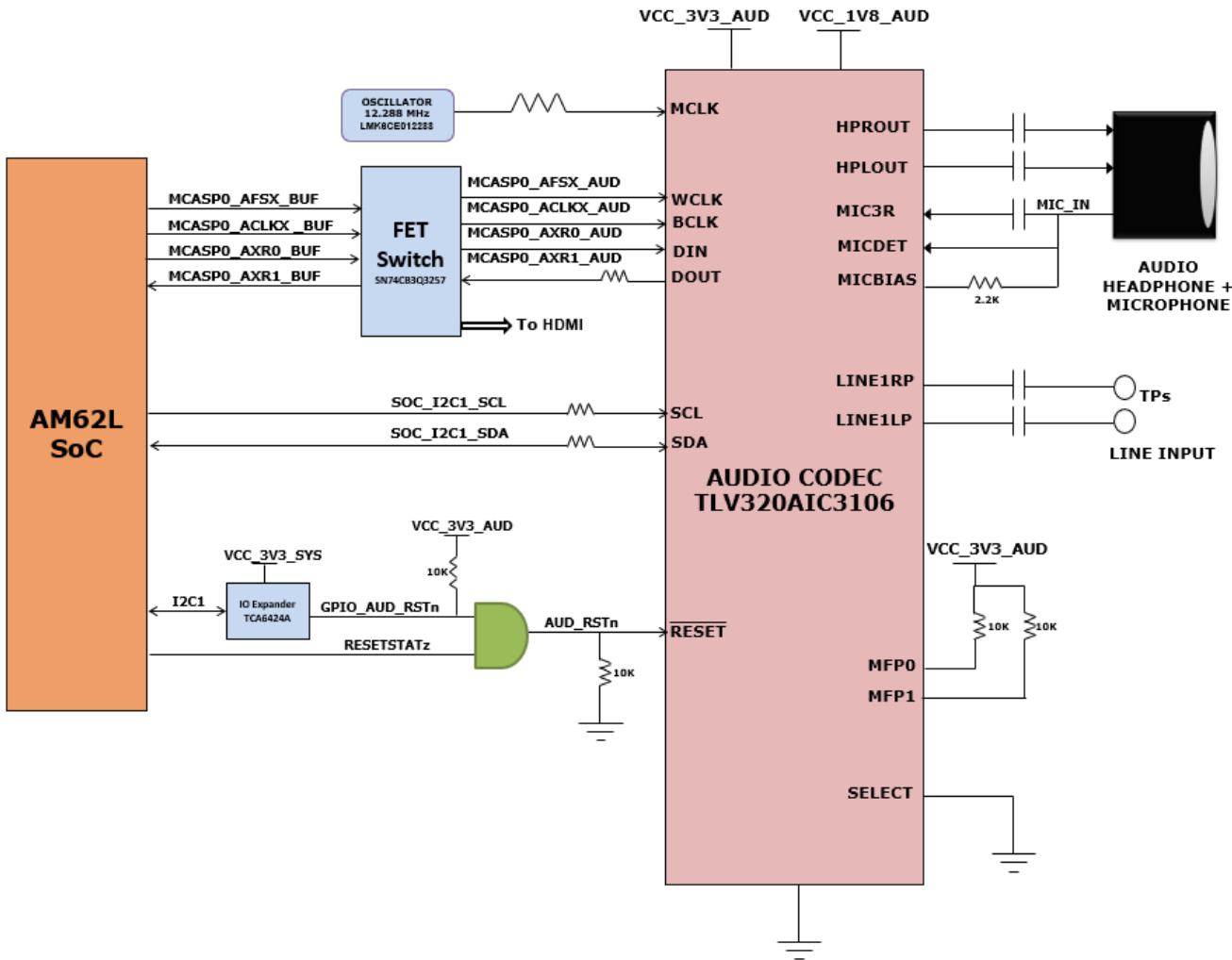

### 2.6.3 オーディオコーデック インターフェイス

AM62L EVM には、McASP0 の信号グループ経由で AM62L とインターフェイスできるように、TI の TLV320AIC3106 ステレオ オーディオ コーデックが搭載されています。

TLV320AIC3106 は、ステレオ ヘッドフォン アンプを内蔵した低消費電力ステレオ オーディオ コーデックであり、シングルエンドまたは完全差動構成でプログラマブルな複数の入力と出力を備えています。TLV320AIC3106 の録音パスには、内蔵マイクロフォン バイアス、デジタル制御のステレオ マイクプリアンプ、自動ゲイン制御 (AGC) が含まれており、複数のアナログ入力の間に MIX および MUX 機能があります。ステレオ オーディオ DAC は、8kHz ~ 96kHz のサンプリング レートをサポートします。

MIC IN とヘッドフォン出力用に、標準的な 3.5mm TRRS オーディオ ジャック コネクタ (J20) (メーカー型番 SJ-43514) が 1 個付属しています。オーディオ コーデックのライン入力は、テストポイントに終端しています。コーデックは I2C1 を介して構成し、デバイスアドレスを 0x1B に設定できます。

オーディオ コーデックへのコントローラ クロック入力である MCLK は、12.288MHz の発振器から供給されます。オーディオシリアル データ バス ビット クロック (BCLK) とオーディオシリアル データ バス入出力 (DIN および DOUT) は、マルチプレクサ / デマルチプレクサを経由して SOC の MCASP0 インスタンスに接続されます。RESETSTATz の AND 出力と、I/O エクスパンダ経由で供給される GPIO は、オーディオ コーデックをリセットするために使用されます。

TLV320AIC3106 は、3.3V のアナログ電源、1.8V のデジタルコア電源、3.3V のデジタル I/O 電源で動作します。

図 2-13. オーディオ コーデック インターフェイスのブロック図

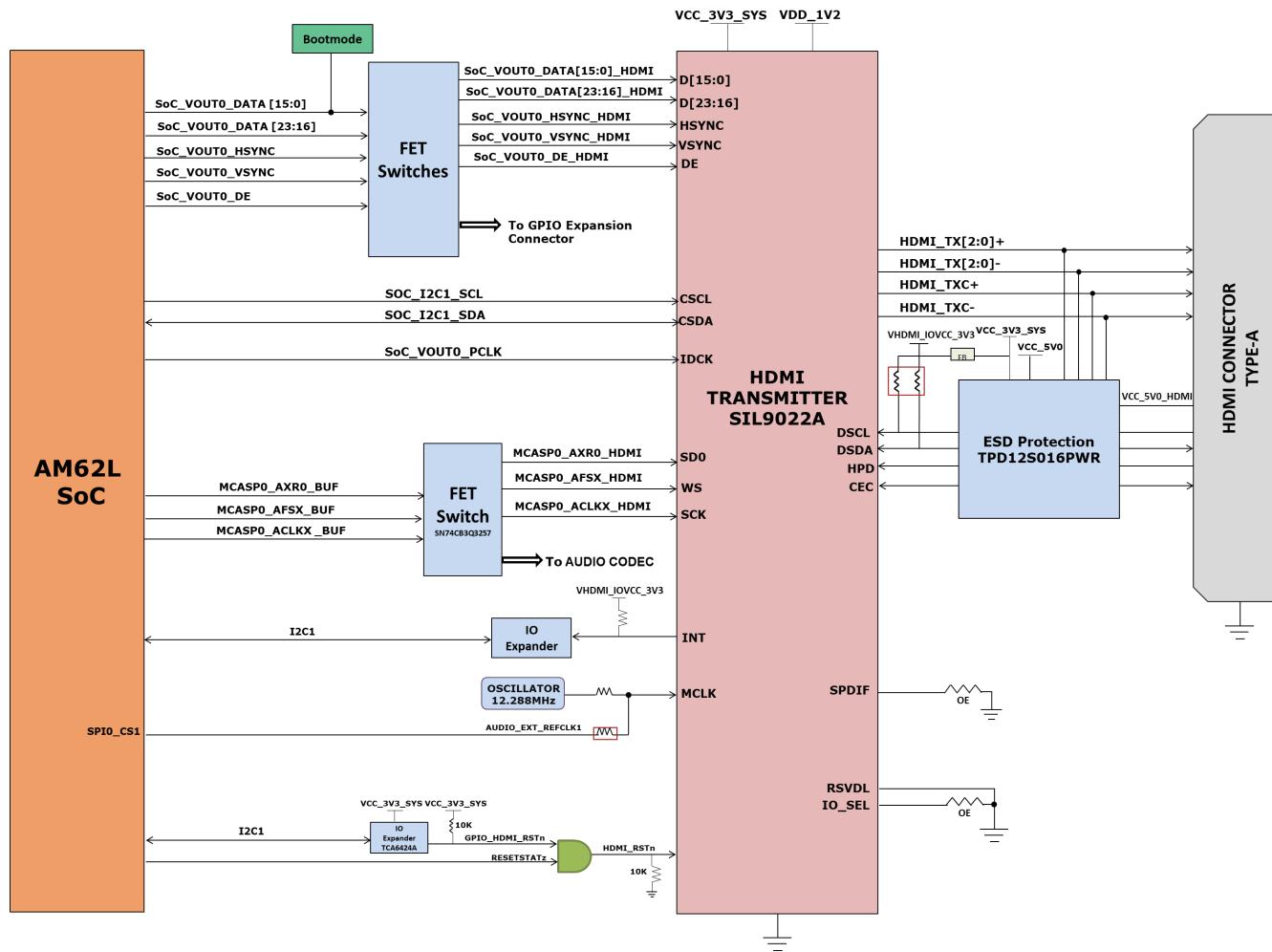

#### 2.6.4 HDMI ディスプレイ インターフェイス

AM62L SoC の DSS (ディスプレイ サブ システム) は、評価基板上で使用され、標準的な Type-A コネクタ経由で HDMI インターフェイスを実現します。この評価基板は、Lattice Semiconductor の Si9022A HDMI トランスマッタを搭載しており、24 ビットのパラレル RGB DSS 出力ストリームおよび McASP0 信号を HDMI 準拠のデジタル オーディオ / ビデオ信号に変換します。

Si9022A を使用するには、SoC がデバイスをセット アップする必要があります。これは、SoC と Si9022A の間の I2C1 インターフェイスを介して行われます。HDMI トランスマッタに接続された SoC\_I2C1 インスタンスは、互換モードレジスタ、TPI レジスタ、CPI レジスタにアクセスします。オーディオ データは、McASP0 インスタンスを介して SoC から HDMI トランスマッタに送信されます。HDMI\_I2C バスは、接続されたシンク デバイスの EDID と HDCP データにアクセスします。

TMDS 差動データ ペアとトランスマッタからの差動クロック信号は、HDMI ESD デバイス (メーカー型番 TPD12S016PWR) 経由で HDMI コネクタに接続されています。このデータは、オンボードの 5V 電源から HDMI コネクタに供給される電流を制限するロード スイッチとしても機能します。

HDMI フレーマには、3.3V 基板 I/O 電源から給電されます。また、専用 LDO (メーカー型番 TLV75512PDQNR) から、AVCC および DVCC 電源用の 1.2V が給電されます。

FET スイッチは、HDMI トランシミッタまたは GPIO 拡張ヘッダへの DSS ビデオ信号を選択するのに使用されます。デフォルトでは、DSS ビデオ信号は HDMI トランシミッタに接続され、J29 1x2 ヘッダを短絡することによって、ソフトウェアに依存せずに GPIO 拡張ヘッダに選択を変更できます。

図 2-14. HDMI インターフェイスのブロック図

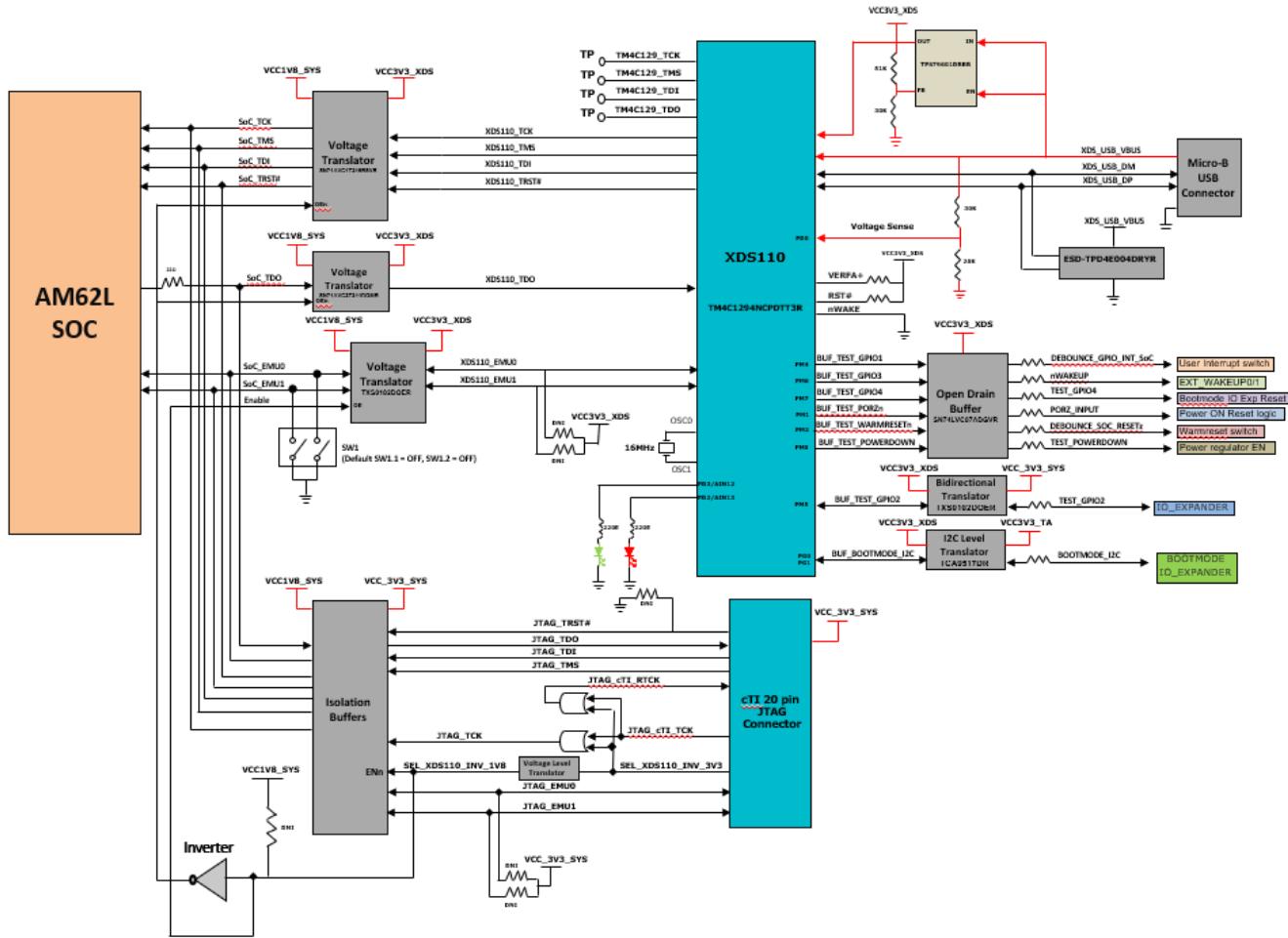

### 2.6.5 JTAG インターフェイス

AM62L EVM には、XDS110 クラスのオンボード エミュレーション機能が搭載されています。このエミュレータの接続には標準的な USB 2.0 micro-B コネクタが使用され、回路はバス電源供給方式の USB デバイスとして機能します。コネクタからの VBUS 電源はエミュレーション回路に電源として使用されているため、EVM 電源が切り離されてもエミュレータへの接続が失われることはありません。電圧変換バッファは、XDS110 回路を EVM の他の部分から分離するために使用されます。

オプションとして、評価基板の JTAG インターフェイスは、20 ピンの標準 JTAG cTI ヘッダ J10 を通じても提供されます。これにより、外部 JTAG エミュレータケーブルを接続できます。電圧変換バッファは、cTI ヘッダの JTAG 信号を評価基板の他の部分から分離するために使用されます。XDS110 セクションと cTI ヘッダー セクションの電圧トランスレータの出力はマルチプレクサによって切り替えられ、AM62L の JTAG インターフェイスに接続されています。自動存在検出回路を使用して cTI 20 ピン JTAG コネクタへの接続が検出されると、マルチプレクサはオンボードのエミュレーション回路の代わりに cTI コネクタからの 20 ピン信号を AM62L SoC にルーティングします。

図 2-15. JTAG インターフェイスのブロック図

表 2-23 に、cTI 20 ピン JTAG コネクタのピン配列を示します。USB 信号には、ESD 電流パルスを VCC または GND に誘導する ESD 保護デバイス (型番 TPD4E004) が用いられています。TPD4E004 は、IEC 61000-4-2 で規定されている最大  $\pm 15\text{kV}$  の人体モデル (HBM) の ESD パルスから保護し、 $\pm 8\text{kV}$  の接触放電と  $\pm 12\text{kV}$  のエアギャップ放電を提供します。

表 2-23. JTAG コネクタ (J10) のピン配置

| ピン番号 | 信号                 |

|------|--------------------|

| 1    | JTAG_TMS           |

| 2    | JTAG_TRST#         |

| 3    | JTAG_TDI           |

| 4    | JTAG_TDIS          |

| 5    | VCC_3V3_SYS        |

| 6    | NC                 |

| 7    | JTAG_TDO           |

| 8    | SEL_XDS110_INV_3V3 |

| 9    | JTAG_cTI_RTCK      |

| 10   | DGND               |

| 11   | JTAG_cTI_TCK       |

| 12   | DGND               |

| 13   | JTAG_EMU0          |

| 14   | JTAG_EMU1          |

表 2-23. JTAG コネクタ (J10) のピン配置 (続き)

| ピン番号 | 信号            |

|------|---------------|

| 15   | JTAG_EMU_RSTn |

| 16   | DGND          |

| 17   | NC            |

| 18   | NC            |

| 19   | NC            |

| 20   | DGND          |

## 2.6.6 XDS110 テストオートメーション

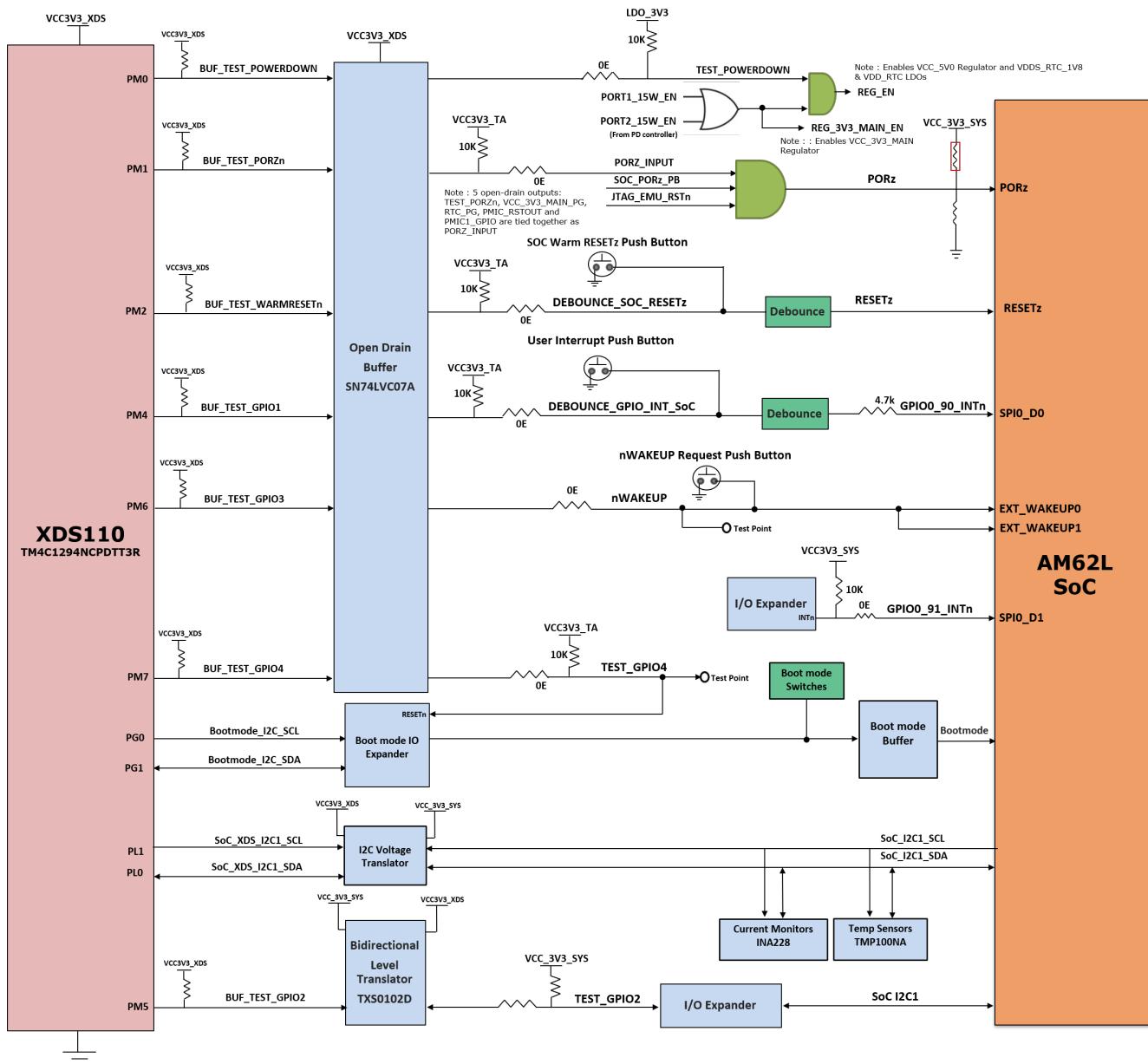

AM62L EVM は、テストオートメーションと呼ばれるオプション機能を備えており、パワーダウン、POR、ウォームリセット、ブートモード制御などいくつかの基本的な動作を外部コントローラから XDS110 経由で操作できます。

図 2-16. テストオートメーション インターフェイスのブロック図

XDS110 テストオートメーションには電圧変換回路があり、コントローラは AM62L で使用される I/O 電圧から絶縁されています。AM62L のブートモードは、DIP スイッチまたは I2C I/O エクスパンダによる XDS テストオートメーションを使用して、ユーザーが制御できます。ブートモードバッファは、DIP スイッチまたは I2C I/O エクスパンダによって駆動されるブートモード制御を分離するために使用されます。ブートモードは、ボード上の 1 つの 8 ビット DIP スイッチと 2 つの 4 ビット DIP スイッチを使用して設定することもでき、スイッチが ON 位置に設定されている場合はプルアップ抵抗をバッファの出力に、OFF 位置に設定されている場合は弱いプルダウン抵抗に接続します。バッファの出力は AM62L SoC のブートモードピンに接続され、リセットサイクル中にブートモードが必要な場合にのみ出力が有効になります。

XDS110 テストオートメーションによってブートモードを設定する場合、必要なスイッチ値が I2C I/O エクスパンダ出力に設定されます。これにより、DIP スイッチ値が上書きされ、SoC に目的のブート値が得られます。ブートモード用に使用されるピンにはそれ以外の機能もあるため、これらは、通常動作時にブートモードバッファをディスエーブルにすることによって自動的に分離されます。

XDS110 からのパワーダウン信号は、ボード上の専用電源を除くすべてのレールをパワーダウンするように評価基板に指示します。同様に、PORZn 信号は SoC にハードリセットを行い、WARMRESETn は SoC にウォームリセットを行います。

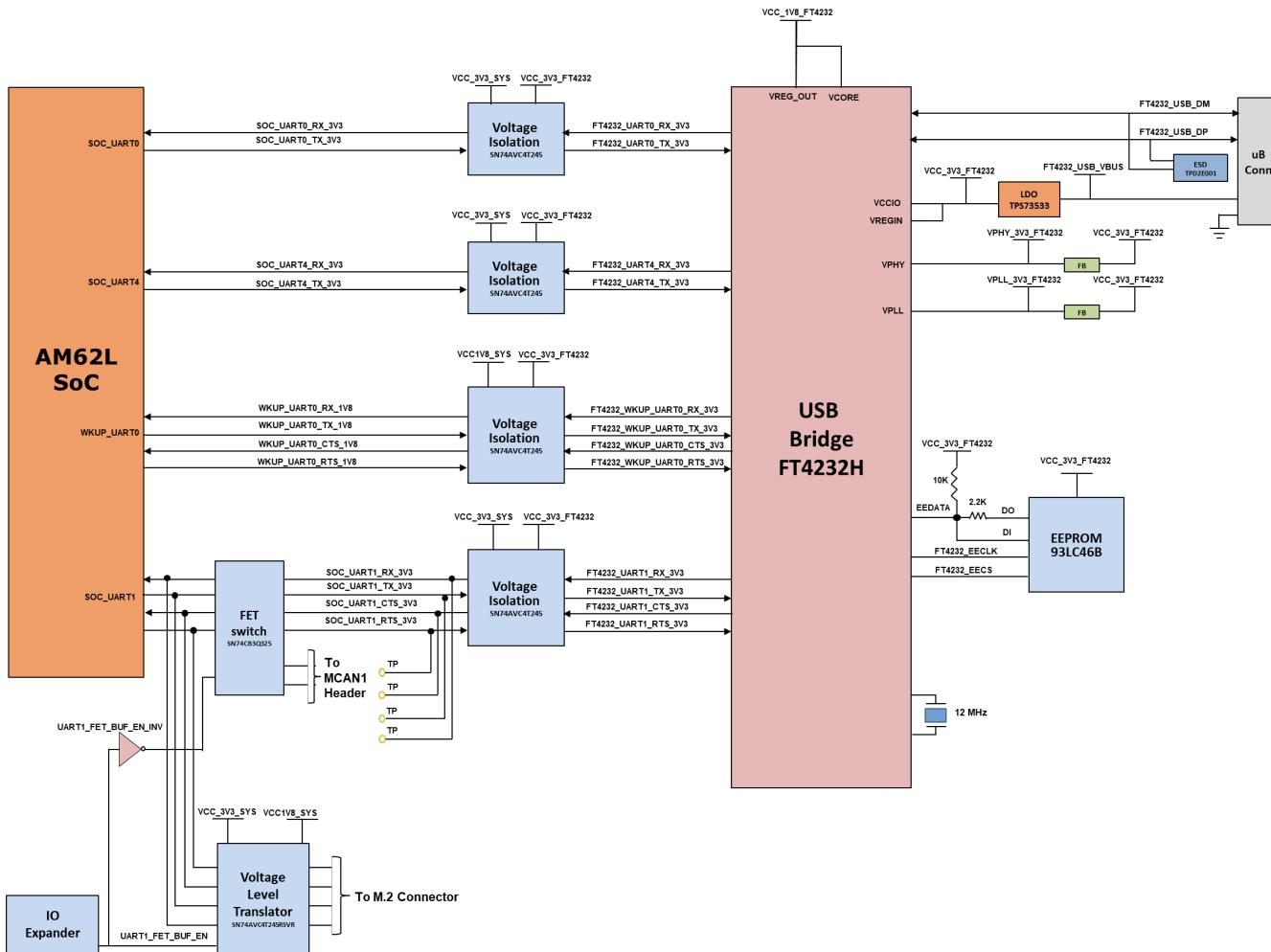

### 2.6.7 UART インターフェイス

SoC の 4 つの UART ポート (WKUP UART0, SoC UART0, SoC UART1, SoC UART4) は、USB-to-UART 機能を実現するためにFTDI ブリッジ FT4232HL とインターフェイスされ、基板上の micro-B USB コネクタ (J7) で終端されています。USB ケーブルを使用して AM62L EVM をホストに接続すると、コンピュータは仮想 COM ポートを確立でき、任意の端末エミュレーション アプリケーションで使用できます。FT4232HL デバイスはバスから電源供給されているため、評価基板の電源が切り離されても COM ポートへの接続が失われることはありません。

表 2-24. UART ポートインターフェイス

| UART ポート   | USB-to-UART ブリッジ | USB コネクタ | COM ポート |

|------------|------------------|----------|---------|

| SoC_UART0  |                  |          | COM1    |

| SoC_UART1  |                  |          | COM2    |

| WKUP_UART0 | FT4232HL         | J7       | COM3    |

| SoC_UART4  |                  |          | COM4    |

FT4232 チップは、接続された外部 SPI EEPROM からの構成ファイルを使用して、「シングルチップ USB から 4 チャネル UART」モードで動作するよう構成されています。EEPROM (93LC46B) は、1Mbit/s のクロック レートに対応しています。EEPROM は、FTDI の Web サイトから入手できる FT\_PROG というユーティリティプログラムを使用して、USB 経由で回路内でプログラム可能です。FT\_PROG は、1 つまたは複数の基板がコンピュータに接続されているときに、ユーザーが基板のシリアル番号を使用して接続されている COM ポートを識別できるように、基板のシリアル番号をプログラムするためにも使用されます。

図 2-17. UART インターフェイスのブロック図

## 2.6.8 USB インターフェイス

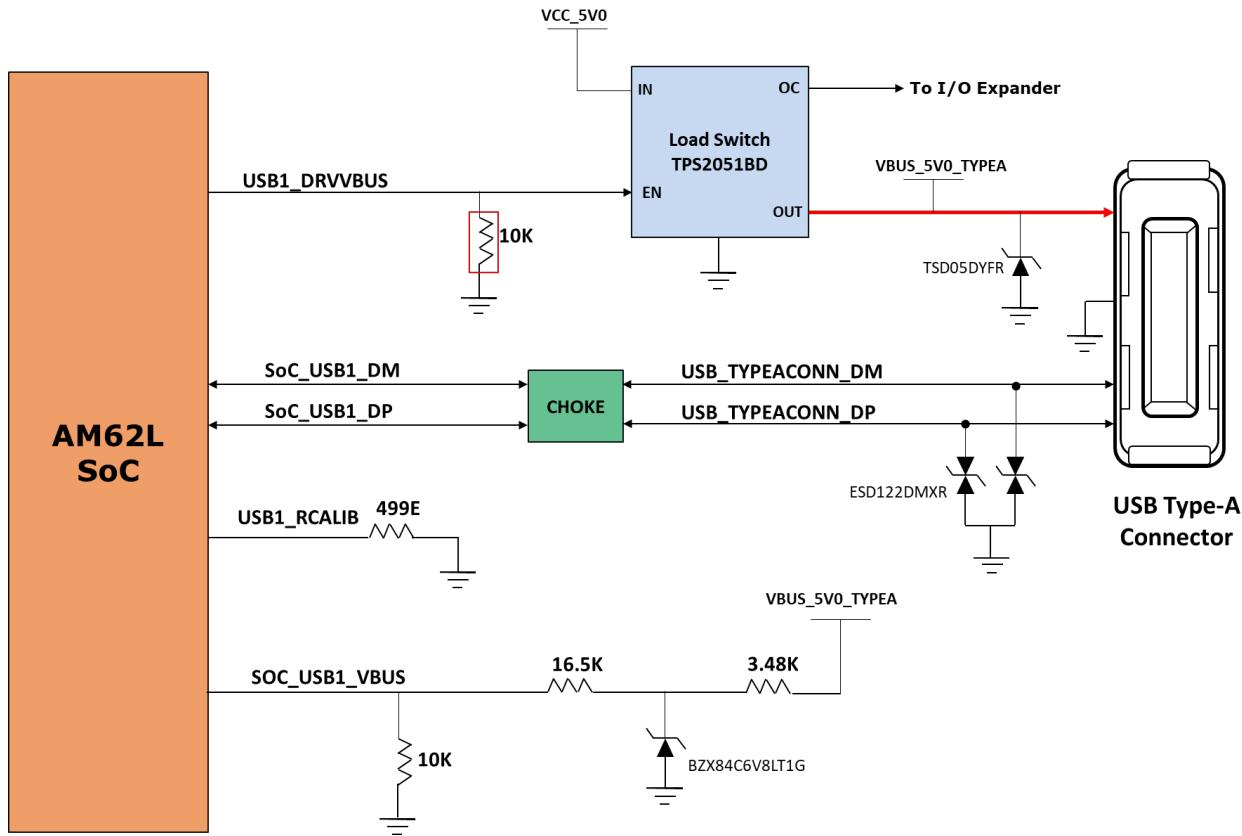

### 2.6.8.1 USB 2.0 Type A インターフェイス

Type-A コネクタ J23 からの USB 2.0 データラインの DP および DM は、AM62L SoC の USB1 インターフェイスに接続されており、USB のハイスピード / フルスピード通信を実現しています。SoC への USB1\_VBUS は、(5V~30V) の VBUS 動作に対応する抵抗分圧回路を介して供給されます。SoC の USB1\_DRVVBUS は、500mA の電流制限付きロードスイッチ (メーカー型番 TPS2051BD) のイネーブルピンを制御し、オンボードの 5V 電源で VBUS に電力を供給できるようになっています。このロードスイッチには過電流表示ピンがあり、EVM 上の I2C ベースの GPIO エクスパンダに接続されています。

EMI/EMC 低減のために、USB データラインにコモン モード チョーク (メーカー型番 DLW21SZ900HQ2B) が配置されているほか、ESD ダイオード保護 (メーカー型番 ESD122DMXR) によって、過渡電圧を抑制します。また、ESD ダイオード (メーカー型番 TSD05DYFR) が VBUS\_5V0\_TYPEA に配置されています。

図 2-18. USB 2.0 Type-A インターフェイスのブロック図

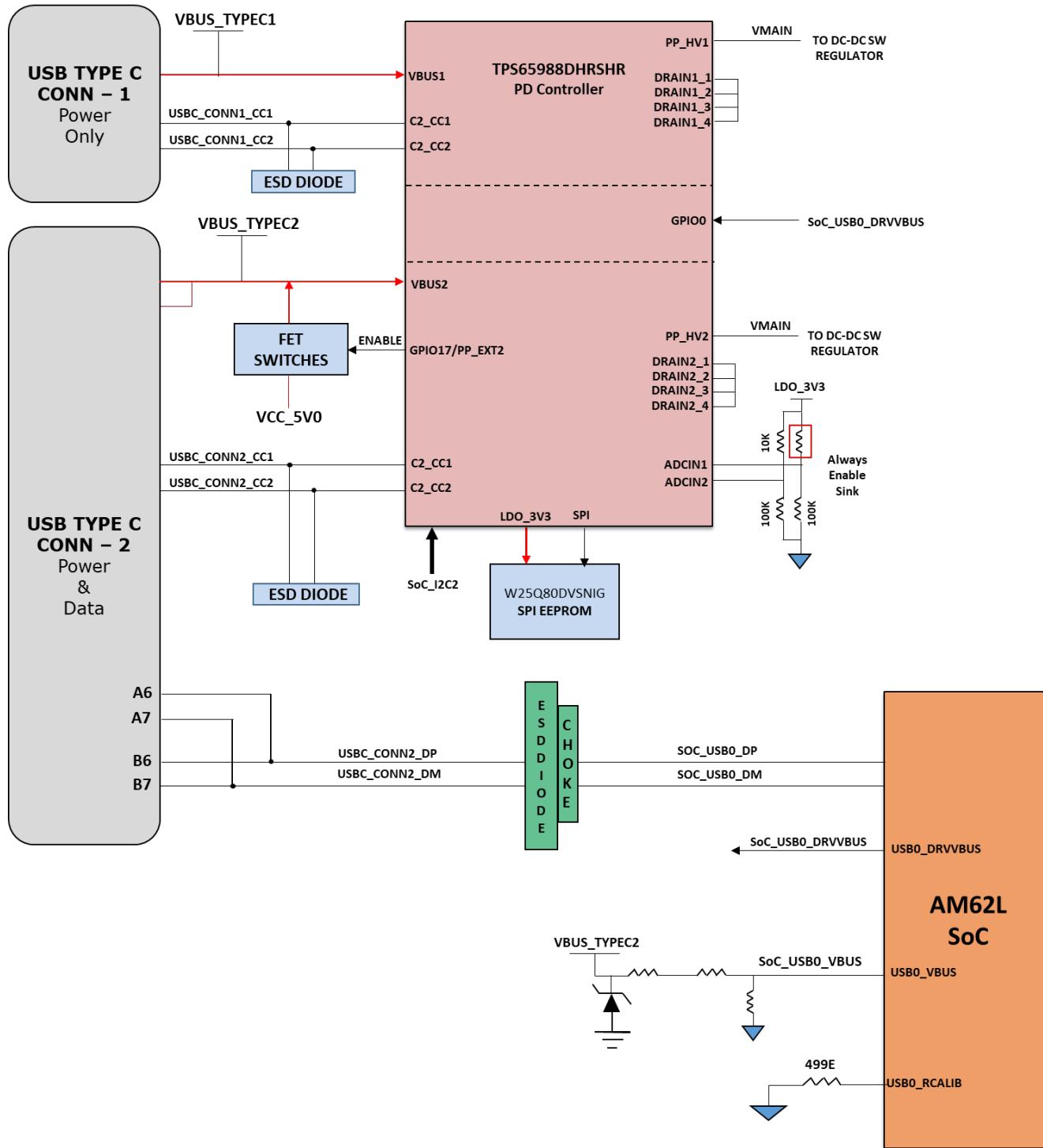

### 2.6.8.2 USB 2.0 Type-C インターフェイス

AM62L EVM では、USB Type-C コネクタ J19 (メーカー型番 2012670005) によって USB 2.0 インターフェイスが提供され、最大 480Mbps のデータレートに対応しています。J19 はデータ通信や、EVM への電源コネクタとして使用することができます。J19 は、PD コントローラ TPS65988DHRSHR IC を使用して、DRP ポートとして構成されています。そのため、ホストとしてもデバイスとしても機能します。ポートの役割は、コネクタに接続されるデバイスのタイプと、そのデバイスがシンクまたはソースのどちらであるかによって決まります。ポートが DFP として機能している場合、500mA で最大 5V を供給できます。

J19 からの USB 2.0 データラインの DP と DM には、チョークと ESD 保護デバイスがあります。SoC への USB0\_VBUS は、(5V~30V) の VBUS 動作に対応する抵抗分圧回路を介して供給されます。

EMI/EMC 低減のため、USB データラインにコモン モード チョーク (メーカー型番 DLW21SZ900HQ2B) が配置されています。USB 2.0 DP/DM 信号の ESD 衝撃を放散させるため、ESD 保護デバイス (型番 ESD122DMXR) が搭載されています。CC 信号には ESD 保護デバイス (部品番号 TPD1E01B04DPLT) が搭載されており、ESD 衝撃を放散させるため、Type-C コネクタ J19 の VBUS レールには TVS2200DRVRC IC が組み込まれています。

図 2-19. USB 2.0 Type-C インターフェイスのブロック図

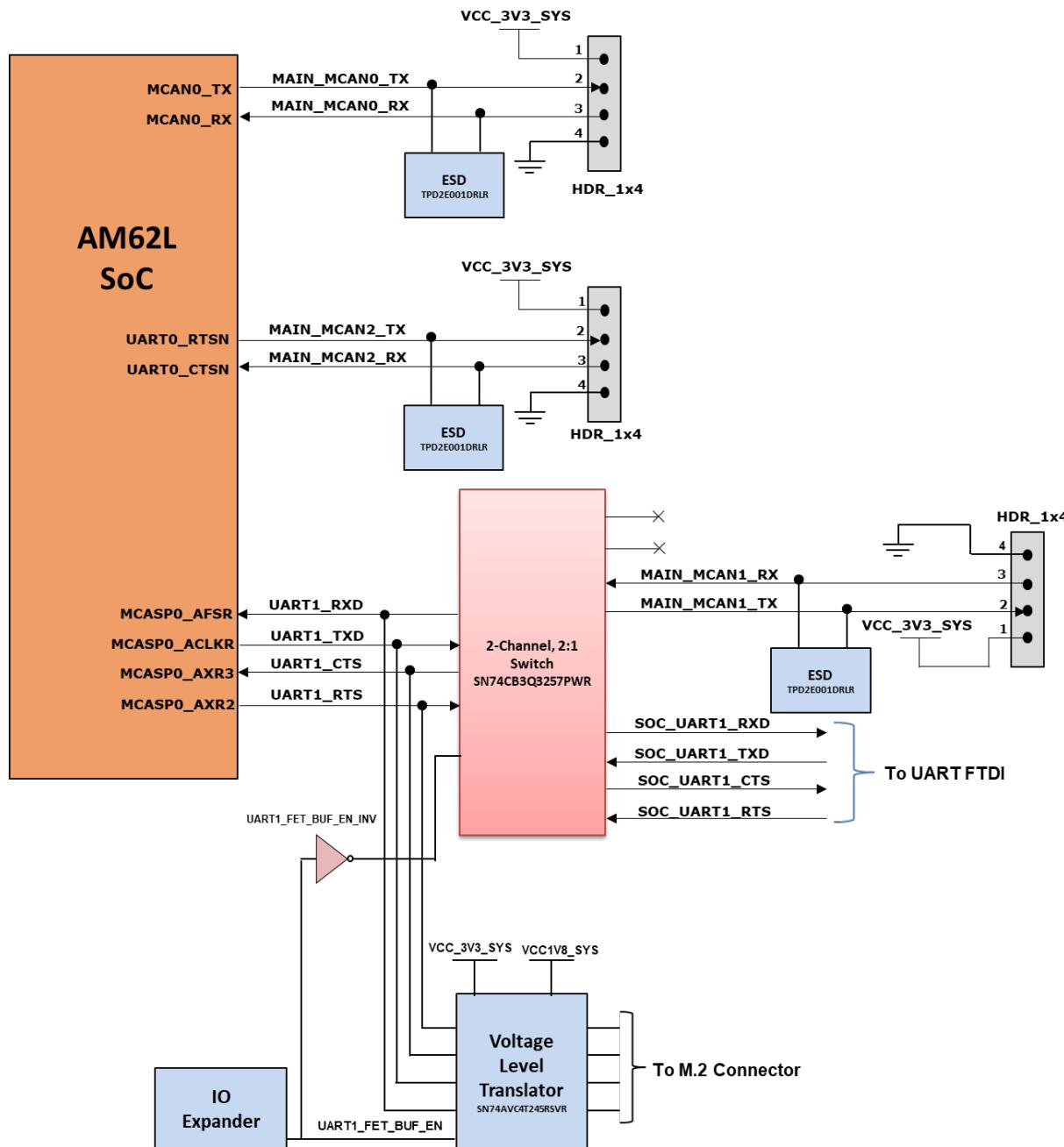

### 2.6.9 MCAN インターフェイス

AM62L EVM には、3 つの MCAN インターフェイスが搭載されています。MAIN\_MCAN0、MAIN\_MCAN1、MAIN\_MCAN2 は、それぞれ J16、J6、J18 という 3 つの 1x4 ヘッダに終端するものとします。ESD 保護のために、メーカー型番 TPD2E001DRLR が、MCAN0、MCAN1、MCAN2 の TX と RX に接続されています。3 つの MCAN ヘッダの最初のピンはすべて VCC\_3V3\_SYS に接続され、4 番目のピンは GND に接続されます。

図 2-20. MCAN インターフェイスのブロック図

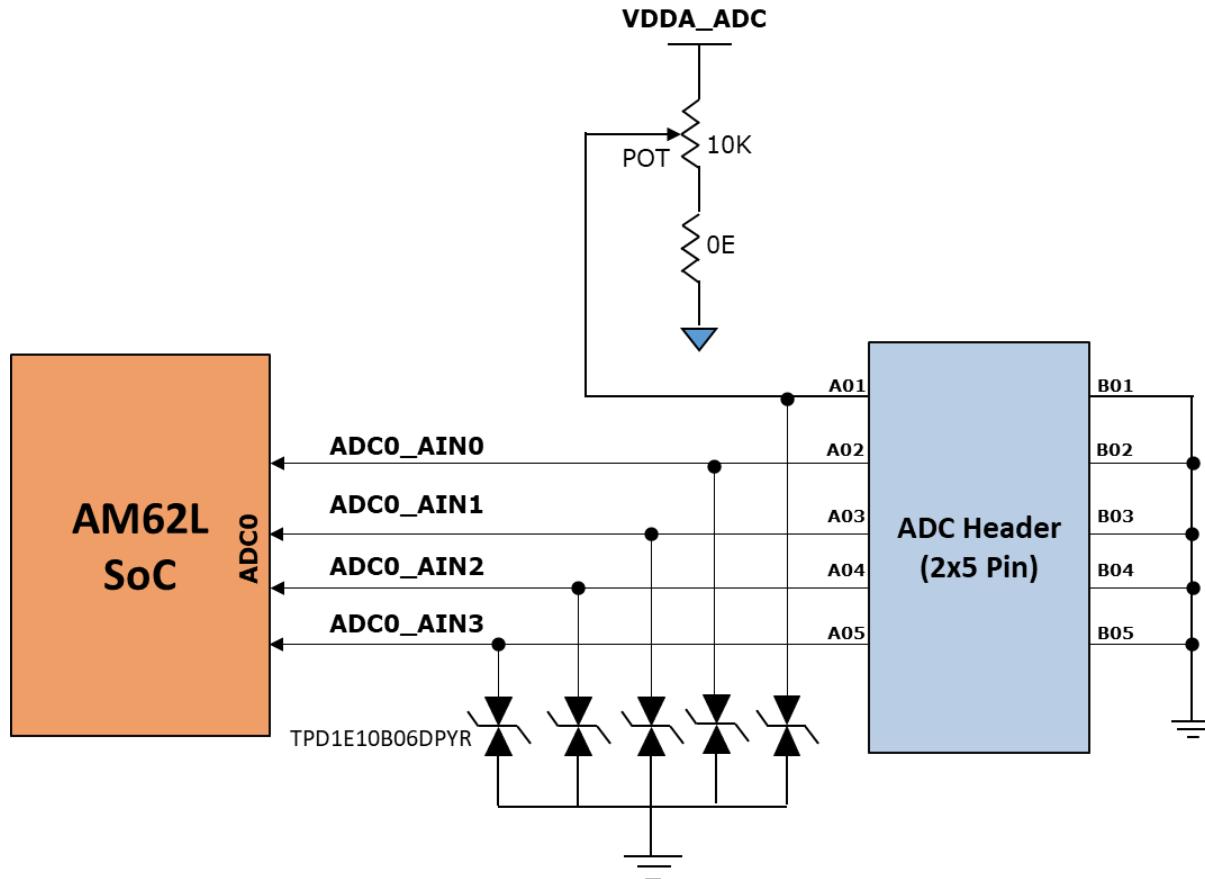

## 2.6.10 ADC インターフェイス

AM62L EVM には、2x5 ピン ヘッダ (J11) で終端された 4 つの ADC 入力があり、ポテンショメータはヘッダの A01 ピンに接続されています。ADC0\_AIN[0:3] の信号には、ESD ダイオード (メーカー型番 TPD1E10B06DPYR) を用いて ESD 保護が行われています。

図 2-21. ADC インターフェイスのブロック図

## 2.6.11 メモリ インターフェイス

### 2.6.11.1 LPDDR4 インターフェイス

AM62L EVM には、最大 1600Mbps/s のデータレートをサポートする Micron のデュアルランク、デュアルダイ 2GB、16 ビット幅 LPDDR4 メモリ (MT53E1G16D1ZW-046 WT:C) が搭載されています。LPDDR4 メモリは最適な位置に配置され、SoC の DDR0 グループに接続されて、ポイントツー ポイント通信をサポートしています。

LPDDR4 メモリはコア電源に 1.8V が必要であるため、電力需要が抑えられます。I/O には、PMIC の 1.1V 電源出力から電力が供給されます。デフォルトのアクティブ状態を設定するため、AM62L SoC によって制御される LPDDR4 リセット (アクティブ Low) はプルダウンされています。また、プルアップ抵抗の実装も可能です。

図 2-22. LPDDR4 インターフェイスの ブロック図

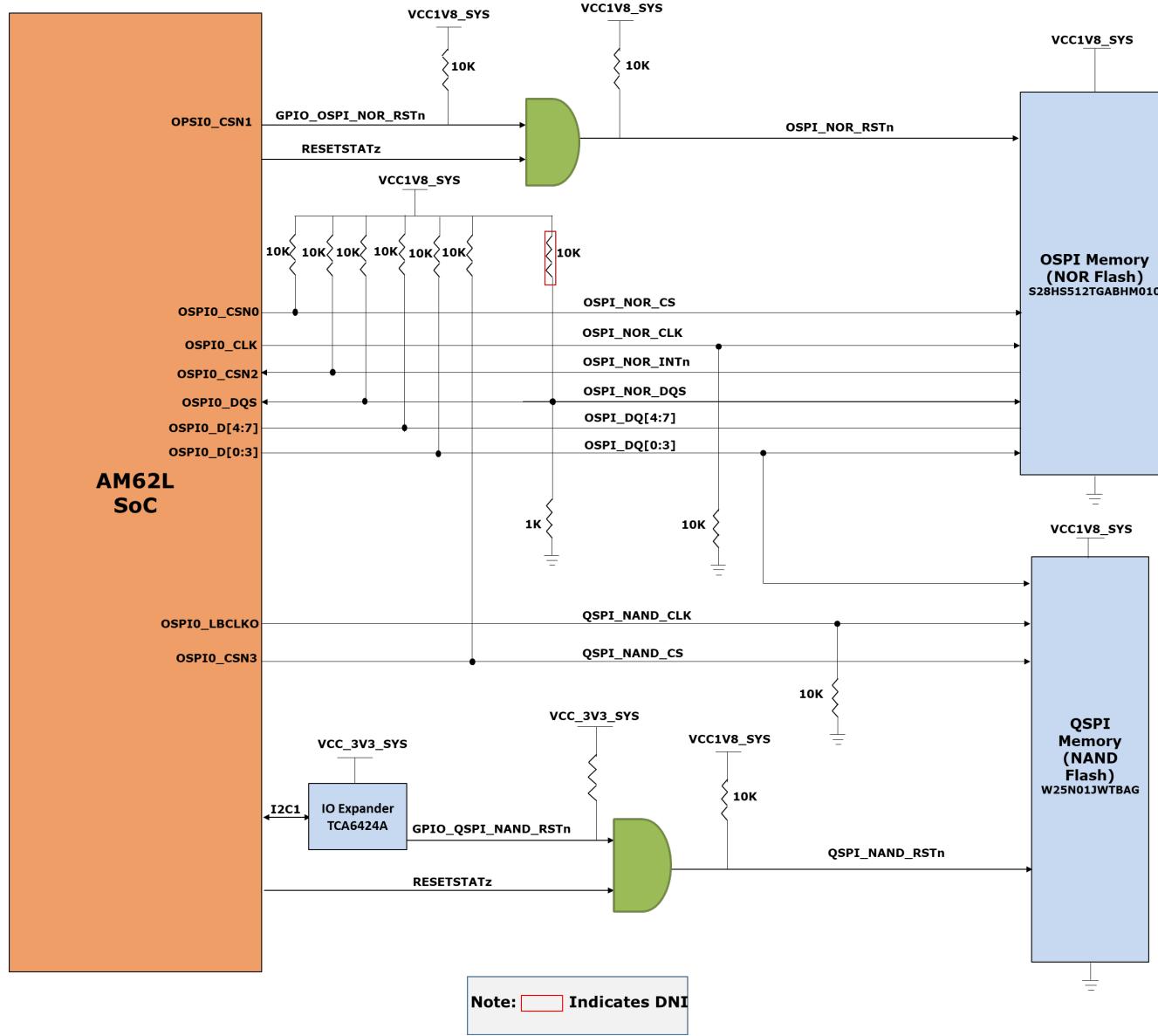

## 2.6.11.2 オクタルシリアルペリフェラルインターフェイス(OSPI)

図 2-23. OSPI のブロック図

### 2.6.11.2.1 OSPI NOR フラッシュ

AM62L EVM ボードでは、512Mb OSPI NOR メモリデバイス (Cypress、メーカー型番 S28HS512TGABHM013) を、AM62L SoC の OSPI0 インターフェイスに接続しています。OSPI メモリは、最高 200Mbps SDR および 400Mbps DDR (クロック速度 200MHz) のメモリ速度でシングルデータレートおよびダブルデータレートに対応しています。また、バスのフローティング状態を防ぐため、DATA[7:0] には外付けプルアップ抵抗が配置されています。OSPI NOR フラッシュと QSPI NAND フラッシュは、デイジーチェーン方式で接続されています。

**リセット:OSPI NOR フラッシュのリセットは、AM62L の RESETSTATz と SoC GPIO の GPIO\_OSPI\_NOR\_RSTn 信号を論理積する回路に接続されています。デフォルトのアクティブ状態を設定するために、GPIO\_OSPI\_NOR\_RSTn にはプルアップ抵抗が配置されています。**

**電源:OSPI NOR フラッシュメモリの VCC ピンと VCCQ ピンは両方とも、オンボードの 1.8V システム電源から供給されます。OSPI I/O グループは、SoC の VDDS1 ドメインから電力を供給され、このドメインは、同じ 1.8V システム電源から給電されています。**

### 2.6.11.2.2 OSPI NAND フラッシュ

AM62L EVM ボードでは、1Gb QSPI NAND フラッシュ メモリ デバイス (Winbond、メーカー型番 W25N01JWTBAG) を、AM62L SoC の OSPI0 インターフェイスに接続しています。QSPI メモリは、最大 80MHz の DTR (デュアル転送レート) と、80MB/s の連続データ転送レートをサポートしています。QSPI NAND フラッシュは DATA[0:3] に接続されています。

リセット:QSPI NAND フラッシュのリセットは、AM62L の RESETSTATz と I/O エクスパンダの GPIO\_QSPI\_NAND\_RSTn 信号を論理積する回路に接続されています。デフォルトのアクティブ状態を設定するため、GPIO\_QSPI\_NAND\_RSTn にはプルアップ抵抗が配置されています。

電源:QSPI NAND フラッシュ メモリの VCC は、オンボードの 1.8V システム電源から供給されます。

### 2.6.11.3 MMC インターフェイス

AM62L SoC には、3 つの MMC ポート (MMC0、MMC1、MMC2) があります。MMC0 は eMMC に、MMC1 は microSD カードコネクタに接続され、MMC2 は Wi-Fi および BT モジュール インターフェイス用の M.2 Key E 拡張コネクタに終端されています。

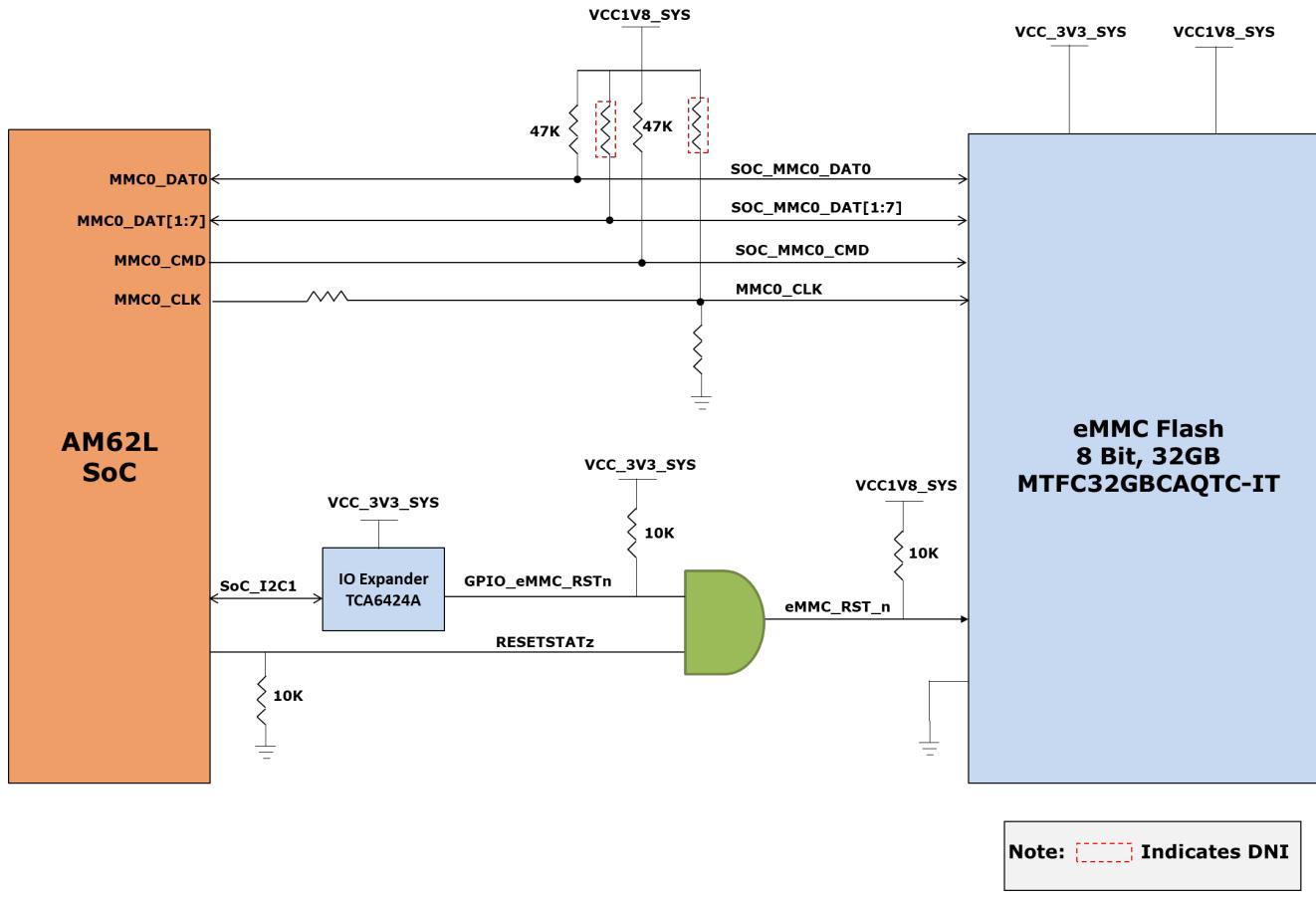

#### 2.6.11.3.1 MMC0 - eMMC インターフェイス

この評価基板には、AM62L SoC の MMC0 ポートに接続された 32GB eMMC フラッシュ メモリ (Micron、メーカー型番 MTFC32GBCAQTC-IT) が搭載されています。

フラッシュ メモリからのデータ バスは、最大 200MHz の HS200 シングル データ レートをサポートする MMC0 インターフェイスの 8 データ ビットに接続されています。Micron の eMMC は、マルチメディア カード (MMC) インターフェイスと NAND フラッシュ コンポーネントを搭載している通信および大容量データストレージ デバイスです。DAT[7:1] にはバスのフローティング状態を防ぐため、外付けプルアップ抵抗を取り付けるオプションがあり、CLK 信号には特性インピーダンスに合わせるため、SoC パッドの近くに直列抵抗が配置されています。

eMMC デバイスには、NAND メモリ用の 3.3V、eMMC インターフェイス用の 1.8V の 2 つの電源が必要です。SoC の MMC0 インターフェイス I/O は、固定 1.8V I/O 電源から供給される VDDSHV2 によって電力が供給されます。

eMMC デバイスには、ホストからのアクティブ Low リセットが必要です。ホストがこの機能を使用するには、ホストは ECSD レジスタ バイト 162、ビット[1:0] を 0x1 に設定して有効にする必要があります。外部リセットは、SoC の RESETSTATz と I/O エクスパンダの GPIO を論理積することによって生成されます。デフォルトのアクティブ状態を設定するため、GPIO ピンにプルアップが提供されています。

図 2-24. eMMC インターフェイスのブロック図

#### 2.6.11.3.2 MMC1 - microSD インターフェイス

この EVM 基板では、microSD カード ソケット (メーカー型番 MEM2051-00-195-00-A) が AM62L SoC の MMC1 ポートに接続されています。これにより、1.8V と 3.3V の両方での I/O 動作を含む UHS1 動作がサポートされます。microSD カード インターフェイスは、デフォルトで SD モードで動作するように設定されています。高速カードの場合、SoC の ROM コードはカードとコントローラがサポートできる最速の速度を検出しようと試み、その後で 1.8V への移行を試みます。SoC の MMC1 I/O は、VDDSHV\_SD\_IO から供給される VDDSHV3 によって電力が供給されます。VDDSHV\_SD\_IO は内部で生成され、SoC から供給されます。

microSD カード コネクタの電源は、ロード スイッチ (メーカー型番 TPS22918DBVR) を使用して供給され、RESETSTATz と I/O エクスパンダの GPIO 出力の論理積によって制御されます。

データ信号、クロック信号、コマンド信号用に、ESD 保護デバイス (部品番号 TPD6E001RSE) が搭載されています。TPD6E001RSE は TVS ダイオードを内蔵したライン終端デバイスで、IEC 61000-4-2 に準拠したシステム レベルの ESD 保護、±8kV の接触放電、±15kV のエアギャップ放電を提供します。

図 2-25. microSD インターフェイスのブロック図

#### 2.6.11.3.3 MMC2 - M.2 Key E インターフェイス

AM62L EVM は、M.2 Key E 拡張機能を搭載しており、Wi-Fi/BT モジュールを、バッファ経由で MMC2、UART1、McASP0 の各インターフェイスに接続できます。これは、産業用温度グレードをサポートするアンテナを搭載した Wi-Fi、デュアルバンド、2.4GHz および 5GHz のモジュールとのインターフェイスとして使用できます。M.2 には、IEEE 規格 802.11a/b/g/n のデータをサポートする MMC2 インターフェイスの 4 ビット I/O が付属しています。M.2 コネクタは、高いスループットと到達範囲の延長ができるほか、Wi-Fi と Bluetooth の共存も実現できるモジュールとインターフェイスできるため、消費電力を最適化する設計に適しています。

M.2 コネクタには、インターフェイス モジュールの電源要件を満たすため、3.3V の電源がオンボード電源として供給されます。SoC の MMC2 インターフェイスは、1.8V I/O 電源に接続された VDDSHV4 電源ドメインから電力が供給されます。

図 2-26. M.2 インターフェイスの ブロック図

#### 2.6.11.4 基板 ID EEPROM

AM62L EVM 基板は、オンボード EEPROM に保存されているバージョンとシリアル番号のデータからリモートで識別可能できます。

Microchip の基板 ID メモリ AT24C512C-MAHM-T は、SoC の I2C0 ポートに接続されており、ヘッダー記述でプログラムされたアドレス 0x51 に応答するように構成されています。EEPROM の I2C アドレスは、A0 ピンを High に駆動し、A1 ピン、A2 ピンを Low に駆動することで変更できます。メモリの最初の 259 バイトは、各基板の識別情報であらかじめプログラムされています。残りの 65277 バイトは、データまたはコードの保存用にユーザーが使用できます。

図 2-27. 基板 ID EEPROM インターフェイスのブロック図

#### 2.6.12 イーサネットインターフェイス

AM62L EVM には、外部通信向けに、1 ギガビット速度のイーサネットポートが 2 つあります。AM62L SoC の RGMII ギガビットイーサネット CPSW ポートの 2 つのチャネルは、個別のギガビットイーサネット PHY トランシーバ DP83867 に接続されています。これらのトランシーバは、内蔵された磁気部品を使用して 2 つの RJ45 コネクタで最終的に終端されます。

PHY DP83867 の 48 ピンバージョンは、設定された Tx および Rx クロックスキュールで 1Gb 動作をアドバタイズして、AM62L 内部の内部遅延に対応するように構成されています。CPSW\_RGMII1 ポートおよび CPSW\_RGMII2 ポートは、外部 PHY トランシーバと通信するために、共通の MDIO バスを使用しています。

イーサネット 10/100/1000Mbps 接続には、ボード上で Link-PP の 2 つのシングル ポート RJ45 コネクタ (メーカー型番 LPJG16314A4NL) が使用されます。RJ45 コネクタには、1000BASE-T リンクと送受信アクティビティを示すための磁気素子および LED が内蔵されています。

イーサネット PHY への I/O 電源は 1.8V の I/O レベルに設定されています。

図 2-28. イーサネット インターフェイスのブロック図

#### 2.6.12.1 CPSW イーサネット PHY ストラッピング

DP83867 のデフォルト構成は、PHY の特定のピンにある複数の抵抗プルアップおよびプルダウン値を使用して決定されています。インストールされている値に応じて、各構成ピンを次の 4 つのモードのいずれかに設定できます。AM62L EVM は、RGMII インターフェイスをサポートする 48 ピン QFN パッケージを使用しています。

DP83867 PHY は、抵抗ストラッピングに基づいて 4 つのレベル構成を使用して、4 つの異なる電圧範囲を生成します。これらの抵抗は、通常 PHY によって駆動されてプロセッサへの入力となる、RX データおよび制御ピンに接続されます。各モードの電圧範囲を以下に示します。

- モード 1 - 0V ~ 0.1764V

- モード 2 - 0.252V ~ 0.3438V

- モード 3 - 0.405V ~ 0.5112V

- モード 4 - 1.2492V ~ 1.5984V

LED\_0 を除くすべてのストラッピング ピンに、プルアップとプルダウンの両方のフットプリントがあります。LED\_0 はミラーネーブル用であり、デフォルトでモード 1 に設定されています。モード 4 は適用できず、モード 2、モード 3 のオプションは不要です。

**表 2-25. CPSW イーサネット PHY1 のデフォルト構成**

|                   |             |

|-------------------|-------------|

| PHY アドレス          | 00000       |

| Auto_neg          | イネーブル       |

| ANG_SEL           | 10/100/1000 |

| RGMII TXCLK スキュー: | 0ns         |

| RGMII RXCLK スキュー  | 2ns         |

**表 2-26. CPSW イーサネット PHY2 のデフォルト構成**

|                   |             |

|-------------------|-------------|

| PHY アドレス          | 00001       |

| Auto_neg          | イネーブル       |

| ANG_SEL           | 10/100/1000 |

| RGMII TXCLK スキュー: | 0ns         |

| RGMII RXCLK スキュー  | 2ns         |

### 2.6.13 GPIO ポート エクスパンダ

AM62L EVM が使用している I/O エクスパンダは、24 ビットの I2C ベース I/O エクスパンダであり、データカードのプログラミング検出や、オンボードで接続されている各種ペリフェラル デバイスに対するリセット信号やイネーブル信号の生成に使用できます。AM62L SoC の SoC\_I2C1 バスは、I/O エクスパンダとインターフェイスするために使用されます。I/O エクスパンダの I2C デバイス アドレスは 0x22 および 0x23 です。

エクスパンダによって制御される信号のリストについては、[表 2-27](#) を参照してください。

**表 2-27. I/O エクスパンダの信号詳細**

| I/O エクスパンダ - 01 |                         |               |                                        |

|-----------------|-------------------------|---------------|----------------------------------------|

| ピン番号            | 信号                      | 方向            | 目的                                     |

| P02             | UART1_FET_SEL           | 出力            | UART1 FET の選択                          |

| P03             | MMC1_SD_EN              | 出力            | SD カード ロード スイッチの有効化                    |

| P04             | VPP_LDO_EN              | 出力            | SoC eFuse 電圧 (VPP = 1.8V) レギュレータのイネーブル |

| P05             | EXP_PS_3V3_EN           | 出力            | EXP CONN 3.3V パワー スイッチのイネーブル           |

| P06             | UART1_FET_BUF_EN        | 出力            | SoC UART1 マルチブレクサの選択                   |

| P10             | DSI_GPIO0               | BIDIRECTIONAL | DSI ディスプレイ GPIO0                       |

| P11             | DSI_GPIO1               | BIDIRECTIONAL | DSI ディスプレイ GPIO1                       |

| P13             | BT_UART_WAKE_SOC_3V3    | 入力            | BT UART WKUP 信号                        |

| P14             | USB_TYPEA_OC_INDICATION | 入力            | USB Type A 過電流インジケータ                   |

| P17             | WLAN_ALERTn             | 入力            | M.2 モジュール WLAN アラート入力                  |

| P20             | HDMI_INTn               | 入力            | HDMI 割り込み                              |

| P21             | TEST_GPIO2              | BIDIRECTIONAL | テスト オートメーション コネクタからの GPIO2 のテスト        |

**表 2-27. I/O エクスパンダの信号詳細 (続き)**

| I/O エクスパンダ - 01 |                       |    |                                 |

|-----------------|-----------------------|----|---------------------------------|

| ピン番号            | 信号                    | 方向 | 目的                              |

| P22             | MCASP0_FET_EN         | 出力 | MCASP0 イネーブルおよび方向制御             |

| P23             | MCASP0_BUF_BT_EN      | 出力 |                                 |

| P24             | MCASP0_FET_SEL        | 出力 |                                 |

| P25             | DSI_EDID              | 入力 |                                 |

| P26             | PD_I2C IRQ            | 入力 | PD コントローラからの割り込み要求              |

| P27             | IO_EXP_TEST_LED       | 出力 | ユーザー テスト LED 2                  |

| I/O エクスパンダ - 02 |                       |    |                                 |

| ピン番号            | 信号                    | 方向 | デバイス                            |

| P00             | BT_EN_SOC             | 出力 | M.2 モジュールの Bluetooth LDO のイネーブル |

| P01             | VOUT0_FET_SEL0        | 出力 | VOUT0 FET スイッチの選択               |

| P10             | WL_LT_EN              | 出力 | M.2 インターフェイス レベル ランスレータのイネーブル   |

| P11             | EXP_PS_5V0_EN         | 出力 | EXP CONN 5V パワー スイッチのイネーブル      |

| P20             | GPIO_QSPI_NAND_RSTn   | 出力 | QSPI NAND フラッシュ リセット制御 GPIO     |

| P21             | GPIO_HDMI_RSTn        | 出力 | HDMI ランスミッタ リセット制御 GPIO         |

| P22             | GPIO_CPSW1_RST        | 出力 | CPSW イーサネット PHY-1 リセット制御 GPIO   |

| P23             | GPIO_CPSW2_RST        | 出力 | CPSW イーサネット PHY-2 リセット制御 GPIO   |

| P24             | GPIO_BOOTMODE_BUF_ENz | 出力 | ブートモード バッファのイネーブル               |

| P25             | GPIO_AUD_RSTn         | 出力 | オーディオ コーデック リセット制御 GPIO         |

| P26             | GPIO_eMMC_RSTn        | 出力 | eMMC リセット制御 GPIO                |

| P27             | SOC_WLAN_SDIO_RST     | 出力 | M.2 モジュール WLAN/SDIO のリセット       |

### 2.6.14 GPIO へのマッピング

表 2-28 に、AM62L EVM ペリフェラルを搭載した AM62L ローパワー SoC の GPIO へのマッピングの詳細を示します。

**表 2-28. AM62L ローパワー SK EVM ペリフェラルを搭載した AM62D ローパワー SoC のマッピング**

| シリアル番号          | GPIO 名称              | GPIO ネット名          | 機能    | 使用 GPIO        | パッケージ信号名   | 制御の方向 | デフォルト状態 | アクティブ状態 | SoC 側の電圧ドメイン | SKEVM に接続されている電圧レベル |

|-----------------|----------------------|--------------------|-------|----------------|------------|-------|---------|---------|--------------|---------------------|

| 1               | WLAN インターフェイスのイネーブル  | WLAN/EN            | イネーブル | GPIO0_51       | MMC2_SDCD  | 出力    | Low     | High    | VDDSHV4      | SoC_DVDD1V8         |

| 2               | WLAN 割り込み            | WLAN IRQ           | 割り込み  | GPIO0_52       | MMC2_SDWP  | 入力    | High    | Low     | VDDSHV4      | SoC_DVDD1V8         |

| 3               | OSPI NOR リセット制御 GPIO | GPIO_OSPI_NO_RSTn  | リセット  | GPIO0_12       | OSPI0_CSn1 | 出力    | High    | Low     | VDDS1        | SoC_DVDD1V8         |

| 4               | OSPI NOR 割り込み        | OSPI_NOR_INTn      | 割り込み  | GPIO0_13       | OSPI0_CSn2 | 入力    | High    | Low     | VDDS1        | SoC_DVDD1V8         |

| 8               | CPSW イーサネット PHY 割り込み | CPSW_RGMII_INTn    | 割り込み  | GPIO0_105      | EXTINTn    | 入力    | High    | Low     | VDDSHV1      | SoC_DVDD3V3         |

| 5               | IO エクスパンダ割り込み        | GPIO0_91_INTn      | 割り込み  | GPIO0_91       | SPI0_D1    | 入力    | High    | Low     | VDDSHV1      | SoC_DVDD3V3         |

| 6               | ユーザー テスト LED 制御信号    | SOC_GPIO0_123      | イネーブル | GPIO0_123      | MMC1_SDWP  | 出力    | Low     | High    | VDDSHV1      | SoC_DVDD3V3         |

| 7               | ユーザー割り込み             | GPIO0_90_INTn      | 割り込み  | GPIO0_90       | SPI0_D0    | 入力    | High    | Low     | VDDSHV1      | SoC_DVDD3V3         |

| 8               | PMIC 割り込み            | PMIC_nINT          | 割り込み  | GPIO0_105      | EXTINTn    | 入力    | High    | Low     | VDDSHV1      | SoC_DVDD3V3         |

| 9               | VOUT0 FET スイッチの選択    | SOC_VOUT0_FET_SEL1 | 選択    | GPIO0_87       | SPI0_CS0   | 出力    | High    | 該当なし    | VDDSHV1      | SoC_DVDD3V3         |

| 10              | VOUT0 FET スイッチの選択    | SOC_VOUT0_FET_SEL0 | 選択    | GPIO0_89       | SPI0_CLK   | 出力    | High    | 該当なし    | VDDSHV1      | SoC_DVDD3V3         |

| I/O エクスパンダ - 01 |                      |                    |       |                |            |       |         |         |              |                     |

| 1               | UART1 FET 選択制御       | UART1_FET_SEL      | 方向制御  | I/O エクスパンダ-P02 |            | 出力    | High    | 該当なし    |              | VCC_3V3_SYS         |

| 2               | SD カード ロード スイッチの有効化  | MMC1_SD_EN         | イネーブル | I/O エクスパンダ-P03 |            | 出力    | High    | High    |              | VCC_3V3_SYS         |

表 2-28. AM62L ローパワー SK EVM ペリフェラルを搭載した AM62D ローパワー SoC のマッピング (続き)

| シリアル番号          | GPIO 名称                                | GPIO ネット名               | 機能    | 使用 GPIO         | パッケージ信号名 | 制御の方向         | デフォルト状態 | アクティブ状態 | SoC 側の電圧ドメイン | SKEVM に接続されている電圧レベル |

|-----------------|----------------------------------------|-------------------------|-------|-----------------|----------|---------------|---------|---------|--------------|---------------------|

| 3               | SoC eFuse 電圧 (VPP = 1.8V) レギュレータのイネーブル | VPP_LDO_EN              | イネーブル | I/O エクスパンダ- P04 |          | 出力            | Low     | High    |              | VCC_3V3_SYS         |

| 4               | EXP CONN 3.3V パワー スイッチのイネーブル           | EXP_PS_3V3_E_N          | イネーブル | I/O エクスパンダ- P05 |          | 出力            | Low     | High    |              | VCC_3V3_SYS         |

| 5               | SoC UART1 マルチブレクサのイネーブル                | UART1_FET_BUF_EN        | イネーブル | I/O エクスパンダ- P06 |          | 出力            | High    | Low     |              | VCC_3V3_SYS         |

| 6               | DSI ディスプレイ GPIO0                       | DSI_GPIO0               | GPIO  | I/O エクスパンダ- P10 |          | BIDIRECTIONAL | 該当なし    | 該当なし    |              | VCC_3V3_SYS         |

| 7               | DSI ディスプレイ GPIO1                       | DSI_GPIO1               | GPIO  | I/O エクスパンダ- P11 |          | BIDIRECTIONAL | 該当なし    | 該当なし    |              | VCC_3V3_SYS         |

| 8               | BT UART WKUP 信号                        | BT_UART_WAKE_SOC_3V3    | 割り込み  | I/O エクスパンダ- P13 |          | 入力            | High    | Low     |              | VCC_3V3_SYS         |

| 9               | USB Type A 過電流インジケータ                   | USB_TYPEA_OC_INDICATION | 割り込み  | I/O エクスパンダ- P14 |          | 入力            | High    | Low     |              | VCC_3V3_SYS         |

| 10              | WLAN アラート割り込み                          | WLAN_ALERTn             | 割り込み  | I/O エクスパンダ- P17 |          | 入力            | High    | Low     |              | VCC_3V3_SYS         |

| 11              | HDMI 割り込み                              | HDMI_INTn               | 割り込み  | I/O エクスパンダ- P20 |          | 入力            | High    | Low     |              | VCC_3V3_SYS         |

| 12              | TEST GPIO2                             | TEST_GPIO2              | GPIO  | I/O エクスパンダ- P21 |          | 該当なし          | High    | 該当なし    |              | VCC_3V3_SYS         |

| 13              | MCASP0 イネーブルおよび方向制御                    | MCASP0_FET_EN           | イネーブル | I/O エクスパンダ- P22 |          | 出力            | Low     | Low     |              | VCC_3V3_SYS         |

| 14              |                                        | MCASP0_BUF_BT_EN        | イネーブル | I/O エクスパンダ- P23 |          | 出力            | Low     | High    |              | VCC_3V3_SYS         |

| 15              |                                        | MCASP0_FET_SEL          | 方向制御  | I/O エクスパンダ- P24 |          | 出力            | High    | 該当なし    |              | VCC_3V3_SYS         |

| 16              | DSI から HDMI カードへのデバイス ID 割り込み          | DSI_EDID                | 割り込み  | I/O エクスパンダ- P25 |          | 入力            | High    | Low     |              | VCC_3V3_SYS         |

| 17              | パワー デリバリ I2C 割り込み要求                    | PD_I2C IRQ              | 割り込み  | I/O エクスパンダ- P26 |          | 入力            | High    | Low     |              | VCC_3V3_SYS         |

| 18              | ユーザー テスト LED 2                         | IO_EXP_TEST_LED         | GPIO  | I/O エクスパンダ- P27 |          | 出力            | Low     | High    |              | VCC_3V3_SYS         |

| I/O エクスパンダ - 02 |                                        |                         |       |                 |          |               |         |         |              |                     |

| 1               | M.2 モジュールの Bluetooth LDO のイネーブル        | BT_EN_SOC               | イネーブル | I/O エクスパンダ- P00 |          | 出力            | High    | High    |              | VCC_3V3_SYS         |

| 2               | VOUT0 FET スイッチの選択                      | VOUT0_FET_SEL0          | 選択    | I/O エクスパンダ- P01 |          | 出力            | Low     | 該当なし    |              | VCC_3V3_SYS         |

| 3               | M.2 インターフェイス レベルトランシスレータのイネーブル         | WL_LT_EN                | イネーブル | I/O エクスパンダ- P10 |          | 出力            | High    | High    |              | VCC_3V3_SYS         |

| 4               | EXP CONN 5V パワー スイッチのイネーブル             | EXP_PS_5V0_E_N          | イネーブル | I/O エクスパンダ- P11 |          | 出力            | Low     | High    |              | VCC_3V3_SYS         |

| 5               | QSPI NAND リセット制御 GPIO                  | GPIO_QSPI_NAND_RSTn     | リセット  | I/O エクスパンダ- P20 |          | 出力            | High    | Low     |              | VCC_3V3_SYS         |

| 6               | HDMI トランスマッタ リセット制御 GPIO               | GPIO_HDMI_RS_Tn         | リセット  | I/O エクスパンダ- P21 |          | 出力            | High    | Low     |              | VCC_3V3_SYS         |

| 7               | CPSW イーサネット PHY-1 リセット制御 GPIO          | GPIO_CPSW1_RST          | リセット  | I/O エクスパンダ- P22 |          | 出力            | High    | Low     |              | VCC_3V3_SYS         |

| 8               | CPSW イーサネット PHY-2 リセット制御 GPIO          | GPIO_CPSW2_RST          | リセット  | I/O エクスパンダ- P23 |          | 出力            | High    | Low     |              | VCC_3V3_SYS         |

| 9               | ブートモード バッファのイネーブル                      | GPIO_BOOTMO_DE_BUF_ENz  | イネーブル | I/O エクスパンダ- P24 |          | 出力            | High    | Low     |              | VCC_3V3_SYS         |

| 10              | オーディオ コーデック リセット制御 GPIO                | GPIO_AUD_RS_Tn          | リセット  | I/O エクスパンダ- P25 |          | 出力            | High    | Low     |              | VCC_3V3_SYS         |

| 11              | eMMC リセット制御 GPIO                       | GPIO_EMMC_RSTn          | リセット  | I/O エクスパンダ- P26 |          | 出力            | High    | Low     |              | VCC_3V3_SYS         |

| 12              | WLAN リセット制御 GPIO                       | SOC_WLAN_SDIO_RST       | リセット  | I/O エクスパンダ- P27 |          | 出力            | High    | Low     |              | VCC_3V3_SYS         |

## 2.7 電源

## 2.7.1 電源入力

Type-C コネクタ (VBUS ラインと CC ライン) はどちらも、デュアル PD コントローラ (メーカー型番 TPS65988) に接続されています。TPS65988 は、スタンダードアロンの USB Type-C およびパワー デリバリ (PD) コントローラであり、2 つの USB Type-C コネクタのケーブルのプラグと向きを検出します。ケーブルを検出すると、TPS65988 は USB PD プロトコルを使用して CC ワイヤで通信を行います。ケーブルの検出と USB PD ネゴシエーションが完了すると、TPS65988 は適切な電力バスを有効にします。TPS65988 の 2 つの内部電力バスは、2 つの Type-C ポートのシンク バスとして構成され、DFP として動作する場合には Type-C CONN 2 から 5V を供給するための外部 FET パスが提供されています。外部 FET パスは、PD コントローラの GPIO17/PP\_EXT2 によって制御され、AM62L SoC の USB0 DRVVBUS の使用も可能にする抵抗オプションも備えています。

TPS65988 PD コントローラは、CC ネゴシエーションにより、3A (最大 12V) の出力を供給できます。両方の Type-C コネクタからの VBUS ピンは、PD コントローラの VBUS ピンに接続されています。PD の出力は VMAIN です。この VMAIN は、オンボードの昇降圧レギュレータと降圧レギュレータに供給され、評価基板用の 5V と 3.3V の固定電源を生成します。

図 2-29. 電源入力のブロック図

## 2.7.2 電源

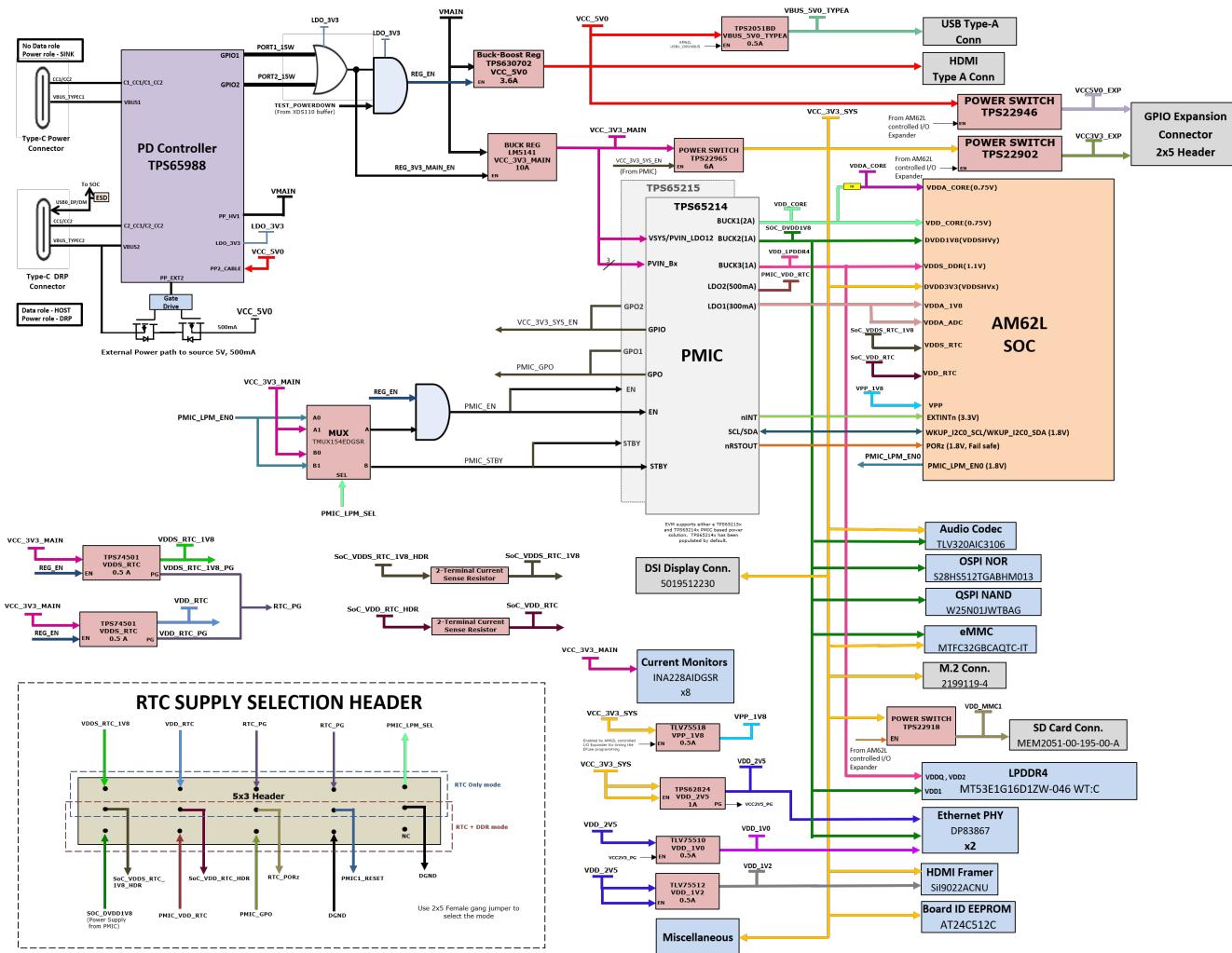

AM62L EVM は、DC/DC コンバータのアレイを使用して、ボード上のさまざまなメモリ、クロック、SoC、その他のコンポーネントに必要な電圧と電力を供給します。

図 2-30 に、AM62L EVM 基板上の各ペリフェラルに対し電源レールを供給するために使用される、各種のディスクリートレギュレータ、PMIC、LDO を示します。

図 2-30. 電力アーキテクチャ

以下のセクションでは、EVM ボード、サポートコンポーネント、リファレンス電圧に電力を供給する電源分配ネットワークのトポロジについて説明します。

注

低消費電力モードをサポートするために必要な接続の詳細については、『AM62L の電源実装』アプリケーションノート (AM62L の電源実装) を参照してください。

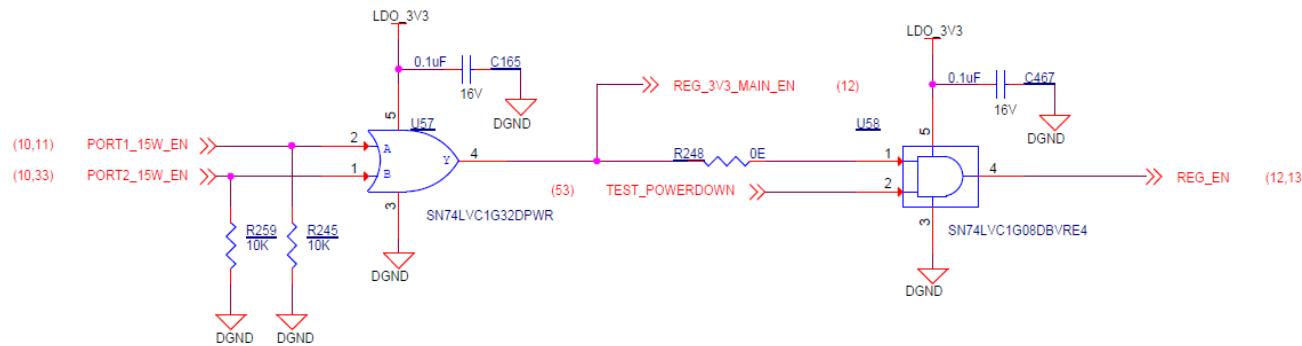

AM62L EVM 基板には、ディスクリート電源コンポーネントに基づく電源ソリューションが搭載されています。電源供給の初期段は、2 つの USB Type-C コネクタ J17 と J19 のいずれかからの VBUS 電圧になります。システムに必要な電力のネゴシエーションには、USB Type-C デュアル PD コントローラ (メーカー型番 TPS65988DHRSHR) が使用されます。PD コントローラの GPIO1 と GPIO2 に提供されるネット名は、それぞれ PORT1\_15W\_EN および PORT2\_15W\_EN です。電力が 15W 以上の場合、これらのピンはネゴシエーションに使用されます。このロジックにより、5V および 3.3V 電源を生成できます。ロジックを、図 2-31 に示します。

図 2-31. 5V および 3.3V 電源の生成を可能にするロジック

REG\_3V3\_MAIN\_EN 信号は 3.3V 電源の生成をイネーブルし、REG\_EN 信号は 5V 電源の生成をイネーブルします。昇降圧コントローラ TPS630702RNMR と降圧コンバータ LM5141RGET は、それぞれ 5V と 3.3V の生成に使用され、レギュレータへの入力は PD 出力です。これらの 3.3V と 5V は、AM62L EVM 基板の電源リソースの主要な電圧です。降圧レギュレータ LM5141RGET から生成された 3.3V 電源は、PMIC、各種 SoC レギュレータ、LDO への入力電源です。昇降圧レギュレータ TPS630702RNMR から生成された 5V 電源は、オンボードのペリフェラルの電源に使用されます。

基板上で使用されるディスクリートレギュレータと LDO は次のとおりです。

- TPS62824DMQR - イーサネット PHY 用に VDD\_2V5 レールを生成

- TLV75510PDQNR - イーサネット PHY 用に VDD\_1V0 を生成

- TLV75512PDQNR - HDMI フレーマ用に VDD\_1V2 を生成

- PTPS6521401VAFR (PMIC - 2) – 各種 SoC およびペリフェラルの電源を生成

- TPS74501PDRVR LDO - VDDS\_RTC\_1V8 を生成

- TPS74501PDRVR LDO - VDD\_RTC を生成

- TPS79601DRBR LDO - XDS110 オンボード エミュレータ

- TPS73533DRVR LDO - FT4232 UART-to-USB ブリッジ

- TLV75518PDBVR LDO - SoC の VPP e-Fuse プログラミング

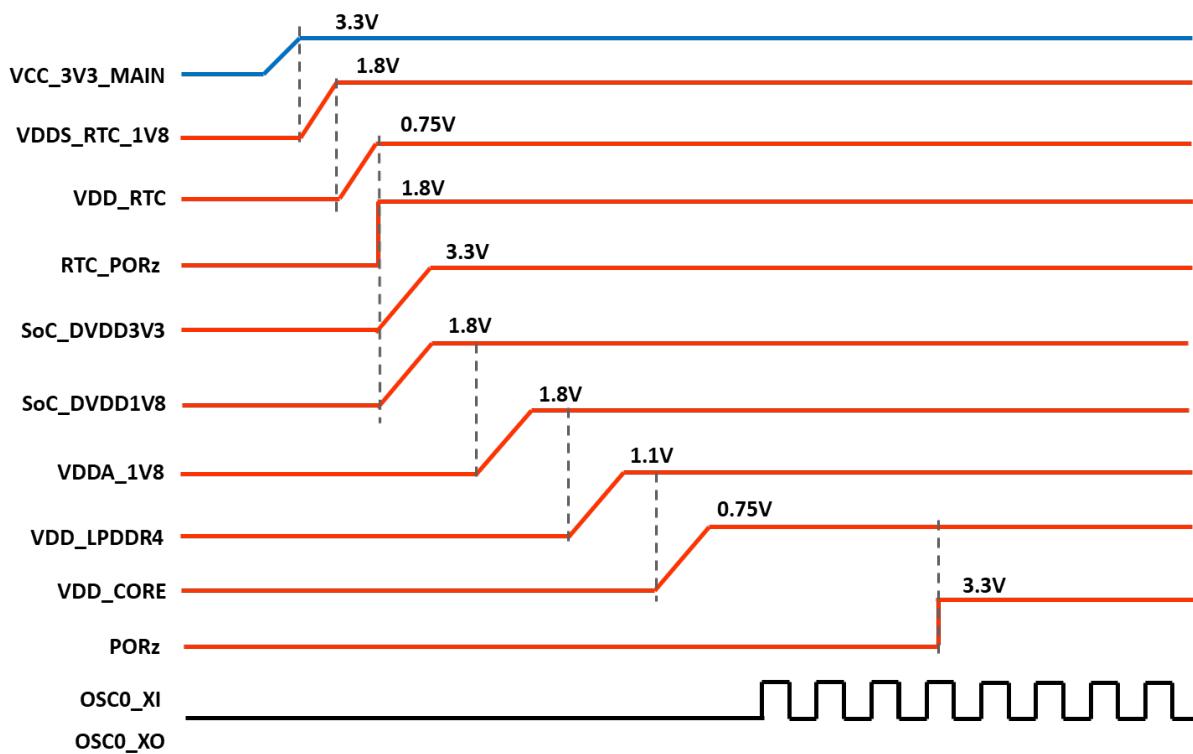

### 2.7.3 電源シーケンス

図 2-32 に、AM62L SoC 電源のパワーアップおよびパワーダウンのシーケンスを示します。

図 2-32. 電源シーケンス

### 2.7.4 AM62L SoC 電源

AM62L SoC のコア電圧は 0.75V です。電流モニタは、SoC 電源レールのすべてに搭載されています。

SoC には異なる I/O グループがあります。各 I/O グループには、表 2-29 に示すように、特定の電源から電力が供給されます。

表 2-29. SoC 電源

| シリアル番号 | 電源               | SoC 電源レール         | I/O 電源グループ | 電圧      |  |

|--------|------------------|-------------------|------------|---------|--|

| 1      | VDD_CORE         | VDDA_CORE         | CORE       | 0.75    |  |

|        |                  | VDDA_DDR_PLL0     |            |         |  |

| 2      | VDDA_CORE        | VDDA_CORE_USB     | USB        | 0.75    |  |

|        |                  | VDDA_CORE_DSI     | DSI        |         |  |

|        |                  | VDDA_CORE_DSI_CLK |            |         |  |

| 3      | SoC_VDD_RTC      | VDD_RTC           | RTC        | 0.75    |  |

| 4      | SoC_VDDS_RTC_1V8 | VDDS_RTC          | RTC        | 1.8     |  |

| 5      | VDDA_1V8         | VDDA_1P8_DSI      | DSI        | 1.8     |  |

|        |                  | VDDA_ADC          | ADC0       |         |  |

|        |                  | VDDA_OSC0         | OSC0       |         |  |

|        |                  | VDDA_PLL[0:1]     |            |         |  |

|        |                  | VDDA_1P8_USB      | USB        |         |  |

| 6      | VDD_LPDDR4       | VDDDS_DDR         | DDR0       | 1.1     |  |

| 7      | VPP_1V8          | VPP_1V8           |            | 1.8     |  |

| 8      | VDDSHV_SD_IO     | VDDSHV3           | MMC1       | 3.3/1.8 |  |

**表 2-29. SoC 電源 (続き)**

| シリアル番号 | 電源          | SoC 電源レール     | I/O 電源グループ | 電圧  |

|--------|-------------|---------------|------------|-----|

| 9      | SOC_DVDD1V8 | VDDSHV2       | MMC0       | 1.8 |

|        |             | VDDSHV4       | MMC2       |     |

|        |             | VDDS0         | GENERAL0   |     |

|        |             | VDDS1         | GENERAL0_1 |     |

|        |             | VDDSHV0       | GPMC       |     |

| 10     | SOC_DVDD3V3 | VDDSHV1       | GENERAL1   | 3.3 |

|        |             | VDDA_3P3_USB  | USB        |     |

| 11     | VDD_MMC1_SD | VDDA_3P3_SDIO |            | 3.3 |

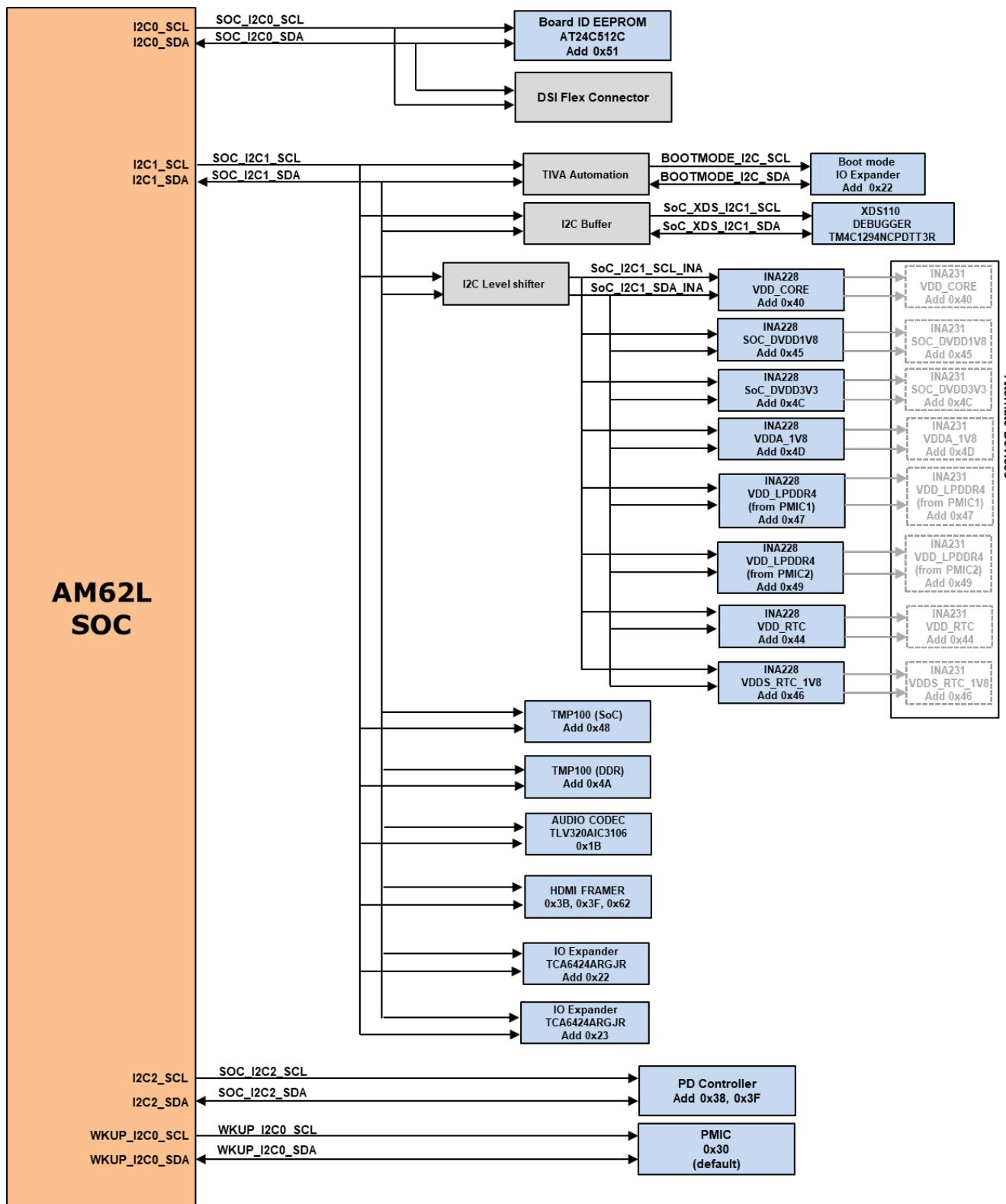

### 2.7.5 電流監視

INA228 電流監視デバイスは、AM62L SoC の各種電源レールの電流と電圧を監視するために使用されます。INA228 は、I2C インターフェイス SoC\_I2C1\_SDA\_INA および SoC\_I2C1\_SCL\_INA (それぞれ SoC\_I2C1\_SCL および SoC\_I2C1\_SDA のレベルシフトバージョン) を介して AM62L SoC とインターフェイスします。TCA9517DR は I2C レベルシフタであり、SoC\_I2C1 を VCC\_3V3\_SYS から VCC\_3V3\_MAIN にレベルシフトするために使用されます。2 端子の幅広シャント抵抗が付属した SoC\_VDDS\_RTC\_1V8 および SoC\_VDD\_RTC 電源を除くすべての電源の負荷電流を測定するために、4 端子の高精度シャント抵抗が実装されています。

#### 注

この設計は、INA228 または INA231 を使用する電流 / 電圧測定をサポートしています。INA228 は、この評価基板 (EVM) にのみ実装されています (スタック PCB フットプリントで実装)。

**表 2-30. INA I2C デバイス アドレス**

| ソース                         | 電源ネット                     | デバイス アドレス | 電源レールに接続されているシャントの値 |

|-----------------------------|---------------------------|-----------|---------------------|

| VCC_CORE                    | VDD_CORE                  | 0x40      | 20mΩ± 1%            |

| VCC_3V3_SYS                 | SoC_DVDD3V3               | 0x4C      | 100mΩ± 0.5%         |

| VCC1V8_SYS                  | SoC_DVDD1V8               | 0x45      | 100mΩ± 0.5%         |

| VDDA1V8                     | VDDA_1V8                  | 0x4D      | 100mΩ± 0.5%         |

| VCC1V1_PMIC1<br>(PMIC 1 より) | VDD_LPDDR4<br>(PMIC 1 より) | 0x47      | 40mΩ± 1%            |

| VCC1V1_PMIC2<br>(PMIC 2 より) | VDD_LPDDR4<br>(PMIC 2 より) | 0x49      | 40mΩ± 1%            |

| SoC_VDD_RTC_HDR             | SoC_VDD_RTC               | 0x44      | 1Ω± 0.5%            |

| SoC_VDDS_RTC_1V8_HDR        | SoC_VDDS_RTC_1V8          | 0x46      | 1Ω± 0.5%            |

## 2.8 クロック処理

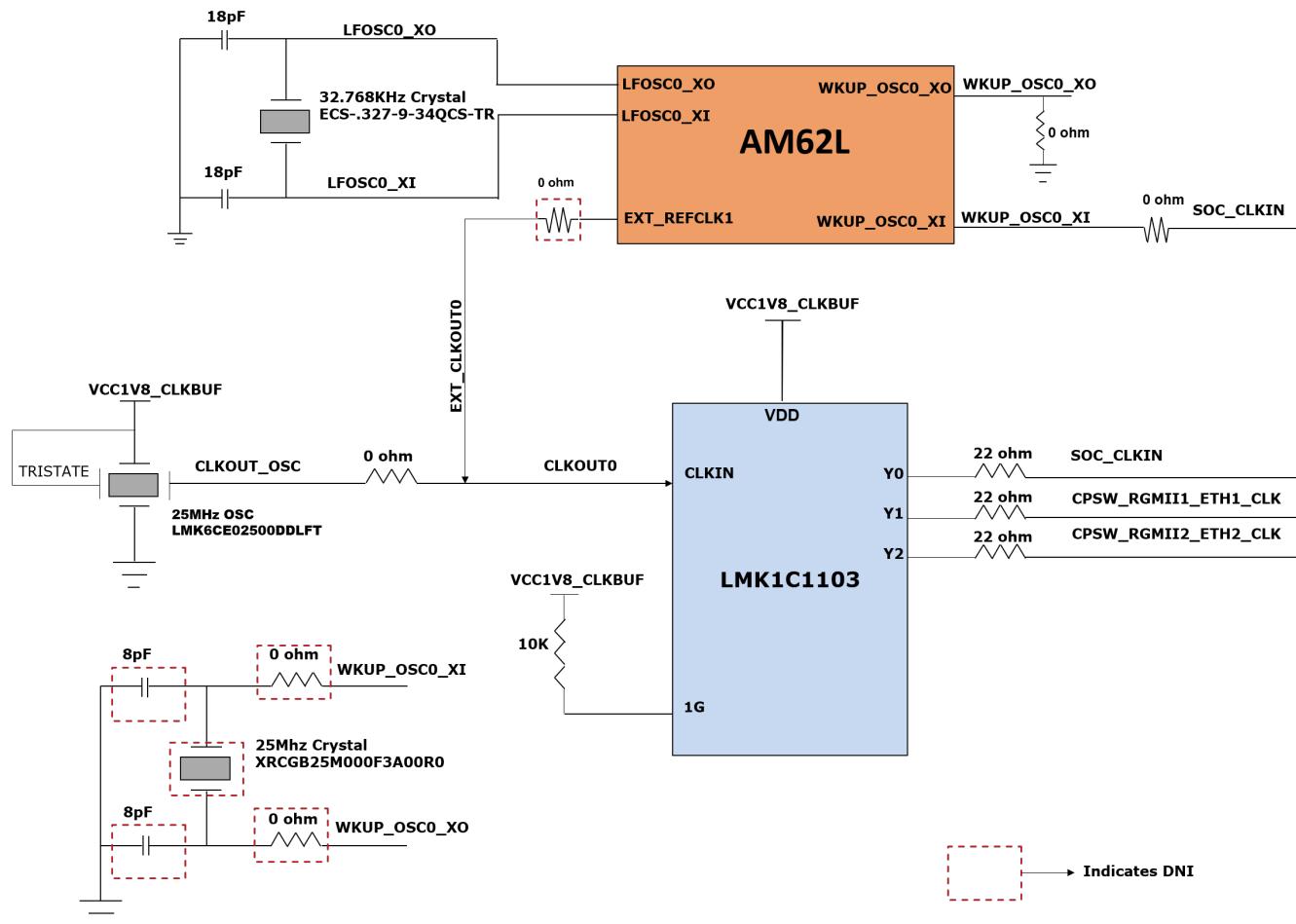

AM62L EVM のクロック アーキテクチャを、図 2-33 に示します。

図 2-33. クロック アーキテクチャ

クロック バッファ (型番 LMK1C1103PWR) は、SoC および 2 つのイーサネット PHY に 25MHz のクロックを供給するために使用されます。LMK1C1103PWR は 1:3 の LVC MOS クロック バッファで、25MHz 水晶振動子 / LVC MOS リファレンス入力を取り込み、3 つの 25MHz LVC MOS クロックを出力します。クロック バッファのソースは、SoC からの CLKOUT0 ピンまたは 25MHz 発振器のいずれかであり、抵抗セットを使用して選択します。デフォルトでは、AM62L EVM のクロック バッファへの入力として発振器が使用されます。クロック バッファの出力 Y1 および Y2 は、2 つのギガビットイーサネット PHY のリファレンスクロック入力として使用されます。

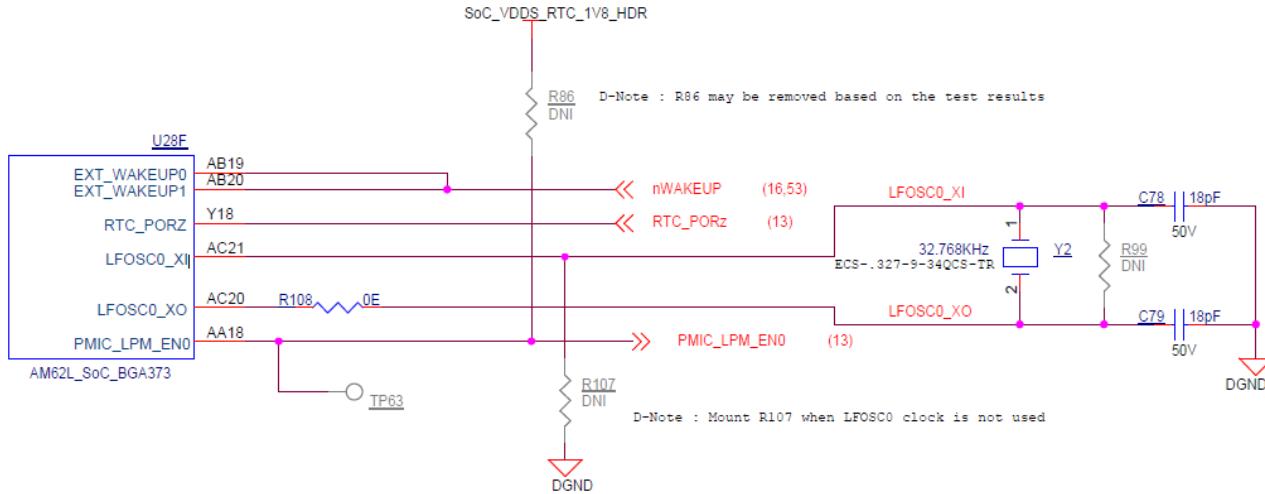

AM62L SoC には、RTC ドメインにクロックを供給するために、1 つの外部水晶振動子 (32.768kHz) が取り付けられています。

## SOC RTC DOMAIN

図 2-34. SOC RTC ドメイン クロック

### 2.8.1 ペリフェラル リファレンス クロック

XDS110、FT4232、M.2 インターフェイス、HDMI フレーマ、オーディオ コーデックなどのペリフェラルに必要なクロック入力は、個別の水晶振動子または発振器を使用してローカルで生成されます。EVM ペリフェラルにリファレンスクロックを提供するために使用される水晶振動子または発振器を、表 2-31 に示します。

表 2-31. クロック表

| ペリフェラル             | メーカー型番               | 説明                     | 周波数       |

|--------------------|----------------------|------------------------|-----------|

| XDS110 エミュレータ (Y4) | XRCGB16M000FXN01R0   | CRY 16.000MHz 8pF SMD  | 16.000MHz |

| FT4232 ブリッジ (Y1)   | 445I23D12M00000      | CRY12.000MHz 18pF SMD  | 12.000MHz |

| M.2 インターフェイス (U66) | ECS-327MVATX-2-CN-TR | OSC 32.768kHz CMOS SMD | 32.768kHz |

| オーディオ コーデック (U59)  | LMK6CE012288CDLFT    | OSC12.288MHz CMOS SMD  | 12.288MHz |

| HDMI フレーマ (U27)    | LMK6CE012288CDLFT    | OSC12.288MHz CMOS SMD  | 12.288MHz |

HDMI トランスマッタが必要とするクロックは、オンボード発振器 または SoC の AUDIO\_EXT\_REFCLK1 のいずれかから供給できます。これらは、抵抗マルチプレクサで選択できます。M.2 モジュールへの 32.768kHz のクロックは、AM62L SoC の WKUP\_CLKOUT0 ボールからデフォルトで供給されます。

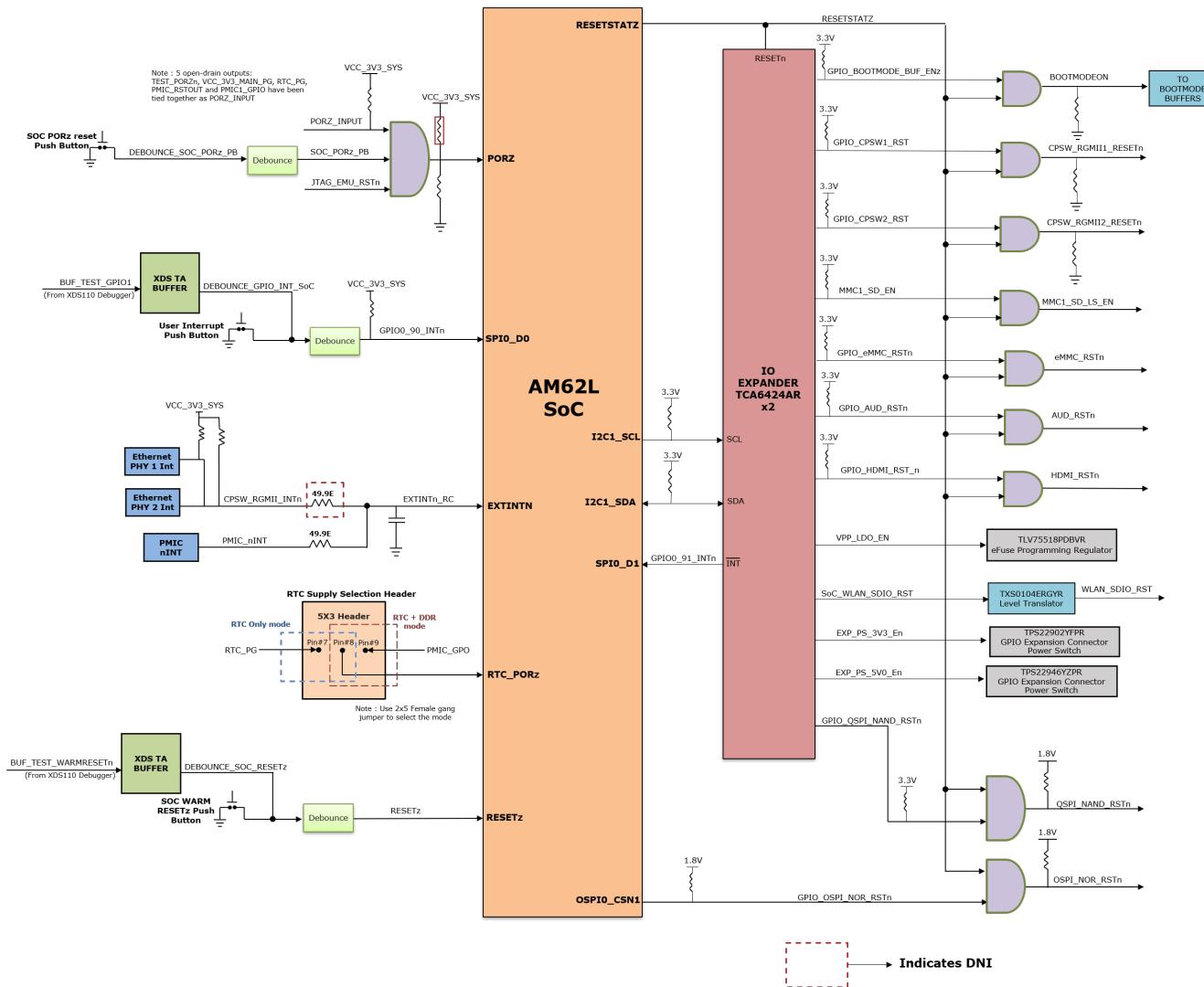

### 2.9 リセット

AM62L EVM のリセットアーキテクチャを、図 2-35 に示します。SoC には次のリセット機能があります。

- RESETSTATz は、MAIN ドメインのウォームリセットステータス出力です。

- RESETz は、MAIN ドメインのウォームリセット入力です

- PORz は、MAIN ドメインのパワー オン / コールドリセット入力です

- RTC\_PORz は、RTC ドメインのパワー オン / コールドリセット入力です

パワー オン リセット時に、MAIN ドメインに接続されているすべてのペリフェラル デバイスは RESETSTATz によってリセットされます。

図 2-35. リセットの ブロック図

## 2.10 拡張ヘッダ

AM62L EVM には、2 つの GPIO 拡張ヘッダが搭載されています。

### 2.10.1 GPIO 拡張ヘッダ

AM62L EVM は、10 ピンおよび 30 ピン GPIO 拡張コネクタ (それぞれ、メーカー型番 67997-410HLF およびメーカー型番 PREC015DAAN-RC) を使用した GPIO 拡張インターフェイスをサポートしています。

10 ピンと 30 ピンの GPIO 拡張コネクタに、以下のインターフェイスおよび I/O が搭載されています。

- 2x SPI:1 CS 付き SPI1 および 1 CS 付き SPI3

- 1x I2C:I2C3

- 1 × UART:UART4

- 13x GPIO:MAIN ドメインからの GPIO

- 5V および 3.3V 電源 (電流制限:155mA と 500mA)

5V および 3.3V の各電源は、それぞれ 155mA および 500mA に電流制限されます。これは、2 個の個別ロードスイッチ TPS22902YFPR および TPS22946YZPR を使用して実現しています。ロードスイッチのインエーブルは、I2C ベースの GPIO ポートエクスパンダと、J26, J25 の各ジャンパを使用して制御できます。J26, J25 の各ジャンパを短絡すると、5V および 3.3V の電源を手動で有効にできます。

2x5 (10 ピン) GPIO 拡張コネクタ (J3) からルーティングされる信号を、表 2-32 に示します。

GPIO 拡張信号は HDMI インターフェイスと共有されます。デフォルトでは、信号は HDMI インターフェイスにルーティングされ、その信号ルーティングはソフトウェアおよび J29 ジャンパの短絡によって、SoC\_VOUT0\_FET\_SEL0、SoC\_VOUT0\_FET\_SEL1 を介して制御できます。

**表 2-32. 10 ピン GPIO 拡張コネクタ (J3)**

| ピン番号 | SoC ポール | ネット名         |

|------|---------|--------------|

| 1    | -       | VCC3V3_EXP   |

| 2    | -       | VCC5V0_EXP   |

| 3    | -       | VCC3V3_EXP   |

| 4    | -       | VCC5V0_EXP   |

| 5    | -       | VCC3V3_EXP   |

| 6    | -       | DGND         |

| 7    | F22     | GPIO0_29_EXP |

| 8    | H18     | GPIO0_26_EXP |

| 9    | H20     | GPIO0_24_EXP |

| 10   | H19     | GPIO0_23_EXP |

2x15 (30 ピン) GPIO 拡張コネクタ (J2) からルーティングされる信号を、表 2-33 に示します。

**表 2-33. 30 ピン GPIO 拡張コネクタ (J2)**

| 番号 | SoC ポール | ネット名           |

|----|---------|----------------|

| 1  | M19     | GPIO0_34_EXP   |

| 2  | N19     | GPIO0_32_EXP   |

| 3  | -       | DGND           |

| 4  | N20     | GPIO0_33_EXP   |

| 5  | L21     | GPIO0_31_EXP   |

| 6  | L20     | GPIO0_41_EXP   |

| 7  | M21     | GPIO0_40_EXP   |

| 8  | -       | DGND           |

| 9  | N21     | GPIO0_39_EXP   |

| 10 | F23     | GPIO0_30_EXP   |

| 11 | -       | DGND           |

| 12 | N23     | SPI3_D0_EXP    |

| 13 | H21     | GPIO0_25_EXP   |

| 14 | P22     | SPI3_CLK_EXP   |

| 15 | N22     | SPI3_D1_EXP    |

| 16 | -       | DGND           |

| 17 | -       | DGND           |