# EVM User's Guide: TMUX48XX-DSG-DDF-EVM

## TMUX48XX 評価基板

### 説明

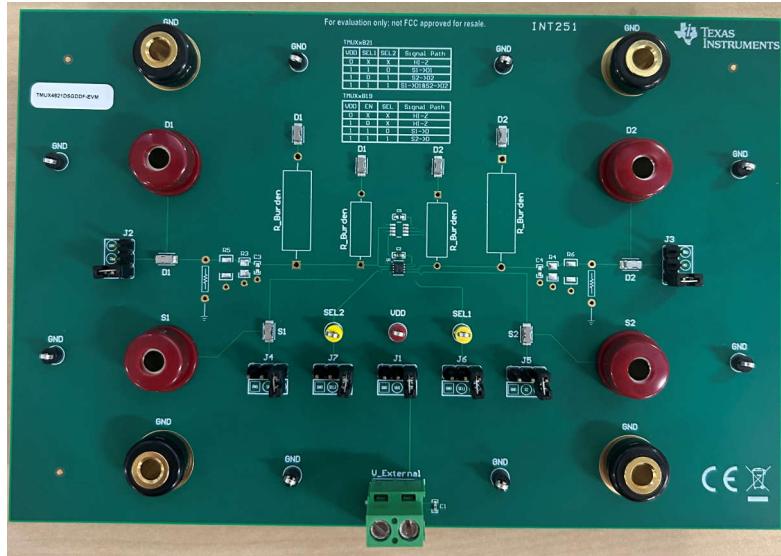

TMUX48XX-DSG-DDF-EVM を使用すると、TMUX4821 および TMUX4819 の性能を評価できます。この評価基板 (EVM) は、TMUX4821 を半田付けした状態で出荷されます。この評価基板 (EVM) を採用すると、エンジニアは TMUX4821 および TMUX4819 low Ron や  $\Delta$ Ron 機能を簡単に評価することができます。この評価基板には複数の抵抗用フットプリントがあり、そのデバイスが信号レンジの合計抵抗にどのような影響を及ぼすかをテストする目的で実装できます。さらに、この評価基板 (EVM) は複数のテストポイントとバナナジャックを搭載しており、マルチプレクサに大電流信号を印加することができます。

### 特長

- V\_External からグランドへのデカップリングコンデンサを使用した外部電源 (1 $\mu$ F 0402)

- VDD からグランドへの電源デカップリングコンデンサ (0.1 $\mu$ F 0402)

- TMUX4821 と TMUX4819 の最大電流能力と電圧能力をサポートする、I/O 上の 8 個のテストポイント

- プローブ作業を容易にする 8 個の追加 GND テストポイント

- TMUX4821 と TMUX4819 の最大電流能力と電圧能力をサポートする、I/O に設けられた 4 個のバナナジャックを搭載

- 追加の 4 個の GND バナナジャックを搭載

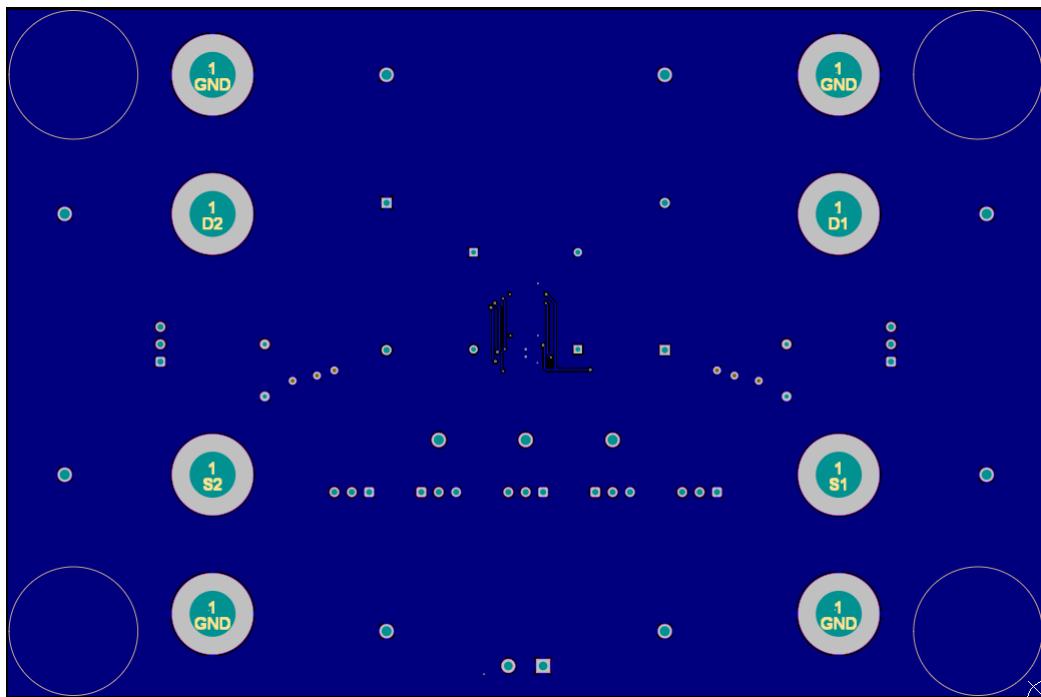

TMUX48XX-DSG-DDF-EVM (上面図)

## 1 評価基板の概要

### 1.1 はじめに

このユーザー ガイドでは、TMUX48XX-DSG-DDF-EVM 評価基板 (EVM) とその想定用途の概要を説明します。このボードを使用すると、DSG および DDF の各パッケージ版の TI の TMUX4821 および TMUX4819 の各マルチプレクサの迅速なプロトタイプ作成と特性評価を実行できます。この評価基板を使用することで、信号パスの合計抵抗に及ぼすデバイスの影響を評価できます。

フィーチャー リストの続きを次に示します。

- デバイスを外部電源に接続または接続解除するための 1 個の 3 ピン ヘッダ

- 本デバイスのロジックを制御するための 2 個の 3 ピン ヘッダ

- デバイスの信号パス状態を変更するための 4 個の 3 ピン ヘッダ

- 追加の RC 負荷に対応できるように、複数の未実装フットプリント

- 抵抗を取り付けるための複数のスルーホール

#### 注意

この評価基板 (EVM) は複数のジャンパを実装しており、複数のヘッダを実装しており、ピンをグランドに短絡します。最初に使用する前に、ピンの状態を認識し、アプリケーションに応じて変更してください。これを守らないと、デバイスおよび EVM の信頼性が損なわれるリスクがあります。

### 1.2 キットの内容

この評価基板には以下が含まれます：

- (1) TMUX48XX-DSG-DDF-EVM

### 1.3 仕様

TMUX48XX-DSG-DDF-EVM は、TMUX4821 および TMUX4819 の評価に使用されます。この評価基板には 7 個の 3 ピン ヘッダが搭載されており、I/O を電圧電源レベルに接続するため、またはグランドに接続するための 4 個のヘッダです。SEL ピンを切り替えて、デバイスの信号パス配線を制御するための 2 個のヘッダ。最後の 3 ピン ヘッダでは、VDD 電源を外部電源に接続するか、基板のグランドに接続するか、フローティングのままにすることができます。

この EVM は各 I/O に複数のテストポイントが配置されており、合計 8 個のテストポイントは最大 2A の定格です。これにより、TMUX4821 および TMUX4819 を最大電流通過能力でテストできます。これらのテストポイントのうち 4 つは、I/O に直接配線されています。残り 4 つは、抵抗テストのために実装可能な未実装負荷抵抗に配線されています。これらは負荷抵抗の上に配置され、上部リードに配線されます。負荷抵抗の両端の電圧を測定する場合は、これらのテスト ポイントをグランドに接続してください。さらに 8 個の追加グランド テスト ポイントが設けられており、ボード上でより高い接続の柔軟性を高めます。

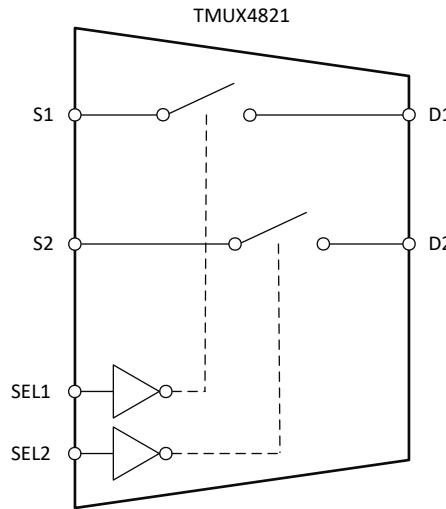

図 1-1. TMUX4821 の概略回路図

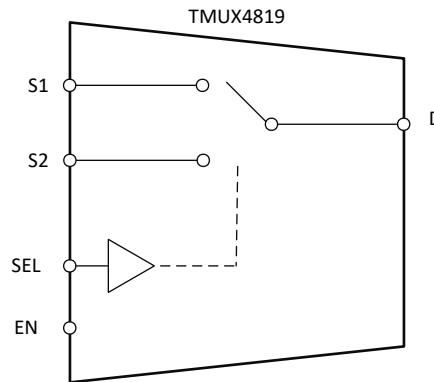

図 1-2. TMUX4819 の概略回路図

## 1.4 製品情報

TMUX4821 および TMUX4819 は、高精度の相補型金属酸化膜半導体 (CMOS) マルチプレクサです。TMUX4821 は、独立して選択可能な 2 個の単極单投 (SPST) スイッチ チャネルを備えています。TMUX4819 は、1 つの単極双投 (SPDT) チャネルを備えています。これらのデバイスは単一の電源 (1.8V~5.5V) で動作しますが、-15V ~ 15V の電源を超える双方向アナログおよびデジタル信号を通過させることができます。

または、最大で  $\pm 15V$  の電源オフ保護も備えており、電源電圧が存在しない場合 ( $VDD = 0V$ ) でも  $Sx$  の電圧から  $Dx$  を絶縁します。この保護機能がない場合、内部 ESD ダイオード経由でスイッチの電圧から電源レールに電力が逆流し、残りのシステムに損傷を引き起こすことがあります。

1mΩ の RON 平坦性を採用した TMUX4821 と TMUX4819 は、歪みを発生させずに信号を通過させるのに最適です。

## 2 ハードウェア

### 2.1 電源要件

TMUX48XX-DSG-DDF-EVM には、選択したロジックに応じて、の **Sx** ピンと **Dx** ピンの間にパッシブ信号経路を提供するために、V-External から J1 端子経由または赤色 VDD テストポイントに直接接続した 1.8V ~ 5.5V の電源が必要です。上向きにしてみた場合、V- External 端子の左側が GND、右側が VDD ですので注意してください。

### 2.2 ヘッダおよびジャンパ情報

TMUX48XX-DSG-DDF-EVM は 7 個の 3 ピン ヘッダを搭載しており、電源接続、制御入力、ソース、ドレインを制御できます。各ヘッダの説明は以下のとおりです。

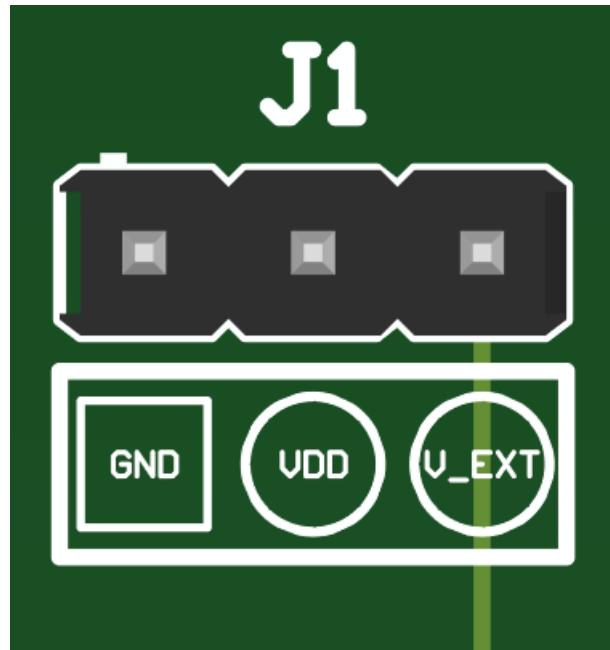

#### 1. 供給ヘッダ J1

ヘッダ J1 は、ジャンパを介して VDD ピンを外部電源またはグランドに接続します。ヘッダ J1 が接続されていない場合、デバイスの電源はフローティングのままになります。図 2-1 に、ヘッダ J1 を示します。

- 外部電源に接続するには、ヘッダ上の J1-2 の位置を J1-3 に短絡します。V\_EXT 端子からデバイスに電力が供給されます。

- グランドに接続するには、ヘッダ上の J1-2 の位置を J1-1 に短絡します。これで、デバイスの電源ピンはグランドに接続されます。

- デバイスの電源ピンをフローティングのままにするには、J1-2 を未接続にしてフローティングのままにします。

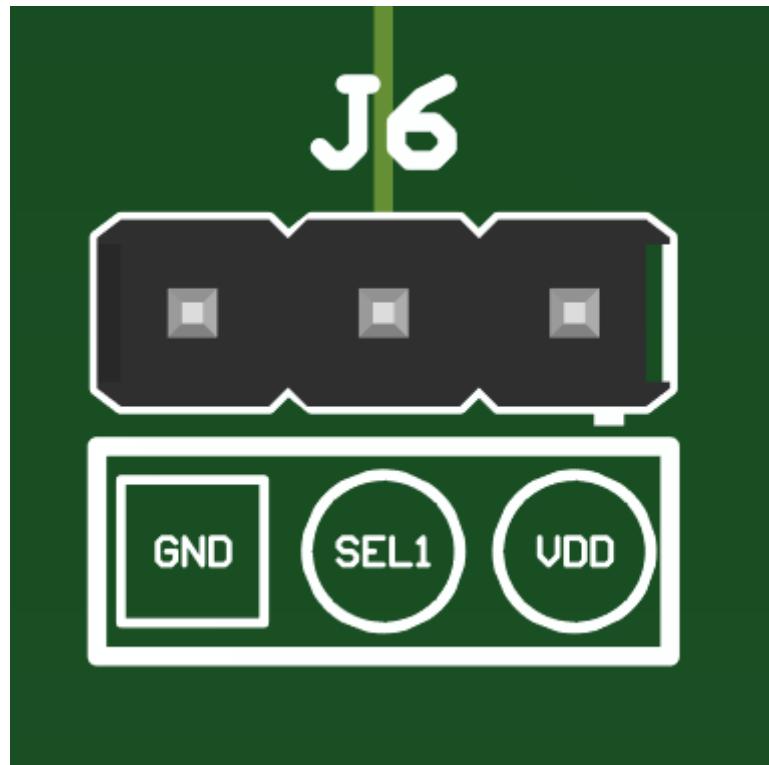

#### 2. 制御ヘッダ J6

ヘッダ J6 は、ジャンパを使って SEL1 ピンを VDD またはグランドに接続します。ヘッダ J6 が接続されていない場合、デバイスの SEL1 ピンはフローティングのままになります。

- VDD に接続するには、ヘッダ上の J6-2 の位置を J6-3 に短絡します。VDD は、デバイスの SEL1 ピンに接続されます。

- グランド、GND に接続するには、ヘッダ上の J6-2 の位置を J6-1 に短絡します。これで、デバイスの SEL1 ピンはグランドに接続されます。

- J6-2 を未接続のままにすると、SEL1 ピンはフローティングのままになります。デバイスが不明な状態になるため、これを行うことは推奨されません。

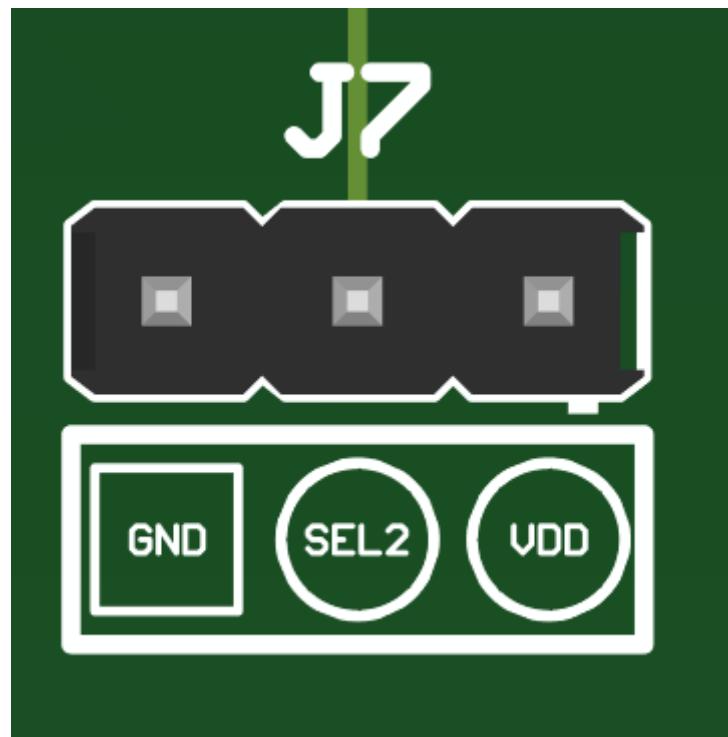

#### 3. 制御ヘッダ J7

ヘッダ J7 は、ジャンパを介して SEL2 ピンを VDD またはグランドに接続します。ヘッダ J7 が接続されていない場合、デバイスの SEL2 ピンはフローティングのままになります。

- VDD に接続するには、ヘッダ上の J7-2 の位置を J7-3 に短絡します。VDD は、デバイスの SEL2 ピンに接続されます。

- グランド、GND に接続するには、ヘッダ上の J7-2 の位置を J7-1 に短絡します。これで、デバイスの SEL2 ピンはグランドに接続されます。

- J7-2 を未接続のままにすると、SEL2 ピンはフローティングのままになります。デバイスが不明な状態になるため、これを行うことは推奨されません。

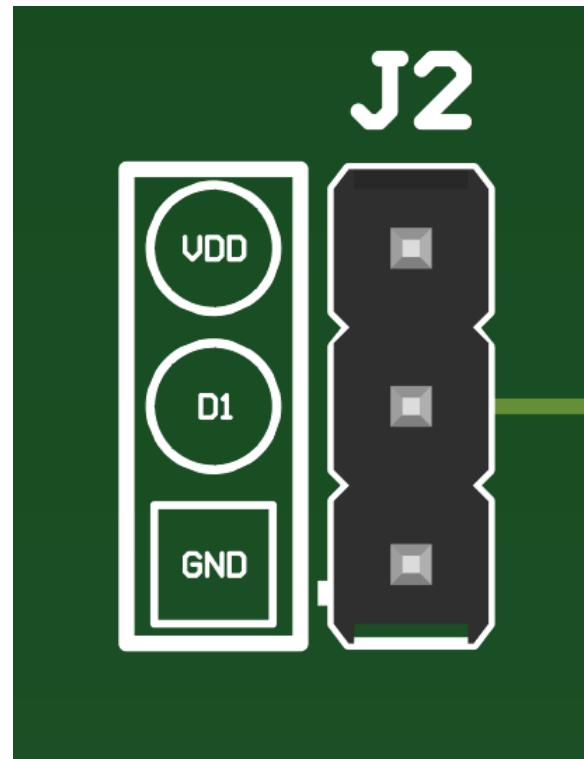

#### 4. ドレインヘッダ J2

ヘッダ J2 は、ジャンパを使って D1 ピンを VDD またはグランドに接続します。ヘッダー J2 が接続されていない場合、デバイスの D1 ピンはフローティングのまになります。

- VDD に接続するには、ヘッダ上の J2-2 の位置を J2-1 に短絡します。VDD は、デバイスの D1 ピンに接続されました。

- グランド、GND に接続するには、ヘッダ上の J2-2 の位置を J2-3 に短絡します。これで、デバイスの D1 ピンはグランドに接続されます。

- J2-2 を未接続のままにすると、D1 ピンはフローティングのまになります。

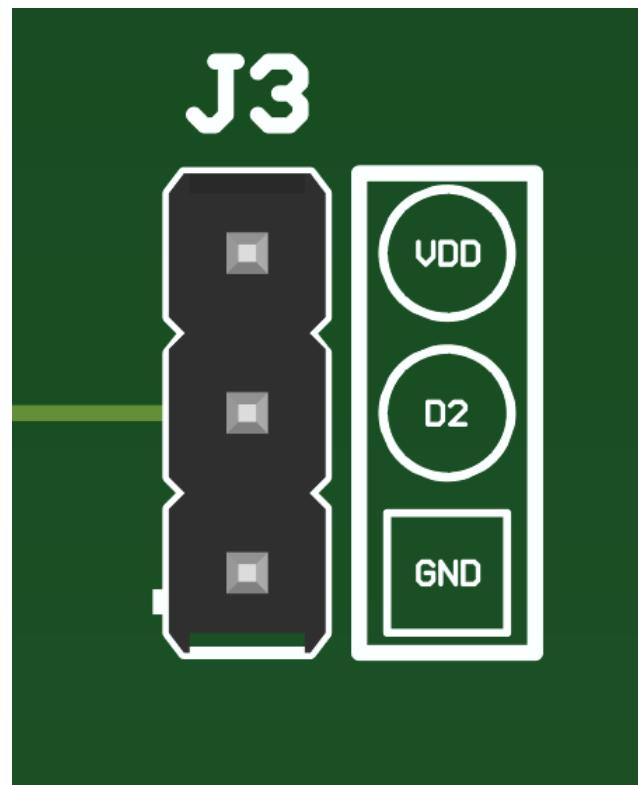

## 5. ドレインヘッダ J3

ヘッダ J3 は、ジャンパを介して D2 ピンを VDD またはグランドに接続します。ヘッダー J3 が接続されていない場合、デバイスの D2 ピンはフローティングのままになります。

- VDD に接続するには、ヘッダ上の J3-2 の位置を J3-1 に短絡します。VDD は、デバイスの D2 ピンに接続されました。

- グランド、GND に接続するには、ヘッダ上の J3-2 の位置を J3-3 に短絡します。これで、デバイスの D2 ピンはグランドに接続されます。

- J3-2 を未接続のままにすると、D2 ピンはフローティングのままになります。

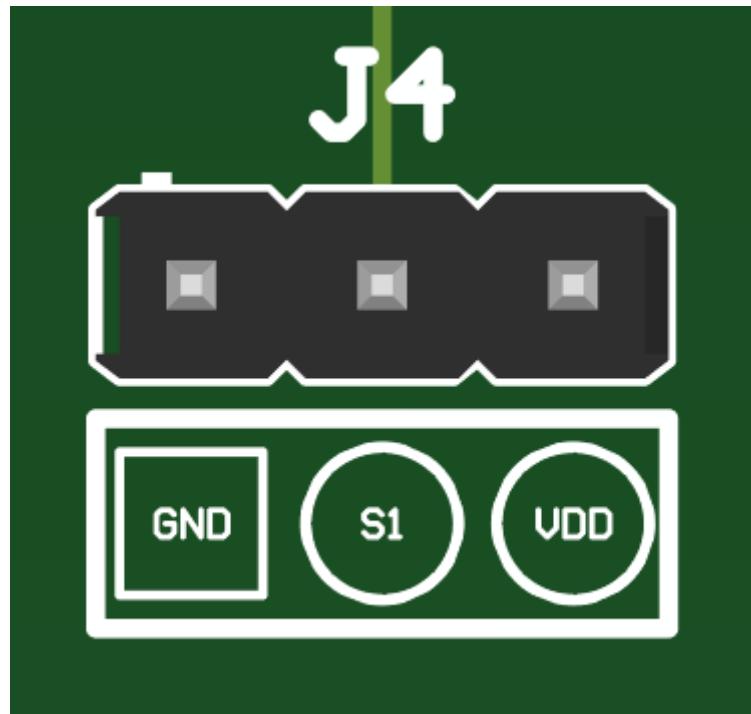

## 6. ソースヘッダ J4

ヘッダ J4 は、ジャンパを使って S1 ピンを VDD またはグランドに接続します。ヘッダー J4 が接続されていない場合、デバイスの S1 ピンはフローティングのまになります。

- VDD に接続するには、ヘッダ上の J4-2 の位置を J4-3 に短絡します。VDD は、デバイスの S1 ピンに接続されます。

- グランド、GND に接続するには、ヘッダ上の J4-2 の位置を J4-1 に短絡します。これで、デバイスの S1 ピンはグランドに接続されます。

- J4-2 を未接続のまにすると、S1 ピンはフローティングのまになります。

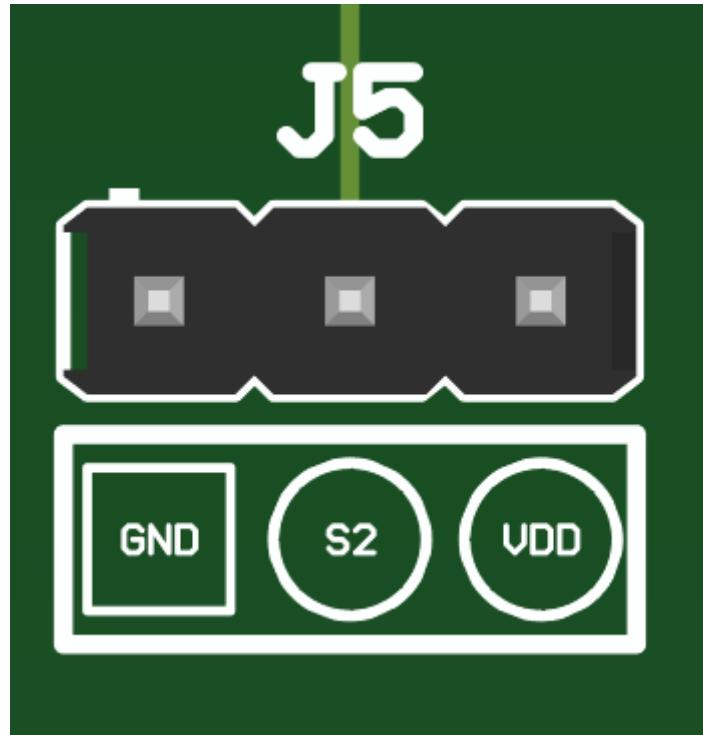

## 7. ソースヘッダ J5

ヘッダ J5 は、ジャンパを使って S2 ピンを VDD またはグランドに接続します。ヘッダ J5 が接続されていない場合、デバイスの S2 ピンはフローティングのまになります。

- VDD に接続するには、ヘッダ上の J5-2 の位置を J5-3 に短絡します。VDD は、デバイスの S2 ピンに接続されます。

- グランド、GND に接続するには、ヘッダ上の J5-2 の位置を J5-1 に短絡します。これで、デバイスの S2 ピンはグランドに接続されます。

- J5-2 を未接続のまにすると、S2 ピンはフローティングのまになります。

図 2-1. ヘッダ J1:J1-1 (GND)、J1-2 (デバイス VDD への接続)、J1-3 (V\_EXT)

図 2-2. ヘッダ J6:J6-1 (GND)、J6-2 (デバイス SEL1 への接続)、J6-3 (VDD)

図 2-3. ヘッダ J7:J7-1 (GND)、J7-2 (デバイス SEL2 への接続)、J7-3 (VDD)

図 2-4. ヘッダ J2:J2-1 (VDD)、J2-2 (デバイス D1 への接続)、J2-3 (GND)

図 2-5. ヘッダ J3:J3-1 (VDD)、J3-2 (デバイス D2 への接続)、J3-3 (GND)

図 2-6. ヘッダ J4:J4-1 (GND)、J4-2 (デバイス S1 への接続)、J4-3 (VDD)

図 2-7. ヘッダ J5:J5-1 (GND)、J5-2 (デバイス S2 への接続)、J5-3 (VDD)

ロジックヘッダ J6 (SEL1) および J7 (SEL2) を使用して、TMUX4821 と TMUX4819 の両方を制御できます。TMUX4819 には EN ピンがあり、SEL2 によって制御でき、SEL ピンは SEL1 によって制御できます。

## TMUXx821

| VDD | SEL1 | SEL2 | Signal Path     |

|-----|------|------|-----------------|

| 0   | X    | X    | HI-Z            |

| 1   | 1    | 0    | S1->D1          |

| 1   | 0    | 1    | S2->D2          |

| 1   | 1    | 1    | S1->D1 & S2->D2 |

図 2-8. TMUX48XX-DSG-DDF-EVM TMUX4821 の真理値表

## TMUXx819

| VDD | EN | SEL | Signal Path |

|-----|----|-----|-------------|

| 0   | X  | X   | HI-Z        |

| 1   | 0  | X   | HI-Z        |

| 1   | 1  | 0   | S1->D       |

| 1   | 1  | 1   | S2->D       |

図 2-9. TMUX48XX-DSG-DDF-EVM TMUX4819 の真理値表

## 2.3 テスト ポイント

このボードには合計 19 個のテスト ポイントがあります。8 GND, 2 SEL, 1 VDD, and 8 I/O。

| テスト ポイント ID | 説明   | 信号       |

|-------------|------|----------|

| S1          | 表面実装 | S1       |

| S2          | 表面実装 | S2       |

| D1          | 表面実装 | D1       |

| D1          | 表面実装 | D1       |

| D1          | 表面実装 | D1       |

| D2          | 表面実装 | D2       |

| D2          | 表面実装 | D2       |

| D2          | 表面実装 | D2       |

| VDD         | 赤    | VDD      |

| SEL1        | 黄    | SEL1/SEL |

| SEL2        | 黄    | SEL2/EN  |

| GND         | 黒    | GND      |

### 3 ハードウェア設計ファイル

以下のセクションには、TMUX48XX-DSG-DDF-EVM のハードウェア設計ファイルを示します。このセクションでは、基板レベルの回路図、PCB レイアウト、部品表 (BOM) を示します。

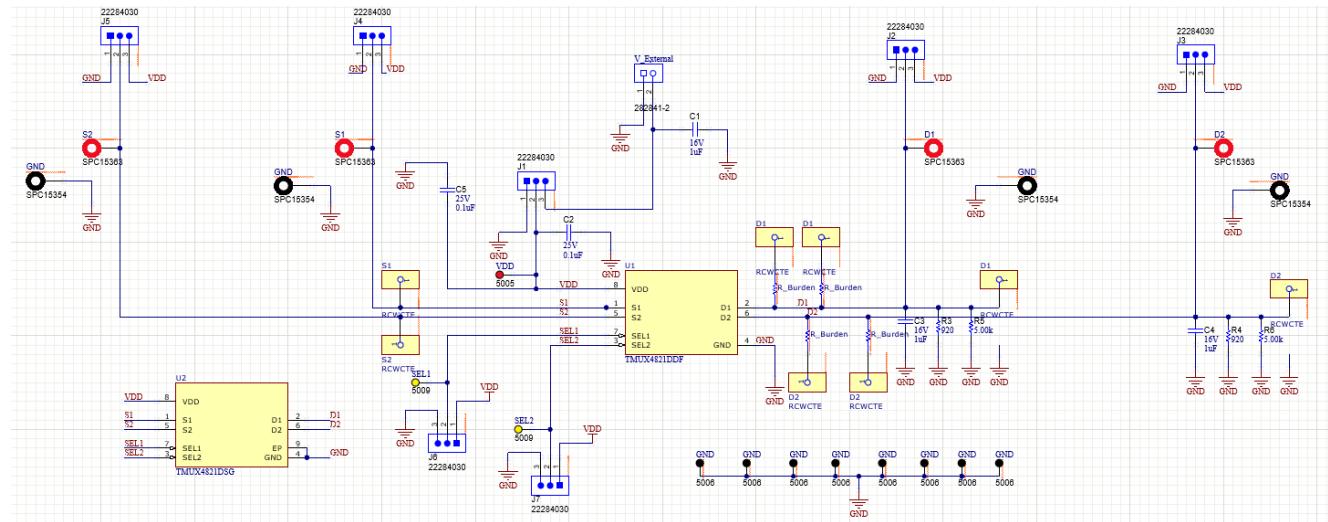

#### 3.1 回路図

図 3-1. TMUX48XX-DSG-DDF-EVM の回路図

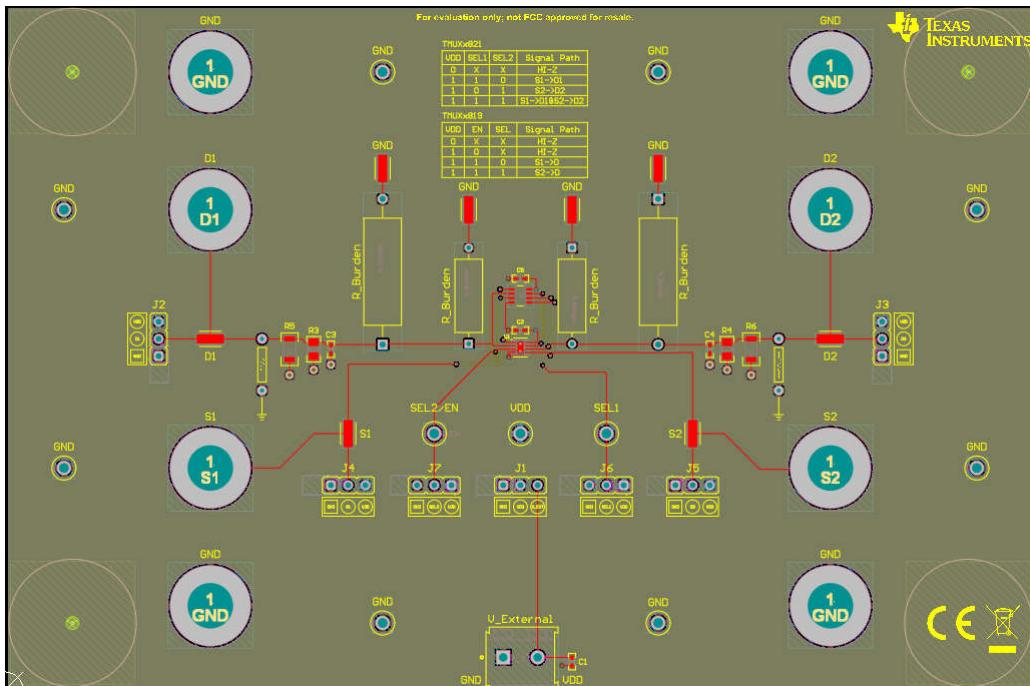

### 3.2 PCB のレイアウト

図 3-2. TMUX48XX-DSG-DDF-EVM の上層レイアウト

図 3-3. TMUX48XX-DSG-DDF-EVM の最下部レイアウト

### 3.3 部品表 (BOM)

表 3-1. 部品表

| 記号                   | 数量 | 値     | 説明                                                                                            | メーカー                 | 部品番号               |

|----------------------|----|-------|-----------------------------------------------------------------------------------------------|----------------------|--------------------|

| C1                   | 1  | 1uF   | コンデンサ、セラミック、1μF、16V、±10%、X5R、0402                                                             | Taiyo Yuden          | EMK105BJ105KVHF    |

| C2                   | 1  | 0.1uF | コンデンサ、セラミック、0.1μF、25V、±10%、X5R、0402                                                           | MuRata               | GRM155R61E104KA87D |

| S1、S2、D1、D2          | 4  |       | バナナ ジャック、半田付けラグ、赤、TH                                                                          | テンマ                  | GSPC15363          |

| S1、S2、D1、D2          | 8  |       | PC テスト ポイント メッキ表面実装タイプ                                                                        | KOA スピア              | RCWCTE             |

| GND                  | 4  |       | バナナ ジャック、半田付けラグ、ブラック、TH                                                                       | テンマ                  | SPC15354           |

| GND                  | 8  |       | テスト ポイント、コンパクト、ブラック、TH                                                                        | Keystone             | 5006               |

| J1、J2、J3、J4、J5、J6、J7 | 7  |       | コネクタ ジャンパー S2 (1 x 2) ポジションシャントコネクタ ブラック オープントップ 0.100 インチ (2.54mm) ゴールド HORTING.100 インチ ゴールド | Sullins              | QPC02SXGN-RC       |

| J1、J2、J3、J4、J5、J6、J7 | 7  |       | ヘッダ、2.54mm、3x1、錫、TH                                                                           | Molex                | 22284030           |

| P1、P2、P3、P4          | 4  |       | バンパー円筒形、ドーム径 0.720 インチ (18.30mm) ポリウレタン ブラック                                                  | Essentra コンポーネント     | RBS-37BK           |

| SEL1、SEL2            | 2  |       | テスト ポイント、コンパクト、イエロー、TH                                                                        | Keystone Electronics | 5009               |

| TMUX48XX-DSG-DDF-EVM | 1  |       | 熱転写プリンタブル ラベル、幅 0.650 インチ x 高さ 0.200 インチ、ロールあたり 10,000                                        | Brady                | THT-14-423-10      |

| U2                   | 1  |       | TMUX4821                                                                                      | テキサス・インスツルメンツ        | TMUX4821DSG        |

| V_External           | 1  |       | 端子台、2 x 1、5.08mm、TH                                                                           | TE の接続               | 282841-2           |

| VDD                  | 1  |       | テスト ポイント、コンパクト、レッド、TH                                                                         | Keystone Electronics | 5005               |

| C3、C4                | 0  | 1uF   | コンデンサ、セラミック、1μF、16V、±10%、X5R、0402                                                             | Taiyo Yuden          | EMK105BJ105KVHF    |

| C5                   | 0  | 0.1uF | コンデンサ、セラミック、0.1μF、25V、±10%、X5R、0402                                                           | MuRata               | GRM155R61E104KA87D |

| R3、R4                | 0  | 920 Ω | RES、920、0.1%、0.125W、0805                                                                      | Yageo America        | RT0805BRD07920RL   |

| R5、R6                | 0  | 5kΩ   | 抵抗、5.00k、0.1%、0.25W、1206                                                                      | 最先端の技術               | D55342E07B05B0TTR  |

| R_Burden             | 0  | 250 Ω | 250 Ω ±0.1% 1W スルー ホール抵抗器 軸難燃性コーティング、耐湿性、安全金属皮膜                                               | Vishay               | CMF60250R00BHEB    |

| R_Burden             | 0  | 45 Ω  | RES 卷線 45 Ω 1% 3W±20ppm/°C セラミック高温 SIL AXL スルーホール バルク                                         | Vishay               | RS02B45R00FE12     |

| U1                   | 0  |       | TMUX4821                                                                                      | テキサス・インスツルメンツ        | TMUX4821DDF        |

## 4 追加情報

### 4.1 商標

すべての商標は、それぞれの所有者に帰属します。

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適したテキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているテキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、[テキサス・インスツルメンツの販売条件](#)、または [ti.com](http://ti.com) やかかるテキサス・インスツルメンツ製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2025, Texas Instruments Incorporated

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適した TI 製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月