## Design Guide: TIPA-020007

# AMD® Versal™ AI エッジシリーズ Gen 2 向け電源供給の概念 実証設計

## 説明

この概念実証では、TI のレギュレータ集積回路 (IC) から 2VE3858 デバイスに必要な電源レールを供給する方法を紹介します。この設計手法は、AMD® 規格と整合しており、統合電源レールを最小化します。利用可能なすべての電源統合オプションについては、[AMD の電源設計マネージャ \(PDM\)](#) ツールを参照してください。どのようなアプリケーションでも、電力を推定するときに実装された PDM を使用します。

## リソース

[TIPA-020007](#)

[LM74910-Q1](#)

[LP8764-Q1](#)

[TPS62893-Q1](#)

[TPS6594-Q1](#)

デザイン フォルダ

プロダクト フォルダ

プロダクト フォルダ

プロダクト フォルダ

プロダクト フォルダ

テキサス・インスツルメンツの™ E2E サポート エキスパートにお問い合わせください。

## 特長

- 2VE3858 デバイスをサポートするために必要な設計上の考慮事項とパワー ツリーのデザインの詳細を示します

- AMD Versal™ AI Edge Series Gen 2 および AMD Versal Prime Series Gen 2 シリーズの他のデバイスに対しても、わずかな修正でパワー ツリー設計の基盤として利用できます

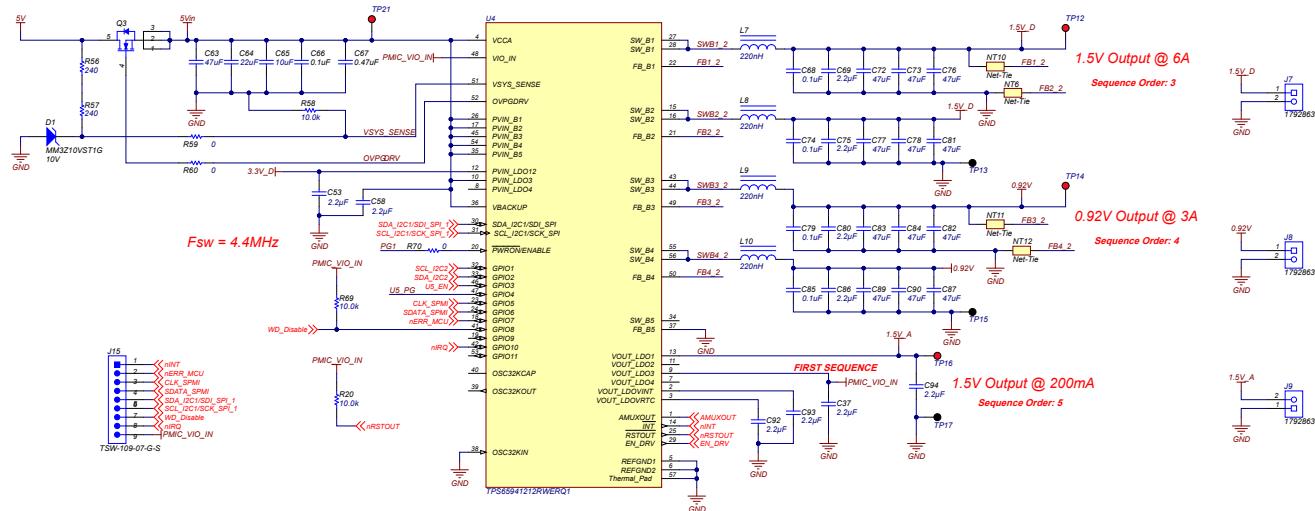

- 2VE3858 のレールの電源シーケンスは、電源管理 IC (PMIC) である TPS6594-Q1 によって制御されます

- TPS6594-Q1 デバイスの GPIO 出力を使用して、TPS6594-Q1、LP8764-Q1、または TPS62893-Q1 デバイスを制御し、電源シーケンスを実行できます

## アプリケーション

- 自動運転モジュール

- 車内監視 ECU

- フロント カメラ

- ミラー代替 / カメラミラー システム

- サラウンド ビュー システムの ECU

## 1 システムの説明

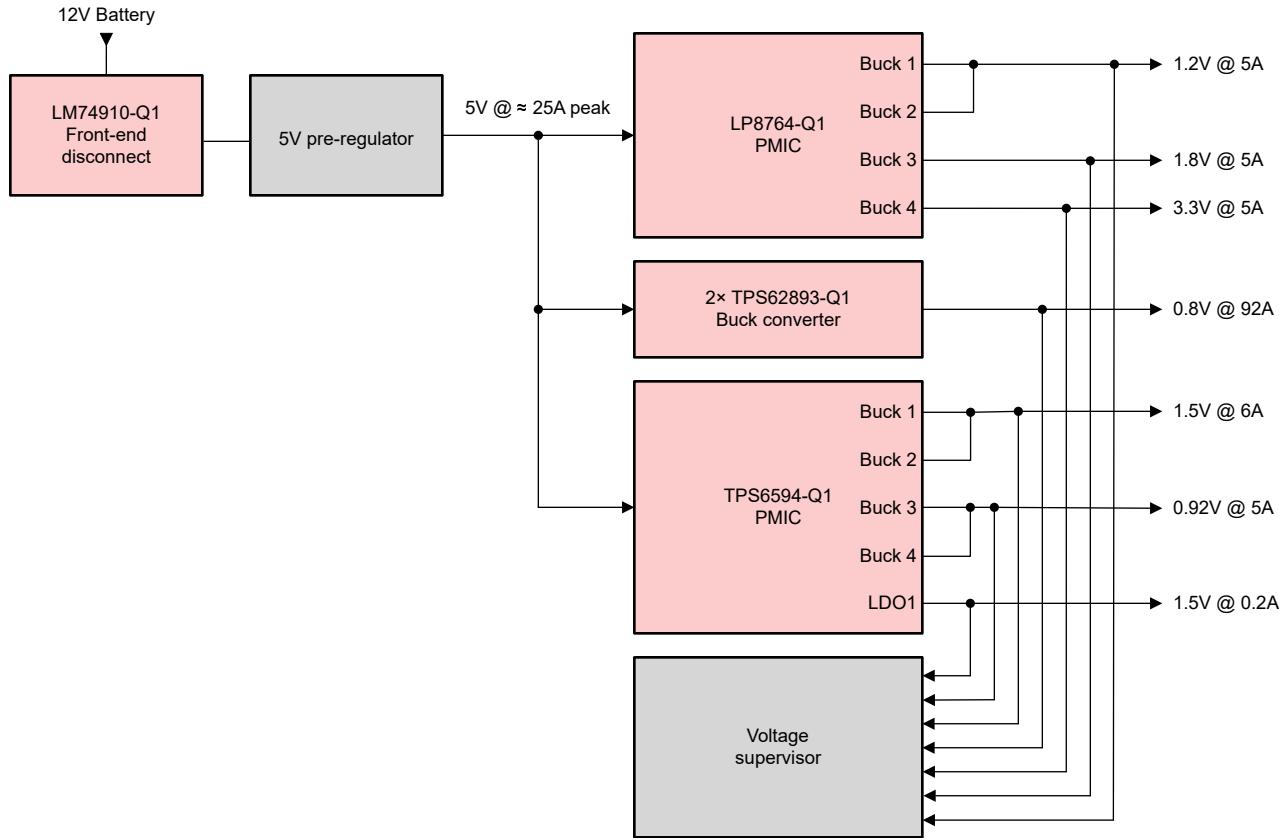

このシステムの最初の電源は、バッテリまたは電源（通常  $8\text{Vin} \sim 18\text{Vin}$  の範囲内）であり、約 150W の電力を供給できます。

電源は、複数の安全機能を備えたプログラム可能な電子安全スイッチとして機能する、LM74910-Q1 集積回路 (IC) によって制御されるオプションのフロント エンド保護 (FEP) サブ回路に供給されます。

FEP に続いているのは「5V プリレギュレータ」と呼ばれる降圧コンバータであり、高電圧入力から安定化された 5V の電圧を生成します。この 5V レールは、2VE3858 デバイスの各電源レールに必要な電圧を調整する、主なポイントオブロード (POL) コンバータに電力を供給します。

2 個の TPS62893-Q1 レギュレータ IC を 2 相構成で使用し、メインコアレールに電力を供給します。TPS6594-Q1 および LP8764-Q1 パワー マネージメント IC (PMIC) は、他のレールのために使用されます。

また、マルチレール電圧スーパーバイザ IC もあり、すべてのレールがそれぞれの許容電圧レベル内にある場合に監視して通信を行います。さらに、機能安全の目的でマルチレール電圧スーパーバイザ IC が搭載されています。

## 2 電力段のパラメータ

表 2-1 は、2VE3858 の各電源レールに関する仕様を示しており、それぞれの電圧と許容誤差、負荷電流、シーケンス順序を含みます。このリファレンス デザインは、AI エッジ シリーズの電力供給仕様すべてを満たすように設計されています。

表 2-1. 2VE3858 デバイス電源レール仕様

| シーケンス | レール名                                                                                                                  | 電圧 (V) | DC 許容誤差 | AC 過渡マージン | ステップ負荷 (%) | 電流 (A) |

|-------|-----------------------------------------------------------------------------------------------------------------------|--------|---------|-----------|------------|--------|

| 2     | VCC_MIPI、VCC_LPD、<br>VCC_FPD、VCC_USB2、<br>VCC_PAUX、VCC_USB3、<br>VCC_RAM、VCC_SOC、<br>VCC_IO、VCC_MMD、<br>VCC_AIE、VCCINT | 0.8    | ±1%     | ±17mV     | 33         | 92     |

| 3     | VCCAUX、VCCAUX_PLL、<br>VCCAUX_LPD、<br>VCCAUX_SMON                                                                      | 1.5    | ±1%     | ±2%       | 100        | 6      |

| 4     | VGTYP_AVCC、<br>VGTYP_MMI_AVCC                                                                                         | 0.92   | ±1%     | ±2%       | 70         | 5      |

| 5     | VGTYP_AVCCAUX、<br>VGTYP_MMI_AVCCAUX                                                                                   | 1.5    | ±1%     | ±2%       | 70         | 0.2    |

| 6     | VGTYP_AVTT、<br>VGTYP_MMI_AVTT                                                                                         | 1.2    | ±1%     | ±2%       | 70         | 5      |

| 1     | VCCIO_PAUX、<br>VCCREG_USB2、<br>VCCIO_USB3、VCCO_HDIO、<br>VCCIO_MIPI、VCCO_PSIO                                          | 1.8    | ±1%     | ±2%       | 100        | 4.3    |

| 1     | VCCO_PSIO、VCCO_HDIO、<br>VCCIO_USB2                                                                                    | 3.3    | ±1%     | +2/-4%    | 100        | 3.8    |

図 2-1 に、2VE3858 デバイスパワー ツリーを示します。

図 2-1. 2VE3858 デバイス最小レール構成のパワー ツリー

## 3 シーケンシング

### 3.1 スタートアップ

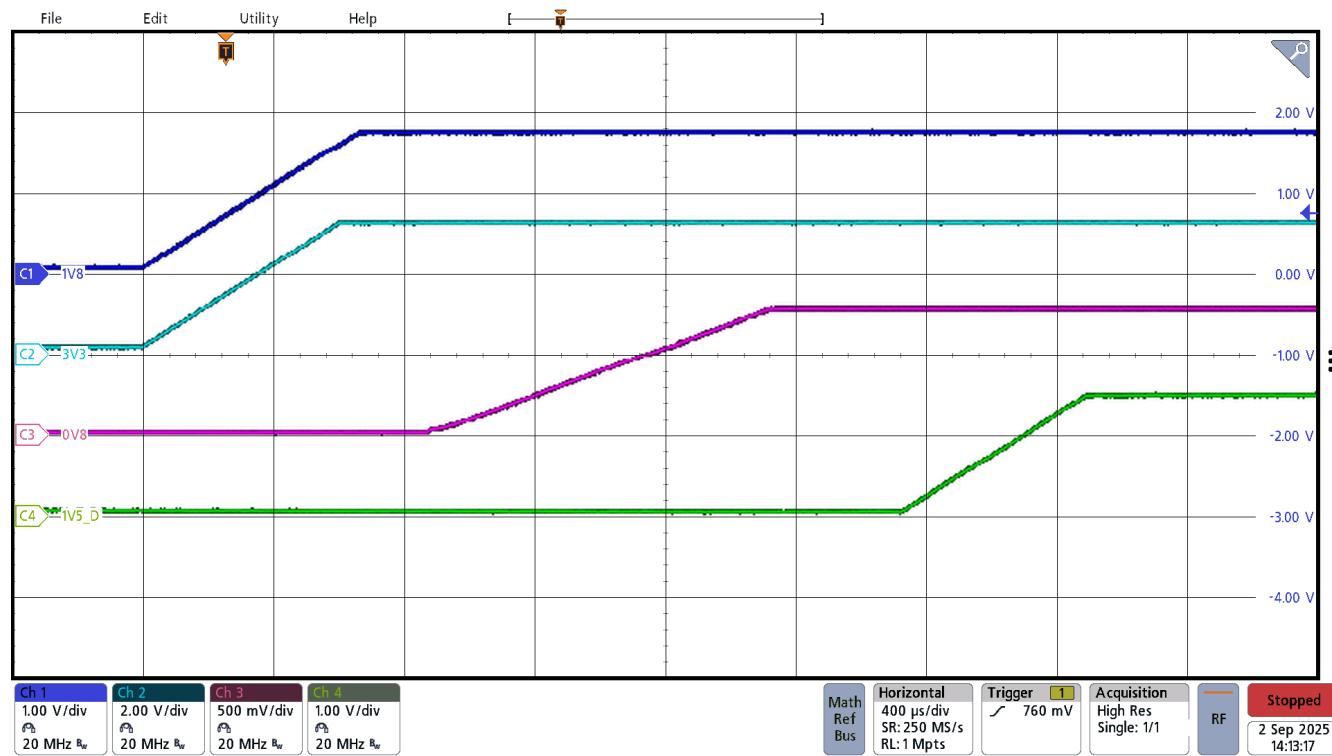

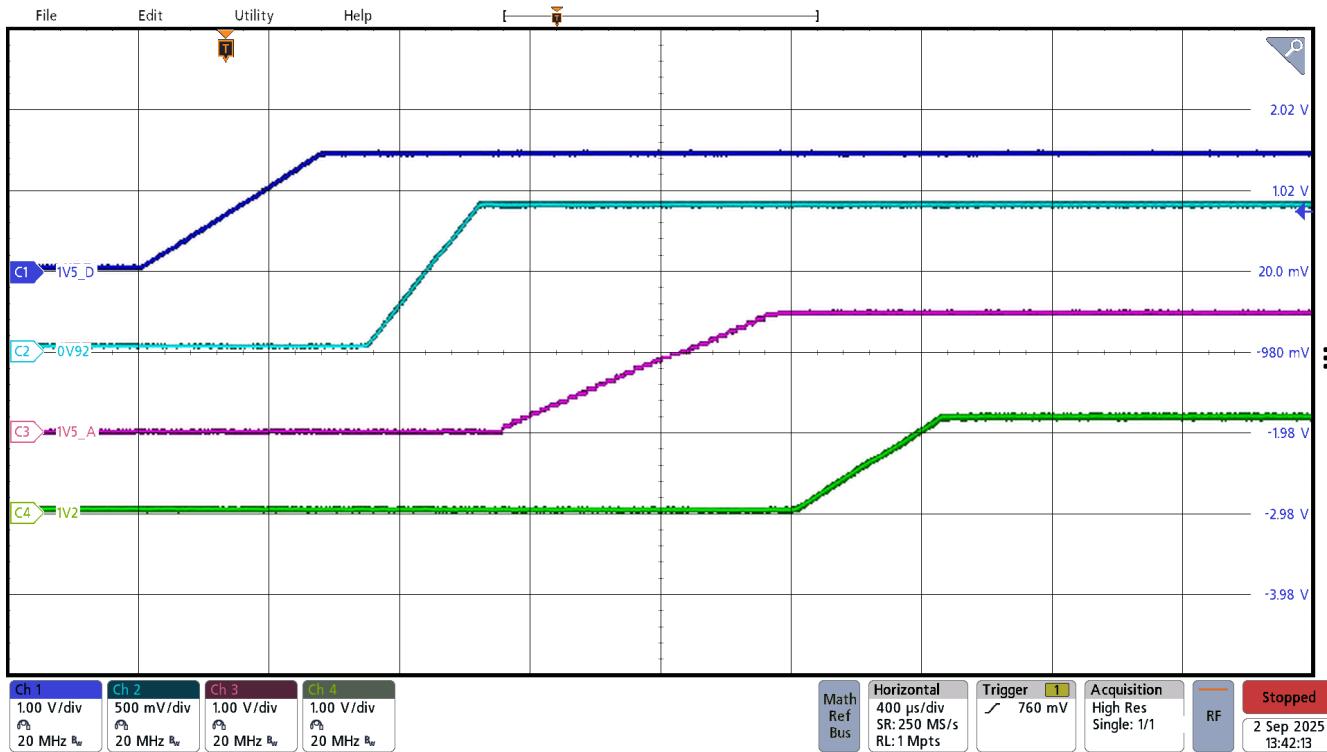

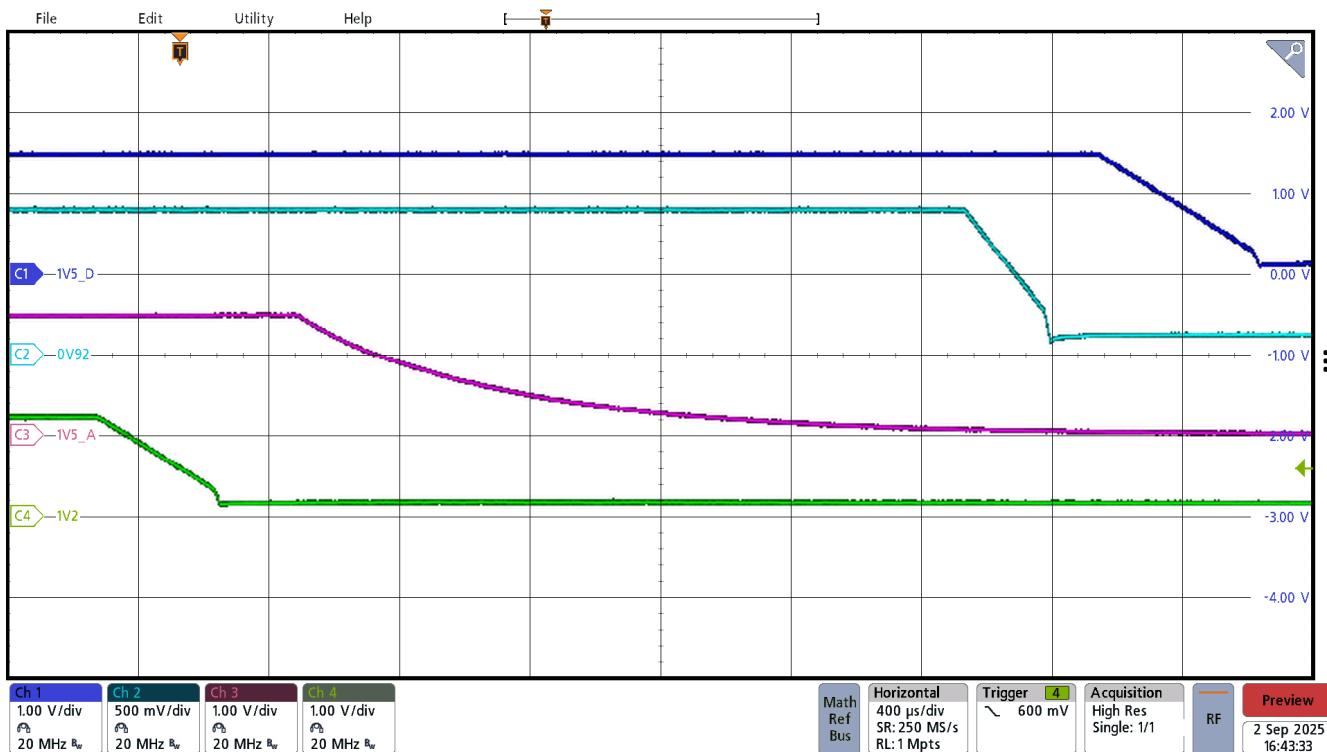

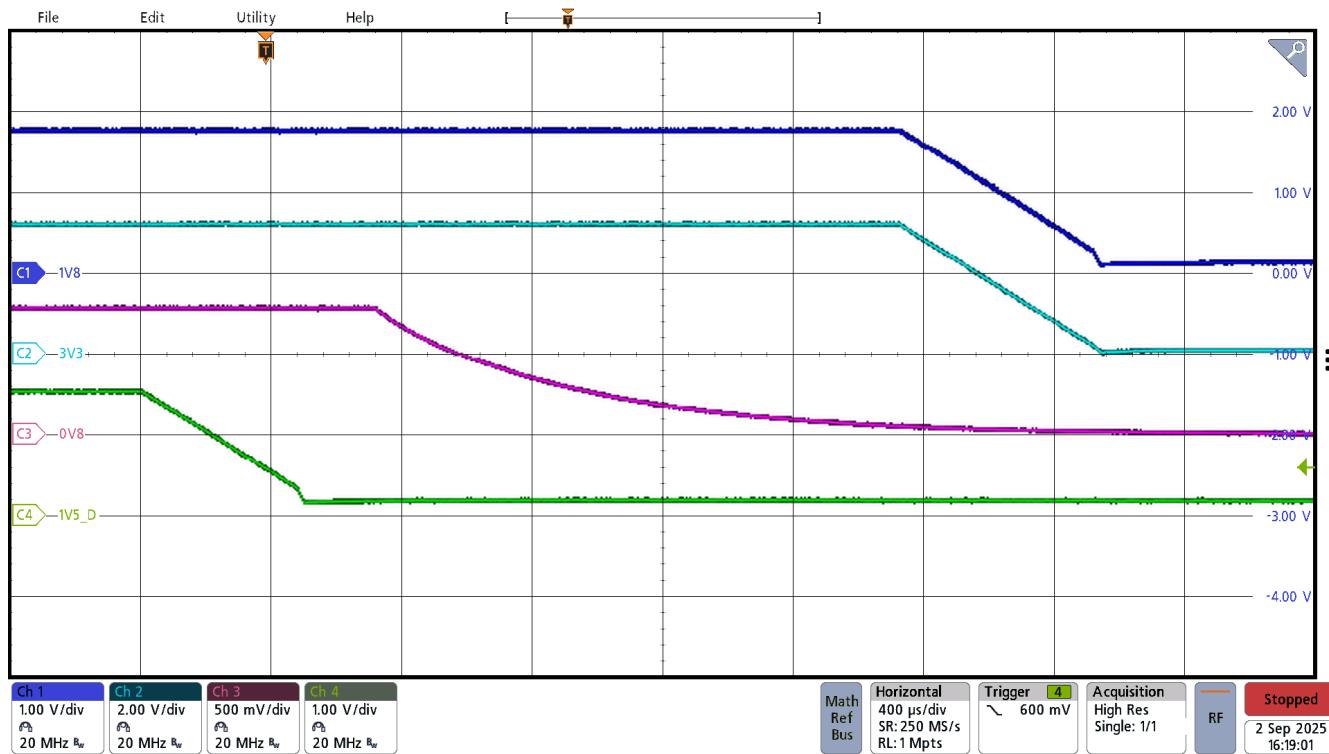

図 3-1 と図 3-2 に、電源レールのスタートアップのタイミングを示します

図 3-1. 2VE3858 デバイス POL レールのスタートアップ シーケンス 1

図 3-2. 2VE3858 デバイス POL レールのスタートアップ シーケンス 2

### 3.2 シャットダウン

図 3-3 と図 3-4 に、電源レールのシャットダウンのタイミングを示します。

図 3-3. 2VE3858 デバイス POL レールのシャットダウン シーケンス 1

図 3-4. 2VE3858 デバイス POL レールのシャットダウン シーケンス 2

## 4 回路図

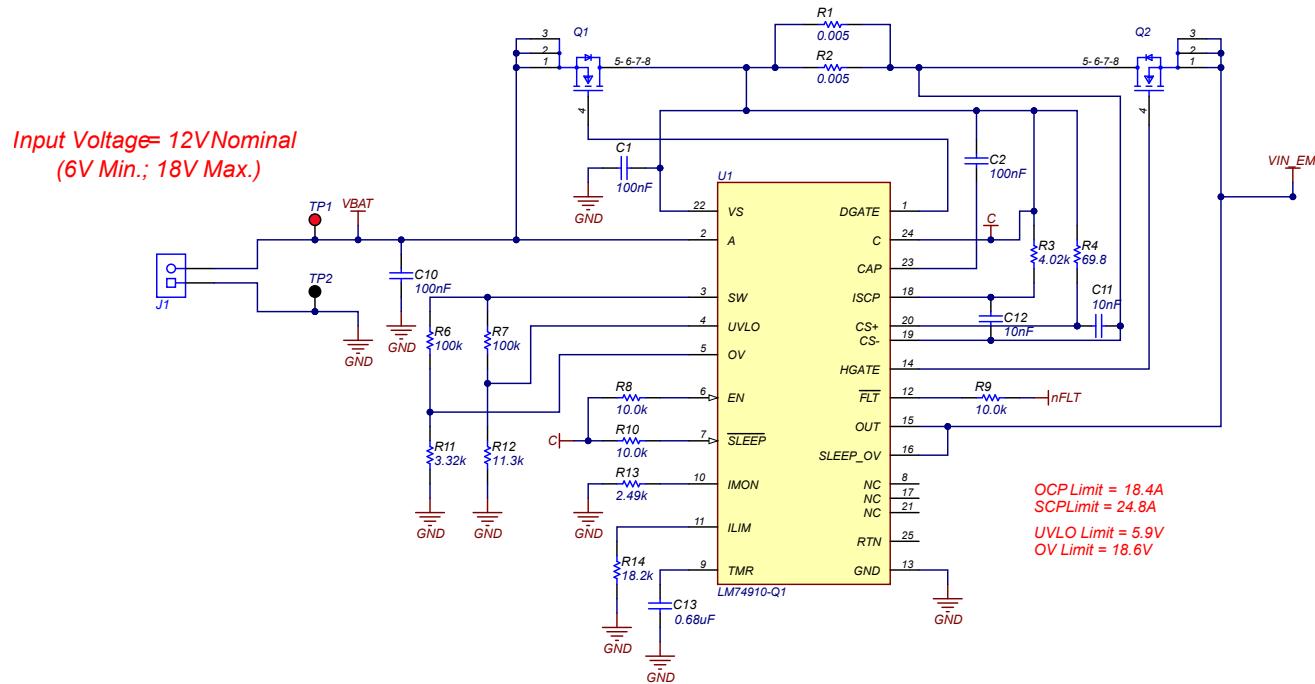

図 4-1 に、重要な部品と LM74910-Q1 の回路図を示します。レイアウトのガイダンスについては、特定のデバイスのデータシートと EVM ユーザー ガイドをご覧ください。

図 4-1. LM74910-Q1 のフロント エンド保護の回路図

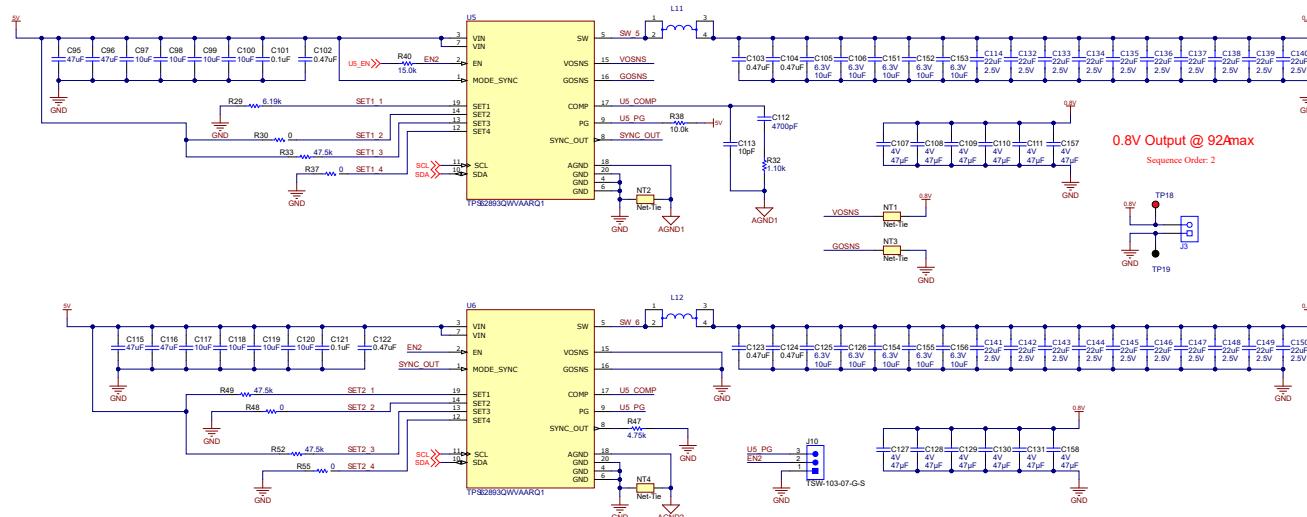

図 4-2 は、重要なコンポーネントを含むデュアルフェーズ TPS62893-Q1 の回路図を示しています。レイアウトのガイダンスについては、特定のデバイスのデータシートと EVM ユーザー ガイドをご覧ください。

図 4-2. TPS62893-Q1 のコア レールの回路図

図 4-3 に、重要な部品と TPS6594-Q1 の回路図を示します。レイアウトのガイダンスについては、特定のデバイスのデータシートと EVM ユーザー ガイドをご覧ください。

図 4-3. TPS6594-Q1 の複数のペリフェラル レールの回路図

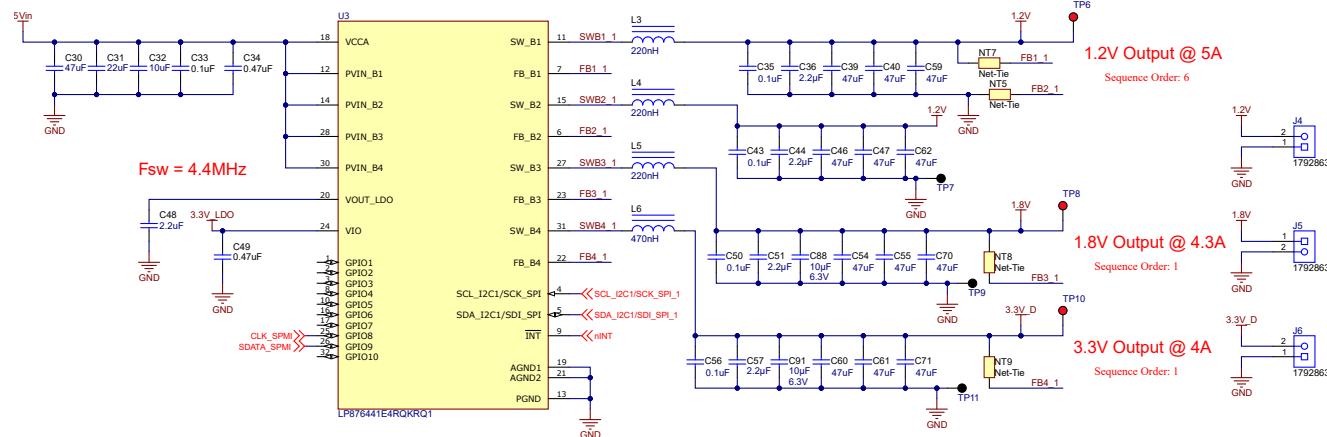

図 4-4 に、重要な部品と LP8764-Q1 の回路図を示します。レイアウトのガイダンスについては、特定のデバイスのデータシートと EVM ユーザー ガイドをご覧ください。

図 4-4. LP8764-Q1 の複数のペリフェラル レールの回路図

## 5 フロントエンド保護

回路のメイン入力、主電源接続の LM74910-Q1 のフロントエンド保護 (FEP) 回路があります。この FEP コントローラには、次のような機能があります：

- 逆極性保護

- 過電流保護 (OCP) 接続解除機能 (R1, R2, R4, R16 の各部品値を使用) をプログラム可能

- プログラマブルな低電圧切断保護および誤動作防止保護 (R2 および R9 分圧器の値を使用)

- プログラマブルな過電圧切断保護およびロックアウト保護機能 (R6 および R11 分圧器の値を使用)

- プログラム可能な保護遅延時間および故障遅延時間 (C13 を介して、TMR ピンから GND へ接続)

- 電流モニタリング (R1, R2, R4、および R13 の部品値を介しています)

LM74910-Q1 以外の、フロントエンド保護 IC では他のオプションも利用できます。[テキサスインストゥルメンツの Web サイト](#)も参照し、[理想ダイオード/OR コントローラセクション](#)で代替品を検索してください。

## 6 複数のペリフェラルレール降圧コンバータ PMIC

TPS6594-Q1 は、4 つの柔軟なマルチフェーズ構成可能な降圧レギュレータに加えて、さらに 1 つの降圧レギュレータと 4 つの LDO を備えた電源管理 IC (PMIC) です。TPS6594-Q1 デバイスは、入力電源の電圧モニタリング、入力過電圧保護、すべての降圧レギュレータおよび LDO レギュレータ出力の電圧モニタリング、レジスタおよびインターフェイスの CRC、電流制限、短絡保護、サーマル事前警告、過温シャットダウンなどの保護および診断機能を備えています。

LP8764-Q1 は、4 つの降圧型 DC/DC コンバータコアを備えたパワー マネジメント IC (PMIC) であり、1 系統の 4 フェーズ出力から 4 系統の 1 フェーズ出力まで、5 種類のフェーズ構成に設定可能です。

両方の PMIC は、不揮発性メモリ (NVM) を使用して、電源シーケンスや出力電圧、GPIO 設定などのデフォルト構成を制御します。NVM は、外部からプログラムしなくとも起動できるように事前にプログラムされています。デバイスのレジスタマップに格納されているほとんどの静的構成は、SPI または I2C インターフェイスを介して変更でき、さまざまなシステム要件に合わせてデバイスを構成できます。エラーが検出された場合にパワーアップ シーケンスを止めるため、NVM はビット整合性エラー検出機能 (CRC) を備えており、システムが未知の状態で起動することを防止します。

## 7 低電圧、大電流、コアレール降圧コンバータ

TPS62893-Q1 は、I2C インターフェイスおよび差動リモートセンスを備えた同期整流型降圧 DC/DC コンバータです。このデバイスをスタック モードで動作させることで、大きな出力電流を供給することや、消費電力を複数のデバイスに分散することができます。スタック動作では、コンバータの動作周波数が同期され、共通の補償信号を共有し、位相をずらして重い負荷に電力を供給します。I2C 互換インターフェイスを使うと、入力電圧、出力電圧、出力電流、温度の遠隔測定データなど、複数の制御、監視、警告機能を備えています。4 本の SET ピンを使用して、起動前にデフォルト設定をプログラムできます。

## 8 電圧監視

プログラム可能な電圧スーパーバイザが含まれています。このデバイスには、I2C を使用してプログラムできる多数のレジスタが搭載されています。プログラム可能なパラメータには、電圧スレッショルド レベル、ヒステリシス レベル、グリッチ耐性時間があります。

## 9 まとめ

このデザインは、LM74910-Q1、TPS62893-Q1、TPS6594-Q1、LP8764-Q1 IC を使用して、2VE3858 デバイスの電力要件を満たします。TPS6594-Q1 および LP8764-Q1 PMIC の I<sub>2</sub>C 制御により、高度な制御が可能となり、1 本のシリアル通信ラインを介してシステムを構成できます。AI Edge シリーズの他のデバイス向けにも、電流要件、使用するペリフェラル、電源シーケンスなど、実際の使用ケースに応じて、この電源設計をカスタマイズおよび最適化することができます。

## 10 ドキュメントのサポート

1. テキサス・インスツルメンツ、[『LM74910-Q1: 車載対応、サーキットブレーカと 200kHz ACS と低電圧保護機能と過電圧保護機能搭載、理想ダイオード』](#)製品ページ

2. テキサス・インスツルメンツ、[『TPS62893-Q1: 車載対応、2.8V ~ 6V 入力、50A 高速過渡、スタッカブル、同期整流降圧コンバータ』](#)製品ページ

3. テキサス・インスツルメンツ、[『TPS6594-Q1: 車載対応、5 個の降圧レギュレータと 4 個の低ドロップアウトレギュレータ搭載、2.8V ~ 5.5V PMIC』](#) 製品ページ

4. テキサス・インスツルメンツ、[『LP8764-Q1: 車載対応 SoC 向け、4 個の 5A 出力、または 1 個の 20A 出力を供給するマルチフェーズ降圧コンバータ PMIC』](#) 製品ページ

## 商標

テキサス・インスツルメンツの™ is a trademark of Texas Instruments.

Versal™ is a trademark of Advanced Micro Devices, Inc.

AMD® is a registered trademark of Advanced Micro Devices, Inc.

すべての商標は、それぞれの所有者に帰属します。

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適したテキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているテキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、[テキサス・インスツルメンツの販売条件](#)、または [ti.com](#) やかかるテキサス・インスツルメンツ製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2025, Texas Instruments Incorporated

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Webツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適したTI製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているTI製品を使用するアプリケーションの開発の目的でのみ、TIはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TIや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TIおよびその代理人を完全に補償するものとし、TIは一切の責任を拒否します。

TIの製品は、[TIの販売条件](#)、[TIの総合的な品質ガイドライン](#)、[ti.com](#)またはTI製品などに関連して提供される他の適用条件に従い提供されます。TIがこれらのリソースを提供することは、適用されるTIの保証または他の保証の放棄の拡大や変更を意味するものではありません。TIがカスタム、またはカスタマー仕様として明示的に指定していない限り、TIの製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TIはそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025年10月