## Design Guide: TIDA-010982

# フィールドトランスマッタ プラットフォーム: 4mA ~ 20mA ループ電源インターフェイスのリファレンス デザイン

## 説明

このリファレンス デザインでは、2 線式ループ電源センサ用の 4 ~ 20mA インターフェイスの実装例を示します。この設計を使用すると、1.8V 信号チェーンを使用した、低消費電力アプリケーションに似た環境で、AFE881H1 と AFE882H1 を評価できます。AFE881H1 と AFE882H1 は、高精度の 16 ビット DAC と HART® モデムを内蔵しています。このリファレンス デザインは、マイコンに接続するためのピン ヘッダ上で、シリアル ペリフェラル インターフェイス (SPI) と UART (Universal Asynchronous Receiver-Transmitter) インターフェイスを提供します。このピン ヘッダは、マイコンに電源を供給するために 3.3V と 1.8V を供給するほか、ADC に使用する 1.25V のリファレンス電圧を供給します。

## リソース

TIDA-010982

デザイン フォルダ

AFE881H1、AFE882H1

プロダクト フォルダ

OPA391、TPS7A03

プロダクト フォルダ

REF35、TVS3301

プロダクト フォルダ

TMUX1219、SN74LV8T165

プロダクト フォルダ

テキサス・インストゥルメンツの E2E™ サポート エキスパートにお問い合わせください。

## 特長

- 2 線式ループ電源センサ用の 4 ~ 20mA ループ インターフェイスの実装

- 包括的な 1.8V 信号チェーンにより、低消費電力と高精度を維持可能

- AFE88xH1 リファレンス内蔵、HART モデム搭載、16 ビット DAC

- 電源出力 (リファレンス電圧 1.8V、3.3V、1.25V)、SPI、UART インターフェイスを供給するマイコン (MCU) インターフェイス

## アプリケーション

- 流量トランスマッタ

- レベルトランスマッタ

- 圧力トランスマッタ

- 温度トランスマッタ

- アナログ出力モジュール

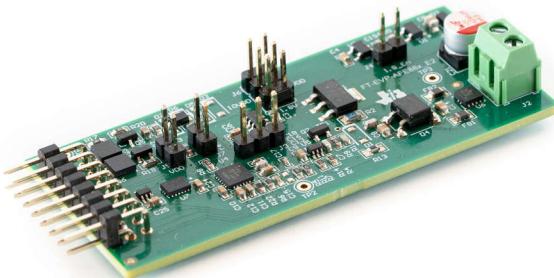

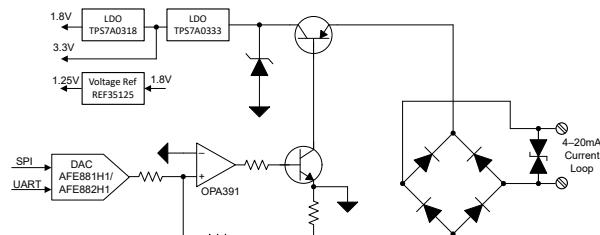

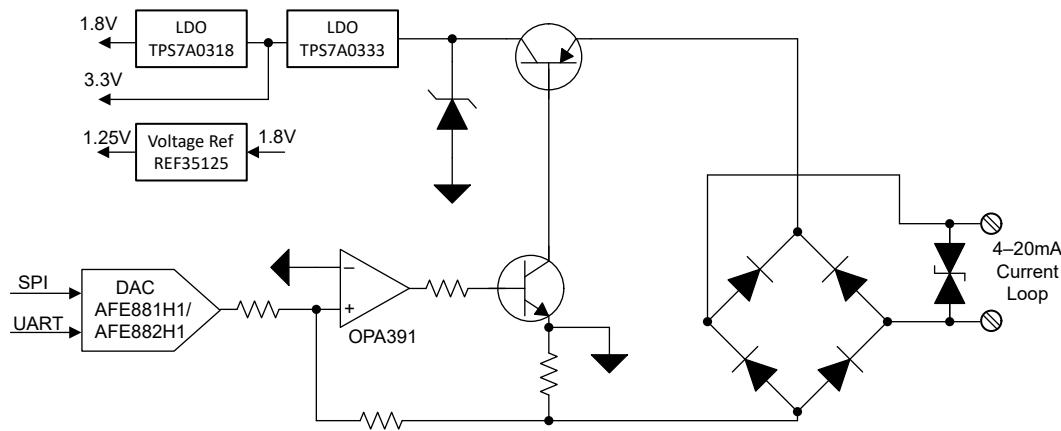

## 1 システムの説明

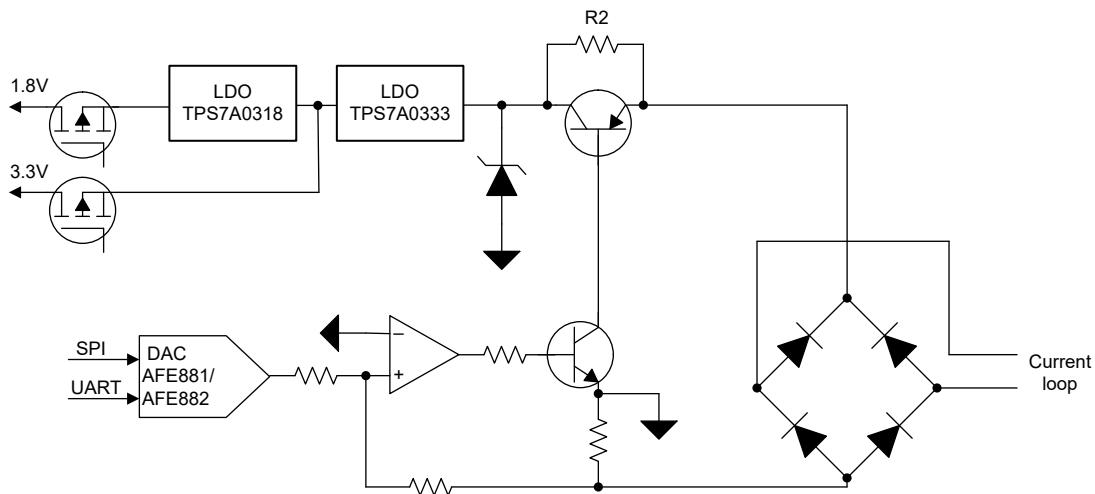

このリファレンス デザインは、ループ電源センサ用の 4 ~ 20mA 電流ループ インターフェイスを実装しています。この設計には、16 ビット DAC である AFE881H1 または AFE882H1 のいずれかが組み込まれています。DAC 出力電圧は OPA391 オペアンプを駆動し、電圧を電流に変換します。

この設計には、1.8V または 3.3V の出力オプションを備えた電源が統合されています。構成設定により、基板上のアナログ回路および接続された MCU の電源として 1.8V と 3.3V のどちらを使用するかが決まります。システムの電力効率を高めるために、低  $I_Q$  の低ドロップアウト (LDO) レギュレータ (TPS7A0333 および TPS7A0318) が使用され、安定した効率的な電力出力を維持します。

この設計には、MCU 用のディスクリート P チャネル金属酸化膜半導体電界効果トランジスタ (PMOSFET) CSD25404 パワー スイッチが搭載されています。このパワースイッチは、MCU に接続されたコネクタ上の 1.8V と 3.3V 電源レールを制御します。追加のバブルク容量により、ループ制限を超える起動電流がサポートされます。このコンデンサは、低消費電力モードに移行する前に MCU の初期化動作に電力を供給します。

### 1.1 主なシステム仕様

| パラメータ          | 仕様        |

|----------------|-----------|

| ループ電源電圧        | 8V ~ 30V  |

| ループ電流範囲        | 3mA~24mA  |

| 分解能            | 16 ビット    |

| RMS ノイズ        | 0.5µA 未満  |

| ピークツーピークノイズ    | 3µA 未満    |

| セトリング タイム      | 1ms 未満    |

| 電源出力           | 3.3V、1.8V |

| 電源出力電流         | 2mA       |

| リファレンス電圧出力     | 1.25V     |

| MCU へのインターフェイス | SPI、UART  |

## 2 システム概要

### 2.1 ブロック図

図 2-1. TIDA-010982 のブロック図

### 2.2 設計上の考慮事項

この設計は、フィールドトランシッタとセンサ向けの 4mA ~ 20mA 出力段を実装しています。AFE881H1 と AFE882H1 は、最大 16 ビットの高分解能で D/A 変換機能を統合しています。低消費電力であるため、システムはループ電源から直接動作できます。さらに、この AFE には HART 通信機能を有効にするモジュールが内蔵されています。AFE881H1 を使用すれば、設計全体は 1.8V 単一電源で動作可能です。

入力部のグレッツ ブリッジにより逆極性保護が実現し、どちらの極性でも動作が可能になります。過電圧保護は TVS3301 TVS ダイオードによって提供され、過剰な電圧レベルから保護します。フェライトビーズによって高周波ノイズが低減されます。

電流のレギュレーションは、パストランジスタとツェナーダイオード、および最初の LDO と組み合わせて行われます。このシステムでは一部の電流を消費し、残りの大部分をツェナーダイオードで消費するため、消費電力を複数のデバイス間で分散し、熱的ストレスを最小限に抑えることができます。専用のオペアンプは、DAC の出力電圧をループ電流に変換します。

システムの各部品には、LDO から供給される 2 つの電源 (1.8V および 3.3V) を使用できます。安定した 1.25V のリファレンス電圧が基板回路上で直接供給されます。リファレンス電圧の出力は、ピンヘッダ経由でも利用できます。

### 2.3 主な使用製品

#### 2.3.1 TPS7A03

TPS7A03 は、非常に優れた過渡性能で 200mA を供給できる超小型超低静止電流の低ドロップアウトレギュレータ (LDO) です。

TPS7A03 は、 $I_Q$  がわずか 200nA と非常に低く、静止電流の低さが重要となる用途に特化して設計されています。このデバイスはドロップアウトモードでも小さな  $I_Q$  消費を維持するため、バッテリ動作時間をさらに延長できます。シャットダウンまたはディセーブルモードでは、わずか 3nA の  $I_Q$  しか消費しないため、バッテリの保存寿命を延ばすのに役立ちます。

TPS7A03 は 0.8V ~ 5.0V の出力範囲を持ち、50mV 刻みで設定可能なため、近年のマイコン (MCU) の低いコア電圧に対応できます。

TPS7A03 は、スマートイネーブル回路を備え、内部で制御されるプルダウン抵抗により、EN ピンをフローティング状態のままにしても LDO をディセーブル状態に維持します。これにより、EN ピンのプルダウンに使用する外付け部品を最小限に抑えることができます。この回路は、デバイスが有効になっている時に外付けのプルダウン回路を通じて流れる電流を最小限に抑える助けにもなります。

### 2.3.2 REF35

REF35 は、ナノパワー、低ドリフト、高精度シリーズのリファレンス デバイスのファミリです。REF35 ファミリは、 $\pm 0.05\%$  の初期精度と 650nA の標準消費電力を特長としています。このデバイスの温度係数 (12ppm/ $^{\circ}\text{C}$ ) と長期安定性 (1000 時間で 40ppm) は、システムの安定性と信頼性の向上に役立ちます。低消費電力と高精度の仕様を組み合わせて、広範な携帯型 / 低-電流アプリケーション向けに設計されています。

REF35 は、3.3ppm<sub>p-p</sub> ノイズおよび 20ppm/mA のロードレギュレーションで、最大 10mA の電流を供給します。この機能セットにより、REF35 は高精度センサと 12~16 ビットデータコンバータ向けの強力な低ノイズで高精度の電源を実現します。

### 2.3.3 TVS3301

TVS3301 デバイスは、最大 27A の IEC 61000-4-5 フォルト電流をシャントし、大電力の過渡現象や落雷からシステムを保護します。このデバイスは、42Ω のインピーダンスで結合した 1kV IEC 61000-4-5 開路電圧の一般的な産業用信号線 EMC 要件に適合しています。TVS3301 は帰還機構を使用して、フォルト中の正確なフラット クランプを提供し、システムがさらされる電圧を、従来型の TVS ダイオードよりも低く保ちます。厳格な電圧レギュレーションにより、設計者は電圧許容誤差の狭いシステム部品を安心して選択できるため、堅牢性を損なうことなくシステムのコストと複雑さを低減できます。TVS3301 は  $\pm 33\text{V}$  の範囲で動作するため、逆配線に対する保護を必要とするシステムでの動作も可能です。

さらに、TVS3301 はスペースの制約が厳しいアプリケーション用に設計された小型の SON フットプリントで供給されるため、標準の SMA および SMB パッケージと比較して大幅なサイズ低減が可能です。リーク電流と容量が小さいため、保護するラインへの影響も最小限です。製品のライフサイクル全体にわたり堅牢な保護を提供するため、テキサス インスツルメンツは TVS3301 をテストし、125°Cで 5000 回の反復サージに対してデバイス性能に変化がないことを確認しています。

### 2.3.4 OPA391

OPA391、OPA2391、OPA4391 (OPAx391) デバイスは、高帯域 (1MHz) と非常に低い静止電流 (24μA) を高精度アンプに独自に組み合わせた製品です。これらの機能とレールツー レール入出力を組み合わせることで、これらのデバイスは高ゲイン、低消費電力のアプリケーションで非常に優れた選択肢になります。10fA という非常に低い入力バイアス電流、わずか 45μV のオフセット (最大値)、および 1.2μV/ $^{\circ}\text{C}$  の温度ドリフトにより、低消費電力要件を必要とするレシオメトリックおよびアンペロメトリック センサ フロントエンドで高い精度を維持できます。

OPAx391 は、テキサス インスツルメンツ独自の e-trim™ オペアンプ技術を採用しており、入力スイッチングやオートゼロ技術を必要とせずに、超低オフセットと低入力オフセットドリフトという独自の組み合わせを実現できます。CMOS ベースのテクノロジー プラットフォームは、最新の堅牢な出力段設計も採用しています。この設計は、高い出力容量に耐えることができ、一般的な低消費電力アンプで共通にみられる安定性の問題を緩和します。

### 2.3.5 AFE881H1

16 ビットの AFE881H1 および 14 ビットの AFE781H1 (AFEx81H1) は、HART 対応センサトランスマッタ アプリケーション向けに設計された、高集積度、高精度、超低消費電力の電圧出力 D/A コンバータ (DAC) です。

AFEx81H1 デバイスには、4mA ~ 20mA の 2 線式 (ループ電源) センサトランスマッタを設計するために必要な構成要素のほとんどが含まれています。これらの部品には、高精度な DAC に加えて、HART 認証周波数偏移変調 (FSK) モデム、10ppm/ $^{\circ}\text{C}$  の電圧リファレンス、および診断用 A/D コンバータ (ADC) が内蔵されています。内在的および機能安全上の問題に対応するには、外部の電圧電流変換と、電源のレギュレーションが必要です。

内蔵の診断 ADC は複数の内部ノードに多重化されており、自動的な自己ヘルス チェックを可能にしています。診断用 ADC、CRC フレーム エラー チェック、あるいはウインドウ付きのウォッチドッグ タイマから、いずれかの障害が検出された場合、本デバイスは (オプションとして) 割り込みの発行、あるいは標準の NAMUR 出力値またはユーザー指定のカスタム値に応じたフェイルセーフ状態への遷移、またはその両方を開始できます。

これらのデバイスは最小 1.71V の電源で動作し、最大静止電流は 220μA です。本デバイスの温度範囲は -40°C ~ +125°C で規定されていますが、-55°C ~ +125°C で機能することができます。

### 2.3.6 AFE882H1

16 ビットの AFE882H1 および 14 ビットの AFE782H1 (AFEx82H1) は、HART 対応のプロセス制御および産業用オートメーション アプリケーション向けに設計された高集積、高精度、超低消費電力の電圧出力 DAC です。

AFEx82H1 デバイスには、4mA ~ 20mA の 3 線式または 4 線式センサトランスマッタまたはアナログ出力モジュールを設計するために必要な構成要素のほとんどが含まれています。これらのデバイスには、高精度な DAC に加えて、HART® 準拠 FSK モデム、10ppm/°C の電圧リファレンス、および診断用 A/D コンバータ (ADC) が内蔵されています。内在的および機能安全上の問題に対応するには、外部の電圧電流変換と、電源のレギュレーションが必要です。

内蔵の診断 ADC は複数の内部ノードに多重化されており、自動的な自己ヘルスチェックを可能にしています。このチェックにより、内蔵のバイアス源や電源レギュレータ、電圧リファレンス、DAC 出力、ダイ温度に関するエラーや故障を検出でき、さらにオプションとして外部電圧源の問題も検出できます。診断用 ADC、CRC フレーム エラー チェック、あるいはウインドウ付きのウォッチドッグ タイマから、いずれかの障害が検出された場合、本デバイスは (オプションとして) 割り込みの発行、あるいはユーザー指定のフェイルセーフ状態への遷移、またはその両方を開始できます。

### 2.3.7 SN74LV8T165

SN74LV8T165 デバイスは、並列またはシリアル入力、シリアル出力の 8 ビットシフトレジスタです。このデバイスには、ロードデータとシフトデータという 2 つの動作モードがあり、SH/LD 入力で制御されます。出力レベルは電源電圧 (VCC) を基準としており、1.8V、2.5V、3.3V、5V の CMOS レベルをサポートしています。

入力は、低電圧 CMOS 入力の昇圧変換 (例: 1.2V 入力から 1.8V 出力、または 1.8V 入力から 3.3V 出力) をサポートするため、低スレッショルド回路を使って設計されています。また、5V 許容の入力ピンにより、降圧変換 (例: 3.3V から 2.5V 出力) が可能です。

### 2.3.8 TMUX1219

TMUX1219 は、汎用の CMOS (相補型金属酸化膜半導体) 単極双投 (SPDT) スイッチです。TMUX1219 は、SEL ピンの状態に基づいて、2 つのソース入力間のスイッチングを行います。1.08V ~ 5.5V の広い動作電源電圧範囲により、個人用電子機器からビルディング オートメーションまで、幅広い用途に使用可能です。このデバイスは、ソース (Sx) およびドレイン (D) ピンで、GND から VDD までの範囲の双方向アナログおよびデジタル信号をサポートします。消費電流が 4nA と低いため、携帯型アプリケーションで使用できます。

すべてのロジック入力のスレッショルドは 1.8V ロジック互換で、有効な電源電圧範囲で動作していれば、TTL と CMOS の両方のロジックと互換性が確実に得られます。フェイルセーフ ロジック回路により、電源ピンよりも先に制御ピンに電圧が印加されるため、デバイスへの損傷の可能性が避けられます。

### 3 システム設計理論

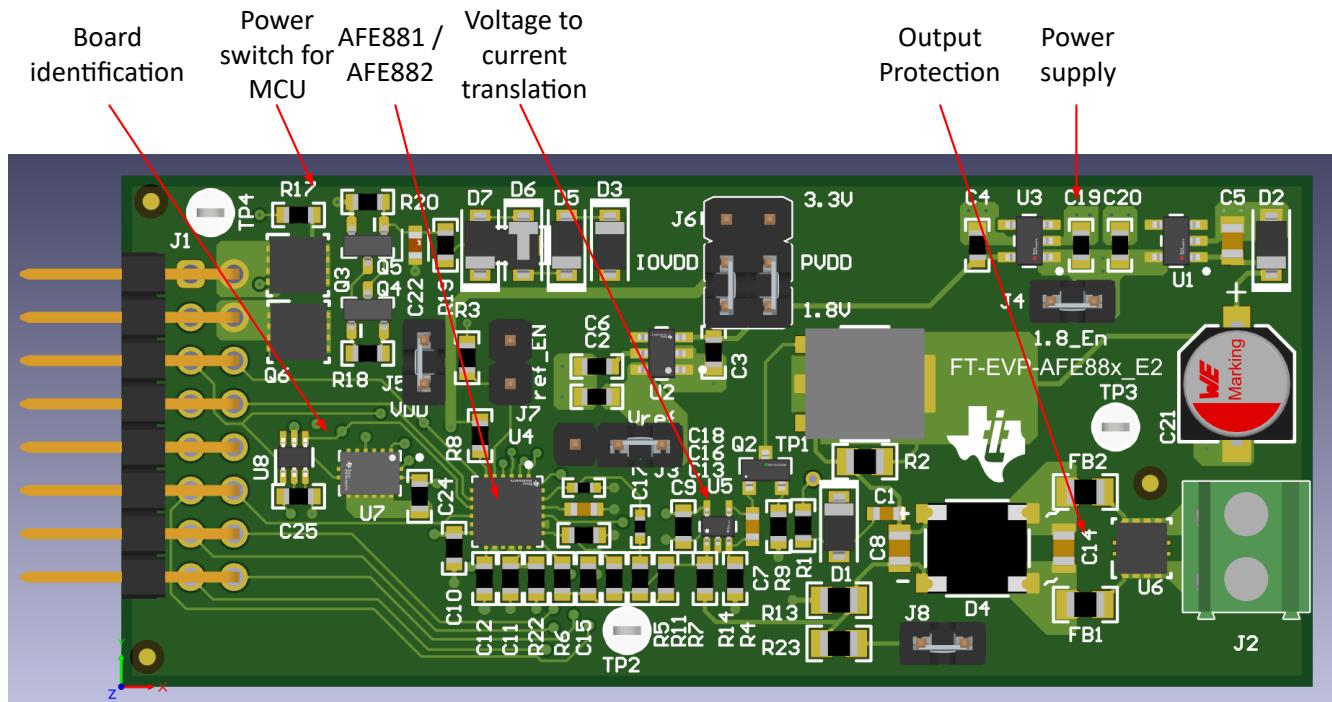

このセクションでは、この設計の各ブロックに関する情報について説明します。図 3-1 に、これらのブロックの配置を示します。

図 3-1. TIDA-010982 の機能プロック

ソフトウェアから基板を識別できるように、各基板にはシフトレジスタが搭載されており、入力ピンによってボード ID 番号がコーディングされ、SPI 経由で MCU から読み取ることができます。

ヘッダで利用可能な 1.8V および 3.3V 電圧は、電圧が安定するとすぐにディスクリートのパワー スイッチとして PMOSFET を使用してオンになります。

AFE881H1 または AFE882H1 はこの設計の主要部品であり、HART モデムを内蔵した電圧 DAC です。出力電圧はオペアンプ、トランジスタ、およびいくつかのパッシブ部品を使用して電流に変換されます。

出力は、ブリッジ整流器を使用して逆極性から、TVS3301 TVS ダイオードを使用して過渡電圧から保護されています。フェライトビーズを使用して高周波ノイズをフィルタリングできます。

電源には、ループ電圧から 3.3V と 1.8V を生成するための 2 つの LDO がオンボードで実装されています。

## 4 ハードウェア、ソフトウェア、テスト要件、テスト結果

### 4.1 ハードウェア要件

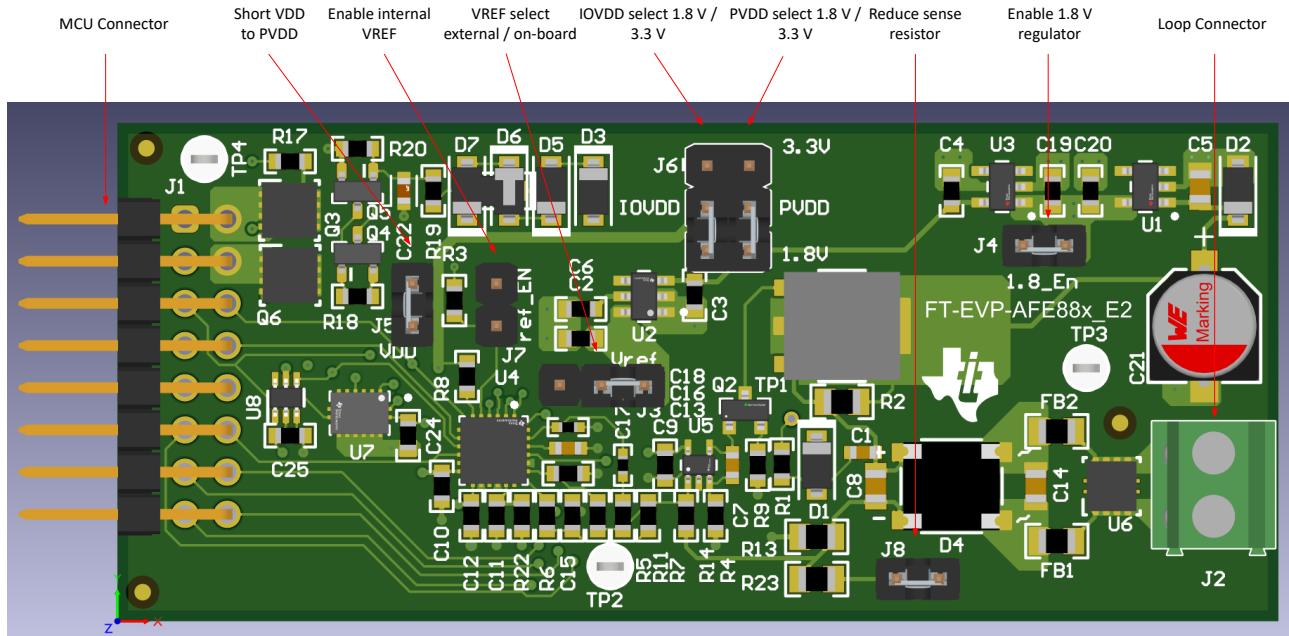

基板を動作させるには、正しく接続を行い、それに応じてジャンパを設定する必要があります。図 4-1 に TIDA-010982 ジャンパを示し、表 4-1 にジャンパとコネクタの簡単な説明を示します。

図 4-1. TIDA-010982 のジャンパ

表 4-1. ジャンパおよびコネクタの説明

| 記号 | ジャンパ、コネクタ        | 説明                                                                                   |

|----|------------------|--------------------------------------------------------------------------------------|

| J1 | MCU コネクタ         | マイコン ボードへの接続                                                                         |

| J5 | VDD から PVDD への短絡 | AFE881H1 を 1.8V で使用する場合は、これを短絡し、内部 LDO を無効にする必要があります                                 |

| J7 | 内部 VREF の有効化     | これを設定すると、AFE881H1 または AFE882H1 の内部リファレンス電圧が有効になります。                                  |

| J3 | VREF 選択          | オンボードの REF35125 を使用するには、1-2 に設定します。MCU コネクタ J1 経由で供給される外部リファレンス電圧を使用するには、2-3 に設定します。 |

| J6 | IOVDD 選択         | 3.3V 動作では 1-3、1.8V では 3-5 に設定します。                                                    |

| J6 | PVDD 選択          | 3.3V 動作では 2-4、1.8V では 4-6 に設定します。                                                    |

| J8 | センス抵抗の低減         | 電圧電流変換のための帰還抵抗を低減します。1.8V 動作の場合は、このジャンパを設定する必要があります。                                 |

| J4 | 1.8V レギュレータの有効化  | このジャンパを設定して 1.8V LDO を有効にします                                                         |

| J2 | ループ コネクタ         | 電流ループに接続します                                                                          |

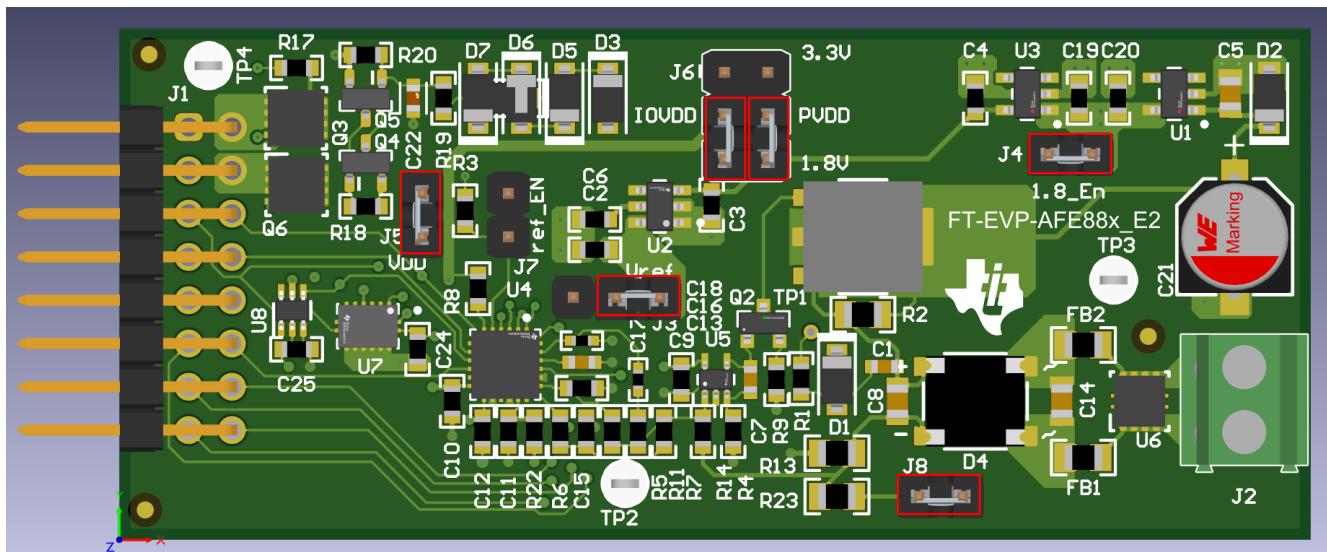

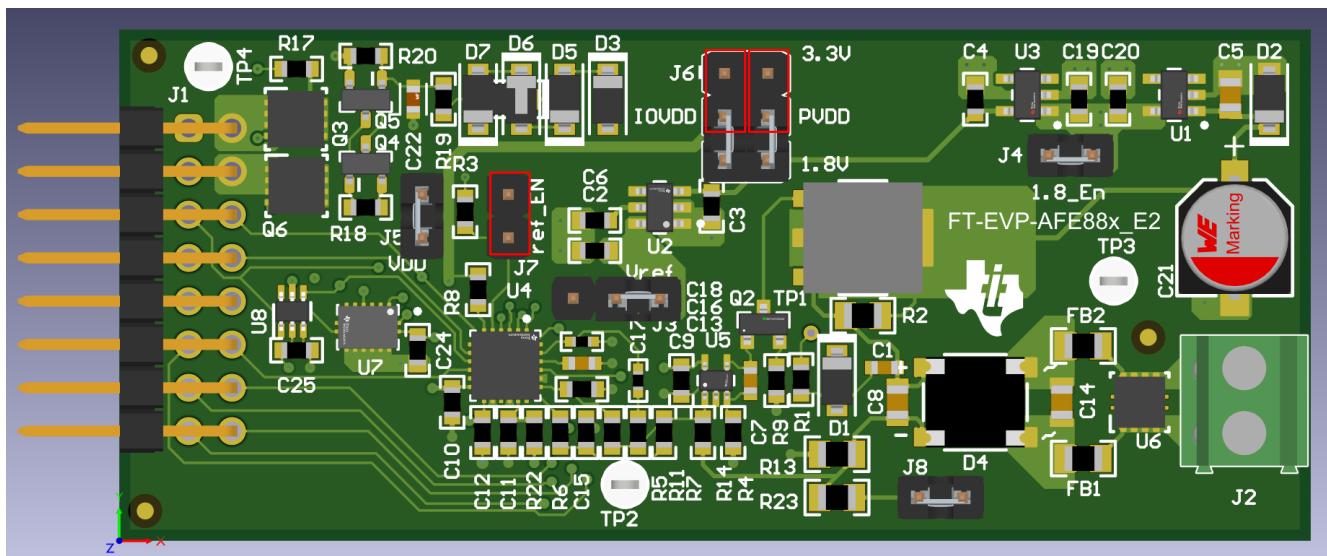

動作電圧が異なる場合、デバイスを損傷しないようにジャンパも異なる設定にする必要があります。図 4-2 に、1.8V 動作時のジャンパを設定する方法を示します。図 4-3 に、3.3V 動作時のジャンパ構成を示します。赤いボックスは、3.3V 動作時のジャンパを設定する方法を示しています。

図 4-2. 1.8V 動作時の TIDA-010982 ジャンパ構成

図 4-3. 3.3V 動作時の TIDA-010982 ジャンパ構成

コネクタ J1 は MCU ボードに接続されます。表 4-2 にピン配置を示します。ピン 1 は PCB でマークされています。

表 4-2. J1 コネクタのピン配置

| ピン | 信号       |

|----|----------|

| 1  | GND      |

| 2  | VDD-3V3  |

| 3  | VREF_EXT |

| 4  | VDD-1V8  |

| 5  | ID0      |

| 6  | SCLK     |

| 7  | 未使用      |

| 8  | SDI      |

| 9  | 未使用      |

| 10 | SDO      |

| 11 | ALARM    |

表 4-2. J1 コネクタのピン配置 (続き)

| ピン | 信号          |

|----|-------------|

| 12 | CS          |

| 13 | CD          |

| 14 | DAC_HART_RX |

| 15 | RTS         |

| 16 | DAC_HART_TX |

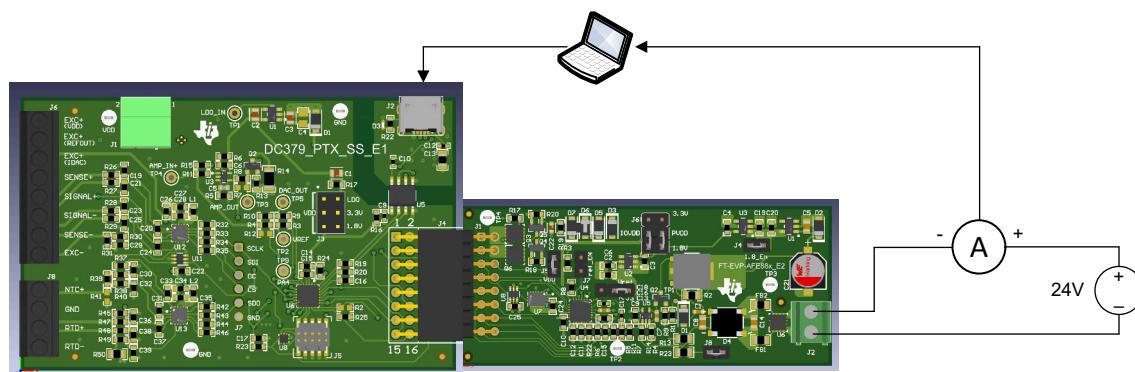

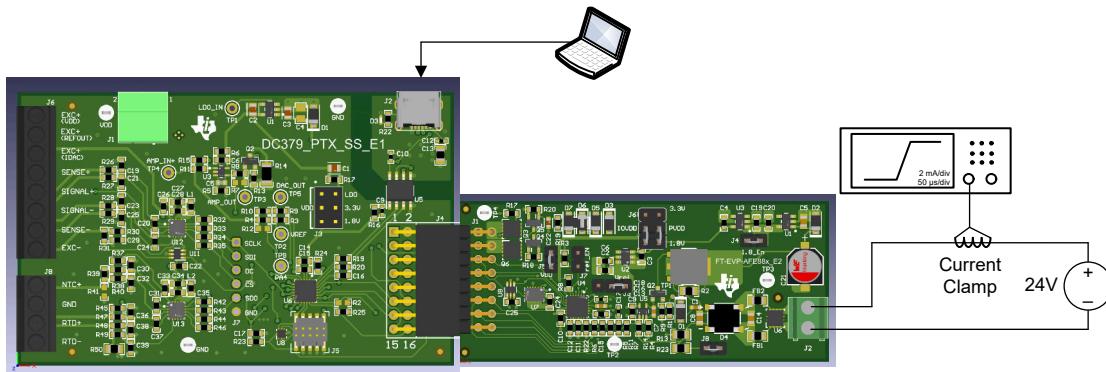

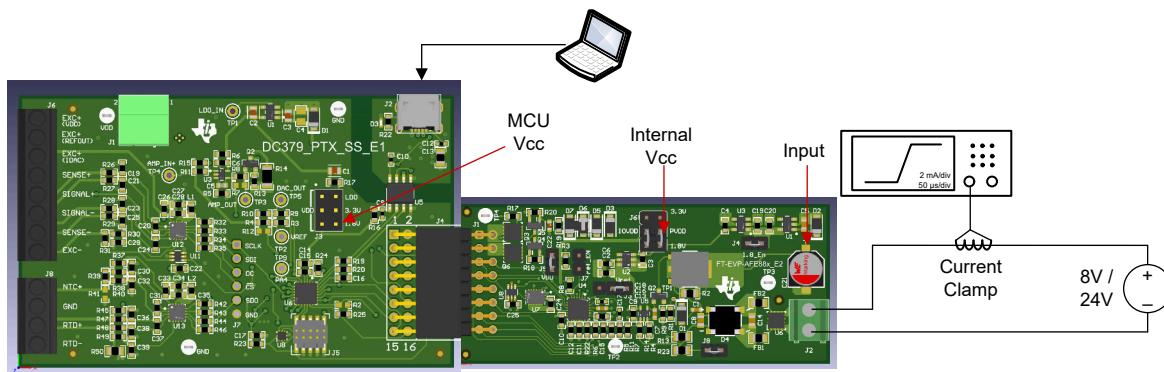

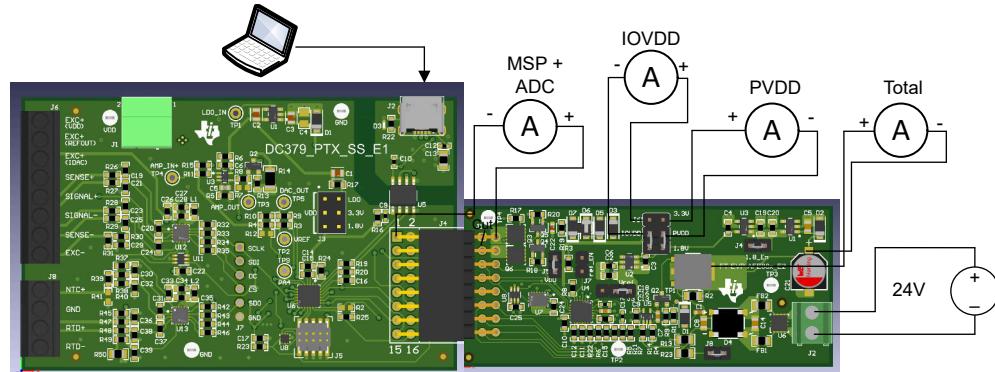

## 4.2 テスト設定

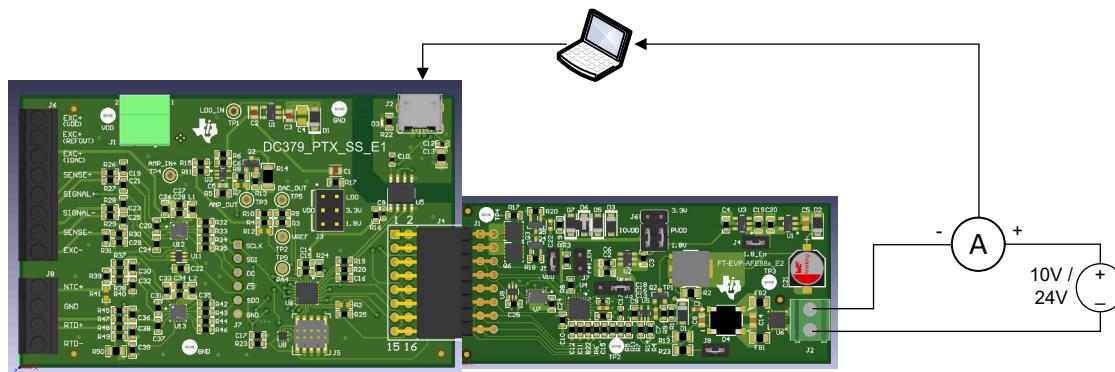

すべてのテストにおいて、このリファレンス デザインは、ADC に加えて AFE および ADC を制御する MCU を搭載した ADS122S14 評価基板と組み合わせて使用されます。さまざまなテスト設定については、次のセクションで説明します。

## 4.3 テスト結果

### 4.3.1 直線性テスト

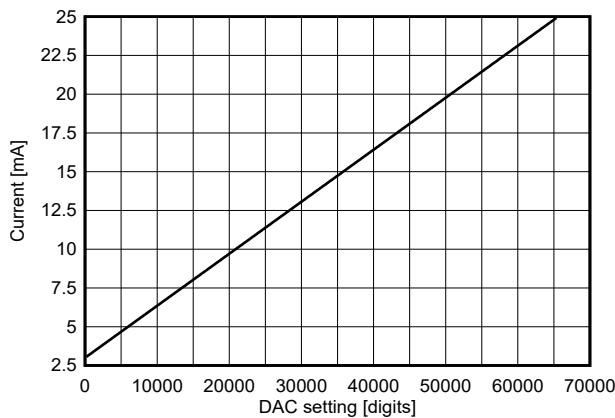

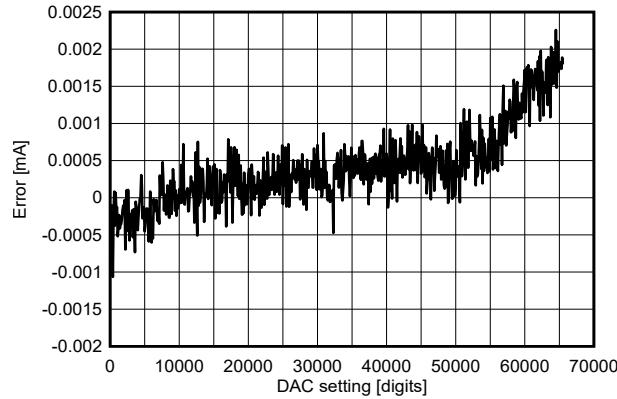

このテストでは、このリファレンス デザインは AFE の SPI 用にマイコンに接続され、アナログ出力は電源と電流計に接続されます。システム全体はループ電流から動作し、絶縁型 UART を介して PC に接続されます。すべてのテストは 10V および 24V のループ電圧で行われ、AFE881H1 は 3.3V および 1.8V 構成、AFE882H1 は 3.3V 構成で行われます。DAC コードを段階的に変化させ、電流計での読み取り値が記録されます。

図 4-4 に包括的な設定を示します。

図 4-4. 直線性テストのテスト設定

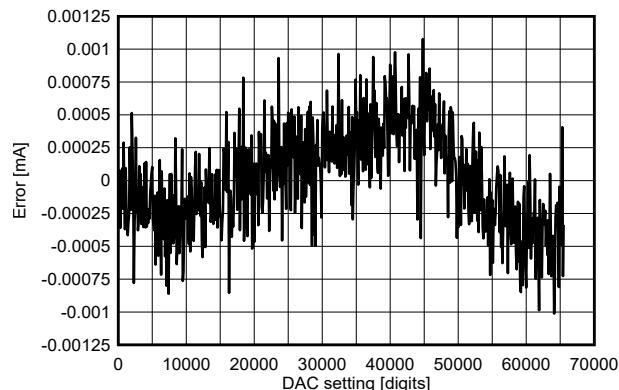

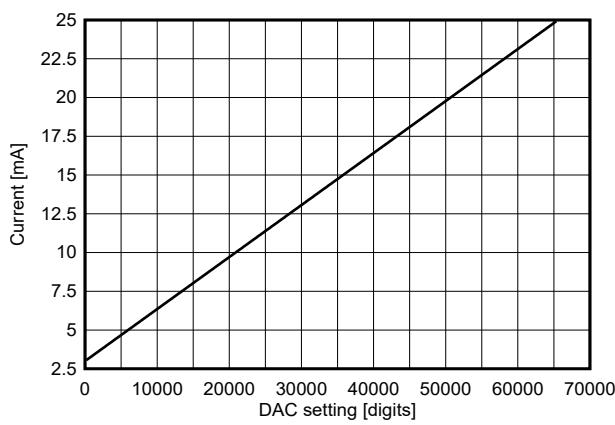

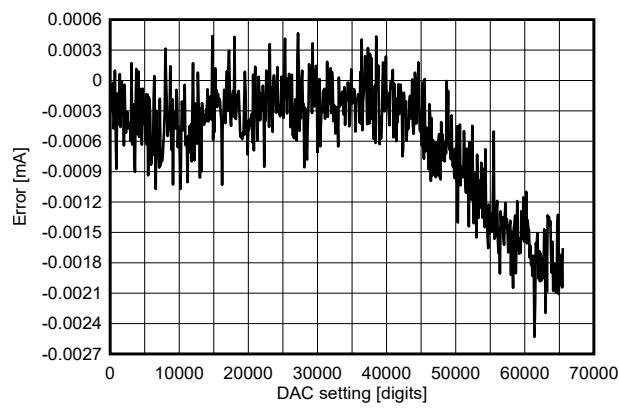

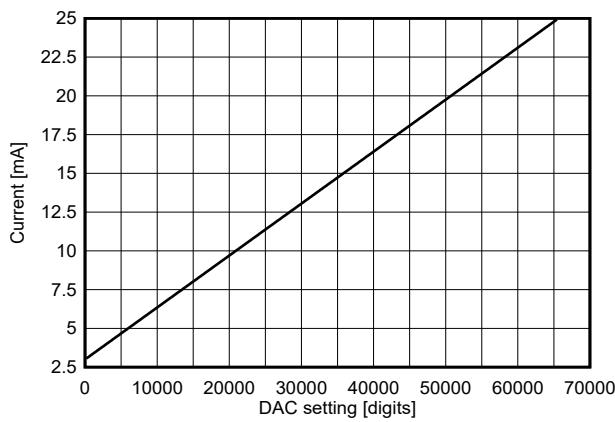

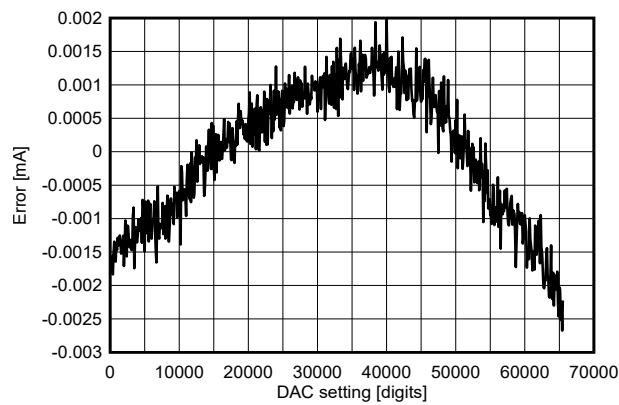

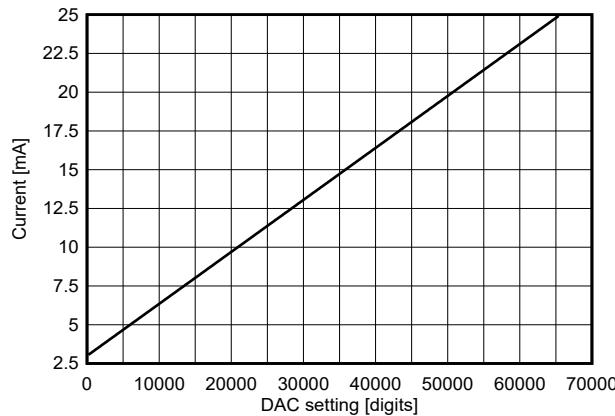

図 4-5 から図 4-16 は、線形トレンドラインを含む直線性を示しており、このトレンドラインは誤差の算出にも使用されます。したがって、この式は理想的な電流を算出するために使用され、測定値との差分が示されます。10V および 24V の各構成については、同じ式を使用して誤差を算出し、あるバイアス ポイントでのキャリブレーションをシミュレーションしてから、別のバイアス ポイントで動作させています。参考として、それぞれの異なる式を以下に示します。

図 4-5. AFE881:1.8V 電源、10V ループ直線性

$y = 3.35466E-04x + 2.99760$

図 4-6. AFE881:1.8V 電源、10V ループ誤差

図 4-7. AFE881:1.8V 電源、24V ループ直線性

$y = 3.35485E-04x + 2.99755$

図 4-8. AFE881:1.8V 電源、24V ループ誤差

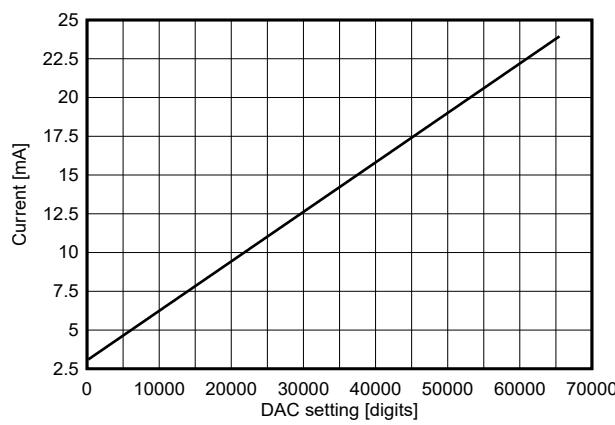

図 4-9. AFE881:3.3V 電源、10V ループ直線性

$y = 3.35189E-04x + 2.99416$

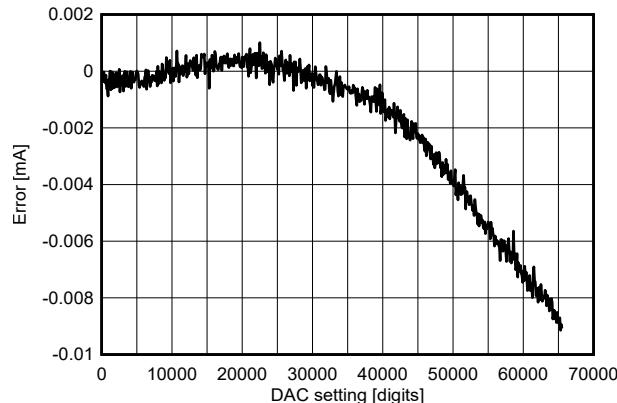

図 4-10. AFE881:3.3V 電源、10V ループ誤差

図 4-11. AFE881:3.3V 電源、24V ループ直線性

$y = 3.35312E-04x + 2.99208$

図 4-12. AFE881:3.3V 電源、24V ループ誤差

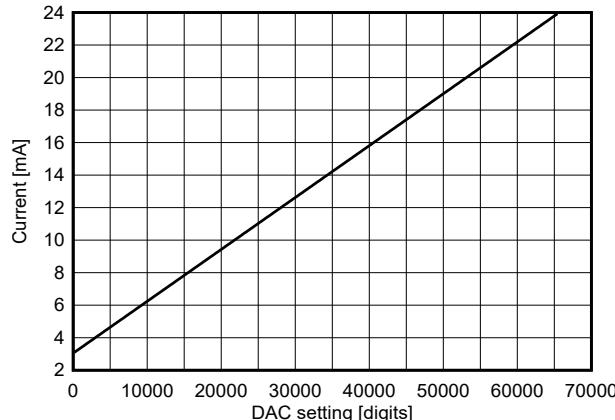

図 4-13. AFE882:3.3V 電源、10V ループ直線性

$y = 3.19149E-04x + 3.04646$

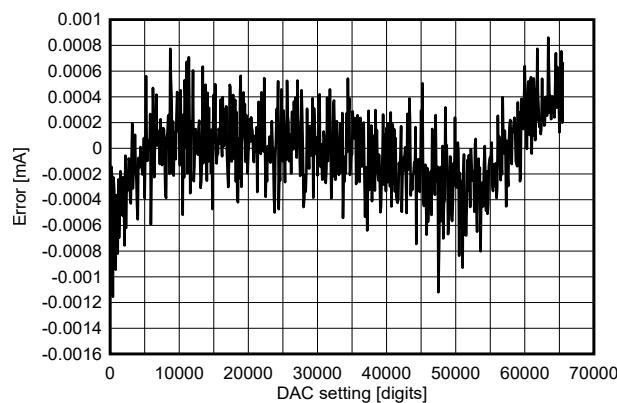

図 4-14. AFE882:3.3V 電源、10V ループ誤差

図 4-15. AFE882:3.3V 電源、24V ループ直線性

$y = 3.19127E-04x + 3.04673$

図 4-16. AFE882:3.3V 電源、24V ループ誤差

#### 4.3.1.1 直線性テストのまとめ

すべての構成において、結果はすべて仕様の範囲内に十分収まっており、どの構成にも不安定性やその他の非線形効果はみられません。AFE881 デバイスでは、3.3V 電源と同様の性能を 1.8V 電源でも得ることができます。

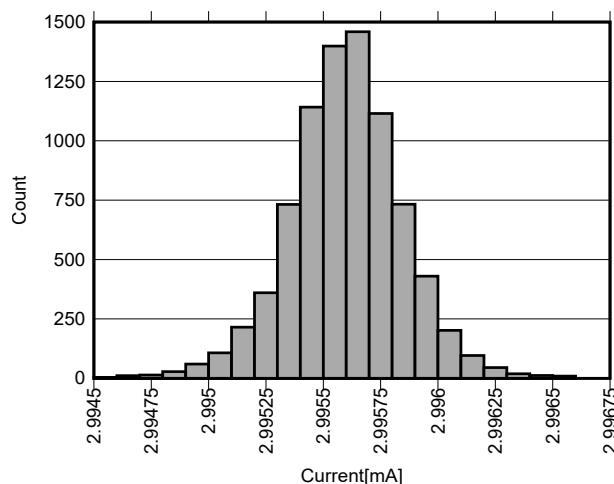

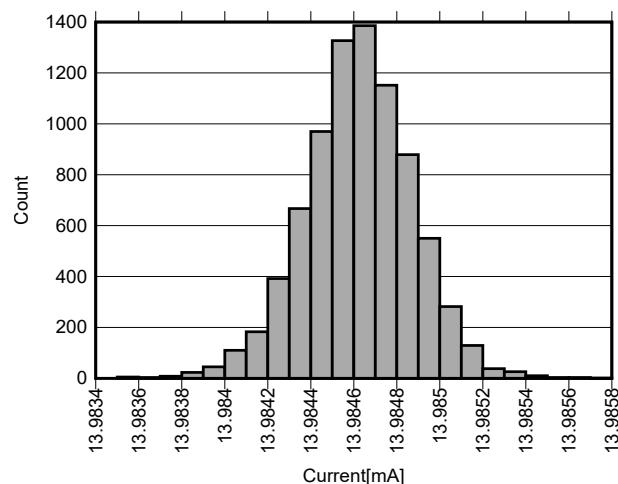

#### 4.3.2 ノイズテストと電流ヒストグラム

このテストでは、テスト設定はセクション 4.3.1 と同様です。性能を測定するために、DAC は 3 種類の出力電流（ゼロ [最小]、中間、最大）に設定され、出力電流は 8192 回測定されます。これらの値からヒストグラムがプロットされ、他のパラメータはこれらの測定値から計算されます。

図 4-17 に包括的な設定を示します。

図 4-17. テスト設定の電流ノイズ

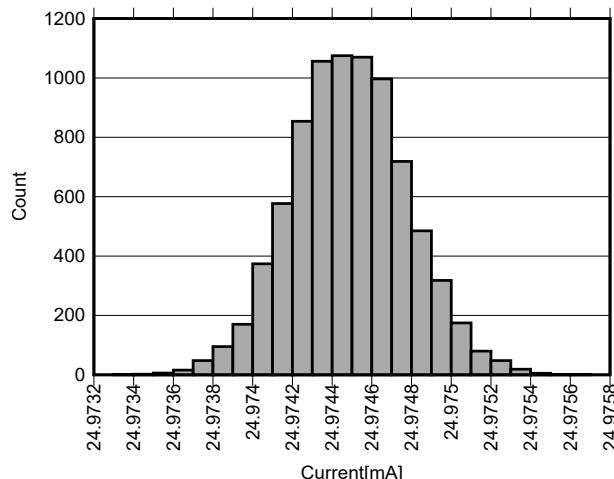

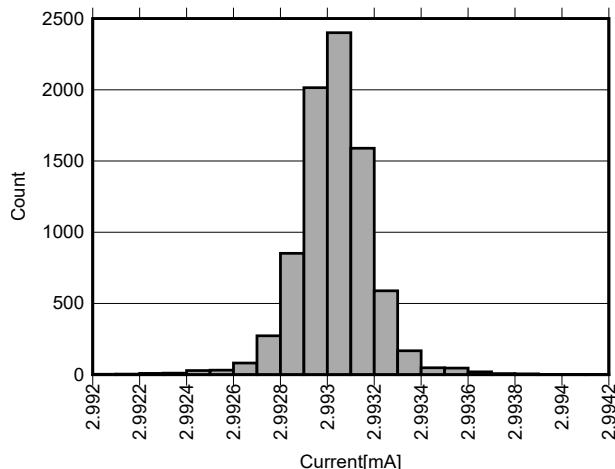

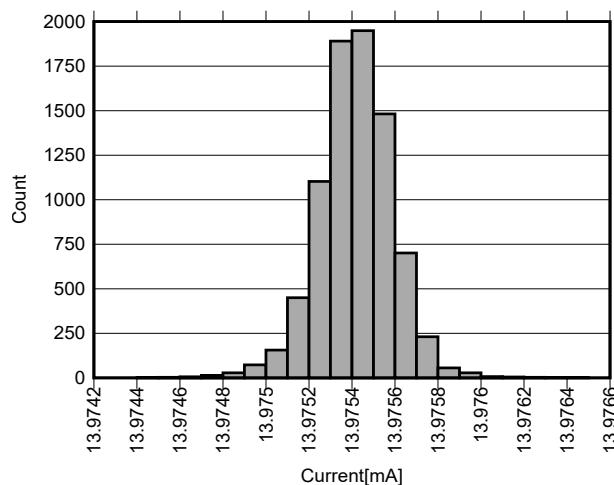

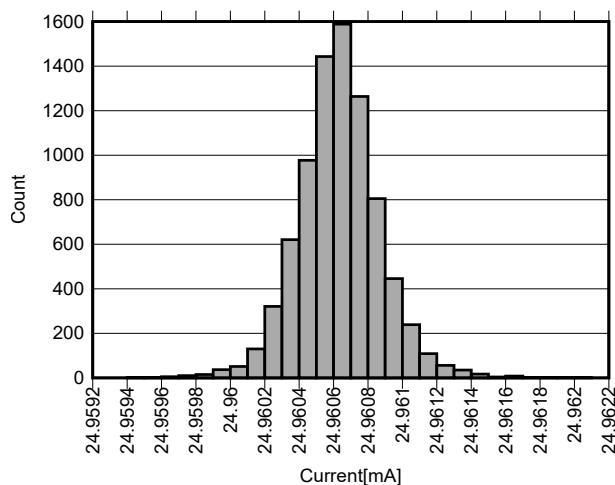

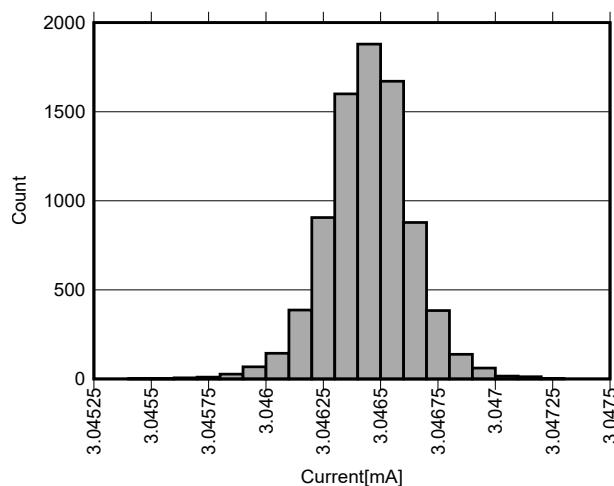

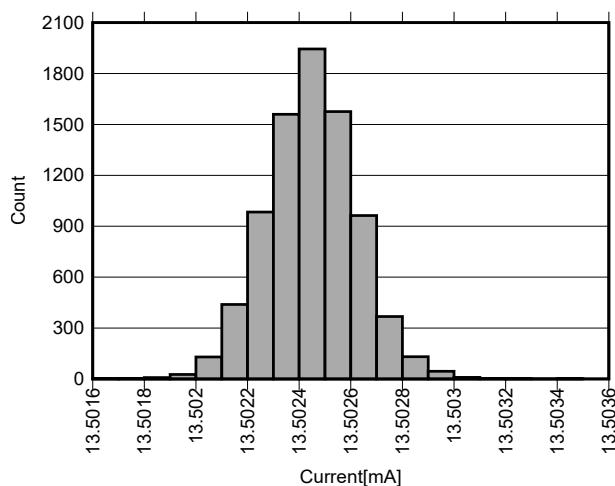

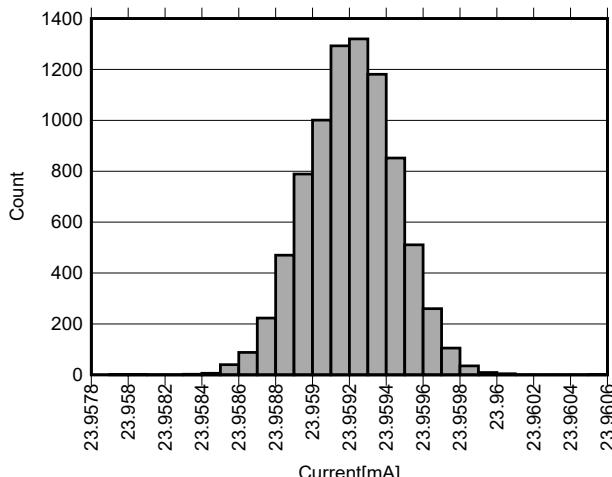

図 4-18 から図 4-26 に、測定された電流のヒストグラムを示します。

図 4-18. 1.8V で動作する DAC が最小設定の AFE881 のヒストグラム

図 4-19. 1.8V で動作する DAC が中間設定の AFE881 のヒストグラム

図 4-20. 1.8V で動作する DAC が最大設定の AFE881 のヒストグラム

図 4-21. 3.3V で動作する DAC が最小設定の AFE881 のヒストグラム

図 4-22. 3.3V で動作する DAC が中間設定の AFE881 のヒストグラム

図 4-23. 3.3V で動作する DAC が最大設定の AFE881 のヒストグラム

図 4-24. 3.3V で動作する DAC が最小設定の AFE882 のヒストグラム

図 4-25. 3.3V で動作する DAC が中間設定の AFE882 のヒストグラム

図 4-26. 3.3V で動作する DAC が最大設定の AFE882 のヒストグラム

#### 4.3.2.1 ノイズ テストと電流ヒストグラムのまとめ

表 4-3 に、図 4-18 から図 4-26 までの未加工データの計算結果を示します。

表 4-3. ノイズのまとめ

| AFE    | 電源電圧 (V) | DAC 設定 | 最小電流 (mA) | 平均電流 (mA) | 最大電流 (mA) | ピークツーピークノイズ ( $\mu$ A) | RMS ノイズ (nA) | ノイズ フリービット (NFB) | 有効ビット数 (ENOB) |

|--------|----------|--------|-----------|-----------|-----------|------------------------|--------------|------------------|---------------|

| AFE881 | 1.8      | 0      | 2.9945    | 2.9956    | 2.9966    | 2.05                   | 247          | 15.6             | 18.6          |

| AFE881 | 1.8      | 32768  | 13.9836   | 13.9846   | 13.9858   | 2.19                   | 250          | 15.5             | 18.6          |

| AFE881 | 1.8      | 65535  | 24.9734   | 24.9745   | 24.9757   | 2.25                   | 289          | 15.4             | 18.4          |

| AFE881 | 3.3      | 0      | 2.9920    | 2.9930    | 2.9942    | 2.15                   | 160          | 15.5             | 19.3          |

| AFE881 | 3.3      | 32768  | 13.9744   | 13.9754   | 13.9764   | 2.04                   | 173          | 15.6             | 19.1          |

| AFE881 | 3.3      | 65535  | 24.9595   | 24.9606   | 24.9621   | 2.62                   | 239          | 15.2             | 18.7          |

| AFE882 | 3.3      | 0      | 3.0455    | 3.0464    | 3.0473    | 1.76                   | 184          | 15.8             | 19.1          |

| AFE882 | 3.3      | 32768  | 13.5016   | 13.5024   | 13.5035   | 1.81                   | 173          | 15.8             | 19.1          |

| AFE882 | 3.3      | 65535  | 23.9580   | 23.9592   | 23.9606   | 2.6                    | 241          | 15.2             | 18.7          |

全体として、このヒストグラム プロットは、この種の信号に対して想定されるガウス分布を示しており、発振やその他の信号の乱れはみられません。これは、ウェイクアップ時に MCU が消費するピーク電流がループ上で観測されず、適切にレギュレーションされていることも証明されます。1.8V と 3.3V の信号チェーンの間に性能の違いはありません。

#### 4.3.3 ステップ応答

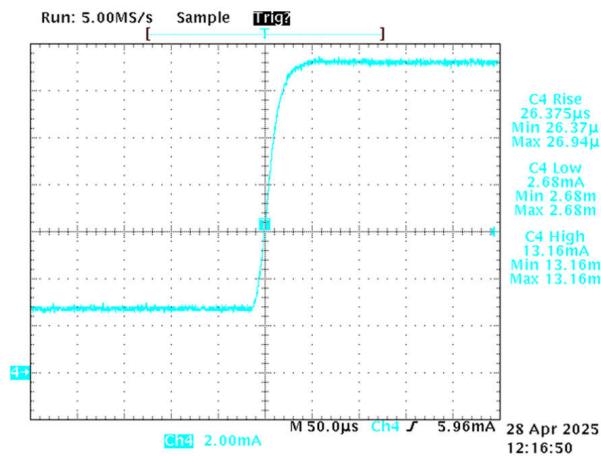

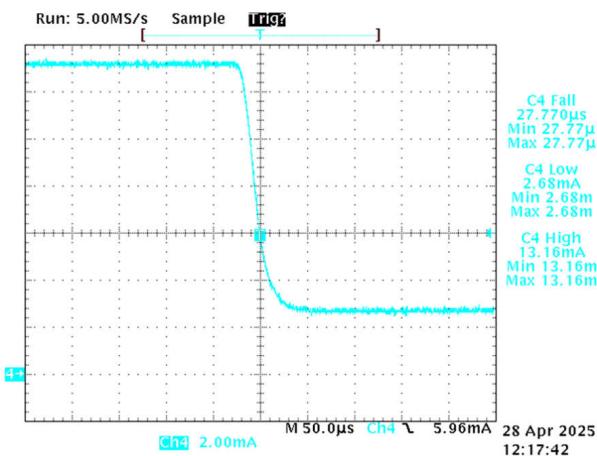

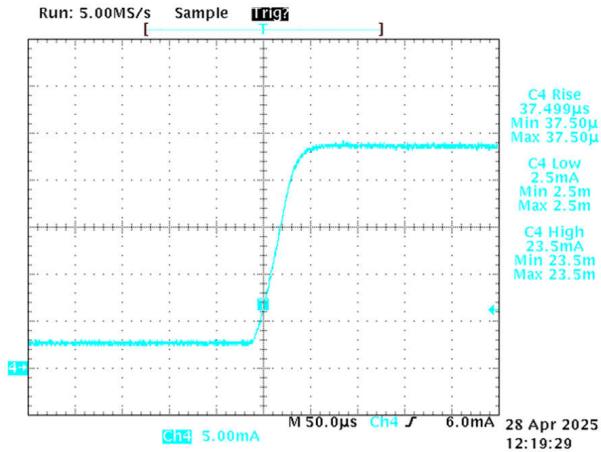

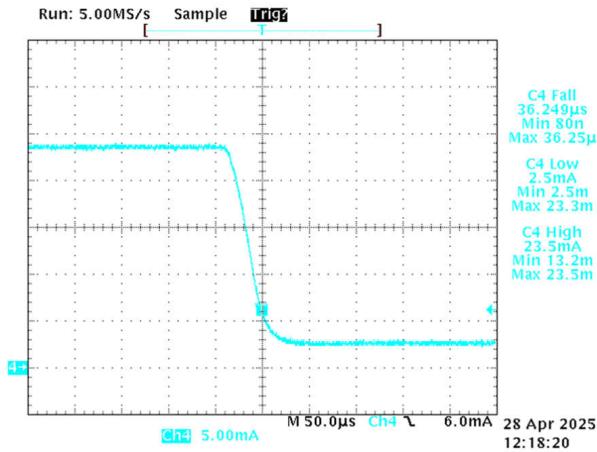

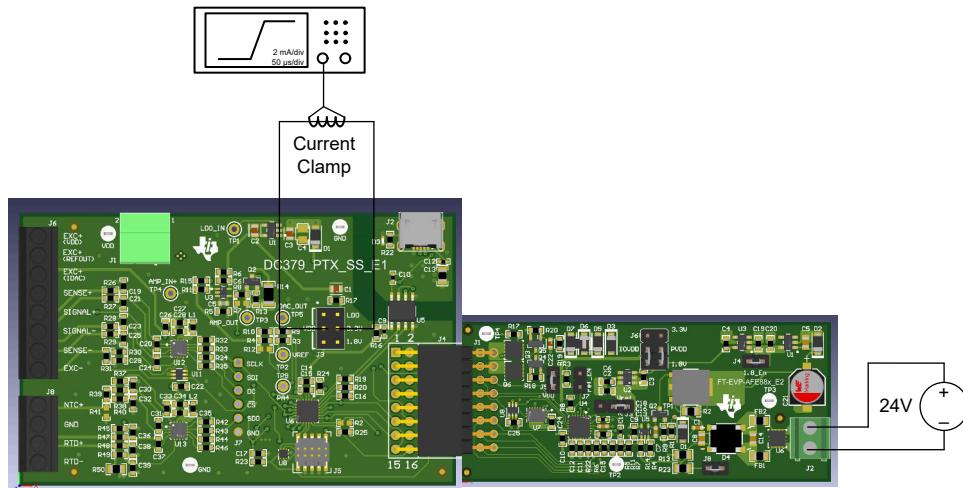

回路のステップ応答をテストするため、この回路は再び 24V 電源に接続されます。電流の測定は、ループ配線をクランプに複数回巻き付けて感度を高めた電流クランプを使用して行われます。

このステップ信号は、PC から AFE88x に対応する DAC 値を送信すると生成されます。このテストでは、ゼロから最大値へのステップ、最大値からゼロへのステップ、および中間電流へのステップが実行されます。これにより、アナログ回路のスルーレートが示され、安定性もテストされます。

図 4-27 に包括的な設定を示します。

図 4-27. ステップ応答測定のテスト設定

以下の図は電流のステップ応答を示しています。

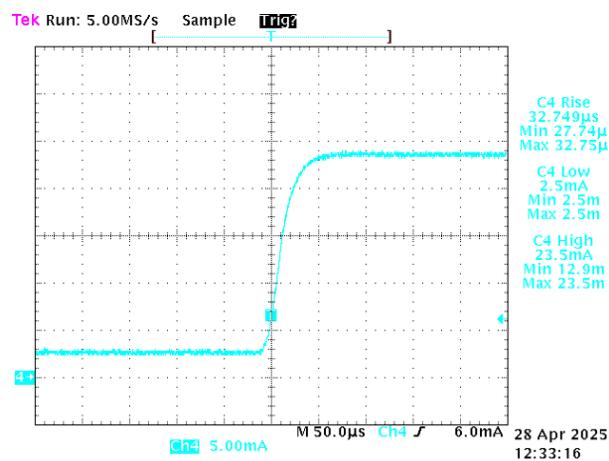

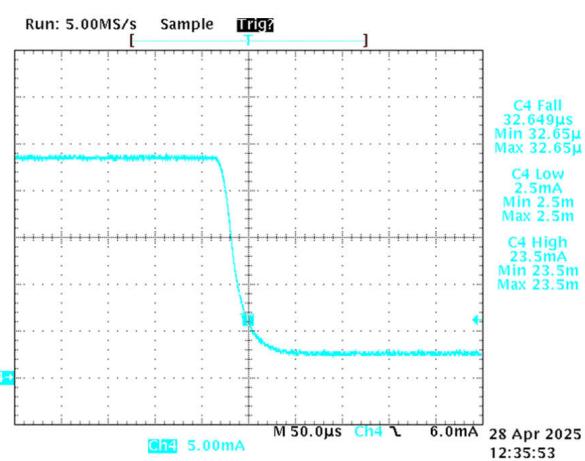

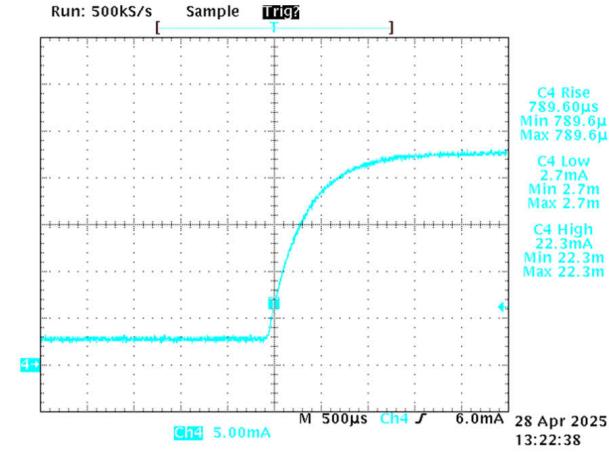

図 4-28. AFE881:3.3V、立ち上がり時間 0 ~ 65535

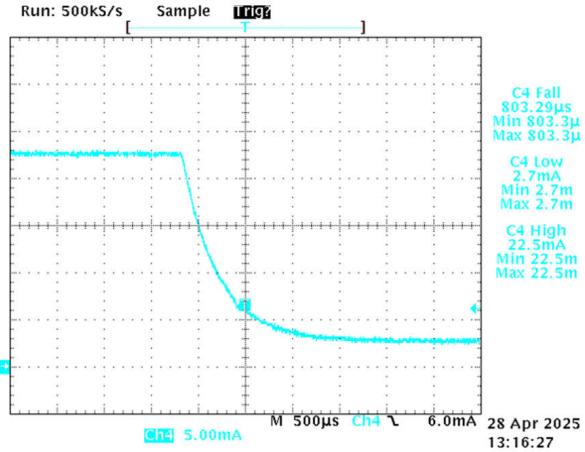

図 4-29. AFE881:3.3V、立ち下がり時間 65535 ~ 0

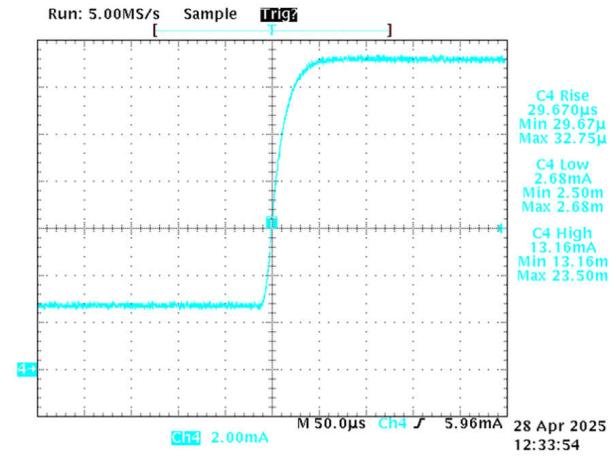

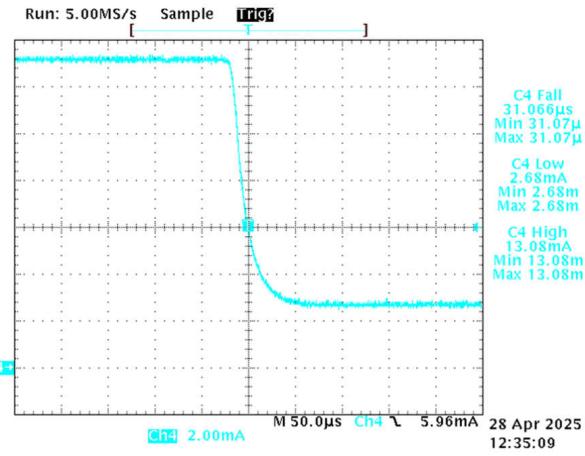

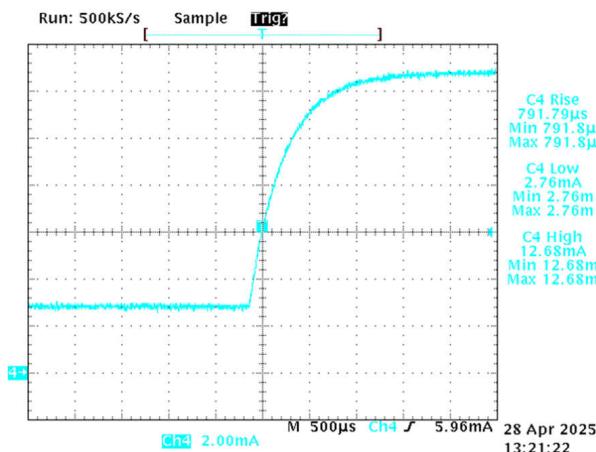

図 4-30. AFE881:3.3V、立ち上がり時間 0 ~ 32768

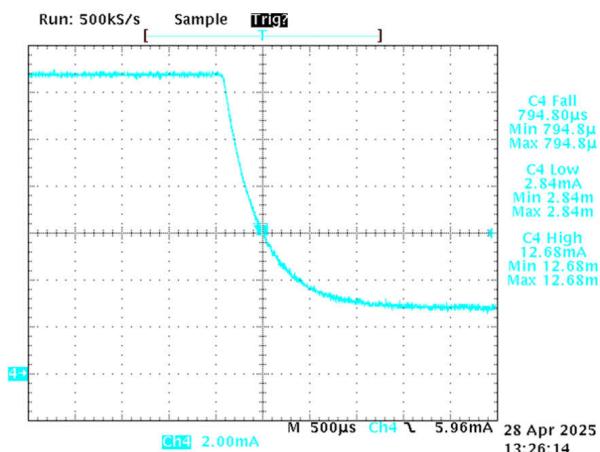

図 4-31. AFE881:3.3V、立ち下がり時間 32768 ~ 0

図 4-32. AFE881:1.8V、立ち上がり時間 0 ~ 65535

図 4-33. AFE881:1.8V、立ち下がり時間 65535 ~ 0

図 4-34. AFE881:1.8V、立ち上がり時間 0 ~ 32768

図 4-35. AFE881:1.8V、立ち下がり時間 32768 ~ 0

図 4-36. AFE882:3.3V、立ち上がり時間 0 ~ 65535

図 4-37. AFE882:3.3V、立ち下がり時間 65535 ~ 0

図 4-38. AFE882:3.3V、立ち上がり時間 0 ~ 32768

図 4-39. AFE882:3.3V、立ち下がり時間 32768 ~ 0

#### 4.3.3.1 ステップ応答のまとめ

表 4-4 に、立ち上がり時間と立ち下がり時間のまとめを示します。AFE882H1 ハードウェアは、立ち上がり時間と立ち下がり時間が低速になるように設計されています。それでも、プロットはオーバーシュート、アンダーシュート、または発振がないことを示しています。

表 4-4. 立ち上がり時間と立ち下がり時間のまとめ

| AFE    | 電源電圧 (V) | DAC 設定 | 立ち上がり時間 (μs) | 立ち下がり時間 (μs) |

|--------|----------|--------|--------------|--------------|

| AFE881 | 3.3      | 65535  | 26           | 28           |

| AFE881 | 3.3      | 32768  | 38           | 36           |

| AFE881 | 1.8      | 65535  | 33           | 33           |

| AFE881 | 1.8      | 32768  | 30           | 31           |

| AFE882 | 3.3      | 65535  | 790          | 803          |

| AFE882 | 3.3      | 32768  | 792          | 795          |

#### 4.3.4 スタートアップ

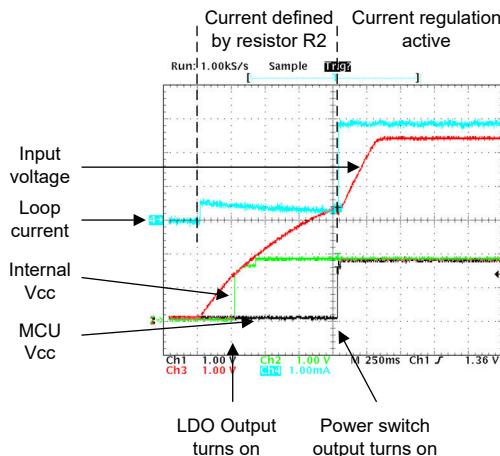

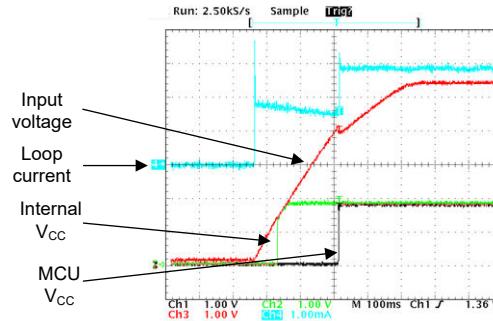

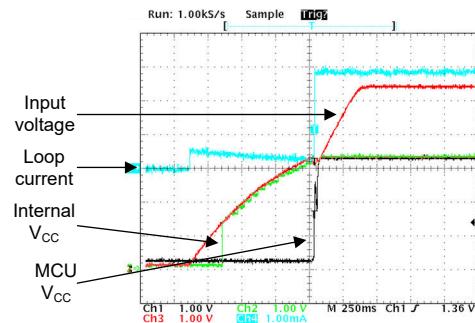

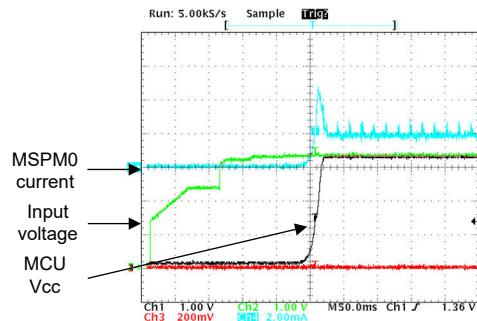

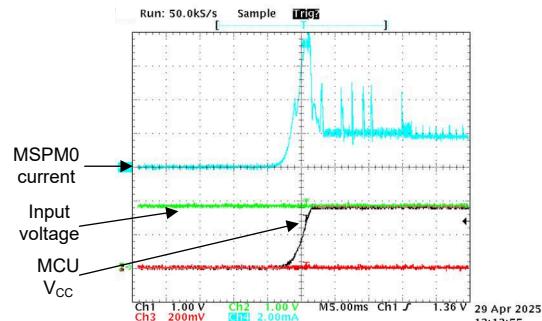

システムの起動動作を調べることも重要です。特に、起動フェーズ全体を通じて、4mA 未満の最小電流を維持できるかどうかや、起動フェーズに要する時間を特定することが重要です。図 4-40 に、最初のステップで起動がどのように監視されているかを示します。

図 4-40. 起動測定のテスト設定

図 4-40 の構成を使用して測定を行うと、図 4-41 に示すスコープ波形が得られます。

図 4-41. AFE881 の 1.8V ~ 8V ループ電圧での起動

図 4-42 は、電流が測定されたような形になる理由を示しています。最初の電流はバイパス抵抗 R2 のみによって決まります。これは内部電圧が立ち上がり、アンプが電源投入されて電流がレギュレーションされるようになるまでの間、電流を流すことができる唯一の部品です。

250ms 後、電圧が十分に高くなると、LDO がオンになり、1.8V を内部に供給します。750ms 以降、内部の電源スイッチがオンになります。このスイッチは中間の 3.3V 電源レールが安定しているかどうかを監視し、遅延を追加します。オンになると、MCU と AFE の IO 電源レールが有効になります。これにより、AFE はパワー オンリセットを抜け、電流のレギュレーションが開始されますが、測定された入力電流は 3mA に段階的に変化します。

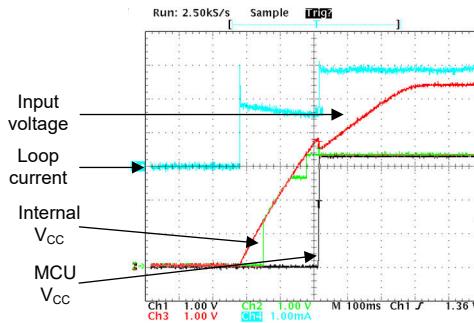

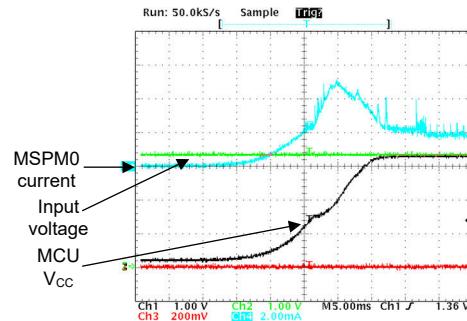

図 4-42. 概略回路図

24V の電源電圧を使用すると初期電流が大きくなるため、システムはより高速に起動します。図 4-43 は、24V ループ電圧を使用した場合と同じ測定値を示しています。電源投入シーケンス開始時の電流は、ほぼ 2mA です。MCU は約 150ms で起動プロセス全体を完了します。

図 4-43. AFE881 の 1.8V ~ 24V ループ電圧での起動

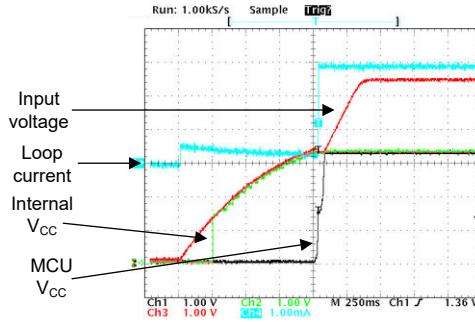

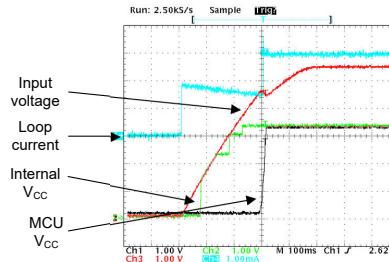

図 4-44 から図 4-47 は、さまざまな構成で実施した同じテストを示しています。

図 4-44. AFE881:3.3V ~ 8V ループ電圧での起動

図 4-45. AFE881:3.3V ~ 24V ループ電圧での起動

図 4-46. AFE882:3.3V ~ 8V ループ電圧での起動

図 4-47. AFE882:3.3V ~ 24V ループ電圧での起動

#### 4.3.5 MCU 電流

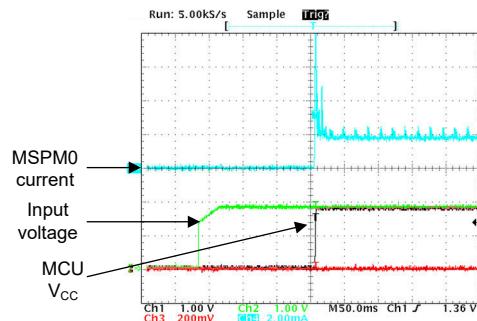

起動動作と電流に加えて、マイコンの電流プロファイルを詳しく調べることも重要です。

図 4-48. MSPM0 電流消費のテスト設定

図 4-48 に、この測定の設定を示します。システムは通常どおり 24V で電源投入され、MCU に流れ込む電流は MCU ボード上に直接取り付けられた電流クランプを使用して測定されます。測定には、MCU とバイパスコンデンサのみが含まれます。

図 4-49 から図 4-52 に、さまざまな条件およびズーム係数での MSPM0 の突入電流を示します。

図 4-49. MSPM0 の起動用 3.3V 電源

図 4-50. MSPM0 の起動用 3.3V 電源 - 詳細

図 4-51. MSPM0 の起動用 1.8V 電源

図 4-52. MSPM0 の起動用 1.8V 電源 - 詳細

#### 4.3.5.1 MCU 電流のまとめ

図 4-49 から図 4-52 は、MSPM0 回路の突入電流が 4mA を容易に超えることを示しています。この電流のピークはシステム全体の入力部では確認されず、電流のレギュレーション回路にも干渉しません。

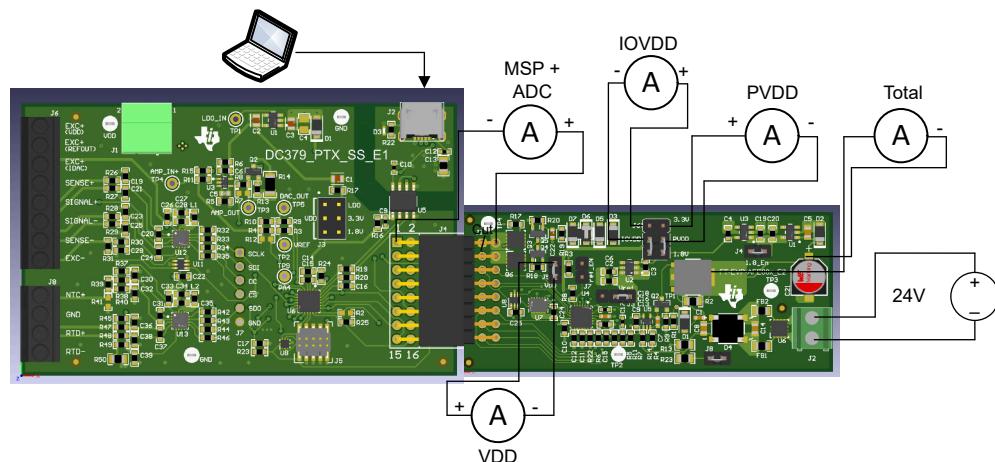

#### 4.3.6 システム電流

システムのどの部分が消費電力に寄与しているかを確認するために、各電源レールの電流が測定されます。3.3V 構成では、AFE881 は内部電圧リファレンスと内部 LDO を使用して PVDD から VDD を生成します。一方、1.8V 構成では、外部リファレンス電圧を使用し、VDD 電源はシステムの 1.8V 電源レールから供給されます。

図 4-53 は、基板上で電流が測定される場所を示しています。図 4-54 は、1.8V 構成ではもう 1 つの電源レールが測定されることを示しています。

図 4-53. 電流測定のテスト設定:3.3V

図 4-54. 電流測定のテスト設定:1.8V

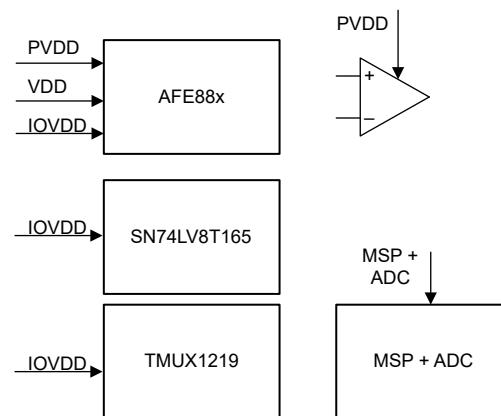

図 4-55 に、主要部品と電源レールの接続を示します。

図 4-55. 簡易電源構成図

#### 4.3.6.1 システム電流のまとめ

表 4-5 に、さまざまな構成で測定された電流を示します。この表の合計電流は、ループ駆動トランジスタと LDO の入力の間で測定された、システムに流れ込む総電流の測定値です。測定された総電流には、LDO の静止電流やリファレンス電圧など、個別に測定されていないすべての電流も含まれます。

**表 4-5. さまざまな構成で測定された電流**

| AFE    | 電源電圧 (V) | DAC 設定 | P <sub>VDD</sub> (μA) | I <sub>OVDD</sub> (μA) | MSP + ADC (mA) | V <sub>DD</sub> (μA) | 合計 (mA) |

|--------|----------|--------|-----------------------|------------------------|----------------|----------------------|---------|

| AFE882 | 3.3      | 0      | 200                   | 1.2                    | 1.958          | 該当なし                 | 2.214   |

|        | 3.3      | 32768  | 217                   | 1.2                    | 1.958          | 該当なし                 | 2.231   |

|        | 3.3      | 65535  | 230                   | 1.2                    | 1.958          | 該当なし                 | 2.244   |

| AFE881 | 3.3      | 0      | 192                   | 1.1                    | 1.99           | 該当なし                 | 2.266   |

|        | 3.3      | 32768  | 203                   | 1.1                    | 1.99           | 該当なし                 | 2.276   |

|        | 3.3      | 65535  | 216                   | 1.1                    | 1.99           | 該当なし                 | 2.289   |

|        | 1.8      | 0      | 50                    | 0.6                    | 1.92           | 89                   | 2.135   |

|        | 1.8      | 32768  | 55.5                  | 0.6                    | 1.92           | 89                   | 2.140   |

|        | 1.8      | 65535  | 61.3                  | 0.6                    | 1.92           | 89                   | 2.146   |

## 5 設計とドキュメントのサポート

### 5.1 デザインファイル

#### 5.1.1 回路図

回路図をダウンロードするには、[TIDA-010982](#) のデザインファイルを参照してください。

#### 5.1.2 BOM

部品表 (BOM) をダウンロードするには、[TIDA-010982](#) のデザインファイルを参照してください。

#### 5.1.3 PCB レイアウトに関する推奨事項

##### 5.1.3.1 レイアウトプリント

レイヤープロットをダウンロードするには、[TIDA-010982](#) のデザインファイルを参照してください。

### 5.2 ツールとソフトウェア

#### ツール

[AFE881H1EVM](#) AFE881H1 16ビット、電圧出力、高精度 DAC および 16ビット ADC 用の評価基板

[AFE882H1EVM](#) AFE882H1 16ビット、電圧出力、高精度 DAC および 16ビット ADC 用の評価基板

[LP-MSPM0G3507](#) MSPM0G3507 80MHz Arm® Cortex®-M0+マイコン向け LaunchPad™ 開発キット

#### ソフトウェア

[MSPM0-SDK](#) MSPM0 ソフトウェア開発キット

### 5.3 ドキュメントのサポート

- テキサス・インスツルメンツ、『[AFE81H1 内蔵 HART® モデム、電圧リファレンス、および 4mA ~ 20mA ループ電源アプリケーション向け診断 A/D コンバータを備えた、16 ビットおよび 14 ビット低消費電力 D/A コンバータ』データシート](#)

- テキサス・インスツルメンツ、『[AFE82H1 16 ビットおよび 14 ビット、低消費電力 D/A コンバータ \(DAC\)、HART® モデム、電圧リファレンス、プロセス制御用診断 ADC 内蔵』データシート](#)

- テキサス・インスツルメンツ、『[OPAX391 高精度、超低  \$I\_Q\$ 、低オフセット電圧、e-trim™ オペアンプ』データシート](#)

- テキサス・インスツルメンツ、『[TPS7A03 ナノパワー  \$I\_Q\$ 、200nA、200mA、高速過渡応答の低ドロップアウト電圧レギュレータ』データシート](#)

- テキサス・インスツルメンツ、『[REF35 超低消費電力、高精度電圧リファレンス』データシート](#)

- テキサス・インスツルメンツ、『[TVS3301 33V 双方向フラットクランプ サージ保護デバイス』データシート](#)

- テキサス・インスツルメンツ、『[TMUX1219 5V 双方向、2:1 汎用スイッチ』データシート](#)

- テキサス・インスツルメンツ、『[SN74LV8T165 パラレルロード 8 ビットシフトレジスタ』データシート](#)

### 5.4 サポート・リソース

テキサス・インスツルメンツ E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツルメンツの使用条件を参照してください。

### 5.5 商標

E2E™, e-trim™, LaunchPad™, and テキサス・インスツルメンツ E2E™ are trademarks of Texas Instruments.

HART® is a registered trademark of FieldComm Group.

Arm® and Cortex® are registered trademarks of Arm Limited.

すべての商標は、それぞれの所有者に帰属します。

## 6 著者

**STEFFEN GRAF** は、テキサス・インスツルメンツのシステム・エンジニアであり、産業用部門でのリファレンス・デザイン開発を担当しています。Steffen は、シングルペア・イーサネット、PoDL (Power Over Data Lines)、IO-Link などの分野で豊富な経験を持っています。彼は、ドイツのダルムシュタットにある応用科学大学で電気工学の修士号を取得しています。

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適したテキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているテキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、[テキサス・インスツルメンツの販売条件](#)、または [ti.com](http://ti.com) やかかるテキサス・インスツルメンツ製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2025, Texas Instruments Incorporated

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Webツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適したTI製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているTI製品を使用するアプリケーションの開発の目的でのみ、TIはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TIや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TIおよびその代理人を完全に補償するものとし、TIは一切の責任を拒否します。

TIの製品は、[TIの販売条件](#)、[TIの総合的な品質ガイドライン](#)、[ti.com](#)またはTI製品などに関連して提供される他の適用条件に従い提供されます。TIがこれらのリソースを提供することは、適用されるTIの保証または他の保証の放棄の拡大や変更を意味するものではありません。TIがカスタム、またはカスタマー仕様として明示的に指定していない限り、TIの製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TIはそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025年10月