## Design Guide: TIDA-00176

# 高分解能位置補間機能付き Sin/Cos エンコーダへのインターフェイス

## 説明

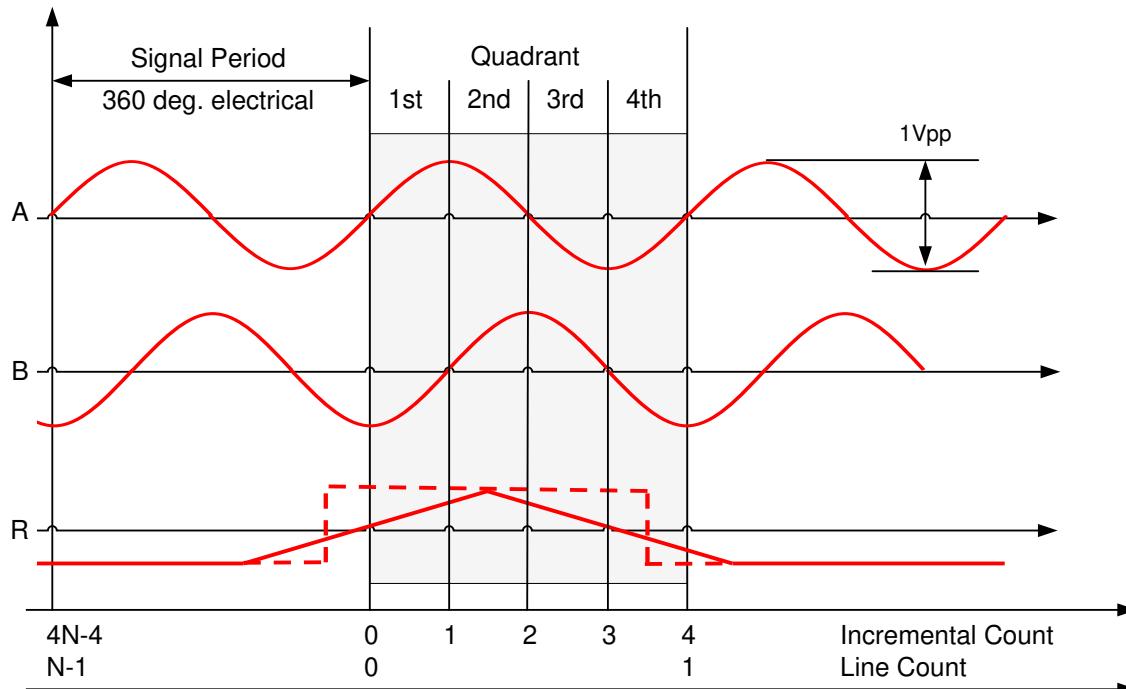

このリファレンス デザインは、Sin/Cos 位置エンコーダに対する EMC 準拠の産業用インターフェイスです。アプリケーションには、高精度の速度制御と位置制御を必要とする産業用ドライブが含まれています。この設計は 16 ビットのデュアル サンプル ADC を使用しており、ドロップイン互換性のある 14 ビットまたは 12 ビットのバージョンが利用できるので、性能とコストを最適化できます。また、TIDA-00176 では、SPI および QEP インターフェイスを使用して外部プロセッサとの接続が容易で、オプションの組込み ADC を使用できます。迅速な評価を実現するために、Piccolo™ F28069M マイコン LaunchPad™ 用のサンプル フームウェアが提供されています。このフームウェアは、Sin/Cos エンコーダから測定した角度を、マイコンの USB 仮想 COM ポート経由で最大 28 ビットの分解能で出力します。

## リソース

|                                |            |

|--------------------------------|------------|

| TIDA-00176                     | デザイン フォルダ  |

| ADS8354, THS4531A              | プロダクト フォルダ |

| TLV3202, OPA2365               | プロダクト フォルダ |

| REF2033, TPS54040A             | プロダクト フォルダ |

| TIPD117                        | ツール フォルダ   |

| Piccolo F28069M マイコン LaunchPad | ツール フォルダ   |

テキサス・インスツルメンツの™ E2E サポート エキスパートにお問い合わせください。

## 特長

- 2.5V オフセット、最大 500kHz の入力周波数で 1V<sub>PP</sub> の差動出力を使用する、EMC 規格準拠、Sin/Cos エンコーダ用の産業用インターフェイス設計

- 高分解能の位置補間、最大 28 ビットの分解能、ケーブル長 70m までテスト済み

- デュアル アナログ シグナル チェーンは、16 ビット デュアル SAR ADC とマイコンの組込み ADC との同時使用が可能で、経路の両方を評価し、経路の一方を最適化することで、帯域幅を減らしてノイズ耐性を向上可能

- SPI および QEP インターフェイスでマイコンに簡単に接続できるほか、ドロップイン互換性のある 14 または 12 ビットの ADC により、分解能要件が未決定のコスト最適化オプションも利用可能

- 16kHz で計算された高分解能な角度と USB 仮想 COM ポート経由で送信された角度データを使用した C2000™ マイコン用フームウェアのサンプルで、性能を簡単に評価可能

- IEC61000-4-2、4-4、4-5 (ESD、EFT、サージに関する EMC 耐性要件) のテスト済み

## アプリケーション

- AC ドライブ

- 精密速度 - 可変ドライブ

- サーボ ドライブ

## 1 システムの説明

### 1.1 設計の概要

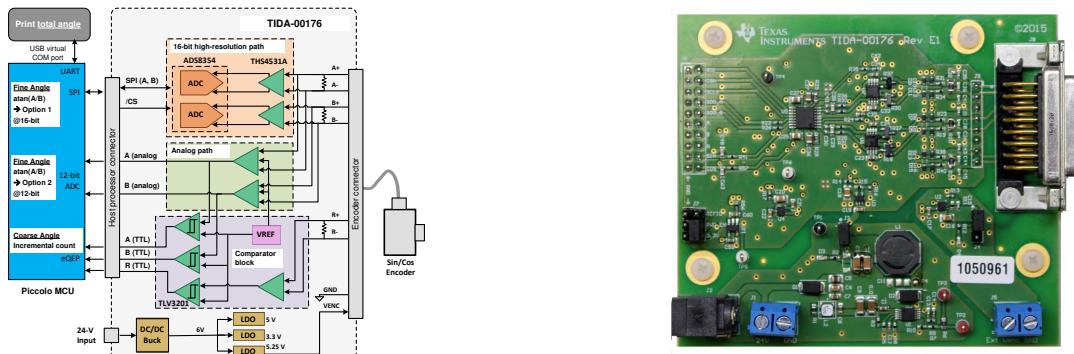

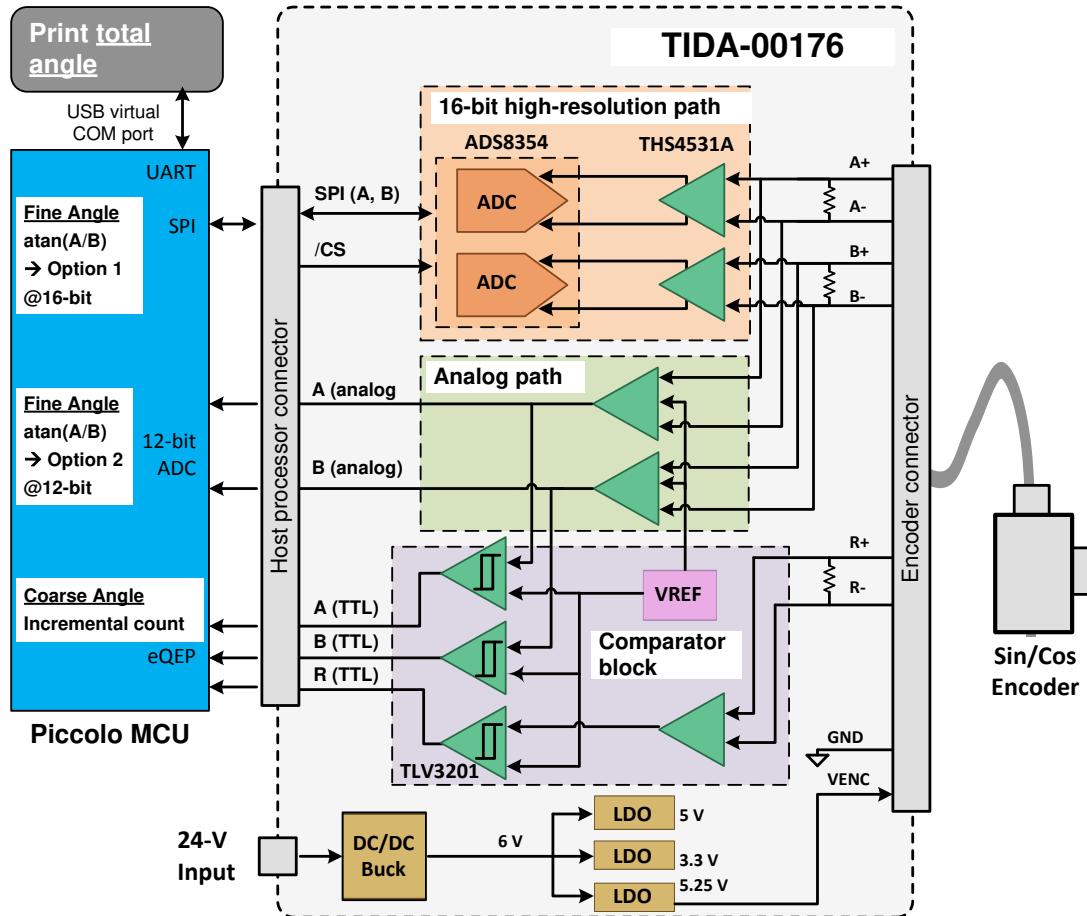

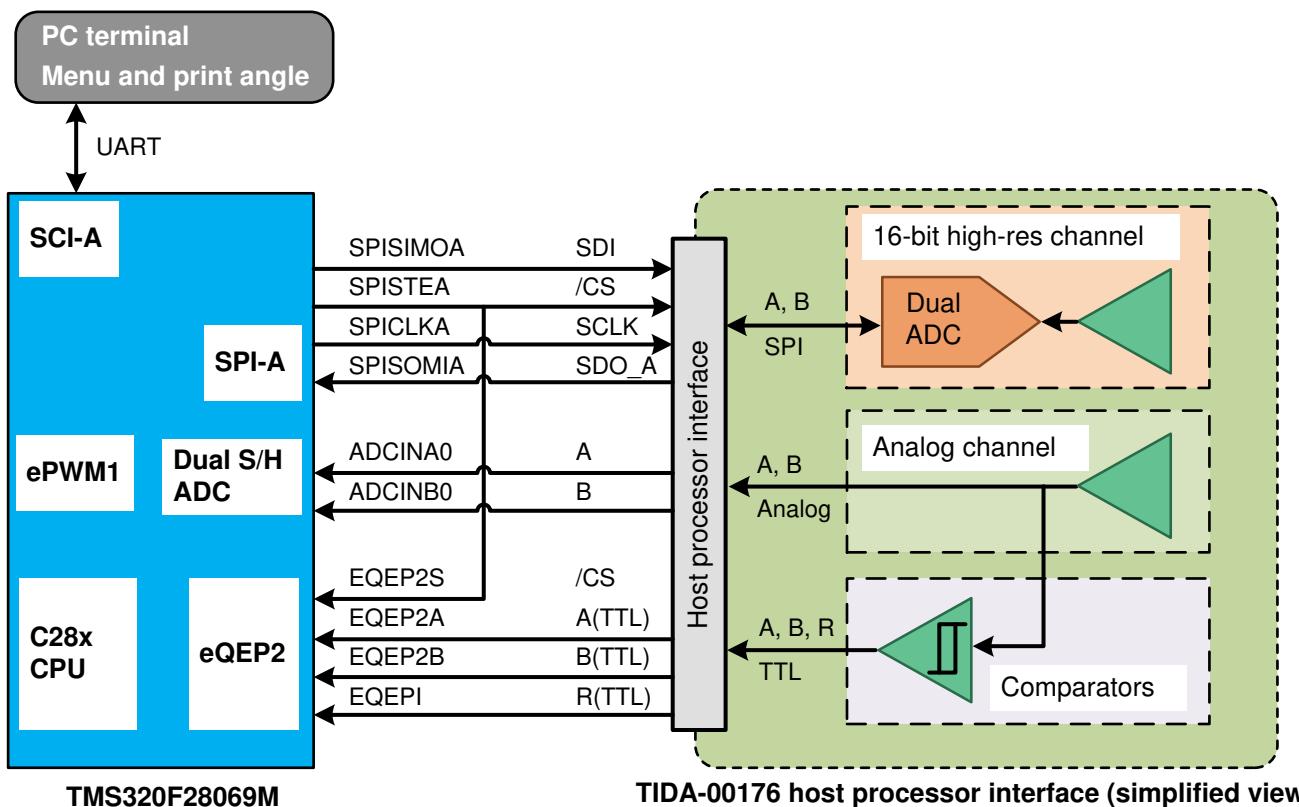

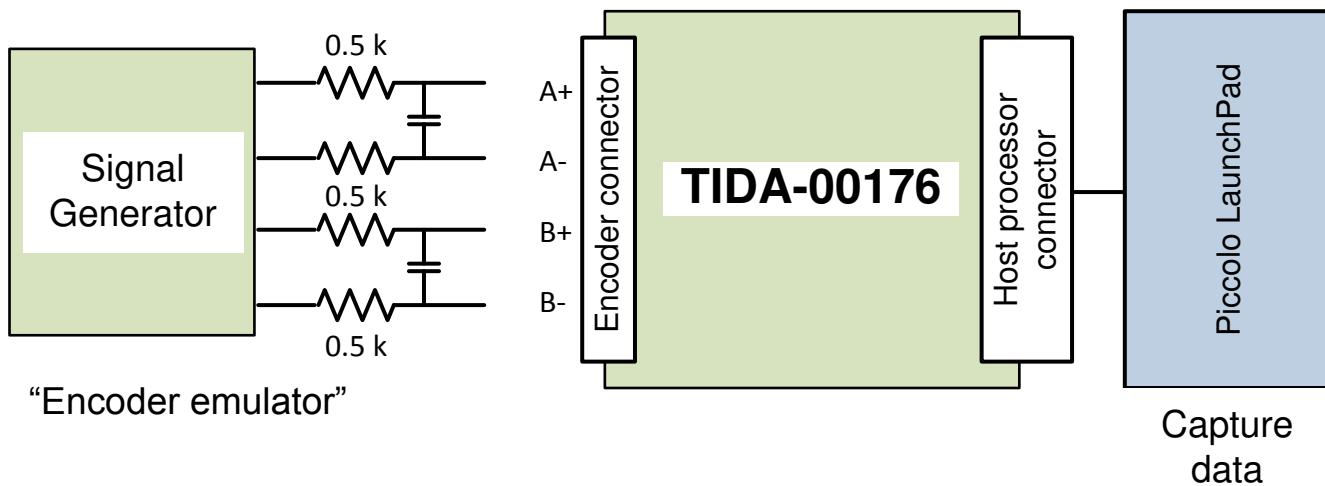

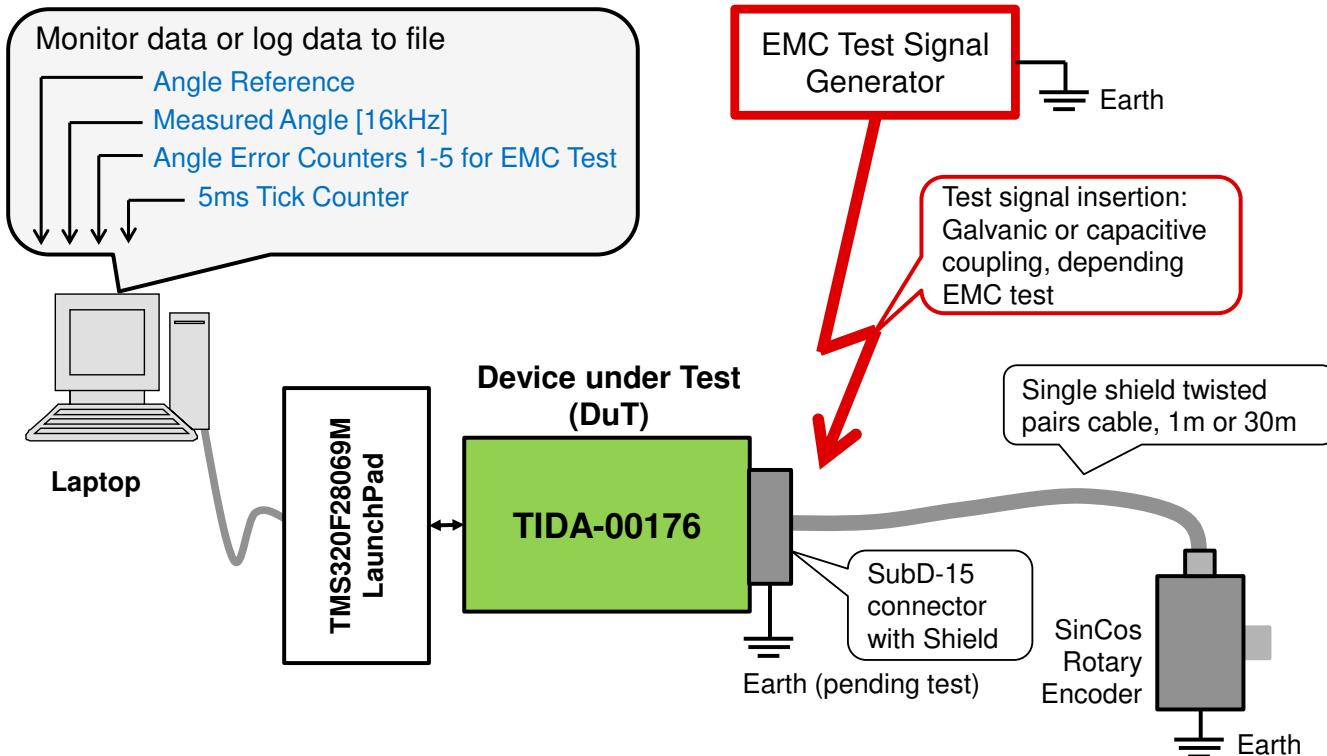

この TI 設計は、 $1V_{PP}$  の差動アナログ出力信号、最高 500kHz の周波数、5V 電源電圧を使用し、Sin/Cos インクリメンタルポジションエンコーダに対する産業用温度、EMC 準拠のインターフェイスを実装するものです。この TI 設計の主要なビルディングブロックは、デュアルパスアナログシグナルチェーン、高速コンパレータブロック、パワー マネージメントブロック、Sin/Cos エンコーダへのインターフェイス、およびデジタル信号処理と高分解能位置計算用のホストマイコンへのインターフェイスです。システムブロック図を簡略化したものを [図 1-1](#) に示します。TI のハードウェア設計は薄緑色のボックスで示されています。

この設計ガイドを容易に評価できるように、TMS320F28069M InstaSPIN™-MOTION LaunchPad にはサンプルファームウェアが用意されています。TMS320F28069M は、両方のアナログ信号路の高分解能角度位置を計算します。一方のパスは、SPI を介した外部 16 ビットデュアル ADC を活用しています。もう一方のパスでは、F28069M 組込みデュアル S/H 12 ビット ADC を使用しています。角度は、最大 28 ビットの分解能と、USB 仮想 COM ポート経由で評価できる出力で計算されます。

図 1-1. Piccolo F28069M LaunchPad を使用した TIDA-00176 の概略システムブロック図

アナログシグナルチェーンは、EMC 保護付きで  $120\Omega$  の終端を実現します。差動  $1V_{PP}$  のサインおよびコサイン入力信号は、それぞれ増幅およびレベルシフトされます。デュアル信号路オプションは、SPI 付きのオンボード高速デュアル 16 ビット同時サンプリング ADC と、1.65V バイアス電圧を備えたデュアルアナログシングルエンド出力が含まれており、C2000™ Piccolo リアルタイム MCU ファミリなどのデュアル S/H ADC 内蔵マイコンとの接続を可能にします。

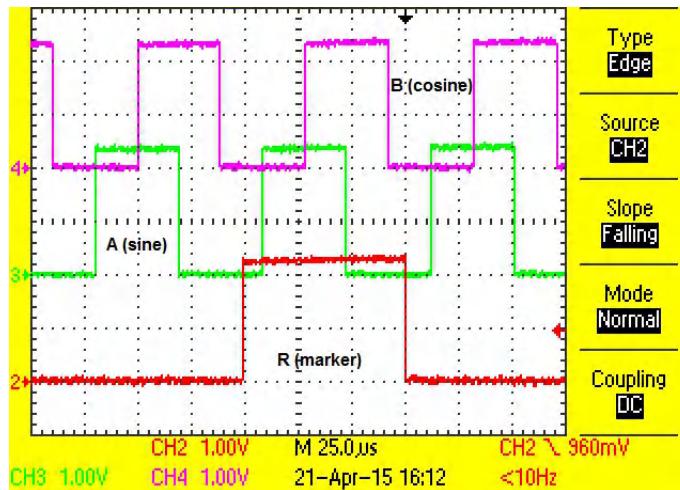

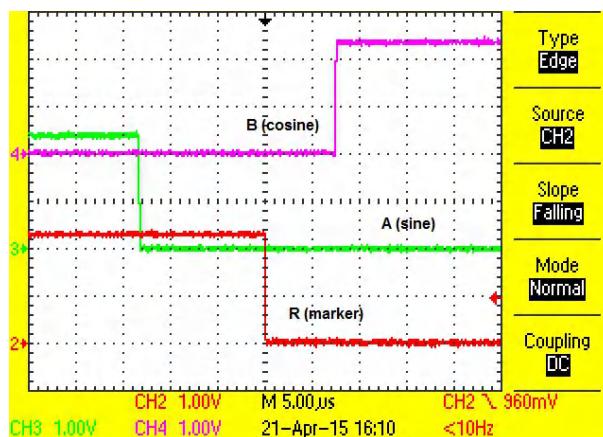

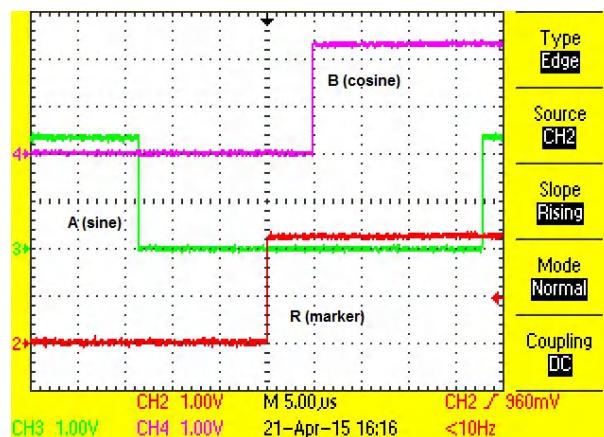

このコンパレータブロックは、高速で低伝搬遅延の調整可能なヒステリシスを採用しており、ノイズ耐性を向上させることができます。また、アナログ信号 A、B、マーカー R を 3.3V TTL レベルでデジタル信号に変換し、C2000 Piccolo MCU 上の QEP モジュールなどの直交エンコーダパルスモジュールとのインターフェイスを確立します。

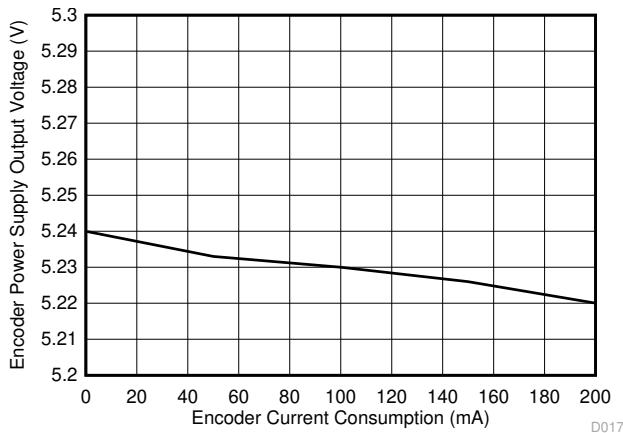

入力範囲が広いオンボードの 24V 電源により、アナログシグナルチェーンに必要な電圧や、Sin/Cos エンコーダに必要な 5.25V 電源電圧を供給します。

Sin/Cos エンコーダを、15 ピンのシールド付き Sub-D コネクタまたは 8 ピンヘッダーのいずれかに接続できます。ホストプロセッサへのインターフェイスとして、1.65V バイアス電圧によって 0 ~ 3.3V の範囲でアナログシングルエンドの信号

A および B を供給し、3.3V I/O を使用して SPI および A、B、R 用のデジタル信号を供給します。デジタル出力信号 A、B、R は、しばしば **ABZ** 信号と呼ばれます。

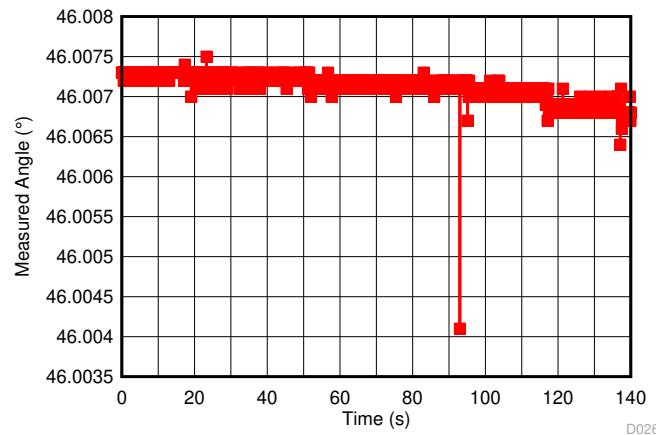

この設計は、EMC 耐性要件および可変速度、電力駆動システムに適用可能な特定のテスト方法に関する規格 IEC 61800-3 に規定されている IEC61000-4-2、4-4、4-5 (ESD、EFT、サージ) に対してテストされています。

## 1.2 アナログ Sin/Cos インクリメンタル エンコーダ

多くのアプリケーションで、インクリメンタル ロータリーまたはリニア位置エンコーダは、角度またはリニア位置と速度を測定するために使用されています。アプリケーションに応じて、TTL/HTL 出力信号またはアナログ正弦波出力信号を採用したエンコーダを使用します。後者はしばしば **Sin/Cos** エンコーダと呼ばれます。アナログ Sin/Cos インクリメンタル エンコーダは、高分解能の位置測定を可能にします。正弦波インクリメンタル信号の高い品質により、デジタル速度制御において高い補間係数を可能にします。応用分野としては、電気モーター、工作機械、印刷機、木工機械、繊維機械、ロボット、ハンドリング デバイス、各種測定装置、試験装置、検査装置などがあります。

### 1.2.1 Sin/Cos エンコーダ出力信号

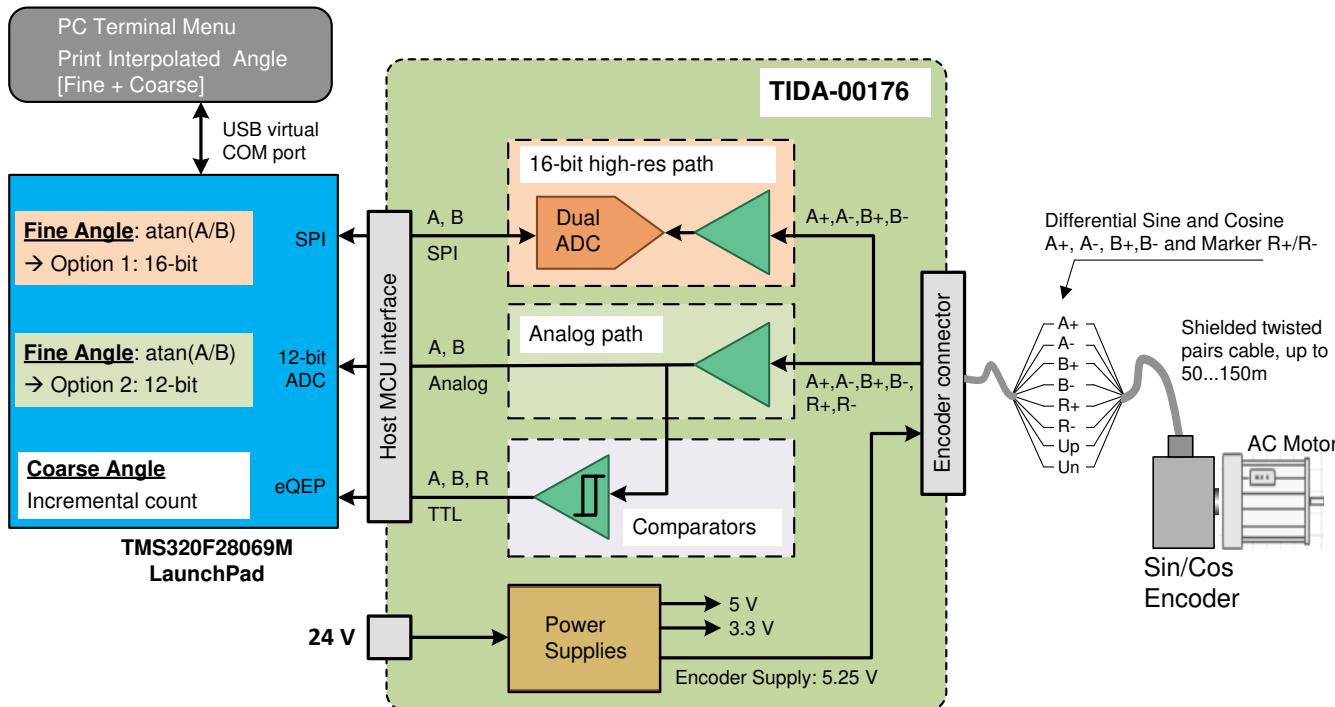

通常、エンコーダを使用して実装する 2 つのセンシング方法があり、光学または誘導性センシングのいずれかをベースとします。光学式ロータリー エンコーダでは、エンコーダ ディスクが光線を変調し、その強度が光電管によって感知されます。これらにより、2 つの 90 度位相シフトされた正弦波インクリメンタル信号 A および B が生成されます。B は、エンコーダのシャフトから時計回りに回転すると A から遅れます。力学的回転 1 回転分の信号 A と B の周期数は、エンコーダのライン数 N に等しくなります。さらにトラックには、力学的回転ごとに 1 回発生するリファレンス マーカー R が流れます。リファレンス マーカーを使用すると、絶対角度位置測定が可能です。

図 1-2. 力学的回転 1 回転分の Sin/Cos エンコーダの単純化されたサインおよびコサイン信号、ライン数 16

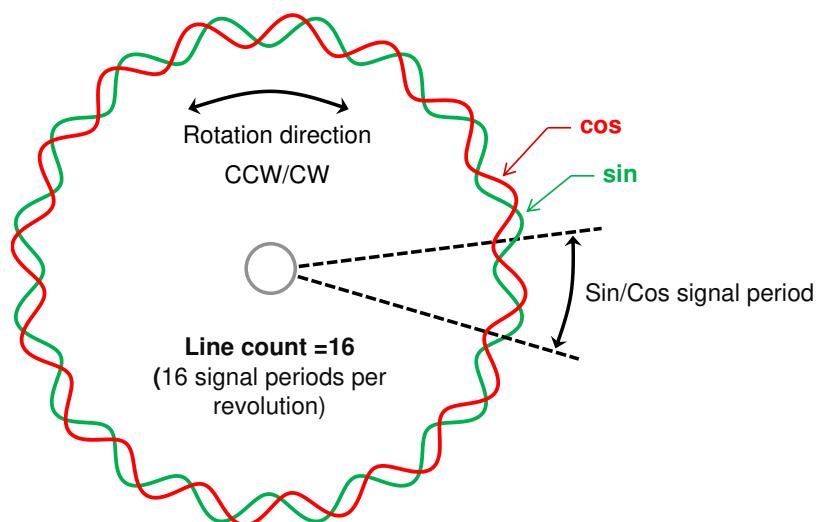

1V<sub>PP</sub> インターフェイスを持つ Sin/Cos エンコーダは、1V<sub>PP</sub> で差動アナログ出力信号 A (A+、A-) と B (B+、B-) を提供し、通常は 2.5V の DC オフセットを提供します。差動リファレンス マーク信号 R (R+、R-) は一般的に振幅がわずかに小さく、ピークは 1 回転ごとに 1 回だけ発生します。図 1-3 に、差動出力信号 A、B、R を示します。A、B、および R は、それぞれ A+ マイナス A-、B+ マイナス B-、および R+ マイナス R- の差動信号を表しています。

図 1-3. 1 回転あたりのライン数が N の Sin/Cos エンコーダの出力電圧信号 A、B、およびマーカー R

Sin/Cos エンコーダの差動出力信号の周波数は、式 1 に示すように、エンコーダのライン数と機械的速度に依存します。

$$f_{A,B} [\text{Hz}] = N \times v [\text{rpm}] \times \frac{1}{60} \quad (1)$$

N は Sin/Cos エンコーダのライン数を表し、v はエンコーダ シャフトの機械的速度を rpm 単位で表します。

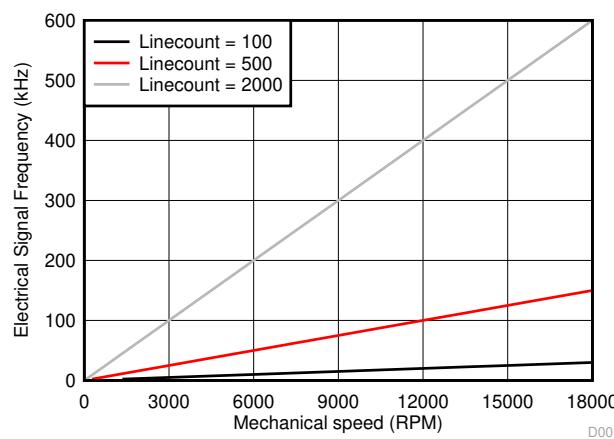

図 1-4 に、ライン数 N = 100、1000、2000 のエンコーダの出力周波数と機械的速度の比較を示します。

図 1-4. Sin/Cos エンコーダの出力信号 A および B の電気的周波数と機械的速度およびライン数との関係

たとえば、ライン数 N=2000 の Sin/Cos エンコーダは、12000rpm の機械的速度で動作し、信号 A と信号 B を 400 kHz の周波数で出力します。

### 1.2.2 Sin/Cos エンコーダの電気的パラメータの例

Sin/Cos エンコーダへの電気インターフェイス モジュールの要件を理解するために、産業用 Sin/Cos エンコーダ モデルをいくつか分析しました。対応するパラメータを 表 1-1 に示します。

**表 1-1. エンコーダの電源電圧例**

| SIN/COS エンコーダ モデル | 電源電圧         | 消費電流       |

|-------------------|--------------|------------|

| 1                 | 5V ± 0.5V DC | 120mA 未満   |

| 2                 | 5V ± 10%     | 150mA      |

| 3                 | 5V ± 5%      | 70mA (最小値) |

Sin/Cos エンコーダの電源は、この仕様の範囲内である必要があります。

アナログ信号チェーンは、信号の振幅、オフセット、および最大周波数に関して、少なくとも [表 1-2](#) に示す要件を満たすように規定する必要があります。

**表 1-2. エンコーダの出力信号 A、B の例**

| SIN/COS エンコーダ モデル | 信号レベル A、B                                        | DC オフセット   | ライン数 N        | 制限周波数 (-3dB) |

|-------------------|--------------------------------------------------|------------|---------------|--------------|

| 1                 | 0.6 ~ 1.2V <sub>PP</sub> 、1V <sub>PP</sub> (標準値) | 2.5V±0.5V  | 50~5000       | ≥180kHz      |

| 2                 | 1V <sub>PP</sub> (+20%、-40%)                     | 2.5V±0.5V  |               | 120 kHz      |

| 3                 | 1V <sub>PP</sub> (±10%)                          | 2.5V±100mV | 1024 または 2048 | 400 kHz      |

**表 1-3. エンコーダ出力信号マーカー R の例**

| SIN/COS エンコーダ モデル | 参照マークで使用可能な部品 G                                   | 静止値 H は参照マーク外 | DC オフセット |

|-------------------|---------------------------------------------------|---------------|----------|

| 1                 | 0.5V <sub>PP</sub> (標準値)、0.2V <sub>PP</sub> (最小値) | -1.7V         | 2.5V     |

**表 1-4. エンコーダの機械的パラメータの例**

| SIN/COS エンコーダ モデル | システム精度     | シャフトの機械的速度 |

|-------------------|------------|------------|

| 1                 | 格子周期の 1/20 | < 16000rpm |

## 1.3 Sin/Cos エンコーダを使用して高分解能位置を計算する方法

### 1.3.1 理論的アプローチ

#### 1.3.1.1 概要

ハードウェアの観点では、通常は 2 つのアプローチが実現します。これは主に A/D コンバータの要件に影響を及ぼします。

「オーバーサンプリング方式」を使用すると、サイン信号とコサイン信号の両方が、サインおよびコサインの最大周波数の 4 倍以上の高さでサンプリングされます。増分カウントおよび位相計算は、ホスト プロセッサに対する後続のデジタル信号処理によって行われます。この方法では、コンバータは必要なく、高速デュアル サンプリング ADC を使用します。

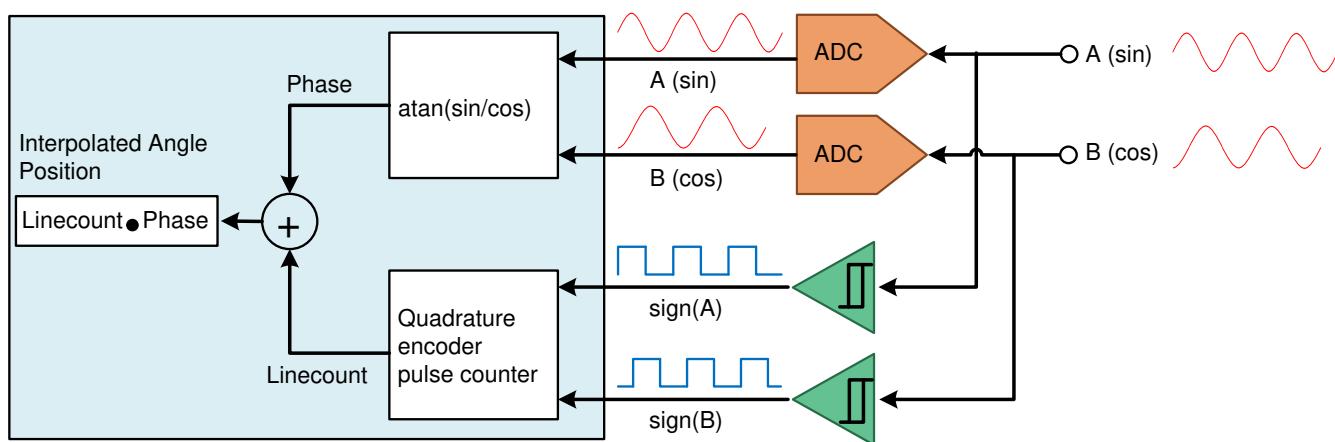

通常使用される「アンダーサンプリング」方式では、個別のハードウェア ブロックを使用して増分カウントと補間増分位相を計算します。この方法の利点は、増分カウントに影響を及ぼさずに補間した位相のみを示すため、最初の方法に比べて ADC のサンプリング周波数と帯域幅を低くできることです。ただし、アンダーサンプリング方式では、サインとコサイン用にそれぞれコンバータがデジタル直交エンコード信号 A と B を生成する必要があります、方向のアップ / ダウン カウンタ (直交エンコード パルス カウンタとも呼ばれます) を駆動します。デュアル サンプリング ADC のアナログ帯域幅は、少なくともサイン / コサインの最大周波数と同じ必要があります。アンダーサンプリング方法の概要を 図 1-5 に示します。

図 1-5. 補間角度計算の信号処理ブロック図

補間した合計角度位置は、粗い角度と細かい角度で構成されます。補間した角度は、実際の増分ライン カウントとこの増分ライン内の位相によって決定されます。増分ライン内の位相は、特定の時間における任意の時点でのアナログ サイン信号とコサイン信号 A および B から導出されます。実際の増分カウントと実際のアナログ サイン信号とコサイン信号の両方を同時にラッチする必要があります、つまり同期してラッチする必要があります。増分ライン カウントは粗い角度を提供し、その増分ライン内のサインとコサインの位相は細かい角度を提供します。補間した合計角度は、図 1-5 の簡略化されたブロック図に示すように、粗い角度と細かい角度の複合です。対応する 式 2 から 式 4 については次の段落で説明します。

### 1.3.1.2 粗分解能角度の計算

増分カウント、つまり増分粗角はカウンタによって決定できます。カウンタは **A** が先行シーケンスの場合はカウントアップし、**B** が先行シーケンスの場合はカウントダウンします。デジタル化すると、**A** と **B** の両方のエッジがカウントされます。このため、1 回の増分カウントは信号 **A** と **B** の両方の 90° 位相シフトに相当します。図 1-3 を参照してください。増分カウントは 0 から始まり、式 2 あたりの増分カウントの最大値  $incr_{MAX}$  を示します。ここで、**N** はライン カウントです：

$$incr_{MAX} = (4 \times N) - 1 \quad (2)$$

増分位置  $\Phi_{incr}$  は次のように計算できます：

$$\Phi_{incr} [\text{deg}] = \frac{360}{4 \times N} \times incr + \Phi_0 \quad (3)$$

ここで、 $incr$  は実際の増分カウント、 $N$  は合計ライン カウント、 $\Phi_0$  はゼロ角度で、使用する場合はリファレンス マーカー **R** によって決定されます。

### 1.3.1.3 詳細分解能角度の計算

正弦波信号 **A** と **B** の位相  $\phi_{A,B}$  は、2 つの連続するライン カウント、つまり 4 つの増分ステップ (互いに等価で) との間の角度を補間するために使用されます。位相  $\phi_{A,B}$  を次の式 4 で計算できます：

$$\phi_{A,B} [\text{deg}] = \begin{cases} 90^\circ + \tan^{-1}\left(\frac{B}{A}\right) & \text{if } A \geq 0 \\ 270^\circ + \tan^{-1}\left(\frac{B}{A}\right) & \text{if } A < 0 \end{cases} \quad (4)$$

エンコーダの回転速度と電源電圧に共通の関数である **A** と **B** の振幅比のみが使用されるため、結果には影響しません。

### 1.3.1.4 補間した高分解能角度計算

表 1-5 に従って増分カウント  $incr$  が位相  $\phi_{A,B}$  と一致すると、次のように合計補間角度  $\Phi_{TOTAL}$  がライン カウント  $N$  で計算されます：

$$\Phi_{TOTAL} [\text{deg}] = \frac{360^\circ}{N} \left( (incr \gg 2) + \left( \times \frac{\phi_{A,B}}{360^\circ} \right) \right) + \Phi_0 \quad (5)$$

#### 注意

正弦波信号 **A** および **B** と増分カウント  $incr$  を同時にラッチする必要があります。

表 1-5. 増分カウントと位相および位相象限との関係例

| 増分カウント | PHASE          | 象限 |

|--------|----------------|----|

| 0      | 0 ≤ 位相 < 90    | 1  |

| 1      | 90 ≤ 位相 < 180  | 2  |

| 2      | 180 ≤ 位相 < 270 | 3  |

| 3      | 270 ≤ 位相 < 360 | 4  |

| 4      | 0 ≤ 位相 < 90    | 1  |

### 1.3.1.5 非理想的な同期の実用化

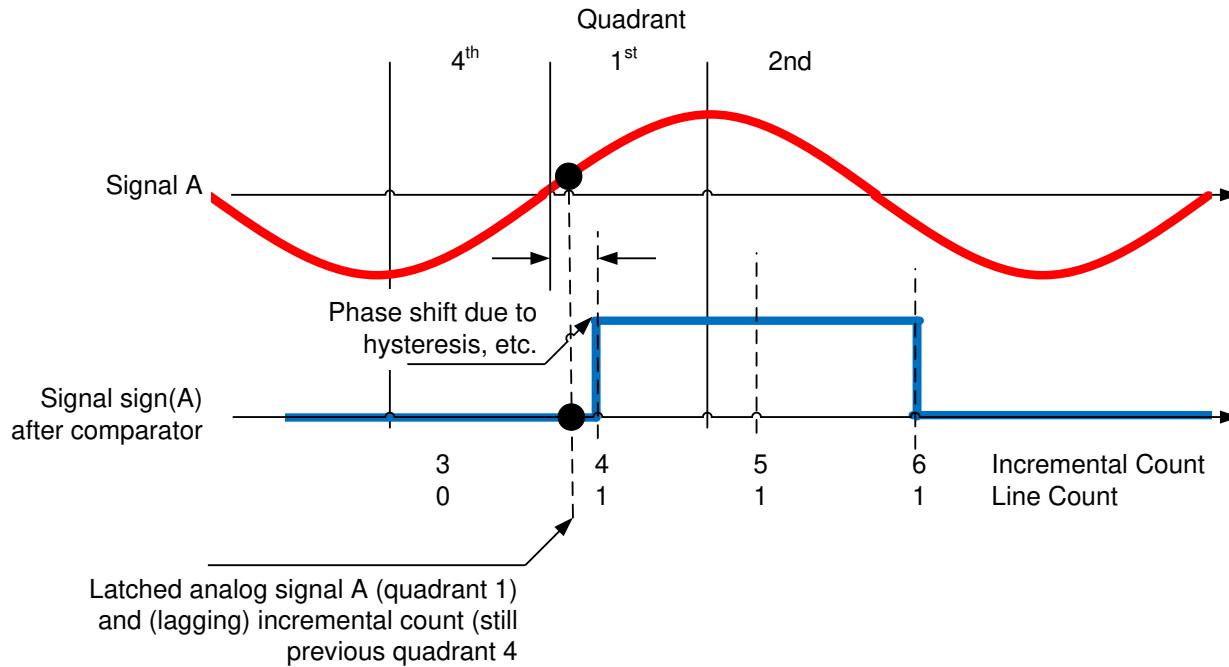

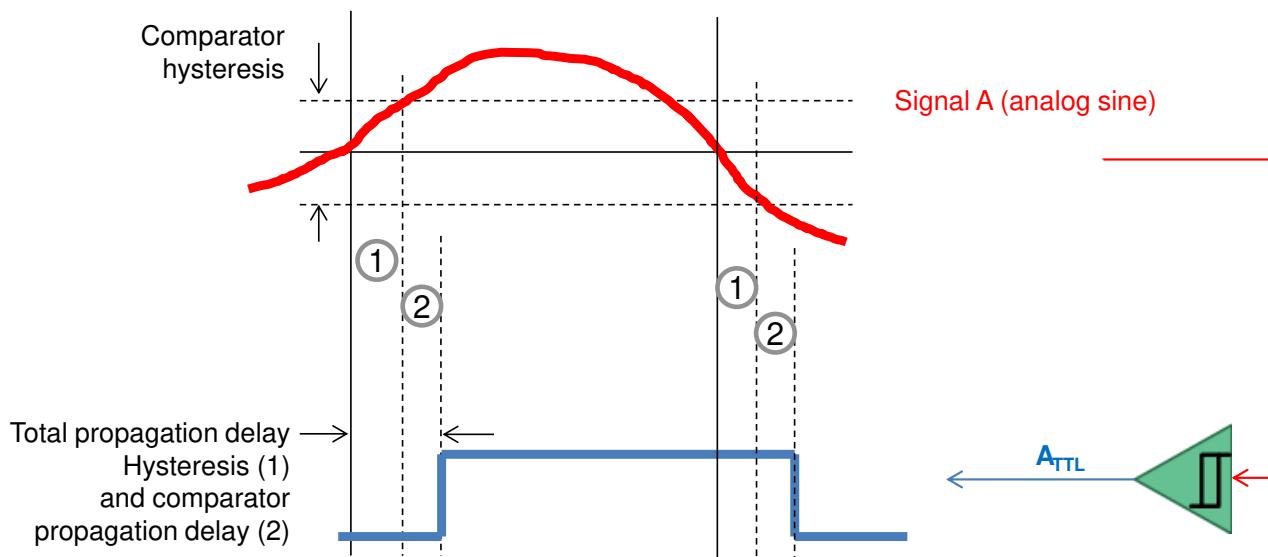

実際には、直交エンコーダのパルスカウンタに入力されるデジタル信号  $A_{TTL}$  および  $B_{TTL}$  は、通常、アナログ信号と比較して位相シフトを持ちます。これは主に、コンパレータのヒステリシスと伝搬遅延、および増分カウントのラッチとアナログ入力  $A$  と  $B$  のサンプリングとの間の非理想的な同期によるものです。

ヒステリシスが位相シフトに及ぼす影響は、信号周波数とはほとんど無関係ですが、信号振幅にはほぼ反比例します。アナログ信号のサンプリングと増分カウントのラッチとの間の伝搬遅延と非理想的同期の影響は、振幅とはほとんど無関係ですが、周波数に比例します。このため、最大位相シフトは、Sin/Cos エンコーダ周波数の最大値、最小振幅で発生します。

つまり、次の象限への各遷移では、たとえば 図 1-6 の第 1 象限に示すように、位相遅れのため増分カウンタはすぐに更新されません。

図 1-6. 位相遅れによるアナログ信号  $A$  に対する  $A_{TTL}$  の位相シフト

概説されている要因は省略できないため、これらのコーナー ケースを検出して修正するための方法を適用する必要があります。あいまいさがあるか、増分ラインカウントとアナログ位相の下位 2 ビットがあることから、位相シフトが  $\pm 90^\circ$  未満である限り、表 1-6 の概略としての補正方法を適用できます。

象限を識別するのに位相情報のみが使用されるため、考慮すべき例外は 2 つだけです。これらは、回転方向に応じて、第 4 象限から第 1 象限への遷移中または第 1 象限から第 4 象限への遷移中に発生します。

表 1-6. 補正方法

| 増分カウント [incr] | 位相 $\phi_{A,B}$ | 補正方法                                             |

|---------------|-----------------|--------------------------------------------------|

| incr%4 = 3    | 0 ≤ 位相 < 90     | incr = incr + 1<br>incr > 4 × N - 1 の場合、incr = 0 |

| Incr%4 = 0    | 270 ≤ 位相 < 360  | incr = incr-1<br>incr < 0 の場合、incr = 4 × N - 1   |

#### 注意

この補正方法は、アナログ  $A$  と  $B$  とデジタル信号  $A_{TTL}$  と  $B_{TTL}$  との間の位相シフトが  $\pm 90^\circ$  未満の場合にのみ機能します。

この設計のワーストケースの計算について、セクション 1.4 に概説します。

### 1.3.1.6 分解能、精度、速度に関する検討事項

理想的な補間角度分解能は、Sin/Cos エンコーダのライン カウントとデュアル ADC の分解能の関数です。等価補間した角度分解能は、次のように計算できます。

$$\Phi_{\text{RESOLUTION}} [\text{bit}] = \log_2(2 \times N) + \text{ADC}_{\text{RESOLUTION}} [\text{bit}] \quad (6)$$

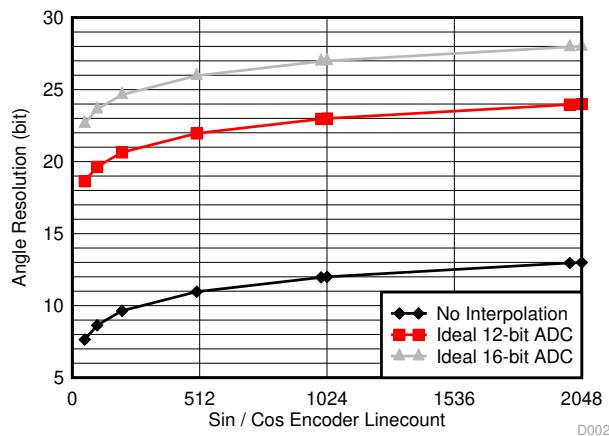

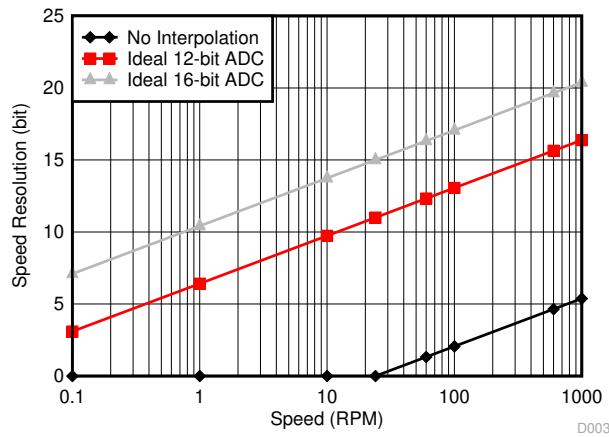

図 1-7 に、補間なし、理想的な 12 ビットによる補間、および 16 ビットのデュアル ADC 向けのライン カウントの関数として、達成可能な補間角度分解能を示します。

図 1-7. 理想的な補間角度分解能とライン カウントと ADC 分解能との関係

ADC のフルスケール入力範囲を使用する場合、16 ビットのデュアル ADC を使用した 2048 ライン カウントの Sin/Cos エンコーダでの理想的な分解能は、28 ビットに相当します。

この高分解能は通常、位置制御には必要ありませんが、特に機械的速度が低い場合には、非常に正確な速度制御に対して必要です。図 1-8 に、ローパスフィルタを使用せずにサンプル レート 1.6kHz で得られる理想的な速度分解能の概要を示します。これは、産業用ドライブの速度閉ループ制御が、16kHz 時に電流閉ループ制御や PWM に比べて 10 分の 1 未満で動作すると仮定しています。

図 1-8. 理想的な速度分解能と機械的速度との関係 (サンプル レート 1.6kHz)、および 1000 ライン カウントのエンコーダ

事実上、ローパスフィルタを適用すると、分解能やノイズ耐性を向上させるものの、フィルタ固有の伝搬 (グループ) 遅延やレイテンシが伴います。

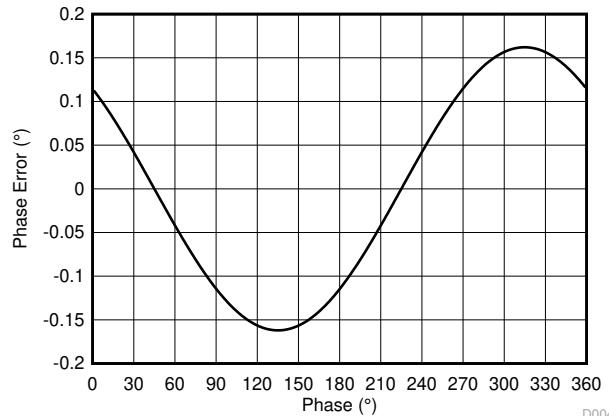

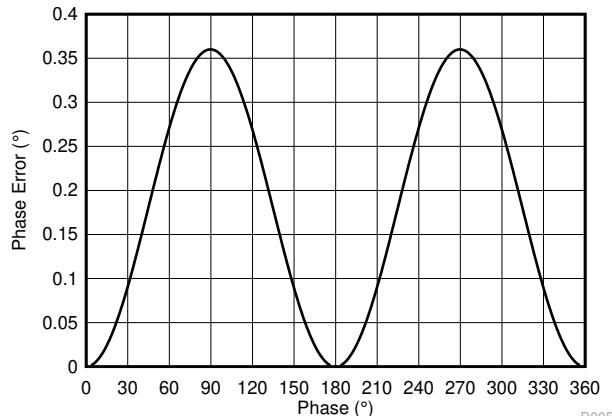

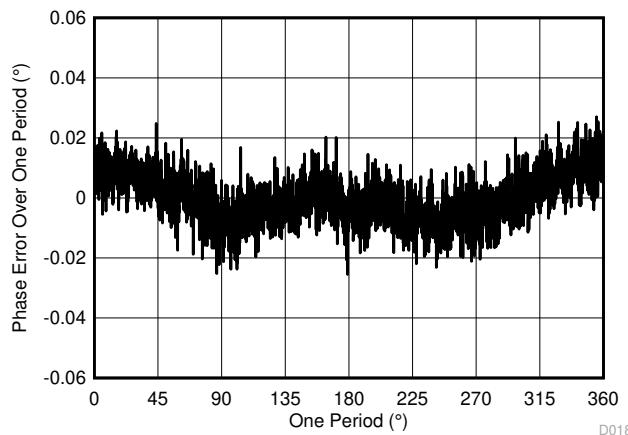

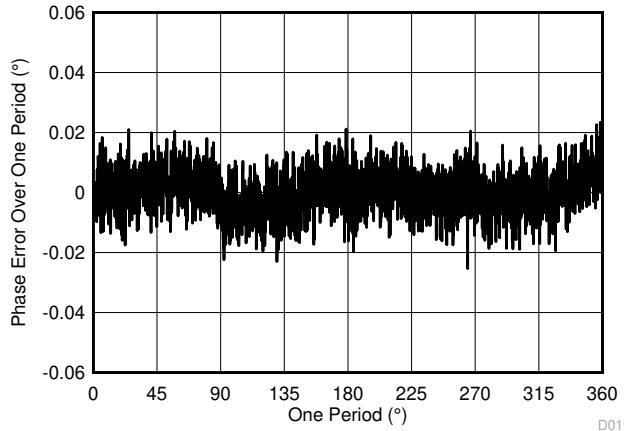

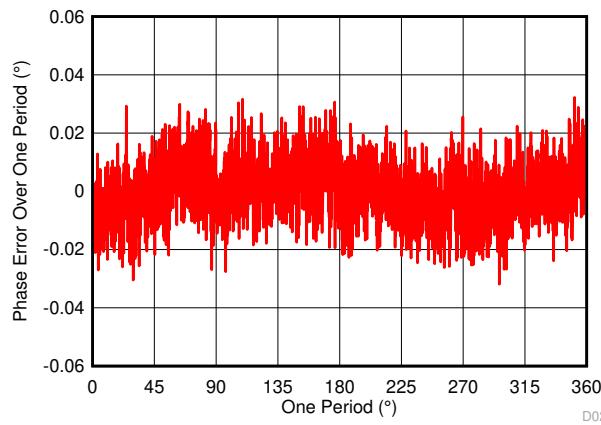

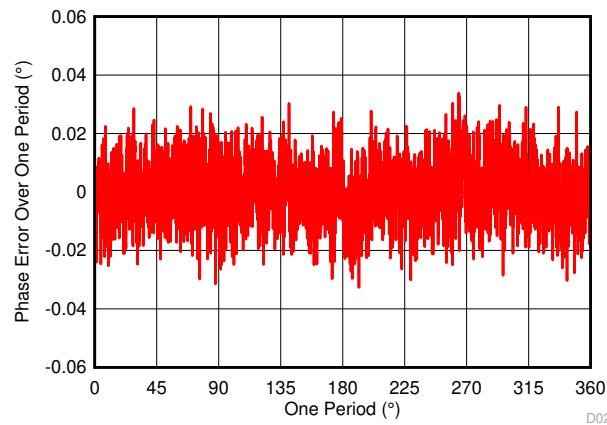

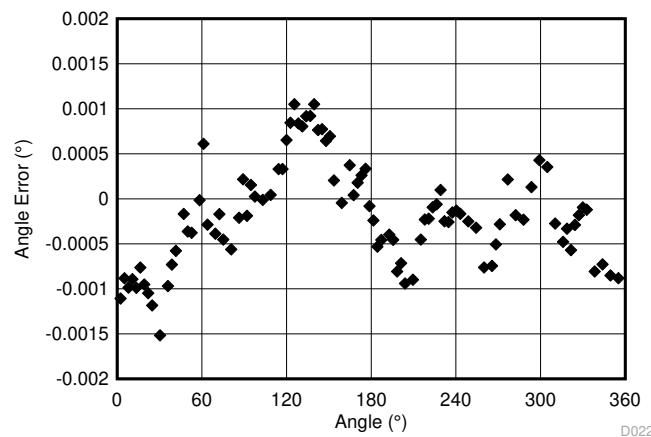

理想的な分解能 表 1-7、図 1-9、図 1-10 に続いて、量子化、オフセット、ゲイン、または位相誤差が補間角度に与える影響の概略を示します。

表 1-7. 位相誤差例の解析

| 誤差発生源                | 例                        | 位相誤差 [MAX]      |

|----------------------|--------------------------|-----------------|

| 信号 A と信号 B の量子化      | 12 ビット                   | 0.012% [0.045°] |

| 信号 A および B のオフセット誤差  | 0.1%                     | 0.05% [0.18°]   |

| 信号 A と B のゲイン誤差      | 0.1%                     | 0.04% [0.15°]   |

| 入力信号 A と B との間の位相シフト | $90 + 0.36^\circ$ [0.1%] | 0.1% [0.36°]    |

図 1-9. 信号 A および B での +0.1% オフセットの位相誤

差

図 1-10. 信号 A と B との間での位相シフト ( $90 + 0.36^\circ$ )

による位相誤差

入力信号 A と B との間の位相シフトにより発生する位相誤差は二重周期を示すことに注意してください。このシグネチャを活用して、信号処理アルゴリズムを使用して、一定の位相シフトの検出と補正を行うことができます。ただし、これらは本設計ガイドの範囲外です。

#### 1.4 アナログ回路仕様に対する Sin/Cos エンコーダ パラメータの影響

アナログ回路を指定するには、セクション 4 に示すように、次の Sin/Cos エンコーダ信号パラメータ (長いケーブルへの対応を含む) が考慮されています。

- Sin/Cos の最小および最大ピークツーピーク振幅: 差動  $0.3 \sim 1.2V_{PP}$ 、フルスケール入力範囲、50% 以上のヘッドルーム ( $1.8V_{PP}$ )

- Sin/Cos オフセット電圧範囲:  $2.5V \pm 1V$

- Sin/Cos 最大周波数:  $500kHz$

- Sin/Cos 最大スルーレート:  $> 2V/\mu s$

- Sin/Cos ライン終端:  $120\Omega \pm 1\%$

- エンコーダの電源電圧および電流:  $5V \pm 5\%$ 、 $200mA$

### 1.4.1 位相補間に関するアナログ シグナル チェーン設計の検討事項

特に高精度の速度制御向けに、高分解能アナログ シグナル チェーンは 16 ビットの分解能をサポートし、補間した角度分解能を実現します。

差動アナログ アンプの AC ノイズフロアと歪みは、16 ビットの分解能と一致している必要があります。 $1V_{PP}$  入力に関しては、これは約  $15\mu V$  に相当します。

- 入力電圧ノイズ:  $15\mu V/SQRT(1MHz) = 15nV/SQRT(Hz)$

- 入力電流ノイズ:  $15\mu A/SQRT(1MHz)/R_{INPUT}, R_{INPUT} = 1k$  の場合、 $15pA/SQRT(Hz)$  に相当

ゲインとオフセットはどちらも DC パラメータであり、そのドリフトは主に温度または経年変化に関係するもので、通常は非常に低速です。初期オフセットとゲインは、初期化時に較正が可能で、実行時でも特定のアルゴリズムを使用できます。したがって、これらのパラメータの要件をわずかに緩和できます。温度範囲全体でのゲインとオフセットのドリフトは、それぞれ  $10LSB$  の範囲にする必要があります。 $1V_{PP}$  の入力信号に関しては、これは約  $150\mu V$  に相当します。

- オフセットのドリフト [ $0 \sim 85^{\circ}C$ ]:  $150\mu V/85^{\circ}C \sim 2\mu V/^{\circ}C$

- ゲインドリフト: [ $0 \sim 85^{\circ}C$ ]:  $160ppm/85^{\circ}C \sim 2ppm/^{\circ}C$

ゲイン設定については、マッチング済み抵抗 (同じパッケージ) を推奨します。

### 1.4.2 増分カウント用のコンパレータ機能システムの設計

図 1-5 を再度参照してください: アナログ信号とデジタル信号 (500kHz 時の ATTLE および BTTL) との間の総伝搬遅延は  $90^{\circ}$  未満、500ns に相当する必要があります。ハードウェアの寄与率は約 50 ~ 70% 以下にする必要があります。これは 250 ~ 350ns に相当し、たとえばハードウェアに起因するオフセットや温度ドリフト、アナログ ローパス / デカッピング フィルタによる位相シフト、以後のホスト プロセッサにおける非理想的な同期などに対応するためのヘッドルームを確保するためです。

コンパレータへの最小  $0.3V_{PP}$  入力で  $160mV$  のヒステリシス ( $\pm 80mV$ ) があったとき、遅延に対するヒステリシスの寄与は約 32 度であり、つまり 500kHz の信号周波数で  $180ns$  です。

コンパレータの伝搬遅延が加算されます。コンパレータの伝搬遅延が短いほど、ヒステリシスを増やすためのヘッドルームや、システムのノイズ耐性を高めるための他の手段を適用することができます。

図 1-11. ヒステリシス付きコンパレータでの信号遅延

## 2 デザインの特長

セクション 1 で概説したように、この TI 設計は、最高 500kHz の入力周波数と 5V 電源電圧による差動 1V<sub>PP</sub> アナログ出力信号 A、B、マーカー R を使用し、Sin/Cos インクリメンタル ポジション エンコーダに対する産業用温度、EMC 準拠のインターフェイスを実現しています。この TI 設計の主要なビルディング ブロックは、デュアル パス アナログ シグナル チーン、高速コンパレータ ブロック、パワー マネージメント ブロック、Sin/Cos エンコーダへのインターフェイス、および デジタル信号処理と高分解能位置計算用のホスト マイコンへのインターフェイスです。

この TI 設計を容易に評価できるように、TMS320F28069M InstaSPIN-MOTION LaunchPad にはサンプル フームウェアが用意されています。TMS320F28069M は、SPI 経由の外付け 16 ビット ADC と内蔵のデュアル S/H 12 ビット ADC を使用して、両方の信号路の高分解能角度位置を計算し、USB 仮想 COM ポート経由で最大 28 ビットの分解能で角度位置データを出力します。

### TIDA-00176 機能の概要

- 幅広い入力電圧範囲: 逆極性保護機能を備えた 24V (17 ~ 36V) により、アナログ シグナル チーンに必要な電圧や、Sin/Cos エンコーダに必要な 5.25V の電圧を供給します。

- エンコーダのインターフェイス: 2.5V  $\pm$ 1V オフセットで 0.3V ~ 1.2V<sub>PP</sub> の差動出力信号 A、B、マーカー R を持つ 5V Sin/Cos エンコーダへの Sub-D15 または 8 ピン ヘッダー インターフェイス、最高 500kHz の入力帯域幅。

- デュアル パス アナログ信号処理: SPI 付きのオンボード高速高分解能デュアル 16 ビット同時サンプリング ADC と、1.65V バイアス電圧を備えたデュアル アナログ出力を備えたデュアル パス オプションにより、外部デュアル S/H ADC との接続を可能にします。ノイズ耐性を高めるために 160mV のヒステリシスを調整可能な高速、低伝搬遅延のコンパレータにより、アナログ信号 A、B、R を 3.3V TTL 信号 (多くの場合 ABZ 信号と呼ばれる) に変換できます。

- 高分解能で角度位置を補間、最大 28 ビットの分解能、ケーブル長 70m までテスト済み。

- EMC 耐性: この設計は、EMC 耐性要件および可変速度、電力駆動システムに適用可能な特定のテスト方法に関する規格 IEC 61800-3 に規定されている IEC61000-4-2、4-4、4-5 (ESD、EFT、サージ) に対してテストされています。

- MCU QEP および SPI への 3.3V デジタル インターフェイス信号と、マイコン内蔵デュアル S/H ADC 用のオプションのシングルエンド アナログ 0 ~ 3.3V 出力によるホスト プロセッサとのインターフェイス。

- 評価用ファームウェア: 16kHz で高分解能デュアル角度位置計算機能を搭載した Piccolo F28069M マイコン向けのサンプル フームウェア。USB 仮想 COM ポートを介したユーザー インターフェイスにより、性能を簡単に評価できます。

### 2.1 Sin/Cos エンコーダ インターフェイス

この設計には、HEIDENHAIN エンコーダ テスト機器と互換性のあるシールド付き Sub-D15 メス型コネクタ、または差動出力信号 A、B、およびマーカー R を使用して 5V Sin/Cos エンコーダとのインターフェイスを行うための 8 ピン ヘッダ コネクタが用意されています。

表 2-1. Sin/Cos エンコーダ インターフェイス

| パラメータ                       | 標準値                                               | 備考                                                                                  |

|-----------------------------|---------------------------------------------------|-------------------------------------------------------------------------------------|

| エンコーダの電源電圧                  | 5.25V [ $\pm$ 5%]、200mA                           | 長いケーブルでの電圧降下を補償できるよう、追加の 0.25V マージンを得るために 5.25V が選択されています。<br>帰還抵抗の変更により、5V などに調整可能 |

| 入力信号                        | A+、A-、B+、B-、R+、R-                                 | 120 $\Omega$ 差動ライン終端                                                                |

| A+、A-、B+、B- の入力レベルおよび同相電圧範囲 | 0.3V ~ 1.2V <sub>PP</sub> 、2.5V $\pm$ 1.0V 同相モード  |                                                                                     |

| R+、R- の入力レベルおよび同相電圧範囲       | 0.2V ~ 0.85V <sub>PP</sub> 、2.5V $\pm$ 1.0V 同相モード |                                                                                     |

## 2.2 ホストプロセッサインターフェイス

信号 A+、A-、B+、B- の高分解能パスは、差動入力と SPI 出力を備えた高速、高分解能のデュアル 16 ビット同時サンプリング ADC が特長です。この機能ブロックの主な特長については、表 2-2 に概説します。

**表 2-2. ADC と SPI 出力を備えた 16 ビット高分解能チャネル**

| パラメータ                    | 標準値                      | 備考                                                       |

|--------------------------|--------------------------|----------------------------------------------------------|

| ゲイン A、B                  | 5.0 (0.1%)               | 整合シングル パッケージ ゲイン設定レジスタ (0.1%)                            |

| ゲインドリフト A、B              | 2ppm/°C                  | マッチング済みシングル パッケージ抵抗                                      |

| オフセット、A、B                | < 10LSB (16 ビット時)        | キャリブレーションなし                                              |

| オフセットのドリフト、A、B           | < 0.15LSB/°C             |                                                          |

| 帯域幅 (-3dB)               | ≥ 500kHz                 |                                                          |

| 量子化                      | 16 ビット                   | FSR = ±5V (ADS8354)<br>ドロップイン互換の 14 または 12 ビットバージョンを利用可能 |

| サンプリング周波数                | 最大 700kSPS               |                                                          |

| データ出力形式 A、B              | 16 ビットの 2 の補数            |                                                          |

| シリアル インターフェイス (SPI スレーブ) | 3.3V、最大 24MHz の SPI クロック | SPI フレームあたりデュアル 16 ビットデータ                                |

信号 A+、A-、B+ における並列の 2 番目のパスは、1.65V バイアス電圧を持つ A および B のシングルエンドアナログ出力を提供し、外部デュアル S/H ADC (例:C2000 Piccolo などのマイコンに組込み) と接続します。

**表 2-3. シングルエンド アナログ出力のアナログ チャネル**

| パラメータ                  | 標準値                             | 備考                                                           |

|------------------------|---------------------------------|--------------------------------------------------------------|

| シングルエンド アナログ出力 A および B | 0 ~ 3.3V、1.65V バイアス電圧 [50ppm/K] | 0 ~ 3V 入力および 1.5V バイアスを持つ ADC に適合するドロップイン互換の 1.5V 基準電圧を利用可能。 |

| ゲイン (A、B)              | 1.66 (0.1%)                     | 可変、0.1% 抵抗を推奨                                                |

| オフセット (A、B)            | < 1mV                           | キャリブレーションなし                                                  |

| オフセットのドリフト (A、B)       | < 2μV/°C                        |                                                              |

| 帯域幅 (-3dB)             | ~ 500kHz                        | 帯域幅調整用の調整可能な LP フィルタ                                         |

コンパレータ ブロックは、高速で低伝搬遅延のコンパレータが特長であり、ノイズ耐性を高めるために 100mV のヒステリシスを調整可能で、アナログ信号 A、B、R を 3.3V TTL に変換できます。

**表 2-4. コンパレータ**

| パラメータ                  | 標準値             | 備考                             |

|------------------------|-----------------|--------------------------------|

| デジタル出力信号 A、B、R         | 3.3V TTL        |                                |

| ヒステリシス                 | ~ 160mV (±80mV) | ノイズ耐性を向上するため、帰還抵抗の変更により調整可能    |

| 伝搬遅延                   | ~ 40ns          | 低伝搬遅延                          |

| 最大位相遅延 (伝搬遅延およびヒステリシス) | < 60°           | 0.3V <sub>PP</sub> 時、500kHz 入力 |

## 2.3 評価用ファームウェア

TIDA-00176 設計の迅速な評価を可能にする Piccolo F28069M マイコン用のサンプル ファームウェアが提供されています。このファームウェアでは、16 ビット デュアル ADC である ADS8354 と、F28069M マイコンの組込みデュアル S/H 12 ビット ADC の両方に対して、補間した高分解能角度を計算します。115000 ポーの USB 仮想 COM ポートを介したユーザー インターフェイスにより、性能を簡単に評価できます。

115000 ポーの仮想 COM ポートを介したユーザー インターフェイスでは、次の機能がサポートされています。

- Sin/Cos エンコーダのライン カウントの選択: 最大 32000

- SPI を介して外部デュアル サンプリング 16 ビット ADC、内蔵 12 ビット デュアル S/H ADC、同期遅延 100ns 未満の増分カウンタを、ハードウェアとソフトウェアで同期サンプリング

- 32 ビット、分数 Q28 形式で高分解能角度を実現。角度を 0 ~ 0.9999999 まで単位ごとにスケーリング、最大 28 ビットの補間角度分解能

- 索引マーカー R の最初の出現後に、自動的に絶対位置を初期化

- TIDA-00176 デザインに搭載されている 16 ビット デュアル ADC (ADS8354) と C2000 オンチップの 12 ビット デュアル S/H ADC の両方を使用して、合計角度、増分角度、位相の 10Hz での表示モードまたは 200Hz 更新レートでのデータダンプ モードをサポートするメニュー

- エンコーダが接続されていない場合、または差動入力電圧が 0.3V<sub>PP</sub> を下回った場合の診断エラーメッセージ

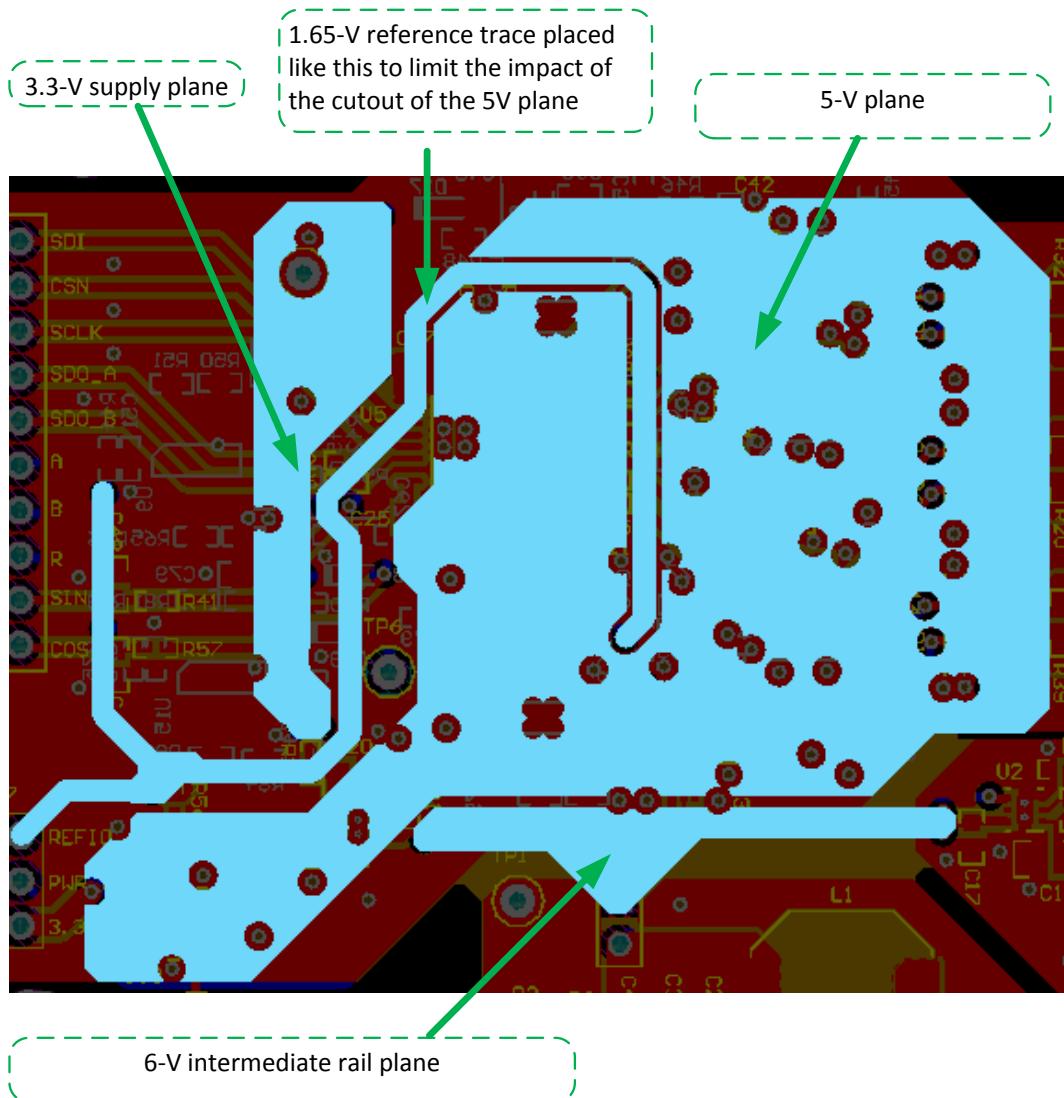

## 2.4 パワー マネージメント

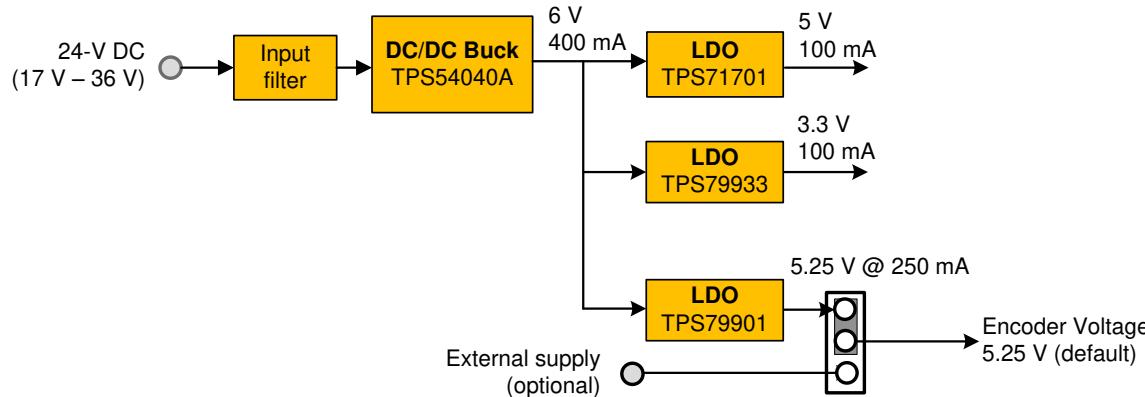

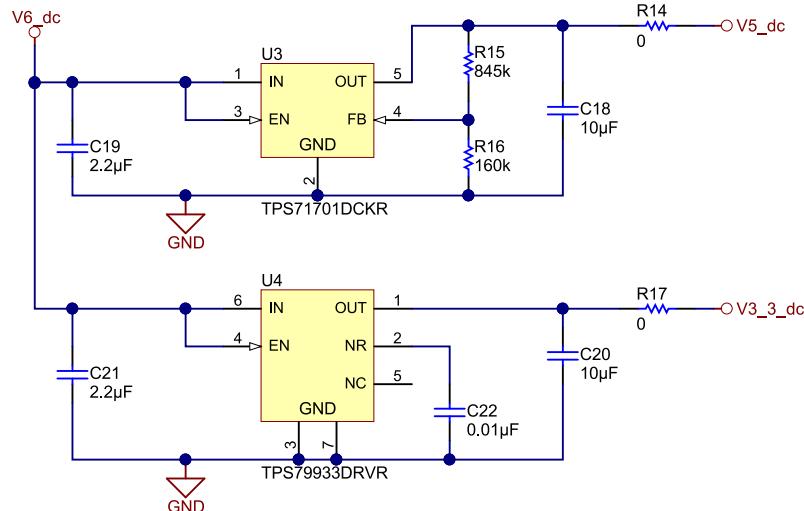

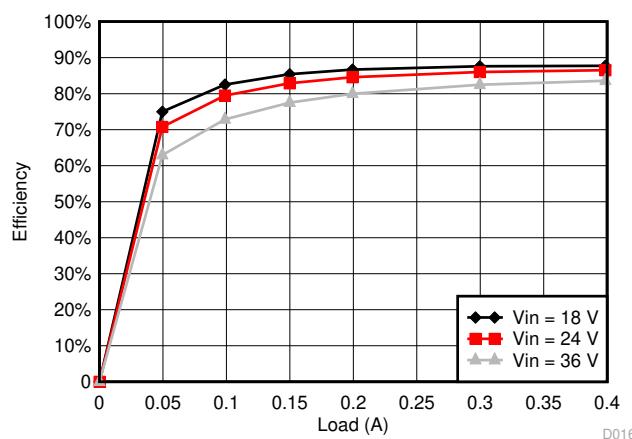

この TI 設計は、17V ~ 36V の広い入力電圧範囲に対応し、逆極性保護機能を備えた 24V DC 入力を特長としています。オンボードパワー マネージメントは、DC/DC 降圧コンバータに分割され、中間 6V レールと 3 つの LDO を生成します。これらの LDO は、対応する 3.3V、5V、5.25V レールを生成します。

5.25V エンコーダ電源は、超低ノイズ LDO およびイネーブル ピンを備えています。このため、Sin/Cos エンコーダの電源電圧は、必要に応じて、ホスト プロセッサを介してオフにできます。

表 2-5. TIDA-00176 電圧レール

| パラメータ      | 電圧             | CURRENT | 備考                                                                              |

|------------|----------------|---------|---------------------------------------------------------------------------------|

| 入力         | 24V [17 ~ 36V] | 150mA   | 広い入力電圧範囲に対応し、逆極性保護機能を搭載                                                         |

| 中間レール      | 6V [±5%]       | 500mA   | 中間レール。高効率 (>80%) の DC/DC 降圧電源                                                   |

| エンコーダ電源    | 5V [±5%]       | 250mA   | 長いケーブルでの電圧降下を補償できるよう、追加の 0.25V マージンを得るために 5.25V が選択されています。帰還抵抗の変更により、5V などに調整可能 |

| 5V 電源レール   | 5V [±5%]       | 100mA   | 高精度のシグナル チェーン供給                                                                 |

| 3.3V 電源レール | 3.3V [±5%]     | 100mA   | 低精度のシグナル チェーン供給                                                                 |

## 2.5 EMC 耐性

この設計は、IEC61000-4-2、4-4、4-5 の ESD、EFT、サージ要件を満たしており、IEC 61800-3 規格の「可変速度、電力駆動システムに対する EMC 耐性要件」で規定されているレベルで動作します。位置エンコーダへの SubD-15 コネクタのみアクセス可能で、エンコーダへの接続にシールド付きエンコーダ ケーブルを使用することを想定しています。エンコーダ ケーブルは

30m を超える可能性があるため、環境 2 で使用するために、表 2-6 に従って ESD、EFT、サージが適用されます。

**表 2-6. EMC 耐性要件**

| PORT                        | EMC テスト                | EMC 規格       | レベル                                                    | 性能(合格)基準 |

|-----------------------------|------------------------|--------------|--------------------------------------------------------|----------|

| Sin/Cos エンコーダ インターフェイス コネクタ | ESD                    | IEC61000-4-2 | CD が不可能な場合は ±4kV CD または 8kV AD                         | B        |

|                             | ファストトランジエント バースト (EFT) | IEC61000-4-4 | ±2kV/5kHz、容量性クランプ                                      | B        |

|                             | サージ 1.2/50μs、8/20μs    | IEC61000-4-5 | ±1kV シールド ケーブルが 20m 超であるため、シールドに直接結合 (2Ω のソース インピーダンス) | B        |

性能(合格)基準を以下のように定義します:

**表 2-7. 性能基準**

| 性能(合格)基準 | 説明                                                                                                |

|----------|---------------------------------------------------------------------------------------------------|

| A        | モジュールは意図した動作を継続すること。テスト実施中も機能や性能の損失がないこと                                                          |

| B        | 一時的な性能低下は許容される。テスト後、手動による介入なしに、モジュールは意図した動作を継続すること。                                               |

| C        | テスト実施中、機能の損失は許容されるが、ハードウェアやソフトウェアの破損はないこと。テスト後、手動による再起動、電源切断、電源投入のいずれかの後、モジュールは意図した動作を自動的に継続すること。 |

### 3 ブロック図

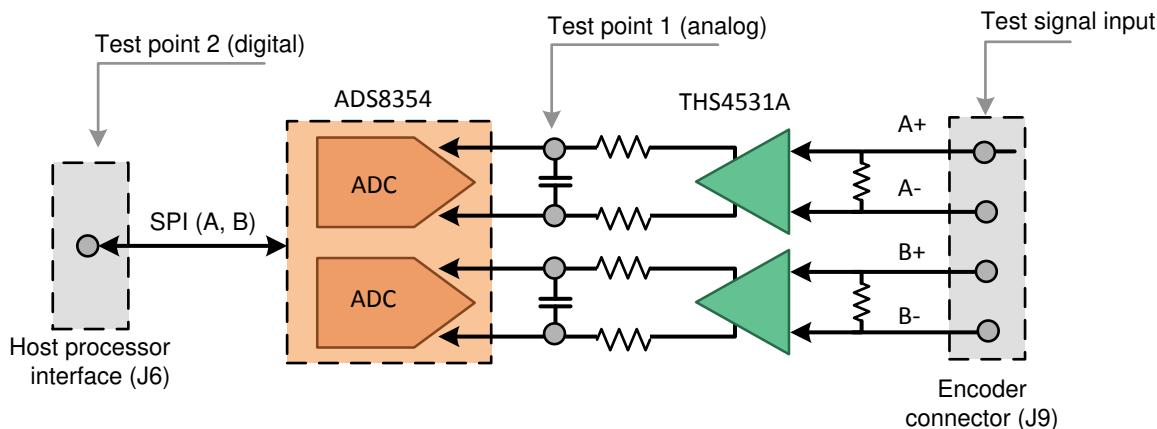

図 3-1 に、この設計のシステム ブロック図を示します。この TI 設計の主要なビルディング ブロックは、アナログ シグナル チェーンのデュアル パス、高速コンパレータ ブロック、パワー マネージメント、デジタル信号処理および高分解能位置計算用の Sin/Cos エンコーダおよびホスト マイコンへのインターフェイスです。TIDA-00176 設計を容易に評価できるように、F28069M Piccolo LaunchPad 向けにサンプル フームウェアが提供されています。このファームウェアは、仮想 COM ポート経由で角度位置を出力します。

図 3-1. Piccolo F28069M LaunchPad を使用した TIDA-00176 のシステム ブロック図

アナログ シグナル チェーンは、EMC 保護機能付きの  $120\Omega$  の終端を実現し、差動  $1V_{PP}$  のサイン入力信号とコサイン入力信号をそれぞれ増幅およびレベル シフトします。デュアル信号路オプションには、SPI 付きのオンボード ADS8354 高速デュアル 16 ビット同時サンプリング ADC と、 $1.65V$  バイアス電圧を備えたデュアル アナログ出力を持つアナログ パスが含まれており、たとえば C2000 Piccolo などの MCU に内蔵された外部デュアル S/H ADC との接続を可能にします。

この高速で低伝搬遅延のコンパレータ ブロックは、調整可能なヒステリシスを採用しており、ノイズ耐性を向上させることができます。また、アナログ信号 A、B、マーカー R を  $3.3V$  TTL レベルでデジタル信号に変換し、C2000™ Piccolo MCU 上の QEP モジュールなどの直交エンコーダ パルス モジュールとのインターフェイスを確立します。

入力範囲が広いオンボードの  $24V$  電源により、アナログ シグナル チェーンに必要な電圧や、Sin/Cos エンコーダに必要な  $5.25V$  を供給します。

Sin/Cos エンコーダ インターフェイスには、15 ピンのシールド付き Sub-D コネクタまたは 8 ピン ヘッダーがあります。ホスト MCU へのインターフェイスは、SPI、A、B、R 用のデジタル  $3.3V$  TTL 準拠信号のほか、 $1.65V$  バイアス電圧で  $0 \sim 3.3V$  にスケールされたアナログ信号 A および B を提供します。

## 4 回路設計と部品選定

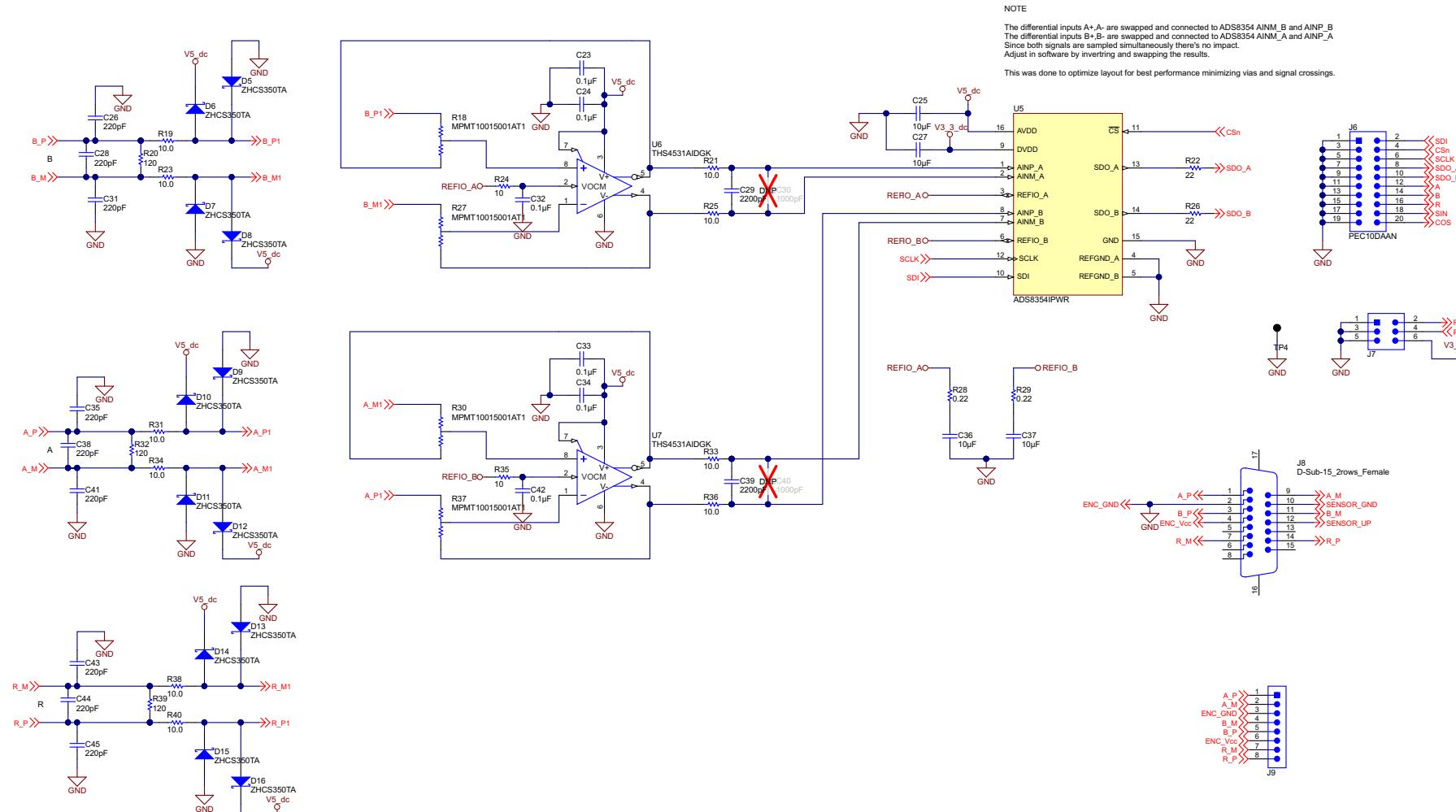

### 4.1 アナログ シグナル チェーン ガイド

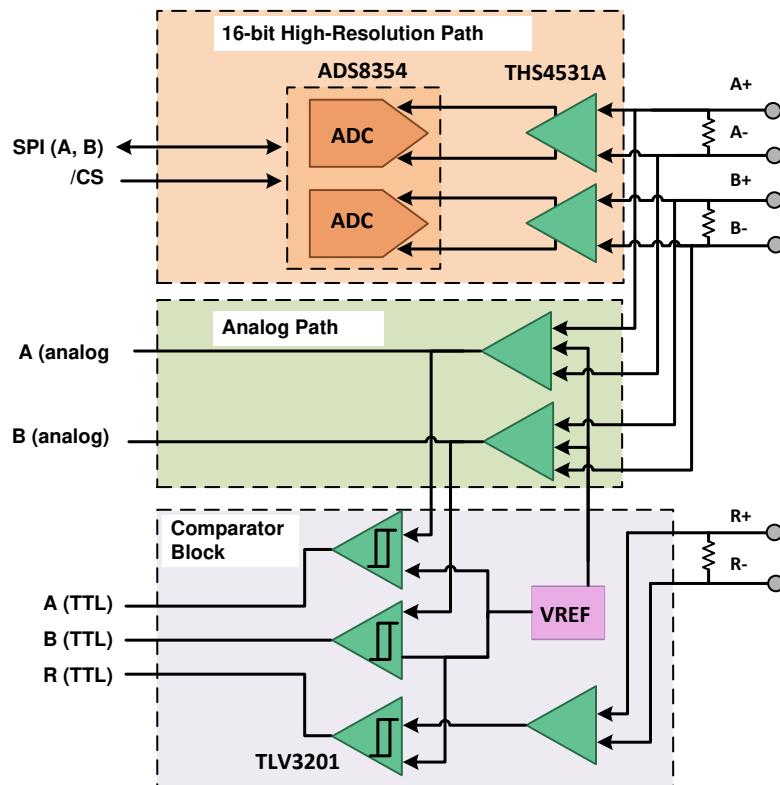

アナログ シグナル チェーン サブシステムとコンパレータ サブシステムの概要を [図 4-1](#) に示します。アナログ シグナル チェーンの場合、次の 2 つのパスが実装されています：

- 完全差動アンプと、SPI 出力を持つ完全差動デュアル 16 ビット ADC を備え、同相モードのノイズ耐性を向上した高分解能の信号路

- コンパレータを駆動するための差動入力シングルエンド アナログ出力を持つアナログ パスと、さらに ADC を内蔵したホスト プロセッサとのインターフェイスとして機能

このデュアル アナログ パスを使用すると、高分解能パスの一部としてオンボード 16 ビット デュアル ADC を使用して設計をテストすること、または ADC 内蔵のマイコンを使用してアナログ 差動からシングルエンドへの変換を行うパスを使用することができます。さらに、高分解能パスからバッファでデカッピングされるアナログ パスにより、コンパレータ パスの理想的なデカッピングが実現されます。これにより、正弦波と余弦波のゼロ交差中に出力レベルを切り替えるときに、高分解能アナログ パスへのクロストークが回避されます。

もう 1 つの使用事例では両方のパスを使用します。一方のパスは、HF ノイズをフィルタリングするために帯域幅を狭めてノイズ耐性を向上させ、もう一方のパスは、最高速度まで標準的な帯域幅を提供します。ノイズ耐性が向上した狭帯域幅は高分解能

16 ビット ADC 専用になり、標準帯域幅を持もう一方のパスは、ADC 内蔵のマイコンへ接続されます。その後、モーター速度が低い場合 (設定されているカットオフ周波数未満)、補間した位相 (アークタンジェント) は高分解能のパスから取得されますが、高速では、もう一方のパスからの補間した位相が使用されます。ホスト プロセッサは、保留中のモーター速度を使用する角度を決定します。

コンパレータ サブシステムは、非常に短い伝搬遅延で信号 A、B、R の TTL レベル出力を生成します。以下のセクションで、各サブシステムについて説明します。

図 4-1. アナログ シグナル チェーン ガイド

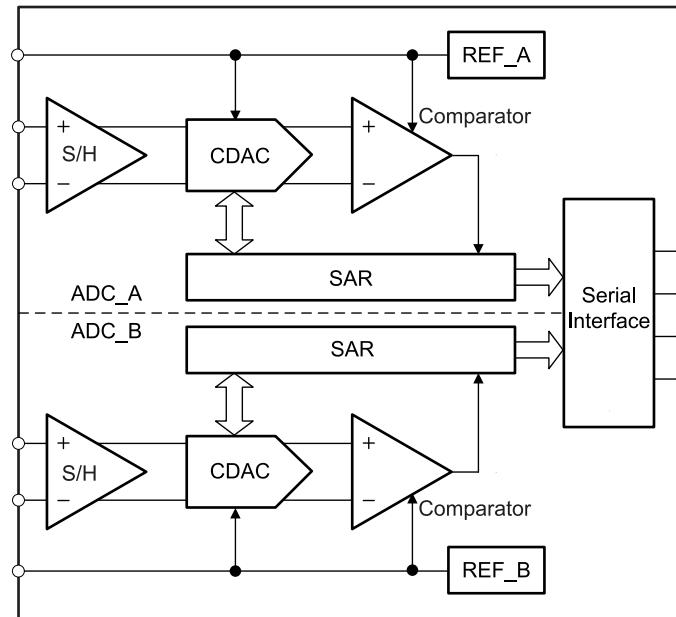

#### 4.1.1 16 ビット デュアル サンプリング ADC を使用する高分解能の信号路

##### 4.1.1.1 部品選定

設計要件を満たすには、高精度デュアル チャネル ADC が必要です。次の理由から、ADS8354 を選択しました。

- 高分解能 (16 ビット)、高精度 (非常に優れた THD および SNR 性能: -93dB SNR, -100dB THD)

- コスト最適化と比べて、必要な分解能に対するフレキシビリティを実現するドロップイン ピン互換性のある 14 ビットと 12 ビットの各バージョン

- 500kHz 以上のアナログ入力信号をサポートする高速 (700kSPS) と帯域幅

- 真の差動入力とデュアル / 独立したリファレンス電圧を搭載したデュアル チャネルで、同相ノイズ耐性を改善

- デュアル チャネル、2 つのチャネルの同時サンプリングにより、サインおよびコサイン入力信号 A および B との間で位相シフトがゼロであることを保証

- ハードウェア (I<sub>C</sub>S の立ち下がりエッジ) によってトリガされるサンプル ポイントを使用すると、ホスト プロセッサは増分カウンタ ラッチを使用して、サンプル ポイントを高精度で同期させることができます。

- サンプル / ホールド回路は、変換プロセスが完了した後でサンプル モードに戻るため、比較的長いサンプル時間で 16 ビット精度に安定

- デュアル、プログラマブル、バッファ付き 2.5V 内部リファレンスにより、アンプに同相モード バイアス電圧を供給し、オフセットおよびオフセットのドリフトに関連する誤差をほぼキャンセルできます。

- 最高 24MHz のクロック周波数でのホスト プロセッサ (デュアル データ) へのシリアル インターフェイスにより、レイテンシを最小化

- 拡張産業温度範囲の全体にわたって完全に仕様を規定: -40°C ~ 125°C

- 小型パッケージ

図 4-2. ADS8354 のブロック図

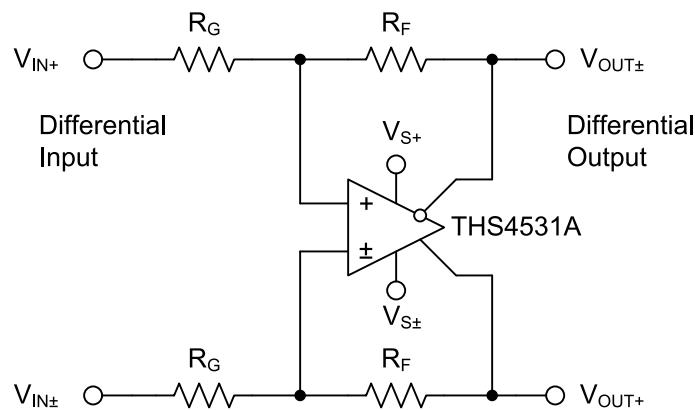

ADS8354 の性能を活用するには、THS45xx ファミリのように出力同相電圧を構成可能な完全差動高速アンプが必要です。

図 4-3. 差動入力 / 差動出力アンプ

信号は完全差動に維持されます。ゲインとオプションのフィルタリングは、入力抵抗と帰還抵抗、およびコンデンサによって定義されます。ゲインは  $RF/RG$  の比で設定され、出力同相電圧は入力信号  $V_{OCM}$  により設定されます。

THS4531A を選択したのは、トポロジを満たし、ADS8354 を駆動でき、[セクション 1.4](#) で規定されている AC および DC 要件を満たしているからです。THS4532 のようなパッケージ別のデュアル差動アンプではなく、パッケージ別のシングルアンプトポロジを採用することで、柔軟性を高め、PCB 配線を容易にしています。

この設計で使用する THS4531A の主要なパラメータは次のとおりです。

- 可変出力同相電圧を備えた完全差動アーキテクチャ

- 高ゲイン帯域幅: 27MHz (G = 5 で 6MHz)

- 低歪み、THD -120dBc (1kHz 時) ( $1V_{RMS}$ 、 $R_L = 2k\Omega$ )

- 小さい入力電圧ノイズ:  $10nV/\sqrt{Hz}$  ( $f = 1kHz$ )

- 非常に低いオフセット、 $V_{OS} = \pm 100\mu V$

- 非常に低いオフセットのドリフト、 $V_{OS}$  ドリフト:  $\pm 2\mu V/\text{°C}$  (産業用温度範囲)

- ADS8354 と同じ電源を活用できる単一 5V 電源

- レールツー レール出力 (RRO) と負のレール入力 (NRI) により、入力と出力の信号スイングを最大化

#### 4.1.1.2 入力信号の終端と保護

差動入力信号は、それぞれ  $120\Omega$  の抵抗で終端されます。差動および同相モード HF ノイズ除去のために、COG コンデンサを追加します。差動ローパスフィルタのカットオフ周波数

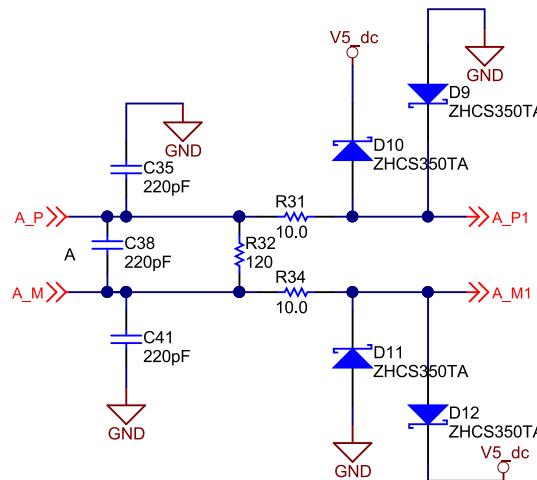

( $-3\text{dB}$ ) は、約  $6\text{MHz}$  です。 $10\Omega$  (1%) のパルス耐性抵抗とショットキー ダイオードを組み合わせて  $5\text{V}$  レールまたは GND にクランプし、入力電流制限による ESD 保護を実現します。図 4-4 に、エンコーダの差動信号 A+ (サイン) と A- (コサイン) の入力段の TIDA-00176 回路図を示します。

図 4-4. アナログ入力の終端

エンコーダ信号 A+/A- (回路図では「A\_P-A\_M」と名付けられています) シグナル コンディショニング ブロック回路図を左から右に見ると、以下の部品 / 機能を区別できます：

- HF ノイズ抑制 COG コンデンサ:C35、C38、C41。同相信号除去を高めるため、各差動入力から GND への  $220\text{pF}$  の COG コンデンサと並列に、追加の  $2\text{nF}$  の COG コンデンサを配置します。ローパスのカットオフ周波数 ( $-3\text{dB}$ ) は約  $6\text{MHz}$  です。

- インピーダンス整合 / 終端抵抗  $120\Omega$ :R32

- パルス耐性電流に対応する電流制限抵抗:R31、R34

- クランプ ダイオード / オペアンプの入力保護 (D9 から D12) を  $5\text{V}$  レールと GND に接続

LP フィルタは、システム仕様に規定された速度で正しい機能と性能を保証するように設計されています。

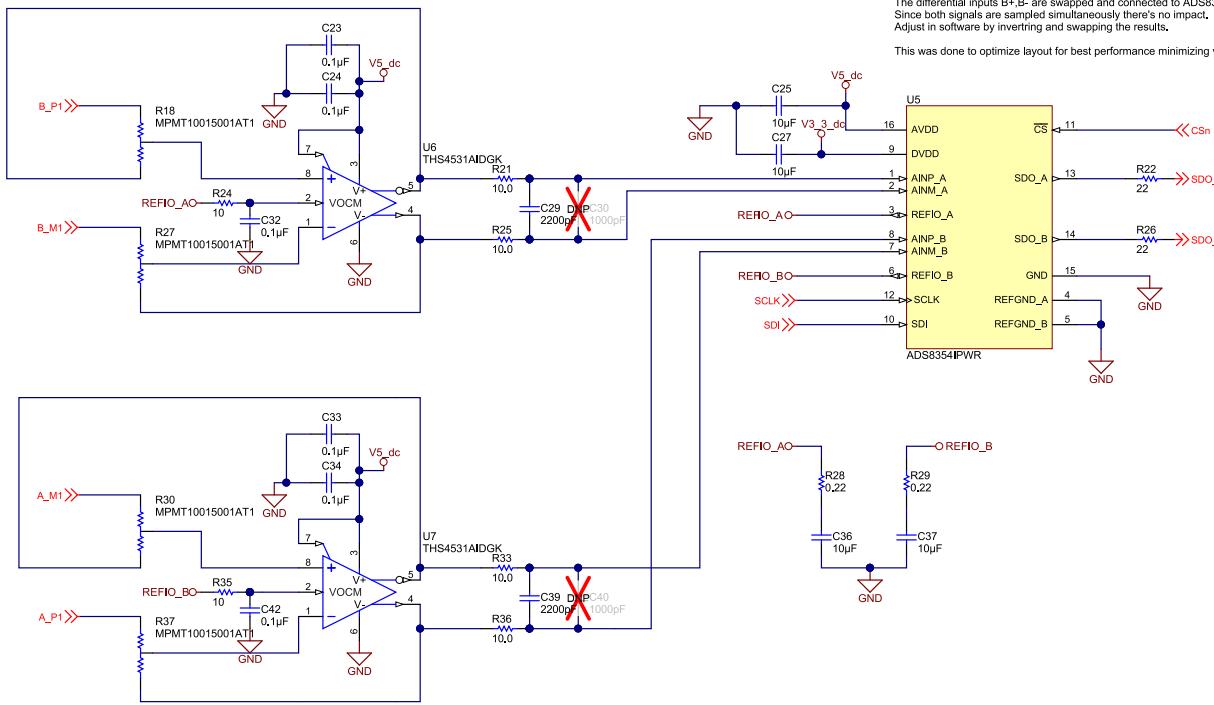

#### 4.1.1.3 差動アンプ THS4531A と 16 ビット ADC ADS8354

高精度の逐次比較型 (SAR) ADC の性能を最大化するために必要な 2 つの主要回路は、入力ドライバとリファレンスドライバ回路です。アンプ選択の詳細については、ADS8354 データシートのセクション 9.1 を参照してください。

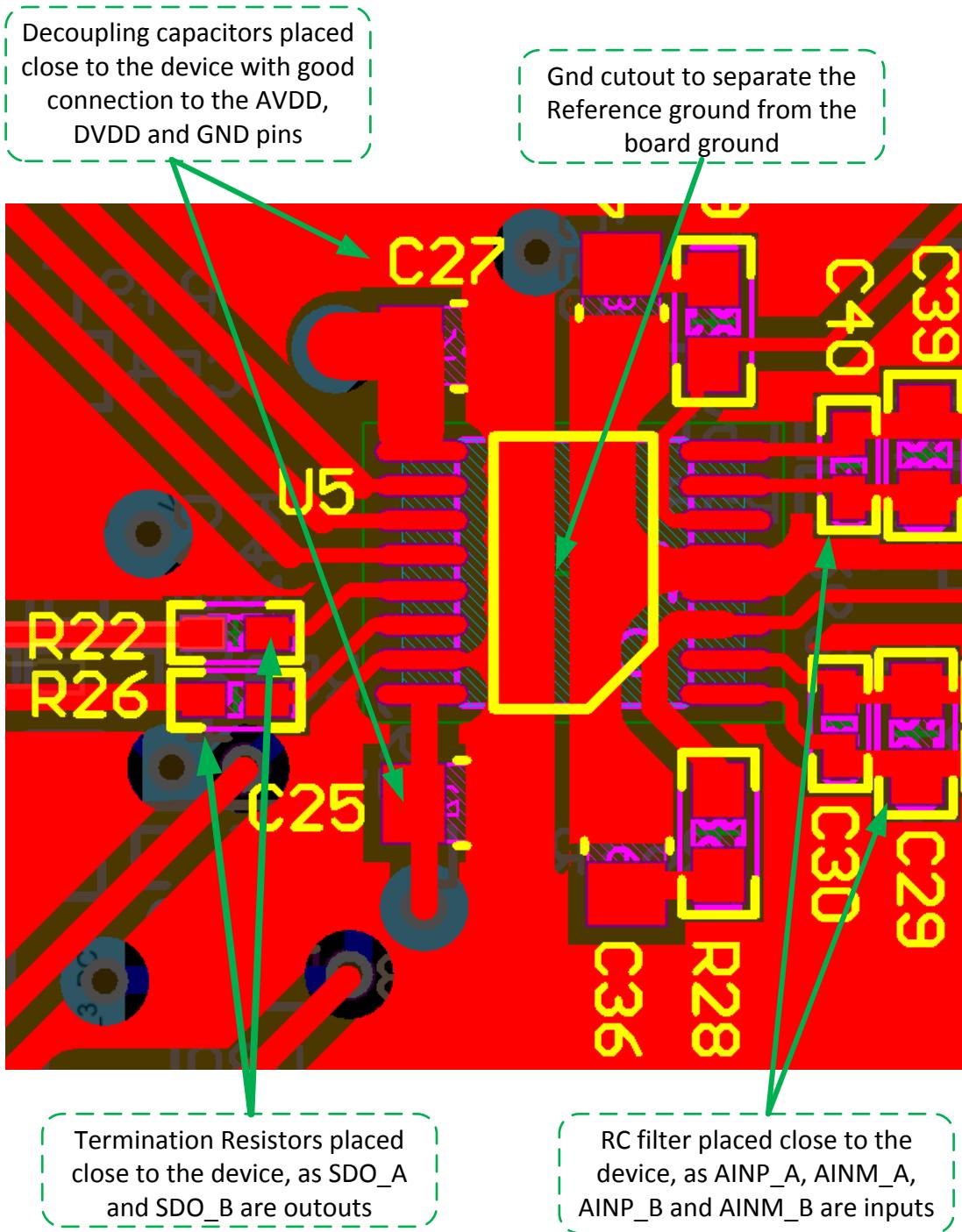

THS4531A は ADS8354 と組み合わせて動作することを考慮しています。実際、入力信号の同相モードまたは DC レベル (公称 2.5V) は、潜在的なオフセットとドリフト誤差を最小限に抑えるため、ADS8354 自体のリファレンス出力から直接 THS4531A に供給されます。

ADS8354 の差動入力フルスケールレンジは、 $\pm 2 \times V_{REF}$  に構成されます。リファレンス電圧が  $V_{REF} = 2.5V$  の場合、FSR は  $\pm 5V$  となります。Sin/Cos エンコーダの差動入力電圧の最大値は  $1.2V_{PP}$  です。 $1.35V_{PP}$  を超える電圧でも、障害として検出される必要があります。最大ピークツーピーク電圧に 50% の安全マージンを追加すると、電圧は  $1.8V_{PP}$  となります。ADC のフルスケール入力範囲を一致させるには、THS4531A のゲインを 5.5 にする必要があります。ただし、5V 電源において THS4531A のリニア出力電圧範囲を維持するには (少なくとも  $0.25 \sim 4.8V$ )、ゲインを約 10% 低減する必要があるため、理想的な差動アンプのゲインは 5 となります。

最小ゲイン誤差と、特にチャネル間のドリフトを確実にするには、0.1% 精度と  $2ppm/K$  の温度ドリフトを持つ高精度でマッチングされた抵抗が必要です。ノイズを最小限に抑えるため、低い  $k\Omega$  範囲の帰還抵抗を選択してください (セクション 1.4 を参照)。

高精度のマッチング抵抗分圧器を使用して、潜在的なゲイン誤差を可能な限り小さくします。詳細については、MPMT10015001AT1 のデータシートを参照してください。

ゲインが 5 のため、標準的な  $1V_{PP}$  の入力信号は ADC のフルスケールレンジ (FSR) の約 50% を利用し、その結果 1 ビットの精度が低下し、等価な 15 ビットの分解能が得られます。低入力電圧  $0.6V_{PP}$  では、FSR の約 25% を活用します。これは、通常は 14 ビットの分解能に相当します。

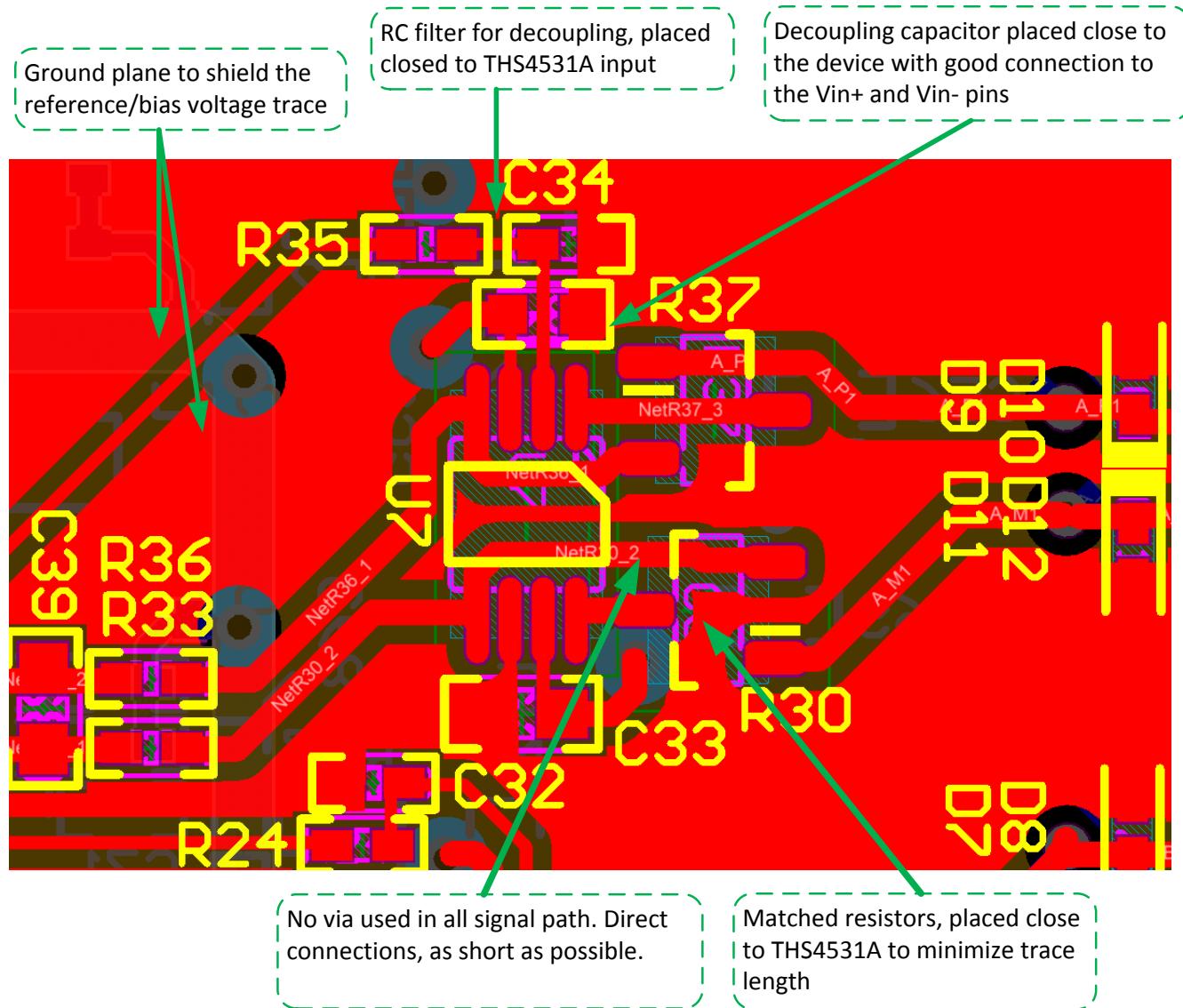

図 4-5 に、高精度アナログ信号路の回路図を示します。ここで、整合ゲイン設定抵抗は R18、R27、R30、R37 です。

アンチエイリアシング フィルタの  $10\Omega$  直列抵抗は R21、R25、および  $2.2nF$  コンデンサは C29 です (ADS8354 チャネル B の場合は R33、R36、C39)。ADC 入力に接続されたフィルタコンデンサ C29 (C39) は、フロントエンドドライブ回路からのノイズをフィルタ処理し、サンプリング チャージ インジェクションを低減して、アクイジション プロセス中に内部のサンプル / ホールド コンデンサを迅速に充電するためのチャージ バケットを提供します。目安として、このコンデンサの値は ADC サンプリング容量の指定値の 10 倍以上にする必要があります。これらのデバイスの場合、入力サンプリング容量は  $40pF$  です。これらのタイプのコンデンサは、高 Q、低温度係数、および電圧、周波数、時間の変化に対して安定した電気的特性を持つため、コンデンサには COG または NPO タイプを使用する必要があります。アンプの安定性の問題を回避するために、アンプの出力に  $10\Omega$  の直列絶縁抵抗 R21、R25 (R31、R39) を使用しています。詳細については、ADS8354 データシートのセクション 9.1 を参照してください。

ADC リファレンス REFIO\_A と REFIO\_B のオフセットのドリフトの影響を最小限に抑えるため、ADC リファレンス電圧を使用して THS4531A のコモンモード出力電圧をバイアスします。THS4531A の  $V_{OCM}$  信号をバッファおよびデカップリングするために、小型の RC フィルタ R24/C32 および R35/C42 R28、R29、C36、C37 を各ピンの近くに追加します。

ADS8354 のリファレンス電圧 REFIO\_A と REFIO\_B はそれぞれ  $10\mu F$  のコンデンサ C36 と C37 でデカップリングされており、 $0.22\Omega$  の抵抗を直列に追加して、高周波発振を防止しています。

重要な信号 A+、A-、B+、B- のビアを最小限に抑えてクロストークのレイアウトを最適化するため、以下の接続が行われています。

1. 差動入力信号 A (A+、A-) は THS4531A の入力で反転され、ADS8354 入力チャネル B に供給されます。

2. THS4531A、B+、B- の差動出力信号は、ADS8354 入力ピン AINP\_A から B-、AINM\_A から B+ に反転されています。

これにより、次のハードウェア関係が得られます。ADS8354 チャネル B は反転された Sin/Cos エンコーダ信号 A と等しく、ADS8354 チャネル A は反転された Sin/Cos エンコーダ信号 B と等しくなります。

図 4-5. デュアル THS4531A および ADS8354 を使用した Sin および Cos シグナル チェーン

### 注

最適性能のレイアウトを実現するために、チャネルは反転および交換されており、ビア数を最小化しています。

帯域幅の低減でノイズ耐性を向上させるには、希望する帯域幅に応じて、10pF 以上のコンデンサ (誤差 1% 以下) を 5kΩ と並列にフィードバック パスへ配置することを推奨します。セクション 4.5 を参照してください。

シリアル インターフェイスを介した ADS8354 レジスタの構成については、セクション 4.3 で説明します。

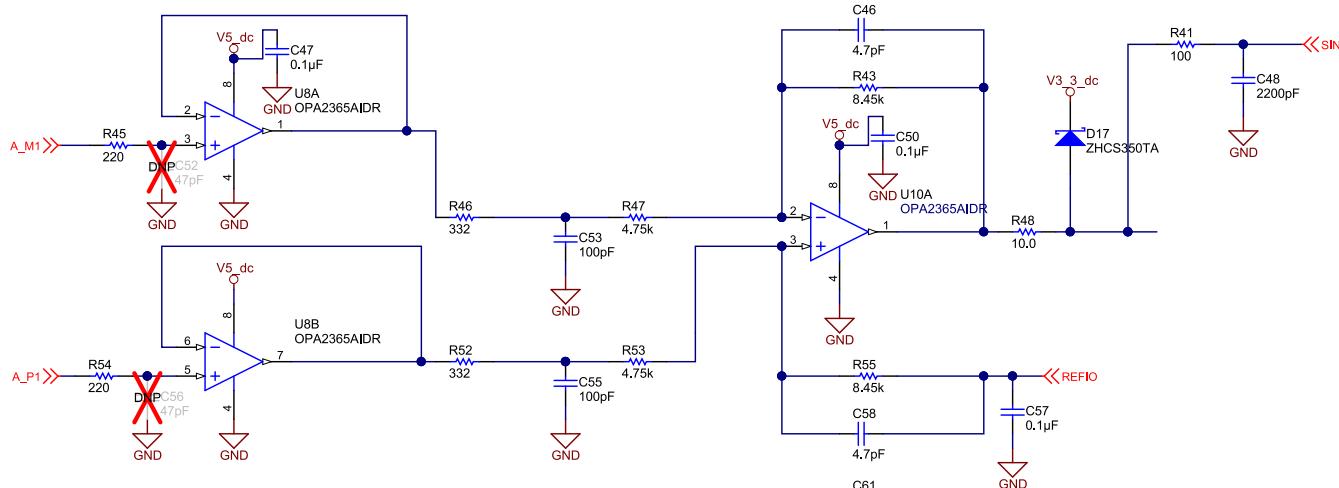

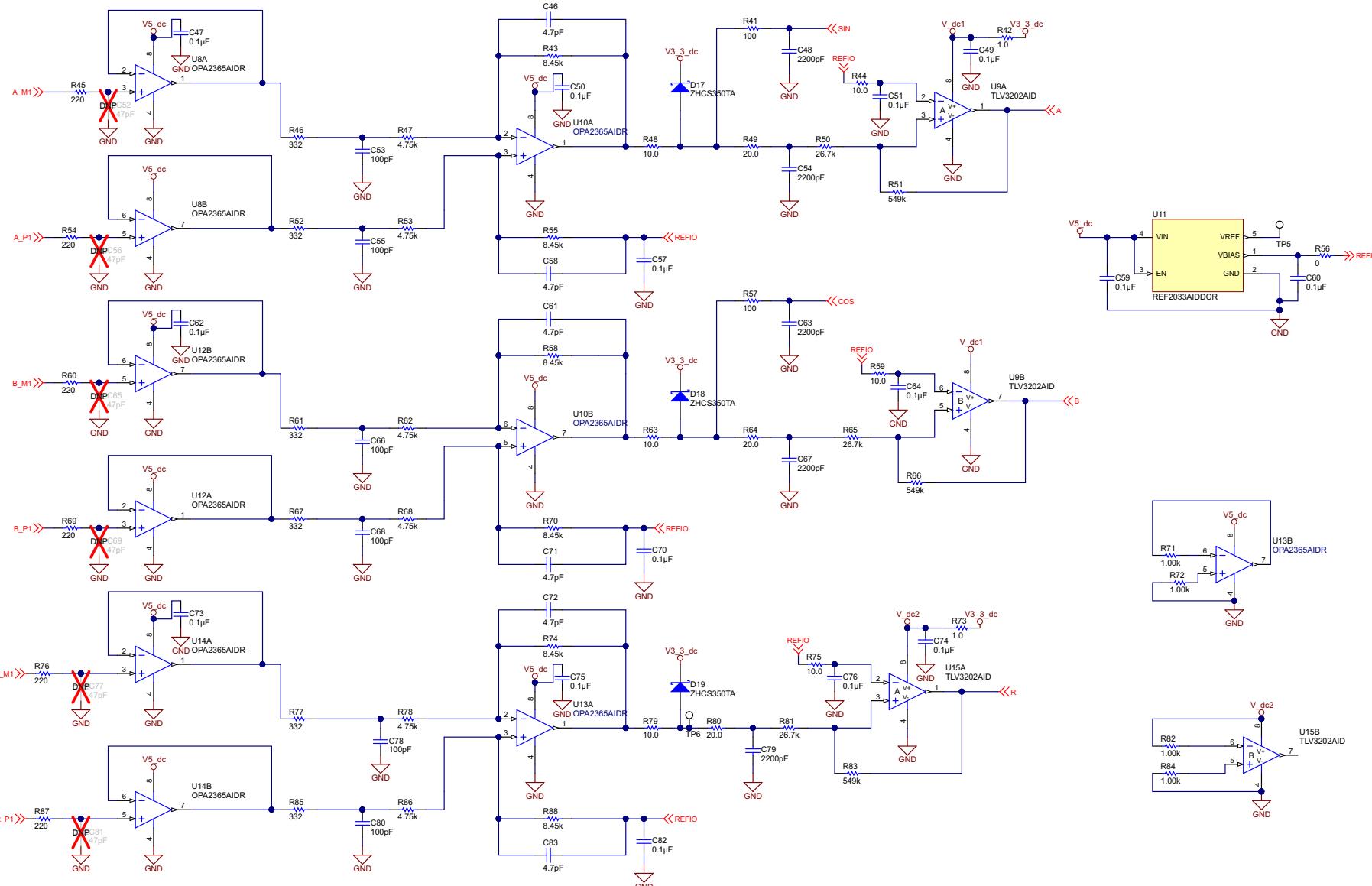

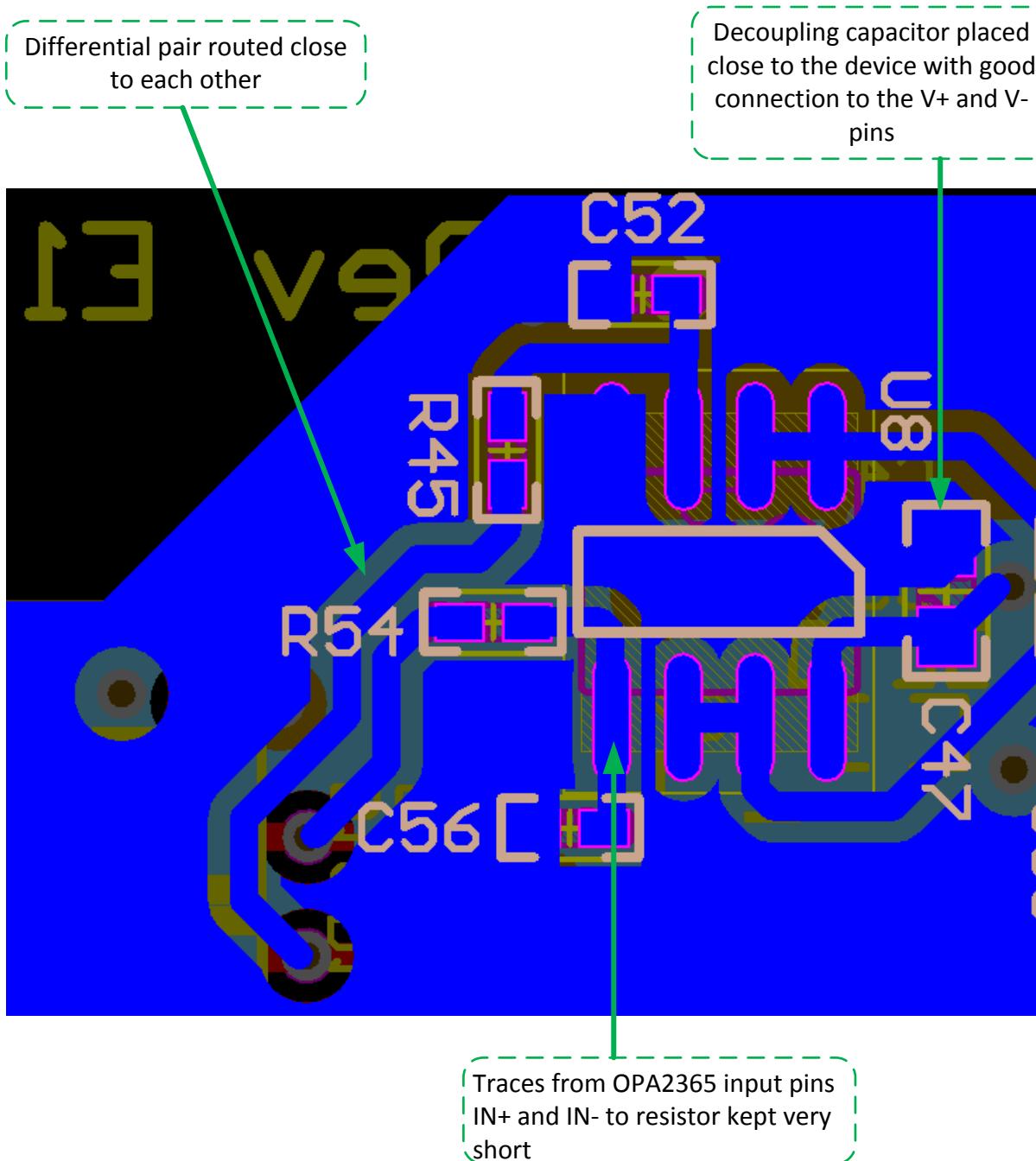

#### 4.1.2 ADC 内蔵マイコン向けシングルエンド出力のアナログ信号路

並列アナログ信号路は、高分解能パス、特に差動アンプに影響を与えないようにする必要があります。このため、差動信号 A+、A-、B+、B- は、入力終端と保護の後にタップ オフされ、オフセット、特にオフセットのドリフトが非常に小さいユニティゲイン アンプでバッファされます。以下のアンプは、差動信号をシングルエンド信号に変換する必要があります。最小帯域幅は 500kHz 以上である必要があります。500kHz

を超える出力信号を持つインクリメンタル エンコーダをサポートするため、理想的にはこれより大きい必要があります。コンパレータへのパスの位相遅延は、最小限のアナログ信号位相シフトを確保するための高分解能パスとほぼ同じにする必要があります。

電源電圧は 5V の单一電源である必要があります。

高分解能チャネルを一致させるには、両方のオペアンプのオフセットのドリフトの合計が 12 ビット以上の等価精度とする必要があります。理想的には、高分解能チャネルのアナログ性能と一致する必要があります。入力バッファおよび差動からシングルエンドへの変換については、以下の要因により、OPA2365 を選択しています。

- 5V レールを活用するための 2.2V から 5.5V への動作

- レールツー レール I/O

- 非常に小さいオフセットおよびオフセットのドリフト: 200 $\mu$ V (最大値) と 1 $\mu$ V/K (代表値)

- 低い電圧および電流ノイズ: 4.5nV/SQRT (Hz) および 0.004pA/SQRT (Hz)

- 優れた THD+N: 0.0004%

- 大きい同相信号除去 (CMRR): 100dB (最小値)

- スルーレート: 25V/ $\mu$ s

- 高速セトリング: 外部 ADC 駆動用、300ns で 0.01% まで

もう 1 つのオプションは OPA2322 です。これは低コストの代替品であり、2mV のオフセット電圧で、AC および DC 性能がわずかに低下しています。

アナログ出力電圧は、1.65V 同相モードを使用して 0 ~ 3.3V の範囲でスケーリングする必要があります。セクション 4.1.1 の最大 1.8V<sub>PP</sub> 入力電圧と同じ条件を適用し、3.3V の FSR に対して 10% のマージンを適用すると、ゲインは 1.66 となります。

チャネル A のアナログ信号チェーンを 図 4-6 に示します。チャネル B は同一です。

外部 ADC を駆動するため、アンチエイリアシングおよびデカップリング RC ネットワーク (R41/C48) が追加されています。このフィルタは、C2000 Piccolo マイコン ファミリに属する組込み 12 ビット デュアル S/H A/ADC で使用するよう最適化されています。他の ADC の場合は、それに応じてフィルタを調整する必要があります。

1.65V バイアス電圧は、100nF のコンデンサ (C57) でデカップリングされています。さらに、LP RC フィルタを追加した結果、HF ノイズ成分をより多く低減できるようになりました。特に、スイッチャの TPS54040A の出力を想定しています。

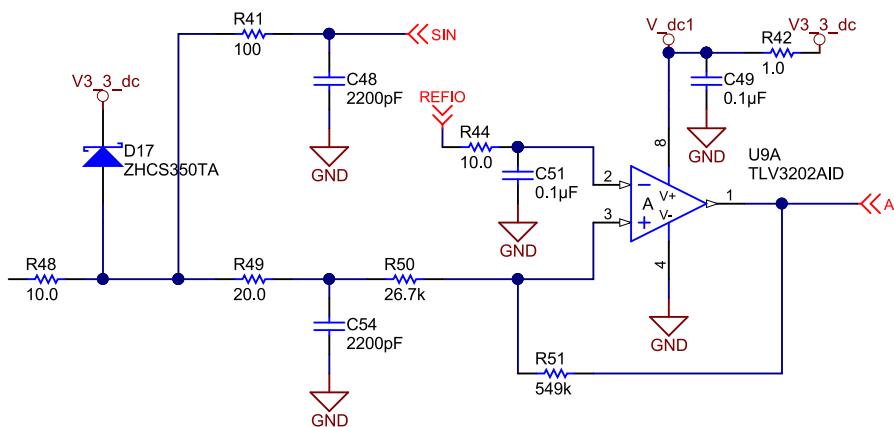

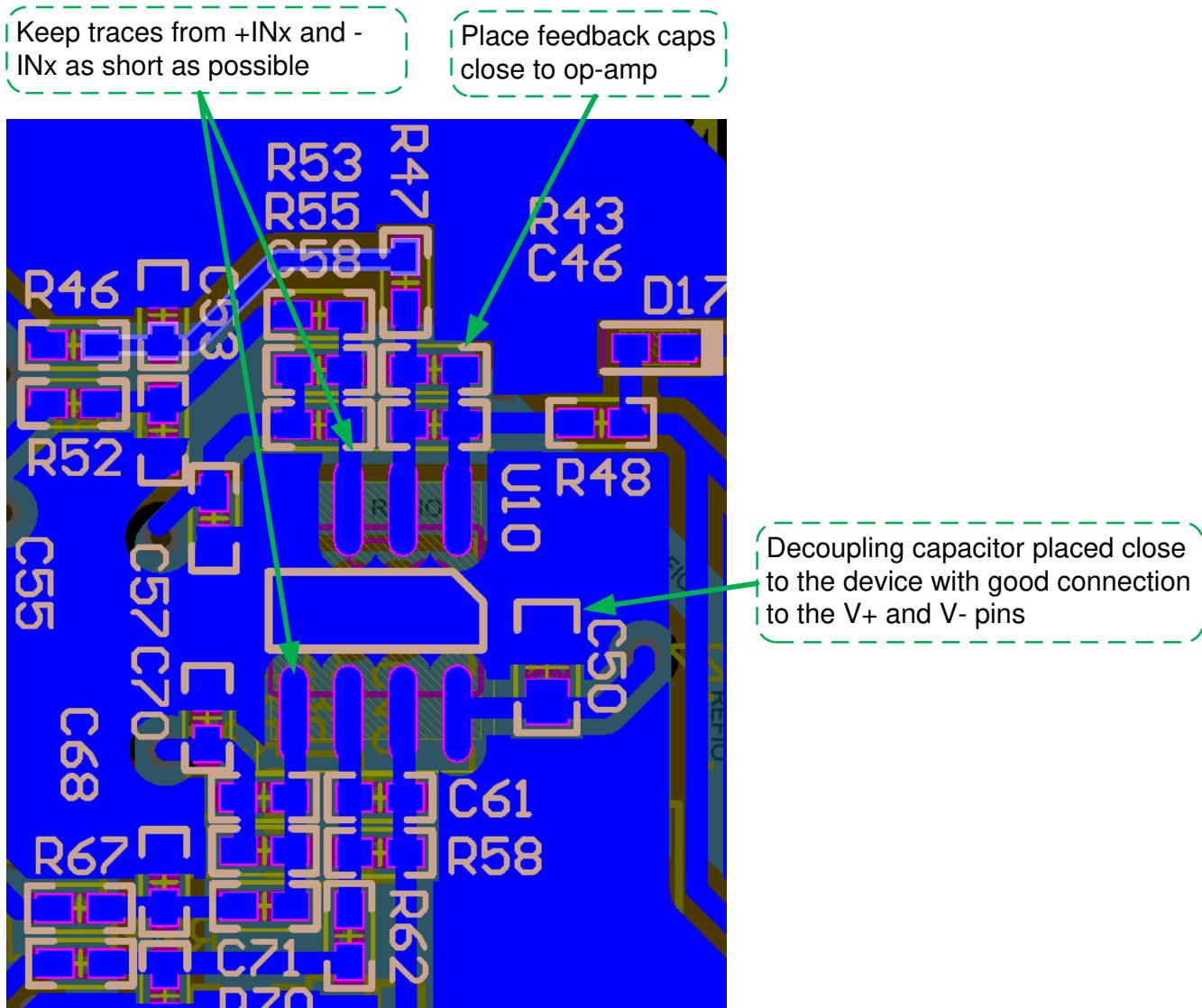

#### 4.1.3 デジタル信号 A, B, R 向けのコンパレータ サブシステム

コンパレータは、アナログ信号 A および B のゼロ交差とマーカー R でのゼロ インデックス パルスを検出し、対応するデジタル 3.3V TTL 互換信号  $A_{TTL}$ ,  $B_{TTL}$ ,  $R_{TTL}$  (しばしば ABZ と呼ばれます) を生成するために必要です。セクション 1.4 で概要を示しているように、低伝搬遅延のコンパレータによってシステムにマージンが追加されています。

選択されたコンパレータは、TLV3201 (シングル) および TLV3202 (デュアル)、40ns、マイクロパワー、プッシュプル出力コンパレータであり、以下の主な特性があります。

- 低伝搬遅延: 40ns (標準値)

- 入力オフセット電圧が 1mV (標準値) と低いため、スイッチング スレッショルドの最小ドリフトを保証

- 3.3V I/O ホスト プロセッサの入力を駆動するためのプッシュプル出力

- 産業用温度範囲

250ns の伝搬遅延を実現した TLC372 デュアルコンパレータは、システム全体の伝搬遅延と最大周波数に応じて、より低コストのオプションとなります。TLV320x ファミリの利点は、他の部品でより多くの遅延を追加でき、同時に 500kHz で要求される最大遅延 500ns を維持できることです。たとえば、ヒステリシスが大きいと伝搬遅延時間が長くなり、同時にノイズ耐性も向上します。

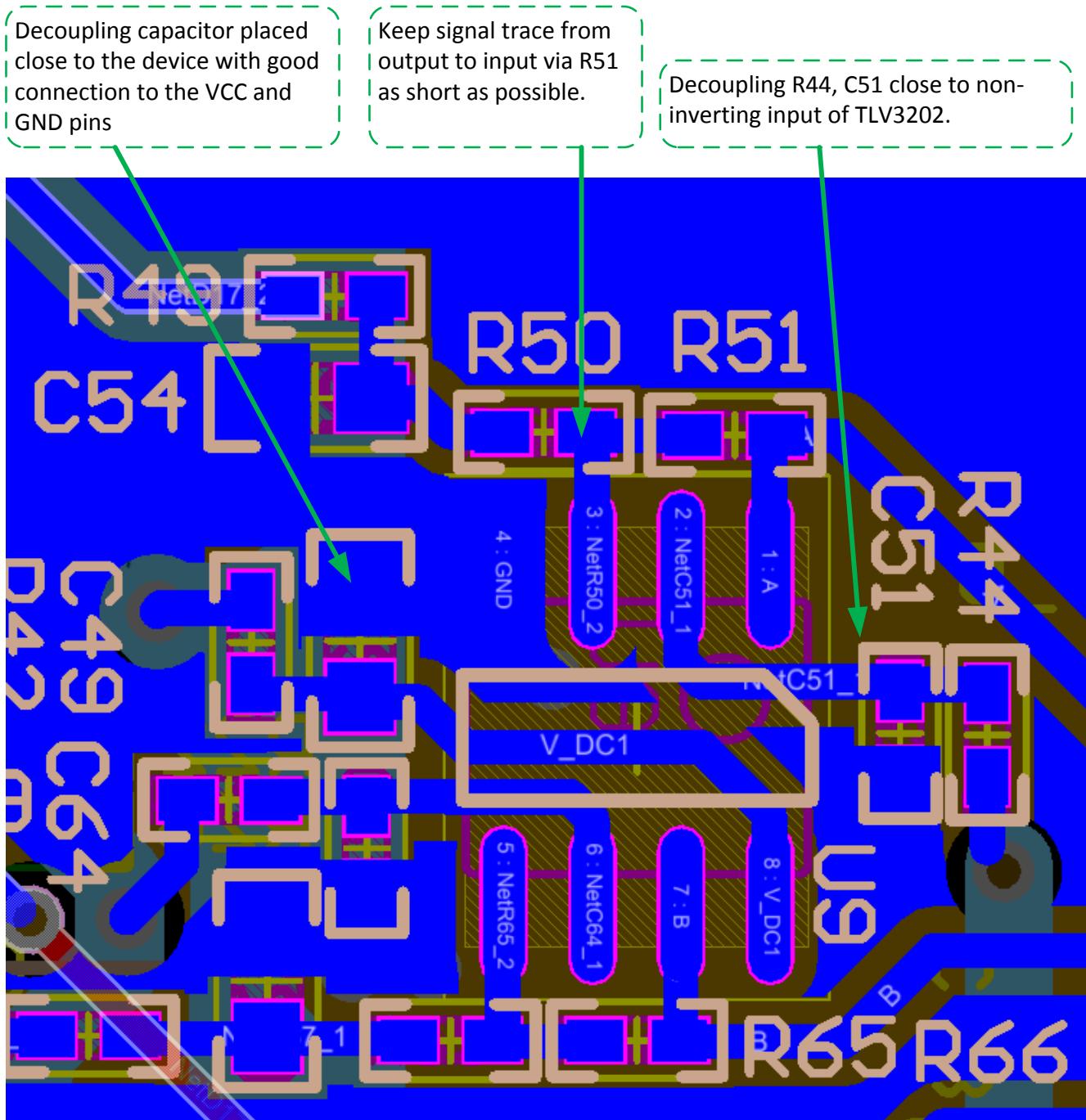

##### 4.1.3.1 ヒステリシス付きの非反転コンパレータ

すべてのコンパレータへの入力信号は、シングルエンドから差動アンプの出力から派生されます。前述のように、出力信号は 3.3V にクランプされ、アナログ シングルエンド信号 A および B とのクロストークを避けるために RC 回路 (信号 A の図 19 の R49, C54 など) でデカップリングされています。

高分解能バスとこのバスとの間で位相が一致し、コンパレータへの入力の RC デカップリング回路が THS4531A 出力の RC フィルタ ( $2 \times 10\Omega$  と  $2.2nF$ ) と一致します。

TLV370x は、アナログ サイン信号とコサイン信号 A および B のゼロ交差とインデックス パルス R を検出するため、非反転コンパレータとして構成されています。図 4-7 に、信号 A に関して対応する回路図を示します。

スイッチング スレッショルドはリファレンス電圧  $V_{REF} = 1.65V$  (REF2033) によって設定されます。この値は、差動からシングルエンドへのアンプのシングルエンド アナログ信号のバイアスにも使用されます。各コンパレータでは、基準入力を REF2033 から取得し、 $10\Omega$  直列抵抗 1 個と  $100nF$  コンデンサ 1 個でデカップリングします。

ノイズ耐性を高めるため、ヒステリシスが追加されます。非反転コンパレータのヒステリシス ( $V_{TH+} - V_{TH-}$ ) は、式 7 に従って計算できます。

$$V_{Hysteresis} = (V_{Out\_High} - V_{Out\_Low}) \times \frac{R_G}{R_F} \quad (7)$$

$V_{Out\_High}$  High レベル、 $V_{Out\_Low}$  Low レベルコンパレータの出力電圧、 $R_F$  は帰還抵抗、 $R_G$  は非反転コンパレータ入力への入力抵抗です。

この設計の構成では、図 4-7 に示すように、ヒステリシスは式 8 につき約 160mV に設定されています。R49 と R48 の大きさは R50 よりも小さいため、これらは無視できます。

$$V_{Hysteresis} = 3.3 V \times \frac{R_{50}}{R_{51}} \sim 160 mV \quad (8)$$

上限と下限のスイッチング スレッショルド  $V_{TH+}$  と  $V_{TH-}$  は、リファレンス電圧  $V_{REF} = 1.65V$  の 式 9 および 式 10 に従って定義されます。

$$V_{TH+} = 1.65 \text{ V} \times \left(1 + \frac{R_{50}}{R_{51}}\right) = 1.73 \text{ V} \quad (9)$$

$$V_{TH-} = (3.3 \text{ V} - 1.65 \text{ V}) \times \left(1 - \frac{R50}{R51}\right) = 1.57 \text{ V} \quad (10)$$

## 注意

下限スレッショルドは、電源電圧の関数です。ただし、この設計の電源電圧許容誤差は、ほとんどの設計での代表値として 5% です。3.3V 電源電圧に対して  $\pm 5\%$  の許容誤差は、下限スレッショルドにわずか  $\pm 16\text{mV}$  だけ影響を与える可能性がありますが、 $V_{TH-}$  の範囲は約 1.56 ~ 1.59V になるため、許容範囲内です。

図 4-7. ヒステリシス付き信号 A コンパレータ

各コンパレータの 3.3V 電源は、 $1\Omega$  の直列抵抗と  $100\text{nF}$  のコンデンサでデカップリングされるため、3.3V レールから他のコンパレータへのクロストークを最小限に抑えます。R49 と C54 で構成される RC ローパスは、外部 ADC に接続されるアナログ信号  $A/\sin$  からコンパレータ スイッチング ノードをデカップリングするために追加されます。

ヒステリシスによりクリーンなデジタル信号が可能になるため、ゼロ交差ポイント付近でのノイズによる高速スイッチングを回避できます。ただし、ヒステリシスには追加の伝搬遅延が発生し、これはコンパレータ入力におけるアナログ信号振幅  $V_{IN\_PEAK-PEAK}$  に依存します。

$$f_{\text{Hysteresis}} \sim \sin^{-1} \left( \pm \frac{160 \text{ mV}}{V_{\text{IN\_PEAK-PEAK}}} \right) \quad (11)$$

最小入力電圧が  $0.3V_{PP}$  と仮定すると、次のように動作します：差動からシングルエンドへのアンプ（ゲイン = 1.66）の出力は、 $0.5V_{PP}$  ( $0 \sim 100\text{kHz}$ ) の振幅を持ち、ローパス フィルタ減衰により  $500\text{kHz}$  で約  $0.32V_{PP}$  になります。デジタル信号 A、B、R のヒステリシスに対応する位相遅延は、コンパレータに  $0.32V_{PP}$  を入力すると約 30 度になります。その結果、 $500\text{kHz}$  の場合、コンパレータの総伝搬遅延は約  $170\text{ns} + 40\text{ns} = 210\text{ns}$  になります。

TLV3201 の伝搬遅延がわずか 40ns と小さいため、コンパレータ ブロック全体の遅延は 500kHz まで 45 度未満に維持されます。

信号 B と R のコンパレータの設定は同じです。また、索引マーカー R のバッファリングおよびゲイン段は、信号 A および B と同じです。これは、索引マーカー R の位相が 500kHz の信号周波数までの信号 A および B と正確に同期するためです。これにより、ゼロインデックスマーカー R が指定されたとおりに、信号 A と B の立ち上がりエッジの少し前に発生。

することが保証されます。ゼロ インデックス マーカー R は絶対ゼロ位置を定義します。したがって、位置オフセットを回避するためには、信号 A と信号 B との正確な関係が必要です。

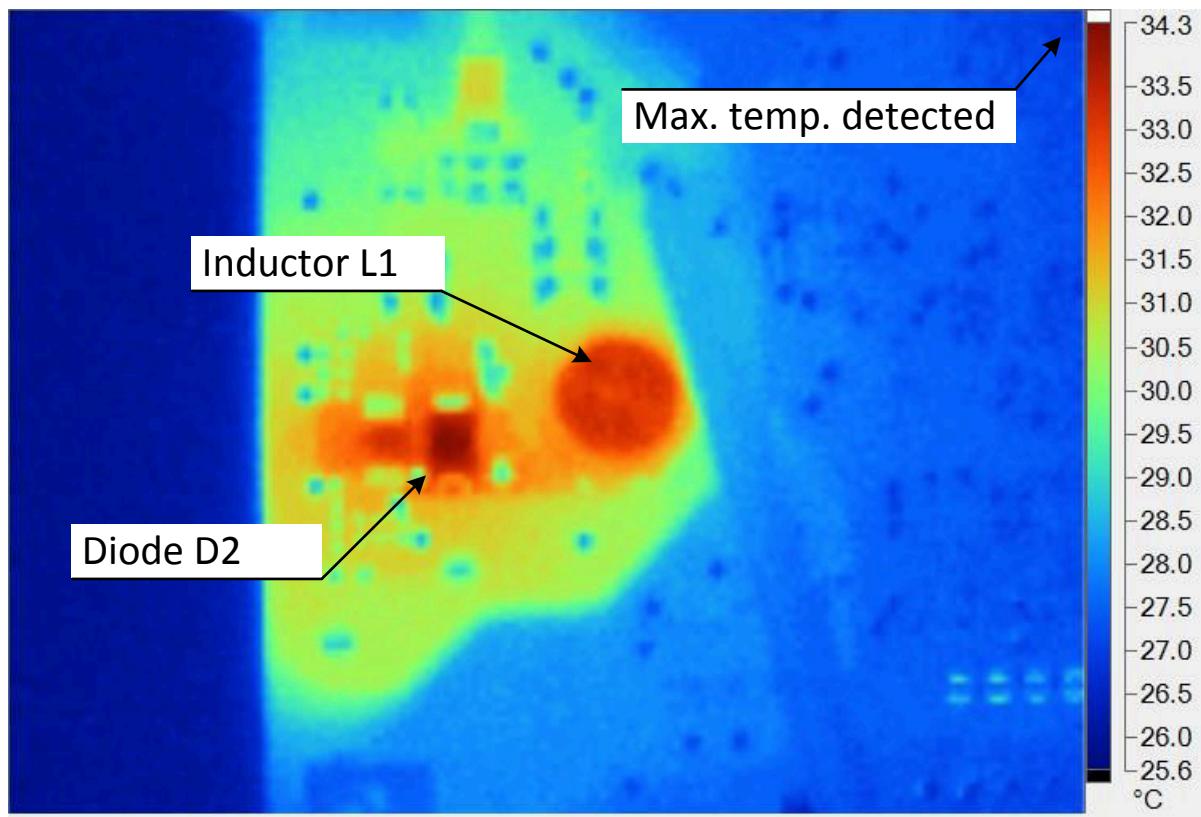

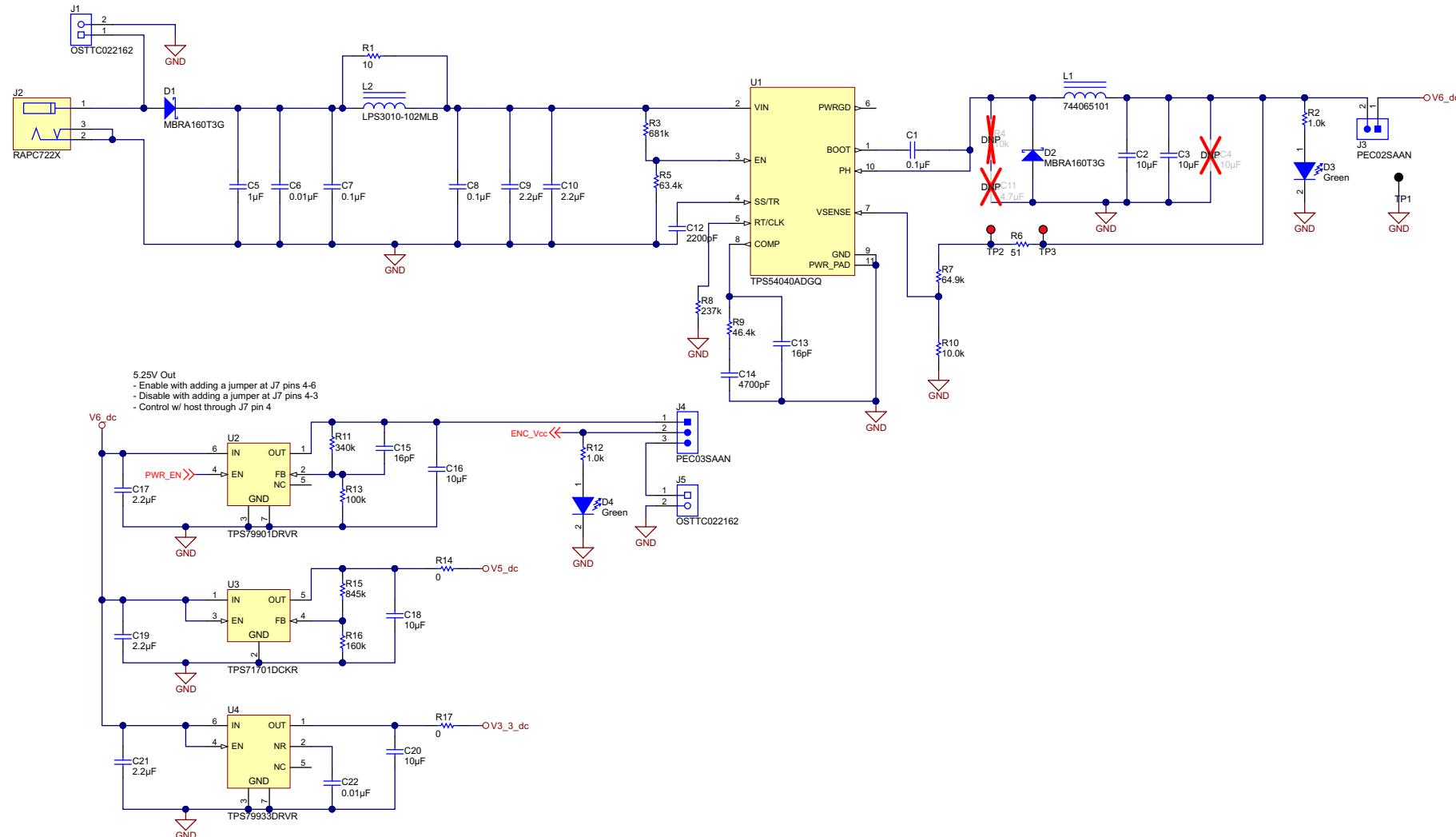

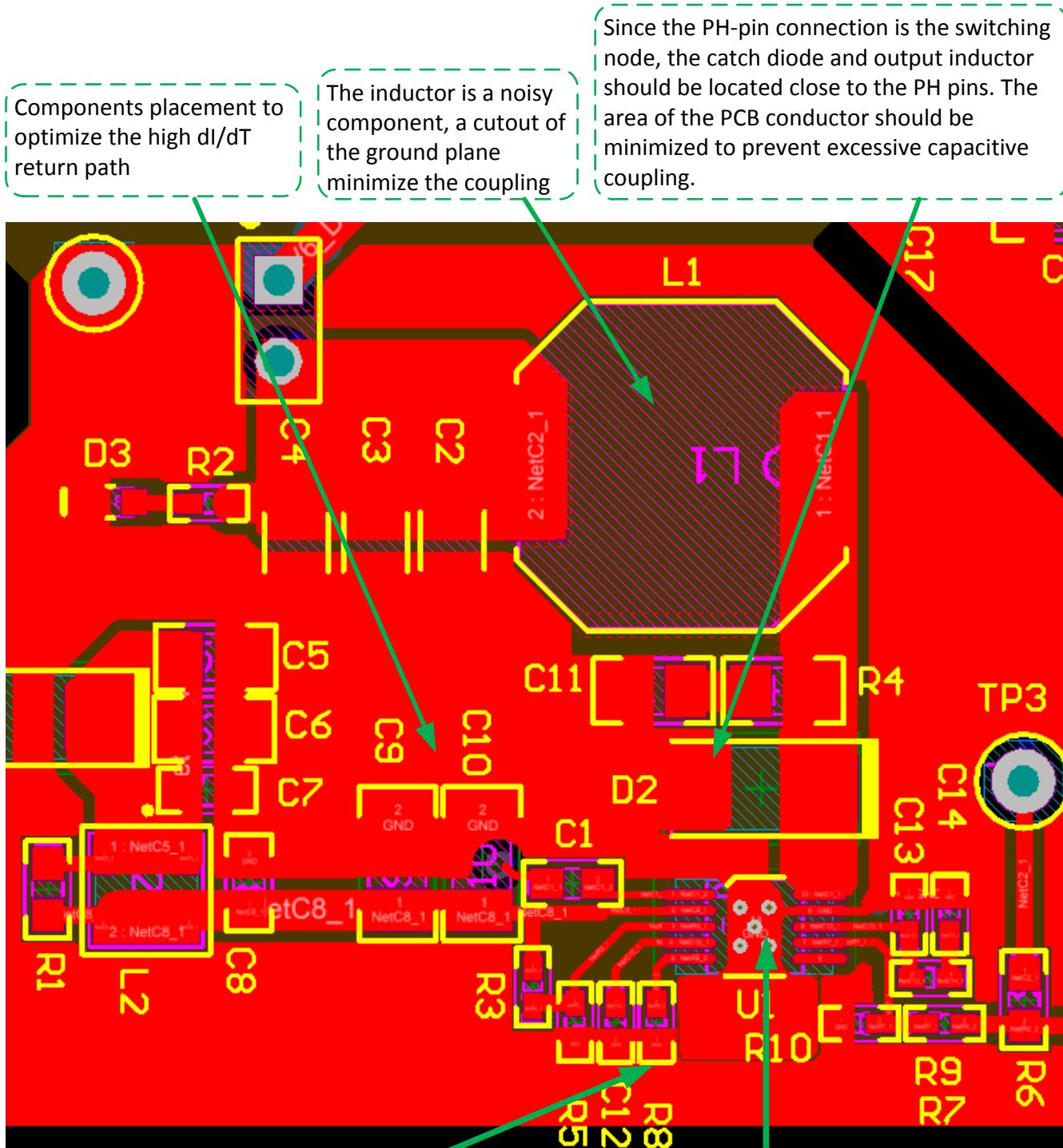

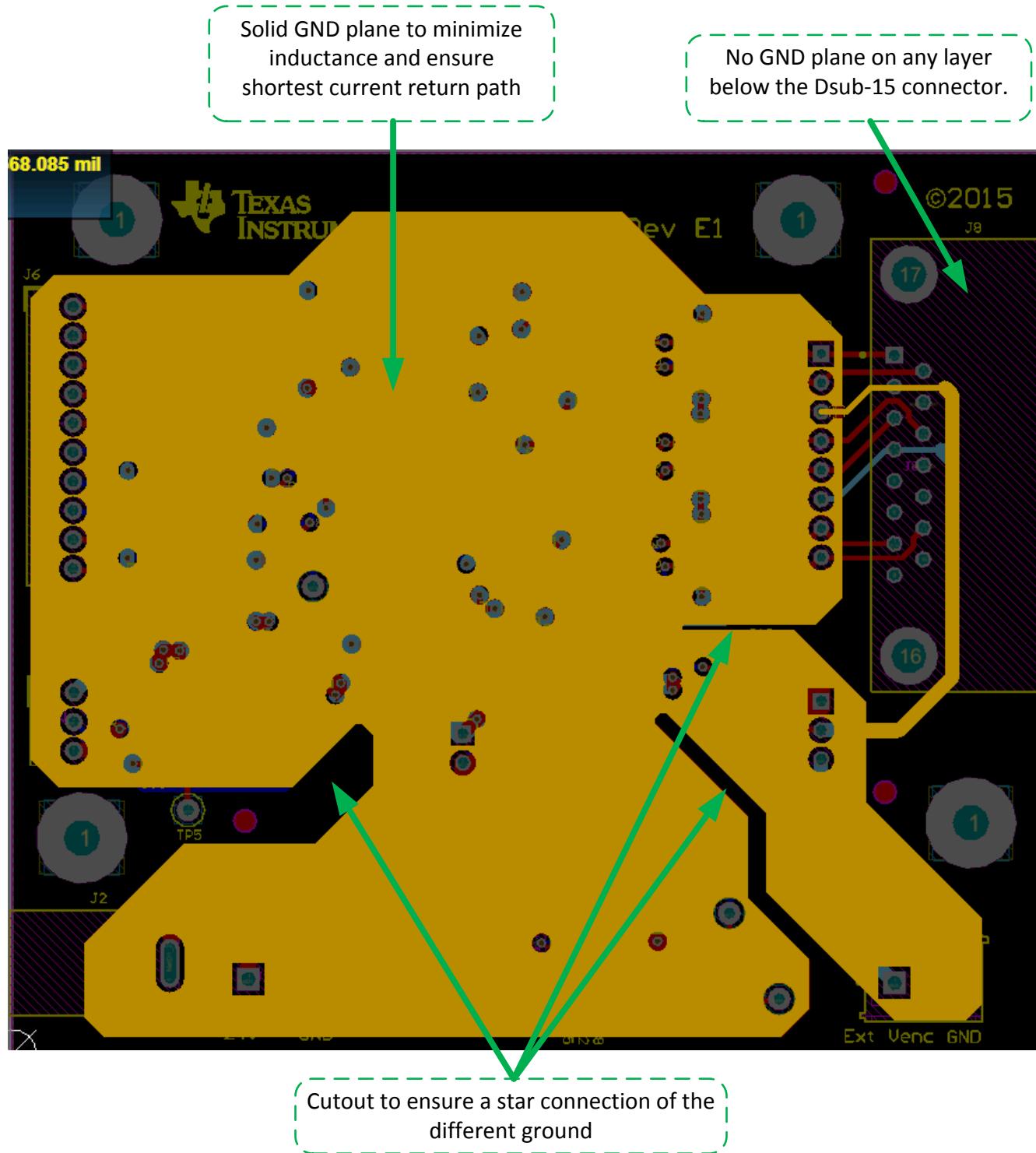

## 4.2 パワー マネージメント

パワーマネージメントは、24V 入力電圧から 6V 中間レールを生成する DC/DC 降圧回路で構成されています。図 4-8 に示すように、エンコーダの電源電圧と 5V および 3.3V レールは中間電圧から派生します。

図 4-8. パワー マネージメント ソリューション

システムやソリューションには高性能が必要であるため、ほとんどの電源レールは低ノイズ LDO から供給されています。その欠点は、効率が制限され、低出力電流能力があることです。電力損失が大きくなるため、最大出力電流は放熱性能によって制限されます。

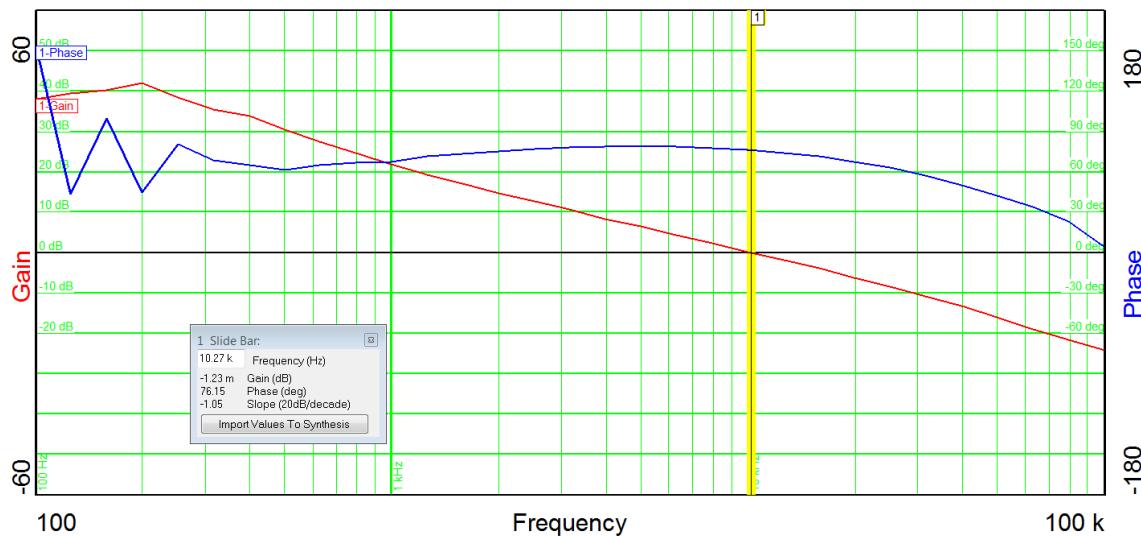

LDO の両端間の電圧降下を低減するために、高効率の DC/DC スイッチングコンバータを使用して 24V 入力から 6V 中間レールを生成する方法を用意しています。適切なレイアウトと部品の選択により、スイッチャソリューションが引き起こすノイズを最小限に抑えるよう注意が必要です。

### 4.2.1 24V 入力から 6V 中間レール

1 個のスイッチング DC/DC コンバータを実装して、3 個の LDO に電力を供給する 6V の中間電圧レールを実現しています。これは基本的に必須の選択肢です。VIN/VOUT 比が高いことから、どの LDO も電力変換には適していないからです。実際、あらゆる LDO の効率は単純に VOUT/VIN として計算できます。ワーストケース (最大 VIN) では、 $5.25V/36V \approx 14\%$  になります。消費電力の残りの 86% は、LDO パッケージによって消費されます。実際に最大電流が 200mA の場合、 $36V \times 200mA \times 86\% = 6.2W$  の電力が LDO パッケージで消費されることになり、妥当なパッケージであれば簡単に、そしてすぐに破損してしまうでしょう。

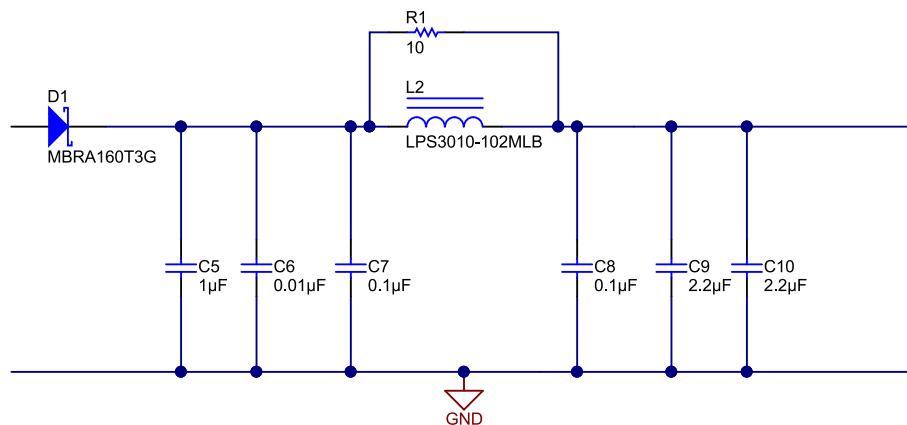

入力フィルタをはじめとして、スイッチング回路の通常の動作によって伝導 EMI が発生することが広く知られています。パワー スイッチのオン / オフが非常に高速に切り替わることによって、大きな非連続性電流が発生します。降圧トポロジでは、コンバータの入力に大きな非連続性電流 ( $di/dt$  が大きい) が存在します。図 4-9 に、入力フィルタに対して選択した値を示します。

入力 EMI フィルタの設計方法の詳細については、アプリケーション レポート『AN-2162 DC/DC コンバータから伝導される EMI に対する簡単な対処方法』(SNVA489) をご覧ください。

図 4-9. 逆極性保護を含む入力フィルタ

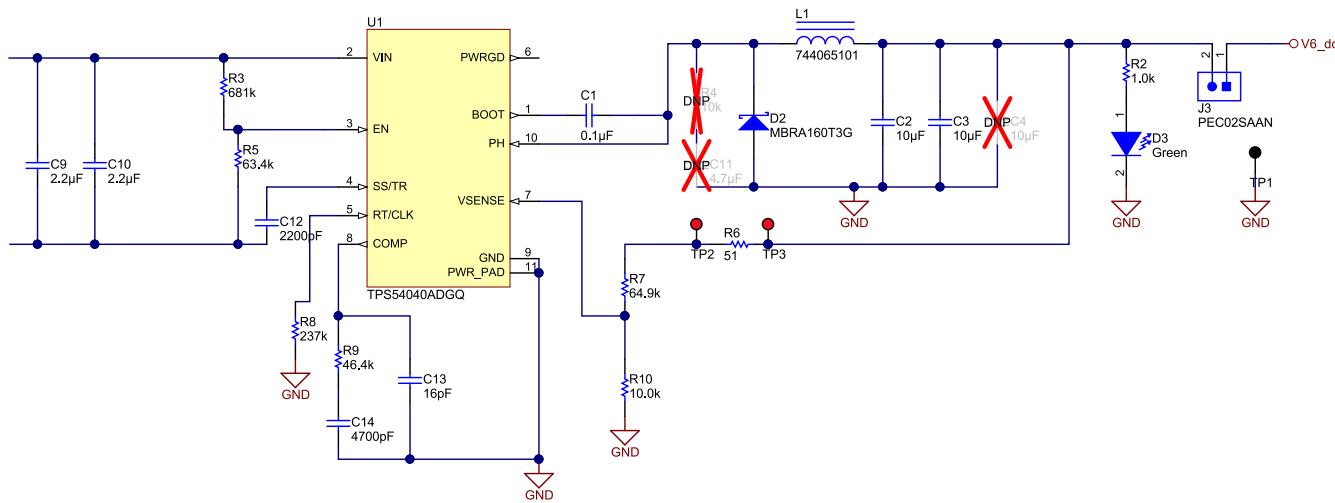

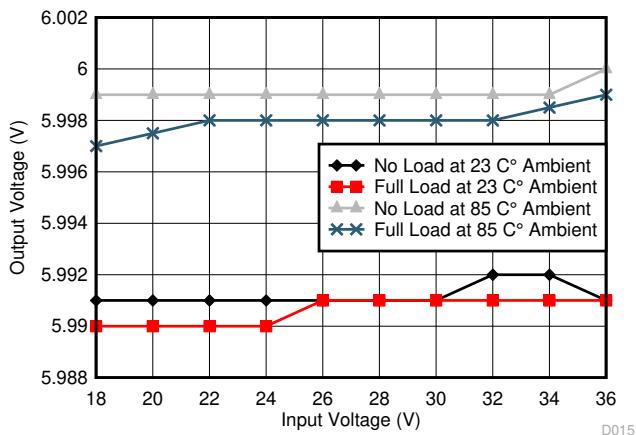

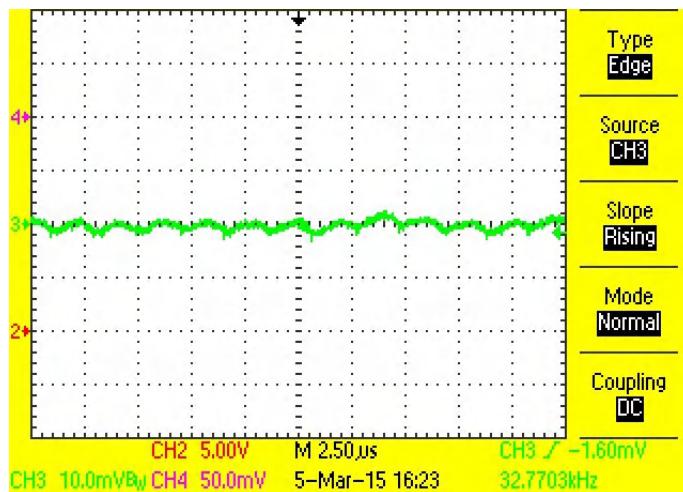

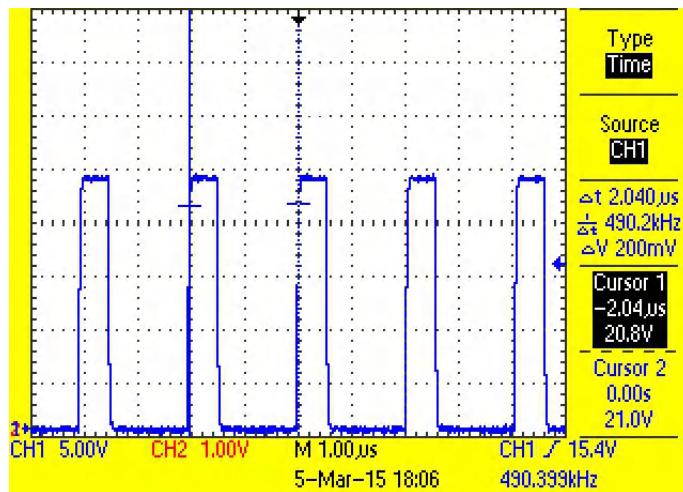

DC/DC 降圧コンバータは、以下の仕様を満たすよう設計されています。

- 入力電圧:  $V_{IN} = 17V \sim 36V$ 、公称 24V

- 出力電圧: 6V (500mA 時)

- スイッチング周波数: 公称 500kHz

- 出力電圧リップル: 25mV<sub>PP</sub> (最大値)

- 効率: 全負荷時で 80% 超

- 非絶縁型トポロジ

TPS54040A は以下の目的のために選択されています: これは、内蔵 FET、3.5 ~ 42V 入力電圧、500mA の出力電流で 0.8 ~ 39V の出力電圧を備えた降圧コンバータです。その周波数は 100kHz ~ 2.5MHz の範囲で変更でき、外部クロックと同期させることもできます。また、有効または無効にすることもできます。これらの特長から TPS54040A は、上記の要件 / 仕様に非常に適合しています。

TPS54040A は TPS5401 とピン互換性があります。TPS54040A からさらに低コストなバージョンで、同様の性能を発揮しますが、出力電圧と有効なスレッショルドの精度が低くなります。

また、TPS54040A は TPS54140A、TPS54240、TPS54340、TPS54540 とピン互換性があることにも注意してください。その結果、部品の選択肢が拡大し、(将来のシステム アップグレードに備えて) コストと電力レベルを変調する機能も実現できます。

図 4-10. TPS54040A を使用した 24V から 6V への DC/DC 降圧コンバータの回路図

設計プロセスの詳細については、TPS54040A データシートまたは TI Design TIDA-00180 を参照してください。

代表的なアプリケーションでは、単純な抵抗デバイダ回路により出力電圧が設定されます。出力電圧、リファレンス電圧 (TPS54040A では 0.8V)、および下側抵抗 (R10 は通常 10kΩ に固定) に応じた上側抵抗の値を [式 12](#) に示します。

$$R7 = R10 \times \frac{V_{OUT} - 0.8 \text{ V}}{0.8 \text{ V}} \quad (12)$$

$V_{OUT} = 6\text{V}$ 、 $R10 = 10\text{k}\Omega$  の場合、 $R7$  により  $65\text{k}\Omega$  が得られます。

6V 出力電圧の許容誤差は  $6\text{V} \pm 4\%$  になります。これは、公差 1% の帰還抵抗、TPS54040A の内部バンドギヤップ公差  $\pm 2\%$  を想定しています。

スイッチング周波数は、 $R8 = 237\text{k}\Omega \sim 500\text{kHz}$  に設定されています。

TPS54040A の回路図では、一部の部品には未実装 (DNP) とマークされています。これは、R4 と C11 によって形成されたスナバ回路の場合です。TPS54040A 設計では、スナバ回路は不要です。スナバ回路は、必要に応じてスイッチノードのリンギングと MOSFET のオーバーシュートを低減するソリューションです。他のオプションの詳細については、スナバ回路の使用方法と計算方法についてのアプリケーションノート『[NexFETTM 高性能 MOSFET のリンギング低減技法](#) (SLPA010) を参照してください。

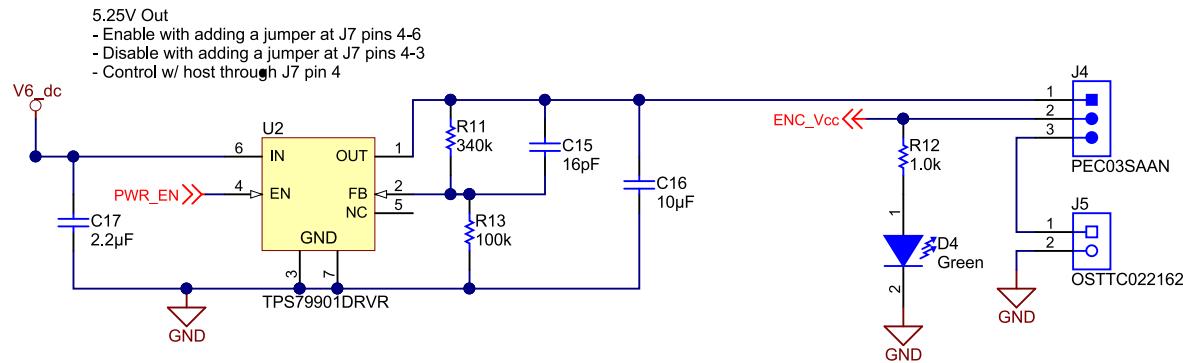

#### 4.2.2 エンコーダ電源

標準的な 5V ( $\pm 5\%$ ) エンコーダ電源仕様を満たし、エンコーダの接続に使用する長いケーブルによる電圧降下を補償する 0.25V のマージンを追加するために、エンコーダ用の 5.25V 電源を選択しました。

5.25V をエンコーダに供給する LDO では、イネーブルピンも提供する必要があります。このようにして、必要に応じて、ホストプロセッサからエンコーダ電源をオフにしたり、エンコーダが接続されていない場合にエンコーダコネクタの電圧をオフにしたりすることができます。

LDO は、安定性を目的とした出力コンデンサと ESR の許容範囲を除き、特別な記述は必要ありません。一方、主な設計には SMPS が関係しますが、これはすべての主な性能 (ノイズ、EMI、効率、コスト、基板面積) に影響するからです。

TPS79901 は、公称 5V (5.25V) よりも少し高い電圧を供給するように設計されており、LDO の高精度の一部を使用して、その熱ストレスを低減します。短時間では、 $5.25\text{V} \pm 2\%$  は、エンコーダの許容電源電圧範囲内です ( $5\text{V} \pm 5\%$ )。このようにして、消費する電力は以下のようになります。

$$P_{LDO,MAX} = (V_{LDO,IN} - V_{LDO,OUT}) \times i_{LDO,MAX} = (6 \text{ V} - 5.25 \text{ V}) \times 250 \text{ mA} = 187 \text{ mW} \quad (13)$$

5V エンコーダの電圧を使用すると、最大消費電力は 250mW に増加します。

実際、 $R_{thja} \approx 180^\circ\text{C/W}$  の場合、最大負荷電流 250mA で動作しても、TPS79901 の接合部温度は周囲温度に対して  $34^\circ\text{C}$  未満しか上昇しないことになります。たとえば、周囲温度  $85^\circ\text{C}$  の場合、接合部は  $120^\circ\text{C}$  になります。

TPS79901 LDO の出力電圧は、[式 13](#) に従って、1% 帰還抵抗 R11 および R13 で設定されます。ここで、1.193V は、TPS79901 のリファレンス電圧の公称値です。

$$V_{ENC\_VCC} = 1.193 \text{ V} \times \left(1 + \frac{R11}{R13}\right) = 1.193 \times \left(1 + \frac{340\text{k}}{100\text{k}}\right) = 5.25 \text{ V} \quad (14)$$

図 4-11. エンコーダ電源用 5.25V LDO の回路図

ジャンパーで、5.25V の LDO 出力と、必要に応じてオプションの外部電源のどちらかを選択します。信号 PWR\_EN はデフォルトでプルアップされていますが、ホストマイコンから Low にアサートすることで、エンコーダの電源電圧を無効化するか、電源をパワー サイクルすることができます (セクション 4.3 を参照)。

#### 4.2.3 シグナル チェーン用電源 5V および 3.3V

セクション 4.1 で説明したように、アナログ シグナル チェーンで要求される電流は低いため、また非常に低いノイズで高性能を実現するには、LDO が再び必須の選択となります。実際、TI の LDO は PSRR が高いため、スイッチャで生成される AC ノイズがブロックされ、ADC や入力バッファやアンプなどノイズに敏感なアナログ部品には影響を与えません。

5V レールは、アナログ バッファ、アンプ、および ADS8354 ADC のアナログ電源電圧専用です。この 3.3V は ADS8354 とコンパレータのデジタル電源専用であり、I/O レベルシフタを必要とせずに、ホストプロセッサへの 3.3V インターフェイスを確保します。選択した部品の消費電力は低いため、3.3V および 5V レール用に LDO がそれぞれ選択され、公称出力電流は 100mA です。

3.3V レールには固定 3.3V LDO TPS79933 を使用し、TPS71701 を 5V レールに使用しました。図 4-12 に回路図を示します。式 15 に従って、5V の出力電圧は、TPS71701  $V_{REF} = 0.8V$  における帰還抵抗  $R15$  および  $R16$  によって設定されます。

$$V_{5V} = V_{REF} \times \left(1 + \frac{R15}{R16}\right) = 0.8V \times \left(1 + \frac{845k}{160k}\right) = 5.02V \quad (15)$$

図 4-12. シグナル チェーン用 5V および 3.3V PoL の回路図

## 4.3 ホストプロセッサインターフェイス

### 4.3.1 信号の説明

10 ピン ヘッダー インターフェイスをホスト プロセッサへの接続に使用できます。ヘッダーは、ADS8354 デュアル 16 ビット ADC と内蔵デュアル S/H ADC (利用可能な場合) を使用して、両方の信号路の高分解能補間角度を計算するために必要な信号を提供します。

このインターフェイスは 3.3V I/O システムに準拠しています。ソリッド GND 接続を行うには、奇数のピンをすべて GND に割り当てます。利用可能な信号を [表 4-1](#) に示します。

**表 4-1. ホスト MCU への TIDA-00176 インターフェイス コネクタ**

| 機能                                                | 信号        | I/O (3.3V)                           | 備考                                                                                                                                         |

|---------------------------------------------------|-----------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| ADS8354 と SPI (スレーブ) を使用した A、B の 16 ビット高分解能出力チャネル | SDI (I)   | デジタル入力                               | シリアル通信用データ入力。デュアル サンプリング モードの構成に使用                                                                                                         |

|                                                   | /CS (I)   | デジタル入力                               | チップ セレクト信号 (アクティブ Low)。/CS の立ち下がりエッジで、アナログ入力 (ホールド) がラッチされ、新しい変換が開始されます。Piccolo マイコンなど、ホスト プロセッサで QEP カウンタを同期的にラッチするには、/CS の立ち下がりエッジを使用します |

|                                                   | SCLK (I)  | デジタル入力、最大 24MHz                      | シリアル通信用クロック                                                                                                                                |

|                                                   | SDO_A (O) | デジタル出力                               | シリアル通信のデータ出力、チャネル A、チャネル B。各チャネル A とチャネル B の 16 ビット 2 の相補データ。入力から出力への信号ゲイン = 5。                                                            |

|                                                   | SDO_B (O) | デジタル出力                               | シリアル通信チャネル B のデータ出力                                                                                                                        |

| デジタル直交エンコード信号 A、B、および索引マーカー R                     | ATTL (O)  | デジタル出力                               | A、B、R のヒステリシス 160mV、構成可能                                                                                                                   |

|                                                   | BTTL (O)  | デジタル出力                               |                                                                                                                                            |

|                                                   | RTTL (O)  | デジタル出力                               |                                                                                                                                            |

| A および B のアナログ シングルエンド出力チャネル                       | A/sin (O) | アナログ出力:0 ~ 3.3V、1.65V バイアス (シングルエンド) | 公称出力範囲:<br>1V <sub>PP</sub> に対して 0.82V ~ 2.48V (1.65V ± 0.83V)、ゲイン = 1.66、バイアス電圧 = 1.65V                                                   |

|                                                   | B/cos (O) | アナログ出力:0 ~ 3.3V、1.65V バイアス (シングルエンド) | 公称出力範囲:<br>1V <sub>PP</sub> に対して 0.82V ~ 2.48V (1.65V ± 0.83V)、ゲイン = 1.66、バイアス電圧 = 1.65V                                                   |

コネクタ ピン構成の詳細については、[セクション 6](#) を参照してください。

#### 注意

ADS8354 16 ビット デュアル サンプリング ADC のアナログ入力サンプルを QEP 増分カウンタ モジュールと同期するには、ADS8354 への /CS 信号を使用して QEP カウンタもラッチします。Piccolo などのマイコンの場合、/CS を eQEP ストローブ入力ピン EPEPxS に接続する必要があります。ここで、x はモジュール番号です。Piccolo eQEPx モジュールは、EQEPxS ピンの立ち下がりエッジで QEP カウンタをラッチするように構成することができます。

#### 4.3.2 16 ビットのデュアル ADC ADS8354 とシリアル出力を使用した高分解能パス

このセクションでは、シリアル インターフェイスを介した ADS8354 の構成の概要を示します。これは、内部 ADS8354 リファレンスによるフルスケール入力電圧範囲のプログラミングとシリアル データ転送に分けられます。

##### 4.3.2.1 ADS8354 入力フルスケール レンジ出力データ形式

この設計で使用するために、ADS8354 は  $\pm 2 \times V_{REF}$  の入力電圧範囲になるように構成します。内部リファレンス電圧  $V_{REF}$  を 2.5V に設定して、 $\pm 5V$  FSR を生成する必要があります。

**表 4-2. TIDA-00176 の ADS8354 伝達特性**

| 入力電圧: AINP_x - AINM_x | モード                       | 入力電圧        | 出力コード (HEX) |

|-----------------------|---------------------------|-------------|-------------|

| < -5V                 | $\pm 2 \times V_{REF}$ 範囲 | NFSC        | 8000        |

| -5V + 1LSB            |                           | NFSR        | 8001        |

| -1 LSB                |                           | -1 LSB      | FFFF        |

| 0                     |                           | 0           | 0000        |

| > 5V - 1LSB           |                           | PFSR - 1LSB | 7FFF        |

各チャネル A および B の出力日付フォーマットは、16 ビット符号付き整数出力 (2 の補数) です。

##### 4.3.2.2 ADS8354 シリアル インターフェイス

ADS8354 は、シリアル クロック (SCLK) を使用して、デバイス内外のデータ転送を同期します。CS 信号は、1 つの変換フレームとシリアル転送フレームを定義します。フレームは、CS の立ち下がりエッジで開始し、CS の立ち上がりエッジで終了します。読み取りまたは書き込み動作を検証するには、フレームの開始と終了の間に、最小 N 個の SCLK の立ち下がりエッジが必要です。表 4-3 に示すように、N は変換結果の読み取りに使用されるインターフェイス モードに依存します。N 個の SCLK 立ち下がりエッジが供給されている場合、フレーム内の書き込み動作が検証され、次の CS 立ち上がりエッジで、内部のユーザー プログラマブル レジスタが更新されます。この CS の立ち上がりエッジでフレームも終了します。CS が High になってから N 個の SCLK の立ち下がりエッジを供給する場合、フレームの書き込み動作は有効ではありません。

**表 4-3. ADS8354 SCLK の立ち下がりエッジによる有効な書き込み動作**

| インターフェイス モード                | 書き込み動作を検証するために必要な最小 SCLK 立ち下がりエッジ数 N |

|-----------------------------|--------------------------------------|

| 32-CLK、デュアル SDO モード (デフォルト) | 32                                   |

| 32-CLK、シングル SDO モード         | 48                                   |

| 16-CLK、デュアル SDO モード         | 16                                   |

| 16-CLK、シングル SDO モード         | 32                                   |

F28069M Piccolo MCU のサンプル ファームウェアは、ADS8354 を 32-CLK のシングル SDO モードで初期化します。

シリアル インターフェイス モードと読み書き動作の詳細については、ADxx54 のデータシートを参照してください。

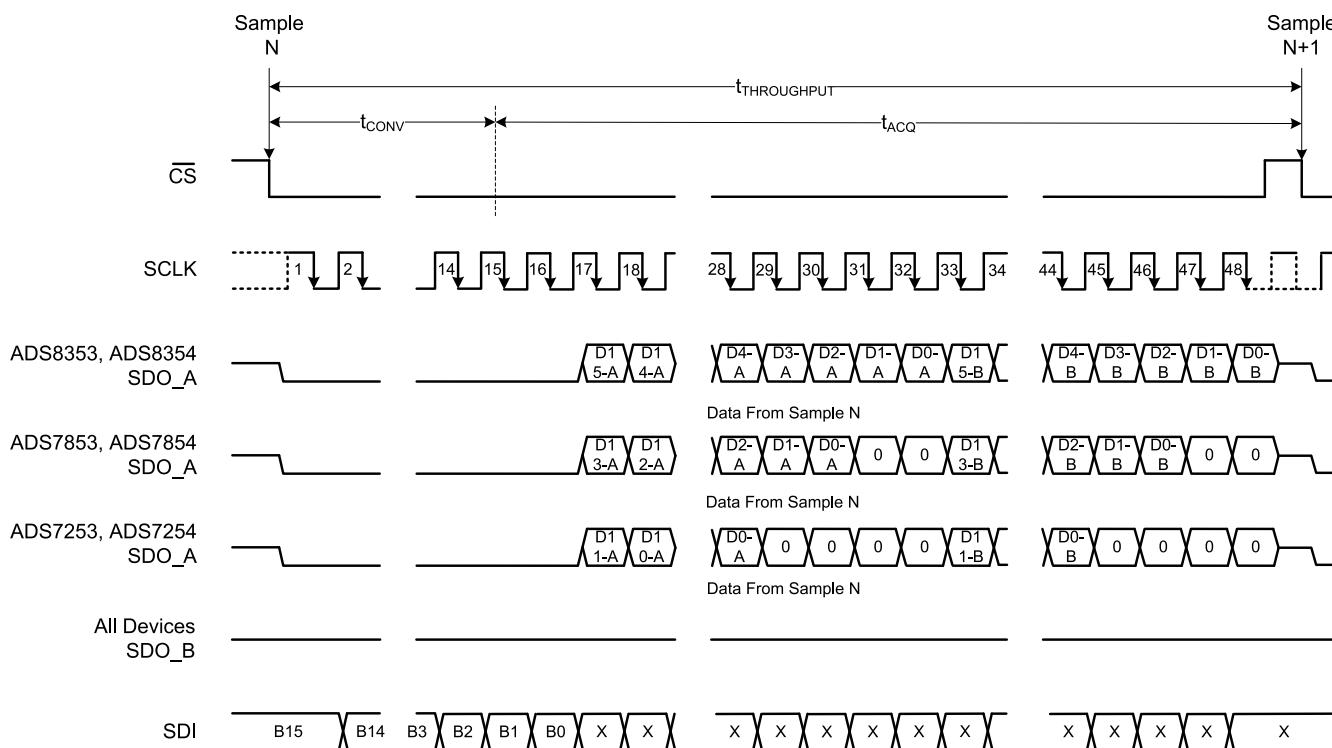

#### 4.3.2.3 ADS8354 変換データの読み取り

表 4-3 に概説しているように、このデバイスでは 4 種類のインターフェイス モードが用意されています。これらは、変換結果の読み取りにも適用できます。これらのモードにより、フレキシブルなハードウェア接続とファームウェア プログラミングが可能になります。32-CLK インターフェイス モードでは、デバイスは内部クロックを使用して、サンプリングされたアナログ信号を変換します。変換は SCLK の最初の 16 周期中に完了し、以後の SCLK の立ち下がりエッジで変換結果を読み取り可能です。ファミリのすべてのデバイス (ADS8354, ADS7854, ADS7254) が、32-CLK インターフェイス モードをサポートしています。32-CLK のインターフェイス モードに加えて、ADS7854 と ADS7254 は 16-CLK インターフェイス モードもサポートしています。16-CLK

インターフェイス モードを使用することで、同じスループットを、はるかに低い SCLK 速度で実現できます。

F28069M Piccolo MCU のサンプル フームウェアは、ADS8354 を 32-CLK のシングル SDO モードで初期化します。

32-CLK、シングル SDO モードでは、1 つの SDO ピン (SDO\_A) のみを使って、両方の ADC (ADC\_A および ADC\_B) から変換結果を読み取ることもできます。SDO\_B は 3-state にとどまり、未接続 (NC) ピンとして扱うことができます。このモードの詳細なタイミング図を、図 4-13 に示します。

図 4-13. 32-CLK、シングル SDO モードのタイミング図

CS の立ち下がりエッジによって、シリアル データバスが 3-state から復帰し、SDO\_A ピンに 0 を出力します。デバイスは、変換時間 ( $t_{CONV}$ ) 中にサンプリングされたアナログ入力を変換します。SDO\_A は、この期間中に 0 を読み取ります。変換プロセスが完了すると、サンプル / ホールド回路はサンプル モードに戻ります。デバイスは、16<sup>th</sup> SCLK の立ち下がりエッジで SDO\_A ピンに ADC\_A の MSB を出力します。以後の SCLK 立ち下がりエッジは、ADC\_A の変換結果をシフトアウトし、その後 SDO\_A ピンで ADC\_B の変換結果をシフトアウトするために使用されます。このモードでは、読み取りまたは書き込みフレームを有効にするために、少なくとも 48 個の SCLK 立ち下がりエッジを割り当てる必要があります。CS の立ち上がりエッジによってフレームは終了し、シリアル バスが 3-state になります。

詳細については、ADSxx54 のデータシートを参照してください。

#### 4.3.2.4 ADS8354 のレジスタ構成

前のセクションで述べたようにモードを選択するには、ADS8354 レジスタ REF DAC\_A、REF DAC\_B、および CFR を次のようにプログラムします。

REF DAC\_X および CFR は 16 ビットのレジスタであり、表 4-4 に示すようにプログラムされます。上位 4 ビットで書き込み / 読み取りモードと、それに対応するレジスタが選択されます。

**表 4-4. ADS8354 のレジスタ構成**

| レジスタ      | データ (HEX) | 備考                                                                                                  |

|-----------|-----------|-----------------------------------------------------------------------------------------------------|

| REF DAC_A | 9FF8      | REF DAC_A への書き込みモード、VREF_A = 2.5V を選択                                                               |

| REF DAC_B | AFF8      | REF DAC_B への書き込みモード、VREF_B = 2.5V を選択                                                               |

| CFR       | 8640      | CFR への書き込みモード、SDO_A で A と B の 32-CLK デュアル SDO モードを選択、FSR = $\pm 2 \times V_{REF}$ 、内部 $V_{REF}$ を選択 |

詳細については、ADSxx54 のデータシートを参照してください。

#### 4.4 エンコーダ コネクタ

Sin/Cos エンコーダへのインターフェイスとして、2 つのコネクタ オプションが利用可能です。デフォルトのコネクタは、シールド付き SubD-15 メス型コネクタです。もう 1 つのオプションは 8 ピンヘッダーです。コネクタ割り当ての詳細については、セクション 6 を参照してください。

#### 4.5 設計のアップグレード

高分解能パス: 高分解能チャネルのノイズ耐性をさらに高めるため、差動アンプ THS4531A では 1 次ローパス フィルタを推奨します。最大 500kHz の高分解能チャネルを使用する場合は、5k $\Omega$  マッチング済み抵抗と並列に 33pF、1% NPO/COG コンデンサを THS4531A 帰還パスにそれぞれ推奨します。カットオフ周波数が低い場合、それぞれ容量の値を高くする必要があります。

信号 PWR\_EN による出力イネーブルを備えた 5.25V LDO: コネクタ J-7、ピン 4 を使用可能ですが、LDO への入力が常にプルアップ (ジャンパ: J7 4-6) またはプルダウン (ジャンパ: J7 4-3) のいずれかで終端されるように、U2、ピン 4 から 3.3V (V3\_3\_dc) への 10k の追加プルアップを推奨します。

## 5 ソフトウェア設計

### 5.1 概要

直交エンコードされたパルス カウンタと SPI が組み込まれた任意の組込みプロセッサまたはマイコンは、TIDA-00176 ハードウェア設計と組み合わせて使用できます。

ただし、TIDA-00176 ハードウェアリファレンス デザインを容易に評価できるように、C2000 F28069M Piccolo LaunchPad 用のサンプル フームウェアが提供されています。その結果、Sin/Cos インクリメンタル ポジション エンコーダを使用して TIDA-00176 を評価することができます。USB 仮想 COM ポートを介したユーザー メニューが提供され、選択した Sin/Cos エンコーダのライン カウントを初期化し、計算された高分解能角度情報を他のユーザーが選択可能なデータとともに印刷します。

F28069M で利用されている主なペリフェラルは、SPI-A ペリフェラルで、デュアル高分解能 16 ビットデータ信号 ( $A_{16\text{-bit}}$  および  $B_{16\text{-bit}}$ ) を読み取ることができます。組込みのデュアル S/H ADC を使用して、シングルエンドアナログ信号  $A_{12\text{-bit}}$  および  $B_{12\text{-bit}}$  を変換できます。直交エンコーダ パルス (eQEP2) モジュールは、信号  $A_{\text{TTL}}$  および  $B_{\text{TTL}}$  およびゼロ インデックス マーカー  $R_{\text{TTL}}$  に基づく、絶対位置の初期化用の方向アップダウントリガメントルス マーカーに使用されます。ePWM1 タイマは、周期的な割り込みを生成し、新しい角度測定をトリガするために使われます。16kHz の周期が選択されました。SCI-A ペリフェラルを使用して、仮想 COM ポート経由で 115000 ポートの UART ベースのユーザー インターフェイスを実装しました。

図 5-1. TMS320F28069M のペリフェラル モジュールと、TIDA-00176 ホスト プロセッサ インターフェイスへのピン構成

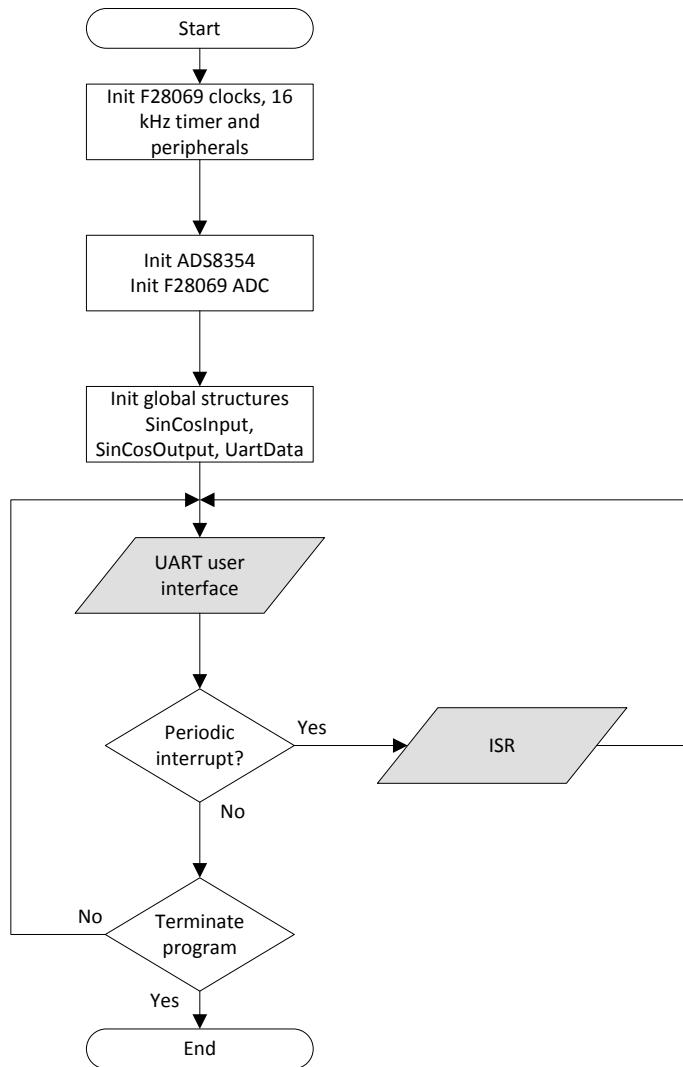

## 5.2 C2000 Piccolo フームウェア

Piccolo TMS320F28069M 用のサンプル フームウェアの開発とコンパイルが行われており、図 5-1 で概要を示したペリフェラル モジュールを活用します。

フームウェアは C2000 controlSUITE™ を活用します。フームウェアは基本的に、3 つの機能ブロックで構成されています。F28069M フームワークは、図 5-2 に概説しているように、必要なデータを同期的にサンプリングし、補間角度を計算するアルゴリズムであり、UART 端末ベースのユーザー インターフェイスです。

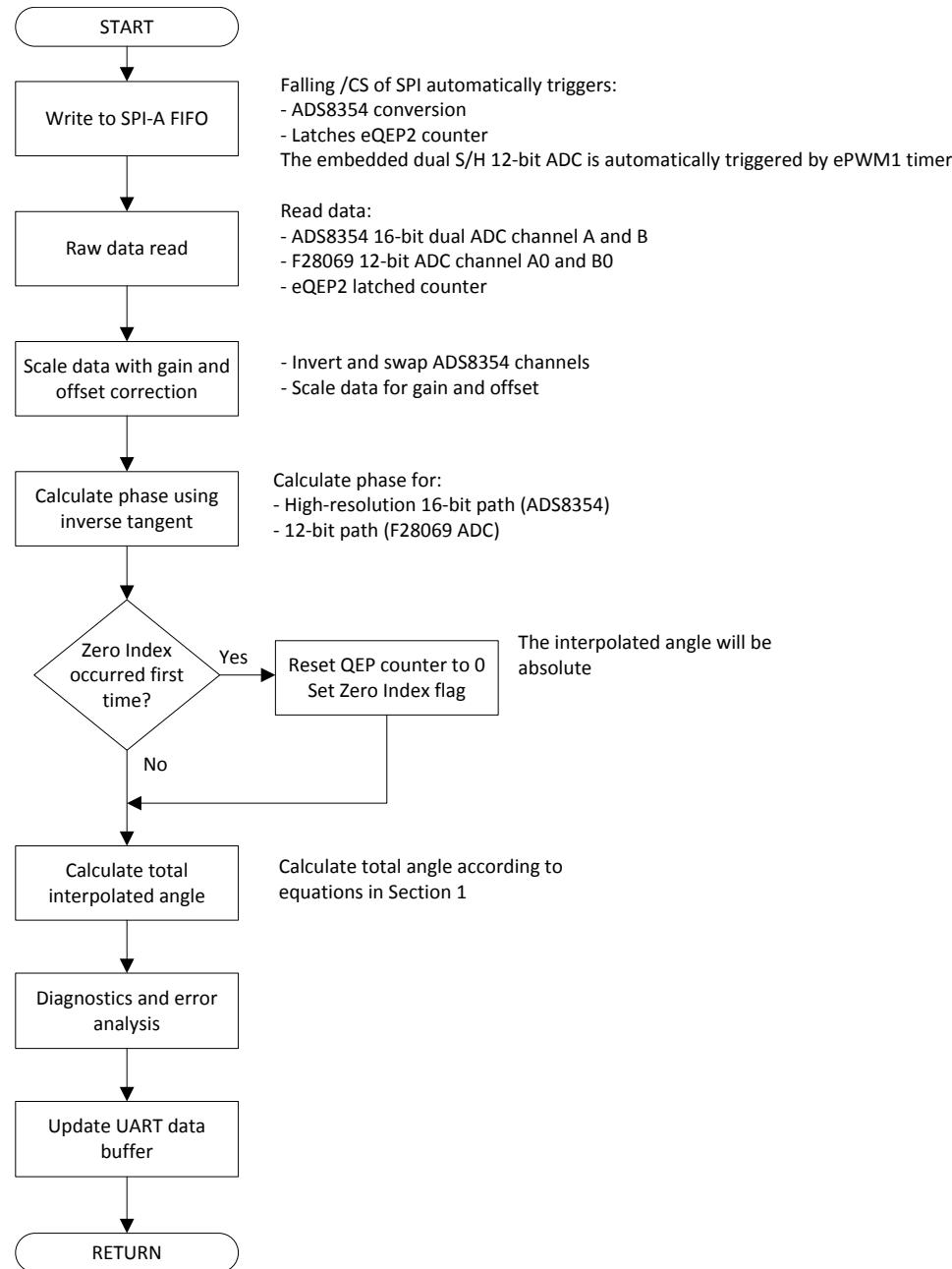

図 5-2. Sin/Cos エンコーダ フームワークのフローチャート

TMS320F28069M フームワークは、TMS320F26069M CPU クロックを 80MHz に初期化し、GPIO マルチプレクサ、SPI-A、SCI-A (UART) などのペリフェラル、ePWM1 ベースの周期タイマと割り込み、組込みの 12 ビット デュアル S/H ADC を初期化します。また、セクション 4.3.2.4 に概要を示すように、SPI-A を通して外部 16 ビット デュアル ADC ADS8354 を構成します。SPI-A は、10MHz のシリアル クロックにより SPI マスターとして構成されます。これは Piccolo F28069M の最大 SPI クロックです。Sitara AM437x や Delfino F287x など他のプロセッサの場合、SPI クロックを最大 24MHz することができます。

初期化後、プログラムは UART ベースのユーザー インターフェイスを起動し、周期割り込みサービス ルーチン (ISR) を提供します。周期 ISR は、外部 16 ビット ADC ADS8354 と内部 12 ビット ADC の両方を基準とした同期データ キャプチャ、中間位相の計算、合計補間角度を実装しています。セクション 1 に概要を示すアルゴリズムに従います。このコード

は、TI の IQmath ライブラリを使用して、32 ビットの整数形式である Q28 固定小数点数を用いて記述されています。32 ビットの固定小数点数を 32 ビットの IEEE 浮動小数点と比較した場合の利点は、データ範囲にかかわらず、分解能が一定に保たれることです。データ範囲は角度 (ユニットごと) と ADC 入力データに対して 0 ~ 1.0 に制限されており、また入力は最大  $\pm 5$  (V) にスケーリングされているため、整数範囲が  $\pm 8.0$  の Q28 の数値により十分なヘッドroomが得られ、すべてのデータについて精度は一定に保たれます。

図 5-3 に、ISR のフローチャートを示します。

図 5-3. 補間角度計算を含む Sin/Cos エンコーダ メイン ISR のフローチャート

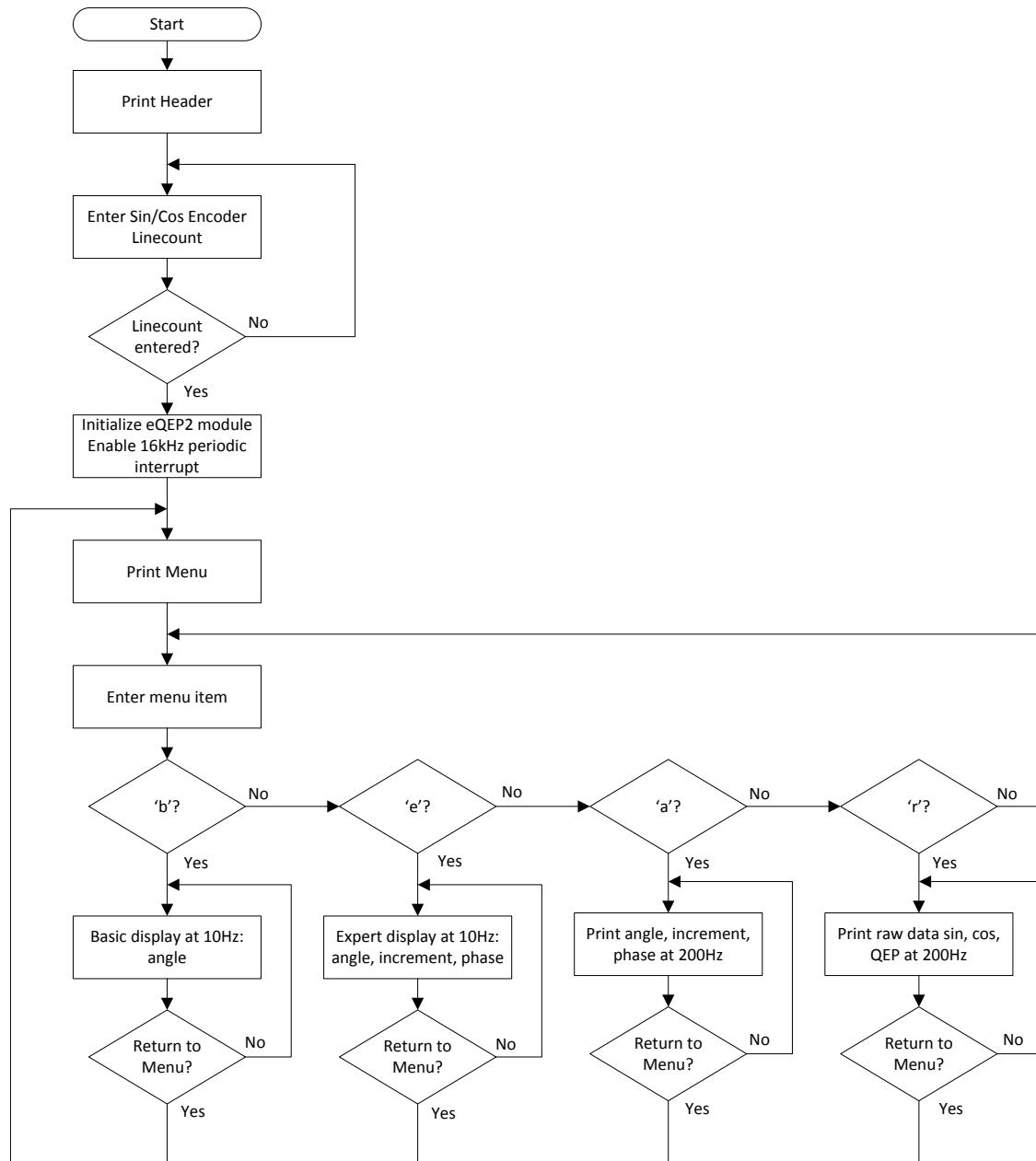

### 5.3 ユーザー インターフェイス

迅速な評価を可能にするために、仮想 COM ポートベースのユーザー インターフェイスが実装されています。Tera Term のような 115000 ポートの任意の端末インターフェースを使用できます。

ユーザー インターフェイスを使用すると、プログラムがメイン メニューに到達する前に、Sin/Cos エンコーダ接続のラインカウントを入力できます。このメニューには、高解像度のアングルだけで基本表示モードを選択するか、またはエキスパート表示モードを選択するためのメニュー項目オプションがあります。どちらも

10Hz の更新レートで表示されます。さらにメニュー項目は 200Hz の更新レートでのデータダンプ モードであり、後分析のためにファイルに書き込むことを意図しています。

ユーザー インターフェイスのフローチャートを [図 5-4](#) に示します。

図 5-4. UART 端末ユーザー インターフェイスのフローチャート

表 5-1 から 表 5-4 に、4 つのメニュー項目それぞれのデータ出力形式の概要を示します。データダンプ モードでは、各行のデータ間の区切り文字として「タブ」が含まれます。

**表 5-1. 基本表示モードの出力形式とデータスケーリング**

| メニュー    | COLUMN 1                    | COLUMN 2 | COLUMN 3 | COLUMN 4 | COLUMN 5 |

|---------|-----------------------------|----------|----------|----------|----------|

| 「b」基本表示 | ADS8354 を使用した<br>総角度 (スケール) | —        | —        | —        | —        |

| データ形式   | フロート (0 ~ 360 度)            | —        | —        | —        | —        |

**表 5-2. エキスパート表示モードの出力形式とデータスケーリング**

| メニュー        | COLUMN 1                    | COLUMN 2                 | COLUMN 3 | COLUMN 4             | COLUMN 5                 |

|-------------|-----------------------------|--------------------------|----------|----------------------|--------------------------|

| 「e」エキスパート表示 | ADS8354 を使用した<br>総角度 (スケール) | マーカー インデックス<br>R が発生しました | 増分カウント   | 位相 ADS8354<br>(スケール) | 位相<br>F28069M ADC (スケール) |

| データ形式       | フロート (0 ~ 360 度)            | フラグ (はい / いいえ)           | 整数       | 浮動小数点数 (0 ~ 1.0)     | 浮動小数点数 (0 ~ 1.0)         |

**表 5-3. 角度データダンプ メニューの形式とスケーリング**

| メニュー     | COLUMN 1                    | COLUMN 2                           | COLUMN 3 | COLUMN 4             | COLUMN 5                     | COLUMN 6           |

|----------|-----------------------------|------------------------------------|----------|----------------------|------------------------------|--------------------|

| 「d」角度ダンプ | ADS8354 を使用した<br>総角度 (スケール) | F28069 ADC を使<br>用した総角度 (スケ<br>ール) | 増分カウント   | 位相 ADS8354<br>(スケール) | 位相<br>F28069M ADC (ス<br>ケール) | 周期的なティック<br>(スケール) |

| データ形式    | フロート (0 ~ 360<br>度)         | フロート (0 ~ 360<br>度)                | 整数       | 浮動小数点数 (0<br>~ 1.0)  | 浮動小数点数 (0<br>~ 1.0)          | 整数 (66μs)          |

**表 5-4. 未加工データダンプ メニューのフォーマットとスケーリング**

| メニュー          | COLUMN 1       | COLUMN 2                 | COLUMN 3                        | COLUMN 4                        | COLUMN 5                      | COLUMN 6                      | COLUMN 7           |

|---------------|----------------|--------------------------|---------------------------------|---------------------------------|-------------------------------|-------------------------------|--------------------|

| 「R」未加工デー<br>タ | 増分カウント<br>(SW) | 増分カウント (ラッ<br>チ オン / CS) | 入力 A+/A-、<br>ADS8354 (スケ<br>ール) | 入力 B+/B-、<br>ADS8354 (スケ<br>ール) | 入力 A+/A-、<br>F28069<br>(スケール) | 入力 A+/A-、<br>F28069<br>(スケール) | 周期的なティック<br>(スケール) |

|               | 整数             | 整数                       | 浮動電圧 (V <sub>PP</sub> )         | 浮動電圧 (V <sub>PP</sub> )         | 浮動電圧 (V <sub>PP</sub> )       | 浮動電圧 (V <sub>PP</sub> )       | 整数 (66μs)          |

## 6 はじめに

### 6.1 TIDA-00176 の PCB の概要

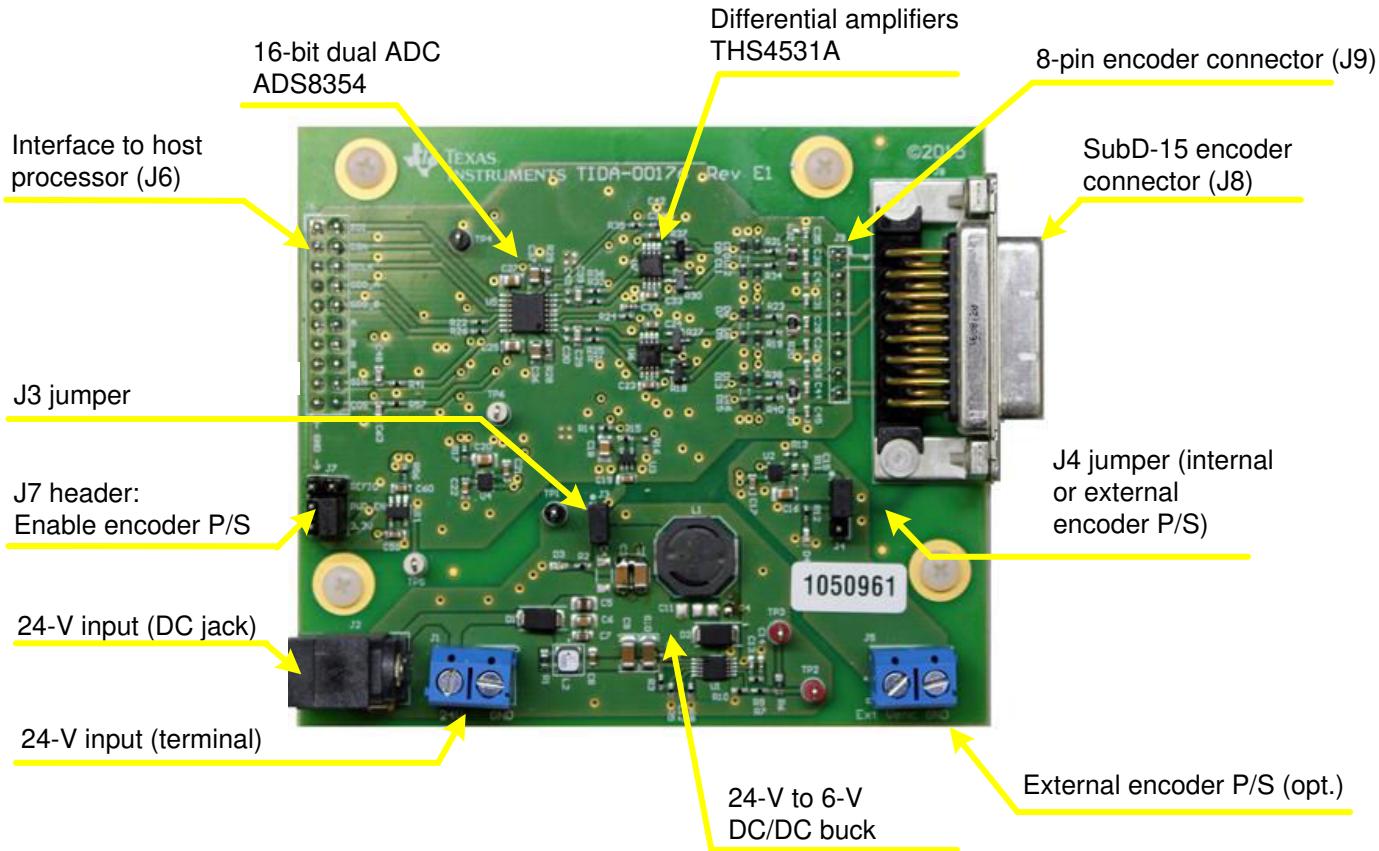

図 6-1 に、TIDA-00176 PCB の上面の写真を示します。ヘッダおよびデフォルトのジャンパ設定については、セクション 6.2 で説明します。

図 6-1. TIDA-00176 基板の画像

## 6.2 コネクタおよびジャンパ設定

### 6.2.1 コネクタとジャンパの概要

表 6-1 から 表 6-4 に、コネクタの割り当てとジャンパ設定の概要を示します。

24V の公称入力電圧は、コネクタ J1 または J2 を介して供給できます。

**表 6-1. コネクタの割り当てとジャンパ設定 (J1 ~ J4)**

| コネクタとピンの割り当て               | 説明                       |

|----------------------------|--------------------------|

| <b>24V 入力 (端子:J1)</b>      |                          |

| 1                          | 24V 入力電圧 (17 ~ 36V)      |

| 2                          | GND                      |

| <b>24V 入力 (DC ジャック:J2)</b> |                          |

| 内部                         | 24V 入力電圧 (17 ~ 36V)      |

| 外部                         | GND                      |

| <b>J3</b>                  |                          |

| 1                          | TPS54040A の出力 (デフォルト 6V) |

| 2                          | 6V 電源レール                 |

| <b>J4</b>                  |                          |

| 1                          | 5.25V 電源 (デフォルト)         |

| 2                          | V_ENC (エンコーダの電源電圧)       |

| 3                          | 外部電源                     |

必要に応じて、コネクタ J5 を通して、5.25V エンコーダの電源電圧以外の外部電源電圧を印加できます。

**表 6-2. 外部エンコーダ電源コネクタ (J5)**

| ピン | 説明          |

|----|-------------|

| 1  | エンコーダ電源 VCC |

| 2  | エンコーダ電源 GND |

**表 6-3. ホスト プロセッサ インターフェイス (J6)**

| ピン | 説明  | ピン | 説明 (3.3V I/O)              |

|----|-----|----|----------------------------|

| 1  | GND | 2  | SDI (ADS8354)              |

| 3  | GND | 4  | /CS (ADS8354)              |

| 5  | GND | 6  | SCLK (ADS8354)             |

| 7  | GND | 8  | SDO_A (ADS8354)            |

| 9  | GND | 10 | SDO_B (ADS8354)            |

| 11 | GND | 12 | A (TTL)                    |

| 13 | GND | 14 | B (TTL)                    |

| 15 | GND | 16 | R (TTL)                    |

| 17 | GND | 18 | A (シングル エンド アナログ 0 ~ 3.3V) |

| 19 | GND | 20 | B (シングル エンド アナログ 0 ~ 3.3V) |

ホスト プロセッサ インターフェイスの信号の詳細については、[セクション 4.3](#) を参照してください。

**表 6-4. コネクタの割り当てとジャンパ設定 (J7 ~ J9)**

| ピン                                | 説明          | ピン | 説明                        |

|-----------------------------------|-------------|----|---------------------------|

| <b>エンコーダ電源イネーブル (J7) 付きヘッダ J7</b> |             |    |                           |

| 1                                 | GND         | 2  | REFIO (1.65V)             |

| 3                                 | GND         | 4  | エンコーダのイネーブル電源電圧 (5.25V)   |

| 5                                 | GND         | 6  | 3.3V                      |

| <b>エンコーダ DSUB15 コネクタ (J8)</b>     |             |    |                           |

| 1                                 | A+          | 2  | エンコーダ電源 GND               |

| 3                                 | B+          | 4  | エンコーダ電源 VCC (デフォルト 5.25V) |

| 5                                 | NC          | 6  | NC                        |

| 7                                 | R-          | 8  | NC                        |

| 9                                 | A-          | 10 | 予約済み                      |

| 11                                | B-          | 12 | 予約済み                      |

| 13                                | NC          | 14 | R+                        |

| 15                                | NC          | —  | —                         |

| <b>エンコーダ 8SIL100 コネクタ (J9)</b>    |             |    |                           |

| 1                                 | A+          | 2  | A-                        |

| 3                                 | エンコーダ電源 GND | 4  | B-                        |

| 5                                 | B+          | 6  | エンコーダ電源 VCC (デフォルト 5.25V) |

| 7                                 | R-          | 8  | R+                        |

### 6.2.2 デフォルトのジャンパ構成

TIDA-00176 基板を使用する前に、以下のデフォルトのジャンパ設定が適用されていることを確認してください。基板画像 [図 6-1](#) を参照してください。

**表 6-5. デフォルトのジャンパ設定**

| ヘッダ | ジャンパ設定                                                             |

|-----|--------------------------------------------------------------------|

| J3  | J3 のピン 1 ~ 2 の間にジャンパを挿入して、3 個の LDO に接続された 6V 中間レールを有効にします          |

| J4  | J4 ピン 1 ~ 2 の間にジャンパを挿入して、オンボードの 5.25V エンコーダ電源をエンコーダ コネクタにルーティングします |

| J7  | J7 ピン 4 ~ 6 の間にジャンパを挿入して、5.25V エンコーダ電源を有効にします。                     |

## 6.3 設計評価

### 6.3.1 前提条件

#### TIDA-00176 の

TI 設計を評価するためには、以下のハードウェア機器とソフトウェアが必要です。

**表 6-6. 前提条件**

| 装置                                       | 備考                                                                    |

|------------------------------------------|-----------------------------------------------------------------------|

| 24V 電源                                   | 250mA 以上の出力電流を供給する 24V 出力電源ブリック<br>出力コネクタ内径 2.1mm× 外径 5.5mm× 9.5mm メス |

| TIDA-00176 ハードウェア                        | セクション 6.2 に基づくデフォルトのジャンパ設定に使用。                                        |

| ボード設定用の 3 個のジャンパ                         | 2 ピン、100mil                                                           |

| TIDA-00176 フームウェア                        | TIDA-00176 設計フォルダからダウンロード                                             |

| InstaSPIN-MOTION F28069M LaunchPad       | TI eStore で入手可能                                                       |

| USB ケーブル                                 | ミニ USB Type-A から USB Type-A へのケーブル                                    |

| TIDA-00176 から LaunchPad へのアダプタ           | TI 社内用 (オプション)                                                        |

| Code Composer Studio 6                   | <a href="http://www.ti.com">www.ti.com</a> からダウンロード                   |

| PC ターミナル プログラム                           | Tera Term などの任意のターミナル プログラム                                           |

| 1V <sub>PP</sub> 出力信号を使用した Sin/Cos エンコーダ | たとえば、ROD480 など                                                        |

### 6.3.2 ハードウェア設定

TIDA-00176 と InstaSPIN-MOTION LaunchPad との間には、以下の接続が必要です。

**表 6-7. TIDA-00176 ホスト プロセッサ インターフェイス (J6) から InstaSPIN -LaunchPad への接続**

| TIDA-00176 ホスト プロセッサ インターフェイス (J6) |                            | 接続先<br>→ | InstaSPIN-MOTION LAUNCHPAD |                                     |

|------------------------------------|----------------------------|----------|----------------------------|-------------------------------------|

| J6-PIN                             | 説明                         |          | ヘッダー ピン                    | 説明 (3.3-V I/O)                      |

| 1                                  | GND                        |          | J3 - ピン 22                 | GND                                 |

| 19                                 | GND                        |          | J2 - ピン 20                 | GND                                 |

| 2                                  | SDI (ADS8354)              |          | J2 - ピン 15                 | GPIO16/SPISIMOA                     |

| 4                                  | /CS (ADS8354)              |          | J2 - ピン 19<br>J6 - ピン 59   | GPIO27/eQEP2S および<br>GPIO19/SPISTEA |

| 6                                  | SCLK (ADS8354)             |          | J1 - ピン 7                  | GPIO18/SPICLKA                      |

| 8                                  | SDO_A (ADS8354)            |          | J2 - ピン 14                 | GPIO17/SPISOMIA                     |

| 10                                 | SDO_B (ADS8354)            | NC       | NC                         | NC                                  |

| 12                                 | A (TTL)                    |          | J6 - ピン 55                 | GPIO24/eQEP2A                       |

| 14                                 | B (TTL)                    |          | J6 - ピン 54                 | GPIO25/eQEP2B                       |

| 16                                 | R (TTL)                    |          | J6 - ピン 58                 | GPIO26/eQEP2I                       |

| 18                                 | A (シングル エンド アナログ 0 ~ 3.3V) |          | J3 - ピン 27                 | ADCIN_A0                            |

| 20                                 | B (シングル エンド アナログ 0 ~ 3.3V) |          | J3 - ピン 28                 | ADCIN_B0                            |

以下の手順に従って、ハードウェアをセットアップします：

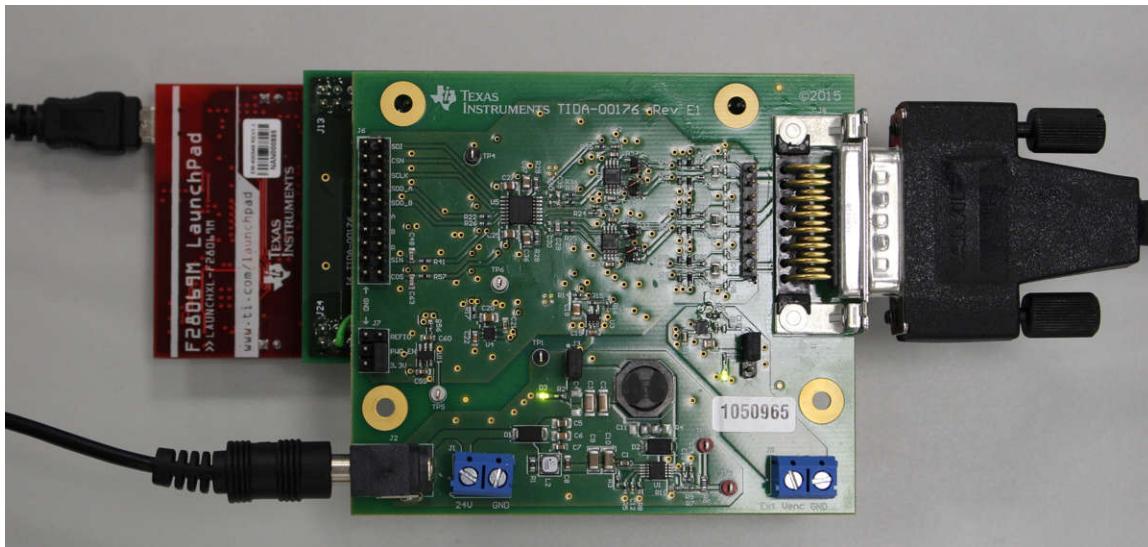

- 適切なコネクタまたはアダプタを使用して TIDA-00176 ボードを InstaSPIN-MOTION LaunchPad に接続します。

### 注

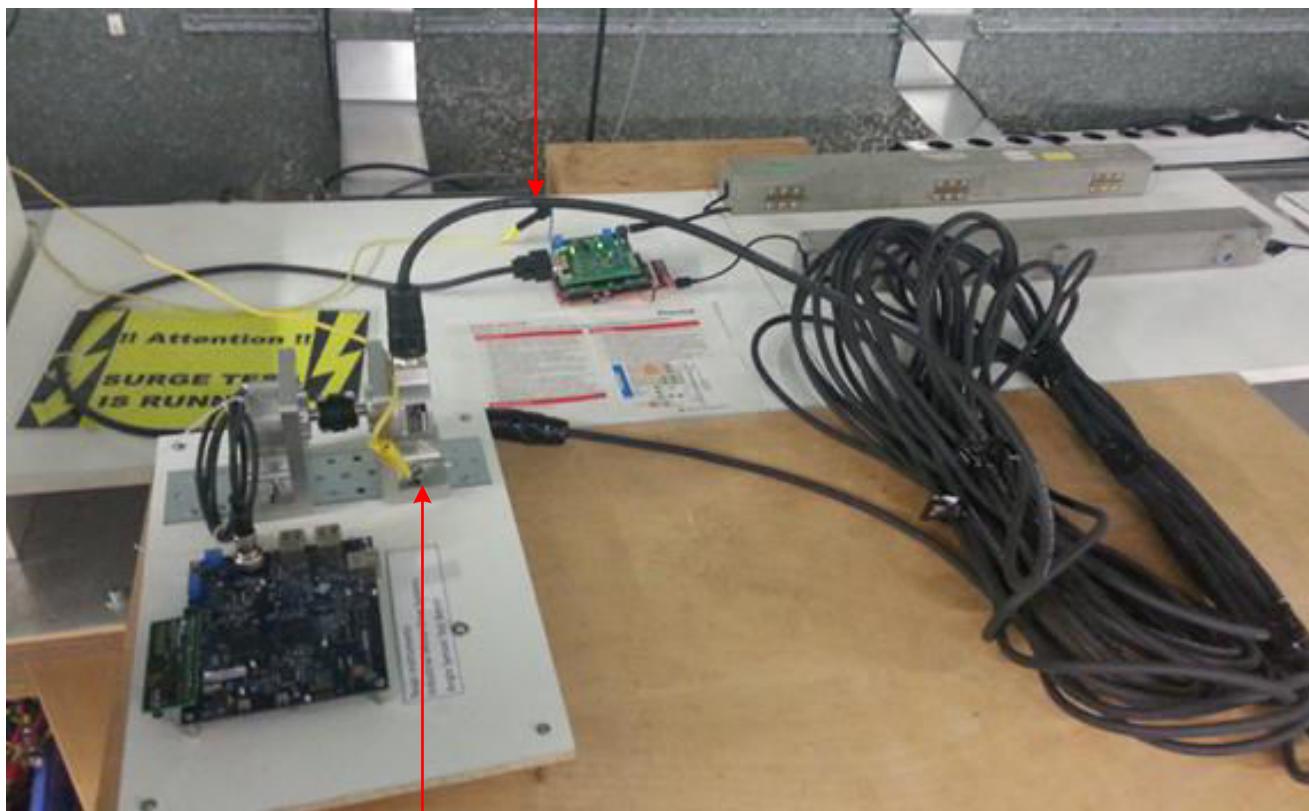

内部テストでは、図 6-2 に示すように、TIDA-00176 と InstaSPIN-MOTION LaunchPad とのインターフェイスとしてアダプタボードが設計されています。

- セクション 6.2.2 に示されているデフォルトの 3 つのジャンパ設定で、TIDA-00176 が構成されていることを確認します。

- SubD-15 コネクタ (J8) または SIL-8 コネクタ (J9) のいずれかを使用して、Sin/Cos エンコーダをボードに接続します。

- 24V 入力を J1 コネクタに電源ブリックから挿入するか、外部電源 (17 ~ 36V) の場合は J2 コネクタを使用します。

- ミニ USB ケーブルを InstaSPIN-MOTION LaunchPad から PC に接続します。

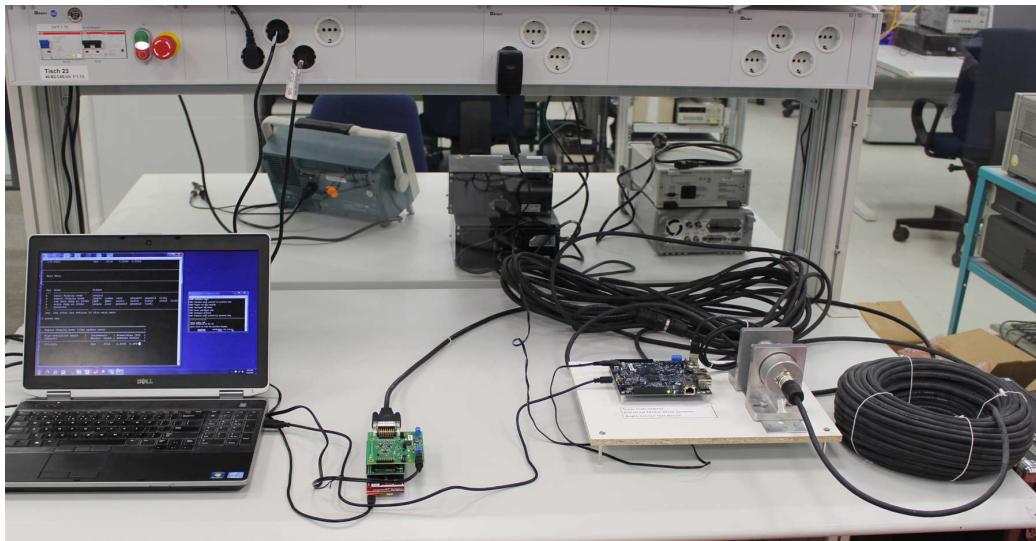

図 6-2. InstaSPIN-MOTION LaunchPad に搭載された TIDA-00176 ボード

また、<http://www.ti.com/tool/launchxl-f28069m> で InstaSPIN-MOTION LaunchPad の前提条件も参照してください。

F28069 LaunchPad 上にある以下のジャンパが設定されていることを確認します：JP1、JP2、JP3、JP7。JP4、JP5、JP6 を設定しないでください。つまり、これらを接続しないでください。

### 6.3.3 ソフトウェアの設定

以下の手順に従って、ソフトウェアをセットアップします：

- まだ終わっていないければ、TIDA-00176 SinCosEncoder フームウェアを TIDA-00176 設計フォルダからダウンロードし、c:\ti\tida-00176\bin などのフォルダに展開します。

- Tera Term のように、仮想 COM ポートに接続できるターミナル プログラムを呼び出します。

- ターミナル プログラムをシリアル コンソール モードでセットアップし、パラメータを次のように設定します：

- ボーレート = 115200、データ = 8 ビット、パリティ = なし、ストップ = 1 ビット、フロー制御 = なし

- Code Composer Studio (CCS) を起動します。

- CCS では、InstaSPIN-MOTION F28069M LaunchPad で XDS100 JTAG ターゲットを設定します。

- CCS で、TMS320F28069M に接続し、TIDA-00176 バイナリ出力ファイルをダウンロードします。実行 → 負荷プログラム → TIDA-00176\_SinCosEncoder\_Firmware\_rev1\_0.out

- CCS でターゲットを実行します。

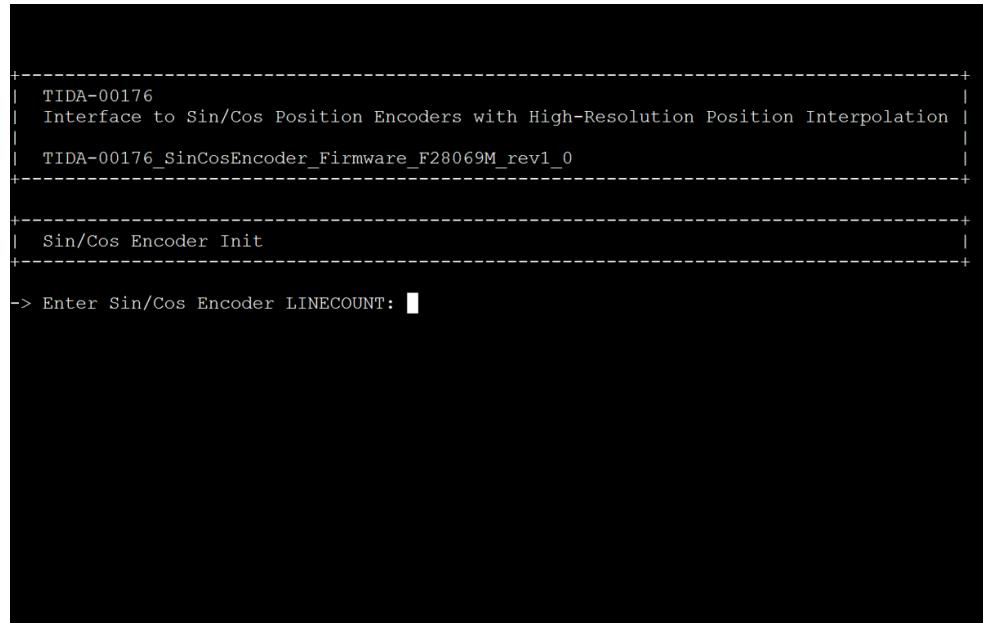

ターミナル プログラムには、図 6-3 に示すように、TIDA-00176 の開始画面が表示されます。

#### 注

バイナリ ファイルを F28069M にロードした後、ステップ 4 ~ 7 は不要になります。LaunchPad をリセットするだけで、プログラムを再起動できます。F28069M が、内部フラッシュからブートするように構成されていることを確認します。InstaSPIN-MOTION LaunchPad のマニュアルを参照してください。

トラブルシューティング: 接続が確立されない場合、USB 仮想 COM ポートである TI XDS100 チャネル B の VCP ドライバを、Windows®7 のデバイスマネージャで有効にする必要があります。詳細については、InstaSPIN-MOTION LaunchPad のマニュアルを参照してください。

```

+-----+

| TIDA-00176

| Interface to Sin/Cos Position Encoders with High-Resolution Position Interpolation |

| TIDA-00176_SinCosEncoder_Firmware_F28069M_rev1_0

+-----+

+-----+

| Sin/Cos Encoder Init

+-----+

-> Enter Sin/Cos Encoder LINECOUNT: ■

```

図 6-3. TIDA-00176 スタートアップ時のユーザー インターフェイス

### 6.3.4 ユーザー インターフェイス

起動後、ユーザー インターフェイスでは、Sin/Cos エンコーダのライン カウントを 10 進数で入力する必要があります。ライン カウントを入力すると、図 6-4 に示すようにメイン メニューが使用可能になります。

```

Interface to Sin/Cos Position Encoders with High-Resolution Position Interpolation |

TIDA-00176 SinCosEncoder Firmware F28069M rev1.0

+-----+

| Sin/Cos Encoder Init

+-----+

-> Enter Sin/Cos Encoder LINECOUNT: 2000

LINECOUNT entered: 2000

+-----+

| Main Menu

+-----+

key mode format

---

b basic display mode [angle]

e expert display mode [angle index incr phase16 phase12 tick]

r raw data dump at 200Hz [QEP QEPL sin16 cos16 sin12 cos12 tick]

a angle dump at 200Hz [angle incr phase16 phase12 tick]

x reserved

---

any any other key returns to this main menu

-> press key

```

図 6-4. TIDA-00176 ユーザー インターフェイスのメイン メニュー

4 種類のメニューが用意されています。各文字 **b**、**e**、**r**、**a** のいずれかを押して選択できます。メニュー項目 **x** は、ソフトウェア開発中の内部テストモード用に予約済みです。

「**b**」または「**e**」を押して基本表示モードまたはエキスパート表示モードを選択します。エキスパート表示モードでは、補間した角度を度または追加情報で印刷します。索引が発生していないため、最初は、合計角度は絶対値ではないことに注意してください。これは、エキスパート表示モードで増分マーカーが「いいえ」に設定されていることで認識できます。増分マーカーが「はい」に変わるまで、エンコーダを時計回りにゆっくりと回します。これで、補間角度は索引 マーカー位置に對して絶対値になります。メイン メニューに戻るには、任意のキーを押します。

```

+=====+

| High-resolution angle [degree] |

+=====+

359.9804

+-----+

| Main Menu

+-----+

key mode format

---

b basic display mode [angle]

e expert display mode [angle index incr phase16 phase12 tick]

r raw data dump at 200Hz [QEP QEPL sin16 cos16 sin12 cos12 tick]

a angle dump at 200Hz [angle incr phase16 phase12 tick]

x reserved

---

any any other key returns to this main menu

-> press key

+=====+

| Expert display mode [10Hz update rate] |

+=====+

+=====+

| High-resolution angle | Increments | Phase/atan [PU] |

| [degree] | Marker Count | ADS8354 F28069 |

+=====+

359.9804 No 0 0.8914 0.8926

```

図 6-5. 基本角度表示およびエキスパート表示モード

「a」を押して、200Hz の更新レートで角度データダンプを開始します。データフォーマットについては、[セクション 5](#) に記載しています。スクリーンショットを [図 6-6](#) に示します。いずれかのキーを押して停止し、メインメニューに戻ります。

| Angle16PU  | Angle12PU  | Incr | Phase16PU | Phase12PU | Tick[32kHz] |

|------------|------------|------|-----------|-----------|-------------|

| 0.85510715 | 0.85510683 | 7005 | 0.25946   | 0.25879   | 9190        |

| 0.85510674 | 0.85510638 | 7005 | 0.25862   | 0.25788   | 9270        |

| 0.85510715 | 0.85510668 | 7005 | 0.25945   | 0.25851   | 9350        |

| 0.85510679 | 0.85510661 | 7005 | 0.25871   | 0.25835   | 9430        |

| 0.85510692 | 0.85510671 | 7005 | 0.25898   | 0.25854   | 9510        |

| 0.85510753 | 0.85510694 | 7005 | 0.26022   | 0.25902   | 9590        |

| 0.85510702 | 0.85510659 | 7005 | 0.25919   | 0.25830   | 9670        |

| 0.85510717 | 0.85510682 | 7005 | 0.25949   | 0.25878   | 9750        |

| 0.85510726 | 0.85510671 | 7005 | 0.25967   | 0.25857   | 9830        |

| 0.85510681 | 0.85510660 | 7005 | 0.25876   | 0.25833   | 9910        |

| 0.85510682 | 0.85510658 | 7005 | 0.25877   | 0.25829   | 9990        |

| 0.85510727 | 0.85510681 | 7005 | 0.25970   | 0.25877   | 10070       |

| 0.85510728 | 0.85510672 | 7005 | 0.25972   | 0.25858   | 10150       |

| 0.85510755 | 0.85510694 | 7005 | 0.26027   | 0.25902   | 10230       |

図 6-6. 更新レート 200Hz での角度ダンプ モード

「r」を押して、200Hz の更新レートで未加工データダンプを開始します。データフォーマットについては、[セクション 5](#) に記載しています。スクリーンショットを [図 6-7](#) に示します。いずれかのキーを押して停止し、メインメニューに戻ります。

| QEP  | QEPL | Vsin16 | Vcos16 | Vsin12 | Vcos12 | Tick[32kHz] |

|------|------|--------|--------|--------|--------|-------------|

| 7005 | 7005 | 1.0044 | 0.0631 | 1.0280 | 0.0583 | 1542        |

| 7005 | 7005 | 1.0108 | 0.0631 | 1.0280 | 0.0583 | 1622        |

| 7005 | 7005 | 1.0069 | 0.0616 | 1.0280 | 0.0583 | 1622        |

| 7005 | 7005 | 1.0150 | 0.0662 | 1.0309 | 0.0597 | 1702        |

| 7005 | 7005 | 1.0089 | 0.0627 | 1.0324 | 0.0612 | 1782        |

| 7005 | 7005 | 1.0083 | 0.0643 | 1.0280 | 0.0597 | 1862        |

| 7005 | 7005 | 1.0101 | 0.0680 | 1.0295 | 0.0612 | 1942        |

| 7005 | 7005 | 1.0066 | 0.0636 | 1.0265 | 0.0597 | 2022        |

| 7005 | 7005 | 1.0072 | 0.0666 | 1.0265 | 0.0597 | 2102        |

| 7005 | 7005 | 1.0083 | 0.0595 | 1.0295 | 0.0568 | 2182        |

| 7005 | 7005 | 1.0047 | 0.0605 | 1.0251 | 0.0554 | 2262        |

| 7005 | 7005 | 1.0032 | 0.0610 | 1.0251 | 0.0583 | 2342        |

| 7005 | 7005 | 1.0040 | 0.0671 | 1.0280 | 0.0612 | 2422        |

| 7005 | 7005 | 1.0110 | 0.0643 | 1.0324 | 0.0597 | 2502        |

図 6-7. 更新レート 200Hz での未加工データダンプ モード

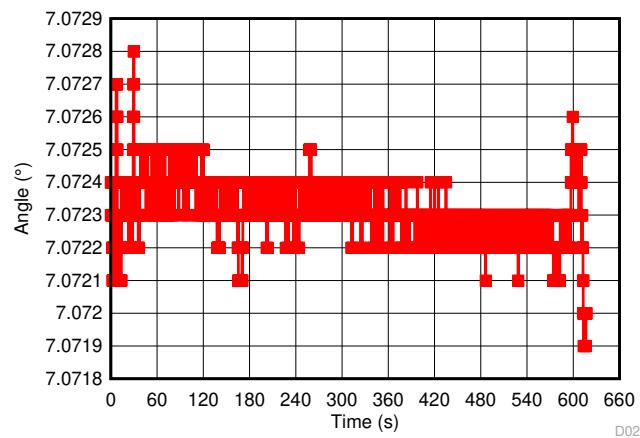

## 7 テスト結果

各機能ブロックと基板全体を特性評価するためにテストを実施しました。特に次のテストを行いました。

- アナログ シグナル チェーン ガイド

- パワー マネージメント

- Sin/Cos エンコーダ シグナル ミュレーションと Sin/Cos エンコーダを搭載したフル システム

- EMC 耐性 (ED, EFT、サージ)

テストは室温約 22 ~ 23 度、または 75 度か 85 度で実施しました。特に記載がない場合は、室温が適用されます。

以下に、TIDA-00176 のテスト セッションで使用した機器を示します：

**表 7-1. TIDA-00176 性能テスト用の試験装置**

| 試験装置                                                                        | 部品番号                                |

|-----------------------------------------------------------------------------|-------------------------------------|

| プログラマブルな 16 ビット波形発生器                                                        | Keysight (アジレント) 33600A             |

| 低速オシロスコープ (電源テストに最適)                                                        | Tektronix TDS2024B                  |

| 高速オシロスコープ (アナログ信号テストに最適)                                                    | Tektronix TDS784C                   |

| 調整可能な SMPS                                                                  | Knuerr-Heinzinger Polaris 125-5     |

| 24V、2.5A 時 SMPS (電源ブリック)                                                    | V-infinity 3A-621DN24               |

| 真の実効値マルチメータ                                                                 | Fluke 179                           |

| 差動プローブ                                                                      | Tektronix P6630                     |

| シングルエンド プローブ                                                                | Tektronix P6139A                    |

| プログラマブル サーマル チャンバー                                                          | Voetsch VT 4002                     |

| プログラマブル電子負荷モジュール                                                            | Chroma 63103                        |

| 電子負荷モジュール用制御モジュール                                                           | Chroma 6314                         |

| 温度カメラ                                                                       | Fluke TI40                          |

| 制御システムのループ アナライザ                                                            | Venable 3120                        |

| HEIDENHAIN シールド ケーブル、PUR M23 オス / メス (4 × 2 × 0.14mm、4 × 0.5mm)、10m、20m、50m | 298399-10、-20、-50                   |

| HEIDENHAIN M23/Sub-D15 オス アダプタ ケーブル、1m                                      | 310196-01                           |

| HEIDENHAIN Sin/Cos エンコーダ                                                    | ROD480-2000、ROD480-1024、ROD486-2048 |

## 7.1 アナログ性能テスト

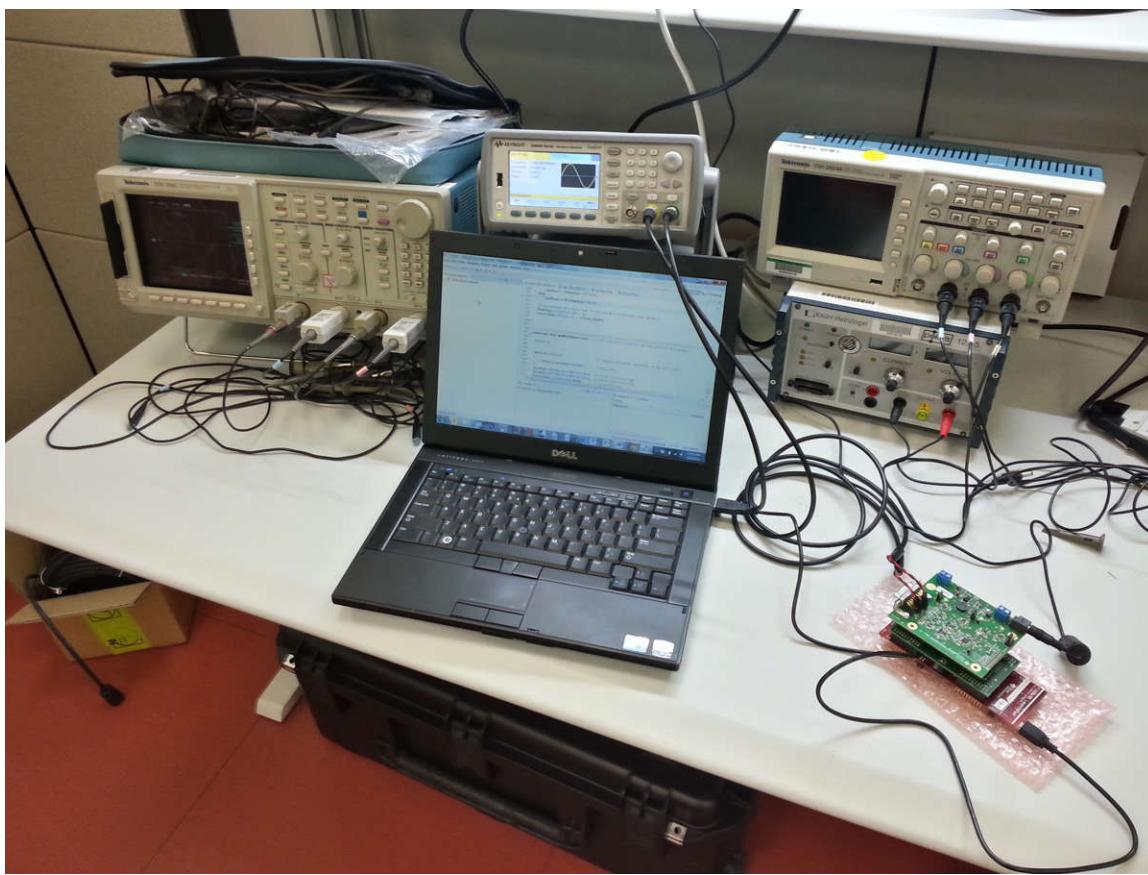

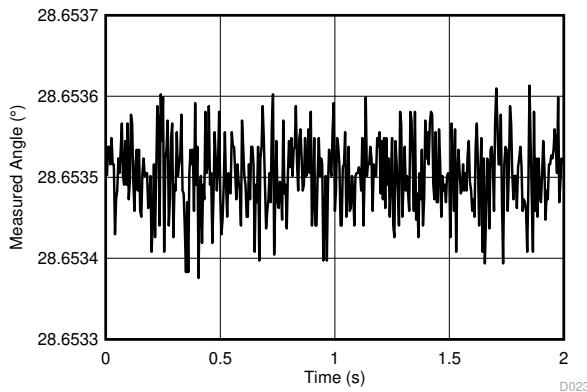

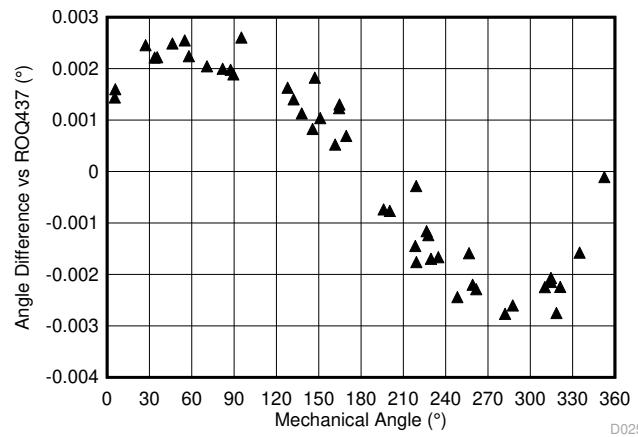

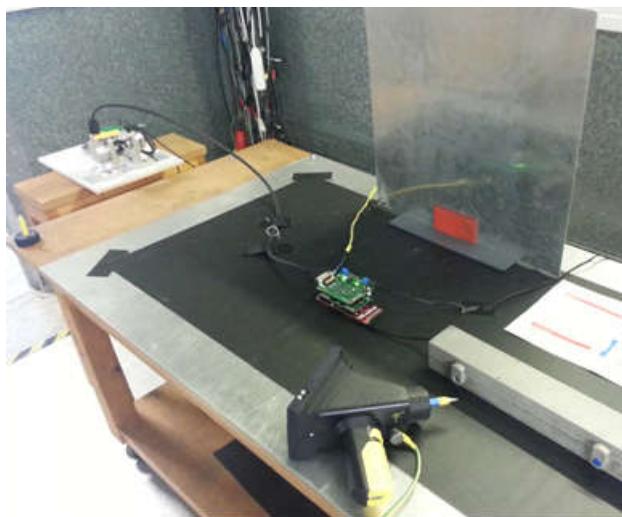

図 7-1 に、TIDA-00176 アナログシグナル チェーンのテスト画像を示します。

図 7-1. TIDA-00176 アナログシグナル チェーンの性能テストのテスト設定

完全差動アンプ THS4531A とデュアル 16 ビット ADC ADS8353 を採用した高分解能の 16 ビット信号路と、差動からシングルエンドへのアナログ信号路がテスト済みです。目的のため、デュアル出力のプログラマブル ファンクションジェネレータを使用しています。入力信号をコネクタ J8 (差動入力 A, B, R) に印加します。出力波形は、分析された信号路に応じて、さまざまなプローブ ポイントで収集されています。

### 7.1.1 高分解能信号路

測定は、高精度、高分解能の信号路で実施されました。1V<sub>PP</sub> の正弦波信号をエンコーダ コネクタ J8 入力 A+、A-、B+、B- に注入し、差動アナログ信号を ADS8354 の差動入力で測定しました。図 7-2 に、テスト用に測定された入力信号と出力信号の概要を示します。

図 7-2. 高分解能シグナル チェーン測定ポイント

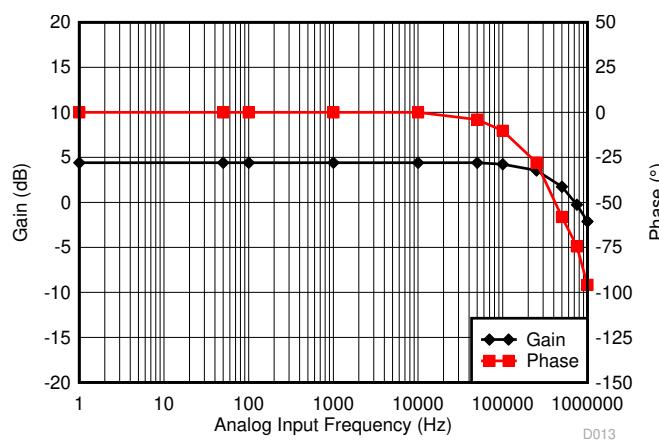

#### 7.1.1.1 エンコーダ コネクタから ADS8354 入力までのアナログパスのボード線図

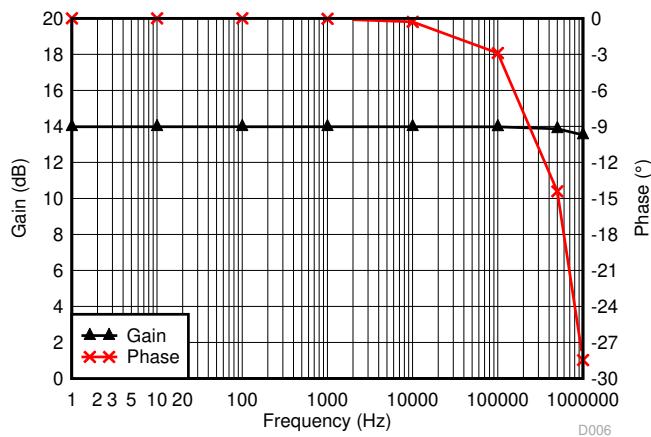

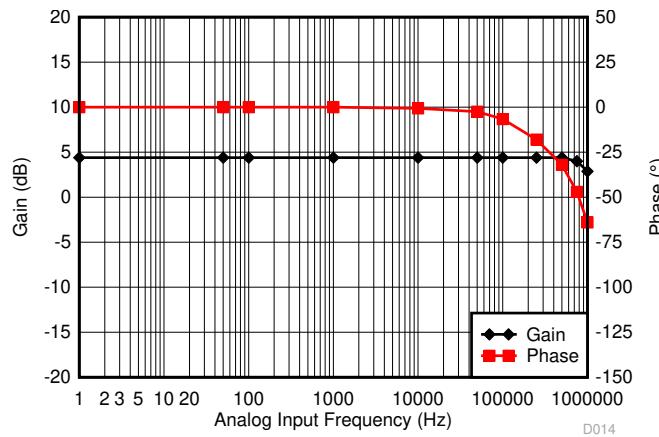

図 7-3 に、振幅と位相応答を示します。この値は主に THS4531A のゲイン設定 2、パッシブ 1 次ローパス フィルタにより定義されます。このフィルタは、2 つの 10Ω 直列抵抗と 2.2nF の並列コンデンサで構成されます。

図 7-3. エンコーダ差動入力から ADS8354 差動入力までの高分解能アナログのボード線図

### 7.1.1.2 高分解能信号路全体の性能プロット (DFT)

以下のテストでは、差動アンプの THS4531A を RC フィルタ経由でデュアル 16 ビット ADC ADS8354 に接続した高分解能シングナル チェーン全体でテストしました。エンコーダの差動入力ピンに正弦波テスト信号が注入され、16 ビットのデジタル データが解析されました。

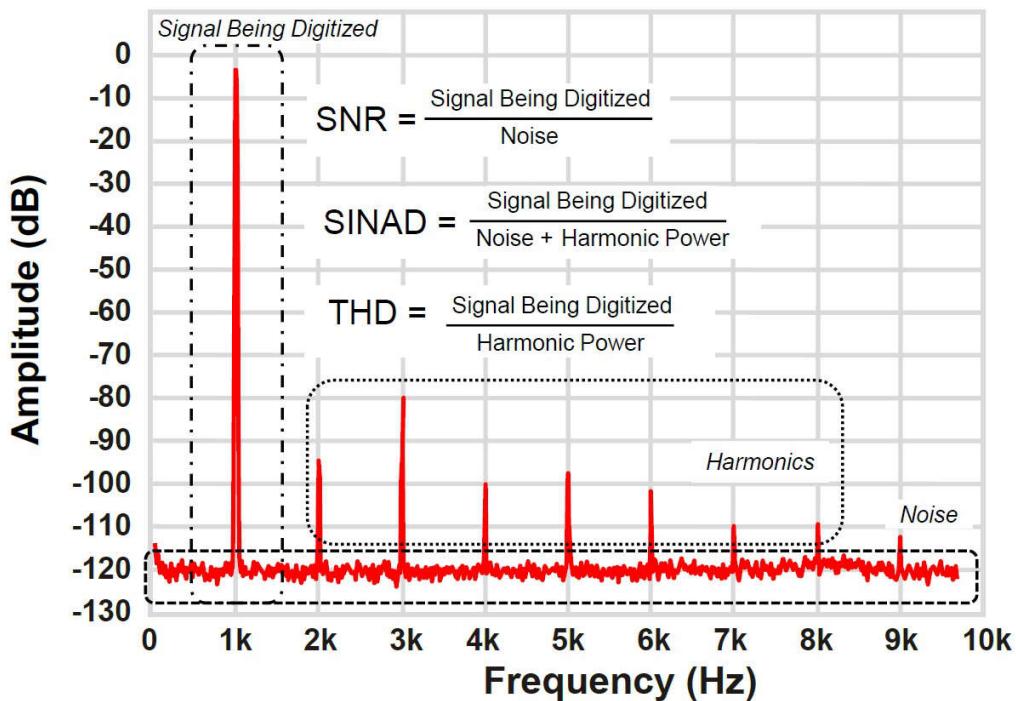

この分析は、信号対雑音比 (SNR)、全高調波歪み (THD)、信号対雑音歪み比 (SINAD)、有効ビット数 (ENOB) の性能を評価するために周波数ドメインで実施しました。本質的に、これらすべてのパラメータは、高速フーリエ変換 (FFT) 解析に基づいて ADC のノイズおよび歪み性能を定量化する異なる方法です。このセクションの末尾には、ADC による信号対雑音比測定の理論について簡単な紹介があります。

テストでは、次の 2 種類の入力信号を使用しました：

- 1.8V の超低ノイズの DC ソース

- 振幅が 0.6V<sub>PP</sub> の 1kHz の正弦波。これは Sin/Cos エンコーダの低い出力を表しています

入力信号は、一度に入力チャネル A+、A-、B+、B- のいずれかに印加され、もう一方のチャネルは未接続です。目的は、2 つのチャネル A と B (またはサインとコサインそれぞれ) の間で超低クロストーク レベルを測定して強調することです。

DC 入力を使用して、最良のノイズ性能を確保します (入力 / ソースからノイズが発生しないため)。1kHz の正弦波を使用して、2 つの並列チャネルの有効ビット数を測定します。

チャネル A および B は、両方とも 32kHz でサンプリングされ、チャネル A および B について連続して 8192 個の 16 ビット サンプルが取得されました。収集されたデータのうち、SNR と THD を測定するため、DFT を計算しました。

結果は次の図に示します。

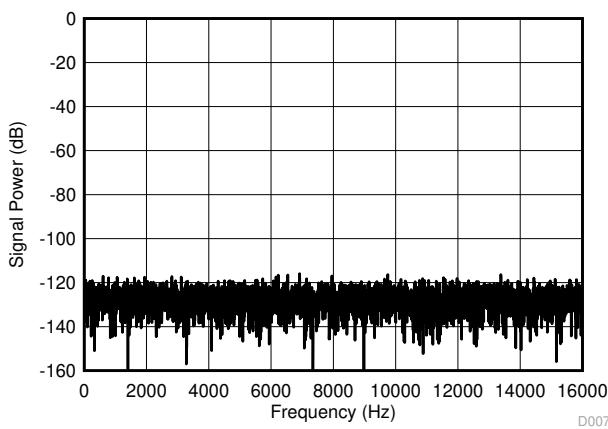

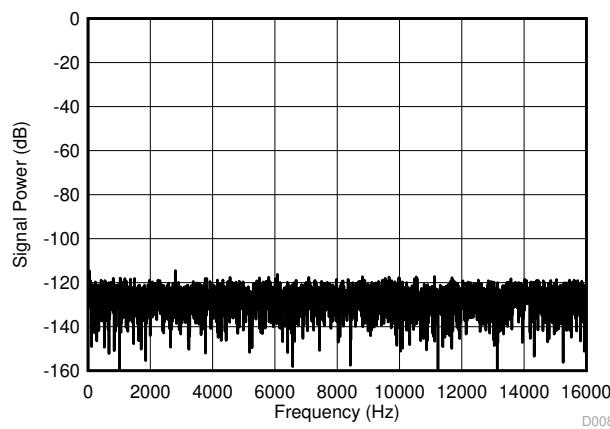

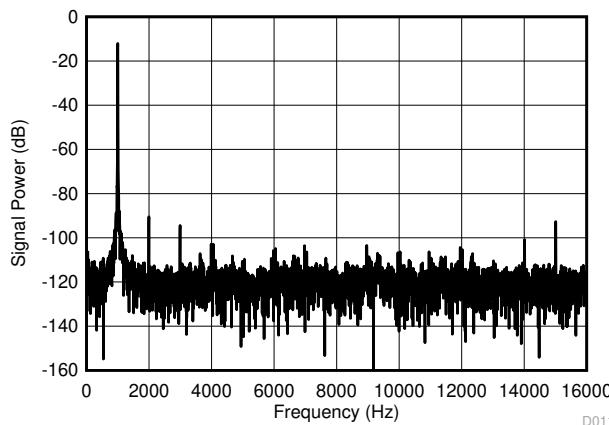

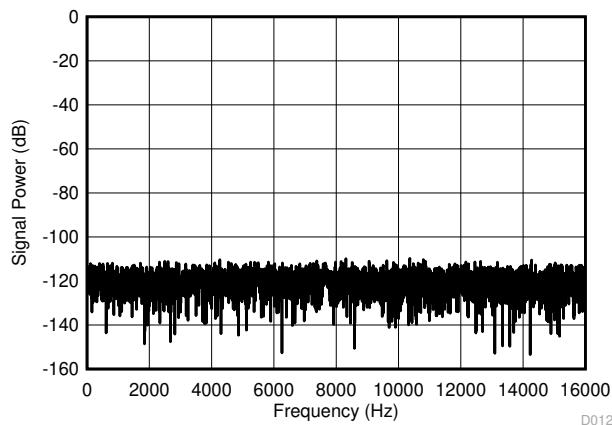

図 7-4. 入力 A で 1.8V DC を使用した 16 ビット チャネル A 出力の DFT

図 7-5. 入力 B で 1.8V DC を使用した 16 ビット チャネル B 出力の DFT

前の図で、測定されたノイズフロアは 120dB 未満であり、これは達成可能な最高の性能を示しています。また、プロットはフルスケール入力範囲、すなわち最大振幅を基準としています。0dB は ADS8354 で可能な最大入力に対応し、この構成では  $2V_{PP}$  となります。

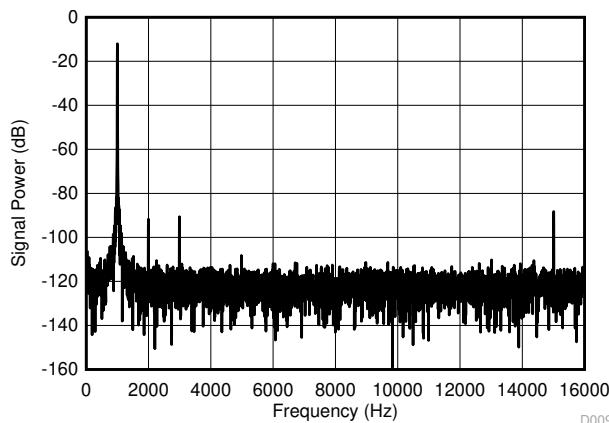

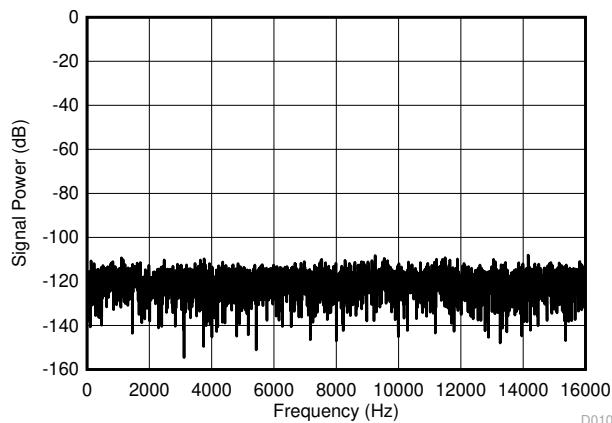

以下の図は、振幅  $0.6V_{PP}$ 、1kHz の正弦波入力電圧での高分解能チャネル全体の DFT を示しています。これは、約  $-6$ dB の入力レベルと、理論上のフルスケール レンジの入力との関係に相当します。

入力信号をチャネル A またはチャネル B のいずれかに印加しました。もう 1 つのチャネルは、クロストークを測定するためにオーブンのままにしました。

図 7-6.  $600mV_{PP}$ 、1kHz の正弦波入力を入力 A に印加した場合の 16 ビットチャネル A 出力の DFT

図 7-7.  $600mV_{PP}$ 、1kHz の正弦波入力を入力 A に印加した場合の 16 ビットチャネル B 出力の DFT

図 7-8.  $600mV_{PP}$ 、1kHz の正弦波入力を入力 B に印加した場合の 16 ビットチャネル B 出力の DFT

図 7-9.  $600mV_{PP}$ 、1kHz の正弦波入力を入力 B に印加した場合の 16 ビットチャネル A 出力の DFT

これらの値は、理論上のフルスケール入力範囲を参照しています。1kHz の正弦波信号の 1 次高調波と 2 次高調波は、信号源自体によるものであることに注意してください（通常、テスト信号の周波数を分離するために、非常に強力なノッチフィルタを使用します。例として [SLAU515](#) も参照してください）。

また、1kHz 信号の周波数がわずかに変化していることにも注意してください。これは TIDA-00176 ハードウェアによるものではなく、F28069 ソフトウェア実装のジッタによるもので、ADS8354 の変換（ホールドモード）を開始する SPI 転送のトリガは、12.5ns に相当する CPU の 1 クロック サイクルのジッタで発生します。

前の写真では、サイン（信号 A+、A-）とコサイン（B+、B-）の 2 つのアナログ チャネル間にクロストークが基本的に存在しないことも強調しました。スペクトル（DFT）はサンプリング周波数の半分です（スペクトルの後半は前半の鏡面コピーなので、プロットには表示されません）。Hann 関数（[http://en.wikipedia.org/wiki/Hann\\_function](http://en.wikipedia.org/wiki/Hann_function)）は、データをウインドウ化して、周波数ドメインのよりクリーンなプロットを取得する目的で使用します。

この設計について、THD、SNR、ENOB とフルスケール信号との関係を計算できます。これらを [表 7-2](#) に示します。

**表 7-2. 高分解能信号路 (THS4531A と ADS8354) の代表的性能**

| パラメータ  | 値 (測定値)       |

|--------|---------------|

| SNR    | 89.1 dB       |

| SINAD  | 88.5 dB       |

| ENOB   | 14.4 ビット      |

| クロストーク | -107 ~ -109dB |

### 7.1.1.3 ADC を使用した AC 性能の定義に関する背景

ADC の代表的な FFT プロットを [図 7-10](#) に示します。

図 7-10. 性能の定義

信号対雑音比は、システムの合計ノイズへの詳しい情報を提供します。データ アクイジョン システムの合計ノイズは、フロントエンド アンプのノイズと ADC ノイズの  $\sqrt{\text{rss}}$  です。ADC ノイズには、量子化ノイズと、ADC 内部回路が寄与するノイズが含まれます。これらすべてのソースからの合計ノイズの寄与 ( $V_{n\_TOT\_RMS}$  と呼ばれます) は、システムの合計信号対雑音比を計算するために、ADC の入力を基準にします。

$$\text{SNR} = \frac{V_{\text{SIGNAL\_RMS}}}{V_{\text{NOISE\_RMS}}} \quad (16)$$

THD は、すべての高調波成分 (一般に 9 つの高調波を使用) の  $\text{rss}$  と、基本信号周波数の出力との比として定義されます。一般にフルスケール (FS) 付近の入力信号で規定されますが、この設計ではクリッピングを防止するため、入力を FS より  $0.5\text{dB}$  低く維持します。

入力信号の実効値 (rms) を  $V_{\text{SIGNAL\_RMS}}$  と表し、(基本波を除く) 最初の 9 つの高調波の合計電力を  $V_{\text{HARMONICS\_RMS}}$  と表すと、THD は次のように計算できます：

$$\text{THD} = \frac{V_{\text{SIGNAL\_RMS}}}{V_{\text{HARMONICS\_RMS}}} \quad (17)$$

SINAD は歪みとノイズの影響を組み合わせて、システム全体の動的性能の累積測定値を提供します。

$$\text{SINAD} = \frac{V_{\text{SIGNAL\_RMS}}}{\sqrt{V_{\text{NOISE\_RMS}}^2 + V_{\text{HARMONICS\_RMS}}^2}} \quad (18)$$

最後に重要な点ですが、ENOB はノイズフロアを上回るビット数を指定するため、ADC からデジタル化された信号の品質を測定する指標として効果的です。(dB で表される SINAD から) 次のように計算されます:

$$ENOB = \frac{SINAD_{dB} - 1.76 \text{ dB}}{6.02 \text{ dB}} \quad (19)$$

パラメータの計算方法の詳細については、[SLAU515](#) を参照してください。

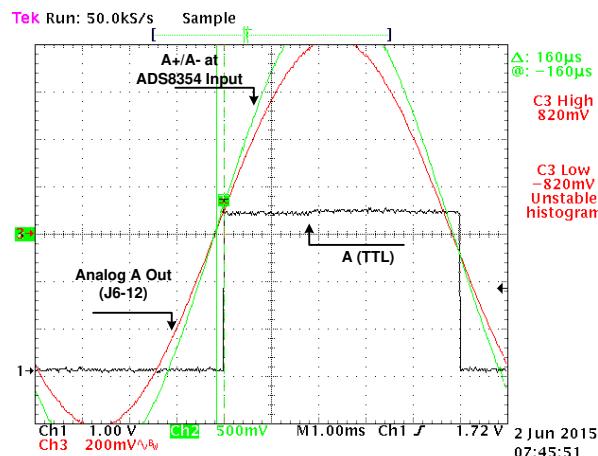

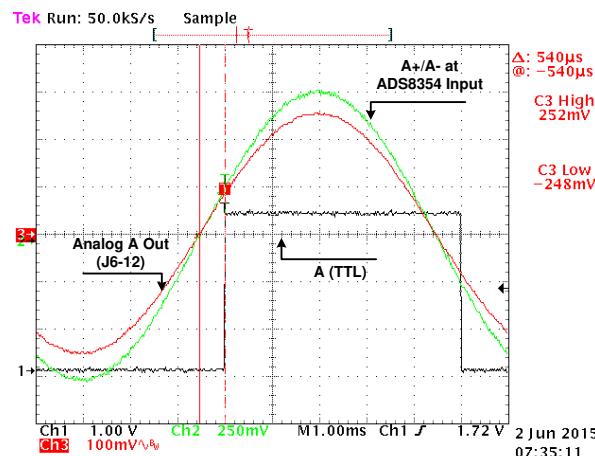

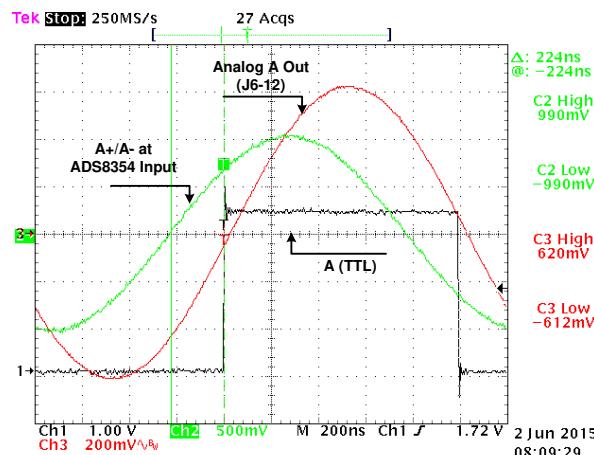

### 7.1.2 差動からシングルエンドへのアナログ信号路

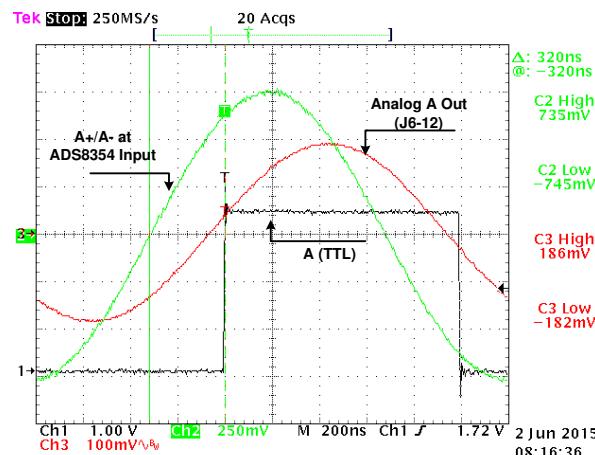

デュアル チャネル信号発生器を使用して、2 つの結合されたサイン波 (同じ振幅、同じ周波数で、それらの間で位相シフトは 90 度) が生成され、J9 コネクタを使用してアナログ差動信号 A+、A-、B+、B- に印加されます。2 つの差動プローブを使用して、入力に印加されている差動信号を取得し、2 つのシングルエンド プローブを、コネクタ J6 のピン 18 とピン 20 にそれぞれあるアナログパスのシングルエンド アナログ出力 A および B に接続しています。

入力に対する出力の振幅はこのように測定され、同時に差動入力とそれぞれのシングルエンド出力との間の位相シフトが測定されます。これにより、アナログ シグナル コンディショニング パスのボード線図を計算できます。

図 7-11. 差動からシングルエンドへのアナログ信号路の伝達関数 — チャネル A および B