Design Guide: TIDA-010234

## 8 ポート IO-Link マスタのリファレンス・デザイン

## 概要

このデザインは、高速で確定的なタイミングを実現する 8 ポート IO-Link マスタを実装します。各ポートは個別のビット・レートとサイクル・タイミングで動作できます。このデザインを使用して、OPC UA、Profinet、EtherCAT、Ethernet IP への接続用リモート IO ゲートウェイを構築できます。PRU ベースのフレーム・ハンドラにより、タイミングと同期を柔軟に調整できます。

## リソース

TIDA-010234

デザイン・フォルダ

LP-AM243

ツール・フォルダ

BOOSTXL-IOLINKM-8

ツール・フォルダ

AM243

プロダクト・フォルダ

TIOL112

プロダクト・フォルダ

TPS274160

プロダクト・フォルダ

テキサス・インスツルメンツの TI E2E™ サ ポート・エキスパートにお問い合わせくださ

## 特長

- 8 つの IO-Link ポート

- IO-Link 転送レート COM1、COM2、COM3 をサポート

- 400µs のサイクル・タイムをサポート

- ポートごとに 500mA の電流

- すべてのポートに過電流保護および制限機能を搭載

- PRU フレーム・ハンドラにより柔軟なタイミングが可能

## アプリケーション

- スタンドアロンのリモート IO

- 通信モジュール

## 1システムの説明

センサとアクチュエータはオートメーションの最も基本的なユニットであり、ネットワーク接続された複数のシステムに情報を供給し、それらのシステムからの命令に従って動作します。従来、センサやアクチュエータのようなデバイスは、インテリジェンスがごく限定的なインターフェイスを経由して制御ユニットに接続していました。その結果、交換できる構成情報や診断情報はごくわずか、または皆無でした。新しいデバイスを取り付けるには、使用する時点で手動の構成が必要だったほか、診断機能がないので、本当に必要なときに予知保全を実施することも不可能でした。

IO-Link (国際電気標準会議 [IEC] 61131-9) は、オープン規格をベースとするプロトコルであり、センサやアクチュエータのような小型デバイスに関するインテリジェント制御のニーズに対処します。この標準は、デバイスとマスタの間で、低速のポイント・ツー・ポイント・シリアル通信を実現します。この場合のマスタは通常、フィールド・バスや PLC に到達するためのゲートウェイとして機能します。接続の確立後にこのインテリジェント・リンクを使用すると、データ交換、構成、診断を目的とする通信を容易に実施できます。

シールドなしの 3 線ケーブルは最大 20m の長さに対応し、一般的に M12 コネクタを両側に取り付けて、IO-Link 接続を確立します。データ・レートの範囲は最大 230kbps に達し、非同期の最小サイクル時間は 400µs +10% です。4 つの動作モードは、双方向の入出力 (I/O)、デジタル入力、デジタル出力、非アクティブ化に対応しています。セキュリティ・メカニズムとディタミニスティック (確定的) なデータ配信は規定されていません。IODD (IO Device Description、IO デバイス記述) というプロファイルは、通信プロパティ、デバイス・パラメータ、ID (識別子) とプロセスと診断に関するデータ、デバイスとメーカーに関する固有の情報を保持しています。

IO-Link システムを配備する多くの利点として、標準化済みの配線、データ可用性の向上、リモートの監視と構成、複数のデバイスのシンプルな置き換え、先進的な診断機能を挙げることができます。IO-Link を採用すると、ファクトリのマネージャは、センサからの更新情報を受け取り、今後の保守や交換に関する計画を立てることができます。交換を必要としているセンシング・ユニットまたはアクチュエータ・ユニットの交換と、PLC から IO-Link マスタ経由での新しいユニットの構成を実施すると、手動のセットアップが不要になり、ダウンタイムを短縮できます。ファクトリの現場へ足を運ばずに、ある構成から他の構成へと製造をリモートで切り替えることができるので、製品のカスタマイズがいっそう容易になります。IO-Link は既存の標準的な I/O 設備と配線に対する上位互換性があるので、ファクトリは製造ラインを IO-Link に簡単にアップグレードすることができます。総合すると、これらの特長を活用して全体のコストを削減し、プロセスの効率と機械の可用性を向上させることができます。

## 2システム概要

#### 2.1 ブロック図

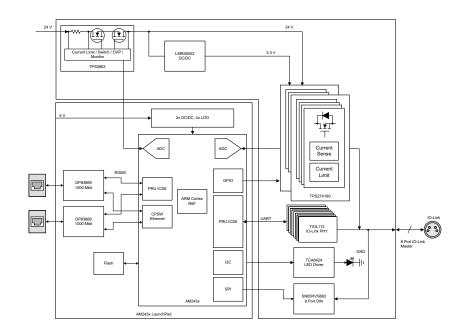

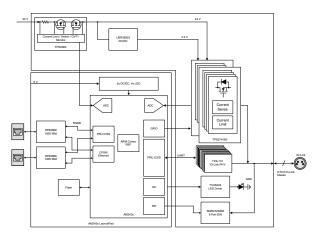

図 2-1 に示すように、このデザインは2つの主要ブロックで構成されています。

1 つ目のブロックは AM243x LaunchPad<sup>™</sup> で、プロセッサ、2 つのイーサネット・ポート、および必要な電源回路とフラッシュ・メモリが含まれています。

2 つ目のブロックは IO-Link BoosterPack です。IO-Link ポートを構築するためのすべてのアナログ回路をここに示します。ここに示す主な部品は、各ポートと IO-Link トランシーバの電源です。

この電源は、4 ポートのハイサイド・スイッチ TPS274160 を使用して構築されており、スイッチング電源だけでなく、構成可能な電流制限と電流監視機能も搭載しています。短絡、デバイスの欠陥、配線の問題が原因で出力が過負荷になった場合に、システムを動作させたまま問題の原因を特定するのに役立ちます。システムの電源入力は、TPS2663 eFuse を使用して過電圧および逆極性から保護されています。また、合計消費電流を観察するための電流監視出力も備えています。

8 つの IO-Link ポートのそれぞれが、TIOL112 をトランシーバとして使用しています。このデバイスは物理層を実装しており、IO-Link マスタ・インターフェイスに必要なときに CQ ラインに電流シンクを内蔵しています。また、ウェークアップ・パルス時に十分な電流を供給するために約 700mA の電流制限を提供し、同時に障害発生時にケーブルや電源が過負荷にならないように電流を制限します。通信中のオーバーシュートを最小限に抑え、放射を低減するため、CQ ラインのスルーレートは制限されます。

ポートのステータスを示すために、シリアル・インターフェイス TCA6424 を搭載したシンプルな LED ドライバがボードに追加されています。 SN65HVS883 には 8 つのデジタル入力が実装されており、各 IO-Link ポートに 1 つずつ搭載されています。

図 2-1. TIDA-010234 のブロック図

#### 2.2 設計上の考慮事項

このリファレンス・デザインは、TIOL112 PHY と、IO-Link マスタの包括的な設計を構築するために必要な周辺部品を使用して、IO-Link マスタを実装します。したがって、物理的な面では、TIOL112 デバイスに加えて、ポートの電源のみを追加する必要があります。

必要な電流シンクはすでに TIOL112 に内蔵されており、5kΩ 未満の電流制限設定抵抗を使用すると自動的にアクティブになります。このモードでは、デバイスはウェークアップ・パルスを直接駆動できます。このモードでは、電流制限が約700mA に設定されているため、ウェークアップを駆動するのに十分な電流を供給できますが、安全なレベルに制限されているため、損傷を受けることはありません。

一方、3 つの通信速度すべてをサポートするハードウェアとフレーム・ハンドラを用意する必要があります。 ここで PHY として使用される TIOL112 デバイスは、すべての速度 (COM1、COM2、COM3) を処理できます。 8 ポートのフレーム・ハンドラは、AM243x のプログラマブル・リアルタイム・ユニット (PRU) に実装されています。

8 ポートの IO-Link 対応マスタ・ゲートウェイを実現するには、8 つの TIOL112 デバイスが必要です。1 つの TPS2724160 が 4 個の IO-Link ポートをサポートしています。その結果、8 つの TIOL112 デバイス (IO-Link PHY)、2 つの TPS2724160 デバイス (ハイサイド・スイッチ)、1 つの TCA6424 デバイス (LED ドライバ)のみが実現します。

#### 2.2.1 フレーム・ハンドラ

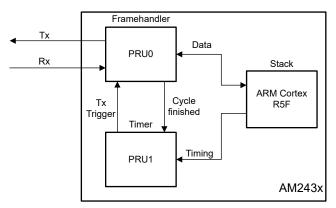

図 2-2 の関係において、さまざまなコアがどのように連携して動作するかを示します。 完全なフレーム処理は、サイクル時間の生成を含む 1 つの産業用通信サブシステム (ICSS) を使用して実行されます。 スタック自体は、単一の Arm® コアに実装されています。

PRU0 はフレーム・ハンドラを実装しており、8 個のポートすべてでフレームの送受信を行います。内部ステート・マシンが完了すると、割り込みが2番目のPRUコアに送信されます。

この割り込みは、サイクル・タイミングの生成に使用されます。PRU1 にはカウント・レジスタがあり、各ポートには比較レジスタと、いくつかのステータスおよび制御ビットがあります。ここでサイクル時間が設定され、次のフレームを送信するタイミングになるとすぐに、トリガが PRU0 に送信されてフレームが送信されます。

Arm コアは両方の PRU を制御します。スタートアップ中はサイクル・タイマはまだ使用されておらず、フレームは PRU0 経由で手動で送信され、Arm コアから Tx がトリガされます。動作モードへの切り替えとプロセス・データの交換が開始されると、PRU1 は適切なサイクル時間に構成され、データ送信のトリガを制御するために引き継ぎます。この場合、各フレームが送信され、デバイスからの応答が受信されるかタイムアウトが発生した後、Arm コアは割り込みを受け取ります。

この方式では、サイクル時間は Arm コアの CPU 負荷とは無関係です。また、そこでタイミングを生成する必要がないため、負荷が減少します。

図 2-2. Sitara PRU - Arm® の関係

## 3 ハードウェア、ソフトウェア、テスト要件、テスト結果

#### 3.1 ハードウェア要件

#### 3.2 テスト構成

さまざまな物理パラメータをテストするために、IO-Link ボード BOOSTXL-IOLINKM-8 を AM243x LaunchPad なしで 24V 電源に接続します。 各テストに必要な信号について、以降のセクションで説明します。

#### 3.3 テスト結果

このセクションで注目するのは、『IO-Link インターフェイスとシステム仕様書』で IO-Link コミュニティが説明している物理 層テストです。

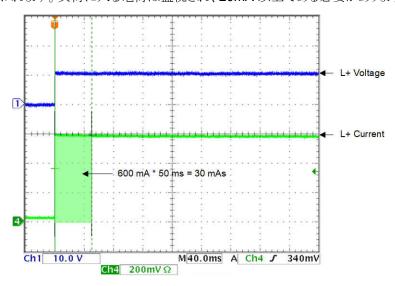

## 3.3.1 電源突入テスト (TCM\_PHYL\_INTF\_ISIRM)

このテスト・ケースでは、L+ ラインの突入時のマスタの動作をテストします。1000mA 以上の負荷を接続し、突入時の充電を観測する必要があります。このテストでは抵抗性負荷を使用し、L+ と L- の電流と電圧を観測します。これは、PSM = 20V、PSM = 30V で行われます。負荷に入る電荷は監視され、20mA 以上である必要があります。

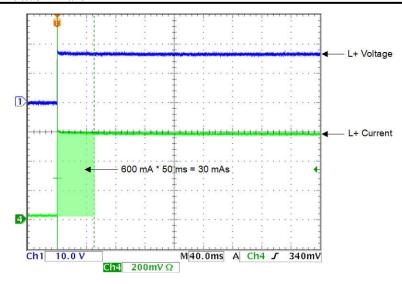

図 3-1. 20V の TCM\_PHYL\_INTF\_ISIRM

図 3-1 に、20V の電源電圧と約  $18\Omega$  の負荷での動作を示します。 TPS274160 ハイサイド・スイッチにより電流は 600mA に制限されます。 したがって、出力電圧は 10V に制限されます。 最初の 50ms では、マスタにより 30mA の電荷が供給されます。

図 3-2.30VのTCM\_PHYL\_INTF\_ISIRM

図 3-2 に、30V の電源電圧で同じテストを示します。したがって、 $28\Omega$  の抵抗性負荷を使用します。電流は引き続き 600mA に制限されており、電圧は約 16V に達します。重要なのは、最初の 50ms の電荷も 30mA であり、規格の要件を満たしていることです。

## 3.3.2 インターフェイス・ウェークアップ電圧 (TCM\_PHYL\_INTF\_IQWUF および TCM\_PHYL\_INTF\_IQWUHL)

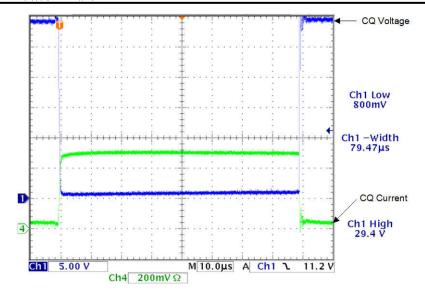

次のテストでは、ウェークアップ・パルスの生成中の IO-Link CQ ライン・ドライバ段の動作を検証します。 CQ 出力に抵抗性負荷がかけられ 500mA の電流が発生し、電圧レベルが観測されます。 最初の 2 つのテストは、ハイサイド・ドライバを検証します。

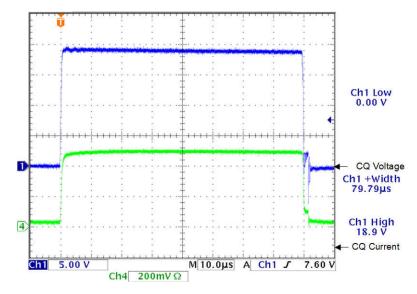

図 3-3. 20V の TCM\_PHYL\_INTF\_IQWUH

図 3-3 に初回のテストを示します。ここでは、電源電圧を 20V に設定し、ラインに 40Ω の負荷をかけて 500mA の電流 を発生させます。電圧レベルが、13V の VTHHHmax を超えている場合に観測されます。スコープ・プロットは 18.9V の 測定値を示しているため、このテストに合格しています。

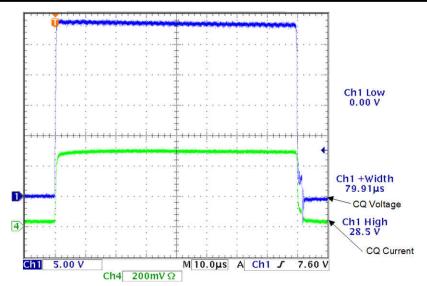

図 3-4.30 Vの TCM\_PHYL\_INTF\_IQWUH

30V の電源電圧で同様の測定を行う必要があります。 図 3-4 のスコープ・プロットは、これを示しています。この場合、抵抗性負荷を 60Ω に変更する必要があるため、結果として得られる電流は引き続き 500mA になります。 28.5V の電圧を測定したので、このテストにも合格しました。

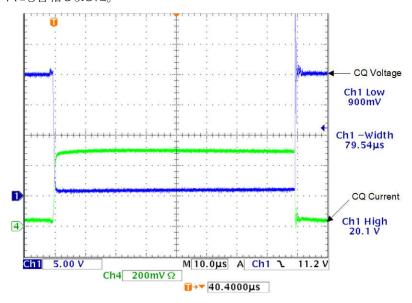

図 3-5. 20V の TCM\_PHYL\_INTF\_IQWUL

ローサイド・ドライバに対しても同じテストを実施します。図 3-5 に、電源電圧 20V での最初のテストを示します。この場合も、抵抗性負荷を使用してラインに負荷をかける必要があり、その結果、500mA になります。この場合、負荷は L+ に接続されます。図に示すように、0.9V の電圧が測定されます。これでこのテストは合格です。

図 3-6. 30V の TCM\_PHYL\_INTF\_IQWUL

最後の物理層テストは類似していますが、30V で、負荷抵抗も同様に高くなっています。 図 3-6 の結果は、再び 0.9V の電圧を示しています。これも合格です。

表 3-1 に、すべての物理層テストの概要と結果を示します。

表 3-1. IO-Link® 物理層テスト

| ID               | 名称                            | 構成                                                   | 仕様 (条項)                                                                                 | コメント       | 結果                                                                                                                                                                                                                                                                                                                                      |

|------------------|-------------------------------|------------------------------------------------------|-----------------------------------------------------------------------------------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SDCI_TC_0<br>001 | TCM_PHYL_INTF_IS<br>M         | マスタ・ポートの供給電流が<br>監視されます。                             |                                                                                         | 500mA でテスト | 20V:合格<br>30V:合格                                                                                                                                                                                                                                                                                                                        |

| SDCI_TC_0<br>002 | TCM_PHYL_INTF_ISI<br>RM       | マスタ・ポートの供給電流が<br>監視されます。                             |                                                                                         | 500mA でテスト | 20V:合格<br>30V:合格                                                                                                                                                                                                                                                                                                                        |

| SDCI_TC_0        | TCM_PHYL_INTF_IL<br>LM        | マスタ・ポートの <b>C/Q</b> での入<br>力電流が監視されます。               | 『IO-Link インターフェイスおよびシステム仕様書<br>V1.1.3』 4 のセクション 5.3.2.3、表 6 を参照して<br>ください               |            | ILLM (VIM = 5V、VSM = 20V):8.56mA 合格 ILLM (VIM = 5.1V、VSM = 20V):8.56mA 合格 ILLM (VIM = 15V、VSM = 20V):8.57mA 合格 ILLM (VIM = VSM = 20V):8.57mA 合格 ILLM (VIM = 5V、VSM = 30V):8.57mA 合格 ILLM (VIM = 5V、VSM = 30V):8.57mA 合格 ILLM (VIM = 5.1V、VSM = 30V):8.57mA 合格 ILLM (VIM = 15V、VSM = 30V):8.58mA 合格 ILLM (VIM = 15V、VSM = 30V):8.58mA 合格 |

| SDCI_TC_0<br>004 | TCM_PHYL_INTF_V<br>REShigh    | マスタ <b>C/Q</b> 出力の出力レベ<br>ルを測定します。                   |                                                                                         |            | VRQHM (VSM = 20V): 0.23V<br>VRQHM (VSM = 30V): 0.228V<br>合格                                                                                                                                                                                                                                                                             |

| SDCI_TC_0<br>005 | TCM_PHYL_INTF_V<br>RESLOW     | マスタ <b>C/Q</b> 出力の出力レベ<br>ルを測定します。                   |                                                                                         |            | VRQLM (VSM = 20V):0.225V<br>VRQLM (VSM = 30V):0.225V<br>合格                                                                                                                                                                                                                                                                              |

| SDCI_TC_0<br>006 | TCM_PHYL_INTF_V<br>THHM       | C/Q 入力のデジタル入力信<br>号が監視されます                           | 『IO-Link インターフェイスおよびシステム仕様書<br>V1.1.3』 4 のセクション 5.3.2.2、表 5 を参照して<br>ください               |            | VIM@VTHHM (VSM = 20V):11.1V<br>VIM@VTHHM (VSM = 30V):11.1V<br>合格                                                                                                                                                                                                                                                                        |

| SDCI_TC_0<br>007 | TCM_PHYL_INTF_V<br>THLM       | C/Q 入力のデジタル入力信<br>号が監視されます                           |                                                                                         |            | VIM@VTHLM (VSM = 20V): 10.35V<br>VIM@VTHLM (VSM = 30V): 10.35V<br>合格                                                                                                                                                                                                                                                                    |

| SDCI_TC_0<br>008 | TCM_PHYL_INTF_V<br>HYSM       | SDCI_TC_0006 と<br>SDCI_TC_0007 の値の比<br>較             |                                                                                         |            | VHYSM (VSM = 20V):0.75V<br>VHYSM (VSM = 30V):0.75V<br>合格                                                                                                                                                                                                                                                                                |

| SDCI_TC_0<br>299 | TCM_PHYL_INTF_V<br>OLTRANGECQ | CQ を 1Ω 経由で 0V および<br>30V に接続した後で動作す<br>るかどうかをテストします | 『IO-Link インターフェイスおよびシステム仕様書<br>V1.1.3』 4 のセクション 5.3.2.2、表 5 - VIL およ<br>び VIH を参照してください |            | 合格                                                                                                                                                                                                                                                                                                                                      |

## 表 3-1. IO-Link® 物理層テスト (continued)

| ID               | 名称                      | 構成 | 仕様 (条項)                                                                     | コメント                                 | 結果                                                             |

|------------------|-------------------------|----|-----------------------------------------------------------------------------|--------------------------------------|----------------------------------------------------------------|

| SDCI_TC_0<br>021 | TCM_PHYL_INTF_IQ<br>WUH |    | 『IO-Link インターフェイスおよびシステム仕様書<br>- V1.1.3』 4 のセクション 5.3.3.3、表 9 を参照して<br>ください | ファンクション・ジェネレータ<br>からのウェークアップ・パル<br>ス | VIM@WURQ (VSM = 20V):18.9V<br>VIM@WURQ (VSM = 30V):28.5V<br>合格 |

| SDCI_TC_0<br>022 | TCM_PHYL_INTF_T<br>WUH  |    |                                                                             | ファンクション・ジェネレータ<br>からのウェークアップ・パル<br>ス | TWUH@WURQ (VSM = 20V):80µs<br>TWUH@WURQ (VSM = 30V):80µs<br>合格 |

| SDCI_TC_0<br>023 | TCM_PHYL_INTF_IQ<br>WUL |    |                                                                             | ファンクション・ジェネレータ<br>からのウェークアップ・パル<br>ス | VIM@WURQ (VSM = 20V): 0.9V<br>VIM@WURQ (VSM = 30V): 0.9V<br>合格 |

| SDCI_TC_0<br>024 | TCM_PHYL_INTF_T<br>WUL  |    |                                                                             | ファンクション・ジェネレータ<br>からのウェークアップ・パル<br>ス | TWUL@WURQ (VSM = 20V):80µs<br>TWUL@WURQ (VSM = 30V):80µs<br>合格 |

## 3.3.3 電流シンク

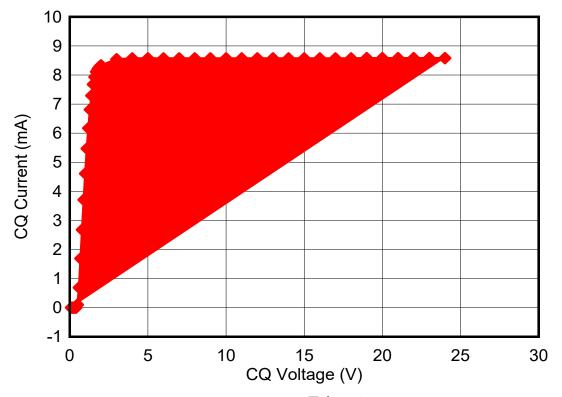

IO-Link 物理層テスト以外に、内蔵電流シンクもテスト済みです。図 3-7 に、RX と電流シンクのみがアクティブなときのCQ ラインへの電流を示します。電流が約 8.5mA の場合、5~15mA の許容範囲内であることが適切です。

図 3-7. TIOL112 の電流シンク

## 3.3.4 タイミング・テスト

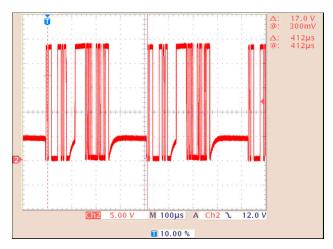

タイミング、特に 400μs のサイクル時間の能力とこの通信中のタイミング・ジッタに関して、さらにテストを実施しました。このテストでは、BOOSTXL-IOLINKM-8 を AM243x LaunchPad と組み合わせ、MCU+ SDK のサンプルをコンパイルおよびロードします。 持続性が無限の 図 3-8 は、約 412μs のサイクル時間を示し、この構成では目に見えないジッタは発生しません。

図 3-8. CQ ライン通信

図 3-9 に、標準で許容される範囲内で約 417µs のタイミングを示します。接続されているデバイスの応答時間もここで確認できます。

図 3-9. マスタ・サイクル・タイミング

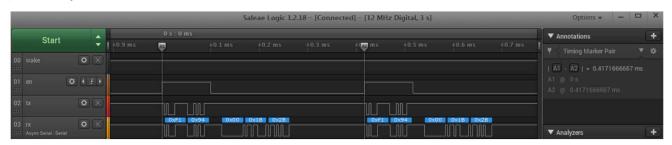

図 3-10 に、CQ ラインの 2 番目の通信サイクルを拡大した図を示します。トリガは 1 サイクルでトリガされ、次のサイクルまで遅延するように設定されます。これにより、サイクル間のジッタを確認できます。無限の持続性により、約 50ns のジッタが目に見えます。立ち上がり時間と立ち下がり時間、およびサイクル・タイミングと比較すると、これは無視できるものであり、システム性能を低下させることはありません。

図 3-10. マスタ・サイクル・ジッタ

## 4 設計とドキュメントのサポート

#### 4.1 設計ファイル

#### 4.1.1 回路図

回路図をダウンロードするには、TIDA-010234 のデザイン・ファイルを参照してください。

#### 4.1.2 BOM

部品表 (BOM) をダウンロードするには、TIDA-010234 のデザイン・ファイルを参照してください。

## 4.2 ツールとソフトウェア

#### ツール

8 ポート IO-Link マスタのリファレンス・デザイン

AM243x Arm ベース・マイコン向け、汎用 LaunchPad 開発キット

IO-Link マスタ・ブースタ・パック

#### ソフトウェア

AM243x Sitara™ マイコン向けソフトウェア開発キット (SDK)

#### 4.3 ドキュメントのサポート

- 1. テキサス・インスツルメンツ、『IO-Link マスタ・デモ』

- 2. テキサス・インスツルメンツ、『TIOL112 および TIOL112x IO-Link デバイス・トランシーバ、低残留電圧、および小型パッケージのサージ保護機能内蔵』データシート

- 3. テキサス・インスツルメンツ、『AM243x Sitara™ マイクロコントローラ』データシート

- 4. 『IO-Link インターフェイスおよびシステム仕様書 V1.1.3』

- 5. 『IO-Link テスト仕様書 V1.1.3』

#### 4.4 サポート・リソース

TI E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、該当する貢献者により、現状のまま提供されるものです。これらは TI の仕様を構成するものではなく、必ずしも TI の見解を反映したものではありません。TI の使用条件を参照してください。

## 4.5 商標

TI E2E<sup>™</sup>, LaunchPad<sup>™</sup>, and Sitara<sup>™</sup> are trademarks of Texas Instruments.

Arm® is a registered trademark of Arm Limited.

IO-Link® is a registered trademark of Profibus User Organization.

すべての商標は、それぞれの所有者に帰属します。

#### 5 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

# Changes from Revision \* (September 2022) to Revision A (April 2023)Page・「リソース」セクションの多数の URL を修正。1・「回路図」および「BOM」セクションの URL を修正。12

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス・デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、TI の販売条件、または ti.com やかかる TI 製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、TIはそれらに異議を唱え、拒否します。

郵送先住所:Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023, Texas Instruments Incorporated