## Design Guide: TIDEP-01022

# Jacinto DRA821 プロセッサをベースにした車載および IoT ゲートウェイリファレンス デザイン

## 説明

このリファレンス デザインは、ドメイン、集中型、ゾーン ゲートウェイアーキテクチャを含む新興アーキテクチャの車載ゲートウェイ向けに最適化されたシステム設計であり、Jacinto™ DRA821 プロセッサ ファミリをベースとしています。DRA821 プロセッサは、クラウド接続を使用するゲートウェイシステム向けにカスタマイズされています。

8 層 PCB 設計として構築されており、最適化された電源アーキテクチャと、イーサネット スイッチ、CAN-FD、PCIe などのさまざまな接続オプションを備え、広範な車載用および産業用アプリケーションに対応しています。

## リソース

[TIDEP-01022](#)

[DRA821](#)

[DP83TG720S-Q1, TCAN1046-Q1](#)

[TLIN1022-Q1, TPS6594-Q1](#)

[LM5141, TPS22965](#)

[TPS61088, TPS62810-Q1](#)

デザイン フォルダ

プロダクト フォルダ

プロダクト フォルダ

プロダクト フォルダ

プロダクト フォルダ

プロダクト フォルダ

## 特長

- 車載用コネクタ付き統合型イーサネット スイッチおよび外部イーサネット スイッチ

- ウェークアップ機能搭載、マルチ CAN/LIN アレイ

- PCIe コネクタ

- TPS6594x ソリューションを活用して最適化済みのパワー マネージメント

- 早期 CAN 応答と高速なシステム起動

- スタンバイ IO ドメインのサポート

- 2666 MT/s (1 秒あたり 3,200M 回の転送が可能) の LPDDR4

- OPSI および eMMC フラッシュ メモリのサポート

- ゲートウェイ アプリケーション スタック (AutoSAR)

## アプリケーション

- 車載用ゲートウェイ

- ADAS ドメイン コントローラ

テキサス・インスツルメンツの™ E2E サポート エキスパートにお問い合わせください。

## 1 システムの説明

車載アーキテクチャは、データ量を増加させ続ける将来の需要に対応するために進化しています。新しい車両アーキテクチャには、集中型、ドメイン、ゾーンの3種類のゲートウェイがあります。集中型ゲートウェイは、パワートレイン、シャーシ、ボディ、ADASなどを含む自動車の多数のドメイン間で、安全かつセキュアにデータを移動します。ドメインコントローラは、機能ドメインにECUを集約し、1つの機能ドメイン内に位置する残りの相互間、およびECUと集中型ゲートウェイの間で、安全かつセキュアにデータを移動します。ゾーンゲートウェイは、ドメインゲートウェイに似ていますが、車両の特定の領域にIOを集約するために物理的に配置されています。

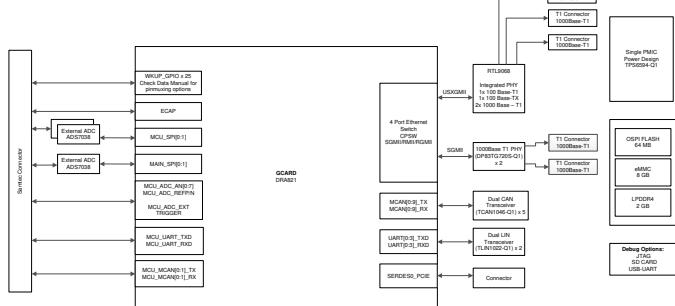

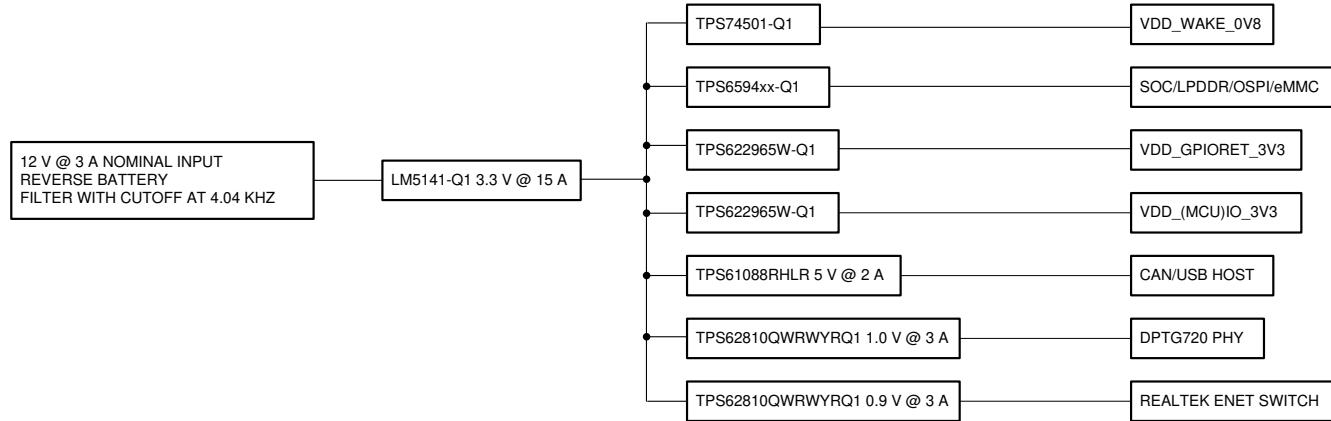

このリファレンスデザインは、DRA821ベースの使いやすい詳細なリファレンスデザインであり、集中型、ドメインまたはゾーンコントローラとして使用できます。DRA821は、高性能の異種SoCであり、車載分野の従来型コネクティビティ(LINとCAN)とともに、PCIe、USB、4ポートのギガビットイーサネットスイッチなどの高速インターフェイス、および安全機能、セキュリティ機能を搭載しています。DRA821の高集積を活用すると、システム全体のBOM(部品表)を低減し、さまざまなゲートウェイ使用事例で使用することができます。ペリフェラル、安全性、セキュリティ機能の詳細については、『[Jacinto™ DRA821 車載用プロセッサ データシート](#)』を参照してください。

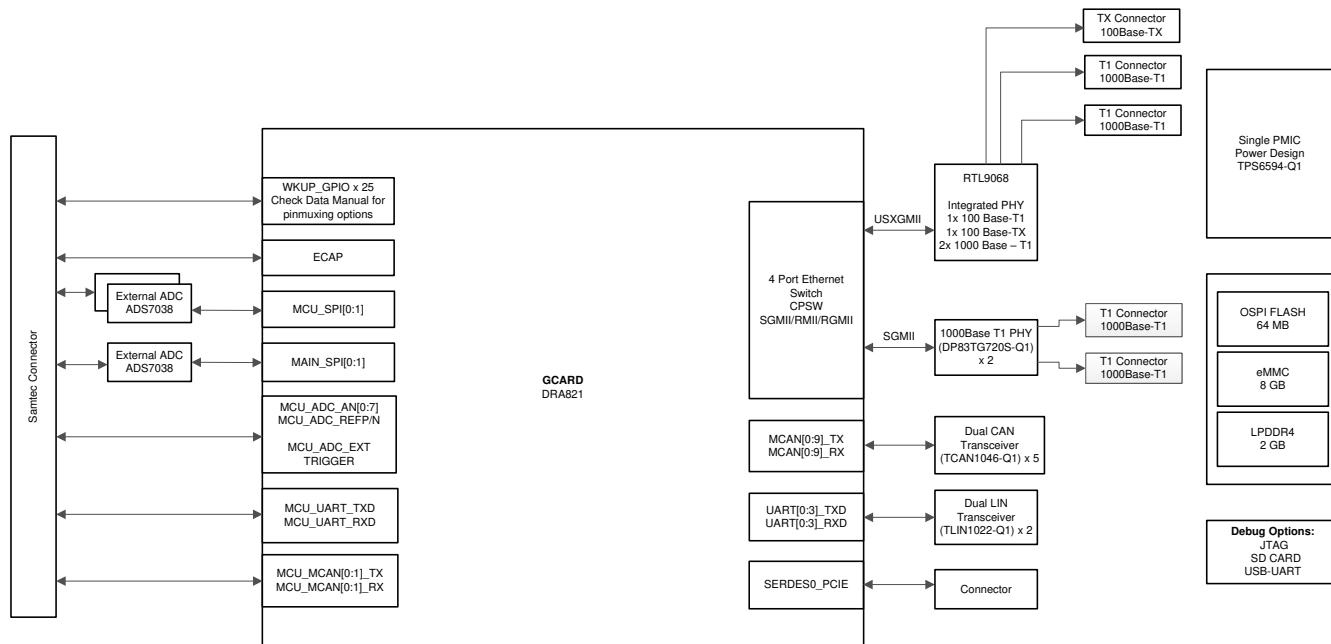

このリファレンスデザインは、単一のPMIC(TPS6594x)を使用する電源アーキテクチャを採用し、オンボードOSPI、eMMC、LPDDR4メモリ、さらにデバッグ機能を搭載しています。このボードは複数のハードウェアコネクタを搭載しており、一連の多様な通信プロトコルを提示およびサポートしています。これらのコネクタに該当するのは、5個のイーサネットポート、10個のCAN-FDポート、4個のLINポート、1個のPCIEコネクタです。SPI、UART、GPIO、I<sup>2</sup>Cなど、各種シリアルプロトコルに容易にアクセスするための複数のヘッダーも実装済みです。

このリファレンスデザインは、OEM(自動車メーカー)とティア1(一次下請け)のメーカー各社が車載分野でフル機能のDRA821ソリューションを容易かつ迅速に製作するための出発点の役割を果たします。このデザインを活用すると、開発コストの大幅な削減と、開発期間の大幅短縮を実現できます。

## 2 主なシステム仕様

表 2-1. 主なシステム仕様

| パラメータ     | 仕様                                                                                                                      |

|-----------|-------------------------------------------------------------------------------------------------------------------------|

| SoC       | DRA821 SoC                                                                                                              |

| 電源        | <ul style="list-style-type: none"> <li>12V</li> <li>シングルPMICソリューション</li> </ul>                                          |

| 自動接続      | <ul style="list-style-type: none"> <li>CAN</li> <li>LIN</li> </ul>                                                      |

| 高速接続      | <ul style="list-style-type: none"> <li>統合型4ポートギガビットイーサネットスイッチ</li> <li>外部Realtekイーサネットスイッチ</li> <li>PCIeコネクタ</li> </ul> |

| シリアルプロトコル | <ul style="list-style-type: none"> <li>SPI</li> <li>I<sup>2</sup>C</li> <li>GPIO</li> <li>ADC</li> <li>UART</li> </ul>  |

| メモリ       | <ul style="list-style-type: none"> <li>2GBのLPDDR4(2666MT/s)</li> <li>8GBeMMC</li> <li>64MBOSPI</li> </ul>               |

| ウェイクアップ   | CAN、LIN、GPIOイベントによるGPIO保持モード                                                                                            |

| デバッグ      | <ul style="list-style-type: none"> <li>JTAG</li> <li>UART経由のUSB</li> <li>SDカード</li> </ul>                               |

### 3 システム概要

#### 3.1 ブロック図

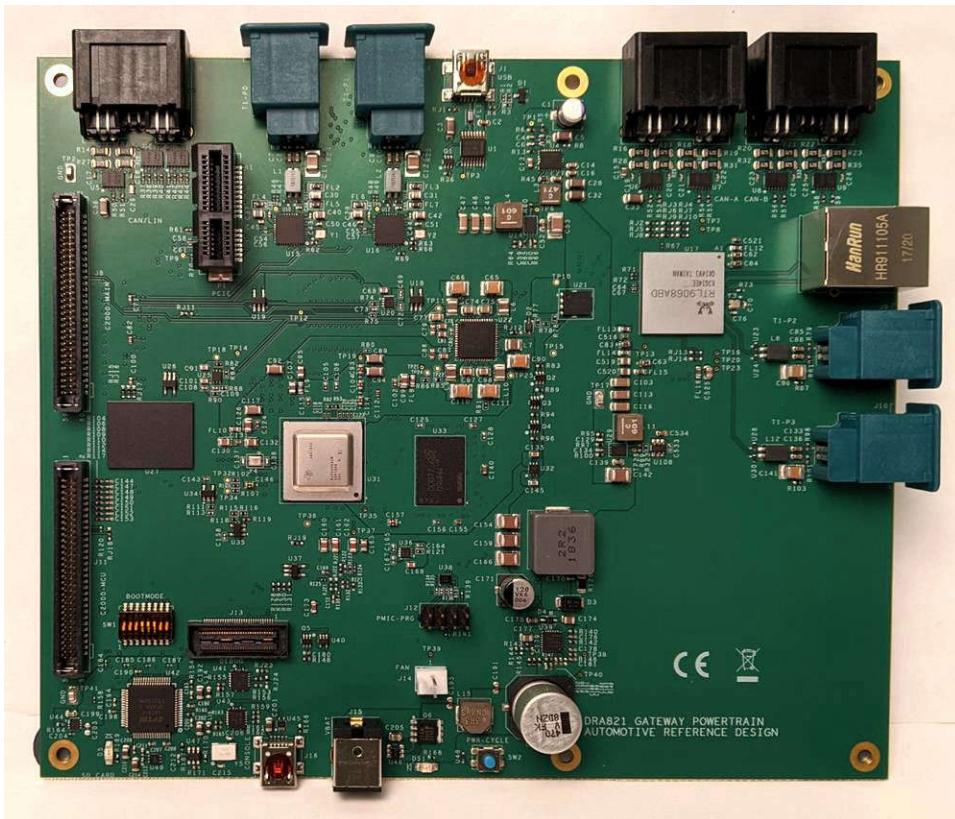

図 3-1. TIDEP-01022 のブロック図

図 3-2. TIDEP-01022 ボード

### 3.2 設計上の考慮事項

- ゲートウェイ アプリケーションをターゲットとする DRA821 SoC の機能を提示します

- 最適化されたシステム リファレンス デザインを示します

- 8 層 PCB のデザイン

- 最適化された電源アーキテクチャ

- 統合型イーサネットスイッチとマルチ CAN サポート

- IO スタンバイのサポート

- システム全体の BOM (部品表) を最小化

### 電源に関する考慮事項

図 3-3. 電源ツリー設計

### 3.3 主な使用製品

#### プロセッサ

このリファレンス デザインは、DRA821 SoC をベースにしています。この SoC は、デュアル ARM Cortex-A72 コアと 4 つの ARM R5F を搭載した異種の車載プロセッサであり、さまざまな処理アプリケーションとリアルタイム アプリケーションをサポートします。また、DRA821 は 4 ポートのイーサネットスイッチ、20 個の CAN-FD インターフェイス、PCIe、統合された HSM、最高 ASIL-D の決定論的能力を備えており、ゲートウェイ アプリケーション内で高帯域幅の安全かつ安全なデータ通信を保証します。

#### 電源

このリファレンス デザインは、単一の TPS6594x PMIC をベースにしています。電源トポロジは、複数のディスクリート降圧と組み合わせて、PMIC への 12V 入力に基づいています。TPS6594x-Q1 は、最適化されたパワー マネージメント、ASIL-D 機能、ウェークアップ機能をチップに統合した PMIC です。

#### イーサネット

##### [内蔵スイッチ]

2 個の 1000Base 車載コネクタを SGMII 経由で DRA821 統合型 4 ポートギガビットイーサネットスイッチポートに接続しています。内蔵スイッチは、1 つの 2.5GB XFI または SGMII、最大 4 つの 1GB SGMII、最大 4 つの RMII (10/100) または RGMII (10/100/1000)、1 つの 5GB QSGMII など、インターフェイスの多様な設定をサポートします。また、TSN/AVB をサポートするために、IEEE 1588 (Annex D, E, F) 対応の時間同期機能も内蔵されています。

##### [外部スイッチ]

RealTek RTL9068 スイッチは、USXGMII (最大 5Gbps) を介して DRA821 の内蔵ギガバイトイーサネットスイッチに接続されます。RJ45 100Base コネクタと 2 つの 1000Base 車載用コネクタは、RTL9068 から供給されます。

## CAN

ボード上には 5 つの TCAN1046 デバイスがあり、合計 10 本の CAN 接続をサポートします。TCAN1046 はデュアル CAN トランシーバで、最高 8Mbps の Classical CAN および CAN-FD バス ネットワークの両方に対応しています。

## LIN

基板には 2 個の TLIN1022 デバイスがあり、合計 4 つの LIN 接続に対応しています。TLIN1022-Q1 デバイスは、デュアルローカル相互接続ネットワーク (LIN) の物理層トランシーバで、ウェークアップおよび保護機能が内蔵され (最大 12V)、LIN 2.2A 標準に準拠しています。

## ウェークアップ機能

ウェークアップ機能は、CAN、LIN、GPIO 入力のいずれかを使用して実現できます。これらの入力は、それぞれ独自の I/O スタンバイドメイン上にあるため、消費電力の削減とウェークアップの相乗効果を実現できます。

## メモリ

このリファレンス デザインは、1 つの MT53D512M32D2DS Micron メモリ バンクを使用しており、2666 MT/s で動作する合計 2GB のオンボード LPDDR4 メモリに対応しています。Micron の MTFC8GAMALNA は、DRA821 の eMMC インタフェイスに接続された 8GB のオンボード NAND フラッシュを搭載しています。OSPI を介した高速ブートをサポートするため、このボードでは 64MB の NOR フラッシュに Cypress の S28HS512T を使用しています。

## コネクタ

このボードには複数の追加ヘッダーを搭載しており、GPIO、SPI、I2C、ADC、ECAP にアクセスできます。また、専用の CAN トランシーバ、LIN トランシーバ、車載イーサネットコネクタもボードに搭載しています。標準的な PCIe コネクタは高帯域通信をサポートしています。ピンのマルチプレクサ制限があるため、SGMII と QSGMII を使用する場合、PCIe コネクタは Gen 2 の速度で 1 レーンを介して動作します。SGMII または QSGMII ポートを使用しない場合、Gen 3 の速度で 2 レーンを取得できます。詳細については、SERDES ピンのマルチプレクサに関する資料を参照してください。テクニカル リファレンスマニュアルの「[4-L シリアライザ / デシリアルライザ \(SERDES\)](#)」セクションを参照してください。

## デバッグ

ミニ USB A/B コネクタ経由の JTAG、SD カード、USB-UART をデバッグ ポートとして利用可能です。

## 4 ハードウェア、ソフトウェア、テスト要件、テスト結果

ソフトウェアはデモ用と参照用に開発されており、現在サポート SDK には統合されていません。以下のリソースでは、基本的なハードウェア セットアップとソフトウェア リファレンスについて説明します。

### 4.1 ハードウェア要件

このボードでは、標準 2.5mm EVM 電源コネクタから起動するために 12V DC 電源が必要です。

### 4.2 ソフトウェア要件

Gateway POC

- Connect アプリ (イーサネット経由のクラウド デモ)

- マルチ CAN、イーサネット

- ブート KPI、安全性

- 高速 CAN 応答をサポート

- 50ms HS 未満

- 70ms 未満 HS + BIST

- プロンプトを表示する Linux の高速起動: 1 秒未満

- メイン R5F 上で最適化されたゲートウェイ機能

### 4.3 テスト設定

診断テストは、電源投入 (12V DC 電源ブリック) 後、コネクタに外付け部品を接続せずにオンボードで実行しました。

### 4.4 テスト結果

ボードの初期起動中に、いくつかのペリフェラルで予備のトグル オン / オフのテストが正常に行われました。

| ペリフェラル         | テスト結果 |

|----------------|-------|

| メイン R5         | 合格    |

| A72            | 合格    |

| Linux ブート      | 合格    |

| CCS JTAG       | 合格    |

| MCU UART コンソール | 合格    |

| メイン UART コンソール | 合格    |

| DDR @ 2666MT/s | 合格    |

| EMMC           | 合格    |

| SD カード         | 合格    |

| LIN            | 合格    |

| SPI            | 合格    |

| MCAN           | 合格    |

| GPIO           | 合格    |

| 発振器            | 合格    |

| 不可欠な電源         | 合格    |

| USB2.0 列挙      | 合格    |

## 5 設計とドキュメントのサポート

### 5.1 デザイン ファイル

#### 5.1.1 回路図

回路図をダウンロードするには、のデザイン ファイルを参照してください。

### 5.1.2 BOM

部品表 (BOM) をダウンロードするには、のデザイン ファイルを参照してください。

### 5.1.3 PCB レイアウトの印刷

レイヤ プロットをダウンロードするには、のデザイン ファイルを参照してください。

### 5.1.4 ガーバー ファイル

ガーバー ファイルをダウンロードするには、のデザイン ファイルを参照してください。

### 5.1.5 アセンブリの図面

アセンブリの図面をダウンロードするには、のデザイン ファイルを参照してください。

## 5.2 ドキュメントのサポート

1. テキサス インスツルメンツ、『[Jacinto™ DRA821 プロセッサ テクニカル リファレンス マニュアル](#)』

2. テキサス インスツルメンツ、『[Jacinto™ DRA821 車載プロセッサ データシート](#)』

## 5.3 サポート・リソース

TI E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、該当する貢献者により、現状のまま提供されるものです。これらは TI の仕様を構成するものではなく、必ずしも TI の見解を反映したものではありません。TI の[使用条件](#)を参照してください。

## 5.4 商標

Jacinto™, テキサス・インスツルメンツの™, and TI E2E™ are trademarks of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

## 6 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| Changes from Revision * (November 2020) to Revision A (December 2020) | Page              |

|-----------------------------------------------------------------------|-------------------|

| • 3200 MT/s の LPDDR4 を 2666 MT/s の LPDDR4 に更新.....                    | <a href="#">1</a> |

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Webツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適したTI製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているTI製品を使用するアプリケーションの開発の目的でのみ、TIはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TIや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TIおよびその代理人を完全に補償するものとし、TIは一切の責任を拒否します。

TIの製品は、[TIの販売条件](#)、[TIの総合的な品質ガイドライン](#)、[ti.com](#)またはTI製品などに関連して提供される他の適用条件に従い提供されます。TIがこれらのリソースを提供することは、適用されるTIの保証または他の保証の放棄の拡大や変更を意味するものではありません。TIがカスタム、またはカスタマー仕様として明示的に指定していない限り、TIの製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TIはそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025年10月