## Design Guide: TIDA-050034

## NXP iMX 7D プロセッサ向け統合型電源のリファレンス デザイン

## 説明

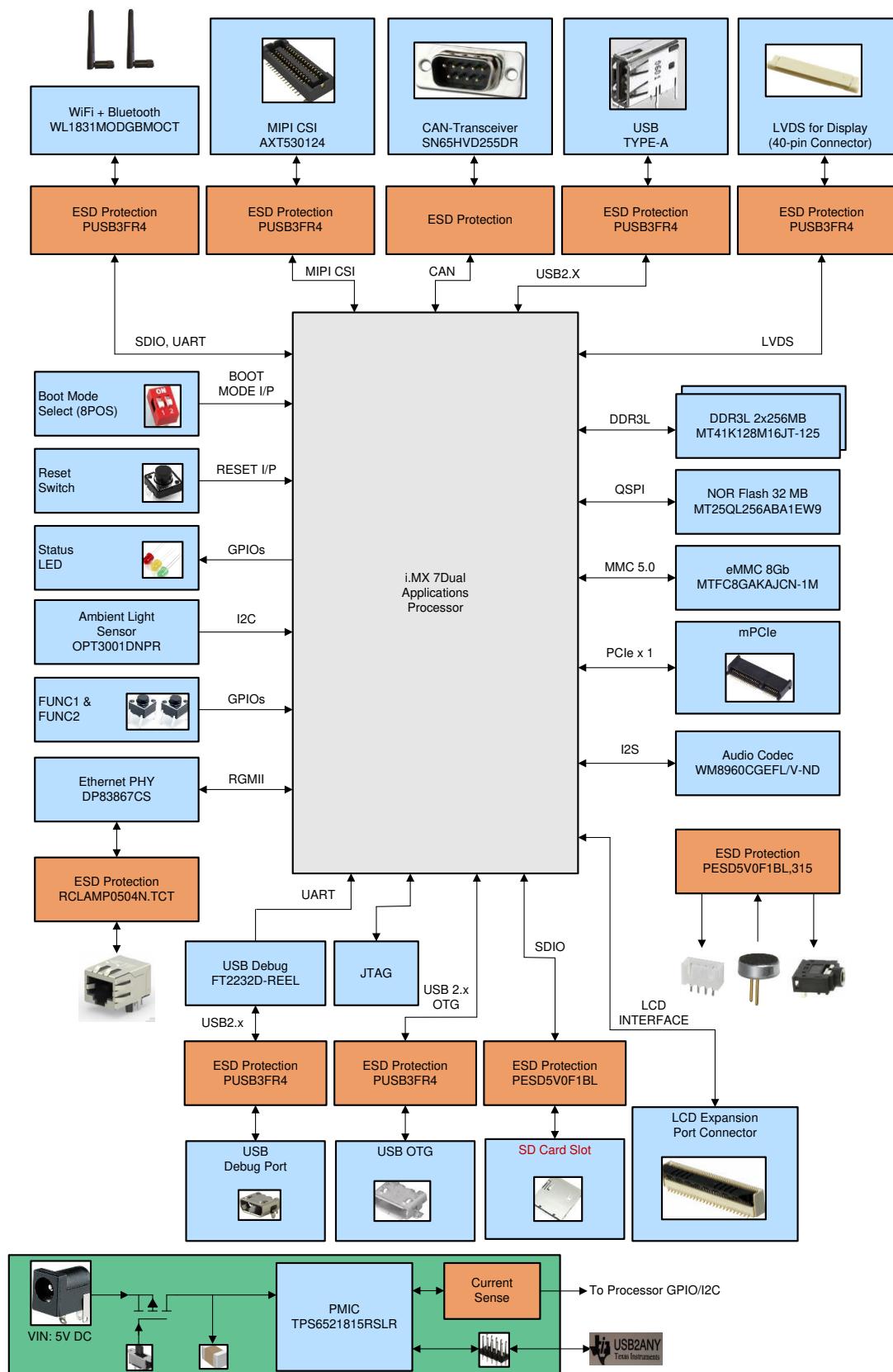

このリファレンス デザインは、TI PMIC、TPS6521815 と NXP® i.MX 7Dual アプリケーション プロセッサと組み合わせたフル機能の開発ボードです。このハードウェア デザインは、DDR3L SDRAM (2x512MB)、64MB シリアル NOR フラッシュ、8GB eMMC 5.0 iNAND、SD カードインターフェイス v3.0、外部 TFT ディスプレイインターフェイス用 50 ピン LCD コネクタ、1000Base-T イーサネット、USB2.0 Type A および micro-AB、外部カメラインターフェイス用モバイル産業用プロセッサインターフェース (MIPI) CSI、mini-PCIeインターフェイスで構成されます。このデザインは、i.MX 7Solo または i.MX 7Dual プロセッサを使用し、代替電源オプションの評価を必要とするプロジェクトに適しています。

## リソース

TIDA-050034

デザイン フォルダ

TPS6521815、TPS51200

プロダクト フォルダ

TPS62067、TPS3808

プロダクト フォルダ

INA3221、TLV755P

プロダクト フォルダ

WL1831MOD、DP83867CR

プロダクト フォルダ

OPT3001

プロダクト フォルダ

## 特長

- NXP i.MX 7D および i.MX 7S システムを短期間で開発できるフルシステム オン ボード

- 低消費電力モードと DVFS をサポート

- Wi-Fi® + Bluetooth® のワイヤレス接続機能

- イーサネット、CAN、USB 有線接続機能

- LCD、HDMI®、MIPI DSI のディスプレイオプション

- 選択可能なブートオプション (SD、eMMC、QSPI)

## アプリケーション

- データコンセントレータ

- 電気メータ

- HVAC ゲートウェイ

- サーモスタット

- 侵入管理パネル

- ビルのセキュリティゲートウェイ

- モジュール搭載コンピュータ

- HMI パネル

- バーコードスキャナー

- ポータブル POS

RadiumBoards でご注文いただけます。

このリファレンス デザインは HDMI® 技術を採用しています。

## 1 システムの説明

TIDA-050034 は、TPS6521815 PMIC から NXP i.MX 7Dual プロセッサに電力を供給するためのリファレンス デザインです。PMIC がプロセッサに電力を供給できることを示すために、さまざまなペリフェラル デバイスを搭載した包括的な評価キット (EVK) ボードを構築し、さまざまな最終製品の開発を支援することは最も重要です。その結果、さまざまな有線およびワイヤレスの接続と、複数のブートオプションが利用可能になります。すべてのペリフェラルを追加する最終的な結果、一部の外部 DC/DC と LDO レギュレータが追加され、必要に応じてより多くの電圧レールと電流供給を提供できるようになりました。最後に、ボード全体が動作することを確認できるように、TI はオープン ソースの組込み Linux Yocto SDK を使用してソフトウェアを開発およびテスト済みであり、この設計のテストを開始しています。

### 1.1 主なシステム仕様

表 1-1. 主なシステム仕様

| パラメータ                | 仕様                                                                                                | 詳細                           |

|----------------------|---------------------------------------------------------------------------------------------------|------------------------------|

| プロセッサ                | i.MX 7Dual、デュアルコアアプリケーション プロセッサ、MCIMX7D7DVM10SC                                                   | <a href="#">セクション 2.2.1</a>  |

| PMIC                 | TPS6521815 自動シーケンシング機能と DVFS (電圧スケーリング機能) を搭載したユーザー プログラマブル PMIC                                  | <a href="#">セクション 2.3.1</a>  |

| 補助電源                 | TPS51200 DDR ターミネータ、TPS62067 2A 降圧、TLV755P LDO                                                    | <a href="#">セクション 2.3.7</a>  |

| メモリ                  | 2 個の 4Gb DDR3L (合計 1GB)、512Mb QSPI NOR フラッシュ (64MB)、8GB eMMC 5.0、SD v3.0 インターフェイス                 | <a href="#">セクション 2.2.2</a>  |

| オーディオ コーデック          | SAI (シリアル オーディオ インターフェイス) を使用して、マイク、スピーカー、ヘッドフォン用に Cirrus Logic の WM8960CGEFL/V-ND コーデックをサポートします。 | <a href="#">セクション 2.2.3</a>  |

| イーサネット               | ギガビットイーサネットインターフェイス — TI の DP83867CS PHY と Pulse Electronics の J1011F21PNL RJ45 ジャック              | <a href="#">セクション 2.3.3</a>  |

| Wi-Fi + Bluetooth    | TI の WL1831MOD デバイスにより、Wi-Fi + Bluetooth をサポート                                                    | <a href="#">セクション 2.3.2</a>  |

| デバッグ方法 (USB-to-UART) | USB からシリアルへの UART 変換を実装するには、FTDI FT2232D が必要です                                                    | <a href="#">セクション 2.2.4</a>  |

| USB ポート              | USB Type-A (TE 1-1734775-1) および micro-AB インターフェイス (ヒロセ® ZX62D-AB-5P8)                             | <a href="#">セクション 2.2.5</a>  |

| LCD ディスプレイ           | LCD サポート用 RGB TFT 50 ピン コネクタ (Hirose FH40-50s-0.5SV)                                              | <a href="#">セクション 2.2.6</a>  |

| MIPI CSI             | 2 レーン MIPI CSI から 30 ピン コネクタ (Panasonic AXT530124)                                                | <a href="#">セクション 2.2.7</a>  |

| ミニ PCIe              | TE AXT530124 30 ピン コネクタ、ダイオード PI6C557-03LE PCIe クロツク ジェネレータ、Molex 78723-1001 micro-SIM カード ソケット   | <a href="#">セクション 2.2.8</a>  |

| JTAG ヘッダー            | 50mil ピッチ、10 ピン ヘッダーを使用して i.MX 7D プロセッサに JTAG 接続                                                  | <a href="#">セクション 2.2.10</a> |

| USB2ANY ヘッダー         | プロセッサ I <sup>2</sup> C バスから分離した PMIC のデバッグ方法。USB2ANY により供給 (標準的な 100mil ピッチ、10 ピン ヘッダー)           | <a href="#">セクション 2.2.11</a> |

| CAN インターフェイス         | マイクロチップ MCP2562-E/MF CAN トランシーバ、TE 5747840-4 DB9 オスコネクタ                                           | <a href="#">セクション 2.2.9</a>  |

| 周囲光センサ               | I <sup>2</sup> C 通信機能搭載の TI OPT3001DNPR デバイス                                                      | <a href="#">セクション 2.3.4</a>  |

| 電流監視                 | 2 × TI INA3221 デバイスは、システム内の 6 つのレールを流れる電流を監視するために使用されます                                           | <a href="#">セクション 2.3.5</a>  |

| コイン セルでの操作           | コイン セルは i.MX 7D SNVS 入力に直接接続可能。TI の TPS3808G25 スーパーバイザを使用すると、コイン セル バッテリが挿入されるまでシステムは電源オンを防止できます。 | <a href="#">セクション 2.3.6</a>  |

| 触感入力、視覚フィードバックです     | ソフトウェアのデバッグに役立つプロセッサの GPIO に接続されているプッシュボタンとステータス LED                                              | <a href="#">セクション 2.2.12</a> |

## 2 システム概要

### 2.1 ブロック図

図 2-1. TIDA-050034 のブロック図

## 2.2 設計上の考慮事項

このデザインは、i.MX 7Dual プロセッサおよび幅広いペリフェラル IC に電力を供給する TI の電源デバイスの能力を示すことを目的とします。これを検証するために、プロセッサから始めて、これらの他の IC をすべて設計に実装する必要がありました。動作評価キットの構築に必要な他のすべてのデバイスは、このセクションに含まれます。電源デバイスとその他の TI デバイスについては、[セクション 2.3](#) を参照してください。

### 2.2.1 プロセッサ - i.MX 7Dual アプリケーション プロセッサ

i.MX 7Dual プロセッサ ファミリは、低消費電力要件を満たす高性能処理に使用され、高度な機能統合も組み込まれています。これらのプロセッサは、ネットワーク接続型デバイスやポータブル デバイスの成長市場をターゲットとしています。

i.MX 7Dual プロセッサは 3 個のコア (型番に応じて 800MHz ~ 1.2GHz で動作する 2 個の Arm® Cortex®-A7 コア、200MHz で動作する 1 個の Cortex®-M4 コア) で構成されています。このプロセッサには 32 ビットの DDR3-1066 メモリインターフェイスが搭載されており、DDR3L、LPDDR2、LPDDR3 インターフェイス (この設計で使用されている DDR3L) もサポートしています。このプロセッサは、イーサネット、EPD コントローラ、MIPI CSI、DSI、LCD インターフェイス、WLAN、Bluetooth、GPS、ディスプレイ、カメラ センサに加えて、セキュリティや改ざんに対する保護機能も向上しています。iMX7D プロセッサの各ピンのマッピングの詳細な表は、[付録 A](#) に記載されています。

| 説明                              | 製造  | 部品番号            |

|---------------------------------|-----|-----------------|

| i.MX 7 シリーズ 32 ビット MPU、デュアル ARM | NXP | MCIMX7D7DVM10SC |

### 2.2.2 i.MX 7Dual メモリ インターフェイス

このプロジェクトは、2×4Gb DDR3L (1GB)、512Mb QSPI NOR フラッシュ (64MB)、8GB eMMC 5.0、SD v3.0 を使用している i.MX 7D プロセッサの 4 種類の外部メモリインターフェイスを使用します。

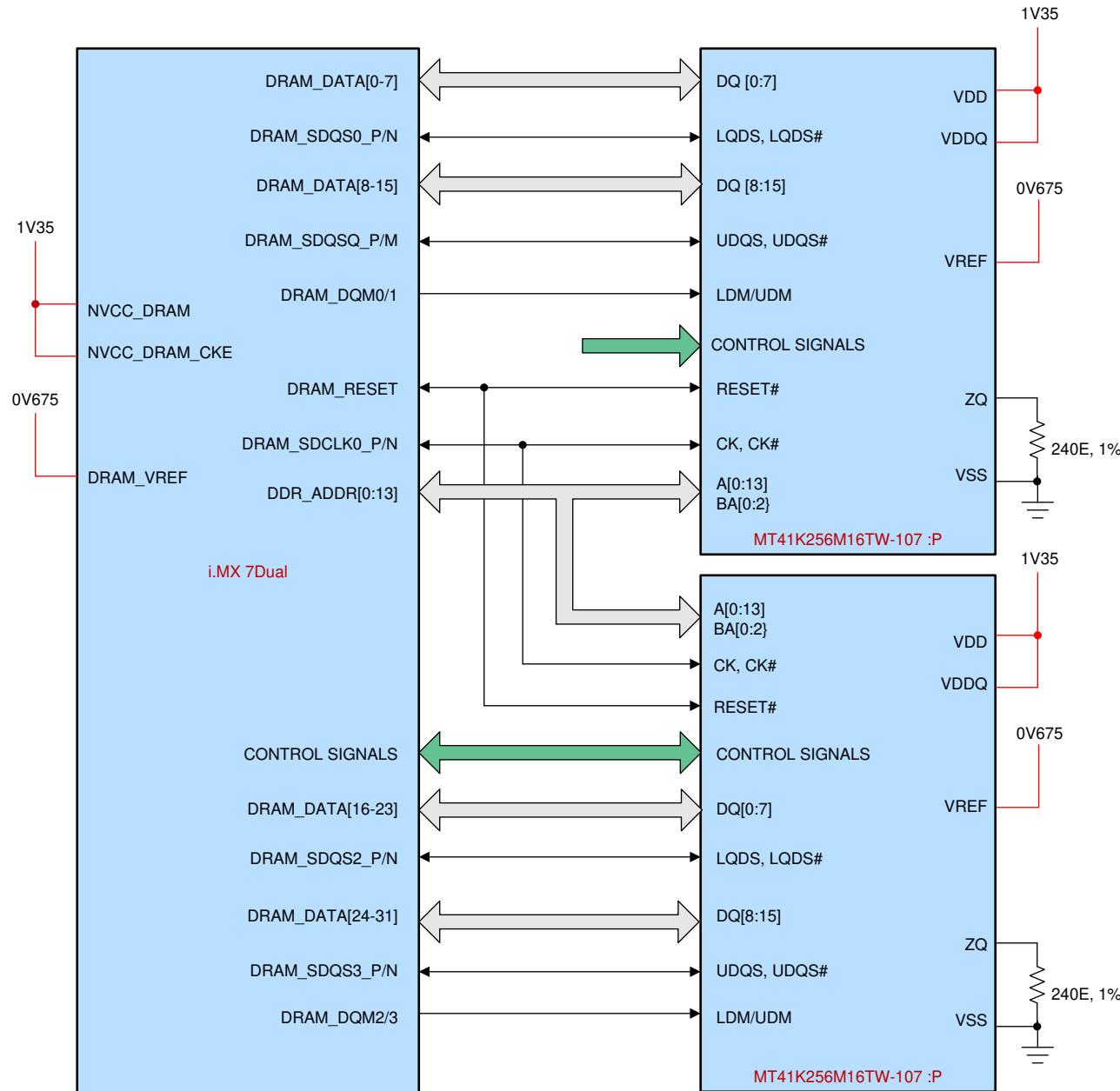

#### 2.2.2.1 DDR3L

i.MX 7Dual には専用の DDR メモリコントローラが搭載され、LP-DDR2、DDR3、DDR3L、LPDDR3 をサポートしています。これらはすべて、1066MT/s のデータレートのみをサポートしています。このデザインには、2 個の 4Gb x16 (1GB) DDR3L メモリが搭載されています。MT41K256M16TW-107:Micron® 製の P は、現在この設計で使用されている 4Gb DDR3L SDRAM です。このデザインでは、2 個の DDR3L メモリを使用し、この設計に必要な 1GB のメモリを提供します。メモリインターフェイスは、2 チャネルの 16 ビットデータ信号、および共有のコマンド信号およびアドレス信号で構成されています。[図 2-2](#) に、DDR インターフェイスを示します。

| 説明                                   | 製造     | 部品番号                |

|--------------------------------------|--------|---------------------|

| IC、DDR3L、4Gb、x16 ビット、1866MHz、FBGA-96 | Micron | MT41K256M16TW-107:P |

図 2-2. DDR3L インターフェイス

### 2.2.2.2 クワッド SPI NOR フラッシュ

i.MX 7Dual プロセッサは、パラレル NOR フラッシュインターフェイスと Quad SPI NOR フラッシュインターフェイスの両方をサポートしています。このプロジェクトは、1 つのシリアル NOR フラッシュのみをサポートしています。Micron の MT25QL256ABA1EW9-0SIT TR は、クロック周波数 133MHz で 512Mb (64MB) の密度を持ち、最大 90MB /s のデータスループットを実現するシリアル NOR フラッシュメモリです。

| 説明                                               | 製造     | 部品番号                  |

|--------------------------------------------------|--------|-----------------------|

| IC、NOR フラッシュ、64MB、SPI、133MHz、2.7 ~ 3.6V、W-PDFN-8 | Micron | MT25QL512ABB1EW9-0SIT |

### 2.2.2.3 eMMC iNAND

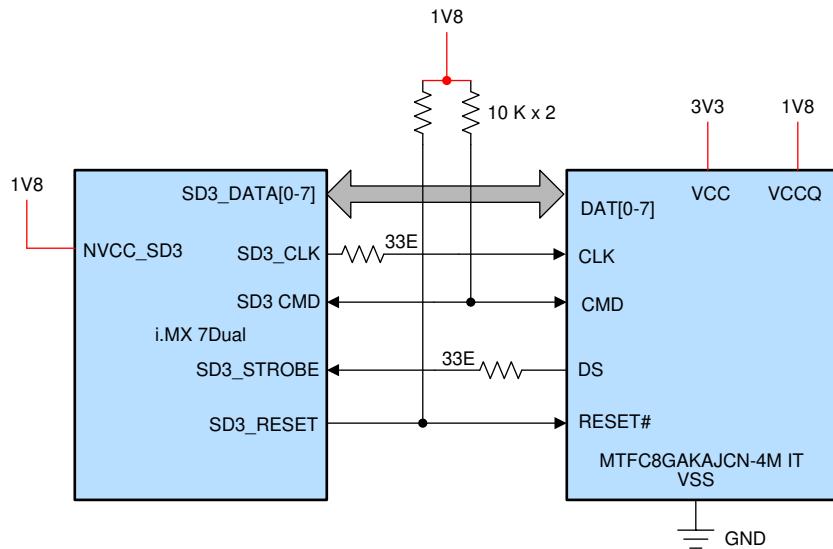

この設計には、8GB の eMMC 5.0 準拠メモリが含まれています。図 2-3 に、プロセッサを使用した eMMC インターフェイスの図を示します。ここで使用されているのはミクロンの IC、MTFC8GAKAJCN-4M IT です。IC は、HS400 をサポートします。HS400 は高速モードであり、200MHz デュアル データレートバスで 400Mbps をサポートします。

| 説明                    | 製造     | 部品番号               |

|-----------------------|--------|--------------------|

| IC、eMMC、8GB、VFBGA-153 | Micron | MTFC8GAKAJCN-4M IT |

図 2-3. eMMC インターフェイス

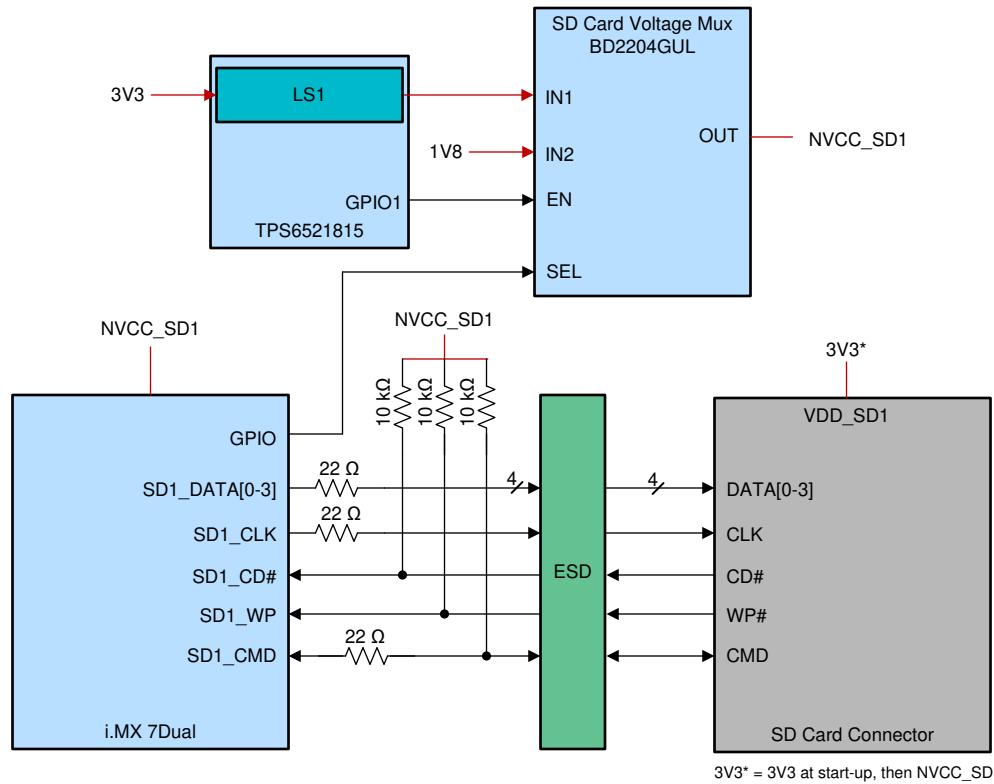

### 2.2.2.4 SD カード コネクタ

このリファレンス デザインには、SD カード コネクタとインターフェイスが搭載されています。SD カードへの電源は、パワーマルチプレクサを使用して 1.8V ~ 3.3V の範囲で選択でき、マルチプレクサに印加される両方の入力電圧は、TPS6521815 PMIC によって供給されます。SD カード コネクタの VDD ピンに印加される初期電圧は、常に 3.3V である必要があります。これは、追加の回路で実現されます。図 2-4 に、SD カード コネクタの電源と配線を示します。

| 説明                            | 製造           | 部品番号            |

|-------------------------------|--------------|-----------------|

| コネクタ、SD カード、プラッシュブル           | Amphenol ICC | 10067847-001RLF |

| ダイオード、ESD 双方向、5.5V、SOD-882D   | NXP          | PESD5V0F1BL     |

| IC、パワー スイッチ N チャネル 2:1、50VCSP | ROHM         | BD2204GUL-E2    |

図 2-4. SD カードの電源とコネクタ

### 2.2.3 オーディオ コーデック

このデザインでオーディオ コーデックを搭載するため、Cirrus Logic の IC (WM8960CGEFL/V-ND) を使用し、マイク、スピーカ、ヘッドホンに接続することができます。プロセッサへのデジタルインターフェイスは、SAI (シリアル オーディオ インターフェイス) を使用しています。このプロジェクトでは、PUI Inc の追加のオンボード マイク TOM-1545P-R があります。

| 説明                                    | 製造              | 部品番号             |

|---------------------------------------|-----------------|------------------|

| 1C、オーディオ コーデック、ステレオ、Class D、QFN-32    | シーラス論理          | WM8960CGEFL/V-ND |

| マイク、アナログ エレクトレット コンデンサ 2V ~ 10V、-45dB | PUI Audio, Inc. | TOM-1545P-R      |

### 2.2.4 USB から UART へのコンバーター

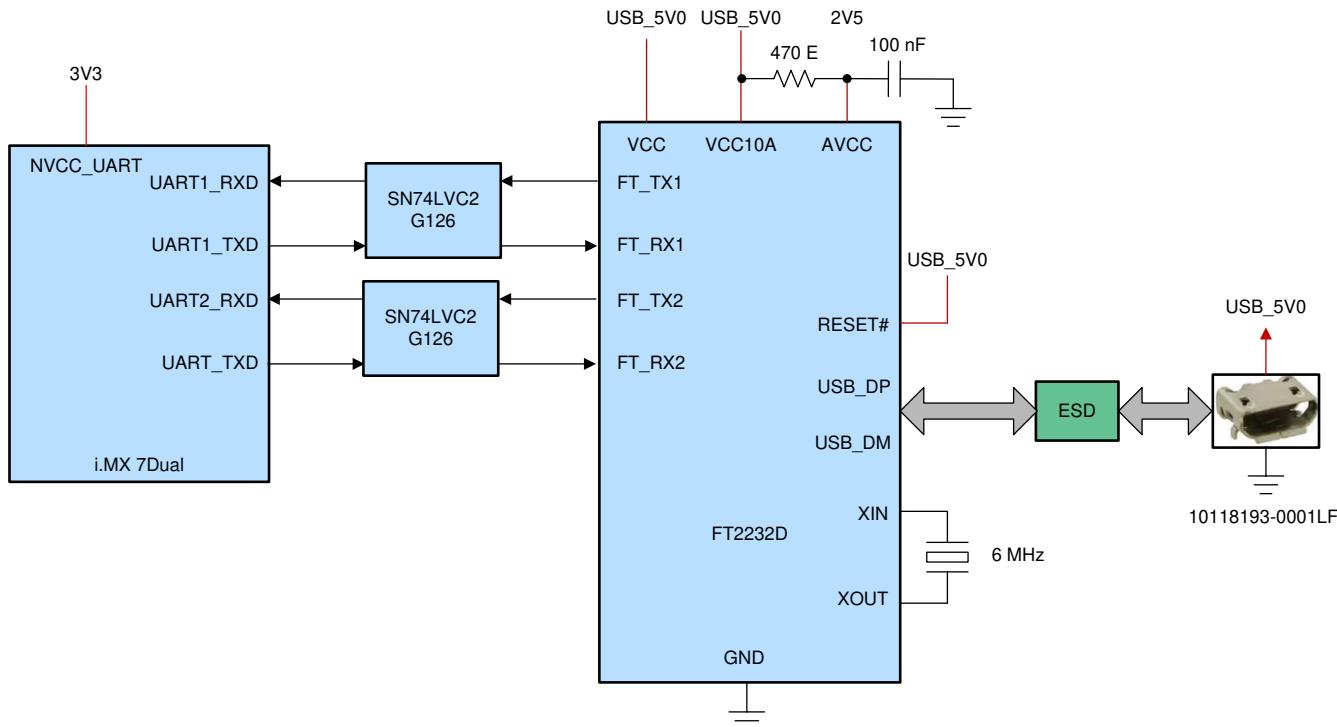

このデザインには、USB からシリアル (UART) へのインターフェイスがあります。この機能を実装するには、FTDI の FT2232D チップを使用し、USB からデュアル ポートへの RS232 コンバータです。相互接続の詳細な図は、図 2-5 を参照してください。

| 説明                                          | 製造       | 部品番号         |

|---------------------------------------------|----------|--------------|

| IC、FT2232D、USB/UART コンバータ、デュアル UART、LQFP-48 | FTDI チップ | FT2232D-REEL |

図 2-5. FT2232 との USB からシリアル UART へのインターフェイス

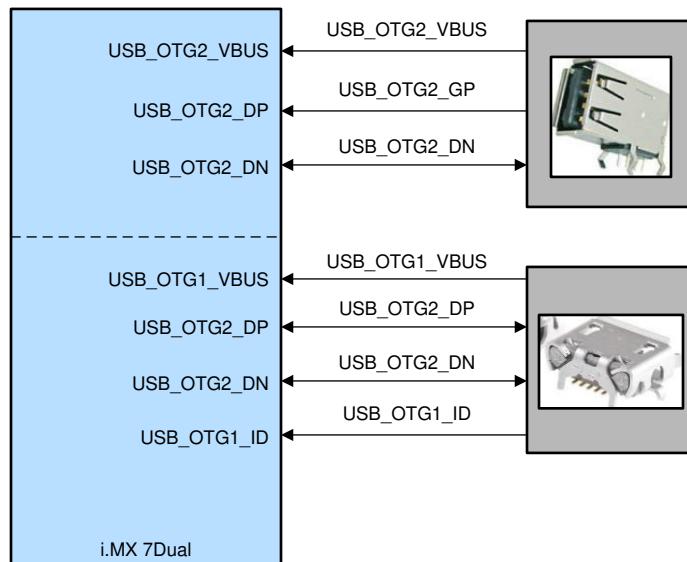

## 2.2.5 USB ポート

このデザインには、2 つの USB インターフェイス、1 つのタイプ A インターフェイスと、もう 1 つの micro-AB インターフェイスが組み込まれています。図 2-6 に示すように、プロセッサの専用 USB インターフェイス On-The-Go (OTG) の両方を持ち、レセプタクルに直接接続します。

| 説明                          | 製造  | 部品番号              |

|-----------------------------|-----|-------------------|

| Conn、USB2.0 Type A、RA、TH    | TE  | 1-1734775-1       |

| Conn、USB2.0 micro-AB、RA、SMD | ヒロセ | ZX62D-AB-5P8 (30) |

図 2-6. USB インターフェイス

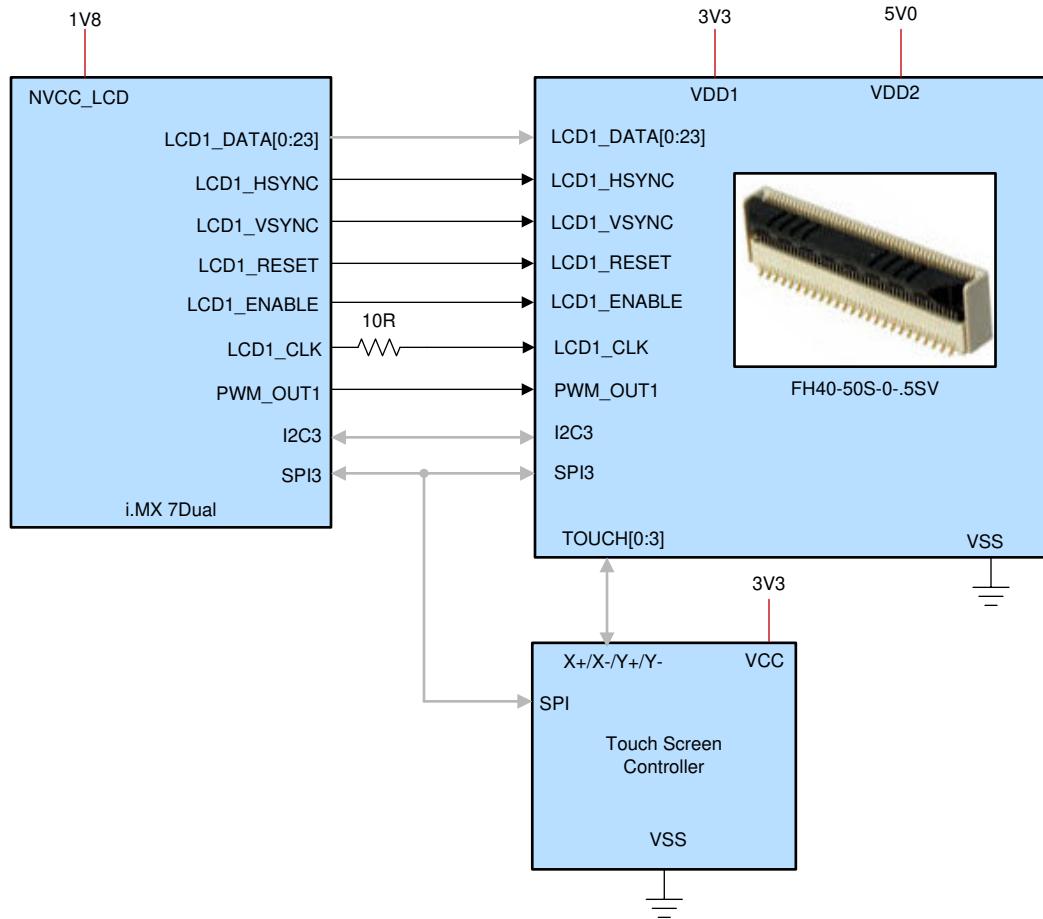

## 2.2.6 LCD スクリーンコネクタ

LCD インターフェイスは 24 の信号を 50 ピンコネクタ経由で接続する RGB TFT インターフェイスです。この接続図を、図 2-7 に示します。

| 説明                    | 製造                     | 部品番号           |

|-----------------------|------------------------|----------------|

| CONN, FPC、垂直、50 ポジション | Hirose Electric Co Ltd | FH40-50S-0.5SV |

図 2-7. i.MX 7D プロセッサからコネクタへの LCD インターフェイス

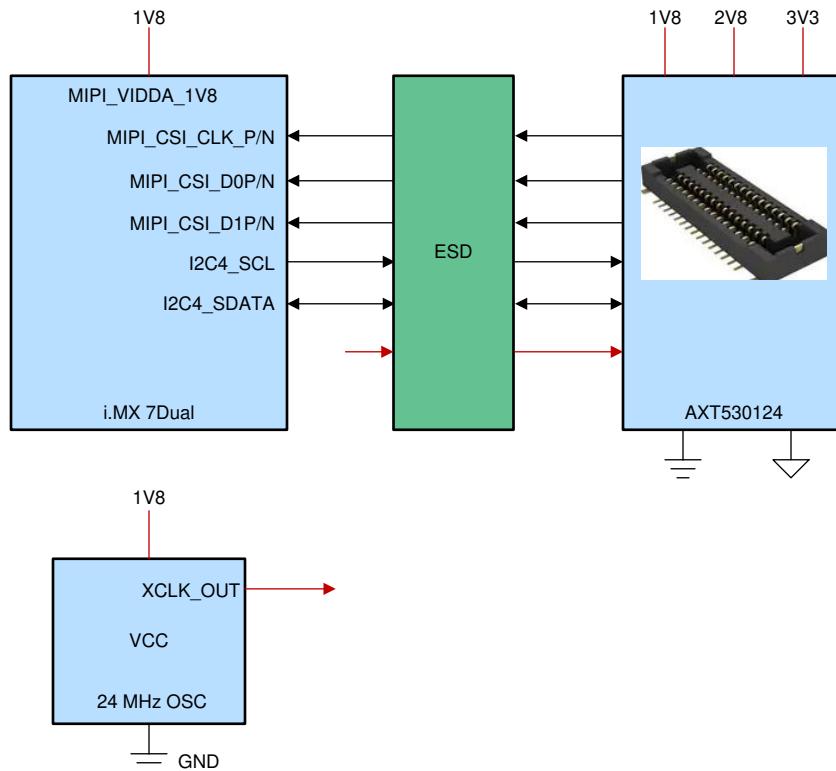

## 2.2.7 モバイル産業用プロセッサ インターフェイス (MIPI) CSI 接続

このデザインには、カメラ用の MIPI CSI が付属しています。i.MX 7D プロセッサは、図 2-8 に示すように、Panasonic の 30 ピンコネクタへのコネクタである 2 レーン MIPI をサポートしています。

| 説明                       | 製造       | 部品番号      |

|--------------------------|----------|-----------|

| コネクタ、ソケット、0.4mm、30 ポジション | パナソニック電工 | AXT530124 |

図 2-8. MIPI CSI コネクタ

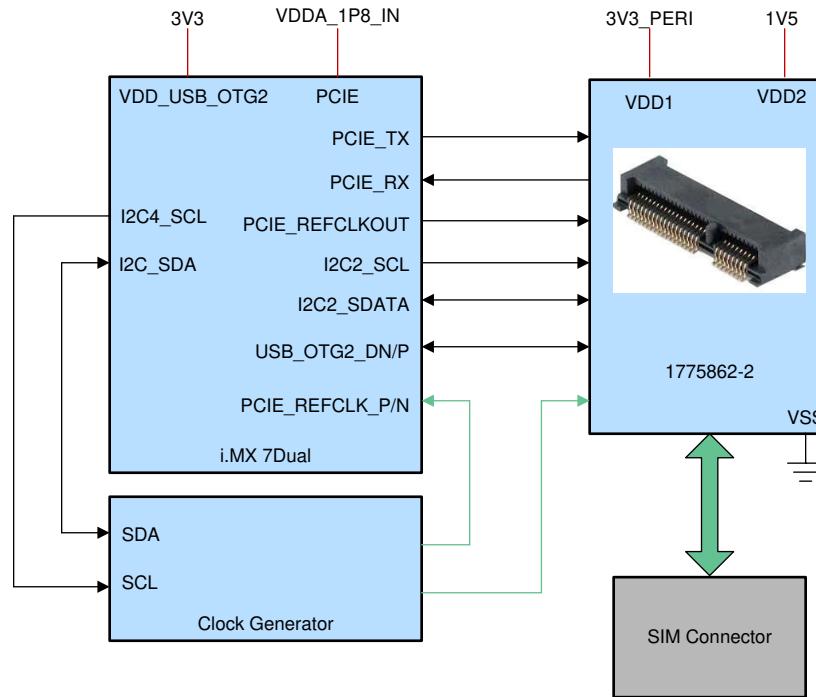

### 2.2.8 Mini PCI Express® コネクタ

mini-PCI Express、つまり mPCIe の信号は、図 2-9 に示すように、このリファレンス デザインのコネクタに終端されています。オンボードの基準クロック ジェネレータを使用します。

| 説明                                          | 製造    | 部品番号         |

|---------------------------------------------|-------|--------------|

| Conn、ソケット、mPCIe、52 ポジション                    | TE    | 1775862-2    |

| IC、PI6C557、PCIe クロック ジェネレータ、200MHz、TSSOP-16 | ダイオード | PI6C557-03LE |

| CONN、Micro SIM カード ソケット、1X1、シールド付き、RA       | Molex | 78723-1001   |

図 2-9. mPCIe インターフェイス

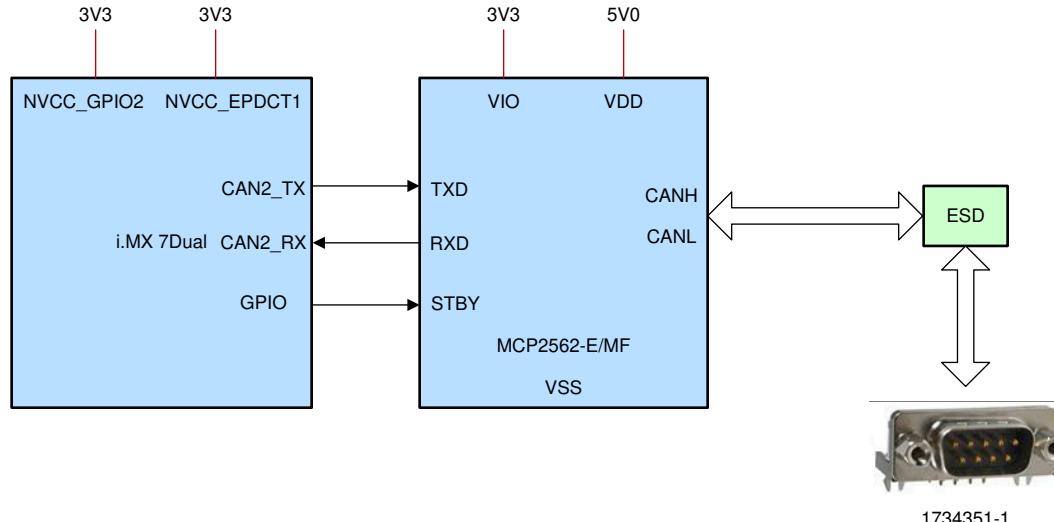

### 2.2.9 CAN トランシーバと標準コネクタ

この設計には CAN インターフェイスが搭載されています。トランシーバは Microchip の MCP2562 で、図 2-10 に示すように標準の 9 ピン D-Sub コネクタに配線されています。

| 説明                               | 製造      | 部品番号         |

|----------------------------------|---------|--------------|

| IC、CAN トランシーバ、SOIC-8             | マイクロチップ | MCP2562-E/MF |

| Conn、DE-9、オス、1x1、6A、ボードロック、RA、TH | TE      | 5747840-4    |

図 2-10. CAN インターフェイス

## 2.2.10 JTAG ヘッダー

JTAG 接続は、プログラミングとデバッグのためにプロセッサに直接アクセスするための i.MX 7Dual の要件と一致しています。

| 説明                                   | 製造  | 部品番号               |

|--------------------------------------|-----|--------------------|

| コネクタ、Berg ストリップ、2x5、1.27mm、1A、ST、SMD | FCI | 20021121-00010*4LF |

## 2.2.11 USB2ANY ヘッダー

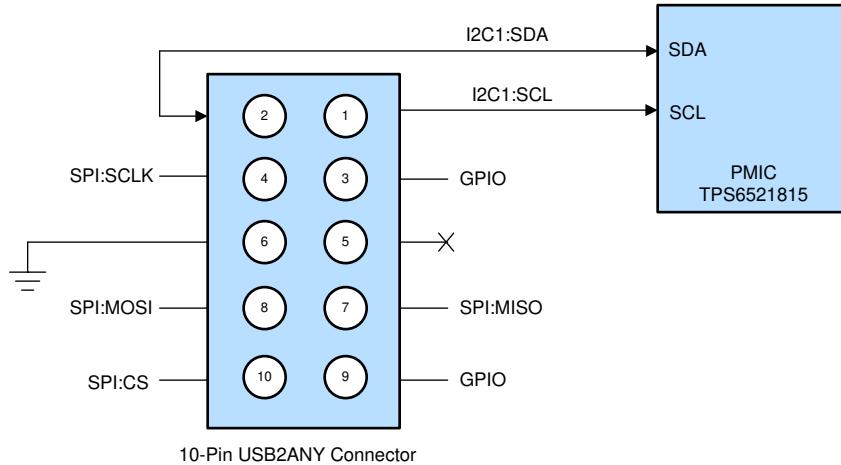

USB2ANY は、TI MCU ベースのアダプタであり、コンピュータが USB 接続を介して電子評価モジュール(EVM)を制御できるようにすることを目的としています。この設計では、USB2ANY の I<sup>2</sup>C インターフェイスを使用して、PMIC の内部レジスタを外部で監視、制御、または再プログラミます。USB2ANY ヘッダの配線を図 2-11 に示します。

| 説明                                  | 製造  | 部品番号         |

|-------------------------------------|-----|--------------|

| コネクタ、Berg ストリップ、2x5、2.54mm、3A、RA、TH | FCI | 68021-210HLF |

図 2-11. PMIC I<sup>2</sup>C ピンへの USB2ANY ヘッダーの接続

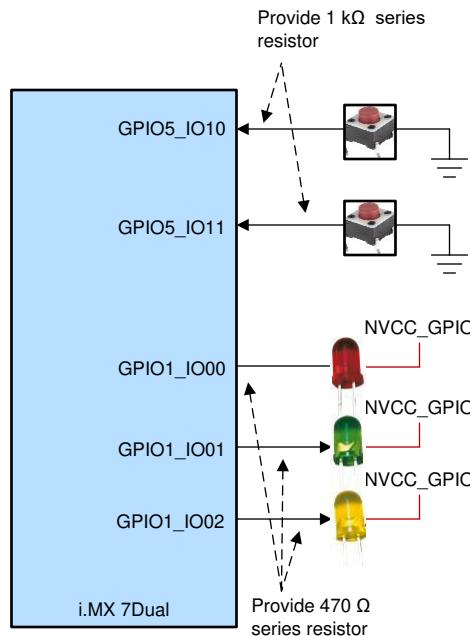

## 2.2.12 機能スイッチとステータス LED

プロセッサの入力として構成された GPIO に接続された 2 つの機能多目的プッシュボタンがあり、ソフトウェア開発者はこのボードを使用して開発されたアプリケーションをテストすることができます。プロセッサの 3 つの GPIO に 3 つの LED が接続され、実行中、完了、または障害が発生しているプロセスのステータスを示します。各プッシュボタンとステータス LED はどちらも、デバッグに使用することや、触感入力と視覚的なフィードバックをユーザーに提供することができます。図 2-12 に、これらの接続を示します。

図 2-12. プッシュ ボタンや LED との GPIO 接続

## 2.3 主な使用製品

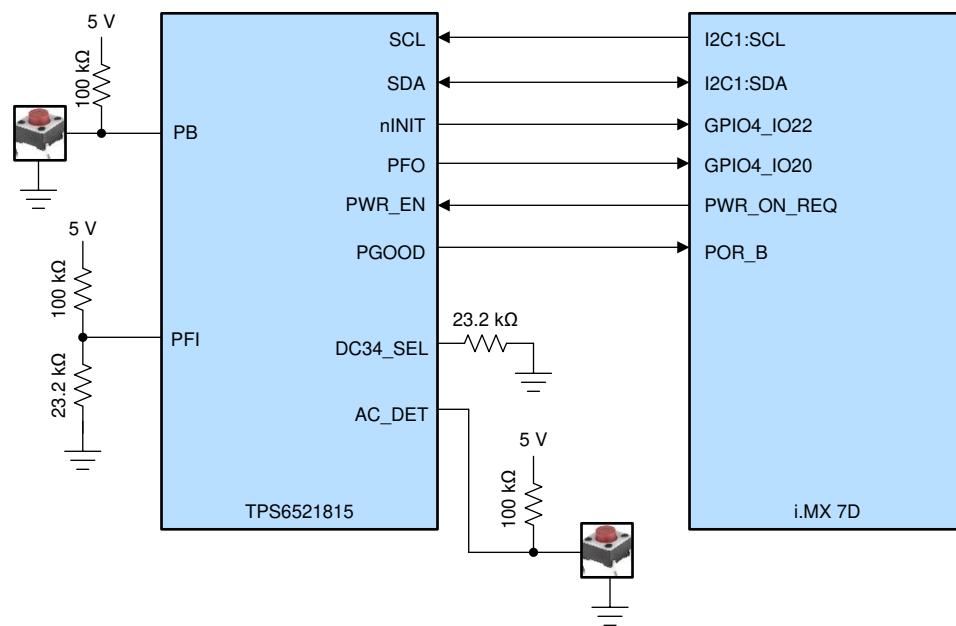

### 2.3.1 TPS6521815 - 電源管理 IC

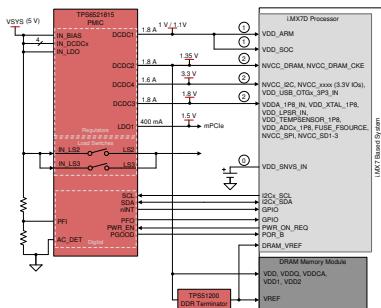

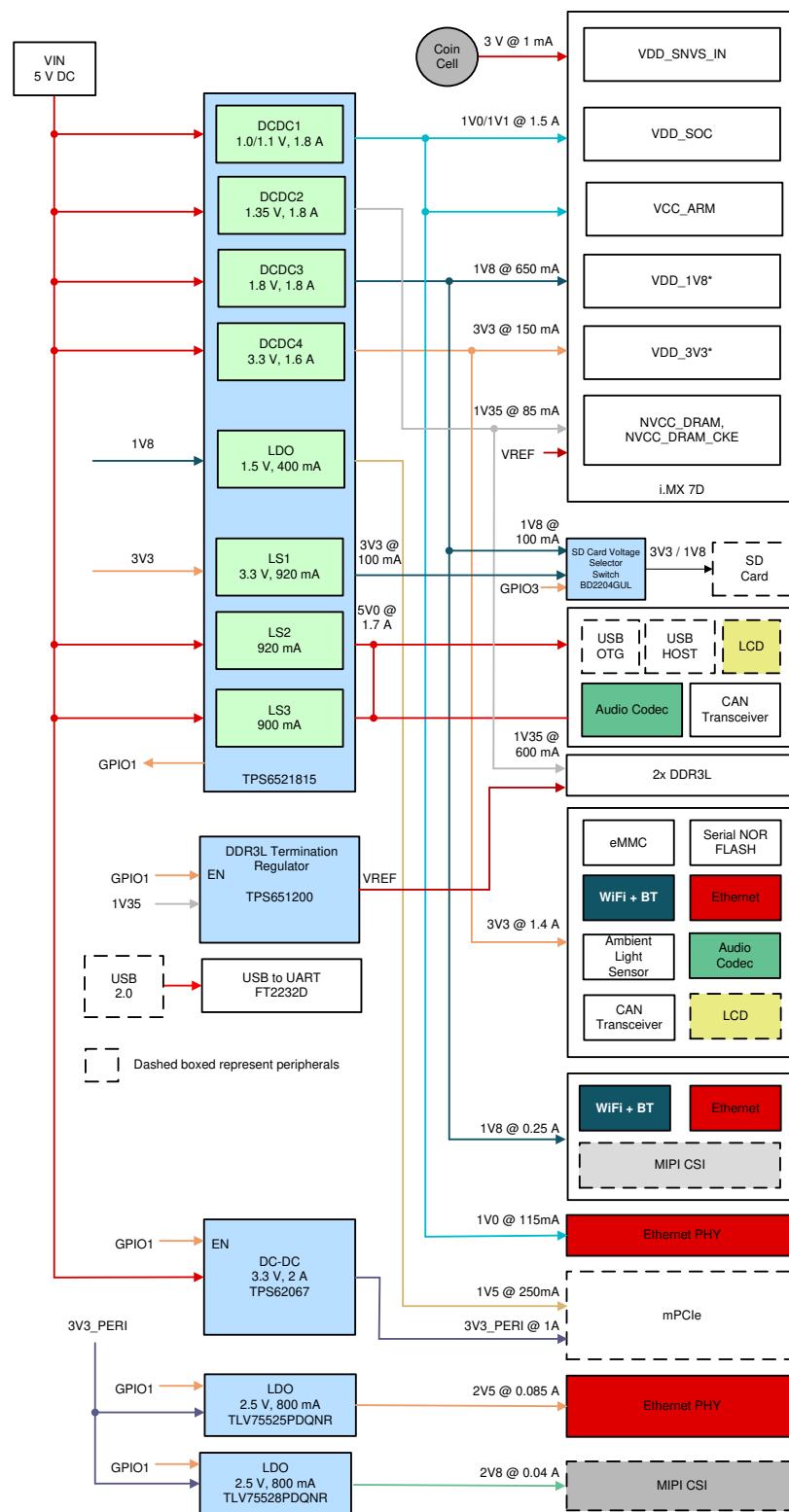

TPS6521815 デバイスは、NXP の i.MX 7Dual などの Arm Cortex プロセッサをサポートするために特別に設計された電源管理 IC (PMIC) です。PMIC は、5V 電源またはリチウムイオン バッテリで動作するアプリケーションに最適です。IC は、3 つの調整可能な降圧 (バック) コンバータ、1 つの昇降圧コンバータ、1 つの可変 LDO レギュレータ、3 つのロードスイッチで構成されており、2 つの電流制限を選択できます。PMIC は、低電圧誤動作防止 (UVLO)、過熱警告とシャットダウン、すべてのレギュレータに対する個別のパワーグッド出力、すべてのレギュレータに対するプログラム可能な電源シーケンス、およびデバイスへのレジスタ読み取りと書き込み用の I<sup>2</sup>C インターフェイスをサポートしています。この設計のフルパワー アーキテクチャを図 2-17 に示します。

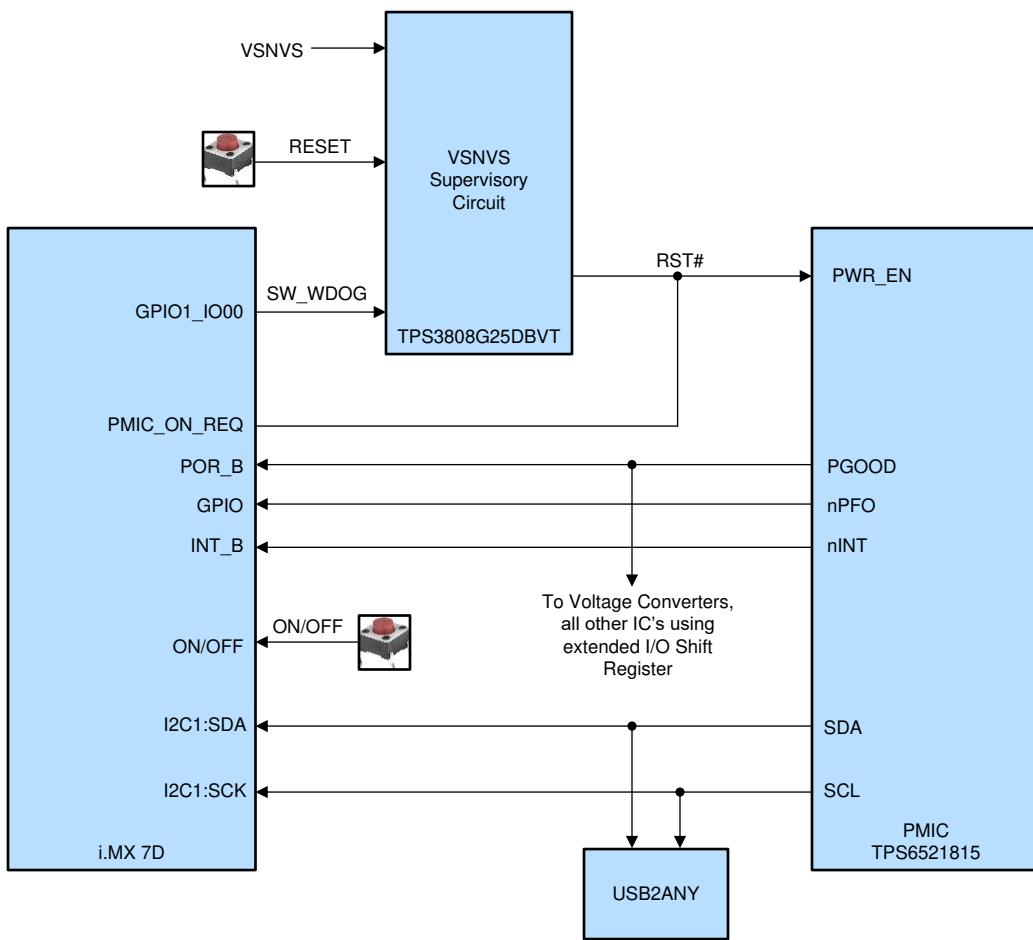

プロセッサと TPS6521815 PMIC の間の I/O 接続や、PMIC のアナログおよびデジタル入力ピンを図 2-13 に示します。

図 2-13. TPS6521815 PMIC I/O の i.MX 7D プロセッサへの配線

### 2.3.2 WL1831MOD - Wi-Fi® + Bluetooth® モジュール

このデザインは TI の Wi-Fi + Bluetooth モジュールである WL1831MODGMBMOCT デバイスを使用しています。プロセッサとのインターフェイスは、Bluetooth の場合は UART を経由し、WLAN (Wi-Fi) では SDIO を経由します。このデザインは、モノポールアンテナ接続用に 2 つの同軸接続を提供します。

| 説明                                                         | 製造 | 部品番号             |

|------------------------------------------------------------|----|------------------|

| モジュール、Wi-Fi+Bluetooth、IEEE 802.11b、802.11g、802.11n、QFM-100 | TI | WL1831MODGMBMOCT |

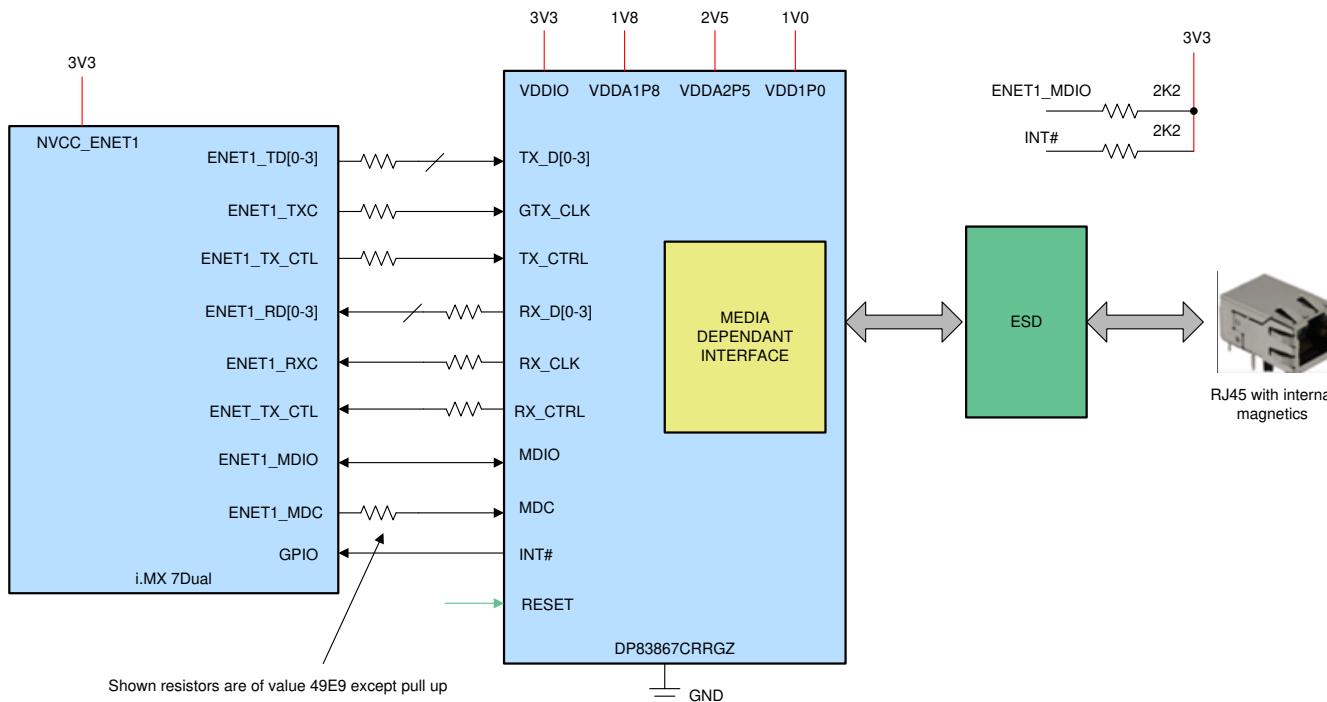

### 2.3.3 DP83867CR - イーサネット PHY

i.MX 7Dual プロセッサは、デュアルイーサネット PHY インターフェイスをサポートしていますが、この設計ではギガビットイーサネットを 1 つだけ使用しています。このリファレンス デザインで使用されている 1000Base-T PHY は DP83867CR デバイスです。プロセッサとのインターフェイスは RGMII を経由し、MDI/MDIO も接続して PHY を管理します。MDI を Cat5e ケーブルに接続するために、Pulse Electronics 製の内部磁気素子を備えた RJ45 を使用しました。[図 2-14](#) にイーサネットインターフェイス接続を示します。

| 説明                                                  | 製造                | 部品番号         |

|-----------------------------------------------------|-------------------|--------------|

| IC、ギガビットイーサネット PHY                                  | TI                | DP83867CRRGZ |

| Conn、磁気素子付きの RJ45 ジャック、1x1、シールド付き、LED (G, Y) RA, TH | PULSE ELECTRONICS | J1011F21PNL  |

図 2-14. DP83867CR PHY とのイーサネットインターフェイス

### 2.3.4 OPT3001 - 環境光センサ

このリファレンス デザインに搭載されている周辺光センサ (ALS) は、TI の IC を使用しています。プロセッサとのインターフェイスは、共有の I<sup>2</sup>C ラインを介して行われます。センサ IC のアドレス (ADDR) ピンは、[表 2-1](#) に従ってアドレス設定を判定するため、抵抗を使用してプルアップまたはプルダウンする必要があります。

| 説明                                | 製造 | 部品番号        |

|-----------------------------------|----|-------------|

| IC、環境光センサ、I <sup>2</sup> C、USON-6 | TI | OPT3001DNPR |

表 2-1. OPT3001 I<sup>2</sup>C スレーブ アドレスオプション

| 7 ビット バイナリ アドレス | 7 ビット Hex アドレス | ADDR ピンの終端 |

|-----------------|----------------|------------|

| 1000100b        | 0x44           | GND        |

| 1000101b        | 0x45           | VDD        |

| 1000110b        | 0x46           | SDA        |

| 1000111b        | 0x47           | SCL        |

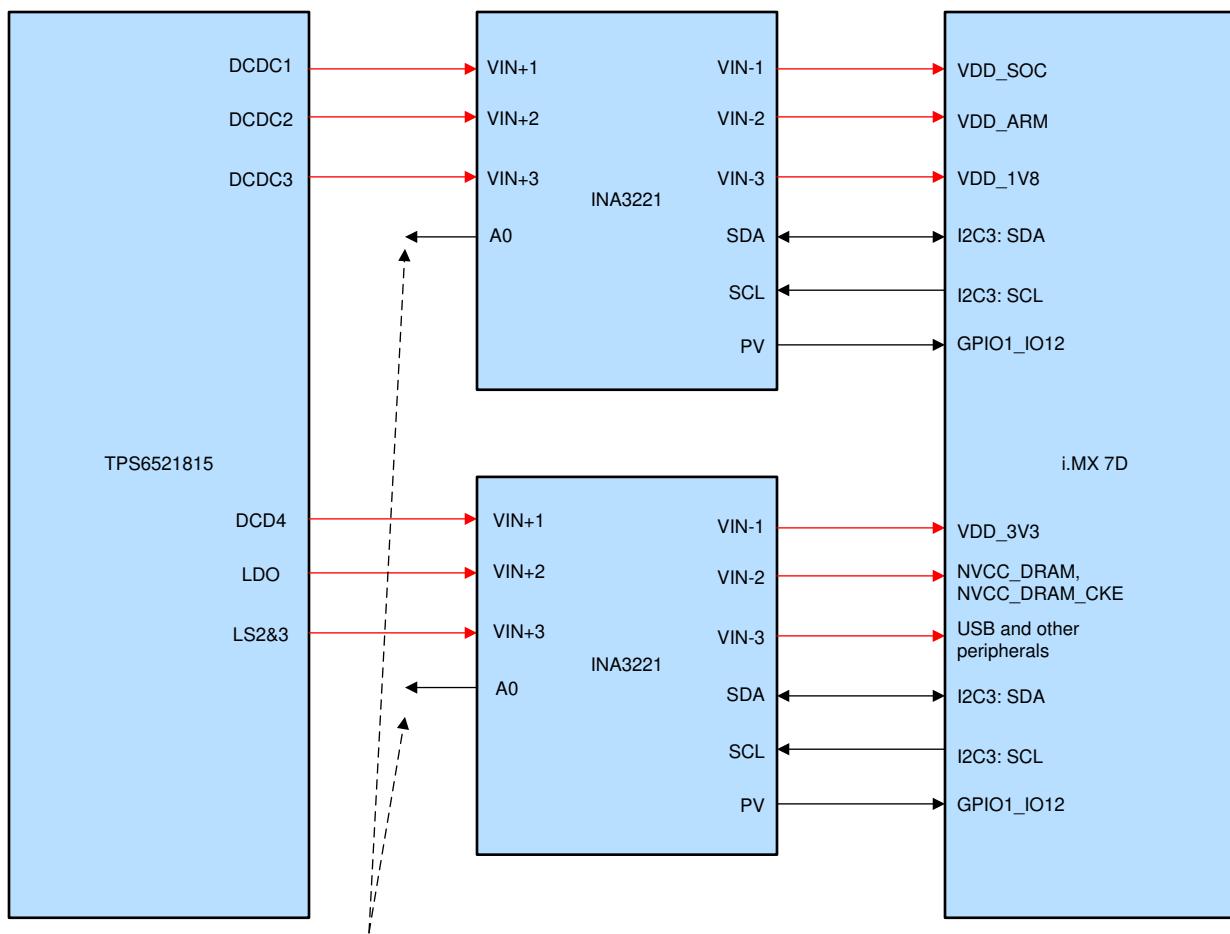

### 2.3.5 INA3221 - 電流監視

電流の情報を測定するため、このデザインの「電力」セクションに電流センス回路が内蔵されています。電流は、INA3221 デバイスを使用して検出されます。TPS6521815 PMIC 電源レールをすべて監視するために使用されるデバイスは 2 つあります。配線を図 2-15 に示します。INA3221 デバイスのアドレスピン A0 は、表 2-2 に従って終端する必要があります。

These pins require pull-up or pull-down resistors to set the I<sup>2</sup>C slave address

図 2-15. INA3221 電流センサ、PMIC からプロセッサへの配線

表 2-2. INA3221 I<sup>2</sup>C スレーブ アドレスオプション

| 7 ビット バイナリ アドレス | 7 ビット HEX アドレス | ADDR ピンの終端     |

|-----------------|----------------|----------------|

| 1000000b        | 0x40           | GND            |

| 1000001b        | 0x41           | V <sub>S</sub> |

| 1000010b        | 0x42           | SDA            |

| 1000011b        | 0x43           | SCL            |

### 2.3.6 TPS3808 リセット方式向け電圧スーパーバイザ

図 2-16 に、このプロジェクトのリセット方式を示します。TPS3808 電圧スーパーバイザは、コイン型電池からの VSNS 電圧を検出します。コイン電池が挿入されていない限り、TPS3808 スーパーバイザは PMIC の電源をオンにしません。これは、電源オンシーケンスが正しいことを確認するために重要です。

TPS3808 デバイスの入力 MR # は、RESET スイッチとプロセッサからのウォッチ ドッグに接続されています。いずれかの入力がデアサークトされると（ロジック low）、PMIC はディセーブルされます。すべての電力出力において、リセットおよび VSNVS が安定すると、PGOOD ピンはパワーオン リセット（POR\_B）をデアサークトします。

図 2-16. TPS3808 スーパーバイザによるリセット方法

### 2.3.7 TLV755P、TPS62067、TPS51200 補助電源

図 2-17 に、フルパワー アーキテクチャを示します。設計に追加される各ペリフェラル デバイスは、プロセッサでは必要としない追加の電圧レベルが必要な場合があります。この設計では、イーサネット PHY 用に 2.5V、MIPI CSI 用に 2.8V を追加する必要がありました。これらの電源レールは、TLV722P 固定電圧 LDO によって生成されます。

また、一部の設計では、プロセッサ電源と同じ電圧で 2 番目のレールに電力を供給するために、追加の電流を必要とします。この場合、mPCIe インターフェイスは、プロセッサやその他の周辺機器（Wi-Fi + Bluetooth、イーサネット、オーディオ コーデック、LCD、ALS、eMMC、NOR フラッシュ）への NVCC\_3V3 電源に割り当てられた 1.4A に加えて、最大 1A の電流を必要とする可能性があります。このため、mPCIe の 3V3\_PERI レールに電力を供給するために TPS62067 を追加しています。TPS62067 は、必要に応じてメイン NVCC\_3V3 レールと並列に配線することもできます。

最後に、DDR メモリを終了する必要がある場合があります。DDR 終端は、メイン電源（1.35V）の半分の電圧である電源（0.675V）を供給し、電流をシンクまたはソースできます。DDR の 1 つのチャネルのみを使用する場合、消費電流が低くなるか、配線がポイントツーポイントである場合は、均等にマッチングされた分圧器の中心をタップオフで十分です。それ

以外の場合は、DDR ターミネータが必要です。この設計では、TPS51200 デバイスを使用して、システム内の 2 つの DDR3L IC を終端しました。

図 2-17. TIDA-050034 フル パワー アーキテクチャ

## 2.4 システム設計理論

フル電源アーキテクチャは、基板上の IC および、基板に接続できるペリフェラルの消費電力を注意深く推定した結果です。TPS6521815 の電源シーケンスが正しいことを確認するため、i.MX 7D プロセッサで可能な限り最良の電源シーケンスを知る必要があります。I<sup>2</sup>C アドレスの競合が発生しないように、I<sup>2</sup>C チェーンを完全に描く必要があります。ブートモードの設定は、意図したメモリストレージ IC を使用してプロセッサをブートするようにマッピングする必要があります。最後に、基板のレイアウトが妥当であることを確認するために、PCB フロア プランニングを行う必要があります。このセクションでは、このシステム設計理論すべてを考慮します。

### 2.4.1 電力推定

このデザインは、5V アダプタから電力を供給されます。この 5V が、TPS6521815 デバイスの主電源です。PMIC は、5 つの異なる電圧を生成します。1.0V/1.1V、動的電圧スケーリング (DVS)、1.8V、3.3V、1.35V、1.5V。ロードスイッチ LS2 と LS3 は、5.0V を供給する IC と USB に電力を供給するために使用されます。各レールの消費電流の推定値を表 2-3 に示します。

表 2-3. システム電力の推定

| 電圧 (V)   | 電源 IC、レール名       | 電源電流 (mA) | IC、レール名をロードします     | 電流 (mA)  | 電力 (mW) |

|----------|------------------|-----------|--------------------|----------|---------|

| 1/1.1    | TPS6521815、DCDC1 | 1800      | iMX7 VDD_ARM       | 500      | 550     |

|          |                  |           | iMX7 VDD_SOC       | 1000     | 1100    |

|          |                  |           | DP83867 VDD1P1     | 115      | 127     |

| 1.35     | TPS6521815、DCDC2 | 1800      | iMX7 NVCC_DRAM     | 85       | 115     |

|          |                  |           | DDR3L VDD/VDDQ     | 295      | 400     |

| 0.675    | TPS51200         | 3000      | iMX7 VREF          | 1        | 0.675   |

|          |                  |           | DDR3L VREF/VTT     | 295 (最大) | 200     |

| 1.8      | TPS6521815、DCDC3 | 1800      | iMX7 NVCC_1P8      | 625      | 1125    |

|          |                  |           | WL1831MOD Vxx      | 200      | 360     |

|          |                  |           | DP83867 VDDA1P8    | 50       | 90      |

|          |                  |           | MIPI CSI           | 350      | 630     |

| 1.5      | TPS6521815、LDO1  | 400       | mPCIe              | 250      | 375     |

| 3.3      | TPS6521815、DCDC4 | 1600      | i.MX7 NVCC_3V3     | 148      | 489     |

|          |                  |           | MTFC8GAKAJCN-1M WT | 150      | 495     |

|          |                  |           | MT25QL256          | 35       | 116     |

|          |                  |           | WL1831MOD          | 1105     | 3647    |

|          |                  |           | DP83867 VDDIO      | 50       | 165     |

|          |                  |           | OPT3001 VDD        | 0.0037   | 0.0122  |

|          |                  |           | MCP2562            | 0.5      | 1.65    |

|          |                  |           | WM8960CGEFL        | 16       | 53      |

| 3.3 (補助) | TPS62067         | 2000      | LCD                | 15       | 50      |

|          |                  |           | mPCIe              | 1000     | 3300    |

| 5        | TPS6521815、LS2/3 | 1820      | FTD2232D           | 31       | 155     |

|          |                  |           | 2x USB2 ポート        | 1000     | 5000    |

|          |                  |           | MCP2562            | 70       | 350     |

|          |                  |           | WM8960CGEFL        | 511      | 2555    |

|          |                  |           | LCD                | 未テスト     | -       |

| 2.5      | TLV75525P        | 500       | DP83867 VDDA2P5    | 86       | 215     |

| 2.8      | TLV75528PP       | 500       | MIPI CSI           | 350      | 980     |

|          |                  |           |                    | 推定総電力    | 23W     |

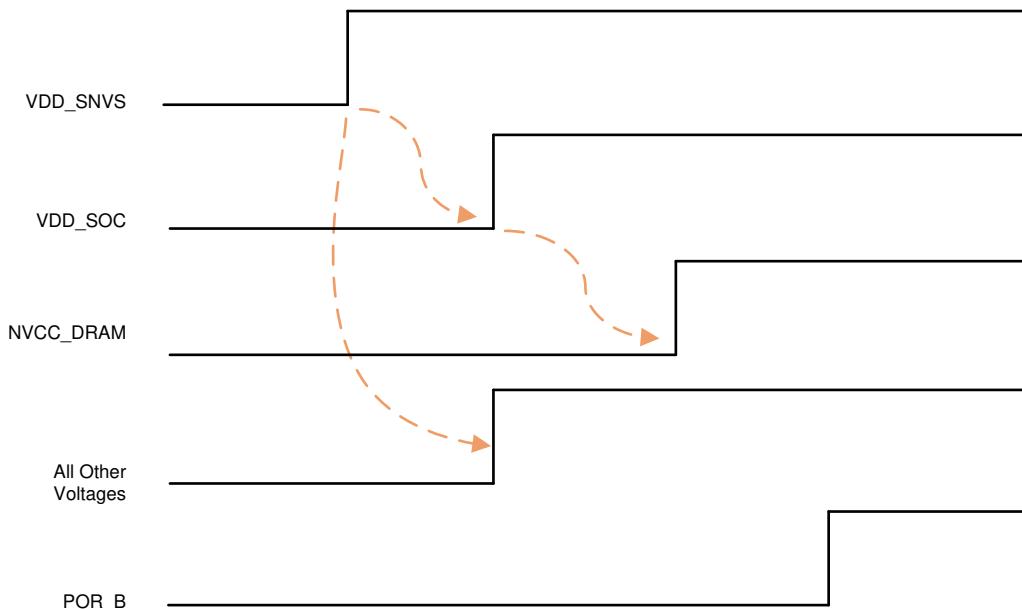

## 2.4.2 電源シーケンス

プロセッサー電源シーケンスを図 2-18 に示します。最初に、VDD\_SNVS は他の電源の前にオンにする必要があります。この設計では、VDD\_SNVS には、プロセッサー入力に直接接続されたコインセル経由で電力を供給します。SNVS 電圧が安定したら、NVCC\_DRAM および NVCC\_DRAM\_CKE を除く他のすべての電力をオンにできます。NVCC\_DRAM と NVCC\_CKE は、VDD\_SOC の後にのみ電源をオンにできます。これらの電圧が安定している場合、通常はパワーオンリセット (POR\_B) です。

図 2-18. i.MX 7D プロセッサーに必要な電源シーケンス

## 2.4.3 I<sup>2</sup>C デバイス チェーン

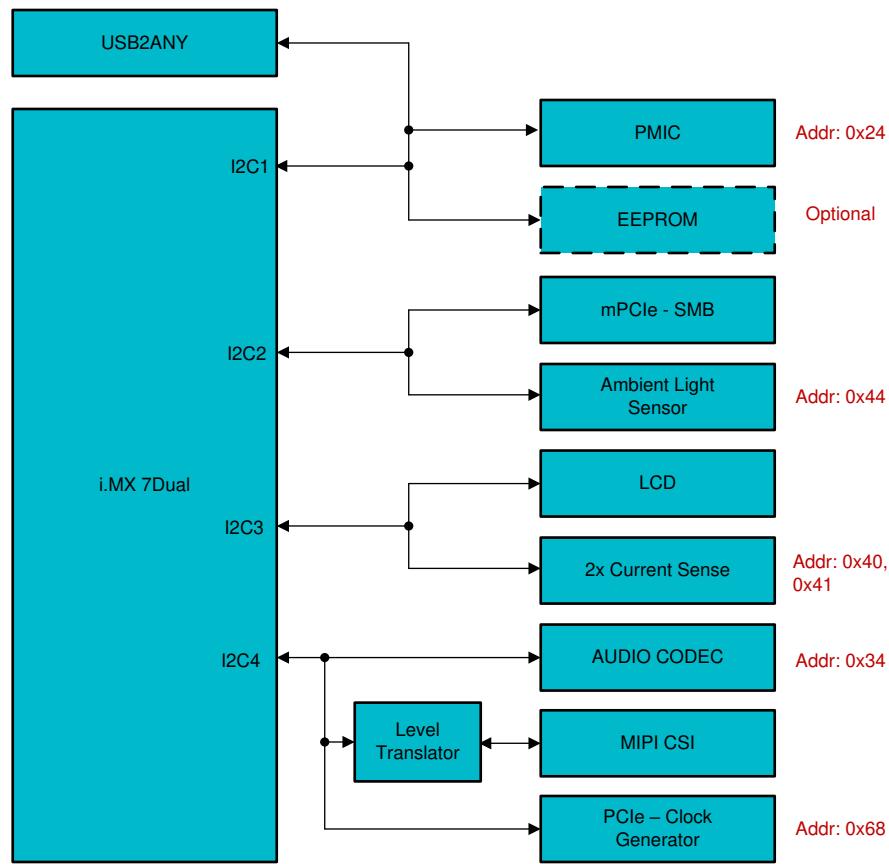

図 2-19 に、プロセッサーから各デバイスへの I<sup>2</sup>C チャネル マッピングを示します。

図 2-19. I<sup>2</sup>C デバイス チェーン

#### 2.4.4 クロック供給方式

各 IC と一致する必要なクロック周波数を以下に示します。

- i.MX 7Dual–24MHz および 32.768KHz

- PI6CFG201BZDIEX (クロック ジェネレータ) – 25MHz

- WL1831 (Wi-Fi/BT) - 32.768KHz

- FT2232 (USB から UART へ) – 6MHz

- WM8960CGEFL/V-ND (オーディオ コーデック) – 24MHz

- DP83867CRRGZ (イーサネット PHY) – 25MHz

- MIPI CSI – 24MHz

#### 2.4.5 BOOT の構成

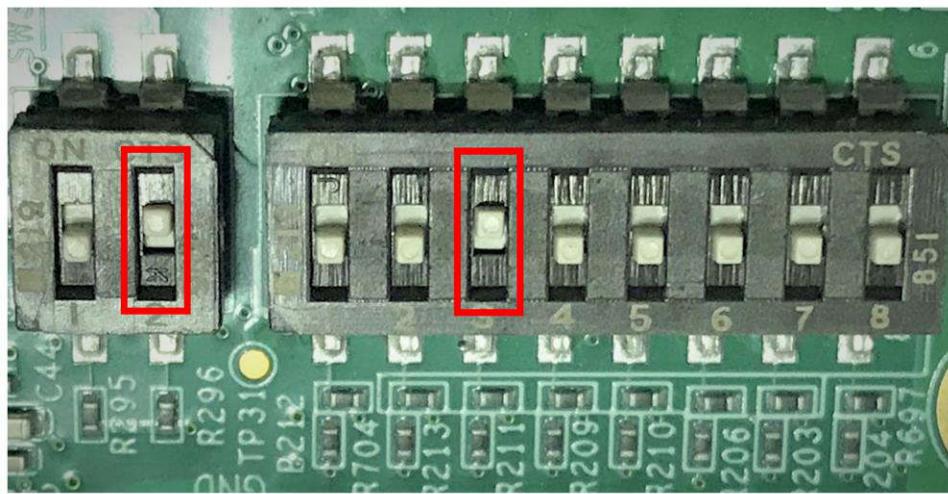

この設計では 2 つの BOOT 構成を使用します。SW3 DIP スイッチで制御されるブート モード ピンは、i.MX 7D プロセッサの専用の BOOT\_MODE0 および BOOT\_MODE1 入力ピンに接続されています。これに加えて、LCD データとピンを共有するブート構成を設定するための 20 の異なるピンがあります。これらの 20 ピンは、SW2 の 8 つの DIP スイッチによって制御されます。使用可能なブートオプションはすべて、表 2-4 (SW3) および 表 2-5 (SW2) に示しています。

表 2-4. SW3 ブート モード設定

| BOOT_MODE[1..0] | ビット 1 | ビット 0 |

|-----------------|-------|-------|

| ヒューズ            | 0     | 0     |

| シリアル ダウンロード     | 0     | 1     |

| 内蔵 BOOT         | 1     | 0     |

| テスト モード         | 1     | 1     |

**表 2-5. SW2 ブート モード設定**

| SW2、ピン 1            | SW2、ピン 2   | SW2、ピン 3   | SW2、ピン 4   | SW2、ピン 5                                            | SW2、ピン 6  | SW2、ピン 7                                                                                         | SW2、ピン 8  |

|---------------------|------------|------------|------------|-----------------------------------------------------|-----------|--------------------------------------------------------------------------------------------------|-----------|

| BT_CFG[14]          | BT_CFG[13] | BT_CFG[12] | BT_CFG[11] | BT_CFG[10]                                          | BT_CFG[6] | BT_CFG[5]                                                                                        | BT_CFG[4] |

| 001b = SD/eSD ブート   |            |            |            | ポートの選択:<br>00b=eSDHC1、<br>01b=eSDHC2、<br>10b=eSDHC3 |           | 0b                                                                                               | 0b        |

| 010b = MMC/eMMC ブート |            |            |            |                                                     |           | バス幅:<br>000b=1 ビット、001b=4 ビット、010b=8 ビット、<br>101b=4 ビット DDR (MMC4.4)、<br>110b=8 ビット DDR (MMC4.4) |           |

| 011b = NAND ブート     |            |            |            | ブロック内のページ:<br>00b=128、01b=64、10b=32、<br>11b=256     |           | BOOT_SEARCH_COUNT:<br>00b=2、01b=2、10b=4、11b=8                                                    | 0b        |

| 100b = QSPI ブート     |            |            |            | 0b                                                  | 0b        | 0b                                                                                               | 0b        |

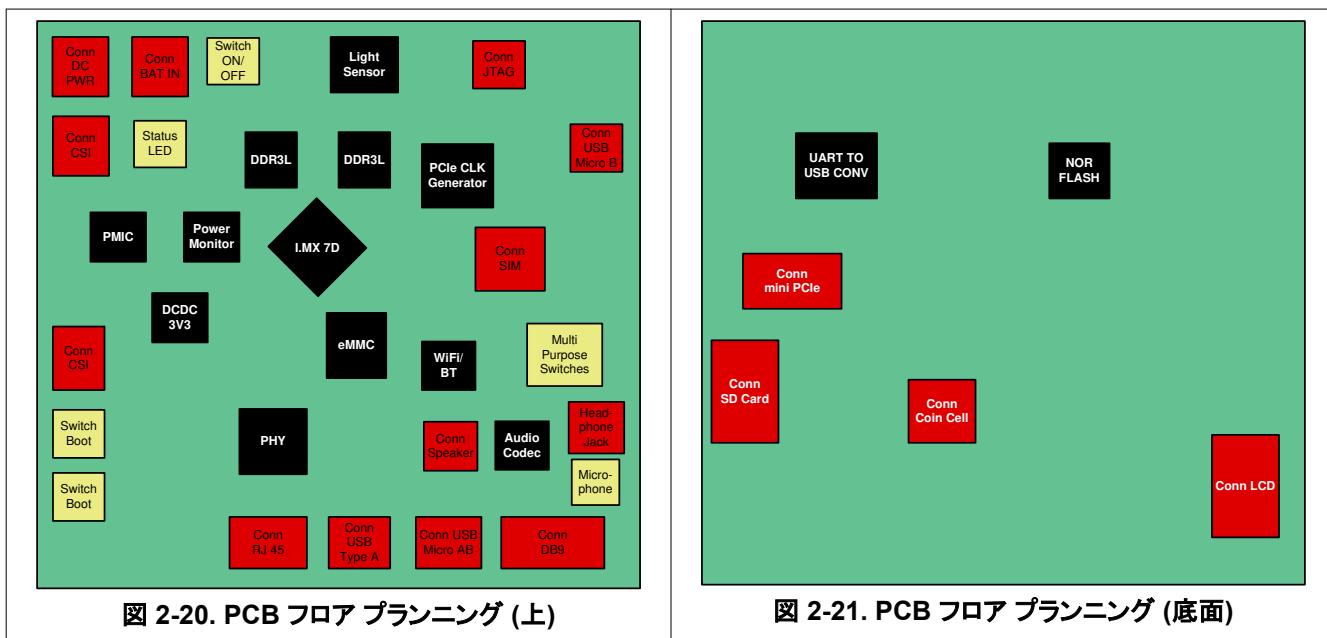

#### 2.4.6 PCB フロア計画

図 2-20 に PCB 上面のフロア計画を示し、図 2-21 に PCB の底面のフロア計画を示します。

### 3 使用開始、試験設定、および試験結果

#### 3.1 ハードウェアとソフトウェアで使用開始

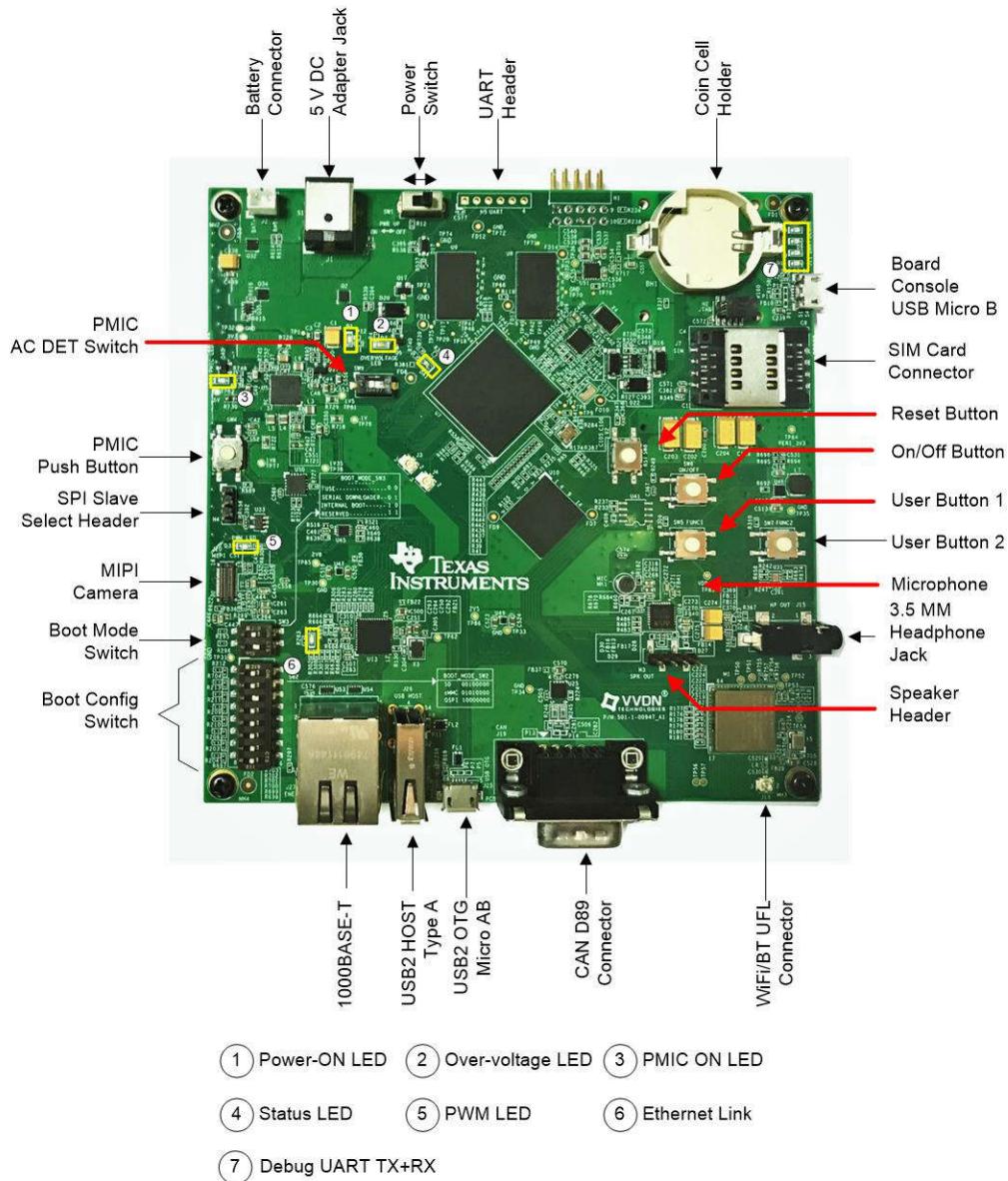

##### 3.1.1 ハードウェア

このセクションでは、TIDA-050034 基板の初期設定、電源投入オプション、ユーザー インターフェイスについて説明します。図 3-1 に、基板上のコネクタやスイッチの位置を確認するためのラベルを付けた完全に組み立てられた PCB の上面を示します。

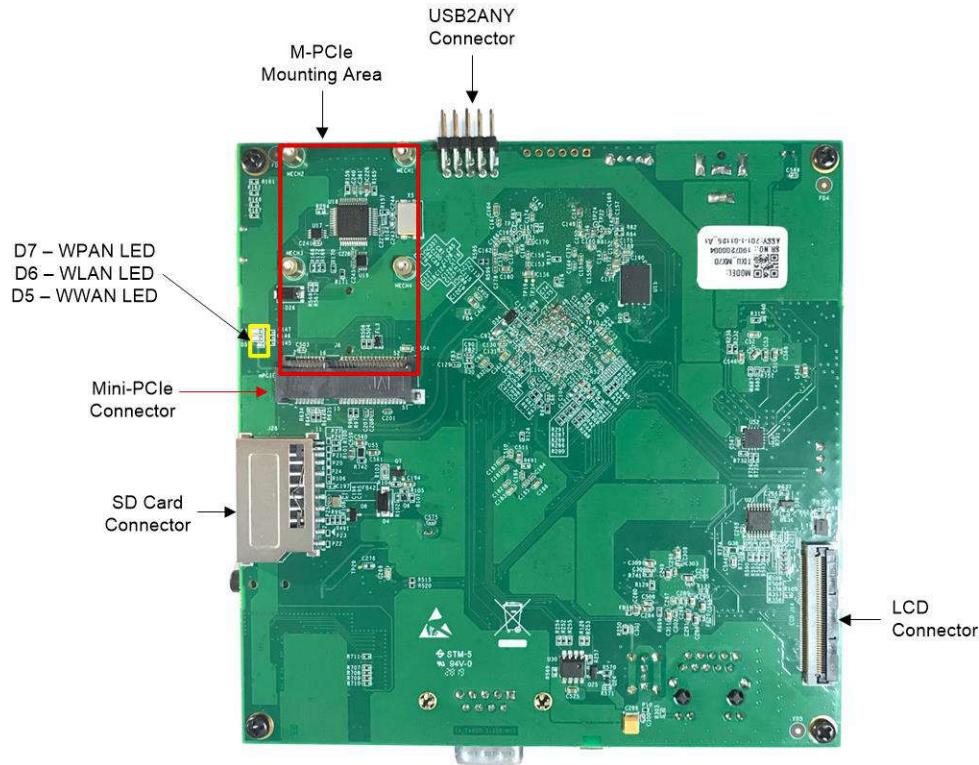

図 3-2 に、完全に組み立てられた PCB の底面にラベルを付けた状態を示します。

図 3-2. ラベル付き TIDA-050034 PCB の底面

以下の手順に従って、システムのハードウェアをセットアップします：

1. PCB の端にある 4 つの穴にネジを差し込んで、ボードにスタンドオフを取り付けます。

2. SW2/SW3 DIP スイッチを使用してブートオプションを設定します (図 3-3)。

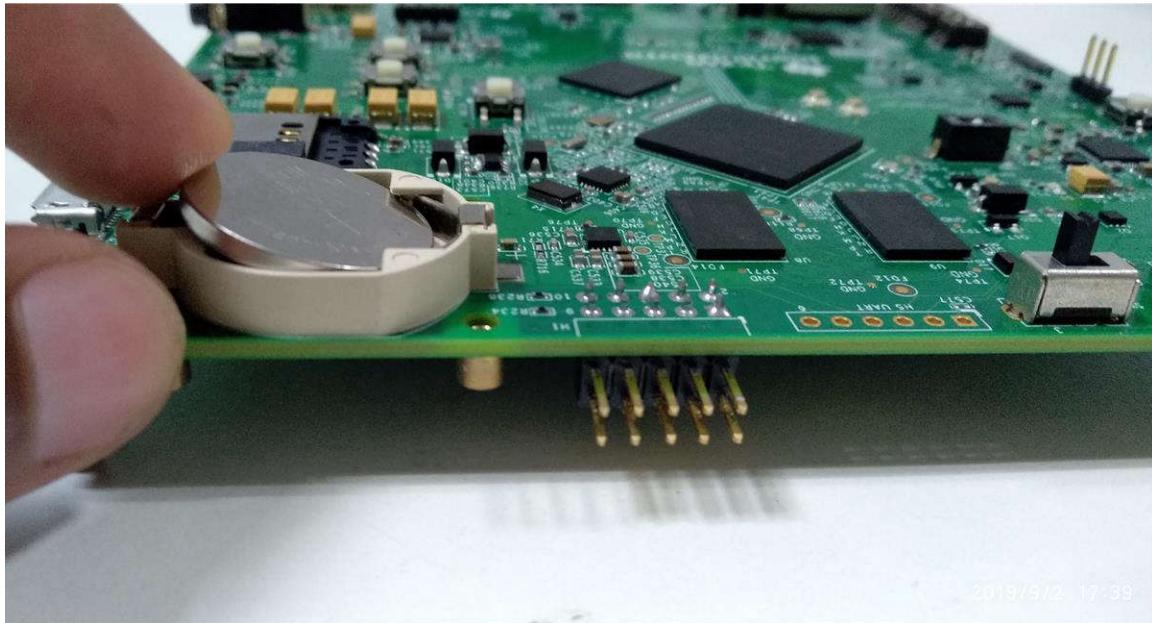

3. CR2032 コイン型電池をホルダー BH1(図 3-4) に挿入します。

4. SD カードを BOOT に使用する場合は、J28 コネクタに SD カードを挿入します (図 3-5)。

5. 端子ウインドウ (図 3-6) で UART デバッグのために USB micro-B ケーブルを J11 コネクタに挿入します。タイプ A プラグはコンピュータの USB ポートに接続します

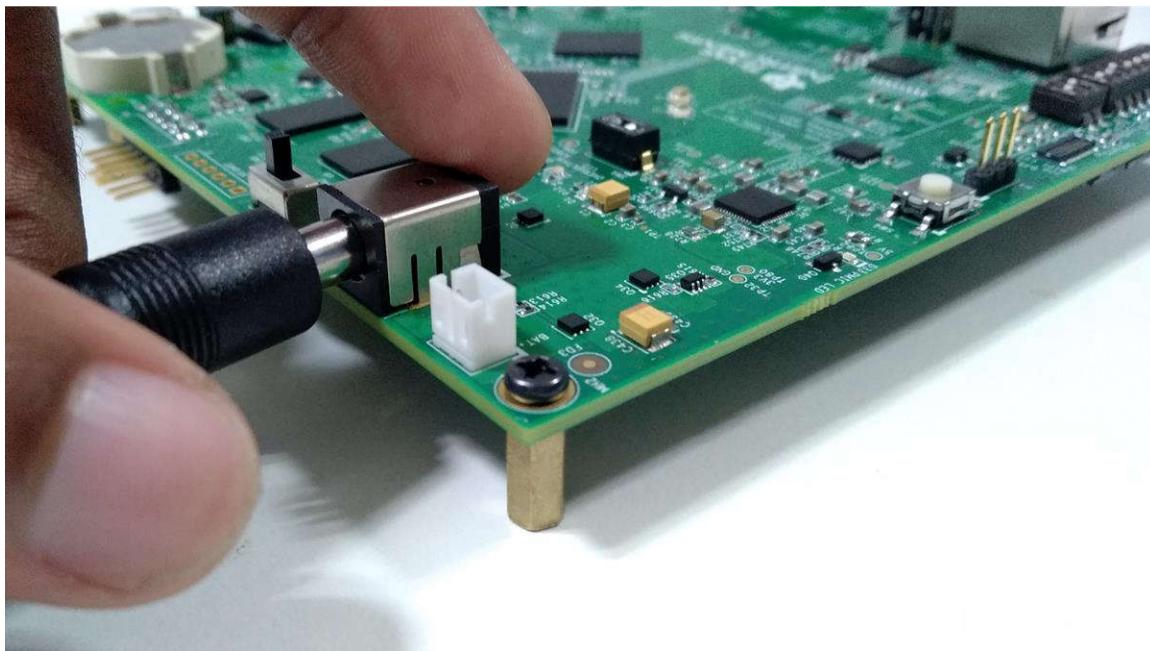

6. 電源 (図 3-7) を供給するために、5V DC アダプタ バレル ジャックを J1 コネクタに挿入します。推奨電源は、CUI Inc の SMI24-CUI-P6 5-V です。

7. SW1 を ON の位置に設定します。

8. BOOT が完了したら、必要なペリフェラルを接続します。次に例を示します。RJ-45 イーサネット (J27)、mini-PCIe (J8)、3.5mm ヘッドフォン ジャック (J15)、MIPI カメラ (J20)、LCD 画面 (J14)、USB デバイス (J26)。

□ Set these switches to ON state for SD Card boot

図 3-3. SD カードからのブート用に DIP スイッチ (SW2、SW3) を設定する

図 3-4. コイン型電池を BH1 に挿入します

注

スーパーバイザがシステムの電源をオンにするには、コイン型電池（公称 3.0V）の電圧が 2.4V を上回る必要があります。コイン型電池の電圧が低すぎる場合は、新しい電池に交換してテストを続行してください。

図 3-5. SD カードを J28 に挿入

図 3-6. micro-B ケーブルの J11 への挿入

---

### 注

ターミナル ウィンドウを使用して TIDA-050034 をデバッグする手順については、[セクション 3.1.2](#) を参照してください

図 3-7. J1 に 5V DC アダプタを挿入する

注

DC 出力電圧、電流定格、極性、パレル ジャック サイズ(内径と外径)が同等である場合は、SMI24-5-V-P6以外の電源 5-V を置き換えることができます。基板上に過電圧保護回路があり、IC の損傷を防止することを意図しているため、5.25V を超える DC 電圧の電源は許容されません。

注

TI は、DC アダプタ電源を取り外す前に、SW1 をオフ位置に切り替えて、常にシステムの電源をオフにすることを推奨しています。

### 3.1.1.1 オンボード LED 情報

表 3-1 に PCB に取り付けられたインジケータ LED を示し、TIDA-050034 リファレンス デザインを使いやすくするための簡単な説明を示します。

表 3-1. インジケータ LED

| 番号<br>(図 3-1 で) | 記号  | 説明              | 意味                                   |

|-----------------|-----|-----------------|--------------------------------------|

| 1               | D1  | 電源オン LED        | ON: 電源オン                             |

|                 |     |                 | OFF: 電源オフ                            |

| 2               | D2  | 過電圧 LED         | ON: 入力過電圧 ( $>5.25V$ )               |

|                 |     |                 | OFF: 入力電圧が推奨範囲内                      |

| 3               | D33 | PMIC オン LED     | ON: PGOOD は high (PMIC アクティブ)        |

|                 |     |                 | OFF: PGOOD は low (PMIC はアクティブ状態ではない) |

| 4               | DA1 | プロセッサ ステータス LED | RED ON: U-boot が実行中です                |

|                 |     |                 | LED OFF: U-Boot からカーネルへの移行           |

|                 |     |                 | 赤で点滅: カーネルが実行中です                     |

|                 |     |                 | GREEN ON: ファイル システムが実行中です            |

| 5               | D35 | PWM LED         | DIM: 周囲光の強度が低い                       |

|                 |     |                 | BRIGHT: 周囲光の強度が高い                    |

**表 3-1. インジケータ LED (続き)**

| 番号<br>(図 3-1 で) | 記号                              | 説明              | 意味                    |

|-----------------|---------------------------------|-----------------|-----------------------|

| 6               | D14                             | イーサネットリンク LED   | ON: イーサネットリンクが確立されました |

|                 |                                 |                 | OFF: イーサネットリンク ダウン    |

| 7               | D9、D8 (COMx)、D10、<br>D11 (COMy) | デバッグ UART TX/RX | D9 および D10 の点滅: 送信データ |

|                 |                                 |                 | D8 および D10 の点滅: 受信データ |

| N/A (下)         | D5、D6、D7                        | mini-PCIe LEDs  | WWAN                  |

|                 |                                 |                 | WLAN                  |

|                 |                                 |                 | WPAN                  |

### 3.1.2 ソフトウェア

TIDA-050034 のテストに使用した主なブートソースは SD カードです。テストの主な方法は、あらかじめビルドされたバイナリイメージを使用して SD カードを準備することです。このセクションの目的は、ソフトウェアを使用して開始することです。使用するソフトウェアが、PCB の正しいスロットに挿入された SD カードにすでに書き込まれており、ブートスイッチが適切に設定されていることを想定しています。

テストに使用したソフトウェアは、組込み Linux Yocto であり、TI のすべての IC 向けに記述されたドライバとパッチを使用して、NXP i.MX 7D プロセッサ向けに記述された元の SDK を変更します。イメージのビルドとインストールを行うには、Ubuntu 16.04 (またはそれ以降)、120GB HDD、完全に組み立てられた TIDA-050034 ボード、micro-SD カード、micro-SD ~ SD カード アダプタ、micro-USB ケーブル、5V DC 電源を動作させる必要があります。ソフトウェア イメージのビルドおよびインストール手順は、このマニュアルでは説明しません。

#### 3.1.2.1 TIDA-050034 のブート

SD カードをボードに付属している SD カードスロットに挿入し、ブートスイッチを SD カードからブートするように設定します。設定されたブートソースに実行可能ファイルが見つからない場合、ソフトウェアは自動的に SD カードからフェッチされます。

USB ケーブルの micro-B 側をボードのデバッグポートに、Type-A 側をホスト PC に接続します。このステップでのボード上の接続は図 3-8 のようになります。

図 3-8. USB 経由でデバッグを行う SD カードからのブートのボード接続

ホスト PC で Windows が実行されている場合は、TeraTerm または Putty を使用して端末を開き、デバイス ノードからデバッグ ログを取得します。FTDI チップのデバイスマネージャにある COMxx ポートに従ってポート番号を変更します。PC と TIDA-050034 ボードの間には 1 本の USB ケーブルのみを接続していますが、2 つの (2) COMxx ポートが使用できます。

たとえば、このボードをテストする場合、ポートレート **115200** の **COM7** または **COM8** ポートを選択し、他の **Putty** 設定をデフォルトオプションのままにします。

基板の電源を入れたときにデバッグ印刷が行われる場合は、そのインターフェイスは機能しています。ログ オンするように求められたら、「root」と入力して **Enter** キーを押します。

```

timx7d login: root

root@timx7d:~#

```

作成時点では、TIDA-050034 の最新のソフトウェア / フームウェア バージョンは **1.1.0\_1** であり、シンプルな Linux コマンドを使って確認できます。

```

root@timx7d:~# fw-version

firmware version : 1.1.0_1

```

TIDA-050034 の電源と消費電力のテストに役立つ他にも、多くの Linux 機能とコマンドがあります。次のセクションでは、いくつか例を紹介します。

### 3.1.2.2 TIDA-050034 をテストするための Linux コマンドの例

バス上にどの I<sup>2</sup>C デバイスがあるかを確認するには、「0」はチャネル 0 の I<sup>2</sup>C デバイスを探していることを意味します (TPS6521815 は、ここでは 0x24 と想定されているため)。

```

root@timx7d:~# i2cdetect -y -r 0

0   1   2   3   4   5   6   7   8   9   a   b   c   d   e   f

```

|     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|-----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| 00: | -- | -- | -- | -- | -- | -- | -- | -- | -- | -- | -- | -- | -- | -- | -- |

| 10: | -- | -- | -- | -- | -- | -- | -- | -- | -- | -- | -- | -- | -- | -- | -- |

| 20: | -- | -- | -- | -- | -- | -- | -- | -- | -- | -- | -- | -- | -- | -- | -- |

| 30: | -- | -- | -- | -- | -- | -- | -- | -- | -- | -- | -- | -- | -- | -- | -- |

| 40: | -- | -- | -- | -- | -- | -- | -- | -- | -- | -- | -- | -- | -- | -- | -- |

| 50: | -- | -- | -- | -- | -- | -- | -- | -- | -- | -- | -- | -- | -- | -- | -- |

| 60: | -- | -- | -- | -- | -- | -- | -- | -- | -- | -- | -- | -- | -- | -- | -- |

| 70: | -- | -- | -- | -- | -- | -- | -- | -- | -- | -- | -- | -- | -- | -- | -- |

室内の照明を点灯した状態で周囲光センサの読み取り値をテストし、ライトを消灯した状態で再度読み取ります。

```

root@timx7d:~# test_als

lux value : 384.000000

root@timx7d:~# test_als

lux value : 16.020000

```

プロセッサの CPU 周波数に対して PMIC にとって動的電圧スケーリングが機能することを確認するために、792MHz は DCDC1 = 1.0V、996MHz は DCDC1 = 1.1V に対応します。

```

root@timx7d:~# echo userspace > /sys/devices/system/cpu/cpu0/cpufreq/scaling_governor

root@timx7d:~# echo 996000 > /sys/devices/system/cpu/cpu0/cpufreq/scaling_setspeed

root@timx7d:~# echo 792000 > /sys/devices/system/cpu/cpu0/cpufreq/scaling_setspeed

```

電流センサ アプリケーションを動作させて、TPS6521815 PMIC から出力される任意のレールの電流を測定するには、最初のプロンプトの「1」は電流センサ IC #1、2 番目のプロンプトの「1」はチャネル 1、「curr1\_input」は、VDD\_ARM および VDD\_SOC レールで使用されている 248mA の値を返します。

```

root@timx7d:~# test_currentsensor

Enter current sensor no[1-2]: 1

Enter voltage Level[1-3]: 1

/*****************************************/

/*          CURRENT SENSOR2           */

/* Location of node:/sys/bus/i2c/devices/2-0040/hwmon/h1mon1/ */

/*****************************************/

/* ===== */

/*          VDD_SOC_ARM           */

/* ===== */

curr1_crit : 16380 mA

curr1_crit_alarm : 0

curr1_input : 248 mA

curr1_max : 16380 mA

curr1_max_alarm : 0

in1_input : 1104 mV

/*****************************************/

```

TIDA-050034 のテスト用に特別に書かれたその他の便利な機能が、iMX 用 Yocto ビルドの一部として含まれる数千もの事前定義済み Linux コマンドに加えて、多くの機能があります。プロセッサのストレステストと PMIC のテストに負荷電流の増加に最も便利なのは、「[stress-ng](#)」です。Linux コマンドの詳細については、[Ubuntu マニュアル](#)を参照してください。

## 4 デザイン ファイル

### 4.1 回路図

回路図をダウンロードするには、[TIDA-050034](#) のデザイン ファイルを参照してください。

### 4.2 部品表

部品表 (BOM) をダウンロードするには、[TIDA-050034](#) のデザイン ファイルを参照してください。

### 4.3 CAD ファイル

CAD ファイルをダウンロードするには、[TIDA-050034](#) のデザイン ファイルを参照してください。

### 4.4 ガーバー ファイル

ガーバー ファイルをダウンロードするには、[TIDA-050034](#) のデザイン ファイルを参照してください。

### 4.5 アセンブリの図面

アセンブリの図面をダウンロードするには、[TIDA-050034](#) のデザイン ファイルを参照してください。

## 5 ソフトウェア ファイル

ソフトウェア ファイルをダウンロードするには、[TIDA-050034](#) のデザイン ファイルを参照してください。

## 6 ドキュメントのサポート

1. テキサス インスツルメンツ、[TPS6521815 ユーザー プログラマブル電源管理 IC \(PMIC\)、6 つの DC/DC コンバータ、1 つの LDO、および 3 つのロードスイッチ付きデータシート](#)

2. テキサス インスツルメンツ、『[TPS6521815 PMIC による NXP i.MX 7 プロセッサへの電力供給』技術ノート](#)

3. 『[MCIMX7SABRE :i.MX 7Dual アプリケーションプロセッサをベースとするスマート デバイス向け SABRE ボード](#)

4. [Ubuntu のマニュアルページリポジトリ](#)

5. [Yocto Project ホーム ページ](#)

### 6.1 商標

テキサス・インスツルメンツの™ is a trademark of Texas Instruments.

NXP® is a registered trademark of NXP B.V.

Wi-Fi® is a registered trademark of Wi-Fi Alliance.

Bluetooth® is a registered trademark of Bluetooth SIG, Inc.

ヒロセ® is a registered trademark of Hirose Electric Co., Ltd.

Arm® and Cortex® are registered trademarks of Arm Limited.

Micron® is a registered trademark of Micron Technology, Inc.

PCI Express® is a registered trademark of PCI-SIG.

すべての商標は、それぞれの所有者に帰属します。

HDMI、HDMI High-Definition Multimedia Interface、HDMI トレードドレス、および HDMI ロゴは、HDMI Licensing Administrator Inc. の商標または登録商標です。

## 7 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| Changes from Revision A (December 2019) to Revision B (November 2025) | Page |

|-----------------------------------------------------------------------|------|

| ドキュメント全体にわたって表、図、相互参照の採番方法を更新。 .....                                  | 1    |

| HDMI 商標情報を追加。 .....                                                   | 1    |

## A プロセッサ ピン マッピング

### A.1 i.MX 7Dual ピン マッピング

次の表に、i.MX 7Dual プロセッサの各ピンのマッピングの詳細なリストを示します。

**表 A-1. i.MX 7D ピン マッピング**

| ピン   | ペリフェラル | 信号           | ルート          | 電力グループ             | 方向      |

|------|--------|--------------|--------------|--------------------|---------|

| AD14 | MMDC   | dram_data_13 | DRAM_DATA13  | NVCC_DRAM (0V)     | 出力      |

| AC14 | MMDC   | dram_cas_b   | DRAM_CAS_B   | NVCC_DRAM (0V)     | 出力      |

| AB14 | MMDC   | dram_sdwe_b  | DRAM_SDWE_B  | NVCC_DRAM (0V)     | 出力      |

| AA14 | MMDC   | dram_odt_1   | DRAM_ODT1    | NVCC_DRAM (0V)     | 出力      |

| AE14 | MMDC   | dram_data_08 | DRAM_DATA08  | NVCC_DRAM (0V)     | 出力      |

| AB15 | MMDC   | dram_ras_b   | DRAM_RAS_B   | NVCC_DRAM (0V)     | 出力      |

| AD15 | MMDC   | dram_sdqs1_p | DRAM_SDQS1_P | NVCC_DRAM (0V)     | 入力 / 出力 |

| AE15 | MMDC   | dram_sdqs1_n | DRAM_SDQS1_N | NVCC_DRAM (0V)     | 入力 / 出力 |

| AB16 | MMDC   | dram_addr_01 | DRAM_ADDR01  | NVCC_DRAM (0V)     | 出力      |

| AC16 | MMDC   | dram_odt_0   | DRAM_ODT0    | NVCC_DRAM (0V)     | 出力      |

| AD16 | MMDC   | dram_data_11 | DRAM_DATA11  | NVCC_DRAM (0V)     | 出力      |

| AE16 | MMDC   | dram_data_12 | DRAM_DATA12  | NVCC_DRAM (0V)     | 出力      |

| AB17 | MMDC   | dram_sdcke_0 | DRAM_SDCKE0  | NVCC_DRAM_CKE (0V) | 出力      |

| AD17 | MMDC   | dram_dqm_1   | DRAM_DQM1    | NVCC_DRAM (0V)     | 出力      |

| AE17 | MMDC   | dram_data_10 | DRAM_DATA10  | NVCC_DRAM (0V)     | 出力      |

| AB18 | MMDC   | dram_addr_14 | DRAM_ADDR14  | NVCC_DRAM (0V)     | 出力      |

| AC18 | MMDC   | dram_addr_02 | DRAM_ADDR02  | NVCC_DRAM (0V)     | 出力      |

| AD18 | MMDC   | dram_data_06 | DRAM_DATA06  | NVCC_DRAM (0V)     | 出力      |

| AE18 | MMDC   | dram_data_09 | DRAM_DATA09  | NVCC_DRAM (0V)     | 出力      |

| AB19 | MMDC   | dram_addr_00 | DRAM_ADDR00  | NVCC_DRAM (0V)     | 出力      |

| AD19 | MMDC   | dram_data_05 | DRAM_DATA05  | NVCC_DRAM (0V)     | 出力      |

| AE19 | MMDC   | dram_data_07 | DRAM_DATA07  | NVCC_DRAM (0V)     | 出力      |

| AB20 | MMDC   | dram_addr_15 | DRAM_ADDR15  | NVCC_DRAM (0V)     | 出力      |

| AC20 | MMDC   | dram_addr_03 | DRAM_ADDR03  | NVCC_DRAM (0V)     | 出力      |

| AD20 | MMDC   | dram_dqm_0   | DRAM_DQM0    | NVCC_DRAM (0V)     | 出力      |

| AE20 | MMDC   | dram_data_02 | DRAM_DATA02  | NVCC_DRAM (0V)     | 出力      |

| AB21 | MMDC   | dram_addr_04 | DRAM_ADDR04  | NVCC_DRAM (0V)     | 出力      |

| AD21 | MMDC   | dram_sdqs0_n | DRAM_SDQS0_N | NVCC_DRAM (0V)     | 入力 / 出力 |

| AE21 | MMDC   | dram_sdqs0_p | DRAM_SDQS0_P | NVCC_DRAM (0V)     | 入力 / 出力 |

| P22  | MMDC   | dram_sdba_1  | DRAM_SDBA1   | NVCC_DRAM (0V)     | 出力      |

| R22  | MMDC   | dram_sdba_0  | DRAM_SDBA0   | NVCC_DRAM (0V)     | 出力      |

| T22  | MMDC   | dram_addr_12 | DRAM_ADDR12  | NVCC_DRAM (0V)     | 出力      |

| U22  | MMDC   | dram_addr_11 | DRAM_ADDR11  | NVCC_DRAM (0V)     | 出力      |

| V22  | MMDC   | dram_addr_06 | DRAM_ADDR06  | NVCC_DRAM (0V)     | 出力      |

| W22  | MMDC   | dram_addr_08 | DRAM_ADDR08  | NVCC_DRAM (0V)     | 出力      |

| Y22  | MMDC   | dram_addr_07 | DRAM_ADDR07  | NVCC_DRAM (0V)     | 出力      |

| AA22 | MMDC   | dram_cs1_b   | DRAM_CS1_B   | NVCC_DRAM (0V)     | 出力      |

| AB22 | MMDC   | dram_sdcke_1 | DRAM_SDCKE1  | NVCC_DRAM_CKE (0V) | 出力      |

| AC22 | MMDC   | dram_reset   | DRAM_RESET   | NVCC_DRAM_CKE (0V) | 出力      |

| AD22 | MMDC   | dram_data_00 | DRAM_DATA00  | NVCC_DRAM (0V)     | 出力      |

**表 A-1. i.MX 7D ピン マッピング (続き)**

| ピン   | ペリフェラル | 信号            | ルート           | 電力グループ           | 方向      |

|------|--------|---------------|---------------|------------------|---------|

| AE22 | MMDC   | dram_data_04  | DRAM_DATA04   | NVCC_DRAM (0V)   | 出力      |

| N23  | MMDC   | dram_sdba_2   | DRAM_SDBA2    | NVCC_DRAM (0V)   | 出力      |

| P23  | MMDC   | dram_addr_13  | DRAM_ADDR13   | NVCC_DRAM (0V)   | 出力      |

| T23  | MMDC   | dram_addr_10  | DRAM_ADDR10   | NVCC_DRAM (0V)   | 出力      |

| V23  | MMDC   | dram_addr_09  | DRAM_ADDR09   | NVCC_DRAM (0V)   | 出力      |

| Y23  | MMDC   | dram_addr_05  | DRAM_ADDR05   | NVCC_DRAM (0V)   | 出力      |

| AB23 | MMDC   | dram_cs0_b    | DRAM_CS0_B    | NVCC_DRAM (0V)   | 出力      |

| AD23 | MMDC   | dram_data_01  | DRAM_DATA01   | NVCC_DRAM (0V)   | 出力      |

| AE23 | MMDC   | dram_data_03  | DRAM_DATA03   | NVCC_DRAM (0V)   | 出力      |

| N24  | MMDC   | dram_data_25  | DRAM_DATA25   | NVCC_DRAM (0V)   | 出力      |

| P24  | MMDC   | dram_dqm_3    | DRAM_DQM3     | NVCC_DRAM (0V)   | 出力      |

| R24  | MMDC   | dram_data_29  | DRAM_DATA29   | NVCC_DRAM (0V)   | 出力      |

| T24  | MMDC   | dram_sdqs3_p  | DRAM_SDQS3_P  | NVCC_DRAM (0V)   | 入力 / 出力 |

| U24  | MMDC   | dram_data_30  | DRAM_DATA30   | NVCC_DRAM (0V)   | 出力      |

| V24  | MMDC   | dram_data_31  | DRAM_DATA31   | NVCC_DRAM (0V)   | 出力      |

| W24  | MMDC   | dram_data_17  | DRAM_DATA17   | NVCC_DRAM (0V)   | 出力      |

| Y24  | MMDC   | dram_sdqs2_p  | DRAM_SDQS2_P  | NVCC_DRAM (0V)   | 入力 / 出力 |

| AA24 | MMDC   | dram_dqm_2    | DRAM_DQM2     | NVCC_DRAM (0V)   | 出力      |

| AB24 | MMDC   | dram_data_22  | DRAM_DATA22   | NVCC_DRAM (0V)   | 出力      |

| AC24 | MMDC   | dram_data_23  | DRAM_DATA23   | NVCC_DRAM (0V)   | 出力      |

| AD24 | MMDC   | dram_sdclk0_p | DRAM_SDCLK0_P | NVCC_DRAM (0V)   | 出力      |

| N25  | MMDC   | dram_data_27  | DRAM_DATA27   | NVCC_DRAM (0V)   | 出力      |

| P25  | MMDC   | dram_data_26  | DRAM_DATA26   | NVCC_DRAM (0V)   | 出力      |

| R25  | MMDC   | dram_data_24  | DRAM_DATA24   | NVCC_DRAM (0V)   | 出力      |

| T25  | MMDC   | dram_sdqs3_n  | DRAM_SDQS3_N  | NVCC_DRAM (0V)   | 入力 / 出力 |

| U25  | MMDC   | dram_data_28  | DRAM_DATA28   | NVCC_DRAM (0V)   | 出力      |

| V25  | MMDC   | dram_data_18  | DRAM_DATA18   | NVCC_DRAM (0V)   | 出力      |

| W25  | MMDC   | dram_data_19  | DRAM_DATA19   | NVCC_DRAM (0V)   | 出力      |

| Y25  | MMDC   | dram_sdqs2_n  | DRAM_SDQS2_N  | NVCC_DRAM (0V)   | 入力 / 出力 |

| AA25 | MMDC   | dram_data_16  | DRAM_DATA16   | NVCC_DRAM (0V)   | 出力      |

| AB25 | MMDC   | dram_data_21  | DRAM_DATA21   | NVCC_DRAM (0V)   | 出力      |

| AC25 | MMDC   | dram_data_20  | DRAM_DATA20   | NVCC_DRAM (0V)   | 出力      |

| AD25 | MMDC   | dram_sdclk0_n | DRAM_SDCLK0_N | NVCC_DRAM (0V)   | 出力      |

| AB13 | MMDC   | dram_zqpad    | DRAM_ZQPAD    | NVCC_DRAM (0V)   | 入力      |

| AC13 | MMDC   | dram_vref     | DRAM_VREF     | DRAM_VREF (0V)   | 入力      |

| AD13 | MMDC   | dram_data_14  | DRAM_DATA14   | NVCC_DRAM (0V)   | 出力      |

| AE13 | MMDC   | dram_data_15  | DRAM_DATA15   | NVCC_DRAM (0V)   | 出力      |

| T1   | ENET1  | enet_mdc      | GPIO1_IO11    | NVCC_GPIO2 (0 V) | 出力      |

| R5   | ENET1  | enet_mdio     | GPIO1_IO10    | NVCC_GPIO2 (0 V) | 入力 / 出力 |

| F14  | ENET1  | rgmii_rd_1    | ENET1_RDATA1  | NVCC_ENET1 (0 V) | 入力      |

| E14  | ENET1  | rgmii_rd_0    | ENET1_RDATA0  | NVCC_ENET1 (0 V) | 入力      |

| D13  | ENET1  | rgmii_rd_2    | ENET1_RDATA2  | NVCC_ENET1 (0 V) | 入力      |

| E13  | ENET1  | rgmii_rd_3    | ENET1_RDATA3  | NVCC_ENET1 (0 V) | 入力      |

| F16  | ENET1  | rgmii_txc     | ENET1_TXC     | NVCC_ENET1 (0 V) | 出力      |

| E16  | ENET1  | rgmii_tx_ctl  | ENET1_TX_CTL  | NVCC_ENET1 (0 V) | 出力      |

**表 A-1. i.MX 7D ピン マッピング (続き)**

| ピン  | ペリフェラル | 信号            | ルート          | 電力グループ           | 方向      |

|-----|--------|---------------|--------------|------------------|---------|

| F15 | ENET1  | rgmii_rx_c    | ENET1_RXC    | NVCC_ENET1 (0 V) | 入力      |

| E15 | ENET1  | rgmii_rx_ctl  | ENET1_RX_CTL | NVCC_ENET1 (0 V) | 入力      |

| F17 | ENET1  | rgmii_td_0    | ENET1_TDATA0 | NVCC_ENET1 (0 V) | 出力      |

| E17 | ENET1  | rgmii_td_1    | ENET1_TDATA1 | NVCC_ENET1 (0 V) | 出力      |

| E18 | ENET1  | rgmii_td_2    | ENET1_TDATA2 | NVCC_ENET1 (0 V) | 出力      |

| D18 | ENET1  | rgmii_td_3    | ENET1_TDATA3 | NVCC_ENET1 (0 V) | 出力      |

| P21 | QSPI   | qspi_a_data_1 | EPDC1_DATA01 | NVCC_EPDC1 (0 V) | 入力 / 出力 |

| N20 | QSPI   | qspi_a_data_2 | EPDC1_DATA02 | NVCC_EPDC1 (0 V) | 入力 / 出力 |

| N21 | QSPI   | qspi_a_data_3 | EPDC1_DATA03 | NVCC_EPDC1 (0 V) | 入力 / 出力 |

| M20 | QSPI   | qspi_a_sclk   | EPDC1_DATA05 | NVCC_EPDC1 (0 V) | 出力      |

| M21 | QSPI   | qspi_a_ss0_b  | EPDC1_DATA06 | NVCC_EPDC1 (0 V) | 出力      |

| M23 | QSPI   | qspi_b_data_0 | EPDC1_DATA08 | NVCC_EPDC1 (0 V) | 入力 / 出力 |

| L25 | QSPI   | qspi_b_data_1 | EPDC1_DATA09 | NVCC_EPDC1 (0 V) | 入力 / 出力 |

| A5  | uSDHC1 | sd_data_0     | SD1_DATA0    | NVCC_SD1 (0 V)   | 入力 / 出力 |

| D6  | uSDHC1 | sd_data_1     | SD1_DATA1    | NVCC_SD1 (0 V)   | 入力 / 出力 |

| A4  | uSDHC1 | sd_data_2     | SD1_DATA2    | NVCC_SD1 (0 V)   | 入力 / 出力 |

| D5  | uSDHC1 | sd_data_3     | SD1_DATA3    | NVCC_SD1 (0 V)   | 入力 / 出力 |

| C5  | uSDHC1 | sd_cmd        | SD1_CMD      | NVCC_SD1 (0 V)   | 入力 / 出力 |

| B5  | uSDHC1 | sd_clk        | SD1_CLK      | NVCC_SD1 (0 V)   | 出力      |

| C6  | uSDHC1 | sd_cd_b       | SD1_CD_B     | NVCC_SD1 (0 V)   | 入力      |

| B4  | uSDHC1 | sd_reset_b    | SD1_RESET_B  | NVCC_SD1 (0 V)   | 出力      |

| C4  | uSDHC1 | sd_wp         | SD1_WP       | NVCC_SD1 (0 V)   | 入力      |

| L3  | UART1  | uart_rx_data  | UART1_RXD    | NVCC_UART (0V)   | 入力      |

| L4  | UART1  | uart_tx_data  | UART1_TXD    | NVCC_UART (0V)   | 出力      |

| L5  | UART2  | uart_rx_data  | UART2_RXD    | NVCC_UART (0V)   | 入力      |

| L6  | UART2  | uart_tx_data  | UART2_TXD    | NVCC_UART (0V)   | 出力      |

| H3  | UART6  | uart_rx_data  | ECSPI1_SCLK  | NVCC_SPI (0V)    | 入力      |

| H4  | UART6  | uart_rts_b    | ECSPI1_MISO  | NVCC_SPI (0V)    | 入力      |

| G5  | UART6  | uart_tx_data  | ECSPI1莫斯     | NVCC_SPI (0V)    | 出力      |

| H5  | UART6  | uart_cts_b    | ECSPI1_SS0   | NVCC_SPI (0V)    | 出力      |

| E20 | ELCDIF | lcd_clk       | LCD1_CLK     | NVCC_LCD (0V)    | 入力      |

| F25 | ELCDIF | lcd_enable    | LCD1_ENABLE  | NVCC_LCD (0V)    | 入力 / 出力 |

| E25 | ELCDIF | lcd_hsync     | LCD1_HSYNC   | NVCC_LCD (0V)    | 入力      |

| F24 | ELCDIF | lcd_vsync     | LCD1_VSYNC   | NVCC_LCD (0V)    | 入力      |

| C21 | ELCDIF | lcd_rs        | LCD1_RESET   | NVCC_LCD (0V)    | 出力      |

| D21 | ELCDIF | lcd_data_00   | LCD1_DATA00  | NVCC_LCD (0V)    | 入力 / 出力 |

| A22 | ELCDIF | lcd_data_01   | LCD1_DATA01  | NVCC_LCD (0V)    | 入力 / 出力 |

| B22 | ELCDIF | lcd_data_02   | LCD1_DATA02  | NVCC_LCD (0V)    | 入力 / 出力 |

| A23 | ELCDIF | lcd_data_03   | LCD1_DATA03  | NVCC_LCD (0V)    | 入力 / 出力 |

| C22 | ELCDIF | lcd_data_04   | LCD1_DATA04  | NVCC_LCD (0V)    | 入力 / 出力 |

| B23 | ELCDIF | lcd_data_05   | LCD1_DATA05  | NVCC_LCD (0V)    | 入力 / 出力 |

| A24 | ELCDIF | lcd_data_06   | LCD1_DATA06  | NVCC_LCD (0V)    | 入力 / 出力 |

| F20 | ELCDIF | lcd_data_07   | LCD1_DATA07  | NVCC_LCD (0V)    | 入力 / 出力 |

| E21 | ELCDIF | lcd_data_08   | LCD1_DATA08  | NVCC_LCD (0V)    | 入力 / 出力 |

| C23 | ELCDIF | lcd_data_09   | LCD1_DATA09  | NVCC_LCD (0V)    | 入力 / 出力 |

**表 A-1. i.MX 7D ピン マッピング (続き)**

| ピン  | ペリフェラル | 信号          | ルート          | 電力グループ           | 方向      |

|-----|--------|-------------|--------------|------------------|---------|

| B24 | ELCDIF | lcd_data_10 | LCD1_DATA10  | NVCC_LCD (0V)    | 入力 / 出力 |

| G20 | ELCDIF | lcd_data_11 | LCD1_DATA11  | NVCC_LCD (0V)    | 入力 / 出力 |

| F21 | ELCDIF | lcd_data_12 | LCD1_DATA12  | NVCC_LCD (0V)    | 入力 / 出力 |

| E22 | ELCDIF | lcd_data_13 | LCD1_DATA13  | NVCC_LCD (0V)    | 入力 / 出力 |

| D23 | ELCDIF | lcd_data_14 | LCD1_DATA14  | NVCC_LCD (0V)    | 入力 / 出力 |

| C24 | ELCDIF | lcd_data_15 | LCD1_DATA15  | NVCC_LCD (0V)    | 入力 / 出力 |

| B25 | ELCDIF | lcd_data_16 | LCD1_DATA16  | NVCC_LCD (0V)    | 入力 / 出力 |

| G21 | ELCDIF | lcd_data_17 | LCD1_DATA17  | NVCC_LCD (0V)    | 入力 / 出力 |

| E23 | ELCDIF | lcd_data_18 | LCD1_DATA18  | NVCC_LCD (0V)    | 入力 / 出力 |

| D24 | ELCDIF | lcd_data_19 | LCD1_DATA19  | NVCC_LCD (0V)    | 入力 / 出力 |

| C25 | ELCDIF | lcd_data_20 | LCD1_DATA20  | NVCC_LCD (0V)    | 入力 / 出力 |

| E24 | ELCDIF | lcd_data_21 | LCD1_DATA21  | NVCC_LCD (0V)    | 入力 / 出力 |

| D25 | ELCDIF | lcd_data_22 | LCD1_DATA22  | NVCC_LCD (0V)    | 入力 / 出力 |

| G23 | ELCDIF | lcd_data_23 | LCD1_DATA23  | NVCC_LCD (0V)    | 入力 / 出力 |

| E3  | uSDHC2 | sd_clk      | SD2_CLK      | NVCC_SD2 (0 V)   | 出力      |

| F6  | uSDHC2 | sd_cmd      | SD2_CMD      | NVCC_SD2 (0 V)   | 入力 / 出力 |

| E4  | uSDHC2 | sd_data_0   | SD2_DATA0    | NVCC_SD2 (0 V)   | 入力 / 出力 |

| E5  | uSDHC2 | sd_data_1   | SD2_DATA1    | NVCC_SD2 (0 V)   | 入力 / 出力 |

| F5  | uSDHC2 | sd_data_2   | SD2_DATA2    | NVCC_SD2 (0 V)   | 入力 / 出力 |

| E6  | uSDHC2 | sd_data_3   | SD2_DATA3    | NVCC_SD2 (0 V)   | 入力 / 出力 |

| D3  | uSDHC2 | sd_cd_b     | SD2_CD_B     | NVCC_SD2 (0 V)   | 入力      |

| C1  | uSDHC3 | sd_clk      | SD3_CLK      | NVCC_SD3 (0 V)   | 出力      |

| E1  | uSDHC3 | sd_cmd      | SD3_CMD      | NVCC_SD3 (0 V)   | 入力 / 出力 |

| B2  | uSDHC3 | sd_data_0   | SD3_DATA0    | NVCC_SD3 (0 V)   | 入力 / 出力 |

| A2  | uSDHC3 | sd_data_1   | SD3_DATA1    | NVCC_SD3 (0 V)   | 入力 / 出力 |

| G2  | uSDHC3 | sd_data_2   | SD3_DATA2    | NVCC_SD3 (0 V)   | 入力 / 出力 |

| F1  | uSDHC3 | sd_data_3   | SD3_DATA3    | NVCC_SD3 (0 V)   | 入力 / 出力 |

| F2  | uSDHC3 | sd_data_4   | SD3_DATA4    | NVCC_SD3 (0 V)   | 入力 / 出力 |

| E2  | uSDHC3 | sd_data_5   | SD3_DATA5    | NVCC_SD3 (0 V)   | 入力 / 出力 |

| C2  | uSDHC3 | sd_data_6   | SD3_DATA6    | NVCC_SD3 (0 V)   | 入力 / 出力 |

| B1  | uSDHC3 | sd_data_7   | SD3_DATA7    | NVCC_SD3 (0 V)   | 入力 / 出力 |

| J1  | uSDHC3 | sd_strobe   | SD3_STROBE   | NVCC_SD3 (0 V)   | 出力      |

| G1  | uSDHC3 | sd_reset_b  | SD3_RESET_B  | NVCC_SD3 (0 V)   | 出力      |

| K24 | GPIO2  | gpio_io_28  | EPDC1_BDR0   | NVCC_EPDC2 (0 V) | 指定なし    |

| D15 | SAI1   | sai_tx_bclk | ENET1_RX_CLK | NVCC_ENET1 (0 V) | 出力      |

| D16 | SAI1   | sai_rx_data | ENET1_TX_CLK | NVCC_ENET1 (0 V) | 入力      |

| D19 | SAI1   | sai_tx_data | ENET1_COL    | NVCC_ENET1 (0 V) | 出力      |

| E19 | SAI1   | sai_tx_sync | ENET1_CRS    | NVCC_ENET1 (0 V) | 入力 / 出力 |

| E10 | SAI1   | sai_mclk    | SAI1_MCLK    | NVCC_SAI (0V)    | 出力      |

| J2  | I2C1   | i2c_scl     | I2C1_SCL     | NVCC_I2C (0 V)   | 入力 / 出力 |

| K1  | I2C1   | i2c_sda     | I2C1_SDA     | NVCC_I2C (0 V)   | 入力 / 出力 |

| K2  | I2C2   | i2c_scl     | I2C2_SCL     | NVCC_I2C (0 V)   | 入力 / 出力 |

| K3  | I2C2   | i2c_sda     | I2C2_SDA     | NVCC_I2C (0 V)   | 入力 / 出力 |

| K5  | I2C3   | i2c_scl     | I2C3_SCL     | NVCC_I2C (0 V)   | 入力 / 出力 |

**表 A-1. i.MX 7D ピン マッピング (続き)**

| ピン   | ペリフェラル      | 信号               | ルート              | 電力グループ                   | 方向      |

|------|-------------|------------------|------------------|--------------------------|---------|

| K6   | I2C3        | i2c_sda          | I2C3_SDA         | NVCC_I2C (0 V)           | 入力 / 出力 |

| B8   | USB         | usb_otg1_dp      | USB_OTG1_DP      | USB_OTG1_VDDA_3P3 (0 V)  | 入力 / 出力 |

| A8   | USB         | usb_otg1_dn      | USB_OTG1_DN      | USB_OTG1_VDDA_3P3 (0 V)  | 入力 / 出力 |

| B7   | USB         | usb_otg1_id      | USB_OTG1_ID      | USB_OTG1_VDDA_3P3 (0 V)  | 入力      |

| C7   | USB         | usb_otg1_chd_b   | USB_OTG1_CHD_B   | USB_OTG1_VDDA_3P3 (0 V)  | 入力 / 出力 |

| A7   | USB         | usb_otg1_rext    | USB_OTG1_REXT    | USB_OTG1_VDDA_3P3 (0 V)  | 入力 / 出力 |

| B10  | USB         | usb_otg2_dp      | USB_OTG2_DP      | USB_OTG2_VDDA_3P3 (0 V)  | 入力 / 出力 |

| A10  | USB         | usb_otg2_dn      | USB_OTG2_DN      | USB_OTG2_VDDA_3P3 (0 V)  | 入力 / 出力 |

| B11  | USB         | usb_otg2_id      | USB_OTG2_ID      | USB_OTG2_VDDA_3P3 (0 V)  | 入力      |

| A11  | USB         | usb_otg2_rext    | USB_OTG2_REXT    | USB_OTG2_VDDA_3P3 (0 V)  | 入力 / 出力 |

| A12  | USB         | usb_h_data       | USB_H_DATA       | USB_H_VDD_1P2 (0 V)      | 入力 / 出力 |

| B12  | USB         | usb_h_strobe     | USB_H_STROBE     | USB_H_VDD_1P2 (0 V)      | 入力 / 出力 |

| T6   | FLEXCAN2    | flexcan_tx       | GPIO1_IO15       | NVCC_GPIO2 (0 V)         | 出力      |

| T5   | FLEXCAN2    | flexcan_rx       | GPIO1_IO14       | NVCC_GPIO2 (0 V)         | 入力      |

| L20  | GPIO2       | gpio_io_14       | EPDC1_DATA14     | NVCC_EPDC1 (0 V)         | 指定なし    |

| P20  | QSPI        | qspi_a_data_0    | EPDC1_DATA00     | NVCC_EPDC1 (0 V)         | 入力 / 出力 |

| AC10 | PCIE        | pcie_refclkout_n | PCIE_REFCLKOUT_N | PCIE_VPH (0V)            | 出力      |

| AB10 | PCIE        | pcie_refclkout_p | PCIE_REFCLKOUT_P | PCIE_VPH (0V)            | 出力      |

| AD10 | PCIE        | pcie_refclkin_p  | PCIE_REFCLKIN_P  | PCIE_VPH (0V)            | 入力      |

| AE10 | PCIE        | pcie_refclkin_n  | PCIE_REFCLKIN_N  | PCIE_VPH (0V)            | 入力      |

| AD11 | PCIE        | pcie_rx_p        | PCIE_RX_P        | PCIE_VPH_RX (0V)         | 入力      |

| AE11 | PCIE        | pcie_rx_n        | PCIE_RX_N        | PCIE_VPH_RX (0V)         | 入力      |

| AB11 | PCIE        | pcie_tx_p        | PCIE_TX_P        | PCIE_VPH_TX (0V)         | 出力      |

| AC11 | PCIE        | pcie_tx_n        | PCIE_TX_N        | PCIE_VPH_TX (0V)         | 出力      |

| AA13 | PCIE        | pcie_rext        | PCIE_REXT        | PCIE_VPH (0V)            | 入力 / 出力 |

| B15  | MIPI_CSI2   | mipi_csi_clk_p   | MIPI_CSI_CLK_P   | MIPI_VDDA_1P8 (0 V)      | 入力 / 出力 |

| A15  | MIPI_CSI2   | mipi_csi_clk_n   | MIPI_CSI_CLK_N   | MIPI_VDDA_1P8 (0 V)      | 入力 / 出力 |

| B16  | MIPI_CSI2   | mipi_csi_d0_p    | MIPI_CSI_D0_P    | MIPI_VDDA_1P8 (0 V)      | 入力 / 出力 |

| A16  | MIPI_CSI2   | mipi_csi_d0_n    | MIPI_CSI_D0_N    | MIPI_VDDA_1P8 (0 V)      | 入力 / 出力 |

| B14  | MIPI_CSI2   | mipi_csi_d1_p    | MIPI_CSI_D1_P    | MIPI_VDDA_1P8 (0 V)      | 入力 / 出力 |

| A14  | MIPI_CSI2   | mipi_csi_d1_n    | MIPI_CSI_D1_N    | MIPI_VDDA_1P8 (0 V)      | 入力 / 出力 |

| AE6  | XTALOSC     | rtc_xtali        | RTC_XTALI        | VDD_SNVS_1P8_CAP (0 V)   | 入力      |

| AD6  | XTALOSC     | rtc_xtalo        | RTC_XTALO        | VDD_SNVS_1P8_CAP (0 V)   | 出力      |

| V1   | XTALOSC     | xtali            | XTALI            | VDDA_1P8 (0 V)           | 入力      |

| V2   | XTALOSC     | xtalo            | XTALO            | VDDA_1P8 (0 V)           | 出力      |

| AC8  | XTALOSC     | onoff            | ONOFF            | VDD_SNVS_IN (0V)         | 入力      |

| AE4  | TEMPSENSO R | rext             | TEMPSENSOR_REXT  | VDD_TEMPSENSOR_1P8 (0 V) | 入力      |

| D12  | I2C4        | i2c_sda          | SAI1_RXC         | NVCC_SAI (0V)            | 入力 / 出力 |

| C12  | I2C4        | i2c_scl          | SAI1_RXFS        | NVCC_SAI (0V)            | 入力 / 出力 |

| G3   | GPIO5       | gpio_io_11       | SD2_RESET_B      | NVCC_SD2 (0 V)           | 指定なし    |

| C3   | GPIO5       | gpio_io_10       | SD2_WP           | NVCC_SD2 (0 V)           | 指定なし    |

| N1   | GPIO1       | gpio_io_00       | GPIO1_IO00       | NVCC_GPIO1 (0 V)         | 指定なし    |

| N2   | GPIO1       | gpio_io_01       | GPIO1_IO01       | NVCC_GPIO1 (0 V)         | 指定なし    |

| N3   | GPIO1       | gpio_io_02       | GPIO1_IO02       | NVCC_GPIO1 (0 V)         | 指定なし    |

表 A-1. i.MX 7D ピン マッピング (続き)

| ピン | ペリフェラル | 信号         | ルート         | 電力グループ        | 方向   |

|----|--------|------------|-------------|---------------|------|

| J6 | GPIO4  | gpio_io_23 | ECSPI2_SS0  | NVCC_SPI (0V) | 指定なし |

| G6 | GPIO4  | gpio_io_21 | ECSPI2_MOSI | NVCC_SPI (0V) | 指定なし |

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適した TI 製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月