## Design Guide: TIDA-010016

# 8 ポートの IO-Link® マスターのリファレンス デザイン

## 説明

高速なタイミングとサイクル時間が求められる PLC アプリケーションに対応するため、このリファレンス デザインでは 8 ポートの IO-Link® マスターを実装しています。これによりそのような要件を満たすシステムを実現できます。これを用いて、OPC UA、Profinet、EtherCAT、Ethernet IP への接続用リモート IO ゲートウェイを構築できます。PRU ベースのフレーム ハンドラにより、タイミングと時間同期を非常に柔軟に設定できます。この設計は、汎用性が高く拡張可能な IO-Link マスターの構築に役立ちます。

## リソース

|             |            |

|-------------|------------|

| TIDA-010016 | デザイン フォルダ  |

| TIOL111     | プロダクト フォルダ |

| INA253      | プロダクト フォルダ |

| TLC59282    | プロダクト フォルダ |

| LM5165      | プロダクト フォルダ |

| TPS4H160-Q1 | プロダクト フォルダ |

TI の TI E2E™ サポート・エキスパートにお問い合わせください。

## 特長

- 8 つの IO-Link ポート

- COM1、COM2、COM3 をサポート

- 400μs のサイクル タイムをサポート

- ポートごとに 500mA の電流

- すべてのポートに過電流保護および制限機能を搭載

- PRU フレーム ハンドラにより柔軟なタイミングが可能

## アプリケーション

- スタンドアロンのリモート IO

- 通信モジュール

TI の TI E2E™ サポート・エキスパートにお問い合わせください。

## 1 システムの説明

センサとアクチュエータはオートメーションの最も基本的なユニットであり、ネットワーク接続された複数のシステムに情報を供給し、それらのシステムからの命令に従って動作します。従来、センサやアクチュエータのようなデバイスは、インテリジェンスがごく限定的なインターフェイスを経由して制御ユニットに接続していました。その結果、交換できる構成情報や診断情報はごくわずか、または皆無でした。新しいデバイスを取り付けるには、使用する時点で手動の構成が必要だったほか、診断機能がないので、本当に必要なときに予知保全を実施することも不可能でした。

IO-Link (国際電気標準会議 [IEC] 61131-9) は、オープン規格をベースとするプロトコルであり、センサやアクチュエータのような小型デバイスに関するインテリジェント制御のニーズに対処します。この規格は、デバイスとマスターの間で低速のポイントツー ポイントシリアル通信を実現します。この場合のマスターは通常、フィールドバスや PLC に到達するためのゲートウェイとして機能します。接続の確立後にこのインテリジェントリンクを使用すると、データ交換、構成、診断を目的とする通信を容易に実施できます。

シールドなしの 3 線ケーブルは最大 20m の長さに対応し、一般的に M12 コネクタを両側に取り付けて、IO-Link 接続を確立します。データレートの範囲は最大 230kbps に達し、非同期の最小サイクル時間は 400μs +10% です。4 つの動作モードは、双方向の入出力 (I/O)、デジタル入力、デジタル出力、非アクティブ化に対応しています。セキュリティメカニズムとディタミニスティック (確定的) なデータ配信は規定されていません。IODD (IO Device Description, IO デバイス記述) というプロファイルは、通信プロパティ、デバイス パラメータ、ID (識別子) とプロセスと診断に関するデータ、デバイスとメーカーに関する固有の情報を保持しています。

IO-Link システムの多くの利点として、標準化済みの配線、データ可用性の向上、リモートの監視と構成、複数のデバイスのシンプルな置き換え、先進的な診断機能を挙げることができます。IO-Link を採用すると、ファクトリのマネージャは、センサからの更新情報を受け取り、今後の保守や交換に関する計画を立てることができます。交換を必要としているセンシング ユニットまたはアクチュエータ ユニットの交換と、PLC から IO-Link マスター経由での新しいユニットの構成を実施すると、手動のセットアップが不要になり、ダウンタイムを短縮できます。ファクトリの現場へ足を運ばずに、ある構成から他の構成へと製造をリモートで切り替えることができるので、製品のカスタマイズがいっそう容易になります。IO-Link は既存の標準的な I/O 設備と配線に対する上位互換性があるので、ファクトリは製造ラインを IO-Link に簡単にアップグレードすることができます。総合すると、これらの特長を活用して全体のコストを削減し、プロセスの効率と機械の可用性を向上させることができます。

### 1.1 主なシステム仕様

表 1-1. 主なシステム仕様

| パラメータ                          | 仕様                              | 詳細                          |

|--------------------------------|---------------------------------|-----------------------------|

| 入力電圧                           | 24V の外部電源                       | <a href="#">セクション 2.3.4</a> |

| 入力電流                           | 接続負荷により異なる (5A を推奨)             | <a href="#">セクション 2.3.4</a> |

| 出力電圧                           | 24V                             | <a href="#">セクション 2.3.3</a> |

| ポートあたりの出力電流                    | 500mA                           | <a href="#">セクション 2.3.3</a> |

| 合計出力電流                         | 4A                              | <a href="#">セクション 2.3.3</a> |

| IO-Link マスター ポートの数             | 8                               |                             |

| イーサネット ポートの数                   | 2                               |                             |

| 対応 I/O データレート                  | COM1, COM2, COM3                |                             |

| サポートされている IO-Link サイクル時間       | 400μs                           |                             |

| フレーム ハンドラ                      |                                 | <a href="#">セクション 2.4.1</a> |

| オーバーサンプリング係数                   | 8 倍                             |                             |

| サンプリング周波数                      | チャネルあたり最大 1.8432MSPS (COM3)     |                             |

| IO-Link 転送レートをサポート             | COM3, COM2, COM1                |                             |

| 等価ボーレート                        | 230.4kbaud, 38.4kbaud, 4.8kbaud |                             |

| RX バッファ サイズ                    | 128 バイト                         |                             |

| TX バッファ サイズ                    | 2 x 128 バイト (ダブル送信バッファ)         |                             |

| スタート ピットおよびピット フィルタ            | 参照テーブルに基づく (調整可能)               |                             |

| バリティ チェック                      | 対応                              |                             |

| T1 時間 (UART フレーム送信遅延、マスク)      | 0 Tbit                          |                             |

| T2 時間チェック (UART フレーム送信遅延、デバイス) | 対応、5 にハードコードさ                   |                             |

| Ta 時間チェック (最大応答時間)             | サポートされており、レジスタによりユーザーが調整可能      |                             |

## 2 システム概要

### 2.1 ブロック図

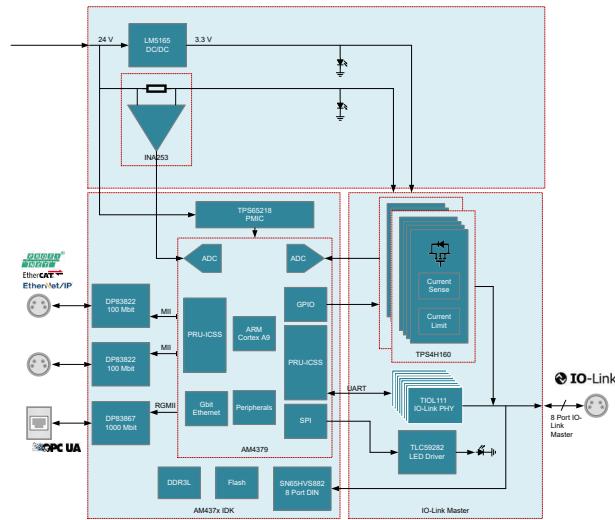

図 2-1. TIDA-010016 のブロック図

### 2.2 主な使用製品

このリファレンス デザインは、1枚の PCB 上で TIOL111、TPS4H160、TLC59282 を使用して、メイン IO-Link マスタ機能を処理します。LM5165 と INA253 と、IDK アダプタ ボードを使用して、電源と電流を監視します。

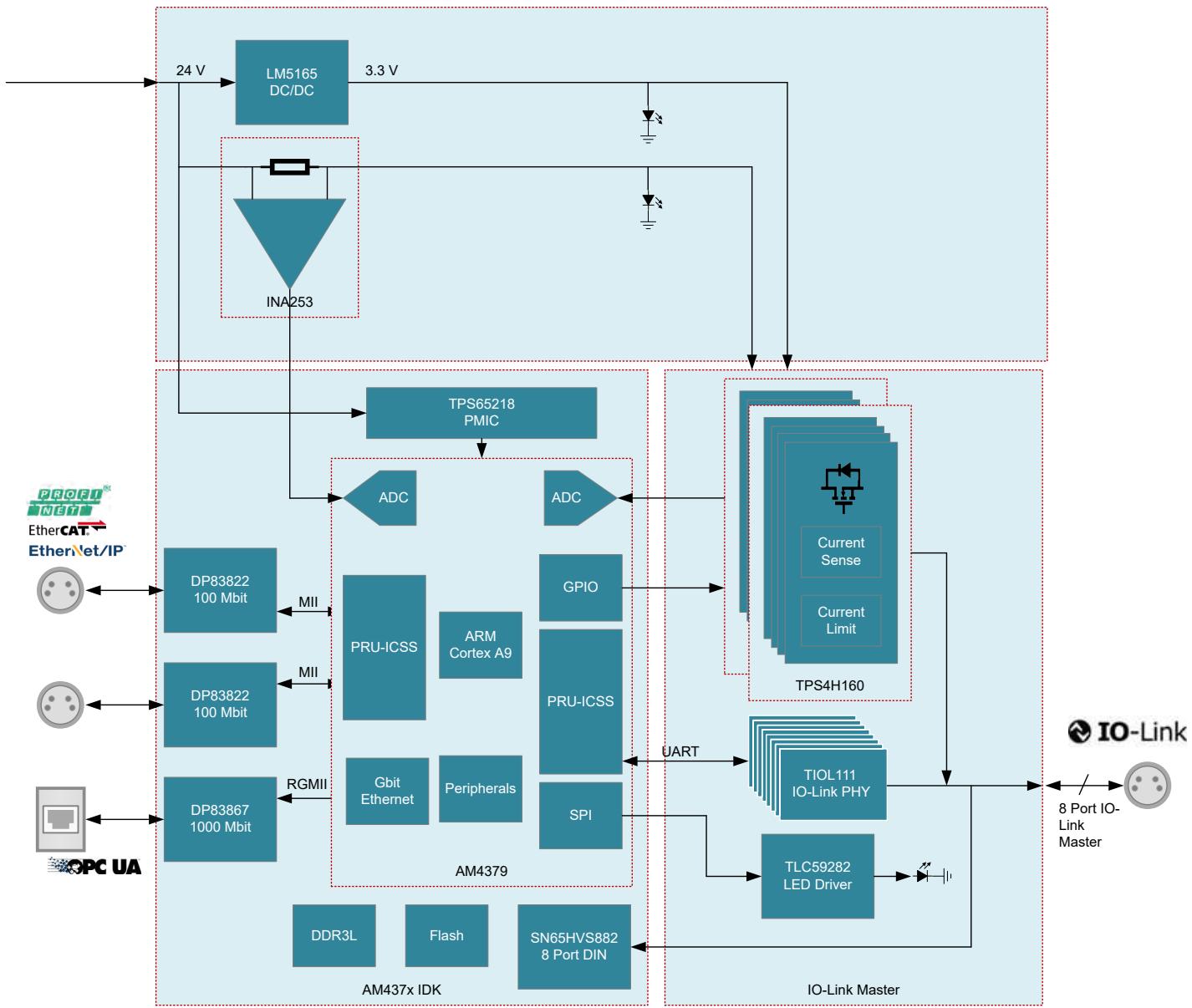

#### 2.2.1 LM5165

LM5165 コンバータは、3V から 65V の電源電圧で動作する、使いやすい同期整流型降圧 DC-DC レギュレータです。このデバイスは、3.3V、5V、12V、24V、48V の非安定化、準安定化、または完全安定化電源レールからの降圧変換を目的としています。ハイサイドおよびローサイドのパワー MOSFET を内蔵した LM5165 は、非常にコンパクトな構成で最大 150mA の DC 負荷電流を高効率かつ超低入力静止電流で供給します。シンプルな実装を目的として設計されており、

動作モードを選択することで、用途に応じて柔軟に最適化できます。低ノイズ、大電流、高速負荷応答が求められる用途に最適な定オ n 時間 (COT) モードでは、このデバイスは予測オ n 時間スイッチング パルスで動作します。オ n 時間を設定する際に入力電圧フィード フォワードを利用することで、入力電圧範囲全体にわたって準固定のスイッチング周波数が実現されます。また、調整可能なピーク電流制限機能を補完するパルス周波数変調 (PFM) モードを採用すると、軽負荷時に非常に優れた効率性能を実現できます。いずれの動作モードでも制御ループ補償が不要なため、設計時間を短縮でき、外付け部品の数も削減されます。

図 2-2. LM5165 のブロック図

この設計の主な特長を以下にまとめます:

- 広い入力電圧範囲: 3V~65V

- 3.3V 固定出力電圧

- 150mA 同期降圧コンバータ

- 2Ω の PMOS 降圧スイッチを内蔵

- 1Ω の NMOS 同期整流器を内蔵

- 外付け整流ダイオードが不要

- PFM または COT モードの動作を選択可能

- ループ補償やブートストラップ部品が不要

このデバイスを使用すると、広い入力電圧範囲に対応した小型電源ソリューションを容易に実装できます。

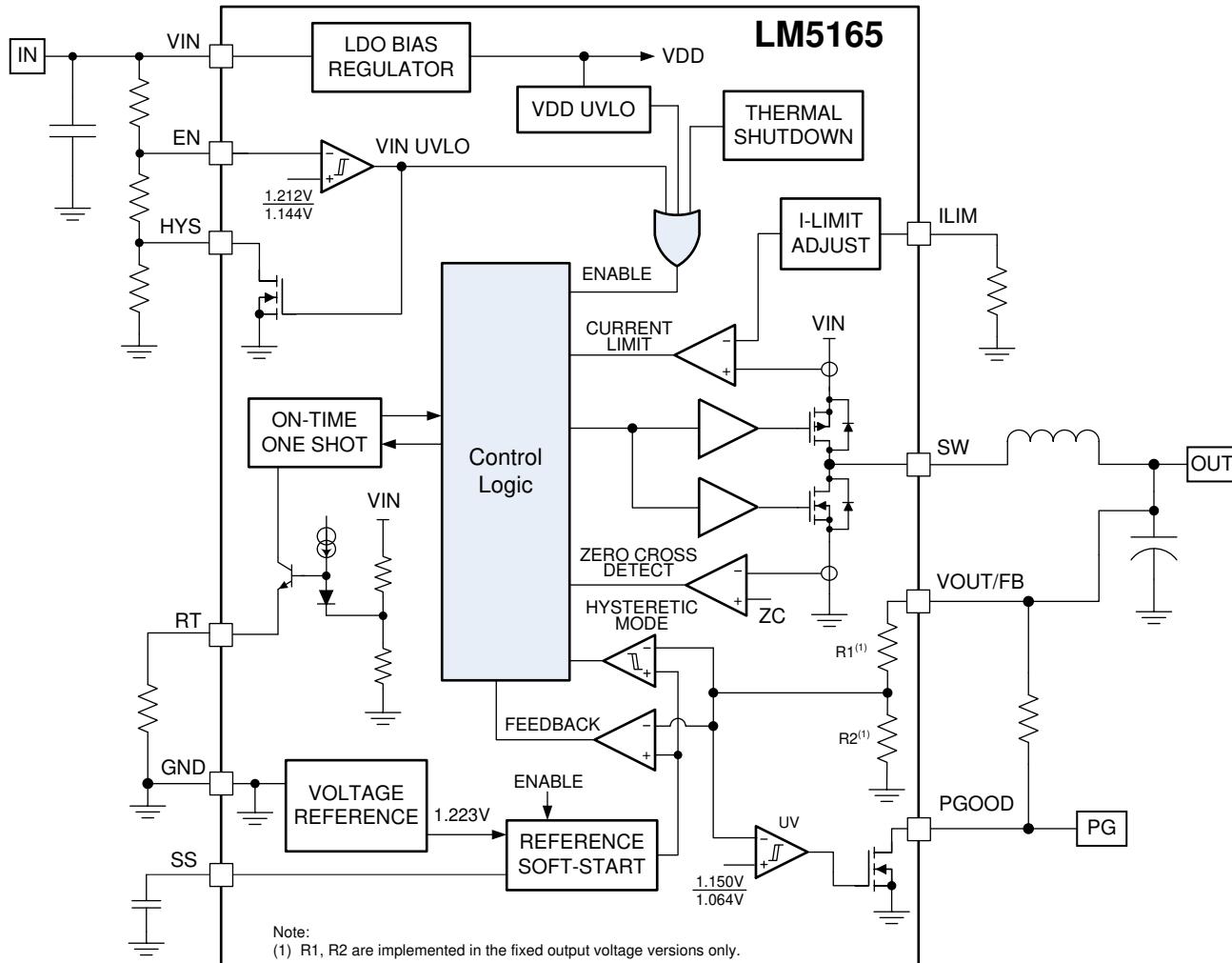

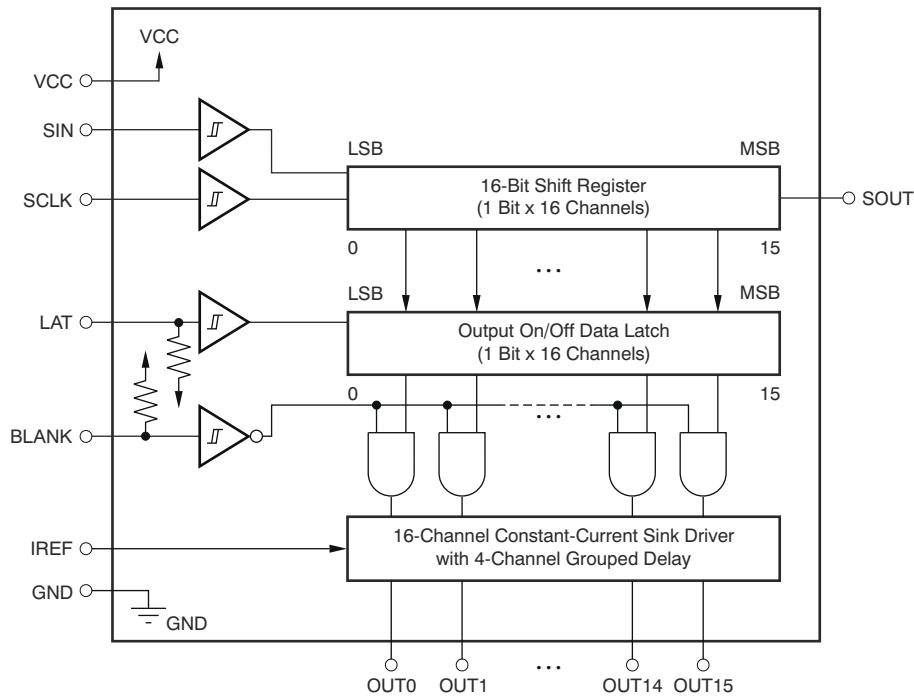

## 2.2.2 TLC59282

TLC59282 は、16 チャネルの定電流シンク LED ドライバです。各チャネルは、内部レジスタにシリアル データを書き込むことでオンまたはオフにできます。16 チャネルすべての定電流値を 1 個の外付け抵抗で設定します。

図 2-3. TLC59282 のブロック図

この設計に関する主な特長:

- 16 チャネル、定電流シンク出力、オン / オフ制御付き

- 35mA の能力 (定電流シンク)

- VCC = 3.0V~5.5V

- シリアル・ペリフェラル・インターフェイス (SPI)

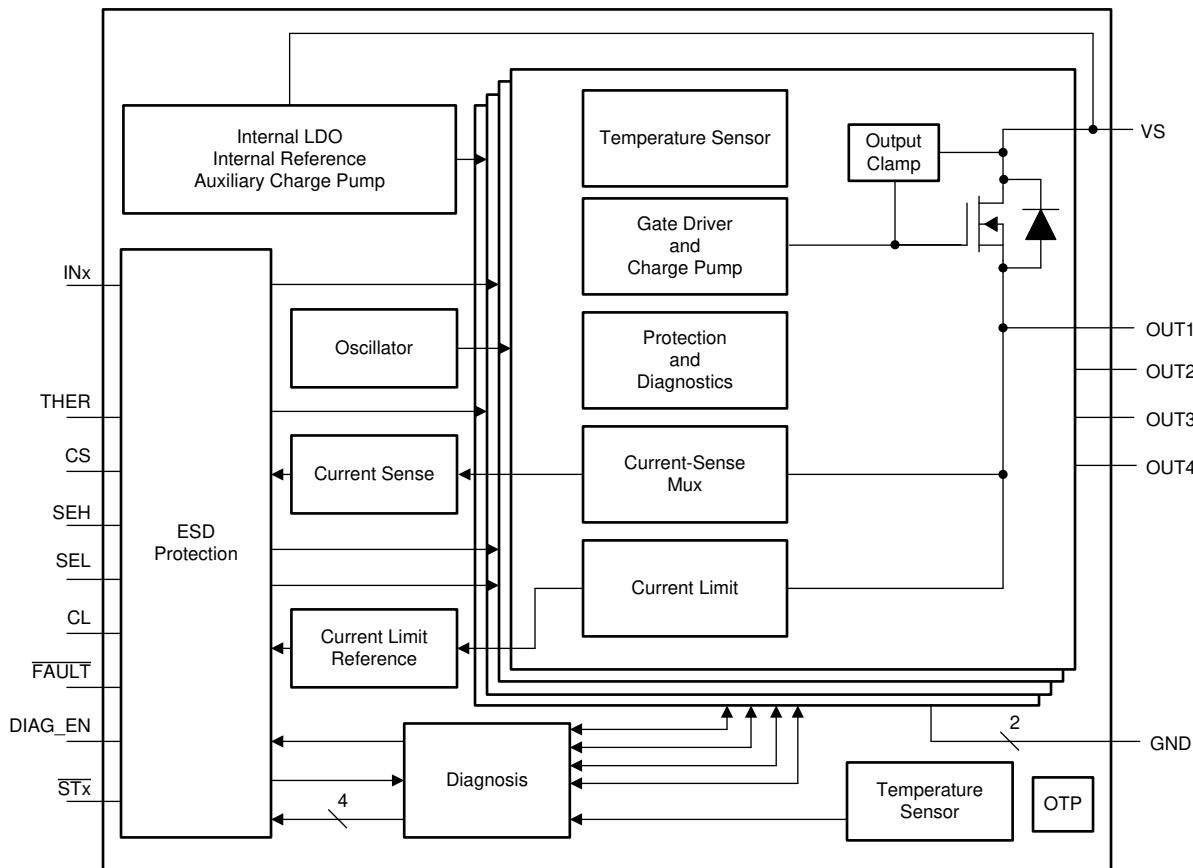

## 2.2.3 TPS4H160-Q1

TPS4H160-Q1 デバイスは、チャージポンプとクアッド チャネル NMOS パワー FET を内蔵したスマート ハイサイド スイッチです。包括的な診断機能と高精度の電流検出機能によって、インテリジェントな負荷制御が可能です。調整可能な電流制限機能により、システム全体の信頼性が大幅に向上します。このデバイスには、オープンドレイン デジタル出力 (バージョン A) と電流検出アナログ出力 (バージョン B) という、異なる診断報告機能を持つ 2 つのバージョンがあります。

バージョン A では、デバイスはオープンドレイン構造によるデジタル フォールトレポートを実装しています。故障が発生すると、デバイスは STx を GND にプルダウンします。マイコンの電源レベルに合わせるためには、3.3V または 5V の外部プルアップが必要です。各チャネルのデジタル ステータスは、STx ピンを互いに接続することで、個別に、またはグローバルに報告できます。

バージョン B では、高精度の電流検出により、追加の補正なしで診断の精度が向上します。1 つの内蔵電流ミラーにより、負荷電流の  $1 / K(CS)$  を供給可能です。ミラーリングされた電流は CS ピン抵抗に流れ、電圧信号になります。K(CS) は、温度と電源電圧に関係なく一定の値です。0V~4V までの広いリニア領域により、負荷電流のリアルタイム監視がより効果的に行えます。CS ピンは、VCS(H) のプルアップ電圧で故障を通知することもできます。

外部の高精度電流制限機能により、アプリケーションごとに電流制限値を設定できます。過電流が発生した場合、デバイスは突入電流を効果的にクランプすることで、システムの信頼性を向上させます。また、PCB トレイスとコネクタのサイズ、および前段の電力段の容量を削減することにより、システムのコストを節約できます。さらに、このデバイスには固定値の内部電流制限機能も実装されています。

このデバイスでは、誘導性負荷(リレー、ソレノイド、バルブ)のために、ドレインとソースの間にアクティブクランプを実装して自己保護を行います。誘導性負荷のスイッチオフサイクル中は、電源(**EBAT**)および負荷(**ELOAD**)の両方のエネルギーが、ハイサイドパワー シンジ 自体で消費されます。また、このデバイスは、クランプがアクティブなときのスイッチングオフのスルーレートを最適化し、過渡電力と **EMI** の影響を最小限に抑え、維持することで、システム設計を支援します。

**TPS4H160-Q1** デバイスは、省電力電球、LED、リレー、ソレノイド、ヒーターなど、幅広い種類の抵抗性、誘導性、容量性負荷のためのハイサイドパワー シンジとして使用できます。

出力ドライバ段により小型のソリューションが必要な場合は、新しく登場した **TPS4H160-Q1** デバイスの小型 QFN パージョンを使用できます。**TPS274160** は、**TPS4H160-Q1** と同等の性能を備えながら、より小型の QFN パッケージで提供されるという利点があります。**TPS274160** は **TPS4H160-Q1** と比較してソリューション サイズを 67% 削減します。

図 2-4. TPS4H160 のブロック図

ここでは、主な機能について説明します:

- 完全な診断機能を備えたクアッド チャネル  $160\text{m}\Omega$  スマートハイサイド シンジ

- バージョン A: オープンドレイン デジタル出力

- バージョン B: 電流センス アナログ出力

- 広い動作電圧範囲:  $3.4\text{V} \sim 40\text{V}$

- 高精度の電流センス:  $25\text{mA}$  を超える負荷時で  $\pm 15\%$

- $500\text{mA}$  を超える負荷について、外付け抵抗により  $\pm 15\%$  で電流制限を変更可能

- 保護

- 電流制限 (内部または外部) による GND への短絡保護

- ラッчикオフ オプションおよびサーマル スイング付きのサーマル シャットダウン機能

- スルーレートが最適化された、誘導性負荷の負の電圧クランプ

- GND 損失およびバッテリ損失保護

- 診断

- 過電流およびグランドへの短絡の検出

- 開放負荷およびバッテリへの短絡の検出

- グローバル フォルト レポートによる高速割り込み

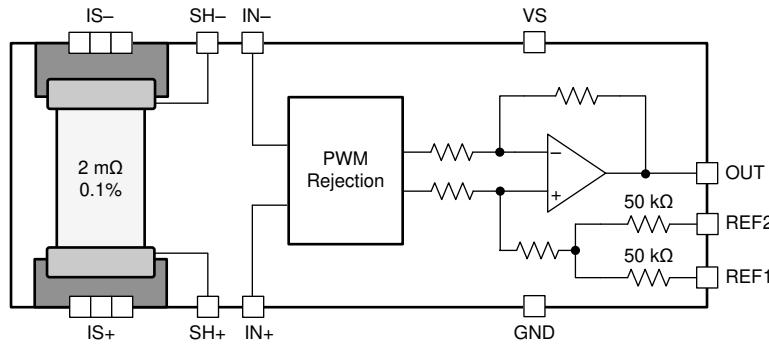

#### 2.2.4 INA253

INA253 は、2 mΩ の高精度電流検出抵抗、80V の同相モード範囲、ゼロ ドリフト構成、高精度、優れ同相モード除去比 (CMRR)、および強化されたパルス幅変調 (PWM) リジェクション機能を備えた電流検出アンプを 1 つのパッケージに統合しています。シャント抵抗値と電流検出アンプのゲインを精密にマッチングさせることで、高精度な測定が可能となり、システムで較正された高精度ソリューションを実現します。強化された PWM 除去機能により、PWM 信号に関連する出力信号の同相過渡の影響が低減されます。複数のゲイン バージョンが用意されており、アプリケーションで予測される目標の電流範囲に基づいて、目的のフルスケール出力電圧を最適化できます。

図 2-5. INA253 のブロック図

このデバイスの主な特長は次のとおりです:

- 高精度のシャント抵抗を内蔵

- シャント抵抗: 2mΩ

- シャント抵抗の公差: 0.1% (最大値)

- -40°C～85°Cで ±15A の連続電流

- 0°C～125°Cの動作温度範囲: 10ppm/°C

- 精度:

- ゲイン誤差: 0.25% (最大値)

- ゲイン ドリフト: 10ppm/°C (最大値)

- オフセット電圧: ±2mA

- オフセット ドリフト: 125µA/°C (最大値)

- 広いコモン モード電圧範囲: -4V ~ 80V

- 利用可能なゲイン: 100mV/A、200mV/A、400mV/A

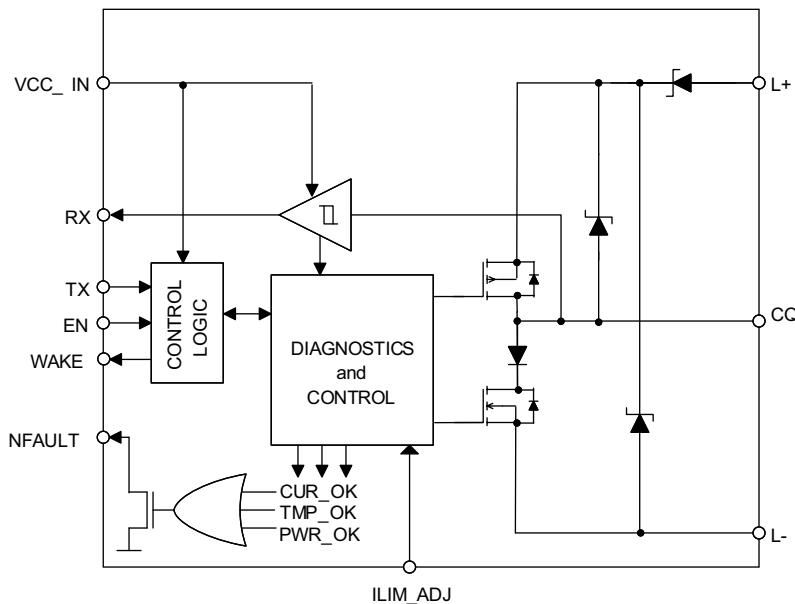

#### 2.2.5 TIOL111

堅牢な TIOL111 トランシーバ ファミリーは、産業用ポイントツー ポイント通信向けに IO-Link インターフェイスを実装しています。デバイスが 3 線式のインターフェイス経由で IO-Link マスターに接続されているとき、マスターはリモート ノードとの通信を開始してデータを交換でき、TIOL111 デバイスは通信の完全な物理レイヤとして機能します。

これらのデバイスは、最大 1kV (500Ω) の IEC 61000-4-5 サージに耐えることができ、また、逆極性保護を内蔵しています。

シンプルなピン プログラマブル インターフェイスにより、制御回路との接続が容易に行えます。出力電流制限は、外付けの抵抗を使用して構成できます。

低電圧、短絡電流、過温に対して故障の報告および内部保護機能が備えられています。

図 2-6. TIOL111 のブロック図

TIOL111 デバイスの主な特長:

- PNP、NPN、または IO-Link を構成可能な出力

- IEC 61131-9 COM1、COM2、COM3 のデータ レートをサポート

- 電流制限を 50mA～350mA に設定可能

- $\pm 65V$  の過渡耐性、100 $\mu$ s 未満

- L+、CQ、L- で最大 55V の逆極性保護

- L+ および CQ に EMC 保護を搭載

- 最大電流 20mA 対応の LDO オプションを搭載

### 2.3 システム設計理論

このリファレンス デザインは、TIOL111 デバイス PHY と、IO-Link マスタの包括的な設計を構築するために必要な周辺部品を使用して、IO-Link マスタを実装します。したがって、物理層側では TIOL111 デバイスに加えて、ポート用の電源および電流シンクが必要です。また、ハードウェアは、ウェークアップ パルスを駆動できる必要があります。

一方、3 つの通信速度すべてをサポートするハードウェアとフレーム ハンドラを用意する必要があります。ここで PHY として使用されている TIOL111 デバイスは、すべての通信速度 (COM1、COM2、COM3) に対応しており、8 ポートのフレーム ハンドラは使用している AM437x の PRU 上に実装されています。

8 ポートのマスタを実現するには、8 つの TIOL111 デバイスが必要です。さらに、4 ポートごとに 1 つの TPS4H160 が必要です。各ポートには 1 つの電流シンクも必要です。その結果、8 つの TIOL111 デバイス (IO-Link PHY)、2 つの TPS4H160 デバイス (ハイサイド スイッチ)、1 つの TLC59282 デバイス (LED ドライバ)のみが実現します。

### 2.3.1 IO-Link® PHY

ここで使用されている TIOL111 デバイスの主な目的は、3.3V ロジック側と 24V インターフェイス間のレベルを変換することです。オプションの内部 LDO、ウェイクアップ検出、および過電流検出は使用されていません。

しかし、マスタ構成の TIOL111 デバイスは、IO-Link 規格に準拠したウェイクアップ パルスを駆動できる必要があります。IO-Link デバイスは SIO モードで起動するため、通信を行う前に IO-Link に構成する必要があります。したがって、出力は Low (約 0V) または High レベル (約 24V) のいずれかになり、駆動されます。モードを切り替えるために、マスタは長さ 80μs のパルスを送信し、このパルスの間に 500mA を駆動でき、なおかつ所定の電圧に達する必要があります。このパルスを検出すると、デバイスは IO-Link モードに切り替わり、通信を開始できます。

これをテストするための正確なパラメータは、[IO-Link® テスト仕様、バージョン 1.1.2](#) に記載されています。[表 2-2](#) および [表 2-1](#) を参照してください。規格に準拠するには、両方の部分を満たす必要があります。

**表 2-1. ウェークアップ パルス テスト仕様の High パルス**

| テスト ケースの属性    | 識別情報、リファレンス                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 識別情報 (ID)     | SDCI_TC_0021                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 名称            | TCM_PHYL_INTF_IQWUH                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 目的 (短絡)       | ウェイクアップ パルスの駆動能力 – ハイサイド ドライバ                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 被試験機器 (EUT)   | マスタとレガシ マスタ                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| テスト ケースのバージョン | 1.0                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| カテゴリ、タイプ      | マスタ プロトコル テスト、合格するためのテスト (陽性テスト)                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 仕様 (条項)       | <a href="#">IO-Link インターフェイスおよびシステム仕様バージョン 1.1.2 のセクション 5.3.3.3、表 9</a> を参照                                                                                                                                                                                                                                                                                                                                                                      |

| 構成 / セットアップ   | –                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| テスト ケース       | 条件、性能                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 目的 (詳細)       | マスターは受信側のスレッショルドの High レベルを超えるように抵抗負荷を駆動するものとします。SDCI 用に構成されたマスタを使って、マスタ C/Q ポートでパルス電圧を測定します。パルス電圧は、C/Q と L- の間に抵抗性負荷を印加して測定します。                                                                                                                                                                                                                                                                                                                 |

| 前提条件          | マスタを SDCI モードに構成                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 手順            | <ul style="list-style-type: none"> <li>a) 最小電源電圧 (<math>V_{SM} = 20V</math>) をマスタに印加します</li> <li>b) C/Q と L- の間に抵抗性負荷 <math>R_{load}</math> を印加します:<br/> <math>R_{load} = V_{THHM_{max}} / I_{QPKHM_{min}} = 26\Omega</math> (51Ω と 51Ω のシャント)</li> <li>c) ウェイクアップ要求をトリガする</li> <li>d) ウェイクアップ要求中に C/Q ポートの電圧を測定する</li> <li>e) VIM が <math>V_{THHM_{max}}</math> を超えているか確認する</li> <li>f) 最大電源電圧 (<math>V_{SM} = 30V</math>) でテストを繰り返す</li> </ul> |

| 入力パラメータ       | –                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| ポスト条件         | –                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| テスト ケースの結果    | チェック、反応                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 評価            | –                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| テストに合格        | ウェークアップ要求中の C/Q のレベルが $V_{THHM_{max}}$ 以上                                                                                                                                                                                                                                                                                                                                                                                                        |

| テストに失敗 (例)    | ウェークアップ要求時の C/Q のレベルは、 $V_{THHM_{max}}$ より小さい                                                                                                                                                                                                                                                                                                                                                                                                    |

| 結果            | $VIM@WURQ (VSM = 18V): <value>$<br>$VIM@WURQ (VSM = 30V): <value>$                                                                                                                                                                                                                                                                                                                                                                               |

表 2-2. ウエークアップ パルス テスト仕様 Low パルス

| テスト ケースの属性    | 識別情報、リファレンス                                                                                                                                                                                                                                                                                                                                                                |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 識別情報 (ID)     | SDCI_TC_0023                                                                                                                                                                                                                                                                                                                                                               |

| 名称            | TCM_PHYL_INTF_IQWUL                                                                                                                                                                                                                                                                                                                                                        |

| 目的 (短絡)       | ウェークアップ パルスのドライバ機能 - ローサイド ドライバ                                                                                                                                                                                                                                                                                                                                            |

| 被試験機器 (EUT)   | マスタとレガシ マスタ                                                                                                                                                                                                                                                                                                                                                                |

| テスト ケースのバージョン | 1.0                                                                                                                                                                                                                                                                                                                                                                        |

| カテゴリ、タイプ      | マスタ プロトコル テスト、合格するためのテスト (陽性テスト)                                                                                                                                                                                                                                                                                                                                           |

| 仕様 (条項)       | <a href="#">IO-Link インターフェイスおよびシステム仕様バージョン 1.1.22 のセクション 5.3.3.3、表 9 を参照</a>                                                                                                                                                                                                                                                                                               |

| 構成 / セットアップ   | –                                                                                                                                                                                                                                                                                                                                                                          |

| テスト ケース       | 条件、性能                                                                                                                                                                                                                                                                                                                                                                      |

| 目的 (詳細)       | マスタは、受信側のスレッショルドの低レベルを下回るように抵抗負荷を駆動するものとします。SDCI 用に構成されたマスタを使って、マスタ C/Q ポートでパルス電圧を測定します。パルス電圧は、C/Q と L+ の間に抵抗性負荷を印加して測定します。                                                                                                                                                                                                                                                |

| 前提条件          | マスタを SDCI モードに構成                                                                                                                                                                                                                                                                                                                                                           |

| 手順            | a) 最小電源電圧 ( $V_{SM} = 20V$ ) をマスタに印加します<br>b) C/Q と L+ の間に抵抗性負荷 $R_{load}$ を印加します:<br>$R_{load} = (V_{SM} - V_{THLM_{min}}) / IQPKLM_{min} = 24\Omega$ (47Ω と 51Ω のシャント)<br>c) ウエイクアップ要求をトリガする<br>d) ウエイクアップ要求中に C / Q ポートの電圧を測定する<br>e) VIM が $V_{THLM_{min}}$ を下回っているか確認する<br>f) 最大電源電圧 ( $V_{SM} = 30V$ ) でマスタに対してテストを繰り返す:<br>$R_{load} = 44\Omega$ (82Ω を 100Ω でシャント) |

| 入力パラメータ       | –                                                                                                                                                                                                                                                                                                                                                                          |

| ポスト条件         | –                                                                                                                                                                                                                                                                                                                                                                          |

| テスト ケースの結果    | チェック、反応                                                                                                                                                                                                                                                                                                                                                                    |

| 評価            | –                                                                                                                                                                                                                                                                                                                                                                          |

| テストに合格        | ウェークアップ要求中の C/Q のレベルが $V_{THLM_{min}}$ 以下                                                                                                                                                                                                                                                                                                                                  |

| テストに失敗 (例)    | ウェークアップ要求が $V_{THLM_{min}}$ より大きいときの C/Q のレベル                                                                                                                                                                                                                                                                                                                              |

| 結果            | $VIM@WURQ (VSM = 20V): <value>$<br>$VIM@WURQ (VSM = 30V): <value>$                                                                                                                                                                                                                                                                                                         |

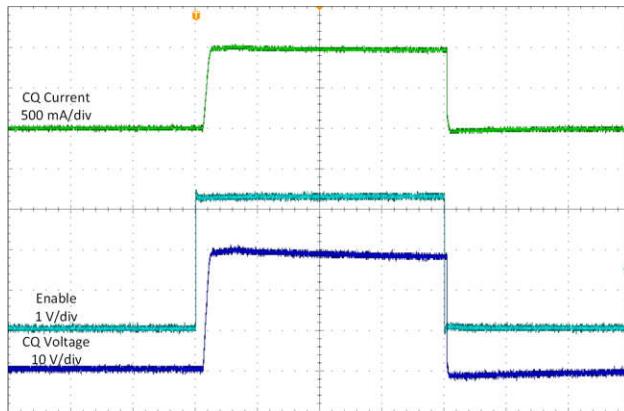

設計前に、TIOL111 デバイスがウェークアップ パルスを生成できることが検証されています。図 2-7 に、4 つのテスト オプションの 1 つを示します。この場合、ハイサイド ドライバは  $VCC = 30V$  で試験されます。CQ には  $26\Omega$  の抵抗が接続されており、このとき CQ ラインはほぼ  $30V$  に達し、CQ 電流は  $500mA$  を超えます。これらは要件を満たしています。

図 2-7. TIOL111 デバイスのウェークアップ パルスのテスト結果

設計上、TIOL111 デバイスはウェークアップ パルスに必要な電流を供給できるため、マスタ PHY として使用できます。

## 2.3.2 電流シンク

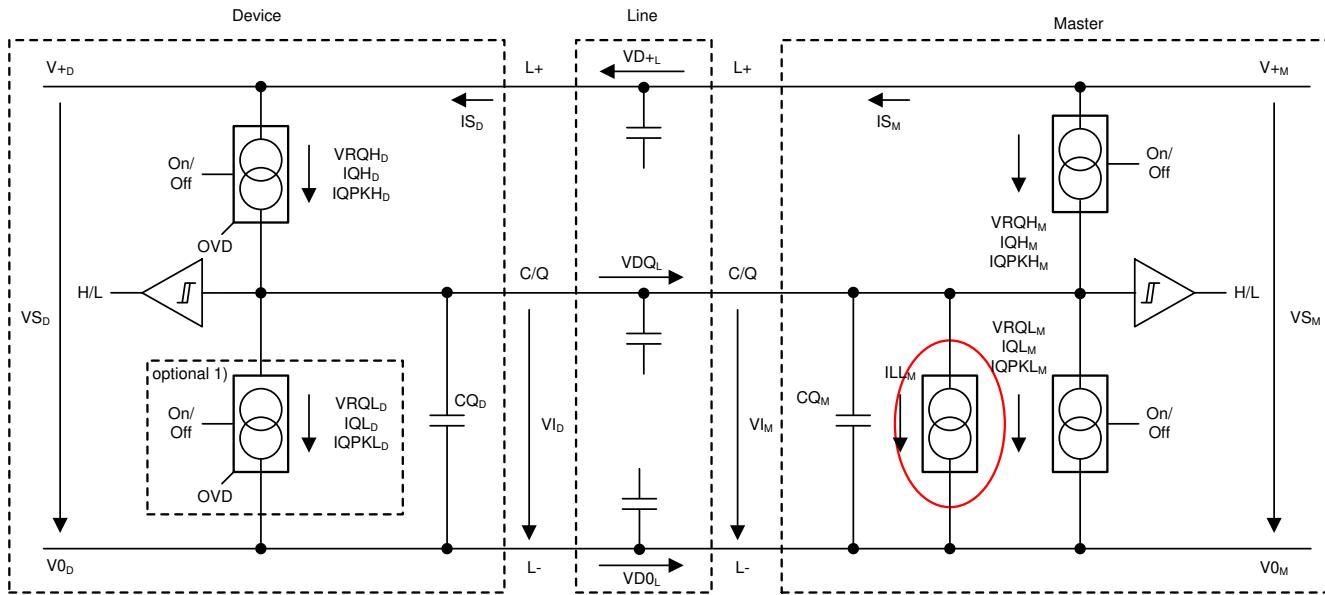

ウェークアップ パルスに加えて、マスタ PHY は本デバイス PHY に 2 番目の重要な違いを示しています(図 2-8 を参照)。このコンデンサには、電流シンクを内蔵する必要があります。TIOL111 デバイスはこれをチップに含まず、ボードに実装しています。

図 2-8. IO-Link® システムのブロック図

表 2-3 の仕様の抜粋が示すように、電流は 5mA と 15mA の間にある必要があります。

表 2-3. IO-Link® マスタ電流シンク (1) の仕様

| ILL <sub>M</sub> | 次の用途の負荷または放電電流:<br>0V < VI <sub>M</sub> < 5V<br>5V < VI <sub>M</sub> < 15V<br>15V < VI <sub>M</sub> < 30V | 0 | N/A | 15 | mA |

|------------------|-----------------------------------------------------------------------------------------------------------|---|-----|----|----|

|                  |                                                                                                           | 5 | N/A | 15 | mA |

|                  |                                                                                                           | 5 | N/A | 15 | mA |

- (1) 電流は、IEC 61131-2 のタイプ 1 デジタル入力の定義と互換性があります。ただし、5V < VI<sub>M</sub> < 15V の範囲では、純粋な P スイッチング デバイスで十分に短いスルーレートを実現するため、最小電流は 2mA ではなく 5mA です。

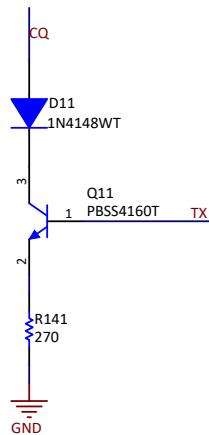

トランスマッタが無効化されているときにのみ動作し、かつ小さく許容できる電流シンクの実装は、単純な NPN トランジスタで実現できます。

図 2-9. シンプルな電流シンク

図 2-9 に回路図を示します。電流シンクは、MCU からの TX ラインによって制御され、TIOL111 デバイスに送られます。TIOL111 デバイスのロジックは反転であり、アイドル状態では TX ラインのデフォルトルーレベルが High なので、ドライバが無効になっているとき、または CQ ラインで 0V を送信しているときに、この電流シンクが有効になります。そのため、通常動作時は消費電流が増加することはありません。

### 2.3.3 L+ 用電源

IO-Link マスターは、L+ ラインに対して少なくとも 200 mA の電流供給能力を持ち、50 ms の間は 400 mA のパルス電流を供給できる必要があります。この状態を、表 2-4 に示すように仕様で規定しています。

表 2-4. L+ 電源の仕様

| 特性       | 指定           | 最小  | 標準値  | 最大   | 単位 | 注記                                                                     |

|----------|--------------|-----|------|------|----|------------------------------------------------------------------------|

| $VS_M$   | デバイスの電源電圧    | 20  | 24   | 30   | V  | <a href="#">IO-Link インターフェイスおよびシステム仕様 バージョン 1.1.2.2 の「電圧レベルの定義」を参照</a> |

| $IS_M$   | デバイスの消費電流    | 200 | 該当なし | 該当なし | mA | 200mA を上回るには外部電源が必要                                                    |

| $ISIR_M$ | デバイスの電流パルス能力 | 400 | 該当なし | 該当なし | mA | ポート電源の投入後、18V において少なくとも 50ms の間、マスターは電源電流供給能力を備えているものとします              |

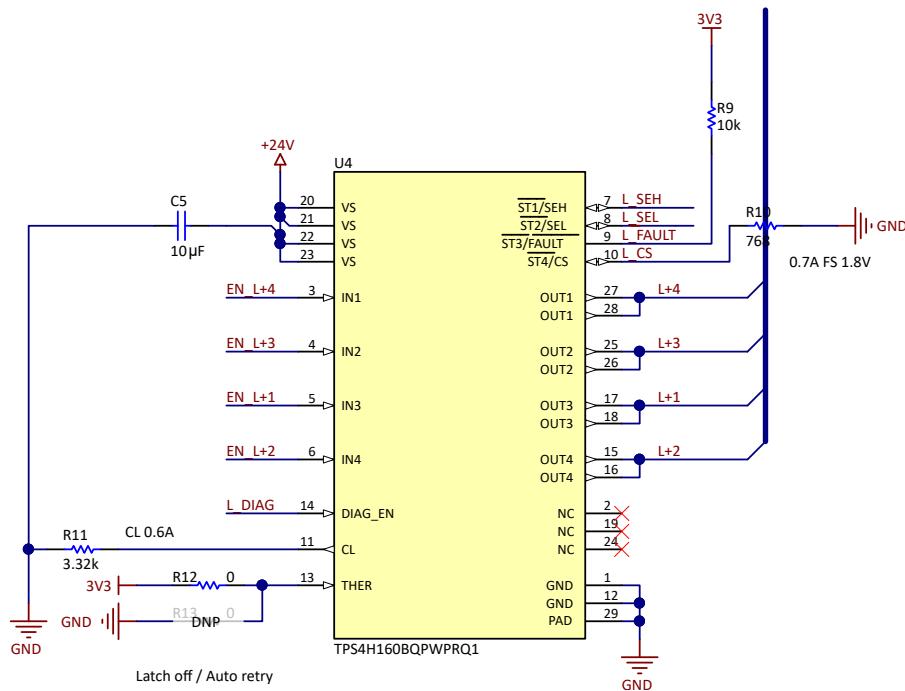

これを供給するために、TPS4H160 デバイスを使用します。このクアッド チャネル ハイサイド スイッチは、プログラム可能な電流制限機能を備えており、電流検出出力が MCU に接続されています。そのため、各チャネルは短絡保護機能を備えており、MCU が各ポートの電流を測定して故障を検出できます。

$IS_m$  の要件を満たすのは非常に簡単で、 $R_{(DS)on}$  が十分に低いすべてのデバイスを使用して達成できます。しかし、 $ISIR_m$  の達成はより困難です。というのも、接合部から周囲環境への電力損失が制限要因となるためです。出力が短絡している場合、または大容量コンデンサを充電する必要がある場合、デバイス内の消費電力は一時的に最大  $400\text{mA} \times 30\text{V} = 12\text{W}$  に達します。設計で 400mA の最小電流を超える電流を駆動した場合、この容量はさらに大きくなります。

L+ ライン上のコンデンサを静的負荷で充電する場合(これは IO-Link デバイスにとって現実的なシナリオです)、L+ ラインの電圧が上昇するにつれて FET の電圧降下が減少し、結果として消費電力も低下するため、状況はやや緩和されます。

しかし、電力はすぐに PCB やヒートシンクへ伝わるわけではないため、主にデバイスのパッケージ自体が制限要因となります。

詳細な仕様と、電源投入後の最初の 50ms での 400mA の電荷(合計 20mAs)の定義については、[IO-Link パッケージ 2015 および Corrigendum バージョン 1.0](#) のセクション 4.4 にあるパワーアップ時の最大デバイス消費電力表を参照してください。

この仕様拡張により、L+ ライン出力の試験は、1000  $\mu\text{F}$  の大容量コンデンサと 150 $\Omega$  の抵抗を並列に接続した構成で行うと定義されています。この負荷は、静的負荷と大きな入力コンデンサでデバイスをシミュレートします。

図 2-10. ハイサイド スイッチ回路図

ハイサイド スイッチは、電流を 0.6 A に制限するように設定されています。この電流値は、ターンオン動作の要件を満たすように選定されています。より高い電流では、コンデンサ充電中の消費電力にパッケージが耐えられず、デバイスは冷却のためにシャットダウンし、再起動します。

電流検出は、最大出力電圧 1.8V で最大 0.7A まで動作するように設定されています（これは、本 IDK で使用している AM4379 デバイス内の ADC によって決定されます）。結果として、図 2-10 に示す回路図になります。TPS4H160 デバイスは、サーマル エラー発生後に 2 つの動作モードを設定できます。すなわち、シャットダウンするか、自動的にリトライするかです。ここでは、再度イネーブルされるまでシャットダウン状態を維持するように設定されています。

他の要件が必要な場合、または中断を伴うターンオン動作が許容される場合は、1 ポートあたり 1A の高い電流でも起動時に問題なく動作します。

### 2.3.4 電源

IO-Link マスターは 24V で動作します。この設計では、AM437x IDK も同様に 24V で電源供給されるため、1 つの電源で両方のボードに給電することも、2 つの別々の 24 V 電源を使用することも可能です。ただし、それに応じてアダプタ ボードのジャンパを設定する必要があります。

電源を IDK に接続し、そこから IO-Link マスターに給電する場合は、アダプタ上の J7 をショートさせる必要があります。すべてのポートで、合計電流が 0.5A に制限されるように注意する必要があります。この構成はテストされておらず、推奨されません。

推奨される方法は、アダプタ ボードを介して IDK に給電することです。したがって、1 台の 24V 電源を J5 または J8 のいずれかに接続する必要があります。ジャンパ J6 と J9 を短絡する必要があります。IDK に電力を供給するには、J7 も短絡する必要があります。IDK に別の電源を使用する場合は、J7 をオープンにしておく必要があります。

表 2-5. 電源ジャンパ設定

| 構成             | 電源                  | J6, J9 | J7   |

|----------------|---------------------|--------|------|

| IDK から電力供給されます | IDK にのみ接続           | オープン   | 短絡   |

| アダプタから電源供給     | 接続先は J8 と J5        | 短絡     | 短絡   |

| 個別の電源          | IDK と J8 または J5 に接続 | 短絡     | オープン |

TLC59282 デバイスおよび TIOL111 デバイスには 3.3V 電源が必要です。IDK の電圧レギュレータに負荷をかけないように、必要な電圧を供給する追加の LM5165 デバイスがアダプタ ボード上にあります。すべての電圧が安定する前に IO-Link マスタが IDK への信号を駆動しないようにするために、IDK からの 3.3V によって LM5165 デバイスがオンになります。

### 2.3.5 ピン配置

AM437x IDK 用 IO-Link マスタ拡張ボードは、IDK 上の 2 つのピン ヘッダを介して接続されます。一部の必要な信号をヘッダに導くためには、ボード上での改造が必要です。図 2-11 にピン配置を示します。変更箇所を表 2-6 に示します。

図 2-11. IDK に接続された IO-Link® ボードのピン配置

表 2-6. 変更点

| ピン     | 信号       | 削除        | 追加                          |

|--------|----------|-----------|-----------------------------|

| J16~5  | TX4      | R187、R264 | R187 から R264 までの配線 (J16-5)  |

| J16~23 | GPIO5_20 | -         | 10kΩ の抵抗 R343               |

| J16~34 | RX4      | R541      | -                           |

| J16~36 | RX5      | R541      | -                           |

| J16~49 | GPIO2_12 | R406      | -                           |

| J16~52 | RX6      | R541      | -                           |

| J16~53 | TX5      | R179、R465 | R179 から R465 までの配線 (J16-53) |

| J16~54 | RX7      | R541      | -                           |

| J16~55 | TX6      | R177、R471 | R177 から R471 までの配線 (J16-55) |

| J16~57 | TX7      | R70、R468  | R70 から R468 までの配線 (J16-57)  |

| J1~31  | AIN0     | R454      | 0Ω 抵抗 R450                  |

| J1~32  | AIN4     | R109      | 0Ω の抵抗 R104                 |

| J1~35  | AIN2     | R561      | 0Ω 抵抗 R435                  |

## 2.4 ソフトウェア フレーム ハンドラ

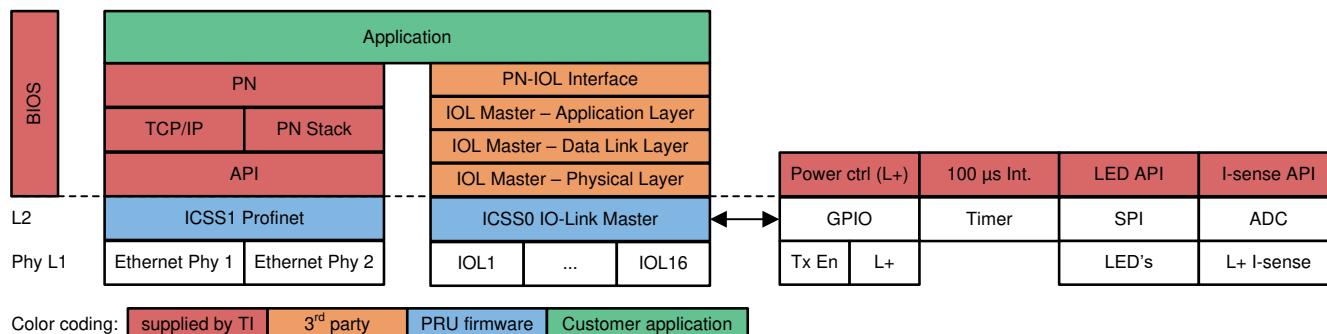

図 2-12. PRU-ICSS IO-Link® マスタ プロジェクト

図 2-12 に、PRU-ICSS IO-Link マスタ プロジェクトの概略構造を示します。次の 6 つの独立した部分にグループ化できます：

- PRU ファームウェアは、プロジェクトのコア部品であり、フレーム処理を実行します。これは、拡張機能を備えたマルチチャネル UART 実装です。

- PRU ファームウェアと、サードパーティが提供するスタックの各層との間に配置されているのが IO-Link ドライバです

- 電源制御や LED 制御など、IO-Link マスタ固有の機能に対応する TI 提供の追加 RTOS ドライバ機能

- サードパーティ製のスタック

- 顧客指定のアプリケーション

- Profinet などのオプションの 2 番目のインターフェイス (TI により提供される場合あり)

### 2.4.1 PRU-ICSS IO-Link® フレーム ハンドラ

IO-Link フレーム ハンドラは、この設計の中核となるソフトウェアの部品です。これはハードウェア UART をソフトウェア実装で置き換え、外部の処理ハードウェアを不要にします。

#### 2.4.1.1 性能上の利点およびメリット

プログラマブル リアルタイム ユニットおよび産業用通信サブシステム(PRU-ICSS)ハードウェアを使用すると、通常のマイコンでは時間的制約が厳しすぎる多くの処理を置き換えること、高い予測性と決定性を備えたソフトウェアを作成、実行できます。ハードウェアに似た動作により、8 チャネルの IO-Link マスタは非常に高速に反応し、ジッタはほぼ発生しません。

IO-Link フレーム ハンドラは、8 チャネルごとに 1 個の PRU を必要とし、ICSS ごとに 16 個のチャネルを提供することができます。多くの場合は利用可能な 2 番目の ICSS を使用して、リアルタイム イーサネットなどの他の処理を実行することもできます。

### 2.4.1.2 動作原理

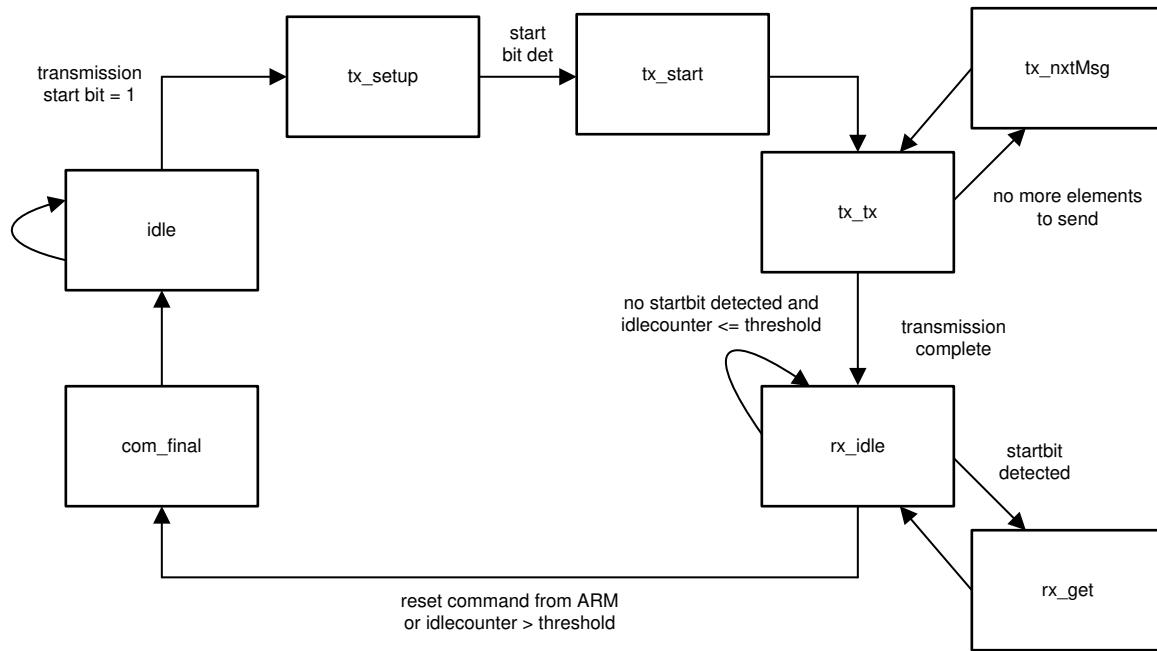

図 2-13. フレーム ハンドラのステート マシンの概略図

図 2-13 に、フレーム ハンドラのステート マシンの概要を示します。これはファームウェアの完全な説明というわけではなく、通信サイクルの一例を示したものでです。

フレーム ハンドラは、「送信スタートビット」によって開始され、選択した送信バッファの新しい送信をトリガします。その後、送信バッファ ポインタが進行中の送信の最後のバイトに達するまで、送信されます。送信の終了時には状態が変化し、受信状態に移行します。この状態では、送信が完了するまでデータを受信し続けます。送信はエラーまたはエラーなしで完了できます。これらのエラーは、ステータス ビットによって通知されます。エラー応答と対策は、IO-Link マスタ スタックの責任です。完了した通信サイクルは、ビット フラグとオプションの割り込みで示されます。

### 3 ハードウェア、ソフトウェア、テスト要件、テスト結果

#### 3.1 必要なハードウェアとソフトウェア

##### 3.1.1 ハードウェア

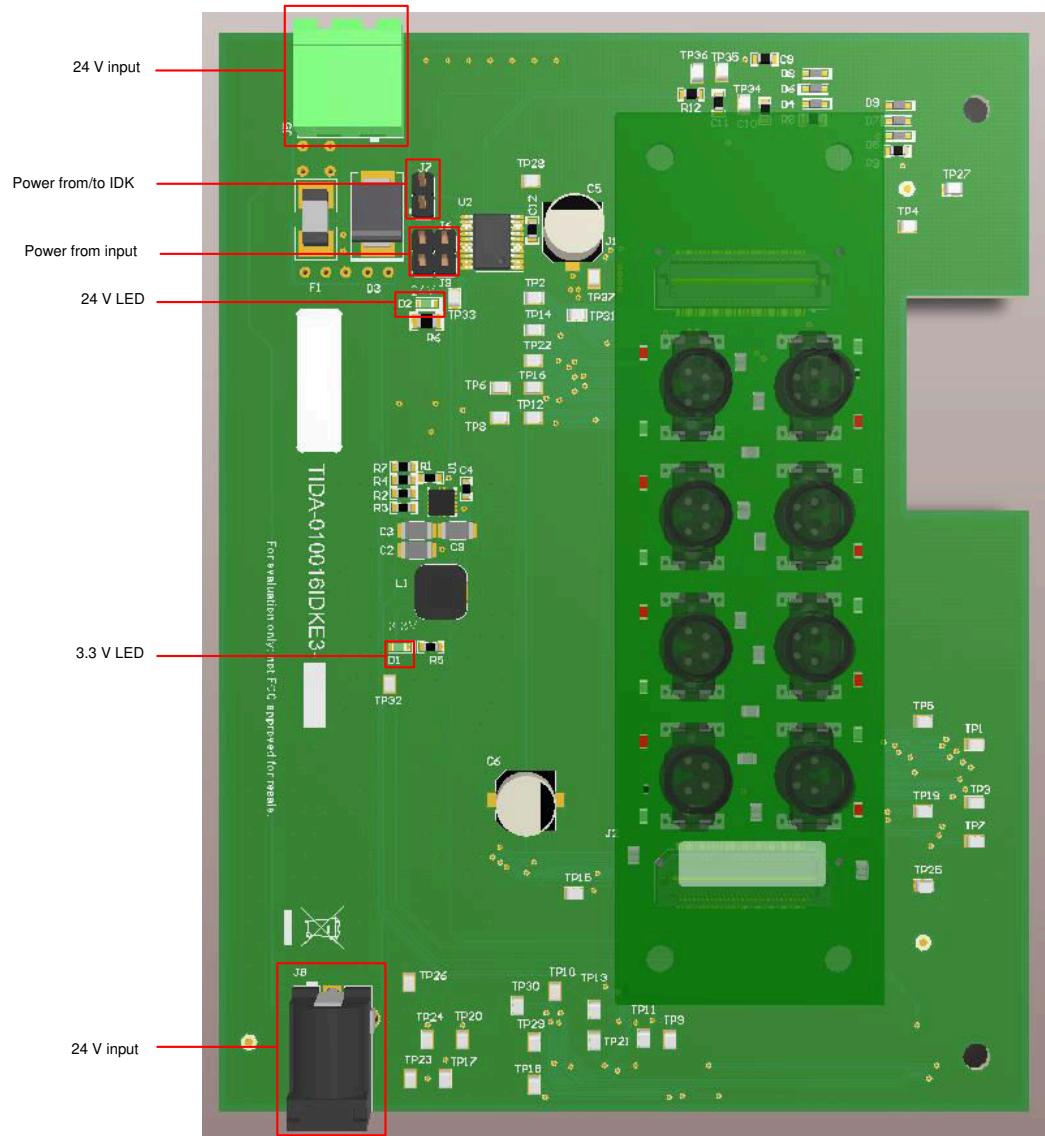

開発を開始するには、2枚の IO-Link マスタ ボードをスタックし、AM437x IDK にスタックする必要があります。24V、5A 電源を J8 または J5 に接続する必要があります。アダプタ ボードのジャンパ J6、J7、J9 を短絡する必要があります。図 3-1 に関連するジャンパおよびコネクタを示します。対応する電圧が存在すると、24V と 3.3V の LED が点灯します。通常の動作では、両方の LED が点灯します。

図 3-1. 電源コネクタとジャンパ

##### 3.1.2 ソフトウェア

簡易的な試験を行う場合は、対応する GPIO を手動で必要なレベルに接続できます。完全な IO-Link 動作を実現する場合、PRU 上にフレーム ハンドラを実装、ARM コア上で IO-Link スタックが動作するようにします。

## 3.2 テストと結果

### 3.2.1 テスト設定

さまざまな物理パラメータを試験するために、IO-Link ボードは IDK を使用せずに 24 V 電源に接続されます。各テストに必要な信号について、以降のセクションで説明します。

### 3.2.2 テスト結果

#### 3.2.2.1 IO-Link® のウェークアップ パルス

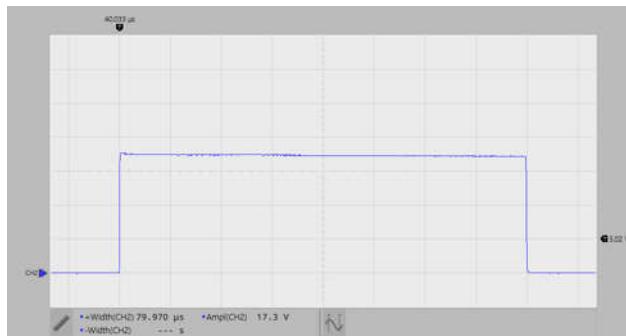

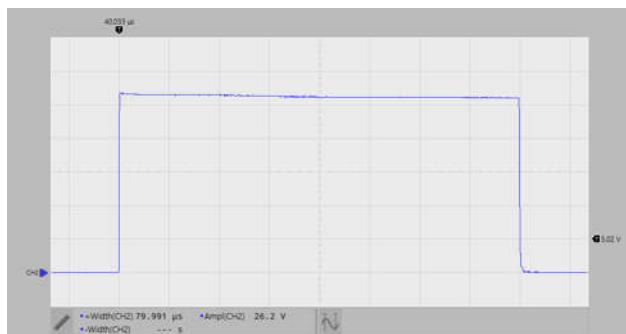

前述のように、PHY は 80 $\mu$ s および 500mA のウェークアップ パルスを供給する必要があります。これをテストするには、イネーブル信号を 3.3V に接続し、TX 信号をファンクション ジェネレータから供給します。このテストを、異なる極性、負荷、電圧で繰り返します。

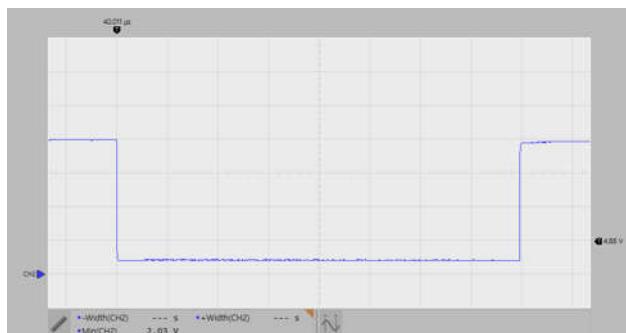

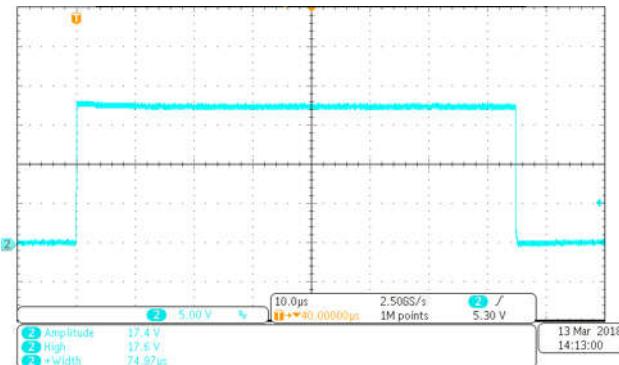

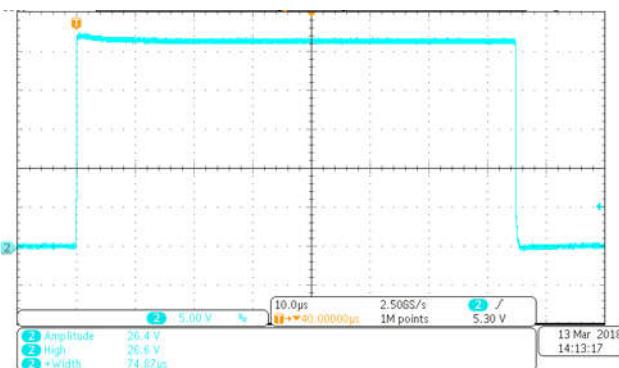

図 3-2. テストケース TCM\_PHYL\_INTF\_IQWUH:ハイサイド ドライバ、負荷 = 26  $\Omega$ 、20V 電源、5V/div、10 $\mu$ s / div

図 3-3. テストケース TCM\_PHYL\_INTF\_IQWUH:ハイサイド ドライバ、負荷 = 26  $\Omega$ 、30V 電源、5V/div、10 $\mu$ s / div

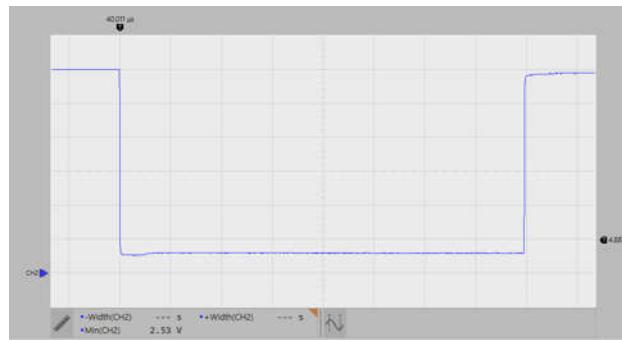

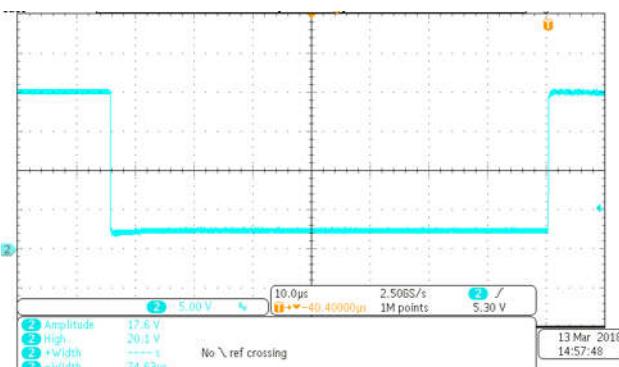

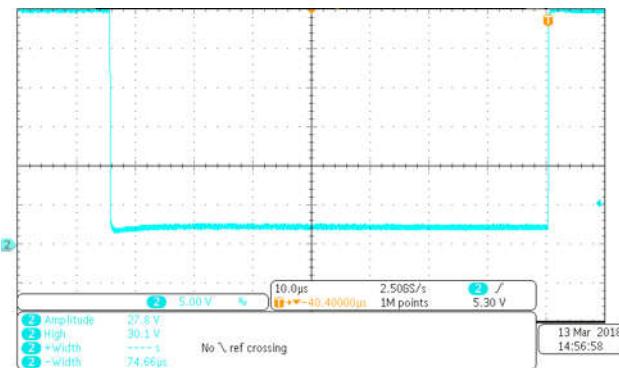

図 3-4. テストケース TCM\_PHYL\_INTF\_IQWUL:ローサイド ドライバ、負荷 = 24Ω、20V 電源、5V / div、10 $\mu$ s / div

図 3-5. テストケース TCM\_PHYL\_INTF\_IQWUL: ローサイド ドライバ、負荷 = 44 Ω、30V 電源、5V / div、10μs / div

図 3-5 から図 3-2 までに示すように、TIOL111 デバイスはこのテストに合格しています。

### 3.2.2.2 L+ ターンオン動作

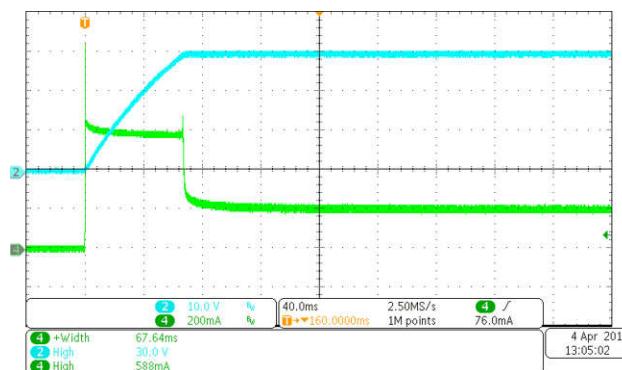

L+ ラインのターンオンは、1000μF のコンデンサに 150Ω の抵抗負荷を並列接続して試験されます。IO-Link マスタは、この試験に合格するために、少なくとも 50ms の間 400mA を供給できなければなりません。この負荷は、大きな入力コンデンサと静的な負荷で IO-Link デバイスをシミュレートします。

図 3-6. テストケース TCM\_PHYL\_INTF\_ISIRM:- 電源投入時の電源電流能力

図 3-6 にテスト結果を示します。チャネル 2 は L+ ラインの電圧を示し、チャネル 4 は L+ の電流を示します。負荷が容量性および抵抗性であるため、初期段階ではハイサイドスイッチによって電流が約 70ms の間、600mA に制限されます。この時間の後、抵抗性負荷は維持され、200mA の電流を引き込みます。このエネルギーは、必要な  $400\text{mA} \times 50\text{ms} = 20\text{mA}$  よりも大きいため、このテストに合格しました。

ただし、このテストでは、異なる IO-Link マスタ実装の動作は大きく異なります。

### 3.2.2.3 CQ の電流シンク

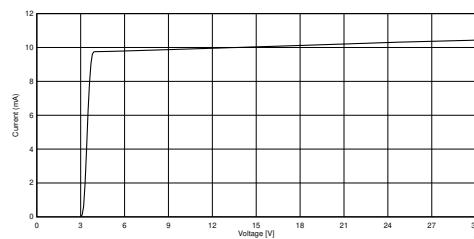

電流シンクを試験するには、試験対象のポートを入力として定義する必要があります。したがって、TIOL111 デバイスのイネーブル信号は Low に固定され、電流シンクを有効にするには TX 信号を 3.3V にする必要があります。次に、ポートの CQ ラインに可変電圧が印加されます。テストケース TCM\_PHYL\_INTF\_ILLM で、テスト手順を定義します。電流が 5.1V 未満では 15 mA 未満であり、5.1V から 30V の範囲では 5~15 mA である必要があります。

図 3-7. CQ ラインの入力電流

シンクの電流が規定された範囲内にあるため、テストに合格です。

### 3.2.2.4 残留電圧

テストケース TCM\_PHYL\_INTF\_IQPKHM は、ウェイクアップ パルス中に IO-Link PHY のハイサイドで発生する電圧降下を検証します。したがって、CQ ラインに  $26\Omega$  の負荷がかかり、ウェークアップ パルスが生成されます。このテストに合格するには、CQ ラインの電圧が 13V を超える必要があります。このテストは、20V と 30V の L+ 電圧で行います。

図 3-8. テストケース TCM\_PHYL\_INTF\_IQPKHM: ウェークアップ電流ハイサイド –20V L+ の結果、17.4V

図 3-9. テストケース TCM\_PHYL\_INTF\_IQPKHM: ウェークアップ電流ハイサイド –30V L+ の結果、26.4V

図 3-9 と図 3-8 に示すように、電圧は 13V を超えているため、ハイサイド ドライバのテストに合格しました。

次の関連するテスト ケースは TCM\_PHYL\_INTF\_IQPKLM です。このテストは以前と類似していますが、ローサイド スイッチをテストしています。したがって、負荷は L+ 電圧が 20V の場合は  $24\Omega$ 、30 V の場合は  $44\Omega$  となります。ローサイドを試験するためには、抵抗を L+ と CQ の間に接続する必要があります。このテストに合格するには、電圧が 8V 未満である必要があります。

図 3-10. テストケース TCM\_PHYL\_INTF\_IQPKLM: ウェークアップ電流ローサイド – 20V L+ の結果、2V

図 3-11. テストケース TCM\_PHYL\_INTF\_IQPKLM: ウエークアップ電流ローサイド – 30V L+ の結果、2V

そのため、ウェークアップ パルス中に電流能力に関するすべてのテストに合格しています。

### 3.2.2.5 IO-Link® 物理層テストの要約

表 3-1 に、すべての物理層テストの概要と結果を示します。

**表 3-1. IO-Link® 物理層テスト**

| ID           | 名称                         | 構成                                                   | 仕様 (条項)                                                                              | コメント       | 結果                                                                                                                                                                                                                                                                                                                                     |

|--------------|----------------------------|------------------------------------------------------|--------------------------------------------------------------------------------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SDCI_TC_0001 | TCM_PHYL_INTF_ISM          | マスタ ポートの供給電流が監視されます。                                 |                                                                                      | 200mA でテスト | 20V:合格<br>30V:合格                                                                                                                                                                                                                                                                                                                       |

| SDCI_TC_0002 | TCM_PHYL_INTF_ISIRM        | マスタ ポートの供給電流が監視されます。                                 |                                                                                      | 500mA でテスト | 20V:合格<br>30V:合格                                                                                                                                                                                                                                                                                                                       |

| SDCI_TC_0003 | TCM_PHYL_INTF_ILLM         | マスタ ポートの C/Q での入力電流が監視されます。                          | <i>IO-Link インターフェイスおよびシステム仕様書 V1.1.22 のセクション 5.3.2.3、表 6 を参照してください</i>               |            | ILLM (VIM = 5V, VSM = 20V): 9.77mA 合格<br>ILLM (VIM = 5.1V, VSM = 20V): 9.77mA 合格<br>ILLM (VIM = 15V, VSM = 20V): 10.04mA 合格<br>ILLM (VIM = VSM = 20V): 10.17mA 合格<br>ILLM (VIM = 5V, VSM = 30V): 9.77mA 合格<br>ILLM (VIM = 5.1V, VSM = 30V): 9.77mA 合格<br>ILLM (VIM = 15V, VSM = 30V): 10.04mA 合格<br>ILLM (VIM = VSM = 30V): 10.43mA 合格 |

| SDCI_TC_0004 | TCM_PHYL_INTF_VREShigh     | マスタ C/Q 出力の出力レベルを測定します。                              |                                                                                      |            | VRQHM (VSM = 20V): 1.003V<br>VRQHM (VSM = 30V): 1.002V<br>合格                                                                                                                                                                                                                                                                           |

| SDCI_TC_0005 | TCM_PHYL_INTF_VRESLOW      | マスタ C/Q 出力の出力レベルを測定します。                              |                                                                                      |            | VRQLM (VSM = 20V): 0.984V<br>VRQLM (VSM = 30V): 0.983V<br>合格                                                                                                                                                                                                                                                                           |

| SDCI_TC_0006 | TCM_PHYL_INTF_VTHHM        | C/Q 入力のデジタル入力信号が監視されます                               |                                                                                      |            | VIM@VTHHM (VSM = 20V): 11.47V<br>VIM@VTHHM (VSM = 30V): 11.47V<br>合格                                                                                                                                                                                                                                                                   |

| SDCI_TC_0007 | TCM_PHYL_INTF_VTHLM        | C/Q 入力のデジタル入力信号が監視されます                               | <i>IO-Link インターフェイスおよびシステム仕様書 V1.1.22 のセクション 5.3.2.2、表 5 を参照してください</i>               |            | VIM@VTHLM (VSM = 20V): 10.75V<br>VIM@VTHLM (VSM = 30V): 10.75V<br>合格                                                                                                                                                                                                                                                                   |

| SDCI_TC_0008 | TCM_PHYL_INTF_VHYSM        | SDCI_TC_0006 と SDCI_TC_0007 の値の比較                    |                                                                                      |            | VHYSM (VSM = 20V): 0.72V<br>VHYSM (VSM = 30V): 0.72V<br>合格                                                                                                                                                                                                                                                                             |

| SDCI_TC_0009 | TCM_PHYL_INTF_IQPKHM       | マスタ C/Q 出力の出力レベルを測定します。                              |                                                                                      |            | VIM (VSM = 20 V): 17.4V<br>VIM (VSM = 30V) : 26.4V<br>合格                                                                                                                                                                                                                                                                               |

| SDCI_TC_0010 | TCM_PHYL_INTF_IQPKLM       | マスタ C/Q 出力の出力レベルを測定します。                              | <i>IO-Link インターフェイスおよびシステム仕様書 V1.1.22 のセクション 5.3.2.3、表 6 を参照してください</i>               |            | VIM (VSM = 20 V): 2.2V<br>VIM (VSM = 30V) : 2.2V<br>合格                                                                                                                                                                                                                                                                                 |

| SDCI_TC_0299 | TCM_PHYL_INTF_VOLTRAN_GECQ | CQ を $1\Omega$ 経由で 0V および 30V に接続した後で動作するかどうかをテストします | <i>IO-Link インターフェイスおよびシステム仕様書 V1.1.22 のセクション 5.3.2.2、表 5 - VIL および VIH を参照してください</i> |            | 合格                                                                                                                                                                                                                                                                                                                                     |

**表 3-1. IO-Link® 物理層テスト (続き)**

| ID           | 名称                  | 構成                                                                     | 仕様 (条項)                      | コメント                                                             | 結果 |

|--------------|---------------------|------------------------------------------------------------------------|------------------------------|------------------------------------------------------------------|----|

| SDCI_TC_0021 | TCM_PHYL_INTF_IQWUH | <i>IO-Link インターフェイスおよびシステム仕様書 V1.1.22 のセクション 5.3.3.3、表 9 を参照してください</i> | ファンクション ジエネレータからのウェークアップ パルス | VIM@WURQ (VSM = 20V): 17.3V<br>VIM@WURQ (VSM = 30V): 26.2V<br>合格 |    |

| SDCI_TC_0022 | TCM_PHYL_INTF_TWUH  |                                                                        | ファンクション ジエネレータからのウェークアップ パルス | TWUH@WURQ (VSM = 20V): 80μs<br>TWUH@WURQ (VSM = 30V): 80μs<br>合格 |    |

| SDCI_TC_0023 | TCM_PHYL_INTF_IQWUL |                                                                        | ファンクション ジエネレータからのウェークアップ パルス | VIM@WURQ (VSM = 20V): 2V<br>VIM@WURQ (VSM = 30V): 2.5V<br>合格     |    |

| SDCI_TC_0024 | TCM_PHYL_INTF_TWUL  |                                                                        | ファンクション ジエネレータからのウェークアップ パルス | TWUL@WURQ (VSM = 20V): 80μs<br>TWUL@WURQ (VSM = 30V): 80μs<br>合格 |    |

### 3.2.2.6 各ポートの電流センス

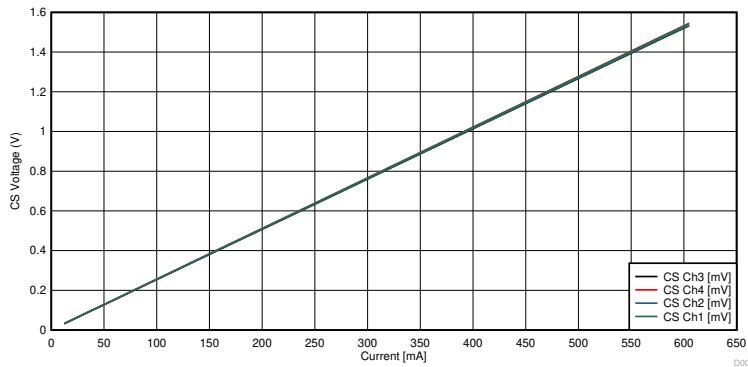

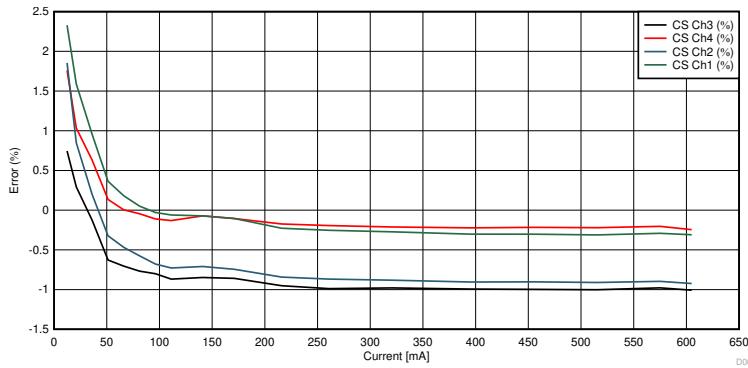

TPS4H160 デバイスの電流センスをテストするため、選択ピンを適切に設定することで各チャネルを選択します。デバイスには 24V で電力が供給され、すべてのチャネルに可変電流シンクが負荷されます。電流センス出力は電圧計に接続されています。一度に 1 つのチャネルがテストされ、結果を図 3-12 および図 3-13 に示します。

図 3-12. TPS4H160 の出力電圧と電流との関係

図 3-13. 電流測定の誤差

誤差は、出力電圧を電流に変換することで計算されます:  $I[\text{mA}] = 300 / 768 \times U \times 1000$ 。誤差は、 $E[\%] = (I_{\text{TPS}} - I_{\text{is}}) / I_{\text{is}}$  によって計算できます。

### 3.2.2.7 TPS4H160 の熱動作

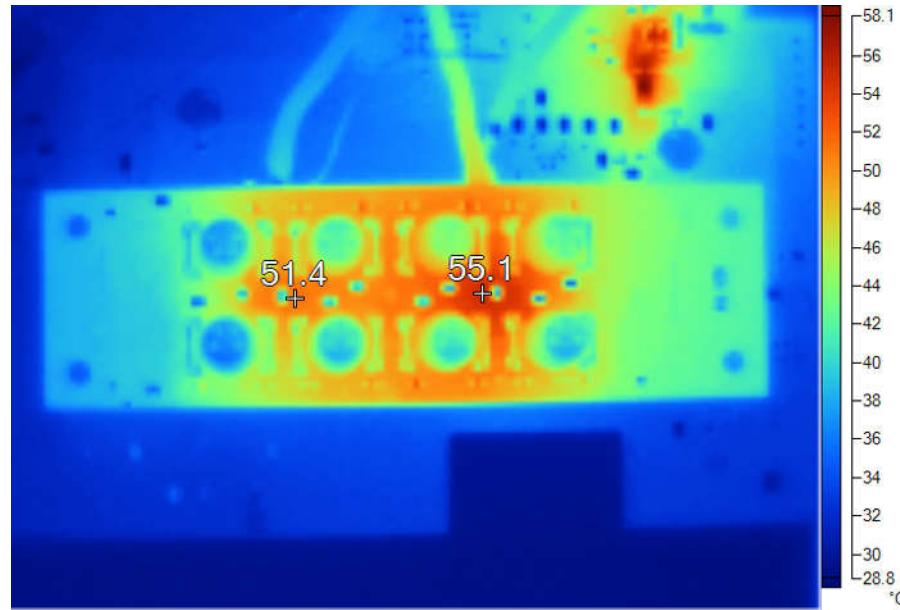

TPS4H160 デバイスにはポートあたり 1A の負荷がかけられ、8 ポートすべてがオンにされています。図 3-14 は、室温でのボードの熱画像を示しています。また、このデザインは、85°C の周囲温度で過熱せずに 1A を処理することもできます。

図 3-14. ポートごとの 1A 負荷時の IO-Link® マスタの熱画像

## 4 デザイン ファイル

### 4.1 回路図

回路図をダウンロードするには、[TIDA-010016](#) のデザイン ファイルを参照してください。

### 4.2 部品表

部品表 (BOM) をダウンロードするには、[TIDA-010016](#) のデザイン ファイルを参照してください。

### 4.3 PCB レイアウトに関する推奨事項

#### 4.3.1 レイアウト プリント

レイヤ プロットをダウンロードするには、[TIDA-010016](#) のデザイン ファイルを参照してください。

### 4.4 Altium プロジェクト

Altium Designer® のプロジェクト ファイルをダウンロードするには、[TIDA-010016](#) のデザイン ファイルを参照してください。

### 4.5 ガーバー ファイル

ガーバー ファイルをダウンロードするには、[TIDA-010016](#) のデザイン ファイルを参照してください。

### 4.6 アセンブリの図面

アセンブリの図面をダウンロードするには、[TIDA-010016](#) のデザイン ファイルを参照してください。

## 5 ソフトウェア ファイル

ソフトウェア ファイルをダウンロードするには、[TIDA-010016](#) のデザイン ファイルを参照してください。

## 6 関連資料

1. IO-Link コンソーシアム、[IO-Link テスト仕様書、バージョン 1.1.2](#)

2. IO-Link コンソーシアム、[IO-Link インターフェイス、システム仕様バージョン 1.1.2](#)

3. IO-Link コンソーシアム、[IO-Link パッケージ 2015 & Corrigendum Version 1.0](#)

4. テキサス・インスツルメンツ、[センサ向けの適切な産業用通信規格の選定](#)

### 6.1 商標

TI E2E™ is a trademark of Texas Instruments.

IO-Link® are registered trademarks of Profibus User Organization.

Altium Designer® is a registered trademark of Altium LLC or its affiliated companies.

すべての商標は、それぞれの所有者に帰属します。

## 7 著者について

STEFFEN GRAF は、テキサス インスツルメンツのシステム エンジニアであり、産業用部門でのリファレンス デザイン開発を担当しています。彼は、ドイツのダルムシュタットにある応用科学大学で電気工学の修士号を取得しています。

## 8 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| Changes from Revision B (December 2018) to Revision C (March 2021) | Page              |

|--------------------------------------------------------------------|-------------------|

| • ドキュメント全体にわたって表、図、相互参照の採番方法を更新。.....                              | <a href="#">1</a> |

| • 小型ソリューションである TPS274160 デバイスのサポートを追加。.....                        | <a href="#">5</a> |

---

| Changes from Revision A (November 2018) to Revision B (December 2018) | Page              |

|-----------------------------------------------------------------------|-------------------|

| • <i>scaleable</i> を拡張可能に変更.....                                      | <a href="#">1</a> |

---

| Changes from Revision * (July 2018) to Revision A (November 2018) | Page              |

|-------------------------------------------------------------------|-------------------|

| • O-Link を IO-Link に変更.....                                       | <a href="#">2</a> |

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適した TI 製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月