TI Designs: TIDA-00807

# 架空電力線用故障表示器向け、超低消費電力、障害監視リファレンス・デザイン

## TEXAS INSTRUMENTS

#### **TI Designs**

故障表示器(FI)は、配電ネットワークの架空電力線上に設置され、障害の発生を検出して表示するデバイスです。FIは一定の間隔で何個も設置され、障害の場所を識別することで停電時間を最小限にできます。架空FIの場合、表示はLEDの点滅で行われることがあります。

堅牢なFIを設計するには課題もあり、ノイズへの耐性を持つ信号チェーンと、正確な測定の保証を、低い消費電力で実現する必要があります。このデザインでは、アナログ・フロントエンド(AFE)部品を注意深く選択することで、機能や性能を犠牲にすることなく消費電力を最小化するためのアーキテクチャを紹介します。デューティ・サイクルの使用と、必要に応じてFIの特定のブロックをイネーブルすることで、さらに電力削減が可能です。超低消費電力MCUとAFEとを組み合わせることで、電流と電圧の測定について±2.0%以下の精度を実現できます。自己テスト機構によるシステム診断の実行などの追加機能も、デザインに実装されています。

#### 設計リソース

| TIDA-00807    | デザイン・フォルダ  |

|---------------|------------|

| MSP430FR5728  | プロダクト・フォルダ |

| OPA2317       | プロダクト・フォルダ |

| SN74LVC1G3157 | プロダクト・フォルダ |

| TPS62740      | プロダクト・フォルダ |

| DAC101C081    | プロダクト・フォルダ |

| LM4041-N      | プロダクト・フォルダ |

| LMT87-Q1      | プロダクト・フォルダ |

| DRV5032       | プロダクト・フォルダ |

E2Eエキスパートに質問

#### デザインの特長

- 電流および電圧の測定

- 測定範囲: 0.5~100A、50~300V

- 測定精度: ≤±2%

- 複数のゲイン段とADCチャネルの使用により、広範囲の電流および電圧に対応

- 障害電流検出のスレッショルドをユーザーが設定可能

- 変電所により要求される電流および電圧レベルの測定と記録を行う機構

- 消費電力

- AFEコンポーネントとMCUは、静的消費電流が 350μA未満になるよう選択

- デュアル・レールの構成可能なDC/DCコンバータ (負荷スイッチ内蔵)により、柔軟な電力削減が可能

- 超低消費電力、少ないピン数、占有面積を基準に MCUを選択

- MCUはLPRFおよび高輝度LEDドライブ用の機能 拡張をサポート

- 自己テストおよび診断

- 低消費電力のホール・スイッチを使用して磁石の存在を検出

- 障害電流は10ビットDACによりシミュレートされ、消費電流は2uA未満

- 温度測定はアナログ出力TMPセンサにより実行

デザインの特長 www.tij.co.jp

使用許可、知的財産、その他免責事項は、最終ページにあるIMPORTANT NOTICE(重要な注意事項)をご参照くださいますようお願いいたします。 英語版のTI製品についての情報を翻訳したこの資料は、製品の概要を確認する目的で便宜的に提供しているものです。 該当する正式な英語版の最新情報は、www.ti.comで閲覧でき、その内容が常に優先されます。 TIでは翻訳の正確性および妥当性につきましては一切保証いたしません。 実際の設計などの前には、必ず最新版の英語版をご参照くださいますようお願いいたします。

www.tij.co.jp

## 1 System Description

Electric power systems consists of overhead transmission/distribution lines that carry the power from various generation stations to substations and distribute power to regions occupied with commercial and residential buildings. An occurrence of fault on the overhead line can lead to extended durations of power outages, cause damages to portions or entire power networks, resulting in productivity and economic loss thereby affecting consumers. To minimize the duration of power outages smart Fault Indicator (FI) devices are installed on overhead power lines to identify and indicate occurrence of overcurrent faults on the line. Visual indication aids utility crew members in identifying the location of faults from a distance and service the faults with faster turnaround times.

The features and complexities of Fault Indicators vary on operating environment, wide input current ranges, power consumption, self- test requirements and measurement accuracy. This design provides a robust architecture with a low power AFE, an ultra -low power MCU and a programmable DC-DC converter with an integrated load switch to control the switching on-off of discrete analog front end. Measurement accuracy of ≤±2% is achieved under low power consumption. An additional feature such as self-test mechanism comprising a DAC and Hall switch is implemented in the design. The self-test mechanism generates a test waveform that simulates faults on the line. The benefit of this mechanism is to validate the working of the FI as expected. To achieve low power consumption, devices in the system have been selected carefully with low power consumption numbers, programmable DC converter and various modes implemented in software. The modes implemented in software are:

- Active Mode: MCU Timer configured to sample analog inputs every sec and place the MCU in Low power mode after sampling. The duty cycle can be varied in firmware to achieve low power consumption.

- Standby Mode: The MCU is placed in Low-power standby mode. A comparator remains active to detect a fault greater than a user-defined threshold level and wake the MCU upon any fault activity.

- Self-Test Mode: If a magnet is detected by the hall switch (when the flux density of the magnet exceeds the operating point threshold of (7.5 mT), the hall switch devices open-drain drives a low voltage. The software then enters Self-test mechanism mode to generate a test waveform to validate the sensing circuitry and software computation.

## 2 Key System Specifications

The key specifications of the system are listed in 表 1.

#### 表 1. Key System Specifications

| Number | Parameters                                       | Description                                                                 | Comments                                                      |

|--------|--------------------------------------------------|-----------------------------------------------------------------------------|---------------------------------------------------------------|

| 1      | Threshold detection                              | Range- 3 – 100A                                                             | User configurable Threshold detection levels in software      |

| 2      | Analog Inputs                                    | 4 analog inputs                                                             | Current Inputs - 2 Voltage Input - 1<br>Temperature input - 1 |

| 3      | AC voltage Input range                           | 50-300V AC with resistor divider and fixed-gain amplifier                   | Measurement Accuracy: ±2%                                     |

| 4      | Current Input Range                              | 0.50A to 100A AC with fixed gain amplifier for High Gain and Low Gain Paths | Measurement Accuracy: ±2%                                     |

| 5      | DC Offset Reference                              | VCC/2                                                                       | Unipolar analog inputs, VCC input voltage set to 3.3V         |

| 6      | Power Supply                                     | Wide Vin range 2.2 V-5.5V DC                                                |                                                               |

| 7      | Minimum Flux density to enter Self-<br>Test Mode | Magnetic Threshold – 4 – 11 mT                                              | Magnet distance > 0.5 mm                                      |

| 8      | Temperature Measurement                          | Temperature Range: -50 – 150 °C                                             | Accuracy: ±0.3°C typical                                      |

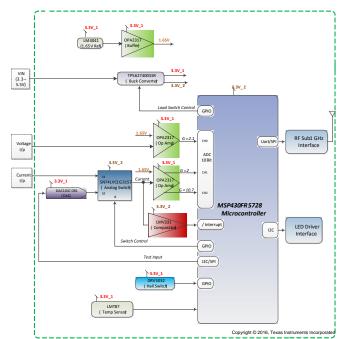

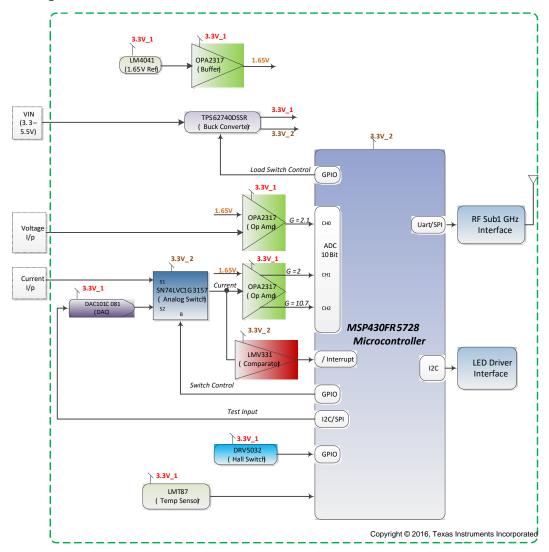

#### 3 Block Diagram

図 1. Block Diagram

The system blocks of this design are based on functionality, details are listed below:

## Current Measurement

- Current inputs are connected to external current transformers with a turns ratio of 2000 to step down the primary current.

- Current input circuitry consists of burden resistors, signal conditioning Op-Amps, reference DC level shift and interface to ADC.

- Current inputs to be sensed by Fault Indicators have wide ranges. To achieve the required accuracy over the wide range of current input, two gain stages are provided for all current inputs.

#### Voltage Measurement

- Voltage input circuit with potential divider circuit divides AC input voltage to a Level that can be measured by ADC. Multiple resistors are used to meet the required voltage rating and also ensure reliability.

- The output of the potential divider is given as input to a differential amplifier. The output of the

www.tij.co.jp Block Diagram

amplifier is connected to the ADCs.

- Single gain stage is provided for the voltage inputs since the expected measurement range is less.

#### MCU handles

- Data sampling by 10-bit Analog-to-Digital converter (ADC).

- Analysis and processing of data to detect faults.

- Control of programmable DC power supply to switch ON-OFF devices.

- Control of analog switch to handle both analog and digital signals.

- Indication of fault occurrence.

#### DC/DC converter

- Programmable DC/DC converter with integrated load switch is beneficial as it provides flexibility to connect or disconnect other system devices to DC-DC converter and reduce the power consumption during the normal operating conditions without fault.

- Control of device power supply is achieved by control signal from the microcontroller.

- Load switch rail is tied to Op-Amp, DAC, Hall Switch, Temperature Sensor, DC offset devices

- Self-Test/Diagnostic Mechanism

- The self-test mechanism is implemented with Hall Switch and external DAC to identify defective devices on the line.

- A magnet with operating magnetic flux > 7.5 mT is placed over the hall switch to trigger a flag and place the device in self-test mode. The software then enters self-test mechanism mode to generate a test waveform to validate the sensing circuitry and software computation.

#### · Reference Offset

The reference is configured depending on the input and level shifted by VCC/2. The DC offset is level shifted for both Voltage and Current measurement to VCC/2 by using a precision shunt voltage reference and Op-Amp for both voltage and current reference.

#### · LED Driver Interface

4 pin header Interface to connect modular board with high intensity LED's for fault indication.

#### Temperature Sensor

- Temperature sensors with an analog output voltage that is linearly and inversely proportional to temperature to monitor temperature.

- Interface to ADC

#### Comparator

User configurable threshold detection levels to wake the MCU from low power mode.

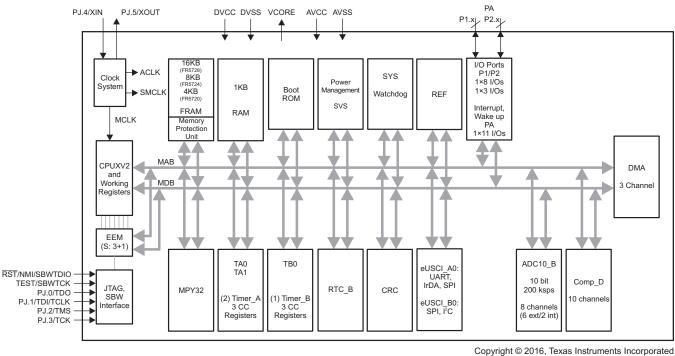

#### Microcontroller - MSP430FR5728 MCU 3.1

The MSP430FR5728 ultra-low-power microcontroller (MCU) consists of multiple features embedded FRAM nonvolatile memory, ultra-low-power 16-bit MSP430™ CPU, and different peripherals targeted for various applications. The architecture, FRAM, and peripherals, combined with seven low-power modes, are optimized to achieve extended battery life in portable and wireless sensing applications. FRAM is a new nonvolatile memory that combines the speed, flexibility, and endurance of SRAM with the stability and reliability of flash, all at lower total power consumption.

Peripherals include a 10-bit ADC, a 16-channel comparator with voltage reference generation and hysteresis capabilities, three enhanced serial channels capable of inter-integrated circuit (12C), serial peripheral interface (SPI), or universal asynchronous receiver/transmitter (UART) protocols, an internal DMA, a hardware multiplier, an real-time clock (RTC), five 16-bit timers, and digital I/Os. 表 2 provides the design features of MSP430FR5728 MCU and 🗵 2 shows the functional block diagram.

| FRAM       | 16K                                                     |

|------------|---------------------------------------------------------|

| SRAM       | 1K                                                      |

| I/O        | Up to 21                                                |

| ADC        | 10-bit ADC, 8 Channels externally , 2 channels internal |

| USCI       | 1                                                       |

| SPI        | 1                                                       |

| Comparator | 12 Channels                                             |

| 12C        | 1                                                       |

| Package    | TSSOP (28)                                              |

表 2. MSP430FR5728 Design Features

図 2. MSP430FR5728 Functional Block Diagram

#### 3.2 Operational Amplifier – OPA2317

The OPA317 series of CMOS operational amplifiers offer precision performance at a very competitive price. These devices are members of the Zero-Drift family of amplifiers that use a proprietary Auto calibration technique to simultaneously provide low offset voltage (90  $\mu$ V max) and near-zero drift over time and temperature at only 35  $\mu$ A (max) of quiescent current.

The OPA317 family features rail-to-rail input and output in addition to near flat 1/f noise, making this amplifier ideal for many applications, and much easier to design into a system. These devices are optimized for low-voltage operation as low as  $\pm 1.8 \text{ V} (\pm 0.9 \text{ V})$  and up to  $\pm 5.5 \text{ V} (\pm 2.75 \text{ V})$ . The OPA317 (single version) is available in the SC70-5, SOT23-5, and SOIC-8 packages. The OPA2317 (dual version) is offered in MSOP-8 and SOIC-8 packages.

The features of rail-to-rail I/O Operational Amplifier are:

Supply Voltage: 1.8 V to 5.5 V

Low Offset Voltage: 20 μV (typ)

CMRR: 108 dB (typ)

Quiescent Current: 35 μA (max)

· Gain Bandwidth: 300 kHz

• Rail-to-Rail Input/Output

Internal EMI/RFI Filtering

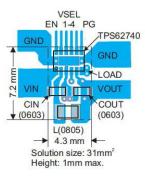

## 3.3 Power Supply - TPS62740

The TPS62740 is industry's first step down converter featuring typ 360 nA quiescent current and operating with a tiny 2.2  $\mu$ H inductor and 10  $\mu$ F output capacitor. This new DCS-control-based device extends the light load efficiency range below 10  $\mu$ A load currents. This has the following features:

- Input voltage range VIN from 2.2 V to 5.5 V

- Typical 360 nA quiescent current

- Up to 90% efficiency at 10-µA output current

- Up to 300 mA output current

- RF friendly DCS-control

- Up to 2 MHz switching frequency

- · Low output ripple voltage

- Automatic transition to no ripple 100% mode

- Slew rate controlled load switch

- Discharge function on VOUT/LOAD

- Power good output

- Optimized for operation with a tiny 2.2 μH inductor and 10 μF COUT

- Small 2 x 3 mm2 SON package

Slew rate controlled switch is used to switch on-off the peripheral supply to reduce the power consumption during the normal operating conditions without fault. This control of peripheral power supply is achieved by control signal from the controller. To obtain the output voltage setting, see  $\gtrsim$  3. The output configured in this application is 3.3 V.

www.tij.co.jp Block Diagram

#### 表 3. TPS67240 Output Voltage Settings

| VOUT | VSEL 4 | VSEL 3 | VSEL 2 | VSEL 1 |

|------|--------|--------|--------|--------|

| 3.0V | 1      | 1      | 0      | 0      |

| 3.1V | 1      | 1      | 0      | 1      |

| 3.2V | 1      | 1      | 1      | 0      |

| 3.3V | 1      | 1      | 1      | 1      |

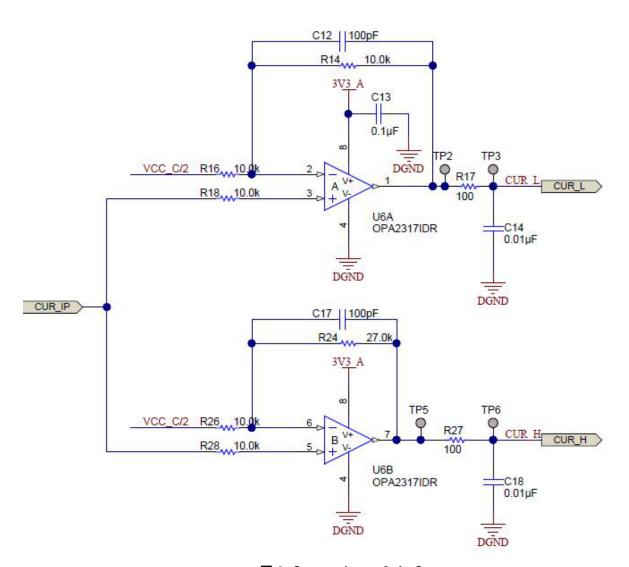

#### 3.4 Current Inputs

The design provides provision to measure one current input and an external current transformer is used to step down the primary current. The current transformer ratio used in the design is 1:2000. The current inputs to be sensed by FCI have wide ranges and may not be able to sense the complete range of current inputs with a single 10-bit ADC range within the required accuracy. To achieve the required accuracy over the wide range of current input, two gain stages are provided for all current inputs.

The gains configured are indicative gains and these gains may change based on the application and the range of currents to be measured.

High gain stage: When the input current is less, the amplification is more. Gain value is currently set to 10.7

Low gain stage: When the input current is High, the amplification is reduced. Gain value is currently set to 2.

図 3. Current Input Gain Stages

#### 3.5 Voltage Inputs

The 120-V or 230-V AC input is divided by the Potential divider to a Level that can be measured by the ADC. Multiple resistors are used to meet the required voltage rating and also ensure reliability. The output of the potential divider is given as input to a differential amplifier. The output of the amplifier is connected to the ADCs. Single gain stage is provided for the voltage inputs since the expected measurement range is less.

#### 3.6 Precision Shunt Voltage Reference - LM4041-N

The LM4041 series of shunt voltage references are versatile, easy-to-use references suitable for a wide array of applications. The advanced design of the LM4041-N eliminates the need for an external stabilizing capacitor while ensuring stability with any capacitive load, thus making the LM4041-N easy to use. Further reducing design effort is the availability of a fixed (1.225 V) and adjustable reverse breakdown voltage.

www.tij.co.jp Block Diagram

Additionally, the reference offers low dynamic impedance, low noise, and a low temperature coefficient to ensure a stable output voltage over a wide range of operating currents and temperatures. The LM4041 uses fuse and Zener-zap reverse breakdown voltage trim during wafer sort to ensure that the prime parts have an accuracy of better than ±0.1% (A grade) at 25°C. Thus, a great deal of flexibility is offered to designers in choosing the best cost-to-performance ratio for their applications. The LM4041 is available in a fixed (1.225 V nominal) or an adjustable version, which requires an external resistor divider to set the output to a value between 1.225 V and 10 V.

#### **Features**

- Small packages: SOT23, SC70 and TO-92

- No output capacitor required

- Output voltage tolerance ±0.1% (max) at 25°C

- Low output noise: 20 μVrms (10Hz to 10kHz)

- Wide operating current range: 60 μA to 12 mA

- Extended temperature range: -40°C to +125°C

- Low temperature coefficient: 100 ppm/°C (max)

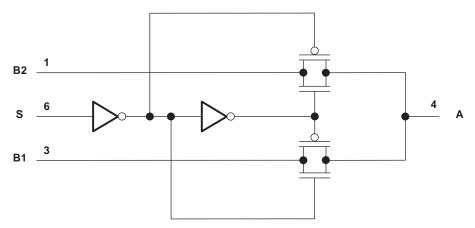

## 3.7 Single-Pole, Double-Throw Analog Switch - SN74LVC1G3157

This single-pole double-throw (SPDT) analog switch is designed for 1.65-V to 5.5-V VCC operation. The SN74LVC1G3157 device can handle both analog and digital signals. The SN74LVC1G3157 device permits signals with amplitudes of up to VCC (peak) to be transmitted in either direction.

図 4. Logic Diagram (Positive Logic)

The 1.65-V to 5.5-V supply operation allows the device to function in many different systems comprised of different logic levels (see 24), allowing rail-to-rail signal switching. Either the B1 channel or the B2 channel is activated depending upon the control input. If the control input is low, B1 channel is selected. If the control input is high, B2 channel is selected.

Applications include signal gating, chopping, modulation or demodulation (modem), and signal multiplexing for analog-to-digital converter (ADC) and digital-to-analog conversion systems.

#### **Features**

- 1.65-V to 5.5-V VCC Operation

- Useful for Both Analog and Digital Applications

- Rail-to-Rail Signal Handling

- Operating Frequency Up to 300 MHz

- High Degree of Linearity

- High Speed, Typically 0.5 ns

- $(V_{CC} = 3 \text{ V}, CL = 50 \text{ pF})$

- Low ON-State Resistance, Typically ≠6 Ω

- $(V_{CC} = 4.5 \text{ V})$

- ESD Protection Exceeds JESD 22

#### 3.8 10-Bit DAC With I2C-Compatible Interface - DAC101C081

The DAC101C081 device is a 10-bit, single channel, voltage-output DAC that operates from a 2.7 V to 5.5 V supply. The output amplifier allows rail-to-rail output swing and has an 6-µsec settling time. The DAC101C081 uses the supply voltage as the reference to provide the widest dynamic output range and typically consumes 132 µA while operating at 5.0 V. It is available in 6-lead SOT and WSON packages and provides three address options (pin selectable).

The DAC101C081 use a 2-wire, I2C-compatible serial interface that operates in all three speed modes, including high speed mode (3.4 MHz). An external address selection pin allows up to three DAC101C081 devices per 2-wire bus. Pin compatible alternatives to the DAC101C081 are available that provide additional address options.

The DAC101C081 each have a 16-bit register that controls the mode of operation, the power-down condition, and the output voltage. A power-on reset circuit ensures that the DAC output powers up to zero volts. A power-down feature reduces power consumption to less than a microWatt. Their low power consumption and small packages make these DACs an excellent choice for use in battery operated equipment. Each DAC operates over the extended industrial temperature range of -40°C to +125°C.

#### **Features**

- Ensured Monotonicity to 10-bits

- Low Power Operation: 156-µA maximum at 3.3 V

- Extended Power Supply Range (2.7 V to 5.5 V)

- I2C-Compatible 2-Wire Interface Which Supports Standard (100-kHz), Fast (400-kHz), and High-Speed (3.4-MHz) Modes

- Rail-to-Rail Voltage Output

- Very Small Package

- Resolution: 10 Bits

- INL: ±2 LSB (Maximum)

- DNL: +0.3/–0.2 LSB (Maximum)

- Setting Time: 6-µs (Maximum)

- Zero Code Error: +10-mV (Maximum)

- Full-Scale Error: -0.7 %FS (Maximum)

www.tij.co.jp Block Diagram

#### 3.9 Low Power Digital-Switch Hall Effect Sensor – DRV5032

The DRV5032 is an automotive-qualified low-power digital-switch Hall effect sensor.

When the applied magnetic flux density exceeds the BOP threshold, the device's open-drain output drives a low voltage. When the flux density decreases below the BRP threshold, the output becomes high-impedance. Integrated hysteresis separates BOP and BRP to provide robust crossovers.

By incorporating an internal oscillator, the DRV5032 samples the magnetic field and updates the output every 3 ms, using just 14  $\mu$ A when powered from 5 V. This low-latency low- current draw sensor is suitable for automotive systems that need continuous monitoring when the engine is off.

The DRV5032 operates from a VCC range of 1.65 to 5.5 V, and supports a Grade 2 ambient temperature range of -40°C to 105°C temperature range of -40°C to 105°C.

#### 3.10 Single General Purpose Low-Voltage Comparator – LMV331

The LMV393 and LMV339 devices are low-voltage (2.7 V to 5.5 V) versions of the dual and quad comparators, LM393 and LM339, which operate from 5 V to 30 V. The LMV331 is the single-comparator version.

The LMV331, LMV339, and LMV393 are the most cost-effective solutions for applications where low-voltage operation, low power, and space saving are the primary specifications in circuit design for portable consumer products. These devices offer specifications that meet or exceed the familiar LM339 and LM393 devices at a fraction of the supply current.

#### **Features**

- 2.7-V and 5-V Performance

- Low Supply Current

- LMV331 130 μA Typ

- LMV393 210 μA Typ

- LMV339 410 μA Typ

- Input Common-Mode Voltage Range Includes Ground

- Low Output Saturation Voltage 200 mV Typical

- Open-Collector Output for Maximum Flexibility

#### 3.11 Reference Voltage

When AC input is applied, the ADC input has to be level shifted to VCC/2 to measure the AC waveform.

The DC offset is level shifted for both Voltage and Current measurement to VCC/2, and the Op-Amp is used for both voltage and current reference.

Software www.tij.co.jp

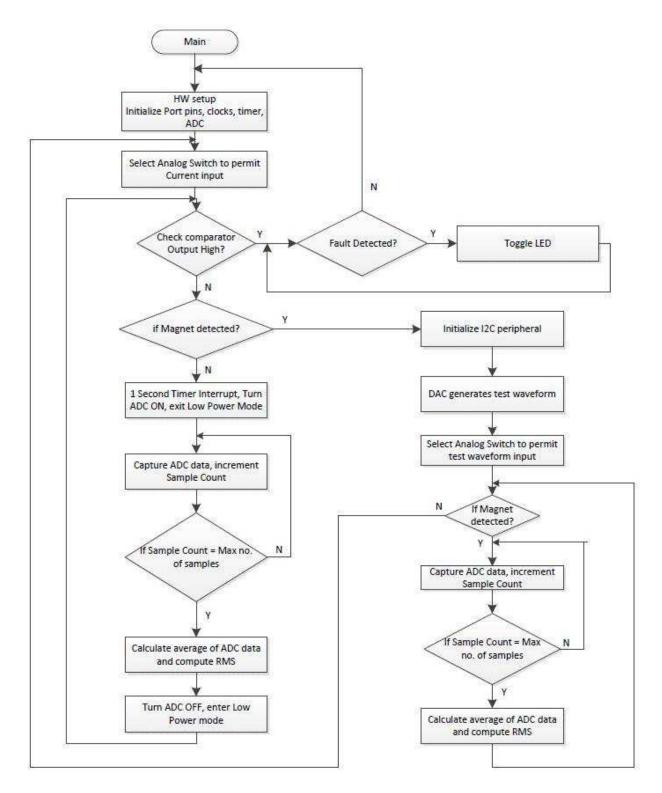

#### 4 Software

This section describes the software flow to process analog inputs, check for over current faults and indicate the occurrence of faults. Figure 5 shows a high-level software flow of the application.

The software implements the modes listed below:

- Active Mode: MCU Timer configured to sample analog inputs every sec and place the MCU in Low power mode after sampling. The duty cycle can be varied in firmware to achieve low power consumption.

- Standby Mode: The MCU is placed in Low-power standby mode. A comparator remains active to detect a fault greater than a user-defined threshold level and wake the MCU upon any fault activity.

- Self-Test Mode: If a magnet is detected by the hall switch (when the flux density of the magnet exceeds the operating point threshold (7.5 mT)), the hall switch devices open-drain drives a low voltage. The software then enters Self-test mechanism mode to generate a test waveform to validate the sensing circuitry and software computation.

The firmware is setup to monitor comparator input, magnet detection and follow the flow as shown in the Figure 5 based on the activity decision. If no activity is detected on comparator input (High Current inputs > 90 A) and Hall switch (magnet detection) the firmware enters Active Mode.

In Active mode MCU timer is configured at 1 sec interval to wake up MCU, sample 64 samples of data conditioned by the Op-Amp on current and voltage lines. The captured samples are stored in a buffer, processed and analyzed in software to check the line status and detect if a fault is detected. If a fault is detected a LED on the board is toggled to indicate occurrence of fault. If a fault is not detected, the firmware places MCU in Low power mode and wakes up the MCU on the next 1 sec timer interrupt to capture data samples and process the data. The benefit of varying the duty cycle and placing the devices in LPM mode helps in achieving low system power consumption numbers. The duty cycle can be varied in software based on the application requirement. To achieve system low power consumption numbers the MCU is placed in LPM mode and programmable DC converter disconnects the load switch rail. The current software is configured to 16% duty cycle and the average current consumption at 8MHz CPU frequency is < 500  $\mu$ A (Active Mode + (MCU in LPM mode and LDO ON)).

If a magnet is detected by the hall switch (when the flux density of the magnet exceeds the operating point threshold (7.5 mT)), the hall switch devices open-drain drives a low voltage. The software then enters Self-test mechanism mode to generate a test waveform to validate the sensing circuitry and software computation.

www.tij.co.jp Software

図 5. High Level Software Flow

Software www.tij.co.jp

#### 4.1 Initialization Routine

The program execution for the initialization routine is shown below during power-up:

- Watch dog

- Disable the watchdog timer

- System Clock

- Initialize the system clock to 8 Mhz DCO.

- Load switch control pin for TPS62740

- · Input pin selected to read comparator output

- Analog switch control pin selected for current input

- LED pins

- Configure the LED port pins as GPIO and initialize the LED ports as output.

- ADC10

- Initialize timer to trigger ADC conversions

- Configure the ADC10 port pins to peripheral mode

- Configure ADC DMA and enable DMA interrupts

#### 4.2 Self Test

When a magnet (http://www.digikey.com/product-detail/en/radial-magnet-inc/8031/469-1014-ND/2810356) is placed near the hall switch and the detected magnetic flux exceeds 7 mT, an output low signal is generated by the Hall switch. In the software a test mode flag is set to indicate magnet detection during which the following peripherals are set:

- · Initialize I2C communication with DAC

- Analog switch control pin selected for test waveform input

For magnet detection case, the program flow can be followed by referring to 🗵 5.

#### 4.3 RMS Calculation

The ADC samples for the selected channels are read and stored in a buffer. The sampled data is corrected for offset by subtracting the DC offset (1.65 V) from each ADC samples for the corresponding channel. This process is repeated for all channels. The offset corrected samples are copied into a bugger until the required number of samples (64 samples) is reached. The RMS is calculated and multiplied with the gain factor (High and Low gain factors).

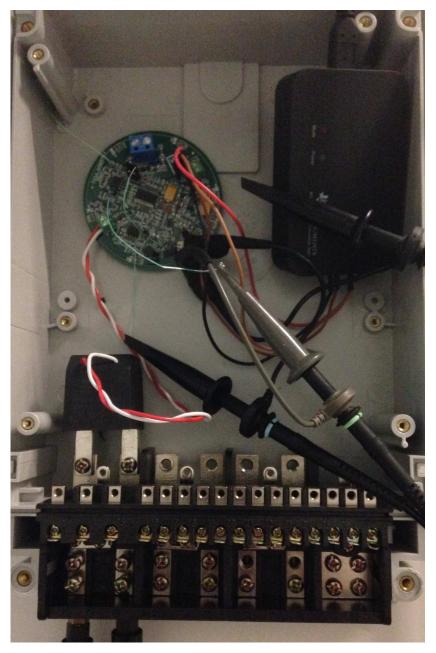

#### 5 Test Setup

Follow the steps provided below to setup the hardware for testing:

- 1. Power Supply A DC input of 3.3 V DC can be applied to connector J5. The TPS62740 DC-DC converter on the hardware provides an output of 3.3V to power the MCU.

- 2. Jumper JP2 Connect Jumper JP2 to ensure 3.3V DC is fed to power the Microcontroller.

- 3. Current Inputs connect an external current transformer with a turns ratio of 2000:1 to connector J3 to feed current inputs to ADC channels of MCU for processing.

- 4. Voltage Inputs Connector J4 is provided on the board to provide a provision to apply AC voltage inputs.

- 5. AC Source: To run the tests a programmable AC source with current adjustable up to 30A has been

www.tij.co.jp Test Setup

used. The currents were measured with a Metering reference meter of error <±0.1%. Current inputs from programmable AC source are applied to connector J3 and AC Voltages from programmable AC source are applied to connector J4.

図 6. Test Setup

Test Data www.tij.co.jp

#### 6 Test Data

The focus of this design is to test the performance of the system, achieve Accuracy measurements of ±2%, showcase Self-Test Mechanism and highlight the various methods implemented in hardware and software to achieve low-power consumption.

#### 6.1 Current Accuracy

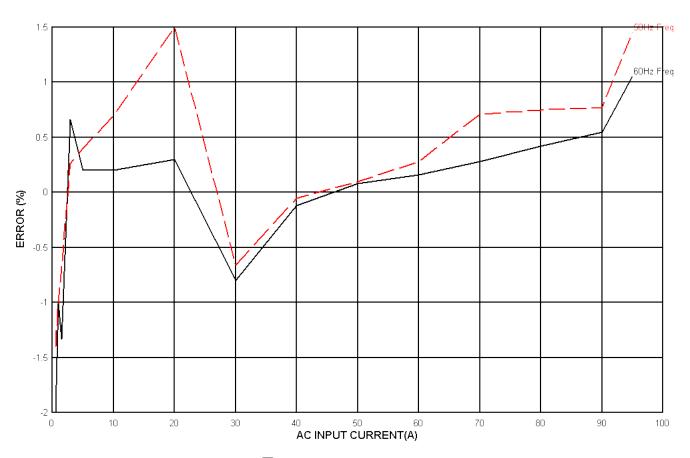

表 4 provides power measurement accuracy results for Current Transformer inputs with Nominal frequency of 50 Hz and 60 Hz. The accuracy results achieved is < +2%.

The highlighted yellow rows in 表 5 showcase the overlapping current inputs between CUR\_L and CUR\_H gain paths. 表 5 indicates that CUR\_L gain path is optimal for current inputs > 20A and CUR\_H gain path for current inputs <=20A.

注: CUR\_L represents the low gain path accuracy results and CUR\_H represents the High gain path accuracy results.

表 4. Current Accuracy

|             | 60 Hz FREQUENCY |       | 50 Hz FREQUENCY |       |

|-------------|-----------------|-------|-----------------|-------|

| CURRENT (A) | CUR_L           | CUR_H | CUR_L           | CUR_H |

| 0.5         |                 | -2.00 |                 | -1.40 |

| 1           |                 | -1.00 |                 | -1.00 |

| 1.5         |                 | -1.33 |                 | -0.66 |

| 3           |                 | 0.66  |                 | 0.26  |

| 5           |                 | 0.20  |                 | 0.40  |

| 10          | -1.50           | 0.20  | -1.70           | 0.70  |

| 20          | -1.10           | 0.30  | -1.05           | 1.50  |

| 30          | -0.80           |       | -0.66           |       |

| 40          | -0.12           |       | -0.05           |       |

| 50          | 0.08            |       | 0.10            |       |

| 60          | 0.16            |       | 0.28            |       |

| 70          | 0.28            |       | 0.71            |       |

| 80          | 0.42            |       | 0.75            |       |

| 90          | 0.55            |       | 0.77            |       |

| 95          | 1.05            |       | 1.45            |       |

www.tij.co.jp Test Data

図 7. Current Accuracy Plot

## 6.2 Voltage Accuracy

表 5 provides the voltage accuracy measurement results.

**60 Hz FREQUENCY 50 Hz FREQUENCY VOLTAGE (V) ACCURACY ACCURACY** 50 -1.60 -1.60 75 -0.80 -0.80 100 -0.60 -0.40 125 -1.12 -1.12 150 -1.33 -1.60 175 -1.04 -1.14 -1.00 200 -1.50 225 -1.33 -1.33 250 -0.16 -0.64

-0.36

表 5. Voltage Accuracy

#### 6.3 Current Consumption

Table 6 provides a list of condition/modes with device state (Powered/Unpowered) to highlight the modes available to achieve low system power consumption.

275

-0.36

Test Data www.tij.co.jp

The current consumption test was measured by measuring the current across jumper JP2.

注: Time to wakeup MCU from LPM3 mode to Active mode is between 78-120 µSec.

#### 表 6. Current Consumption

| CONDITION/MODE                                        | DEVICE STATE                                                                                      | CURRENT  | CLOCKS | DETAILS                 |

|-------------------------------------------------------|---------------------------------------------------------------------------------------------------|----------|--------|-------------------------|

| Continuous Sampling of input Data (no fault detected) | All devices powered                                                                               | 1.75 mA  | 8 MHz  |                         |

|                                                       |                                                                                                   | 700 µA   | 1 MHz  |                         |

| Continuous Sampling of input                          | All devices powered                                                                               | 3.75 mA  | 8 MHz  | LED ON indicating fault |

| Data (fault detected)                                 |                                                                                                   | 2.70 mA  | 1 MHz  | occurrence              |

| Standy Mode (MCU in LPM3                              | All devices powered                                                                               | 500 μΑ   | 8 MHz  | No sampling of Data     |

| mode)                                                 |                                                                                                   | 500 μΑ   | 1 MHz  |                         |

| Standby Mode (MCU in LPM3 mode)                       | Comparator and MCU powered with all other devices unpowered                                       | < 15 µA  | 8 MHz  | No sampling of Data     |

|                                                       |                                                                                                   | < 15 µA  | 1 MHz  |                         |

| Active Mode (Duty cycle 2%)                           | Active Time: All devices powered<br>Standby Time: Only comparator powered with<br>MCU in LPM mode | < 100 µA | 8 MHz  |                         |

|                                                       |                                                                                                   | < 50 μΑ  | 1 MHz  |                         |

| Active Mode (Duty cycle 10%)                          | Active Time: All devices powered<br>Standby Time: Only comparator powered with<br>MCU in LPM mode | < 200 µA | 8 MHz  |                         |

|                                                       |                                                                                                   | < 100 μΑ | 1 MHz  |                         |

| Active Mode (Duty cycle 50%)                          | Active Time: All devices powered<br>Standby Time: Only comparator powered with<br>MCU in LPM mode | < 900 µA | 8 MHz  |                         |

|                                                       |                                                                                                   | < 450 μΑ | 1 MHz  |                         |

| Active Mode (Duty cycle 90%)                          | Active Time: All devices powered<br>Standby Time: Only comparator powered with<br>MCU in LPM mode | < 1.6 mA | 8 MHz  |                         |

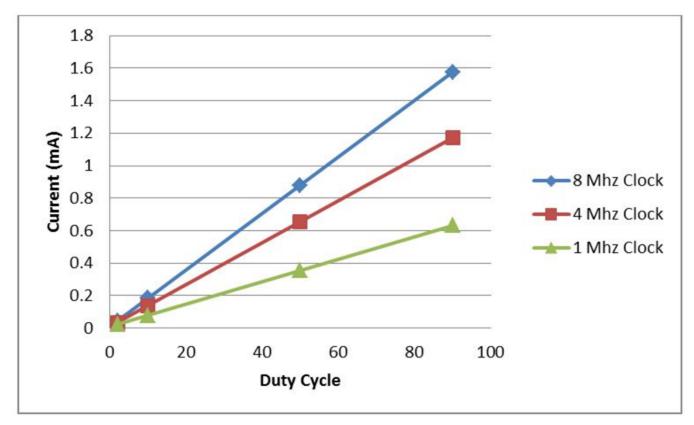

図 8. Current Consumption Plot

www.tij.co.jp Test Data

#### 6.4 Self-Test Mode

Fault Indicator designs require in-field testing to ensure the device is working as expected and identify defective devices. The Self-Test mode was validated by placing a magnet (http://www.digikey.com/product-detail/en/radial-magnet-inc/8031/469-1014-ND/2810356) at a distance of 5 mm over the hall switch. An output low signal is generated by Hall switch, then the software enters Self-Test mechanism mode. In this mode the test waveform (10A) generated by DAC is fed to sensing circuitry to validate the Analog front end and software computation. The LED is toggled to indicate successful validation of device.

#### 6.5 DAC Measurement

表 7 shows the current accuracy results for test waveforms generated by DAC.

| CURRENT (A) | CUR_L | CUR_H |

|-------------|-------|-------|

| 1           |       | 0.50  |

| 5           |       | 0.80  |

| 10          |       | 1.00  |

| 20          |       | 1.40  |

| 30          | 0.32  |       |

| 50          | 0.65  |       |

| 90          | 1.20  |       |

表 7. DAC measurement - Current Accuracy

## 6.6 Temperature Sensor Measurement

The output voltage of temperature sensor was measured at room temperature, and the corresponding operating temperature was obtained from the *LMT87/LMT87-Q1 Transfer* table in the *LLMT87/LMT87-Q1 SC70/TO-92 Analog Temperature Sensors with Class-AB Output Data Sheet* (SNIS170). The obtained temperature measurement was within ±0.3°C accuracy of reference room temperature.

#### 7 Design Files

#### 7.1 Schematics

To download the schematics, see the design files at TIDA-00807.

#### 7.2 Bill of Materials

To download the bill of materials (BOM), see the design files at TIDA-00807.

#### 7.3 PCB Layout Recommendations

#### 7.3.1 OPA2317 Layout Guidelines

Attention to good layout practice is always recommended. Keep traces short and, when possible, use a printed circuit board (PCB) ground plane with surface-mount components placed as close to the device pins as possible.

Place a 0.1-μF capacitor closely across the supply pins. Apply these guidelines throughout the analog circuit to improve performance and provide benefits, such as reducing the electromagnetic interference (EMI) susceptibility.

Design Files www.tij.co.jp

Optimize circuit layout and mechanical conditions for lowest offset voltage and precision performance. Avoid temperature gradients that create thermoelectric (Seebeck) effects in the thermocouple junctions formed from connecting dissimilar conductors. These thermally-generated potentials can be made to cancel by assuring they are equal on both input terminals. Other layout and design considerations include:

- Use low thermoelectric-coefficient conditions (avoid dissimilar metals).

- Thermally isolate components from power supplies or other heat sources.

- Shield op amp and input circuitry from air currents, such as cooling fans.

Following these guidelines reduces the likelihood of junctions being at different temperatures, which can cause thermoelectric voltages of 0.1  $\mu$ V/°C or higher, depending on the materials used.

#### 7.3.2 SN74LVC1G3157 Layout Guidelines

TI recommends keeping signal lines as short as possible. TI also recommends incorporating microstrip or stripline techniques when signal lines are greater than 1 inch in length. These traces must be designed with a characteristic impedance of either 50  $\Omega$  or 75  $\Omega$ , as required by the application. Do not place this device too close to high-voltage switching components, as they may interfere with the device.

#### 7.3.3 TPS62740 Layout Guidelines

As for all switching power supplies, the layout is an important step in the design. Care must be taken in board layout to get the specified performance. If the layout is not carefully done, the regulator could show poor line and/or load regulation, stability issues as well as EMI problems and interference with RF circuits. It is critical to provide a low inductance, impedance ground path. Therefore, use wide and short traces for the main current paths. The input capacitor should be placed as close as possible to the IC pins VIN and GND. The output capacitor should be placed close between VOUT and GND pins. The VOUT line should be connected to the output capacitor and routed away from noisy components and traces (for example, SW line) or other noise sources. The exposed thermal pad of the package and the GND pin should be connected. See Figure 6 for the recommended PCB layout.

図 9. Recommended PCB Layout

#### 7.3.4 Layout Prints

To download the layer plots, see the design files at TIDA-00807.

#### 7.4 Altium Project

To download the Altium project files, see the design files at TIDA-00807.

www.tij.co.jp Design Files

#### 7.5 Layout Guidelines

To download the layout guidelines, see the design files at TIDA-00807.

#### 7.6 Gerber Files

To download the Gerber files, see the design files at TIDA-00807.

#### 7.7 Assembly Drawings

To download the assembly drawings, see the design files at TIDA-00807.

#### 8 **Software Files**

To download the software files, see the design files at TIDA-00807.

#### 9 **Related Documentation**

- 1. MSP430FR572x Mixed-Signal Microcontrollers Data Manual

- 2. OPA317, OPA2317, OPA4317 Low Offset, Rail-to-Rail I/O Operational Amplifier Precision Catalog **Data Sheet**

- 3. SN74LVC1G3157 Single-Pole Double-Throw Analog Switch Data Sheet

- 4. TPS6274x 360nA IQ Step Down Converter For Low Power Applications Data Sheet

- DAC101C08xx 10-Bit Micro Power Digital-to-Analog Converter With an I2C-Compatible Interface Data Sheet

- 6. LM4041-N-xx Precision Micropower Shunt Voltage Reference Data Sheet

#### 9.1 商標

MSP430 is a trademark of Texas Instruments.

すべての商標および登録商標はそれぞれの所有者に帰属します。

改訂履歴 www.tij.co.jp

## 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| 2016 | <b>=12</b> 月発行のものから更新 Pag | је |

|------|---------------------------|----|

| • [  | と計リソース 」にDRV5032を 追加      | 1  |

#### TIの設計情報およびリソースに関する重要な注意事項

Texas Instruments Incorporated ("TI")の技術、アプリケーションその他設計に関する助言、サービスまたは情報は、TI製品を組み込んだアプリケーションを開発する設計者に役立つことを目的として提供するものです。これにはリファレンス設計や、評価モジュールに関係する資料が含まれますが、これらに限られません。以下、これらを総称して「TIリソース」と呼びます。いかなる方法であっても、TIリソースのいずれかをダウンロード、アクセス、または使用した場合、お客様(個人、または会社を代表している場合にはお客様の会社)は、これらのリソースをここに記載された目的にのみ使用し、この注意事項の条項に従うことに合意したものとします。

TIによるTIリソースの提供は、TI製品に対する該当の発行済み保証事項または免責事項を拡張またはいかなる形でも変更するものではなく、これらのTIリソースを提供することによって、TIにはいかなる追加義務も責任も発生しないものとします。TIは、自社のTIリソースに訂正、拡張、改良、およびその他の変更を加える権利を留保します。

お客様は、自らのアプリケーションの設計において、ご自身が独自に分析、評価、判断を行う責任がお客様にあり、お客様のアプリケーション(および、お客様のアプリケーションに使用されるすべてのTI製品)の安全性、および該当するすべての規制、法、その他適用される要件への遵守を保証するすべての責任をお客様のみが負うことを理解し、合意するものとします。お客様は、自身のアプリケーションに関して、(1) 故障による危険な結果を予測し、(2) 障害とその結果を監視し、および、(3) 損害を引き起こす障害の可能性を減らし、適切な対策を行う目的での、安全策を開発し実装するために必要な、すべての技術を保持していることを表明するものとします。お客様は、TI製品を含むアプリケーションを使用または配布する前に、それらのアプリケーション、およびアプリケーションに使用されているTI製品の機能性を完全にテストすることに合意するものとします。TIは、特定のTIリソース用に発行されたドキュメントで明示的に記載されているもの以外のテストを実行していません。

お客様は、個別のTIリソースにつき、当該TIリソースに記載されているTI製品を含むアプリケーションの開発に関連する目的でのみ、使用、コピー、変更することが許可されています。明示的または黙示的を問わず、禁反言の法理その他どのような理由でも、他のTIの知的所有権に対するその他のライセンスは付与されません。また、TIまたは他のいかなる第三者のテクノロジまたは知的所有権についても、いかなるライセンスも付与されるものではありません。付与されないものには、TI製品またはサービスが使用される組み合わせ、機械、プロセスに関連する特許権、著作権、回路配置利用権、その他の知的所有権が含まれますが、これらに限られません。第三者の製品やサービスに関する、またはそれらを参照する情報は、そのような製品またはサービスを利用するライセンスを構成するものではなく、それらに対する保証または推奨を意味するものでもありません。TIリソースを使用するため、第三者の特許または他の知的所有権に基づく第三者からのライセンス、あるいはTIの特許または他の知的所有権に基づくTIからのライセンス、あるいはTIの特許または他の知的所有権に基づくTIからのライセンスが必要な場合があります。

TIのリソースは、それに含まれるあらゆる欠陥も含めて、「現状のまま」提供されます。TIは、TIリソースまたはその仕様に関して、明示 的か暗黙的かにかかわらず、他のいかなる保証または表明も行いません。これには、正確性または完全性、権原、続発性の障害に関する保 証、および商品性、特定目的への適合性、第三者の知的所有権の非侵害に対する黙示の保証が含まれますが、これらに限られません。

TIは、いかなる苦情に対しても、お客様への弁護または補償を行う義務はなく、行わないものとします。これには、任意の製品の組み合わせに関連する、またはそれらに基づく侵害の請求も含まれますが、これらに限られず、またその事実についてTIリソースまたは他の場所に記載されているか否かを問わないものとします。いかなる場合も、TIリソースまたはその使用に関連して、またはそれらにより発生した、実際的、直接的、特別、付随的、間接的、懲罰的、偶発的、または、結果的な損害について、そのような損害の可能性についてTIが知らされていたかどうかにかかわらず、TIは責任を負わないものとします。

お客様は、この注意事項の条件および条項に従わなかったために発生した、いかなる損害、コスト、損失、責任からも、TIおよびその代表者を完全に免責するものとします。

この注意事項はTIリソースに適用されます。特定の種類の資料、TI製品、およびサービスの使用および購入については、追加条項が適用されます。これには、半導体製品(http://www.ti.com/sc/docs/stdterms.htm)、評価モジュール、およびサンプル(http://www.ti.com/sc/docs/sampterms.htm)についてのTIの標準条項が含まれますが、これらに限られません。

Copyright © 2017, Texas Instruments Incorporated 日本語版 日本テキサス・インスツルメンツ株式会社