TI Designsリファレンス・デザイン グリッド・インフラストラクチャ・アプリケーション用の10/100Mbps 産業用イーサネット・ブリック、IEEE 1588 PTPトランシーバ(ツイス トペア/光ファイバ)搭載

# TEXAS INSTRUMENTS

# TI Designs リファレンス・デザイン

イーサネット・ベースの通信は、グリッド・アプリケーションで使用される多くのシステムに追加されています。イーサネット・インターフェイスは銅線または光ファイバを使用します。イーサネットにより、グリッドはよりスマートで効率的になります。電力グリッドの運用で、タイミングは常に重要な役割を果たしてきました。スマート・グリッドにおいては、時刻情報の役割が、事後の障害解析で履歴データを相互関連させるためのものから、リアルタイムの分析で迅速な是正動作と自動化運転を行うためのものに変化しています。

イーサネットを使用する場合、IEEE 1588規格のPrecision Time Protocol (PTP)により、ナノ秒精度で時刻を同期できます。IEEE 1588規格のPTPでは、分散システム内の既存のイーサネット・ネットワークで使用するNetwork Time Protocol (NTP)と同等の精度とコスト効果を実現できます。

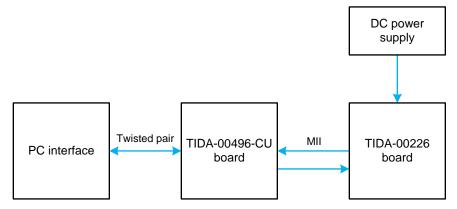

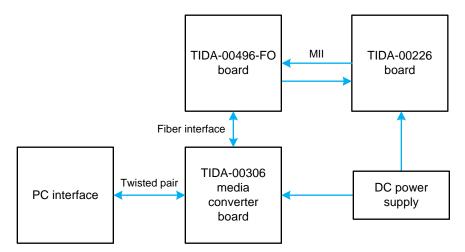

このTI Designは、Precision PHYTER™の機能を実証するための小型イーサネット・ブリックです。PHYTERは、時刻情報をデコードするためTiva™ MCUに接続されています。このTI Designでは、10/100Mbpsの銅線インターフェイスまたは100Mbpsの光ファイバ・インターフェイスと、小型のLCコネクタ付きトランシーバを組み合わせて構成できます。

# 設計リソース

| TIDA-00496    | デザイン・フォルダ  |

|---------------|------------|

| DP83630       | プロダクト・フォルダ |

| TPS75433      | プロダクト・フォルダ |

| TM4C129XNCZAD | プロダクト・フォルダ |

| TPS62177      | プロダクト・フォルダ |

| DP83849       | プロダクト・フォルダ |

| INA196AIDBVR  | プロダクト・フォルダ |

| TPD4E1U06DCK  | プロダクト・フォルダ |

| CDCE913PW     | プロダクト・フォルダ |

E2Eエキスパートに質問

# デザインの特長

- 10/100Mbpsのツイストペア(銅線)インターフェイスと 100BASE-FX光ファイバ・インターフェイスでテスト済み

- DP83630 Precision PHYTERを基盤とし、IEEE 1588 PTPトランシーバはIEEE 1588 V1およびV2に対応

- 消費電力: 銅線、3.3Vにおいて350mW未満

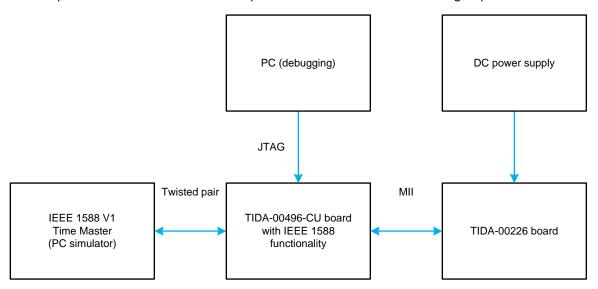

- 通信およびIEEE 1588機能テストのため、Tiva MCU TI Design (TIDA-00226)と接続

- LCコネクタ付きのHFBR-5961L/ALトランシーバ: Fast Ethernet FOインターフェイスに使用した場合、3.3V でトランスミッタ175mA未満、レシーバ120mA未満の消費電力

- 出力定格2AのオンボードLDOを搭載

- リンク、動作、速度を示す3つのプログラム可能LED

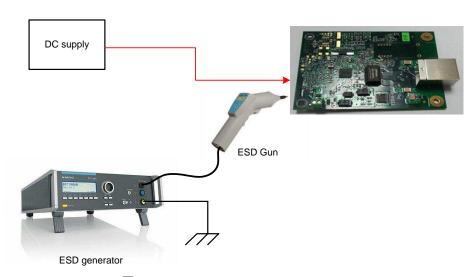

- ESD IEC61000-4-2準拠で6KVまでの接触放電テスト 済み

- 産業用温度範囲: -40℃~85℃でPHYの動作を規定

# 主なアプリケーション

- マージング・ユニット

- IEC61850の機能に対応した保護リレー

- IEC61850に対応した電源品質アナライザ

- デジタル・フォルト・レコーダ

- 変電所自動化用のPTPサーバー

- PTPからPPSへのコンバータ

- IEC61850準拠のイーサネット・スイッチ

使用許可、知的財産、その他免責事項は、最終ページにあるIMPORTANT NOTICE(重要な注意事項)をご参照くださいますようお願いいたします。 英語版のTI製品についての情報を翻訳したこの資料は、製品の概要を確認する目的で便宜的に提供しているものです。 該当する正式な英語版の最新情報は、www.ti.comで閲覧でき、その内容が常に優先されます。 TIでは翻訳の正確性および妥当性につきましては一切保証いたしません。 実際の設計などの前には、必ず最新版の英語版をご参照くださいますようお願いいたします。

# 1 System Description of Electrical Substation

# 1.1 Time Synchronization in a Smart Substation

The generation and distribution of energy is a sophisticated, mature industry. Synchronizing generators, or keeping them in phase at 50 or 60 cycles per second across an electricity grid, is a common and accepted part of their safe and effective management around the world. Not doing so wastes energy and ultimately serious damages the system. Consequently, synchronization has been built into the core power system design for many years. Their growing importance is making time synchronization an integral part of the increasingly sophisticated control systems that are crucial to managing the modern power utility.

Time synchronization plays a pivotal role in two key areas:

- 1. Improving the accuracy of fault diagnosis and the subsequent quality of decision making, which helps reduce down time

- 2. Ensuring electricity networks are operating efficiently within system limits by helping increase the accuracy of control decisions by automatic control and protection equipment

As long as all processes and events in a facility like a substation are controlled from one singular central point, the absolute accuracy of the stations system time is not really important. However, as soon as time-synchronized switching events involving more than one substation have to be performed, the absolute accuracy of each station's time reference gains significant importance.

2

# 1.1.1 Challenges in Substation Timing

Currently, a lot of measurement and control data in the power grid must have an absolute accuracy of approximately 1 ms:

- SCADA data

- · Data from event and disturbance recorders

- Time stamped data from protection relays (IEDs)

- Lightning strike correlation

A time accuracy of 1 ms is relatively easy to reach, but some current and emerging future measurement applications require a much higher accuracy. The applications mentioned in  $\frac{1}{2}$  1, for example, require an absolute accuracy of 1  $\mu$ s or better:

- Sampled values

- · Synchrophasor measurements

- · Traveling wave fault location

表 1. Timing Accuracy for Different Time Sync Protocols

| PROTOCOL | MEDIA    | SYNC ACCURACY |

|----------|----------|---------------|

| NTP      | Ethernet | 1 to 10 ms    |

| IRIG-B   | Coaxial  | 1 to 10 ms    |

| PTP      | Ethernet | 20 to 100 ns  |

# 1.1.2 Approaches for Time Synchronization

There are two main approaches for synchronizing protection relays and other control devices:

- Dedicated timing systems that use stand-alone cabling and repeaters

- Networked timing systems that use Ethernet networking cables and switches shared with other automation applications

# **Dedicated Timing Systems**

Time synchronization systems in substations have historically used a separate distribution system with its own cabling (coaxial, twisted pair, or fiber optic). Two common methods in use are:

- IRIG-B time code, conveying time, and date information along with synchronization pulses

- One pulse per second (PPS), which is a very accurate synchronization pulse that has no time of day or date information

#### **Networked Timing Systems**

The Ethernet networks now widely used for substation automation systems can synchronize the internal clocks of devices throughout a substation. This has the advantage of not requiring additional cabling, but this does require support for suitable protocols by the various protection relays, power quality meters, and other such devices. Two network-based protocols are commonly used: NTP and PTP. Both protocols, when used in substations, work through the exchange of messages over Ethernet. NTP and PTP can compensate for propagation delay through bidirectional communication. NTP is a more established standard and is widely used, but PTP offers greater performance through the use of special networking hardware.

# 1.2 Power System Automation

Power system automation is one of the important aspects in an electrical power network. In power system automation, data acquisition system plays a major role as a base of the power system automation. From the recent trends and developments in power system automation, computerized system automation is most efficient compared to normal systems. A computerized power network for a data acquisition system helps the system and controller to meter and monitor the values for further manipulations for full-scale power system automation and system controlling.

The computerized data acquisition for metering and monitoring of power system automation can be divided into three general categories: data collection, metering, and monitoring. The data collection system collects data from the power system network using the digital power monitors through the current and potential transformers. The collected data will be metered by the digital power monitor consisting of a microcontroller (MCU) with peripherals like memory, an A/D converter, and sample and hold circuitry. According to the programming done in the MCU, the power monitor will store the parameters in the memory and will perform all the logical and arithmetic calculations to manipulate the parameters and to calculate the different power data like KWH, KVAR, KVA, PF, and so on. The collected parameters of the power system and the calculated power data can be monitored on the screen of the digital power monitor. The values are then sent to the computer system using the communication system like serial communication RS-485 and RS-232 for n number of power monitors using the data converter.

# **Structure of Power System Automation**

The functional structure of power system automation will be as follows:

- Electrical protection

- Control

- Measurement

- Monitoring

- Data communications

# **Benefits of Power System Automation**

Important benefits of automation are as follows:

- Improved quality of service and reduced manpower requirements

- · Improved reliability with reduced system implementation costs

- Maintenance and expansion of customer base and reduced operating costs

- High value service provider and reduced maintenance costs

- Added value services with the ability to defer capacity addition projects

- Improved customer access to information and also improved information for engineering decisions

- Enterprise information accessibility along with improved information for planning decisions

- Flexible billing options and reduced customer outage minutes

# 1.3 Classification of Power System Automation

#### 1.3.1 Substation Automation

For many years, substations have been equipped to perform automatic reclosing, bus sectionalizing, load transfers, capacitor switching, and so on. In the past, these and other functions were implemented using a combination of control panels, auxiliary relays, switches, lights, meters, transducers, and extensive wiring and cabling.

Modern protection relays are called intelligent electronic devices (IEDs), which typically consists of one or more protection systems and communications ports. IEDs can transmit data, execute control commands, and frequently provide a local user interface. Typical examples are relays, meters, and specialized sensors.

Only one panel is required when numerical relays are used. Interestingly, at the same time the space requirements are reduced by a factor of four, as is the installed cost. Advances in communications technology tie everything together into a useful network. Within the substation, a single high-speed Local Area Network (LAN) transmits data and control commands, replacing the extensive and costly cables that had been required. At the present time, a number of different LAN techniques and protocols are in use. The industry is actively working on development of a new standard LAN definition that will be based on the use of Ethernet and Manufacturing Messaging Specification (MMS) and will be compatible with the Utility Communications Architecture (UCA<sup>TM</sup>). There are already many techniques for moving data out of the substation to a master station or to other substations. These include the use of leased or dedicated telephone lines, dial-up phone lines, cellular telemetry techniques, satellite transmissions, various flavors of radio techniques, and fiber-optic networks. This variety of communications methods results in the ability to transmit large amounts of information at a rapidly declining cost per bit.

Substation automation components are:

- Remote terminal unit

- Telemetry and remote control device

- IEDs

- Implements functions in a substation, such as a protection relay

- Bay controller

- Controls all devices related to a single bay (transformer, feeder, and so on) and communicates with relays for functionality

- Human machine interface (HMI)

- Typically an industrial PC with operator console for local control and system configuration

- Communication buses

- Connection between devices

- Upwards communication interfaces

- Implemented in the HMI, the bay controller, or an IED

# 1.3.2 Distribution Automation

Distribution automation systems enable an electric utility to monitor, coordinate, and operate system components in a real-time mode from remote locations. The distribution automation is modular and may be implemented in phases to include remote monitoring and control of substation, feeder, and consumer devices and loads.

The goals of distribution automation are:

- Reduced costs

- · Improved service reliability

- Better consumer service

- · Enhanced government relations

#### 1.4 Communication in a Substation

#### 1.4.1 Serial Communication

RS-232, RS-422, and RS-485 are serial communication methods for substation and protection applications. RS-232 is the best known and widely implemented interface. However, some of the other interfaces can be used in situations where RS-232 is not appropriate (for example, for long distances or when there is a need to network multiple devices).

RS-232 is an interface to connect one data terminal equipment (DTE) to one data communication equipment (DCE) at a maximum speed of 20 kbps with a maximum cable length of 50 ft. This was sufficient when almost all computer equipment were connected using modems, but soon after people started to look for interfaces capable of one or more of the following:

- · Connect DTEs directly without modems

- Connect several DTEs in a network structure

- Ability to communicate over longer distances

- Ability to communicate at faster rates

RS-485 is the most versatile communication standard in the standard series defined by the EIA, as it performs well on all four points. That is why RS-485 is currently a widely used communication interface in data acquisition and control applications where multiple nodes communicate with each other.

### 1.4.2 Migration From Serial Communication to Ethernet

Serial communications were traditional in utilities installations; they were well understood and proven, available in robust packaging, and with adequate speed for their time. They required continuous point-to-point connections for operation. However, serial lines have been often associated with proprietary protocols and limited speed. Ethernet connectivity is becoming more popular because it offers standards-based interoperability and performance, along with the hardened characteristics required for many utilities installations. As older substations with serial communications are upgraded, serial interfaces are being replaced by Ethernet connections.

Ethernet's simple and effective design has made it the most popular networking solution at the physical and data link levels. With high speed options and a variety of media types from which to choose, Ethernet is efficient and flexible. These factors and the low cost of Ethernet hardware have made Ethernet an attractive option for industrial networking applications. Also, the opportunity to use open protocols such as TCP/IP over Ethernet networks offers the possibility of a level of standardization and interoperability. The result has been an ongoing shift toward the use of Ethernet for Grid Infrastructure applications. Ethernet is increasingly replacing proprietary communications.

#### 1.4.2.1 Advantages With Ethernet

Because Ethernet is a standard, it is the least expensive way to have connectivity. Being a standard means more choices in products that can connect together and a greater potential for reasonably priced replacement components and long-term support. As a standard, Ethernet is the protocol of choice for new technologies that are being introduced in industrial facilities such as factories and substations. It is more profitable today for developers of technologies such as programmable controllers, dual-ported IEDs, and low-cost security cameras to introduce a product that will work with a large variety of installed

communications devices than to go to the expense of developing specific versions to meet proprietary communications requirements. Further, with Ethernet using fiber cabling, bandwidth is essentially free because it is practically unlimited for a one-time installation cost. An added benefit, of course, is that industrial Ethernet is compatible with IT facilities and eliminates a conversion bottleneck where factory and corporate networks meet.

8

#### 1.4.3 Fiber versus Copper

While fiber cable is preferred for noise immunity, twisted pair cabling also has a role in substations. Within control room rack cabinets, copper cabling is safely used for short Ethernet interconnections. The same twisted pair cable and RJ45 port connectors can be used for both 10-Mbps and 100-Mbps speeds, simplifying installations. The assumption has been that copper cabling is less costly, so most RTU and IED manufacturers use RJ45 ports on their products for both lower cost and 10/100-Mbps compatibility. This makes some use of copper necessary even if only to connect to a nearby media converter.

However, the comparative cost of fiber and UTP copper needs to be re-examined. A recent analysis of the installation costs of copper versus fiber (typical for new substations and upgrades) shows surprisingly little difference.

# 1.4.3.1 Advantages of Fiber Optic

- Galvanic isolated and robust communication interface

- Cabling distance is greater than UTP cable to meet wide range demands and reduced communication failures

- Harsh environment capability: EMI immunity, high temperature, high pressure, high voltage

- · No grounding required

- Intrinsically safe, small size, and lightweight

- Integrated telemetry: fiber itself is a data link

- · Wide bandwidth and high sensitivity

# 1.4.4 Ethernet Speed

Initially, fiber with Ethernet was operated at a 10-Mbps speed, more than enough bandwidth to move data in the substation. As noted above, the trend now is to use fiber at a 100-Mbps speed because there is no longer a cost premium for 100 Mb. However, 100 Mb will soon be a necessity. Three major changes in substation operations are driving the need for a 100-Mbps full-duplex Ethernet speed: security, time synchronization per IEC61850, and redundancy.

Security: Substations are a vital part of essential public services. Pressures to secure facilities continue to grow. An example of an increasingly popular security tool is video surveillance. Video requires roughly 5 Mb of bandwidth to support one uncompressed picture-quality full-motion video image data stream. A 100-Mbps Ethernet environment can easily accommodate several security cameras without compromising other LAN traffic.

Time Synchronization per IEC61850: One of the areas the emerging IEC61850 standard addresses is the data movement associated with sampling and digitization of voltage and current measurements within a substation. Protection IEDs base their decisions on current and voltage samples, measured by other IEDs. The sample data must be moved and synchronized within a few milliseconds to assure proper decisions, and thus assure proper relay and power switching operations. Within a substation, typically 25 to 75 IEDs will be transmitting time-critical sample data. This high data rate can be handled reliably in a single common network by 100-Mbps full-duplex multi-casts Ethernet over fiber media, possibly with multiple VLAN segments in larger substations.

10

Redundancy: The mission-critical communications services for substations need a high level of availability. Within the Ethernet network serving a substation, redundancy is fairly easy to achieve. Networked devices may be sequentially connected by fiber cabling in a ring structure, with any two segments of a ring able to recover from any fault in the ring. With dual-ported IEDs and dual redundant rings, even multiple faults will typically not cause problems from loss of data connectivity. The ring topology—connecting multiple substation devices in series—drives up the bandwidth required in the ring and 100-Mbps full-duplex Ethernet can handle the load.

#### 1.5 PTP

IEEE Standard 1588-2008 specifies the second generation of PTP, which is also known as "PTPv2" or "1588v2". This is capable of very accurate time synchronization by using special Ethernet hardware that records the exact time a PTP synchronization message is received at the Ethernet card. This information can compensate for the uncertainty introduced by real-time operating systems and other processing delays in both the synchronization master and the devices that are to be synchronized. The time-stamping hardware does not affect the operation of any other protocols running over Ethernet, so the same port can be used for IEC 61850, DNP3, IEC 60870-5-104, Modbus/IP, and other substation automation protocols. The PTP-specific hardware does marginally increase the cost of Ethernet switches. Native support for PTP is only available in the latest generation of protection relays and may be an option to be specified at the time of order (depending on the vendor). PTP supports multiple master-capable clocks, but these vote amongst themselves to choose a single clock to be the "grandmaster". If the grandmaster fails or suffers degraded performance any other master-capable clock on the network will step up to be the grandmaster if it has better accuracy. The time required for this does vary; however, if PTP settings (known as a "profile") optimized for the power industry are used, this is usually less than 5 seconds.

# 1.5.1 PTP Clock Types

- Grandmaster: Synchronized with an external source as a GPS satellite (GPS clocks).

- Ordinary clock: Can act either a master or a slave (protection relay). In most network implementations, the clocks remain in the Slave state and only become master when the grandmaster fails.

- Transparent clock: Corrects the time information before forwarding it without synchronizing itself (managed Ethernet switch).

- Boundary clock: Acts as a slave to the upstream master clock, and master clock to downstream slave clocks (managed Ethernet switch).

The PTP clocks can be either one-step or two-step ones; their mixing should be avoided. Two-step clocks send sync messages (which contain the approximate time) and follow-up messages (which contain a more precise value of when the sync message left the clock). One-step clocks do not send follow-up messages. Instead, the sync message carries a precise time stamp. The one-step mode is preferable.

#### 1.5.2 IEEE 1588 Standard

IEEE 1588 is a standard for a precision clock synchronization protocol for networked measurement and control systems. This defines a PTP designed to synchronize real-time clocks in a hierarchical distributed system. IEEE 1588 features include:

- Intended for LAN using multicast communications

- · Targeted accuracy of microseconds or sub-microsecond

- IEEE 1588v1 originally was designed for time distribution for the measurement and control industry.

- IEEE 1588v2 is designed to distribute frequency and time to a higher accuracy and precision, to the scale of nanoseconds and fractional nanoseconds.

- The protocol operates over packet switched networks. The standard is currently defined to run over IEEE 802.3, UDP/IPv4, UDP/IPv6, DeviceNet, ControlNet, and PROFINET.

- Designed to operate automatically to establish master-slave hierarchy for time distribution. (not for the telecommunications industry)

- Introduces "transparent clocks" to overcome the network's delay variation.

# 1.5.2.1 Applications

Version\_1 of the protocol is used for applications in:

- Industries (for example, Automation)

- · Test and measurement

- · Power networks

- Military and Avionic

Version\_2 (released June 2008) is made for applications in:

Telecom

12

- Broadcasting

- · Power and Utilities

# 1.6 Other Features of IEEE 1588 Ethernet PHY

# 表 2. DP83630 — Additional Features

| FEATURES                       | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Internal loopback              | The DP83630 includes a Loopback Test mode for facilitating system diagnostics. The Loopback mode is selected through bit 14 (Loopback) of the Basic Mode Control Register (BMCR). Writing 1 to this bit enables MII transmit data to be routed to the MII receive outputs. Loopback status may be checked in bit 3 of the PHY Status Register (PHYSTS). While in Loopback mode the data will not be transmitted onto the media. To ensure that the desired operating mode is maintained, autonegotiation should be disabled before selecting the Loopback mode.                                |

| Energy detect mode             | When Energy Detect is enabled and there is no activity on the cable, the DP83630 will remain in a low power mode while monitoring the transmission line. Activity on the line will cause the DP83630 to go through a normal power up sequence. Regardless of cable activity, the DP83630 will occasionally wake up the transmitter to put ED pulses on the line, but will otherwise draw as little power as possible. Energy detect functionality is controlled via register Energy Detect Control (EDCR), address 1Dh.                                                                        |

|                                | The DP83630 contains several system diagnostic capabilities for evaluating link quality and detecting potential cabling faults in twisted pair cabling.                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Link diagnostic capabilities   | These capabilities include:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Link diagnostic capabilities   | Linked Cable Status                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                | Link Quality Monitor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                | Time Domain Reflectometry (TDR) Cable Diagnostics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Polarity reversal              | The DP83630 detects polarity reversal by detecting negative link pulses. Inverted polarity indicates the positive and negative conductors in the receive pair are swapped. Since polarity is corrected by the receiver, this does not necessarily indicate a functional problem in the cable. Since the polarity indication is dependent on link pulses from the link partner, polarity indication is only valid in 10-Mb modes of operation, or in 100-Mb autonegotiated mode. Polarity indication is not available in 100-Mb forced mode of operation or in a parallel detected 100-Mb mode. |

| Cable swap indication          | As part of autonegotiation, the DP83630 has the ability (using Auto-MDIX) to automatically detect a cable with swapped MDI pairs and select the appropriate pairs for transmitting and receiving data. Normal operation is termed MDI, while crossed operation is MDIX.                                                                                                                                                                                                                                                                                                                        |

| 100-Mb cable length estimation | The DP83630 provides a method of estimating cable length based on electrical characteristics of the 100-Mb link. This essentially provides an effective cable length rather than a measurement of the physical cable length. The cable length estimation is only available in 100-Mb mode of operation with a valid link status.                                                                                                                                                                                                                                                               |

#### 1.7 Selection of Ethernet PHY

#### 表 3. TI Ethernet PHY

| ETHERNET PHY PART NUMBER | APPLICATION                                                                            |  |

|--------------------------|----------------------------------------------------------------------------------------|--|

| DP83848                  | 10BASE-T and 100BASE-TX Copper Interface                                               |  |

| DP83620                  | 10BASE-T and 100BASE-TX and 100BASE-FX Fiber Interface                                 |  |

| DP83630/DP83640          | 10BASE-T and 100BASE-TX and 100BASE-FX Fiber Interface with IEEE 1588 PTP capabilities |  |

| DP83849                  | Dual Port 10/100-Mbps Ethernet PHY Transceiver for use as Media Converter              |  |

# 1.8 TIDA-00496 Advantage

The TIDA-00496 demonstrates the following functionalities:

- 10/100-Mbps communication with copper interface using RJ45

- IEEE 802.3 100BASE-FX interface with LC-type transceiver

- DP83630 supports IEEE 1588 real-time Ethernet applications by providing hardware support for three time-critical elements.

- IEEE 1588 synchronized clock generation

- Packet timestamps for clock synchronization

- Event triggering and timestamping through GPIO

- IEEE 1588 V1 and V2 Supported

- Interface to Tiva ARM® MCU using TIDA-00226

- Onboard regulator

- Uses DP83649 for media conversion (copper to fiber) to test FO interface

This design demonstrates using TI Ethernet PHY with IEEE 1588 PTP capabilities for communication and time synchronization. This design demonstrates the communication with commonly used interfaces like copper or fiber. This design fits in a small form factor and can be further optimized based on the application configuration.

# **Key System Specifications**

# 表 4. Key System Specifications

| COMPONENT                | ADDITIONAL INFORMATION                                                                                                                                                                                                                                                                       |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ethernet PHY             | DP83630 Ethernet PHY features:  • DP83630 Precision PHYTER™ IEEE 1588 PTP Transceiver  • MII or RMII: Resistor strapping options  • Configurable PHY addresses: Resistor strapping options  • Single register access for complete PHY status  • Industrial temperature rating: −40°C to 85°C |

| Power supply             | Single 3.3 V ± 0.3 V supply                                                                                                                                                                                                                                                                  |

| Power supply input       | Possible power input options are:                                                                                                                                                                                                                                                            |

| Media interface          | Copper: 10/100 Mbps<br>Fiber: 100 Mbps                                                                                                                                                                                                                                                       |

| Power consumption        | Ethernet PHY with copper interface: < 350 mW Ethernet PHY with fiber interface: < 350 mW Transceiver: < 1.1 W                                                                                                                                                                                |

| Internal loop back       | The loopback function enables MII transmit data to be routed to the MII receive data path.                                                                                                                                                                                                   |

| MAC controller interface | 50-terminal MII interface connector                                                                                                                                                                                                                                                          |

| Clock                    | The design has three options to provide clock to DP8630K:      25-MHz crystal with internal oscillator     External oscillator to generate the clock (not populated)      Using Tl's CDCE913PW and a 25-MHz crystal to generate the clock over I²C lines (not populated)                     |

| Status LEDs              | LED_ACT, LED_Link, LED_Speed                                                                                                                                                                                                                                                                 |

| ESD                      | IEC61000-4-2 Level 2, Criterion B                                                                                                                                                                                                                                                            |

www.tij.co.jp Block Diagram

# 3 Block Diagram

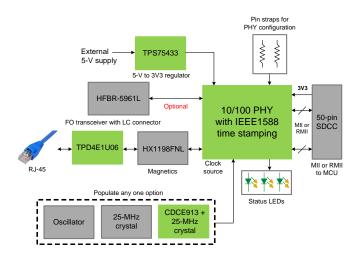

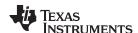

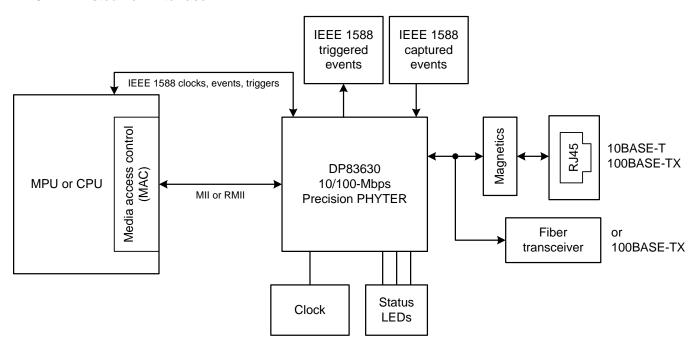

図 1. Ethernet Brick Block Diagram

Block Diagram www.tij.co.jp

#### 3.1 Ethernet PHY — DP83630

The Ethernet PHY used in the design provides multiple functionalities:

- 1. Twisted Pair or FO communication Interface

- 2. Hardware assisted IEEE 1588 PTP

Having these functions integrated into one device enables easy migration for customers from a simple Ethernet interface to a PTP-enabled Ethernet interface.

The DP83630 Precision PHYTER™ device delivers the highest level of precision clock synchronization for real-time industrial connectivity based on the IEEE 1588 standard. The DP83630 has deterministic low latency and allows the choice of MCU with no hardware customization required. The integrated IEEE 1588 functionality allows system designers the flexibility and precision of a close to the wire timestamp. The three key IEEE 1588 features supported by the device are:

- · Packet time stamps for clock synchronization

- Integrated IEEE 1588 synchronized low jitter clock generation

- Synchronized event triggering and time stamping through GPIO

The DP83630 offers innovative diagnostic features unique to Texas Instruments, including dynamic monitoring of link quality during standard operation for fault prediction. These advanced features allow the system designer to implement a fault prediction mechanism to detect and warn of deteriorating and changing link conditions. This single-port fast Ethernet transceiver can support both copper and fiber media.

| PARAMETER                   | VALUE                                                 |

|-----------------------------|-------------------------------------------------------|

| Manufacturer part number    | DP83630                                               |

| Description                 | DP83630 Precision PHYTER IEEE 1588<br>PTP Transceiver |

| Туре                        | Transceiver                                           |

| Protocol                    | MII, RMII                                             |

| Number of drivers/receivers | 1/1                                                   |

| Supply voltage              | 3 to 3.6 V                                            |

| Operating temperature       | -40°C to 85°C                                         |

表 5. Key Specifications for DP83630

The DP83630 pins are classified into the following interface categories (each interface is described in the sections that follow):

- Serial management interface (SMI)

- MAC data interface

- · Clock interface

- LED interface

- · GPIO interface

- JTAG interface

- Reset and power down

- Strap options

16

- 10/100-Mbps PMD interface

- Power and ground pins

www.tij.co.jp Block Diagram

The major features of the Ethernet PHY are described as follows:

#### MAC interface

The DP83630 supports several modes of operation using the MII pins. The options are defined in the following sections and include:

- MII Mode

- RMII Mode

- Single Clock MII Mode (SCMII)

In addition, the DP83630 supports the standard 802.3u MII SMI.

The modes of operation can be selected by strap options or register control. For RMII Slave mode, use the strap option because it requires a 50-MHz clock instead of the normal 25 MHz. In each of these modes, the IEEE 802.3 SMI is operational for device configuration and status. The SMI of the MII allows for the configuration and control of multiple PHY devices, gathering of status, error information, and the determination of the type and capabilities of the attached PHYs. The current design uses MII.

#### Architecture

The Ethernet PHY supports the following communication architecture:

- 100BASE-TX Transmitter

- 100BASE-TX Receiver

- 100BASE-FX Operation

- 10BASE-T Transceiver Module

#### LED interface

The DP83630 supports three configurable LED pins:

- LED\_LINK

- LED\_SPEED/FX\_SD

- LED ACT

#### PHY address

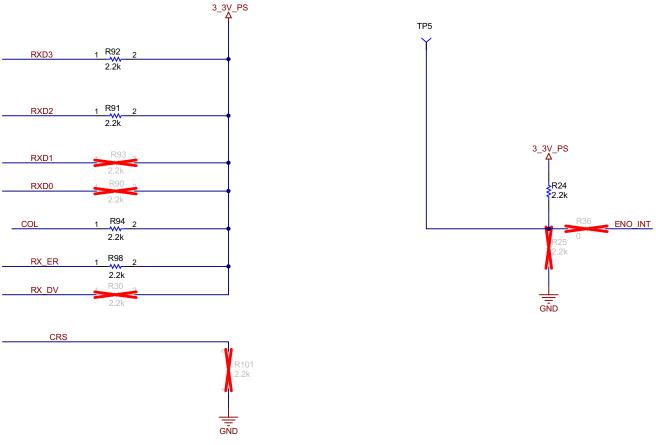

The five PHY address strapping pins are shared with the RXD[3:0] pins and COL pin.

The DP83630 can be set to respond to any of 32 possible PHY addresses through strap pins. The information is latched into the PHYCR register (address 19h, bits [4:0]) at device power-up and hardware reset. Each DP83630 or port sharing an MDIO bus in a system must have a unique physical address.

The DP83630 uses many of the functional pins as strap options to place the device into specific modes of operation. The values of these pins are sampled at power up or hard reset. During software resets, the strap options are internally reloaded from the values sampled at power up or hard reset. The strap option pin assignments are defined in  $\gtrsim$  6. The functional pin name is indicated in parentheses. Use a 2.2-k $\Omega$  resistor for pulldown or pullup to change the default strap option. If the default option is required, then there is no need for external pullup or pulldown resistors. Because these pins may have alternate functions after reset is deasserted, do not directly connect them to VCC or GND.

### 表 6. Comparison of DP83630 and DP83640

| PARAMETER          | DP83630 | DP83640 |

|--------------------|---------|---------|

| Function           | PHY     | PHY     |

| Port count         | Single  | Single  |

| Supply voltage (V) | 3.3     | 3.3     |

| Data rate (Mbps)   | 10/100  | 10/100  |

Block Diagram www.tij.co.jp

| PARAMETER        | DP83630                                    | DP83640                                          |

|------------------|--------------------------------------------|--------------------------------------------------|

| Special Features | IEEE 1588 PTP FX support Cable diagnostics | IEEE 1588 PTP<br>FX support<br>Cable diagnostics |

| Pin/Package      | 48WQFN                                     | 48LQFP                                           |

表 6. Comparison of DP83630 and DP83640 (continued)

Choosing between the DP83630 and DP83640 is based on the application need as the difference is package only.

#### 3.1.1 MII — MAC DATA INTERFACE

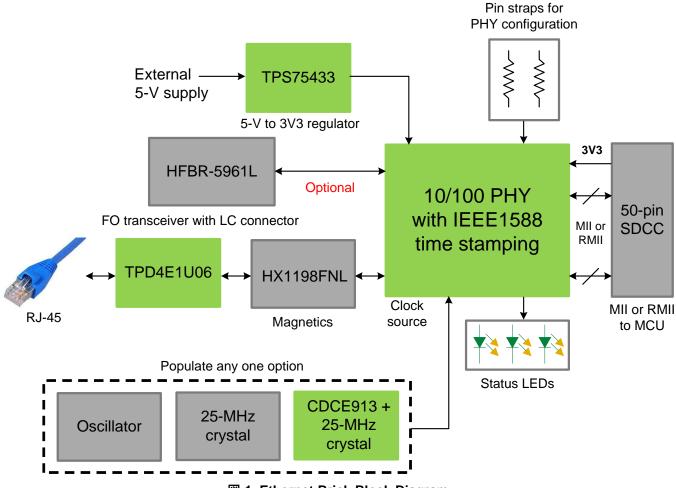

図 2. MII Signaling

The MII signals are as follows:

18

- MII transmit clock: 25-MHz transmit clock output in 100-Mbps mode or 2.5 MHz in 10-Mbps mode derived from the 25-MHz reference clock. The MAC should source TX\_EN and TXD[3:0] using this clock

- MII transmit enable: Active high input indicates the presence of valid data inputs on TXD[3:0]

- MII transmit data: Transmit data MII input pins, TXD[3:0], that accept data synchronous to the TX\_CLK (2.5 MHz in 10-Mbps mode or 25 MHz in 100-Mbps mode)

- MII receive clock: Provides the 25-MHz recovered receive clocks for 100-Mbps mode and 2.5 MHz for 10-Mbps mode

- MII receive data valid: Asserted high to indicate that valid data is present on the corresponding RXD[3:0]

www.tij.co.jp Block Diagram

MII receive error: Asserted high synchronously to RX\_CLK to indicate that an invalid symbol has been detected within a received packet in 100-Mbps mode

- MII receive data: Nibble wide receive data signals driven synchronously to the RX\_CLK (25 MHz for 100-Mbps mode, 2.5 MHz for 10-Mbps mode). RXD[3:0] signals contain valid data when RX\_DV is asserted

- MII carrier sense: Asserted high to indicate the receive medium is non-idle

- MII collision detect: Asserted high to indicate detection of a collision condition (simultaneous transmit and receive activity) in 10-Mbps and 100-Mbps half duplex modes

The interface to the controller is through a 50-pin high-speed connector. Male connector is mounted on the controller board and the female is on the Ethernet PHY Brick board. The connector has the MII signals and the power input (5-V or 3.3-V DC).

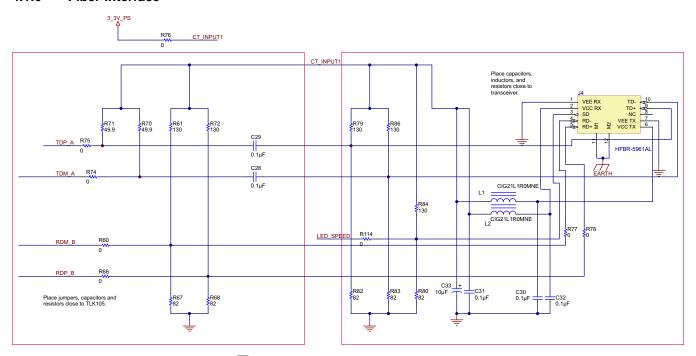

#### 3.1.2 Fiber Network Interface for 100BASE-FX

The HFBR-5961L transceiver provides the system designer with a product to implement a range of solutions for multimode fiber Fast Ethernet and SONET OC-3 (SDH STM-1) physical layers for ATM and other services. This transceiver is supplied in the industry standard 2x5 DIP style with an LC fiber connector interface with an external connector shield (HFBR-5961L).

#### 3.1.2.1 Transmitter Section

The transmitter section of the HFBR-5961L uses a 1300-nm InGaAsP LED. This LED is packaged in the optical subassembly portion of the transmitter section. It is driven by a custom silicon IC, which converts differential PECL logic signals, ECL referenced (shifted) to a 3.3-V supply, into an analog LED drive current.

### 3.1.2.2 Receiver Section

The receiver section of the HFBR-5961L uses an InGaAs PIN photodiode coupled to a custom silicon trans impedance preamplifier IC. It is packaged in the optical subassembly portion of the receiver. This pin and preamplifier combination is coupled to a custom quantizer IC, which provides the final pulse shaping for the logic output and the Signal Detect function. The Data output is differential. The Signal Detect output is single ended. Both Data and Signal Detect outputs are PECL compatible, ECL referenced (shifted) to a 3.3-V power supply. The receiver outputs, Data Output and Data Out Bar, are squelched at the Signal Detect deassert. That is, when the light input power decreases to a typical –38 dBm or less, the Signal Detect deasserts, meaning the Signal Detect output goes to a PECL low state. This forces the receiver outputs, Data Out and Data Out Bar to go steady PECL levels high and low, respectively.

| PARAMETER                | VALUE                      |

|--------------------------|----------------------------|

| Manufacturer part number | HFBR-5961LZ                |

| Description              | TXRX MMF FE SONET OC-3 2X5 |

| Data rate                | 155 MBd                    |

| Wavelength               | 1300 nm                    |

| Applications             | Ethernet                   |

| Voltage supply           | 3.3 V                      |

| Connector type           | LC duplex                  |

| Mounting type            | Through hole               |

表 7. Fiber Transceiver Key Specifications

Block Diagram www.tij.co.jp

Alternative FO Transceiver modules include:

- Avago HFBR-5961ALZ

- Avago HFBR-57E5APZ

- Avago AFBR-59E4APZ

20

www.tij.co.jp Block Diagram

# 3.1.3 Twisted Pair Interface (Copper) With ESD Protection Using TPD4E1U06DCK

#### 3.1.3.1 ESD Diodes

The ESD rating for DP83630 is 8 kV (at RZAP = 1.5 k $\Omega$  and CZAP = 120 pF). The network or Medium Dependent Interface (MDI) connection is through the transmit (TX+ and TX-) and receive (RX+ and RX-) differential pair terminals. The transmit and receive terminals connect to a termination network, then to a 1:1 magnetics (transformer), then to ESD protection devices and an RJ45 connector. This design uses the TPD4E1U06 as for ESD protection in between the RJ45 connector and the isolation transformer. The TPD4E1U06 is a quad-channel ultra-low capacitance TVS diode. It offers a ±15-KV IEC air-gap and ±15-KV contact discharge ESD protection compliant to IEC61000-4-2.

| PARAMETER                                 | VALUE                            |

|-------------------------------------------|----------------------------------|

| Manufacturer part number                  | TPD4E1U06DCKR                    |

| Description                               | TVS DIODE 5.5VWM 15VC SC70-6     |

| Unidirectional channels                   | 4                                |

| Voltage—Reverse standoff (Typ)            | 5.5 V (Max)                      |

| Voltage—Breakdown (Min)                   | 6.5 V                            |

| Voltage clamping (Max) at I <sub>PP</sub> | 15 V (Typ)                       |

| Current peak pulse (10/1000 µs)           | 3 A (8/20 μs)                    |

| Power peak pulse                          | 45 W                             |

| Power line protection                     | Yes                              |

| Applications                              | Ethernet, HDMI                   |

| Operating temperature                     | -40°C to 125°C (T <sub>A</sub> ) |

| Mounting type                             | Surface mount                    |

表 8. ESD Diode Key Specifications

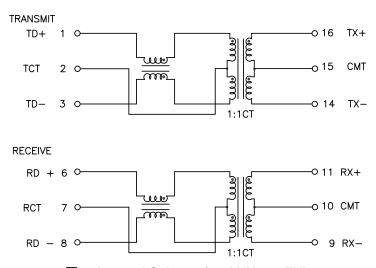

# 3.1.3.2 Isolation Transformer

This reference design uses a shielded RJ45 connector without internal isolation transformer. RJ45 is the standard cable used for all the Ethernet and LAN applications.

An external isolation transformer is interfaced. The design uses HX1198FNL (MODULE XFRMR SGL ETHR LAN 16SOIC) from Pulse Electronics. It is a 1:1 transformer with an isolation of 1.5 kV<sub>RMS</sub> (for 60 seconds). Based on the application, it may be necessary to connect a common-mode choke along with the isolation transformer. HX1198FNL already has a common-mode transformer integrated into. 🗵 3 shows the internal schematic of HX1198FNL.

Block Diagram www.tij.co.jp

図 3. Internal Schematic of HX1198FNL

Block Diagram www.tij.co.jp

# 表 9. RJ45 Connector Key Specifications

| PARAMETER                    | VALUE                           |  |

|------------------------------|---------------------------------|--|

| Manufacturer part number     | 6116526-1                       |  |

| Description                  | CONN MOD JACK 8P8C R/A SHIELDED |  |

| Connector type               | Jack                            |  |

| Number of positions/contacts | 8p8c (RJ45, Ethernet)           |  |

| Number of ports              | 1                               |  |

| Number of rows               | 1                               |  |

| Mounting type                | Through hole                    |  |

| Orientation                  | 90° angle (Right)               |  |

| Termination                  | Solder                          |  |

| Shielding                    | Shielded                        |  |

| Ratings                      | Cat5                            |  |

| Features                     | Board guide                     |  |

| LED color                    | Does not contain LEDs           |  |

| Tab direction                | Down                            |  |

| Operating temperature        | −40°C to 85°C                   |  |

Block Diagram www.tij.co.jp

#### 3.2 Host MCU With MII — TM4C129XNCZAD

The Tiva TM4C129XNCZAD is an ARM Cortex™-M4-based MCU with 1024KB flash memory, 256KB SRAM, 120-MHz operation, USB host/device/OTG, Ethernet controller, integrated Ethernet PHY, hibernation module, and a wide range of other peripherals. An internal multiplexer allows different peripheral functions to be assigned to each of these GPIO pads. When adding external circuitry, consider the additional load on the development board's power rails. The Tiva PinMux Utility can quickly develop pin assignments and the code required to configure them. The TM4C129XNCZAD MCU is factory programmed with a quick start weather display program. The quick start program resides in on-chip flash memory and runs each time power is applied, unless the application has been replaced with a user program.

#### Performance

- ARM Cortex-M4F processor core, 120-MHz operation

- 150 DMIPS performance, 1024KB flash memory

- 256KB single-cycle system SRAM, 6 KB of EEPROM

- Communication interfaces

- Eight universal asynchronous receivers and transmitters (UARTs)

- Four quad synchronous serial interface (QSSI) modules with bi-, quad-, and advanced SSI support

- Ten I<sup>2</sup>C modules with four transmission speeds, including a high-speed mode

- Two controller area network (CAN) 2.0 A/B controllers

- 10/100 Ethernet MAC

- Ethernet PHY with IEEE 1588 PTP hardware support

- USB 2.0 OTG/host/device with a ULPI-interface option and link power management (LPM) support

- Analog support

- Two 12-bit analog-to-digital converter (ADC) modules, each with a maximum sample rate of one million samples per second

- · Operating range (ambient)

- Industrial (–40°C to 85°C) temperature range

- Extended (–40°C to 105°C) temperature range

- One JTAG module with integrated ARM Serial Wire Debug (SWD)

- 212-ball BGA package

24

TM4C129XNCZAD supports the following Ethernet interfaces:

- 10/100-Mbps Ethernet interface with internal MAC and PHY

- 10/100-Mbps Ethernet interface with external MAC and internal PHY. The external MAC is interfaced with the MII/RMII

www.tij.co.jp Block Diagram

#### 3.3 Fiber-to-Ethernet Media Converter — DP83489

The DP83849IF is a dual industrial temperature PHY with fiber support (FX), which does not need any software conflagration to function as a copper-to-fiber media converter.

The dual Ethernet PHY features:

- Low-power 3.3-V, 0.18-μm CMOS technology detection

- Low power consumption: < 600 mW typical</li>

- 3.3-V MAC interface and filters

- Auto-MDIX for 10/100 Mbps

- IEEE 802.3u PCS, 100BASE-TX transceivers

- IEEE 802.3u 100BASE-FX fiber interface

- Dynamic link quality monitoring

- Flexible MII port assignment

- Integrated ANSI X3.263-compliant TP-PMD

- TDR-based cable diagnostic and cable length physical sub-layer with adaptive equalization detection and baseline wander compensation

- Optimized latency for real-time Ethernet

- Programmable LED support for link, 10/100-Mbps operation mode, activity, duplex, and collision

- Single register access for complete PHY

- SNI (configurable) status

- MII SMI (MDC and MDIO)

- 80-pin TQFP package (12×12 mm)

The DP83849IF pins are classified into the following interface (See the DP83849IF datasheet for details):

- SMI

- MAC data interface

- Clock interface

- LED interface

- JTAG interface

- · Reset and power down

- Strap options

- 10/100-Mbps PMD interface

- · Special connect pins

- · Power and ground pins

# 3.4 Power Supply

The Ethernet PHY operates on a single supply. The Ethernet brick board can be powered by:

- External 5 V

- 5 V from the host board (TIDA-00226)

- 3.3 V from the host board (TIDA-00226)

Block Diagram www.tij.co.jp

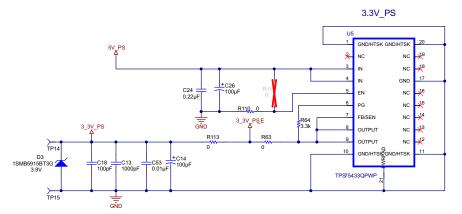

The TPS75433, Single-Output LDO, 2.0-A, Fixed 3.3 V with Fast Transient Response is used when the board is configured for a fiber interface. The power supply from the host MCU board (TPS62177 28-V, 0.5-A Step-Down Converter) is used for copper interface.

www.tij.co.jp Block Diagram

# 3.4.1 Single-Output LDO — TPS75433

The TPS752xxQ and TPS754xxQ devices are low-dropout regulators with integrated power-on reset and power good (PG) functions respectively. These devices are capable of supplying 2 A of output current with a dropout of 210 mV (TPS75233Q, TPS75433Q). Quiescent current is 75  $\mu$ A at full load and drops down to 1  $\mu$ A when the device is disabled. These devices are designed to have fast transient response for larger load current changes.

The TPS754xxQ and TPS752xxQ are offered in 1.5 V, 1.8 V, 2.5 V, and 3.3 V fixed-voltage versions and in an adjustable version (programmable over the range of 1.5 to 5 V). Output voltage tolerance is specified as a maximum of 2% over line, load, and temperature ranges. The TPS754xxQ and TPS752xxQ families are available in a 20-pin TSSOP (PWP) package.

#### Features:

- 2-A low-dropout voltage regulator

- Available in 1.5-V, 1.8-V, 2.5-V, and 3.3-V fixed output and adjustable versions

- Open drain power-on reset with 100-ms delay (TPS752xxQ)

- Open drain PG status output (TPS754xxQ)

- Dropout voltage typically 210 mV at 2 A (TPS75233Q)

- Ultralow 75-μA typical quiescent current

- Fast transient response

- 2% tolerance over specified conditions for fixed-output versions

- 20-pin TSSOP PowerPAD™ (PWP) package

- Thermal shutdown protection

# 4 Ethernet Brick Design Theory

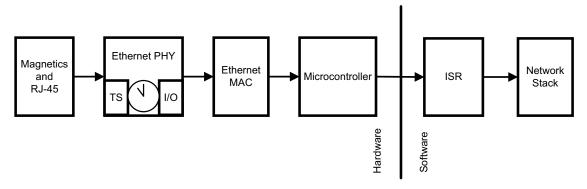

#### 4.1 Ethernet PHY

#### 4.1.1 PHY Interface

28

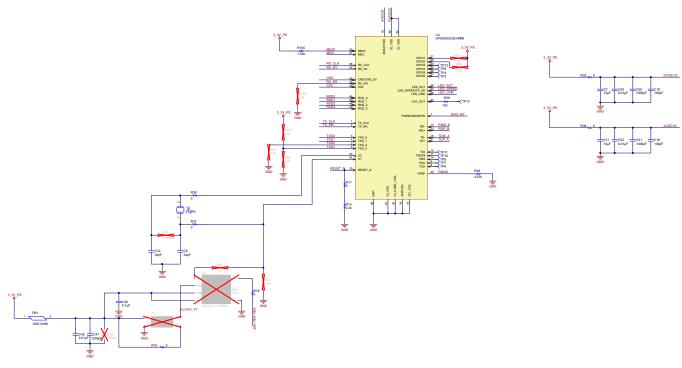

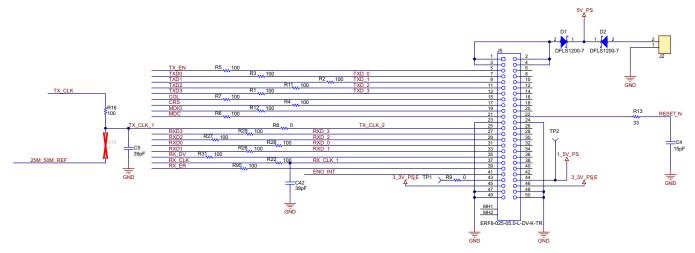

☑ 4 shows the DP83630 Brick configured for 10/100-Mbps communication using MII. A 25-MHz crystal (default) oscillator is connected. There are other clock options provided. The DP83630 package is WQFN. Alternatively, the DP83640, which is LQFP, can be used.

The PHY has general purpose I/Os (GPIOs) with the following functionality:

- GPIO 3,4,8,9: These pins may be used to signal or detect events.

- GPIO1: CLK\_OUT OUTPUT ENABLE: When high, enables clock output on the CLK\_OUT pin at power-up

- GPIO2: PHY CONTROL FRAME ENABLE: When high, allows the DP83630 to respond to PHY Control Frames

図 4. DP83630 PHY

注: 図 4 is configured for copper. When fiber interface is required, R100 is populated.

# 4.1.2 PHY Bootstrap Configuration

For a copper interface, the brick has been configured as shown in 表 10:

表 10. Interface Selection

| PIN NAME | FUNCTIONALITY | CONFIGURATION         |

|----------|---------------|-----------------------|

| RX_DV    | MII Mode      | PD                    |

| RX_ER    | FX ENABLE     | PU—Copper<br>PD—Fiber |

The PHY ID programmed is 7 as shown in 表 11:

表 11. PHY ID Configuration

| PIN NAME | FUNCTIONALITY | CONFIGURATION |

|----------|---------------|---------------|

| PHYAD0   | COL           | PU            |

| PHYAD1   | RXD_3         | PU            |

| PHYAD2   | RXD_2         | PU            |

| PHYAD3   | RXD_1         | PD            |

| PHYAD4   | RXD_0         | PD            |

図 5. Pin Strap Options

注: R98 is not populated for a fiber configuration.

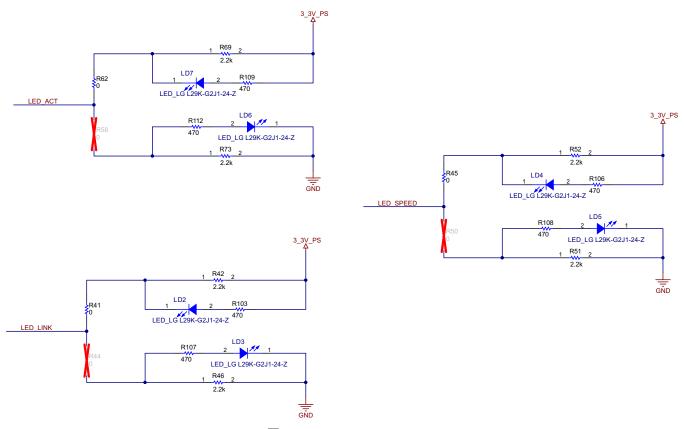

# 4.1.3 LEDs

30

The DP83630 supports three configurable LED pins: LED\_LINK, LED\_SPEED/FX\_SD, and LED\_ACT. The LEDs support two operational modes, which are selected by the LED mode strap. Because these LED pins are also used as strap options, the polarity of the LED is dependent on whether the pin is pulled up or down.

図 6. LED Configuration

注: R45 is not populated for a fiber option.

# 4.1.4 Cable Specifications

The specifications in  $\frac{12}{5}$  are for the FO cable that is used to test the communication with a media converter.

表 12. FO Cable Specifications

| PARAMETER                | VALUE                           |

|--------------------------|---------------------------------|

| Manufacturer part number | DK-2632-02                      |

| Description              | Cable fiber optic dual LC-SC 2M |

| First connector          | LC duplex                       |

| Second connector         | SC duplex                       |

| Cable diameter           | 0.12" (3.0 mm)                  |

| Cable type               | Buffered fiber                  |

| Fiber type               | 62.5/125                        |

| Length (overall)         | 6.56' (2.0 m)                   |

| Type                     | Multimode, duplex               |

| Color (cable)            | Orange                          |

| Color (connectors)       | Black, red                      |

32

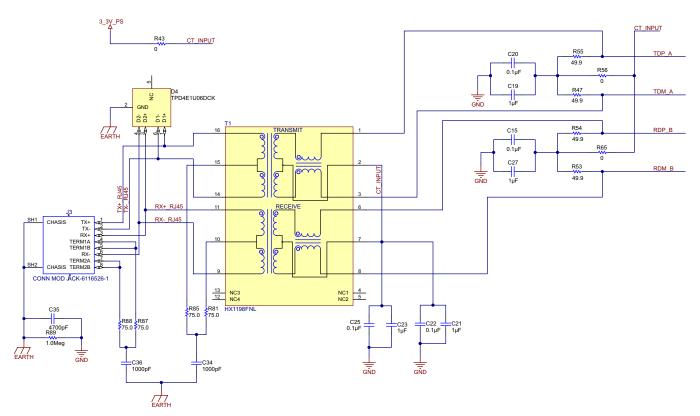

# 4.1.5 Twisted Pair Interface

図 7. DP83630 Functional Diagram

The DP83630 supports both twister pair (100BASE-TX and 10BASE-T) and Fiber (100BASE-FX) media. The port may be configured for twisted pair (TP) or fiber (FX) operation by strap option or by register access. At power-up or reset, the state of the RX\_ER pin will select the media for the port. The default selection is twisted pair mode, while an external pulldown will select FX mode of operation.

図 8. Twisted Pair (Copper) Interface for DP83630 PHY

注: The TVS diode array for ESD protection is provided across the RJ45 connector. In some of the applications based on testing, the TVS diode array is moved after the isolation transformer. This change needs to be verified for surge, ESD, and other EMC tests before implementing.

# 4.1.6 Fiber Interface

図 9. FO Interface for DP83630 PHY

The HFBR-5961L transceiver datasheet from Avago Technologies provides recommended decoupling and termination circuits and also alternative termination circuits. The design uses these recommended circuit and the TI EVM circuit. Any of these configuration can be populated.

#### 4.1.7 MII to Host

図 10. Interface Connector to Host MCU

The MII signals have been provided with 100R termination. Additionally, many of the MII signals have 50R internal termination. These terminations have been provided for improving EMI performance (radiated emission). The use of only internal termination or a combination of Internal and external termination can be optimized based on performance and EMI testing.

#### 4.1.8 Host MCU Interface

The 32-bit ARM Cortex-M4F MCU-Based Small Form Factor Serial-to-Ethernet Converter TI Design has been used as the host to test Ethernet communication interface. Find more information is available at the TIDA-00226 product page.

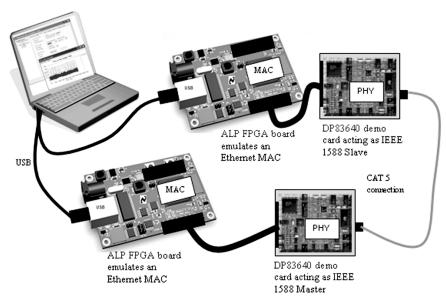

#### IEEE 1588 Stack for Testing PTP Time Stamping Functionality

PTP daemon (PTPd) implements the PTP as defined by "IEEE Std 1588-2002" (also known as PTP version 1). PTPd can coordinate the clocks of a group of LAN connected computers with each other. Check with TI Industrial to get the updated files for PTP implementation and make the following changes:

- 1. Download and install latest TivaWare<sup>™</sup>. Example path at the default location: *C:\ti\TivaWare\_C\_Series-2.1.0.12573\third\_party*

- 2. Add the *third\_party > fatfs*, *third\_party > lwip-1.4.1*, *third\_party > ptpd-1.1.0*, and the sub-directories to project Include path.

- 3. Replace the following files in *third\_party > lwip-1.4.1* with the ones from the downloaded TIDA-00496 project:

- lwip-1.4.1\ports\tiva-tm4c129\include\netif\tivaif.h

- lwip-1.4.1\ports\tiva-tm4c129\netif\tiva-tm4c129.c

- lwip-1.4.1\ports\tiva-tm4c129\sys arch.c

- lwip-1.4.1\src\core\ipv4\ip.c

- 4. Replace the following files in *third\_party > ptpd-1.1.0* with the ones from the downloaded TIDA-00496 project:

- ptpd-1.1.0\src\dep\datatypes\_dep.h

- ptpd-1.1.0\src\dep\msg.c

- ptpd-1.1.0\src\dep\net.c

- ptpd-1.1.0\src\dep-tiva\ptpd msg.c

- ptpd-1.1.0\src\dep-tiva\ptpd net.c

- ptpd-1.1.0\src\dep-tiva\ptpd\_servo.c

- ptpd-1.1.0\src\arith.c

- ptpd-1.1.0\src\datatypes.h

- ptpd-1.1.0\src\probe.c

36

ptpd-1.1.0\src\protocol.c

## 4.2 Power Supply

The Ethernet PHY operates on a single supply. The Ethernet PHY brick board can be powered by:

- External 5 V

- 5 V from the host board (TIDA-00226)

- 3.3 V from the host board (TIDA-00226)

The TPS75433, Single Output LDO, 2.0-A, Fixed 3.3 V with Fast Transient Response is used when the board is configured for fiber interface. The power supply from the host MCU board (TPS62177 28-V, 0.5-A Step-Down Converter) is used for the copper interface.

A 2-A LDO has been provided on the board. When the board is tested for copper interface the DC-DC converter on the serial-to-Ethernet converter can power the brick and so the onboard LDO output is disabled by depopulating R63. When the communication interface is tested with fiber, the current requirement is more; to source, the required current onboard LDO is used. Populate R63 to use the onboard LDO.

The output current capacity of the regulator is 2 A. This can be used to power any other application that has a 3.3-V power supply.

図 11. Regulator for PHY and FO Transceivers

# 4.3 Design Configuration for Twisted Pair (Copper) and Fiber Interface

The Ethernet brick provides board configurations for the following functionalities:

- Twisted pair (copper) interface

- · Fiber interface

To make the design easy to use, two sets of design files have been provided: One for a copper interface and the other for a fiber interface. The design is the same except that the DNI components applicable for copper and fiber have been clearly identified. The functionality for copper or fiber can be tested with same PCB by assembling components as per respective BOM.

#### 4.4 Design Guidelines

#### 4.4.1 Reducing Radiated Emissions in 10/100-Mbps Ethernet LAN Applications

PHYTER products are designed to limit EMI in system implementations in three ways:

- 1. Analog and digital power distribution systems are intentionally partitioned, both externally and within the component, to reduce cross functional noise that can result in EMI.

- 2. Key analog blocks within the component are designed and tested to meet specific ground and power supply noise rejection targets, further reducing the effects of cross functional noise.

- 3. In some PHYTER products, including DP83849 and DP83630/DP83640 products, integrated series terminations are provided on digital signal drivers, reducing I/O related EMI.

In addition to these designed in advantages, key recommendations for designing reduced EMI applications include:

- Use high quality CAT5E or better cable in implementing network systems. If possible use shielded

- Use shielded network connectors connected to a decoupled chassis ground plane.

- Use equal length differential MDI signal traces with a strip line impedance of 50  $\Omega$ .

- Carefully match the values and placement of MDI termination components.

- Use a common mode choke component in conjunction with the isolation transformer.

- Place local bypass components (including capacitors and optionally ferromagnetic beads) between device supply pins and power sourcing vias on PCBs.

- Reduce the energy of digital signal sources by including series termination resistors in signal paths (series resistors on all MII signals).

#### 4.4.2 Clock IN (X1) Recommendations

The DP83630 supports an external CMOS level oscillator source or a crystal resonator device.

Oscillator

If an external clock source is used, X1 should be tied to the clock source and X2 should be left floating. For RMII Slave Mode, the 50-MHz oscillator is used.

Crystal

38

A 25-MHz, parallel, 20-pF load crystal resonator should be used if a crystal source is desired. The load capacitor values will vary with the crystal vendors; check with the vendor for the recommended loads. The oscillator circuit is designed to drive a parallel resonance AT cut crystal with a minimum drive level of 100 μW and a maximum of 500 μW. If a crystal is specified for a lower drive level, a current limiting resistor should be placed in series between X2 and the crystal.

www.tij.co.jp Firmware

#### 5 Firmware

# 5.1 Ethernet Brick Configuration

### 表 13. PHY Functionality Configuration

| FUNCTIONALITY                      | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Hardware reset                     | A hardware reset is accomplished by applying a low pulse (TTL level), with a duration of at least 1 $\mu s$ , to RESET_N. This pulse resets the device such that all registers are reinitialized to default values, and the hardware configuration values are re-latched into the device (similar to the power-up/reset operation). The time from the point when the reset terminal is de-asserted to the point when the reset has concluded internally is approximately 200 $\mu s$ . |

|                                    | Set the external PHY address. (All the read and write requests to the PHY shall use the configured external PHY address). To reset the MII PHY:                                                                                                                                                                                                                                                                                                                                        |

| External MII PHY mitialization     | Set the BMCR (0x00) register bit 15 to one.                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| External Will FITT ITIItialization | <ul> <li>Set the BMCR (0x00) register to auto negotiation enable and auto negotiation restart by<br/>setting bit 12 and bit 8 to one.</li> </ul>                                                                                                                                                                                                                                                                                                                                       |

|                                    | <ul> <li>Poll the BMSR (0x01) register bit 5 to check if autonegotiation is complete.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                       |

| MII_MODE                           | The MII_MODE is selected by pin 32 (RX_DV). This terminal has internal weak pull down defaults to MII mode. An external pull-up makes the PHY to operate in RMII mode.                                                                                                                                                                                                                                                                                                                 |

| PHY ID                             | PHY ADDRESS [4:0]: The DP83630 provides five PHY address pins, the state of which is latched into the PHYCTRL register at system Hardware-Reset. The DP83630 supports PHY Address strapping values 0 (<00000>) through 31 (<11111>). Pin names are COL, RXD_3, RXD_2, RXD_1, RXD_0.                                                                                                                                                                                                    |

| PHYID                              | A 2.2-k $\Omega$ resistor should be used for pull-down or pull-up to change the default strap option. If the default option is required, then there is no need for external pull-up or pull down resistors. Since these pins may have alternate functions after reset is deasserted, they should not be connected directly to VCC or GND.                                                                                                                                              |

|                                    | The DP83630 supports three configurable LED pins.                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| LED configuration                  | LED_LINK, LED_SPEED, LED_ACT are the supported LED functionalities.                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 222 oomigaration                   | The LEDs support two operational modes, which are selected by the LED mode strap, and a third operational mode that is register configurable.                                                                                                                                                                                                                                                                                                                                          |

| TPI/fiber interface                | FX ENABLE: This strapping option enables 100BASE-FX (fiber) mode. This mode is disabled by default. An external pulldown will enable 100BASE-FX mode.                                                                                                                                                                                                                                                                                                                                  |

注: When fiber mode is enabled through strap, the other configuration (auto-negotiation disabled, SD option, LED configuration) occurs automatically. Note that the external strap resistors are only sampled upon power up or upon a reset via the RESET\_N pin.

If the fiber is configured via register access, write PHYCR2[9], SOFT\_RESET, after enabling or disabling fiber mode through register access to ensure correct configuration.

### 5.2 DP83630 Precision PHYTER Control Registers

#### 表 14. PHY Control Registers Including PTP Registers Configuration

| COMMANDS<br>(FUNCTIONALITY) | DESCRIPTION                                                                                                                                                             |              |                                           |

|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------------------------------------------|

|                             | FIELD                                                                                                                                                                   | BIT LOCATION | DESCRIPTION                               |

| Command format of           | Command type                                                                                                                                                            | 31:30        | Set to 01 for write<br>Set to 10 for read |

|                             | PHY address                                                                                                                                                             | 29:25        | Set to PHY address or to 0x1F (broadcast) |

| MDIO                        | Page select                                                                                                                                                             | 24:21        | Register page select                      |

|                             | Register address                                                                                                                                                        | 20:16        | Register address                          |

|                             | Write data                                                                                                                                                              | 15:0         | Write data                                |

| Reset PHY                   | Select PTP 1588 CONFIGURATION REGISTERS page4 by writing the value 0x0000 to PAGESEL (Page Select Register).  To reset PHY write the value 0x8000 to the BMCR register. |              |                                           |

Firmware www.tij.co.jp

# 表 14. PHY Control Registers Including PTP Registers Configuration (continued)

|                                                          | Control Registers including FTF Registers Configuration (Continued)                                                                                                                                                                                                                                                                                                                                                 |

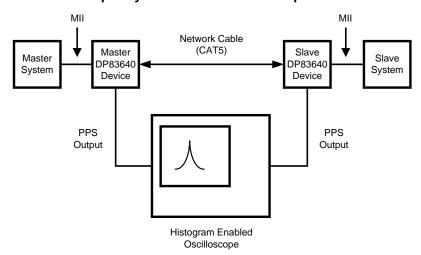

|----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|