# ディスクリート差動アンプと統合型差動アンプの比較

Esteban Garcia

Product marketing engineer

Jacob Nogaj

Applications engineer

オペアンプと抵抗ネットワークを使用して作成できる多くの有用な回路の1つが、差動アンプ(DA)です。DAsを使用すると、2つの信号の差を測定できます。これは、ソーラーパネル、パワーバンク、その他のDC/DCモジュールなど、システムの電流と電圧のセンシングに便利です。さらに、多くのDAsはゲインを適用し、信号に基準電圧を追加し、入力信号からの同相ノイズを低減できます。

DAsには、ディスクリート(外付け抵抗を使用)と統合型(モノリシック抵抗またはオンダイ抵抗を使用)の2つの主なタイプがあります。この記事では、測定データ(オフセット電圧、同相除去比CMRR、ゲイン誤差、温度範囲全体でのゲイン誤差ドリフト)を使用して、ディスクリートDAと統合型DAを比較します。

## ゲイン誤差

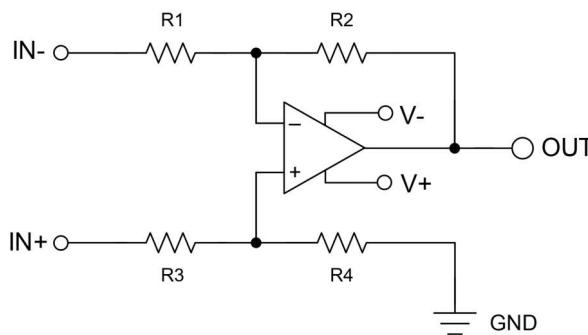

図1に示すように、標準的なDAはオペアンプと4つの抵抗で構成されています。R1/R2抵抗ラダーの中点はオペアンプの反転端子に接続され、R3/R4の中点は非反転端子に接続されます。

図1. 標準的なDA

式1に、標準的なDAの伝達関数を示します。ゲインは、R2とR1の比( $R1 = R3$ かつ $R2 = R4$ と想定)によって決定されることに注意してください。小さいゲイン誤差を達成しようとする場合、マッチング済みの抵抗が必要になります。公差 $\pm 1\%$ の抵抗は、最大2%のゲイン誤差を引き起こす可能性があります。ディスクリート抵抗は大きな変動を示しますが、統合型DAsに含まれるモノリシック抵抗は、多くの場合、わずか0.01%のゲイン誤差を実現するようにトリミングされています。

$$V_{\text{OUT}} = \left( V_{\text{IN}+} - V_{\text{IN}-} \right) \times \left( \frac{R_2}{R_1} \right) + V_{\text{REF}} \quad (1)$$

## ゲインドリフト

ゲインドリフトはもう1つの重要なパラメータです。特に、ソーラーパネル、モータードライブ、バッテリパックのようなシステムでは、1日中や動作中に温度が変動する可能性があります。TIのINA600 DAの薄膜抵抗はすべて同じパッケージ内にあり、互いにデジタル化されているため、4つの抵抗はすべて温度変動を等しく観測し、同じゲイン比を維持しながら一緒にドリフトします。外部抵抗を使用するディスクリート実装では、DAのゲインドリフト性能に大きなばらつきが生じることがあります。これは、温度によるストレスが基板の表面全体で勾配として現れ、入力信号に印加されるゲインの変化につながるためです。

## オフセット電圧

入力信号にゲインを印加するとき、オフセット電圧の大きさが output 信号に影響を及ぼす誤差の大きさに大きな影響を及ぼす可能性があります。そのため、電圧または電流のセンシングには、優れたオフセット電圧を持つオペアンプを選択することを推奨します。ディスクリート DA を構築する場合、設計のコアとして活用できるオペアンプを自由に選ぶ柔軟性があります。一方、統合型 DA のオフセット電圧は固定され、内部オペアンプに依存します。ただし、e-Trim™ オペアンプ技術などの抵抗トリミング手法を使用すると、統合型 DA でオフセット電圧を下げることができます。

## CMRR

DA を考慮する場合、電圧および電流センシング アプリケーションで同相信号を除去できる能力は主な要因です。ゲイン誤差と同様に、CMRR は使用する部品（抵抗など）のマッチングによって決まります。代表的なオペアンプの CMRR は最大 100dB である場合もありますが、ミスマッチの抵抗が原因で CMRR が最小 60dB 低下する可能性があるため、ノイズの多い環境の産業用システムには理想的ではありません。代表的な統合型 DA の CMRR は一般的に少なくとも 90dB ですが、最大で 130dB に達することもあります。

## レール電圧を超えた電圧監視が可能なゲイン構成

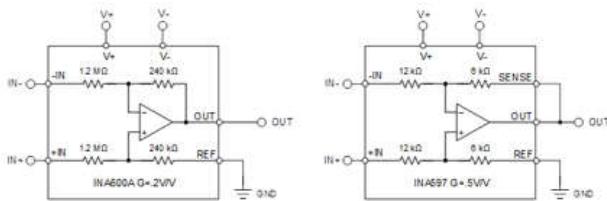

DAs は通常ユニティゲイン構成（ゲイン = 1）で使用されますが、0.5 ~ 2 の範囲で変化することができます。DA の抵抗ネットワークの値を変更することで、減衰を大きくして ADC の入力範囲（3.3V または 5V）まで電圧をスケールダウンする必要があるさまざまなアプリケーション向けに、幅広いゲイン比を実現できます。図 2 に示すように、抵抗ネットワークの値を変更すると、減衰が大きくなります。

図 2. INA600A DA と INA597 DA の比較

DAs の見過ごされている利点は、入力をレールを超えて行うことができることです。抵抗ラダーは DA の入力電圧を分圧

するため、統合型アンプの入力には減衰された電圧のみが印加されます。標準的なオペアンプを使用する場合、電源電圧は同相電圧範囲を制限します。この DA の柔軟性により、利用可能な電源レールが限られている場合でも、より高い電圧を監視するのに適しています。図 3 に示すように、入力電圧範囲は DA の推奨電源電圧を超えてさらに拡張されています。

6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                                    |                                                        | MIN                    | MAX                    | UNIT |

|------------------------------------|--------------------------------------------------------|------------------------|------------------------|------|

| Supply voltage $V_S = (V_+ - V_-)$ | Single-supply                                          | 2.7                    | 40                     | V    |

|                                    | Dual-supply                                            | ±1.35                  | ±20                    |      |

| Input voltage range                | Single-supply / Dual-supply                            | (V <sub>+</sub> ) - 40 | (V <sub>-</sub> ) + 85 | V    |

| C <sub>CSP</sub>                   | Bypass capacitor on the power supply pins (see note 1) | 0.1                    |                        | μF   |

| Specified temperature              | Specified temperature                                  | -40                    | 125                    | °C   |

図 3. INA600 DA の推奨動作条件

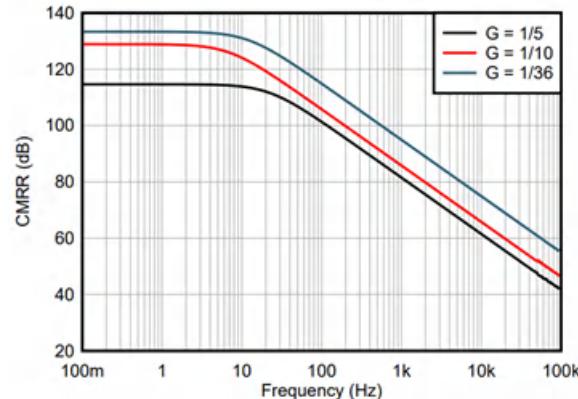

電力密度の高いシステムでは、プリント基板のパターンによって引き起こされるスイッチング周波数と寄生インダクタンスの増加が、同相ノイズを完全に除去できないため、電圧監視精度に影響を及ぼす追加の電圧の外乱につながる可能性があります。CMRR が高い統合型 DA を使用すると、入力間に観測される同相ノイズをすべて除去できますが、ディスクリート DA の外付け抵抗で高い CMRR を実現するのは難しく、特にゲイン比が高い場合には、抵抗のミスマッチによって困難になります。

式 2 に、寄生インダクタンスとスイッチング周波数が信号の電圧外乱の大きさにどのような影響を及ぼすかを示します：

$$V = L \times \frac{di}{dt} \quad (2)$$

図 4 に、統合型 DA の周波数帯域における CMRR 特性を示します。

図 4. INA600 DA の出力換算 CMRR と周波数との関係

## テスト設定と比較

CMRR とオフセット電圧誤差を、温度範囲全体にわたる各回路の相対的性能の指標として使用しました。各デバイスでは、高精度線源測定ユニットを DA の両方の入力ピンに接続し、キャリブレーションされた 8.5 枝のマルチメータを使用してオフセット電圧の変化を測定しました。デバイス性能を高精度で表現するために、5 回の平均化を行い、テストを実施しました。デバイスは、 $\pm 18V$  の分割電源構成で  $-35V$  から  $35V$  の同相電圧をスイープするようにデバイスを構成しました。オープンを使用して過熱テストを実施し、テストボード全体で一様な温度を確保するために十分な浸漬時間を確保しました。

中間電源で同相電圧を維持しながらデバイス入力の両端に差動電圧を強制的に印加すると、ゲイン誤差とゲイン誤差ドリフトの両方がテストされます。対応する入力範囲を持つ各デバイスをスイープすると、出力が強制的に  $-10V \sim +10V$  の範囲になります。この結果、対応するスロープと理想的なスロープを比較し、ゲイン誤差のパーセンテージを評価することができます。

表 1 で、CMRR の性能と、ディスクリート DA と 2 つの TI の統合型 DAs のオフセットを、さまざまな動作温度範囲で比較します。

| 温度 (°C) | ディスクリート DA |                   | INA600    |                   | INA597    |                   |

|---------|------------|-------------------|-----------|-------------------|-----------|-------------------|

|         | CMRR (dB)  | オフセット ( $\mu V$ ) | CMRR (dB) | オフセット ( $\mu V$ ) | CMRR (dB) | オフセット ( $\mu V$ ) |

| 125     | 73.06      | -237.88           | 98.33     | 801.82            | 102.66    | -26.12            |

| 85      | 71.89      | -285.95           | 100.12    | 661.56            | 103.70    | -10.22            |

| 25      | 70.35      | -221.42           | 101.63    | 582.19            | 100.33    | -3.24             |

| -40     | 73.26      | -206.95           | 106.82    | 500.60            | 105.97    | 13.4              |

表 1. CMRR とオフセット電圧の比較

表 2 は、異なる動作温度範囲にわたって、同じディスクリート DA と統合型 DAs でゲイン誤差とドリフト性能を比較します。

| 温度 (°C) | ディスクリート DA |         | INA600    |         | INA597    |         |

|---------|------------|---------|-----------|---------|-----------|---------|

|         | ゲイン誤差 (%)  | ゲインドリフト | ゲイン誤差 (%) | ゲインドリフト | ゲイン誤差 (%) | ゲインドリフト |

| 125     | 0.14806    | -237.88 | 98.33     | 801.82  | 102.66    | -26.12  |

| 85      | 71.89      | -285.95 | 100.12    | 661.56  | 103.70    | -10.22  |

| 25      | 70.35      | -221.42 | 101.63    | 582.19  | 100.33    | -3.24   |

| -40     | 73.26      | -206.95 | 106.82    | 500.60  | 105.97    | 13.4    |

表 2. ゲイン誤差とドリフトの比較

予想どおり、統合型 DAs はディスクリート DA に比べて高い CMRR、低いゲイン誤差、および低いゲイン誤差ドリフトを実現します。ディスクリート DA のオフセット電圧は統合型 DAs の 1 つを上回っていますが、ソフトウェア キャリブレーションによりこれを補償することができます。

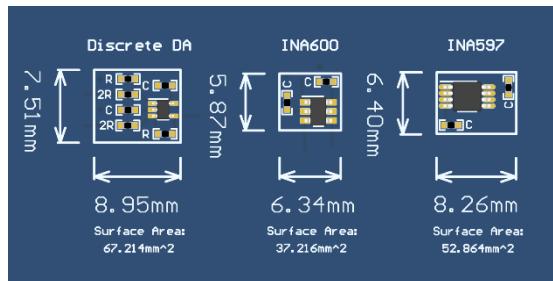

図 5 は、3 種類の DA バリエーションそれぞれのレイアウトを簡略化し、各ソリューションのサイズを比較します。比較のために最小のデバイス パッケージを使用し、抵抗とコンデンサは 0402 パッケージとしました。

図 5. サイズの比較

## まとめ

電圧センシングを実現する方法は多数ありますが、統合型 DA を採用することで、ディスクリート実装では実現できない優れた性能上の利点が得られます。TI の INA600 などの統合型 DAs では、オペアンプの電源電圧による入力電圧制限が影響しなくなり、高い減衰比により電源レールを超える電圧を柔軟に監視できます。

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Webツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適したTI製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているTI製品を使用するアプリケーションの開発の目的でのみ、TIはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TIや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TIおよびその代理人を完全に補償するものとし、TIは一切の責任を拒否します。

TIの製品は、[TIの販売条件](#)、[TIの総合的な品質ガイドライン](#)、[ti.com](#)またはTI製品などに関連して提供される他の適用条件に従い提供されます。TIがこれらのリソースを提供することは、適用されるTIの保証または他の保証の放棄の拡大や変更を意味するものではありません。TIがカスタム、またはカスタマー仕様として明示的に指定していない限り、TIの製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TIはそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025年10月