## Technical Article

## PFC の力率を改善する方法

Bosheng Sun

## はじめに

では [Power Tips #116](#)、力率補正 (PFC) の全高調波歪み (THD) を低減する方法について説明しました。この Power Tip では、PFC の性能を評価するもう一つの重要な基準について説明します。それは 力率 (Power Factor) であり、式 1 に示すように、二乗平均平方根 (RMS) 電流と RMS 電圧 (アンペア単位) の積です。

$$PF = \frac{\text{Real power}}{\text{Apparent power}} \quad (1)$$

力率は、AC 電源からどれだけ効率的にエネルギーを取り込んでいるかを示します。力率が低い場合、電力会社は実際に負荷が必要とする以上の電流を発生させなければならず、その結果、ブレーカや変圧器といった要素が過熱し、寿命の低下や公共電力インフラの維持コストの増加につながります。

理想的には力率は 1 であり、その場合、負荷は AC 電源から見て純粋な抵抗として振る舞います。しかし、実際の世界では、電気負荷は AC 電流波形に歪みを引き起こすだけでなく、AC 電流が AC 電圧に対して位相が進んだり遅れたりする原因にもなり、力率の低下を招きます。このため、力率は「歪み力率」と「位相差力率」の積として計算することができます。

$$PF = \frac{\cos\Phi}{\sqrt{1 + THD^2}} \quad (2)$$

ここで  $\phi$  は電流と電圧の位相差角を、THD は電流の全高調波歪みを表します。

THD の要求値が厳しくなるほど、力率の要求値も高くなります。[表 1](#) に、最近リリースされた [モジュール型ハードウェアシステム向け共通冗長電源\(M-CRPS\)](#) の基本仕様の 力率要件を示します。

表 1. M-CRPS 力率要件

| 出力電力 | 10% 負荷 | 20% 負荷 | 50% 負荷 | 100% 負荷 |

|------|--------|--------|--------|---------|

| 力率   | >0.92  | >0.96  | >0.98  | >0.99   |

式 2 が示すように、力率を改善するためにまず行うべきことは THD (全高調波歪み) を低減することです (この点については [Power Tips #116](#) で解説しました)。しかし、THD が低いからといって、必ずしも力率が高いとは限りません。PFC の AC 入力電流と AC 入力電圧が同相でなければ、たとえ電流波形が理想的な正弦波 (低 THD) であっても、位相角  $\phi$  によって力率は 1 未満になります。

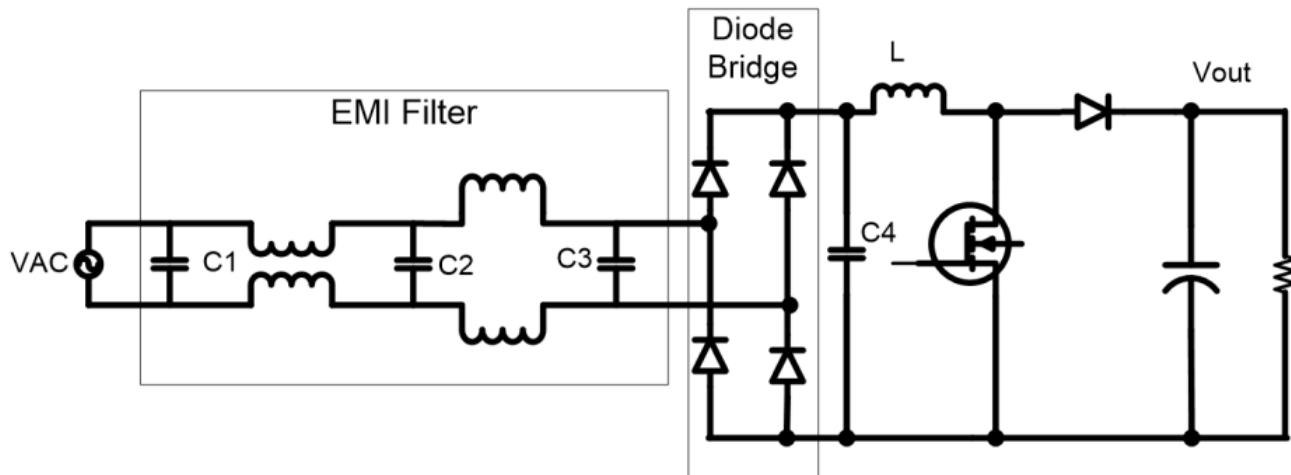

入力電流と入力電圧の位相差の主な原因は、PFC に使用される EMI フィルタ (電磁干渉フィルタ) です。[図 1](#) に、EMI フィルタ、ダイオードブリッジ整流器、昇圧コンバータの 3 つの主要な部分で構成される標準的な PFC 回路図を示します。

図 1. 典型的な PFC 回路図 (EMI フィルタ、ダイオードブリッジ整流器、ブーストコンバータで構成)。出典:テキサス・インスツルメンツ

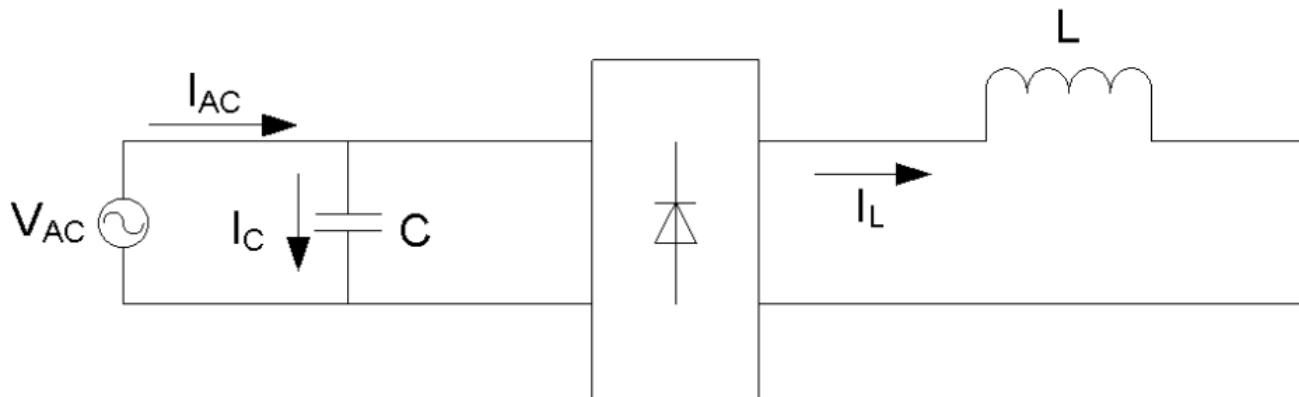

図 1 に示す通り、C1、C2、C3、C4 は EMI X コンデンサです。EMI フィルタ内のインダクタは、PFC 入力電流の位相を変化させません。したがって、図 2 C は C1、C2、C3、C4 の組み合わせとなるように簡略化でき 図 1 ます。

図 2. 簡略化した EMI フィルタ。ここで C は C1、C2、C3 の合成容量を表します。出典:テキサス・インスツルメンツ

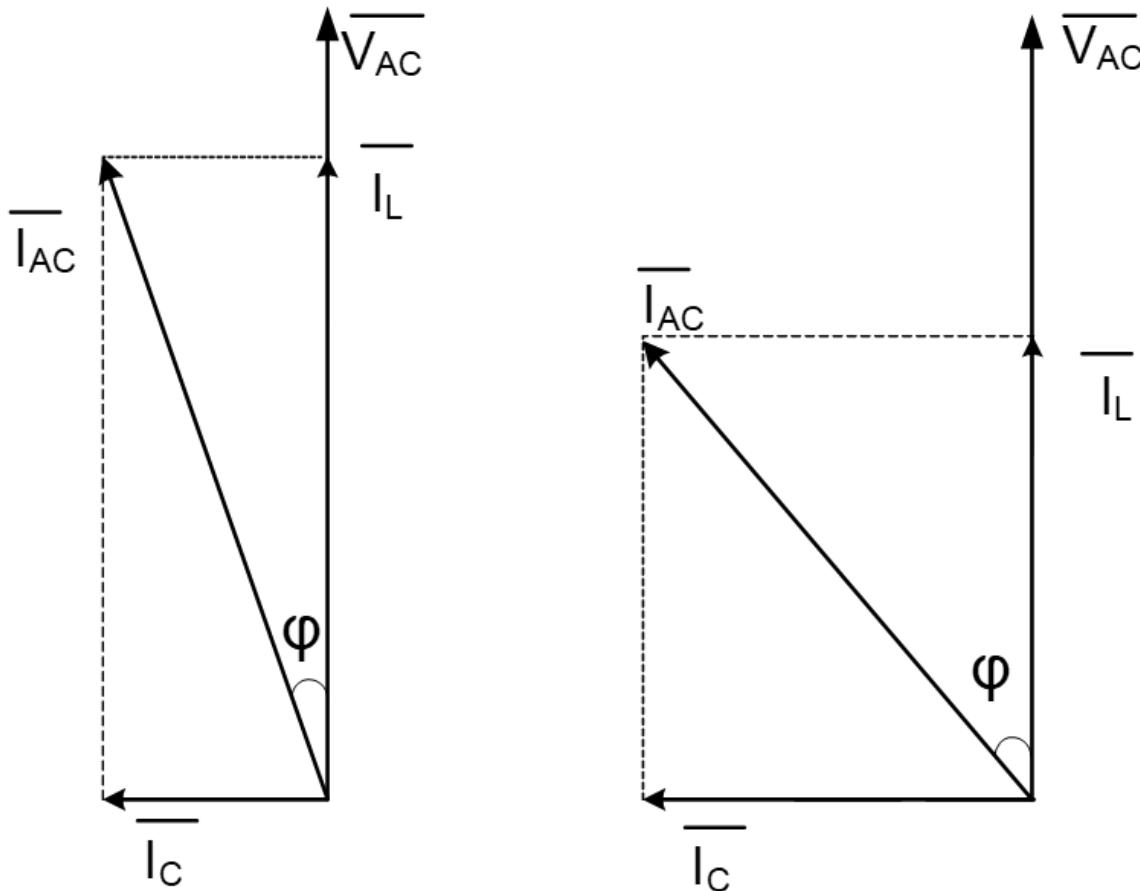

図 3 に示すとおり、X コンデンサは、AC 入力電流を AC 電圧より進ませる原因となります。PFC インダクタ電流は です  $\vec{I}_L$  入力電圧は です  $\vec{V}_{AC}$  また、X コンデンサのリアクティブ電流は です  $\vec{I}_C$  .PFC の総入力電流は です  $\vec{I}_{AC}$  これは、力率の測定元からの電流でもあります。PFC の電流制御ループはを強制的に行います  $\vec{I}_L$  に従います  $\vec{V}_{AC}$  の無効電流です  $\vec{I}_C$  はを導きます  $\vec{V}_{AC}$  を 90 度だけ変化させ、それによってが生じます  $\vec{I}_{AC}$  は、を導きます  $\vec{V}_{AC}$  .その結果、力率が低下します。

この効果は、のようく軽い負荷と高いラインで増幅されます。 $\vec{I}_C$  が全体の電流において、より大きな比重を占めます。その結果、力率が M-CRPS 仕様などの厳格な仕様を満たすのは困難です。

Heavy-load and low-line

Light-load and high-line

図 3. X コンデンサです  $\vec{I}_C$  によって AC 電流が AC 電圧を導きます。出典: テキサス・インスツルメンツ

幸いにも、デジタルコントローラを用いれば、次のいずれかの方法でこの問題を解決できます。

#### 方法 1:

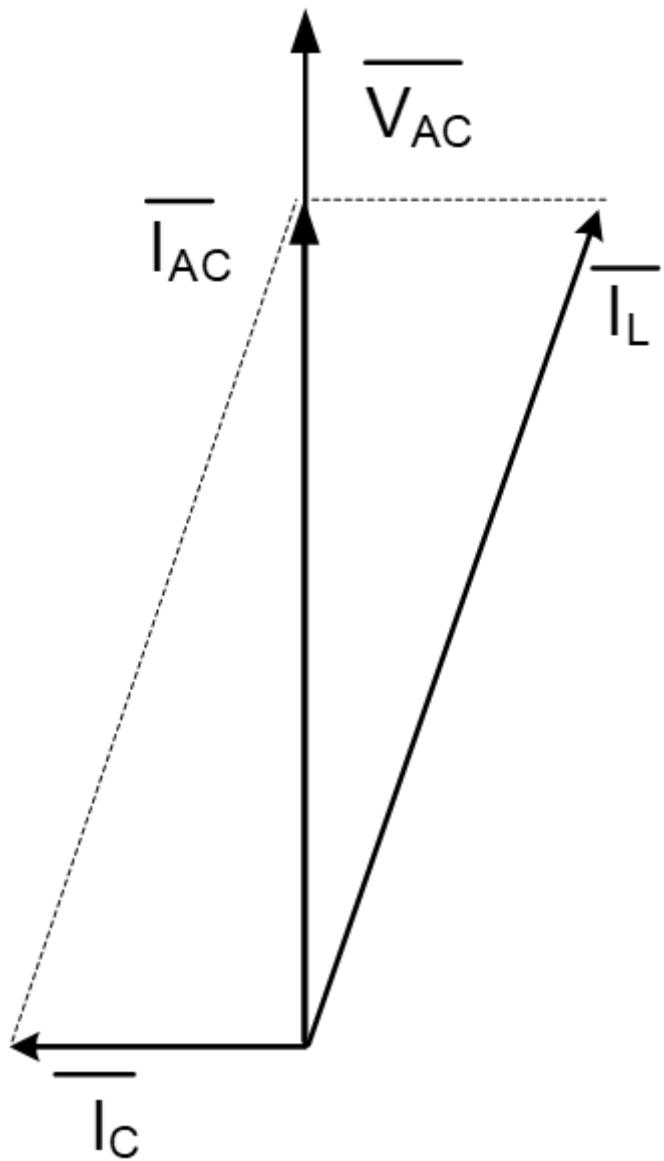

一方、 $\vec{I}_C$  を強制的に使用できる場合、合計電流が入力電圧につながります  $\vec{I}_L$  は、を遅らせます  $\vec{V}_{AC}$  ある程度低下します (図 4 を参照)。そして、は合計電流です  $\vec{I}_{AC}$  は入力電圧と位相を一致させるため、力率が改善します。

図 4. を強制する  $\overrightarrow{I_L}$  は、を遅らせます  $\overrightarrow{V_{AC}}$  合計電流がになります  $\overrightarrow{I_{AC}}$  は入力電圧と同相になります。出典:テキサス・インスツルメンツ

電流ループはインダクタ電流を基準値に追従させるため、を許容します  $\overrightarrow{I_L}$  は、を遅らせます  $\overrightarrow{V_{AC}}$  は、より遅れる必要がります  $\overrightarrow{V_{AC}}$ 。従来の平均電流モード制御を用いた PFC では、電流基準は式 3 によって生成されます。

$$I_{REF} = A * B * C \quad (3)$$

ここで、A は電圧ループ出力、B は  $1/V_{AC\_RMS}^2$ 、C は検出された入力電圧  $V_{AC}(t)$  です。

電流リファレンスを遅延させるため、A/D コンバータ (ADC) はを測定します  $\overrightarrow{V_{AC}}$  の測定結果は循環バッファーに保存されます。次に、最新の入力電圧 ( $V_{IN}$ ) データを使用する代わりに、式 3 で以前に保存されていた  $V_{IN}$  データを使用して、現在の瞬間の電流リファレンスを計算します。電流リファレンスはを遅らせます  $\overrightarrow{V_{AC}}$ 、そのとき電流ループはを実現します  $\overrightarrow{I_L}$  は、を遅らせます  $\overrightarrow{V_{AC}}$ 。これにより、先端 x コンデンサが補償されます  $\overrightarrow{I_C}$  と力率を改善することができます。

遅延時間は入力電圧と出力負荷に基づいて動的に調整する必要があります。入力電圧が低く、負荷が重いほど、必要な遅延は短くなります。それ以外の場合 になります  $\vec{I}_L$  が過度に遅延し、遅延がまったくない場合よりも力率が悪化します。この問題を解決するには、動作条件に基づいて遅延時間を正確かつ動的に調整するために、ルックアップテーブルを使用します。

## 方法 2:

力率の低下は、主に EMI X コンデンサによって発生します  $\vec{I}_C$ 、もしを計算すれば  $\vec{I}_C$  所定の X コンデンサ値と入力電圧に対して求め、その後を減算します  $\vec{I}_C$  理想的な合計入力電流から PFC 電流ループの新しい電流リファレンスを形成することで、入力電圧と位相が揃った総入力電流がより良くなり、良好な力率を実現できます。

詳細に説明するために、力率 1 の PFC の場合、 $\vec{I}_{AC}$  はと位相が同じです  $\vec{V}_{AC}$  式 4 に、入力電圧を示します。

$$v_{AC}(t) = V_{AC} \sin(2\pi f t) \quad (4)$$

ここで、 $V_{AC}$  は  $V_{IN}$  のピーク値、 $f$  はのピーク値、 $f$  は  $V_{IN}$  の周波数です。理想的な入力電流は、式 (5) で表されるように、入力電圧と完全に同相である必要があります。

$$i_{AC}(t) = I_{AC} \sin(2\pi f t) \quad (5)$$

ここで、 $I_{AC}$  は入力電流ピーク値です。

コンデンサの電流は であるからです  $i_C(t) = C \frac{dv_{AC}(t)}{dt}$  、式 6 を参照。

$$i_C(t) = 2\pi f C V_{AC} \cos(2\pi f t) \quad (6)$$

式 7 は、図 2 から取られています。

$$i_L(t) = i_{AC}(t) - i_C(t) \quad (7)$$

式 5、6、7 を組み合わせると、式 8 が得られます。

$$i_L(t) = I_{AC} \sin(2\pi f t) - 2\pi f C V_{AC} \cos(2\pi f t) \quad (8)$$

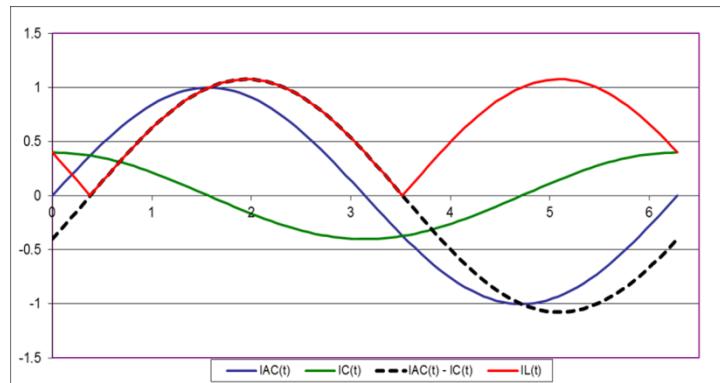

PFC 電流ループの電流リファレンスとして式 8 を使用する場合、EMI X コンデンサを完全に補償できます  $\vec{I}_C$  力率 1 を達成することができます。図 5 では、青の曲線は、推奨される入力電流  $i_{AC}(t)$  の波形であり、これはと同相です  $\vec{V}_{AC}$  緑の曲線は、コンデンサの電流  $i_C(t)$  であり、の特性から導かれます  $\vec{V}_{AC}$  の 90 度です。黒の点線の曲線は  $i_{AC}(t) \sim i_C(t)$  です。赤の曲線は整流された  $i_{AC}(t) \sim i_C(t)$  です。理論的には、PFC 電流ループがこの赤い曲線をリファレンスとして使用する場合、EMI X コンデンサを完全に補償できるようになります  $\vec{I}_C$  力率を大きくすることができます。

**図 5. 電流基準には  $i_{AC}(t)$  (青)、 $i_C(t)$  (緑)、 $i_{AC}(t) - i_C(t)$  (赤)、整流された  $i_{AC}(t) - i_C(t)$  (赤) が適用されます。出典: テキサス・インスツルメンツ**

式 (8) に示される電流基準を生成するためには、まず EMI X コンデンサの無効電流  $i_C(t)$  を計算する必要があります。デジタルコントローラを使用する場合、ADC が入力 AC 電圧をサンプリングし、その値を CPU が割り込みループ処理で一定周期ごとに読み取ります。式 9 で入力 AC ゼロクロスが連続した 2 つの ADC サンプル数を計算することで、式 9 で入力 AC 電圧の周波数を決定します。

$$f = \frac{f_{isr}}{2 * N} \quad (9)$$

ここで、 $f_{isr}$  は割り込みループの周波数、 $N$  は 2 つの連続する AC ゼロクロス中の ADC サンプル数です。

コサイン波形  $\cos(2\pi ft)$  を得るために、ソフトウェアフェーズロックループは、入力電圧と同期した内部正弦波を生成し、コサイン波形を取得できるようにします。式 (6) を用いて  $i_C(t)$  を計算し、それを式 (7) から差し引くことで、新しい電流基準が得られます。

### AC ゼロクロス領域での電流リファレンスの再形成

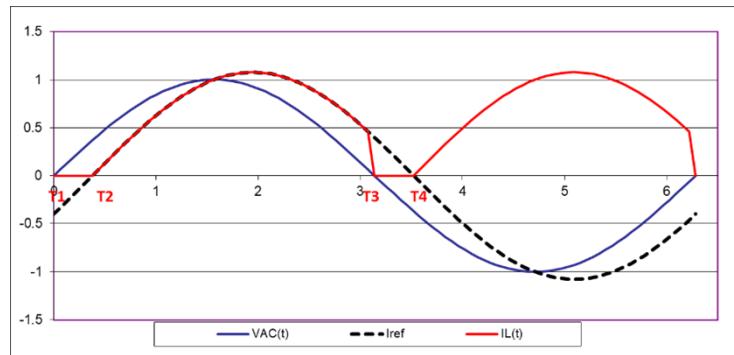

これら 2 つの方法では、を促進します  $\vec{i}_L$  は、を遅らせます  $\vec{V}_{AC}$  は力率を改善するためのものですが、AC ゼロクロッキング時に追加の電流ひずみを引き起こす可能性があります。図 6 を参照してください。PFC 電力段で使用されるダイオードブリッジ整流器のため、ダイオードは逆電流をすべて遮断します。図 6 を参照すると、T1 および T2 の間、 $V_{AC}(t)$  は正の半サイクルですが、予測される  $i_L(t)$  (黒色の点線) は負です。しかしこれは不可能です。なぜならダイオードが負の電流を遮断するため、この期間中、実際の  $i_L(t)$  はゼロのままだからです。同様に、T3 および T4 の間、 $V_{AC}(t)$  は負になりますが、予測される  $i_L(t)$  は正のままでです。この場合も、 $i_L(t)$  もダイオードによってブロックされ、ゼロのままでです。

したがって、これら 2 つの期間においては電流基準もゼロにする必要があります。そうでないと、制御ループ内の積分器が蓄積してしまいます。そして、2 つの期間が終了して電流が再び導通を開始すると、制御ループは必要以上に大きな PWM デューティ比を生成し、電流スパイクが発生します。図 6 の赤い曲線は、ダイオードブリッジを使用した場合の実際の  $i_L(t)$  を示しており、PFC 電流ループの電流リファレンスとして赤の曲線を使用する必要があります。

図 6. 赤の曲線は、ダイオードブリッジを使用する場合に実際の  $i_L(t)$  が何を示す最終的な電流リファレンス曲線であり、PFC 電流ループの電流リファレンスとして使用する必要があるかを示しています。出典: テキサス・インスツルメンツ

## 力率の最適化

力率の低下は主に PFC EMI フィルタで使用される X コンデンサによって引き起こされますが、インダクタ電流を遅延させることで X コンデンサの無効電流の影響を補償することができます。インダクタ電流を遅延させる 2 つの方法のいずれかを使用できるようになったので、Power Tips #116 のガイダンスと組み合わせて、高力率と低 THD の両方の要件を満たすことができます。

## 関連コンテンツ

- Power Tips #116: PFC の THD を低減する方法

- Power Tips #123: 二重昇圧コンバータを使用して、高変換比設計の電力範囲を拡張

- Power Tips #122: 1kW 高密度 LLC 電源モジュールに使用される平面トランスの概要

- Power Tips #121: アクティブ スナバを使用した位相シフトフル ブリッジ効率の改善

この記事は、以前 EDN.com で公開された記事です。

## 商標

すべての商標は、それぞれの所有者に帰属します。

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適したテキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているテキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、[テキサス・インスツルメンツの販売条件](#)、または [ti.com](#) やかかるテキサス・インスツルメンツ製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2025, Texas Instruments Incorporated

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月